Texas Instruments Sitara AM3359, Sitara AM3354, Sitara AM3352, Sitara AM3351, Sitara AM3357 User Manual

...Page 1

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

Reference

Design

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

AM335x Sitara™ Processors

1 Device Overview

1.1 Features

1

• Up to 1-GHz Sitara™ ARM®Cortex®-A8 32‑Bit

RISC Processor

– NEON™ SIMD Coprocessor

– 32KB of L1 Instruction and 32KB of Data Cache

With Single-Error Detection (Parity)

– 256KB of L2 Cache With Error Correcting Code

(ECC)

– 176KB of On-Chip Boot ROM

– 64KB of Dedicated RAM

– Emulation and Debug - JTAG

– Interrupt Controller (up to 128 Interrupt

Requests)

• On-Chip Memory (Shared L3 RAM)

– 64KB of General-Purpose On-Chip Memory

Controller (OCMC) RAM

– Accessible to All Masters

– Supports Retention for Fast Wakeup

• External Memory Interfaces (EMIF)

– mDDR(LPDDR), DDR2, DDR3, DDR3L

Controller:

• mDDR: 200-MHz Clock (400-MHz Data

Rate)

• DDR2: 266-MHz Clock (532-MHz Data Rate)

• DDR3: 400-MHz Clock (800-MHz Data Rate)

• DDR3L: 400-MHz Clock (800-MHz Data

Rate)

• 16-Bit Data Bus

• 1GB of Total Addressable Space

• Supports One x16 or Two x8 Memory Device

Configurations

– General-Purpose Memory Controller (GPMC)

• Flexible 8-Bit and 16-Bit Asynchronous

Memory Interface With up to Seven Chip

Selects (NAND, NOR, Muxed-NOR, SRAM)

• Uses BCH Code to Support 4-, 8-, or 16-Bit

ECC

• Uses Hamming Code to Support 1-Bit ECC

– Error Locator Module (ELM)

• Used in Conjunction With the GPMC to

Locate Addresses of Data Errors from

Syndrome Polynomials Generated Using a

BCH Algorithm

• Supports 4-, 8-, and 16-Bit per 512-Byte

Block Error Location Based on BCH

Algorithms

• Programmable Real-Time Unit Subsystem and

Industrial Communication Subsystem (PRU-ICSS)

1

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

– Supports Protocols such as EtherCAT®,

PROFIBUS, PROFINET, EtherNet/IP™, and

More

– Two Programmable Real-Time Units (PRUs)

• 32-Bit Load/Store RISC Processor Capable

of Running at 200 MHz

• 8KB of Instruction RAM With Single-Error

Detection (Parity)

• 8KB of Data RAM With Single-Error

Detection (Parity)

• Single-Cycle 32-Bit Multiplier With 64-Bit

Accumulator

• Enhanced GPIO Module Provides ShiftIn/Out Support and Parallel Latch on

External Signal

– 12KB of Shared RAM With Single-Error

Detection (Parity)

– Three 120-Byte Register Banks Accessible by

Each PRU

– Interrupt Controller (INTC) for Handling System

Input Events

– Local Interconnect Bus for Connecting Internal

and External Masters to the Resources Inside

the PRU-ICSS

– Peripherals Inside the PRU-ICSS:

• One UART Port With Flow Control Pins,

Supports up to 12 Mbps

• One Enhanced Capture (eCAP) Module

• Two MII Ethernet Ports that Support

Industrial Ethernet, such as EtherCAT

• One MDIO Port

• Power, Reset, and Clock Management (PRCM)

Module

– Controls the Entry and Exit of Stand-By and

Deep-Sleep Modes

– Responsible for Sleep Sequencing, Power

Domain Switch-Off Sequencing, Wake-Up

Sequencing, and Power Domain Switch-On

Sequencing

– Clocks

• Integrated 15- to 35-MHz High-Frequency

Oscillator Used to Generate a Reference

Clock for Various System and Peripheral

Clocks

• Supports Individual Clock Enable and

Disable Control for Subsystems and

Peripherals to Facilitate Reduced Power

Consumption

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Page 2

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

www.ti.com

• Five ADPLLs to Generate System Clocks

(MPU Subsystem, DDR Interface, USB and

Peripherals [MMC and SD, UART, SPI, I2C],

L3, L4, Ethernet, GFX [SGX530], LCD Pixel

Clock)

– Power

• Two Nonswitchable Power Domains (RealTime Clock [RTC], Wake-Up Logic

[WAKEUP])

• Three Switchable Power Domains (MPU

Subsystem [MPU], SGX530 [GFX],

Peripherals and Infrastructure [PER])

• Implements SmartReflex™ Class 2B for

Core Voltage Scaling Based On Die

Temperature, Process Variation, and

Performance (Adaptive Voltage Scaling

[AVS])

• Dynamic Voltage Frequency Scaling (DVFS)

• Real-Time Clock (RTC)

– Real-Time Date (Day-Month-Year-Day of Week)

and Time (Hours-Minutes-Seconds) Information

– Internal 32.768-kHz Oscillator, RTC Logic and

1.1-V Internal LDO

– Independent Power-on-Reset

(RTC_PWRONRSTn) Input

– Dedicated Input Pin (EXT_WAKEUP) for

External Wake Events

– Programmable Alarm Can be Used to Generate

Internal Interrupts to the PRCM (for Wakeup) or

Cortex-A8 (for Event Notification)

– Programmable Alarm Can be Used With

External Output (PMIC_POWER_EN) to Enable

the Power Management IC to Restore Non-RTC

Power Domains

• Peripherals

– Up to Two USB 2.0 High-Speed OTG Ports

With Integrated PHY

– Up to Two Industrial Gigabit Ethernet MACs (10,

100, 1000 Mbps)

• Integrated Switch

• Each MAC Supports MII, RMII, RGMII, and

MDIO Interfaces

• Ethernet MACs and Switch Can Operate

Independent of Other Functions

• IEEE 1588v2 Precision Time Protocol (PTP)

– Up to Two Controller-Area Network (CAN) Ports

• Supports CAN Version 2 Parts A and B

– Up to Two Multichannel Audio Serial Ports

(McASPs)

• Transmit and Receive Clocks up to 50 MHz

• Up to Four Serial Data Pins per McASP Port

With Independent TX and RX Clocks

• Supports Time Division Multiplexing (TDM),

Inter-IC Sound (I2S), and Similar Formats

• Supports Digital Audio Interface

Transmission (SPDIF, IEC60958-1, and

AES-3 Formats)

• FIFO Buffers for Transmit and Receive (256

Bytes)

– Up to Six UARTs

• All UARTs Support IrDA and CIR Modes

• All UARTs Support RTS and CTS Flow

Control

• UART1 Supports Full Modem Control

– Up to Two Master and Slave McSPI Serial

Interfaces

• Up to Two Chip Selects

• Up to 48 MHz

– Up to Three MMC, SD, SDIO Ports

• 1-, 4- and 8-Bit MMC, SD, SDIO Modes

• MMCSD0 has Dedicated Power Rail for

1.8‑V or 3.3-V Operation

• Up to 48-MHz Data Transfer Rate

• Supports Card Detect and Write Protect

• Complies With MMC4.3, SD, SDIO 2.0

Specifications

– Up to Three I2C Master and Slave Interfaces

• Standard Mode (up to 100 kHz)

• Fast Mode (up to 400 kHz)

– Up to Four Banks of General-Purpose I/O

(GPIO) Pins

• 32 GPIO Pins per Bank (Multiplexed With

Other Functional Pins)

• GPIO Pins Can be Used as Interrupt Inputs

(up to Two Interrupt Inputs per Bank)

– Up to Three External DMA Event Inputs that can

Also be Used as Interrupt Inputs

– Eight 32-Bit General-Purpose Timers

• DMTIMER1 is a 1-ms Timer Used for

Operating System (OS) Ticks

• DMTIMER4–DMTIMER7 are Pinned Out

– One Watchdog Timer

– SGX530 3D Graphics Engine

• Tile-Based Architecture Delivering up to 20

Million Polygons per Second

• Universal Scalable Shader Engine (USSE) is

a Multithreaded Engine Incorporating Pixel

and Vertex Shader Functionality

• Advanced Shader Feature Set in Excess of

Microsoft VS3.0, PS3.0, and OGL2.0

• Industry Standard API Support of Direct3D

Mobile, OGL-ES 1.1 and 2.0, OpenVG 1.0,

and OpenMax

• Fine-Grained Task Switching, Load

Balancing, and Power Management

• Advanced Geometry DMA-Driven Operation

for Minimum CPU Interaction

2

Device Overview Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 3

www.ti.com

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

• Programmable High-Quality Image AntiAliasing

• Fully Virtualized Memory Addressing for OS

Operation in a Unified Memory Architecture

– LCD Controller

• Up to 24-Bit Data Output; 8 Bits per Pixel

(RGB)

• Resolution up to 2048 × 2048 (With

Maximum 126-MHz Pixel Clock)

• Integrated LCD Interface Display Driver

(LIDD) Controller

• Integrated Raster Controller

• Integrated DMA Engine to Pull Data from the

External Frame Buffer Without Burdening the

Processor via Interrupts or a Firmware Timer

• 512-Word Deep Internal FIFO

• Supported Display Types:

– Character Displays - Uses LIDD

Controller to Program these Displays

– Passive Matrix LCD Displays - Uses LCD

Raster Display Controller to Provide

Timing and Data for Constant Graphics

Refresh to a Passive Display

– Active Matrix LCD Displays - Uses

External Frame Buffer Space and the

Internal DMA Engine to Drive Streaming

Data to the Panel

– 12-Bit Successive Approximation Register

(SAR) ADC

• 200K Samples per Second

• Input can be Selected from any of the Eight

Analog Inputs Multiplexed Through an 8:1

Analog Switch

• Can be Configured to Operate as a 4-Wire,

5-Wire, or 8-Wire Resistive Touch Screen

Controller (TSC) Interface

– Up to Three 32-Bit eCAP Modules

• Configurable as Three Capture Inputs or

Three Auxiliary PWM Outputs

– Up to Three Enhanced High-Resolution PWM

Modules (eHRPWMs)

• Dedicated 16-Bit Time-Base Counter With

Time and Frequency Controls

• Configurable as Six Single-Ended, Six DualEdge Symmetric, or Three Dual-Edge

Asymmetric Outputs

– Up to Three 32-Bit Enhanced Quadrature

Encoder Pulse (eQEP) Modules

• Device Identification

– Contains Electrical Fuse Farm (FuseFarm) of

Which Some Bits are Factory Programmable

• Production ID

• Device Part Number (Unique JTAG ID)

• Device Revision (Readable by Host ARM)

• Debug Interface Support

– JTAG and cJTAG for ARM (Cortex-A8 and

PRCM), PRU-ICSS Debug

– Supports Device Boundary Scan

– Supports IEEE 1500

• DMA

– On-Chip Enhanced DMA Controller (EDMA) has

Three Third-Party Transfer Controllers (TPTCs)

and One Third-Party Channel Controller

(TPCC), Which Supports up to 64

Programmable Logical Channels and Eight

QDMA Channels. EDMA is Used for:

• Transfers to and from On-Chip Memories

• Transfers to and from External Storage

(EMIF, GPMC, Slave Peripherals)

• Inter-Processor Communication (IPC)

– Integrates Hardware-Based Mailbox for IPC and

Spinlock for Process Synchronization Between

Cortex-A8, PRCM, and PRU-ICSS

• Mailbox Registers that Generate Interrupts

– Four Initiators (Cortex-A8, PRCM, PRU0,

PRU1)

• Spinlock has 128 Software-Assigned Lock

Registers

• Security

– Crypto Hardware Accelerators (AES, SHA,

RNG)

– Secure Boot

• Boot Modes

– Boot Mode is Selected Through Boot

Configuration Pins Latched on the Rising Edge

of the PWRONRSTn Reset Input Pin

• Packages:

– 298-Pin S-PBGA-N298 Via Channel Package

(ZCE Suffix), 0.65-mm Ball Pitch

– 324-Pin S-PBGA-N324 Package

(ZCZ Suffix), 0.80-mm Ball Pitch

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Device OverviewCopyright © 2011–2016, Texas Instruments Incorporated

3

Page 4

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

1.2 Applications

• Gaming Peripherals

• Home and Industrial Automation

• Consumer Medical Appliances

• Printers

• Smart Toll Systems

• Connected Vending Machines

• Weighing Scales

• Educational Consoles

• Advanced Toys

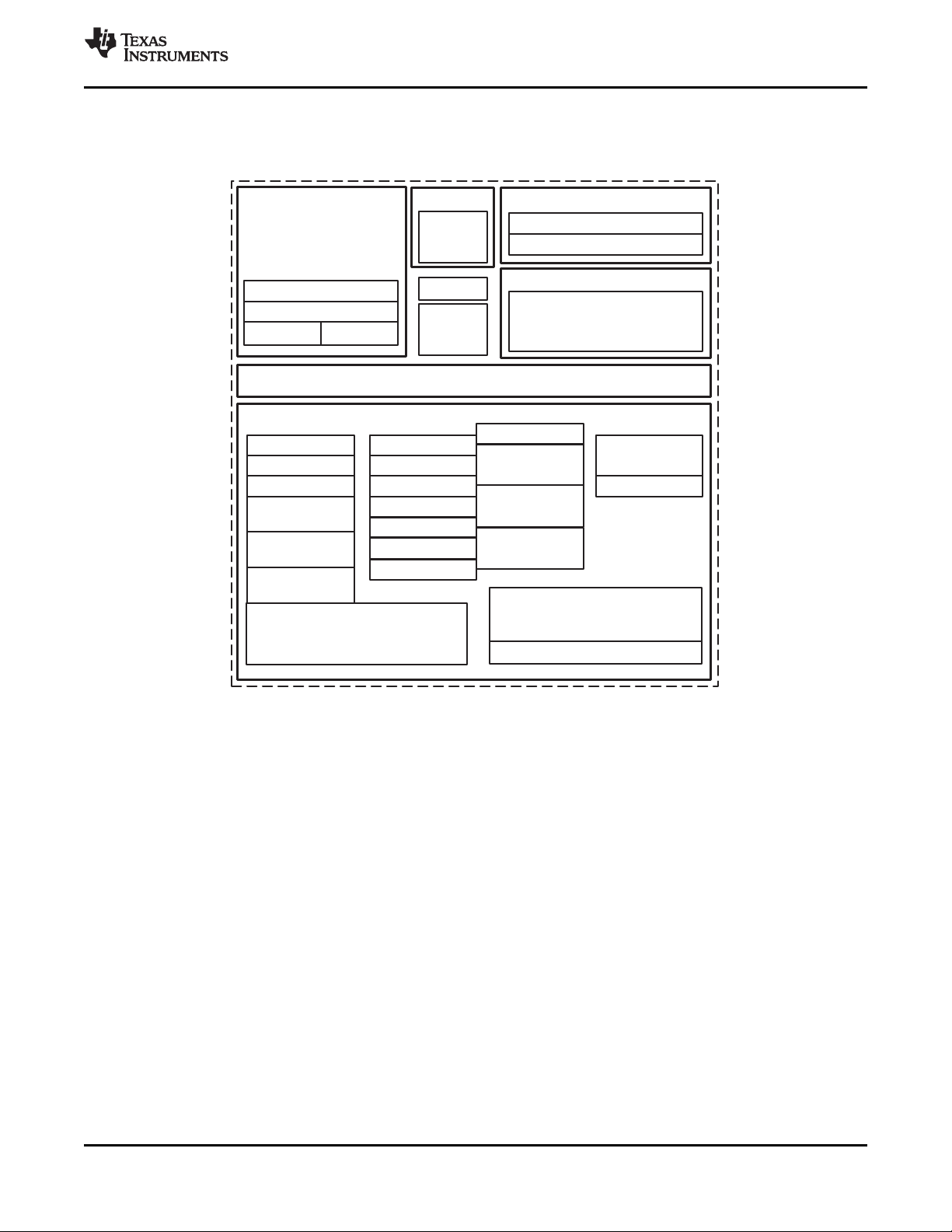

1.3 Description

The AM335x microprocessors, based on the ARM Cortex-A8 processor, are enhanced with image,

graphics processing, peripherals and industrial interface options such as EtherCAT and PROFIBUS. The

devices support high-level operating systems (HLOS). Linux®and Android™ are available free of charge

from TI.

The AM335x microprocessor contain the subsystems shown in Figure 1-1 and a brief description of each

follows:

The microprocessor unit (MPU) subsystem is based on the ARM Cortex-A8 processor and the PowerVR

SGX™ Graphics Accelerator subsystem provides 3D graphics acceleration to support display and gaming

effects.

The PRU-ICSS is separate from the ARM core, allowing independent operation and clocking for greater

efficiency and flexibility. The PRU-ICSS enables additional peripheral interfaces and real-time protocols

such as EtherCAT, PROFINET, EtherNet/IP, PROFIBUS, Ethernet Powerlink, Sercos, and others.

Additionally, the programmable nature of the PRU-ICSS, along with its access to pins, events and all

system-on-chip (SoC) resources, provides flexibility in implementing fast, real-time responses, specialized

data handling operations, custom peripheral interfaces, and in offloading tasks from the other processor

cores of SoC.

www.ti.com

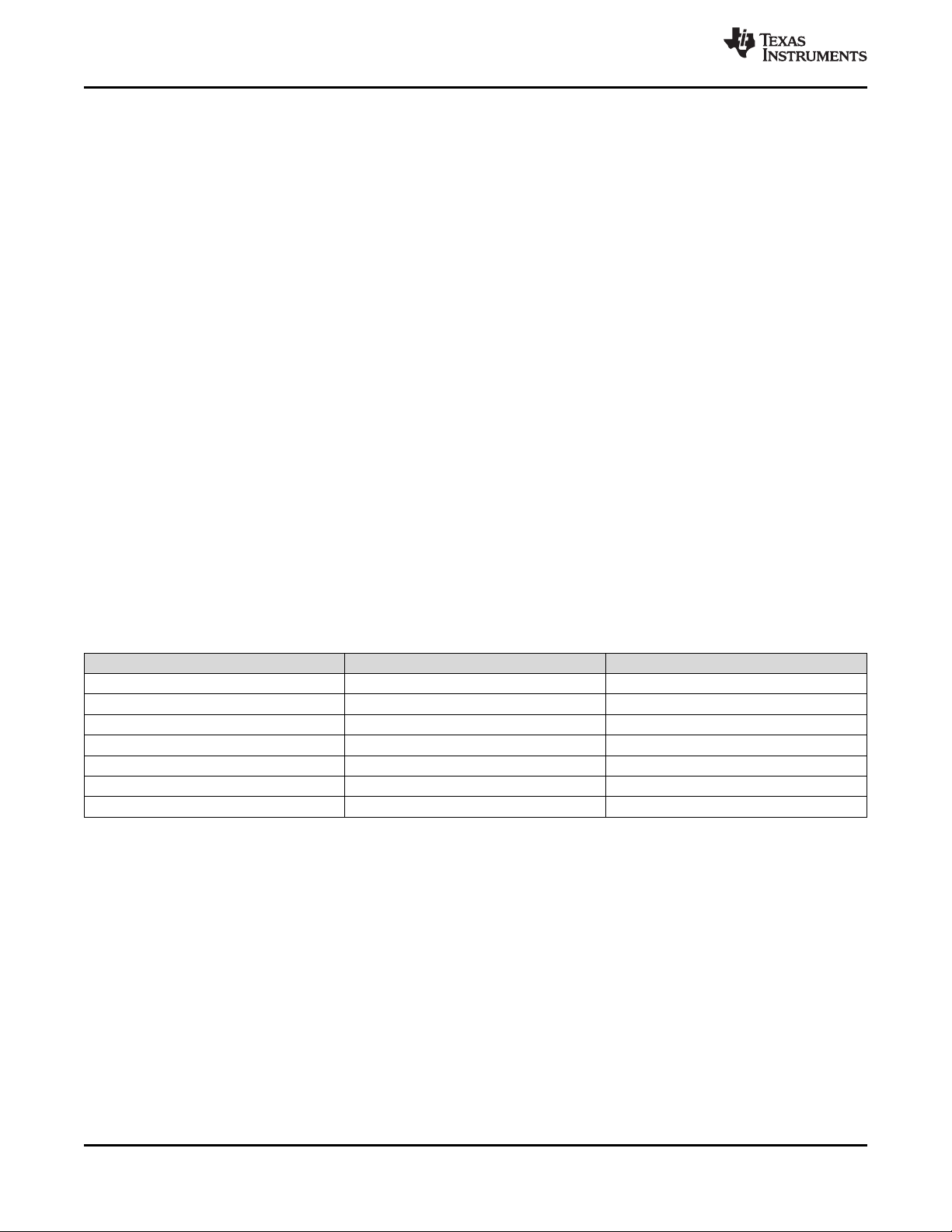

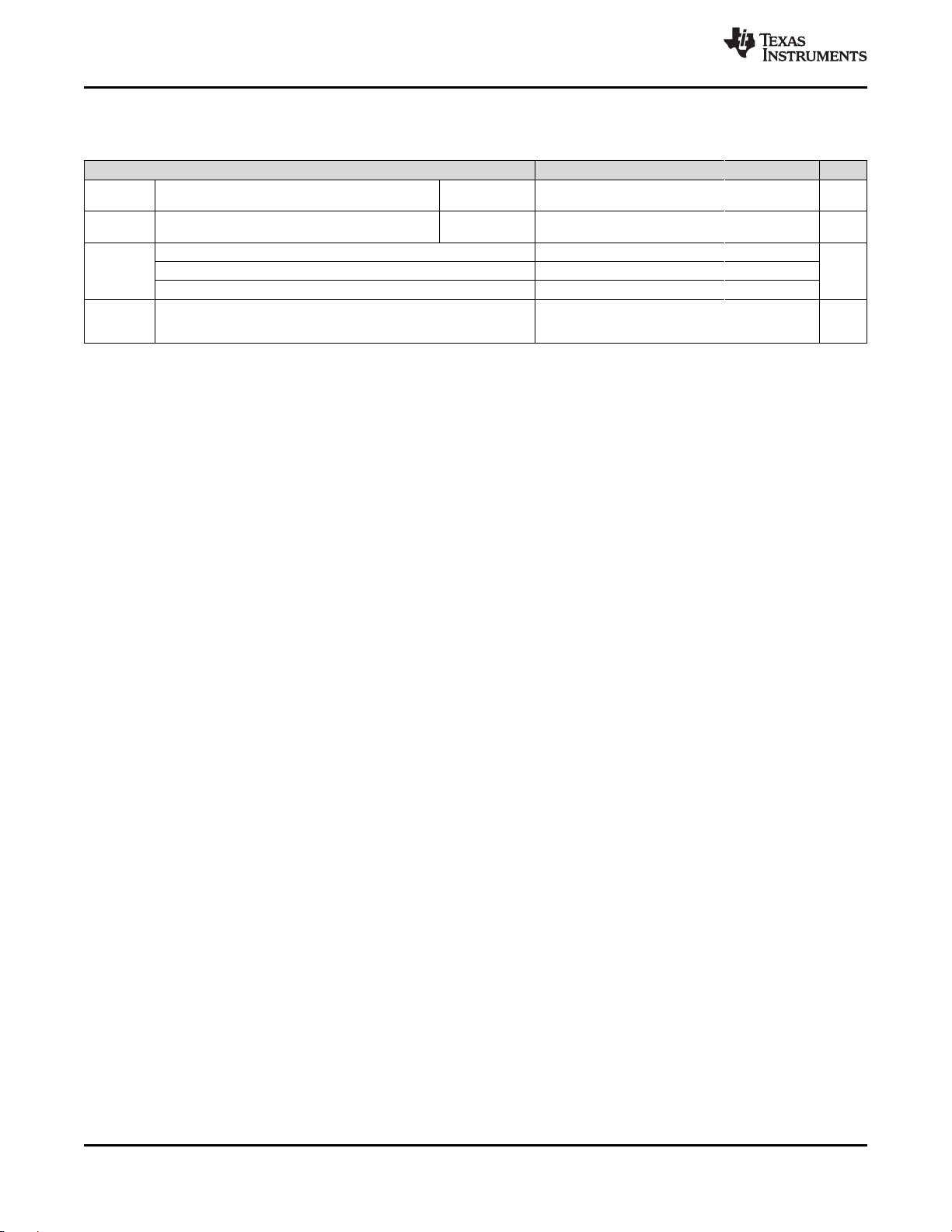

Device Information

PART NUMBER PACKAGE BODY SIZE

AM3359ZCZ NFBGA (324) 15.0 mm × 15.0 mm

AM3358ZCZ NFBGA (324) 15.0 mm × 15.0 mm

AM3357ZCZ NFBGA (324) 15.0 mm × 15.0 mm

AM3356ZCZ, AM3356ZCE NFBGA (324), NFBGA (298) 15.0 mm × 15.0 mm, 13.0 mm × 13.0 mm

AM3354ZCZ, AM3354ZCE NFBGA (324), NFBGA (298) 15.0 mm × 15.0 mm, 13.0 mm × 13.0 mm

AM3352ZCZ, AM3352ZCE NFBGA (324), NFBGA (298) 15.0 mm × 15.0 mm, 13.0 mm × 13.0 mm

AM3351ZCE NFBGA (298) 13.0 mm × 13.0 mm

(1) For more information, see Section 9, Mechanical, Packaging, and Orderable Information.

(1)

4

Device Overview Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 5

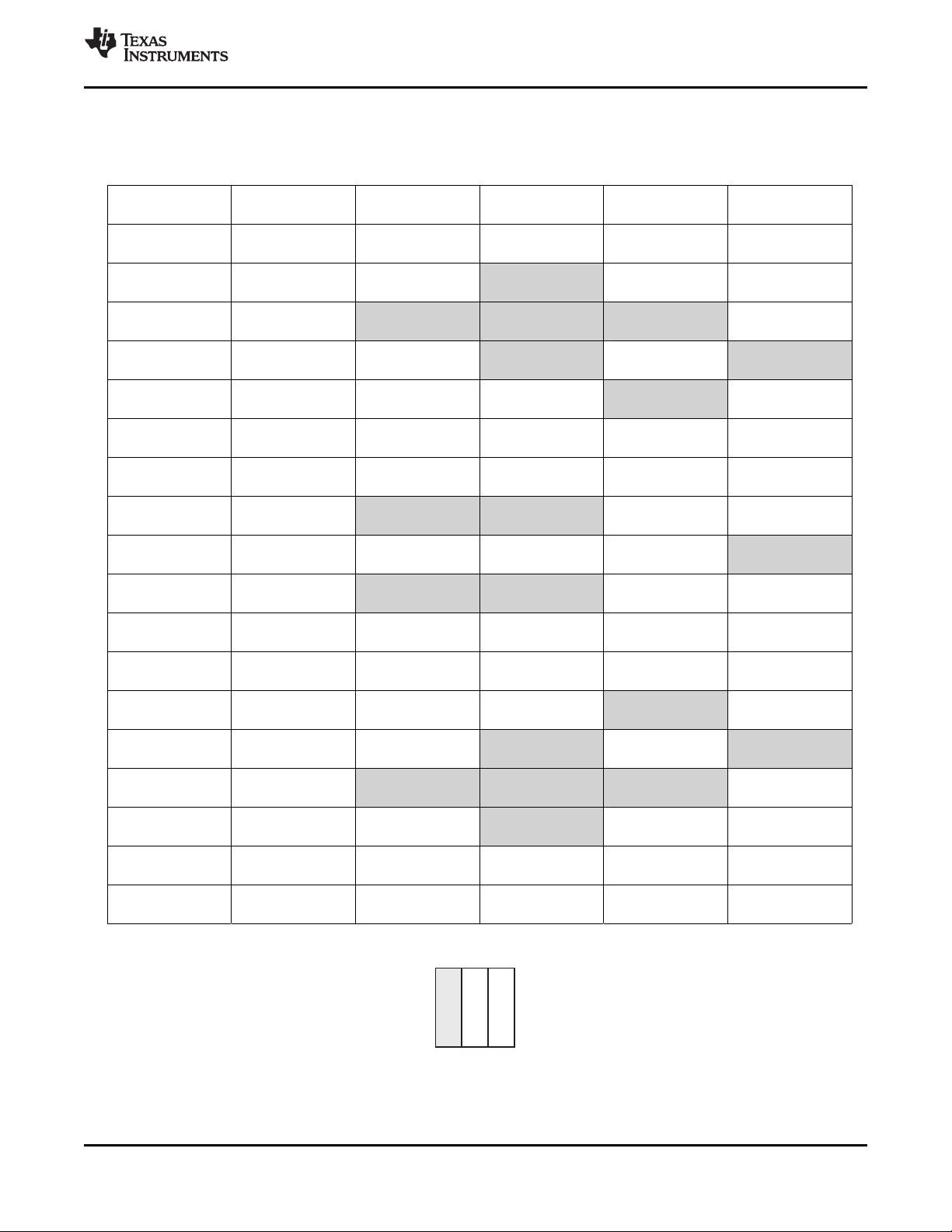

ARM

Cortex-A8

Up to 1 GHz

32KB and 32KB L1 + SED

256KB L2 + ECC

176KB ROM

64KB RAM

Graphics

PowerVR

SGX

3D GFX

Crypto

64KB

shared

RAM

24-bit LCD controller

Touch screen controller

Display

PRU-ICSS

EtherCAT, PROFINET,

EtherNet/IP,

and more

L3 and L4 interconnect

USB 2.0 HS

OTG + PHY x2

CAN x2

(Ver. 2 A and B)

McASP x2

(4 channel)

I C x3

2

SPI x2

UART x6

Serial System Parallel

eDMA

Timers x8

WDT

RTC

eHRPWM x3

eQEP x3

PRCM

eCAP x3

ADC (8 channel)

12-bit SAR

JTAG

Crystal

Oscillator x2

MMC, SD and

SDIO x3

GPIO

EMAC (2-port) 10M, 100M, 1G

IEEE 1588v2, and switch

(MII, RMII, RGMII)

mDDR(LPDDR), DDR2,

DDR3, DDR3L

(16-bit; 200, 266, 400, 400 MHz)

NAND and NOR (16-bit ECC)

Memory interface

Copyright © 2016, Texas Instruments Incorporated

www.ti.com

1.4 Functional Block Diagram

Figure 1-1 shows the AM335x microprocessor functional block diagram.

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Figure 1-1. AM335x Functional Block Diagram

Submit Documentation Feedback

Device OverviewCopyright © 2011–2016, Texas Instruments Incorporated

5

Page 6

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table of Contents

www.ti.com

1 Device Overview ......................................... 1

1.1 Features .............................................. 1

1.2 Applications........................................... 4

1.3 Description............................................ 4

1.4 Functional Block Diagram ........................... 5

2 Revision History ......................................... 7

3 Device Comparison ..................................... 8

3.1 Related Products ..................................... 9

4 Terminal Configuration and Functions ............ 10

4.1 Pin Diagrams........................................ 10

4.2 Pin Attributes ........................................ 18

4.3 Signal Descriptions.................................. 51

5 Specifications........................................... 80

5.1 Absolute Maximum Ratings......................... 80

5.2 ESD Ratings ........................................ 81

5.3 Power-On Hours (POH)............................. 82

5.4 Operating Performance Points (OPPs) ............. 82

5.5 Recommended Operating Conditions............... 85

5.6 Power Consumption Summary...................... 87

5.7 DC Electrical Characteristics........................ 89

5.8 Thermal Resistance Characteristics for ZCE and

ZCZ Packages ...................................... 93

5.9 External Capacitors ................................. 94

5.10 Touch Screen Controller and Analog-to-Digital

Subsystem Electrical Parameters................... 97

6 Power and Clocking ................................... 99

6.1 Power Supplies...................................... 99

6.2 Clock Specifications................................ 107

7 Peripheral Information and Timings .............. 116

7.1 Parameter Information ............................. 116

7.2 Recommended Clock and Control Signal Transition

Behavior............................................ 116

7.3 OPP50 Support .................................... 116

7.4 Controller Area Network (CAN).................... 117

7.5 DMTimer ........................................... 118

7.6 Ethernet Media Access Controller (EMAC) and

Switch.............................................. 119

7.7 External Memory Interfaces........................ 127

2

7.8 I

C.................................................. 191

7.9 JTAG Electrical Data and Timing.................. 193

7.10 LCD Controller (LCDC) ............................ 194

7.11 Multichannel Audio Serial Port (McASP) .......... 210

7.12 Multichannel Serial Port Interface (McSPI) ........ 215

7.13 Multimedia Card (MMC) Interface ................. 221

7.14 Programmable Real-Time Unit Subsystem and

Industrial Communication Subsystem (PRU-ICSS) 224

7.15 Universal Asynchronous Receiver Transmitter

(UART)............................................. 233

8 Device and Documentation Support.............. 236

8.1 Device Nomenclature .............................. 236

8.2 Tools and Software ................................ 237

8.3 Documentation Support............................ 241

8.4 Related Links ...................................... 244

8.5 Community Resources............................. 244

8.6 Trademarks ........................................ 244

8.7 Electrostatic Discharge Caution ................... 244

8.8 Glossary............................................ 244

9 Mechanical, Packaging, and Orderable

Information............................................. 245

9.1 Via Channel........................................ 245

9.2 Packaging Information ............................. 245

6

Table of Contents Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 7

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision I (December 2015) to Revision J Page

• Added Secure boot to Security feature list ........................................................................................ 3

• Added extended temperature range for the AM3351 device in Table 3-1 .................................................... 8

• Added Section 3.1, Related Products ............................................................................................. 9

• Reformatted and added content to Section 8, Device and Documentation Support...................................... 236

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Revision HistoryCopyright © 2011–2016, Texas Instruments Incorporated

7

Page 8

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

www.ti.com

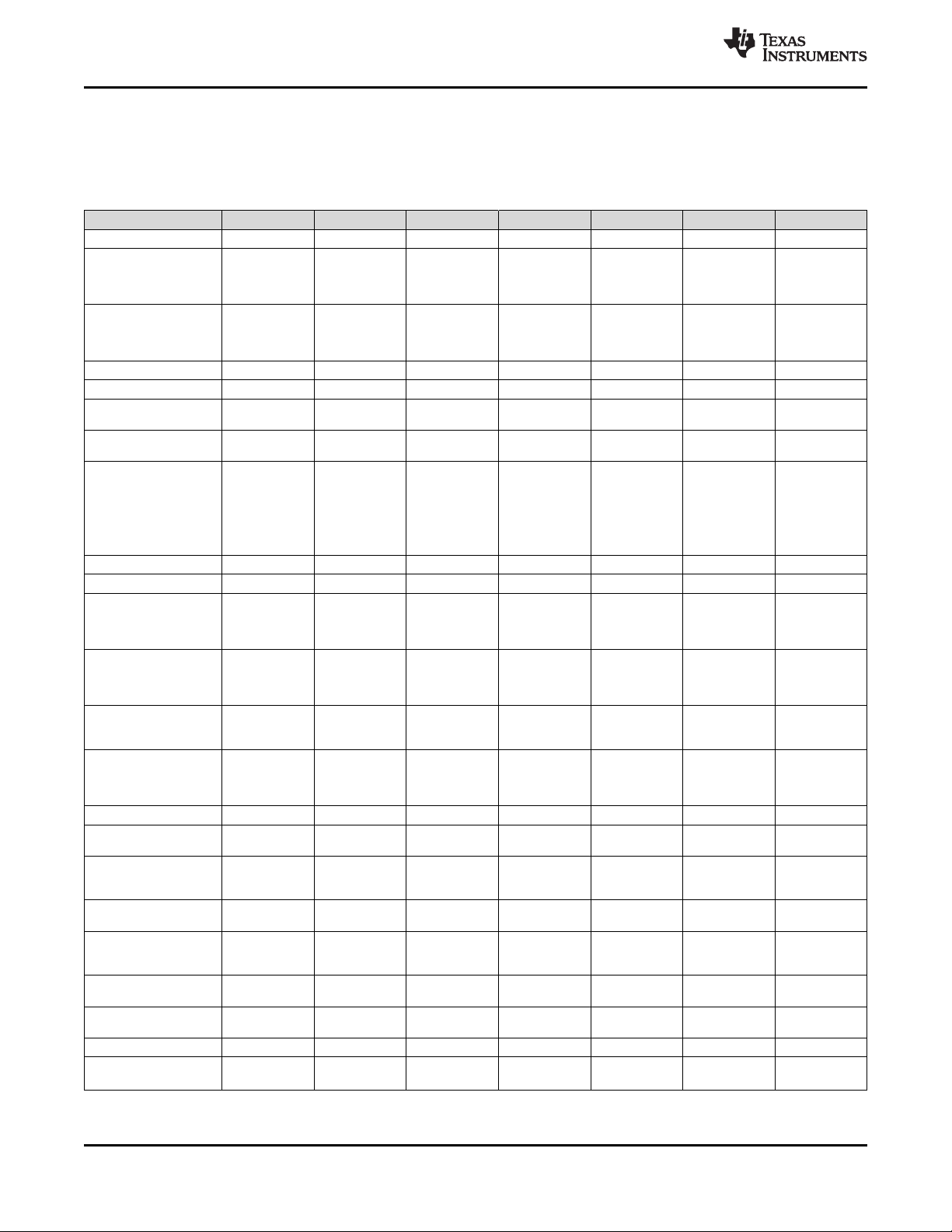

3 Device Comparison

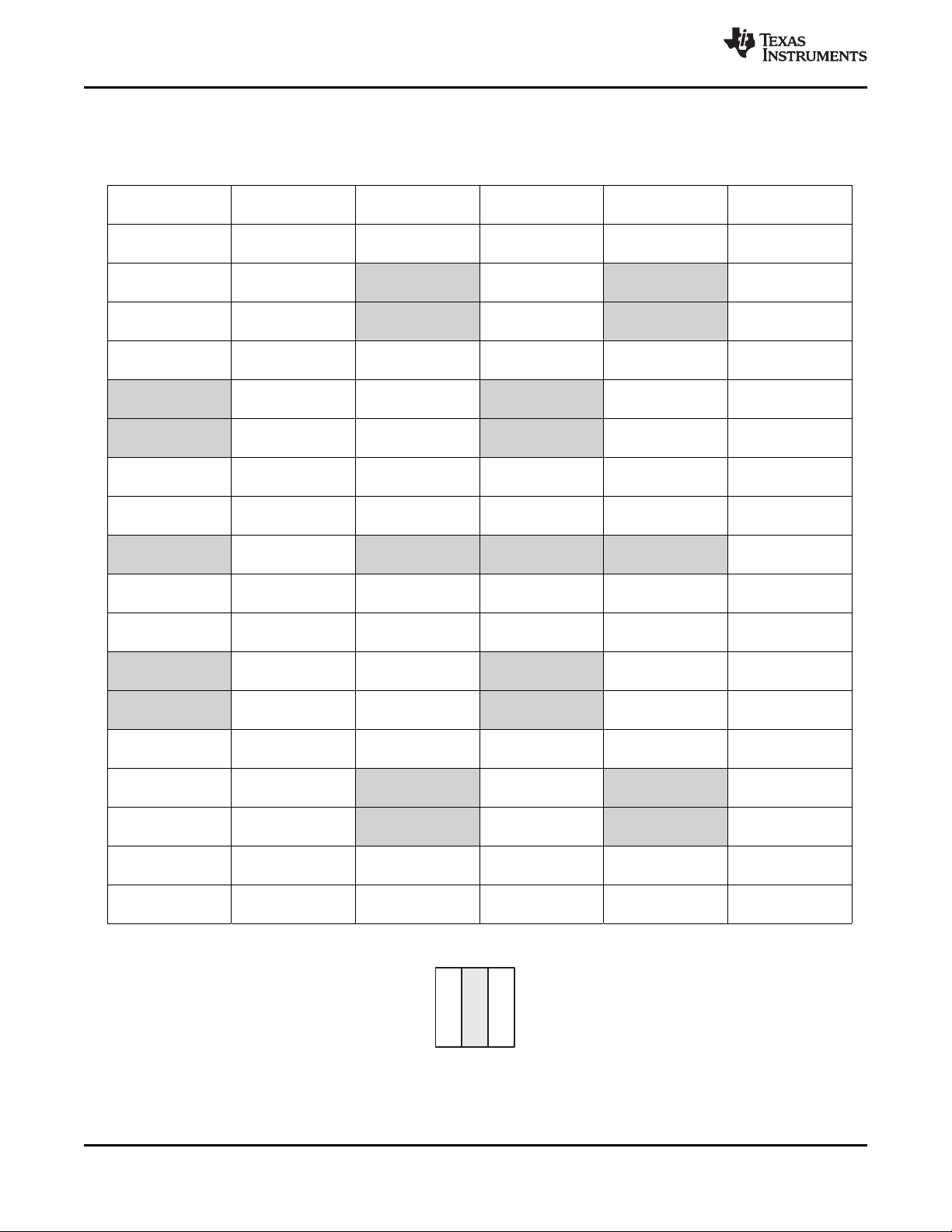

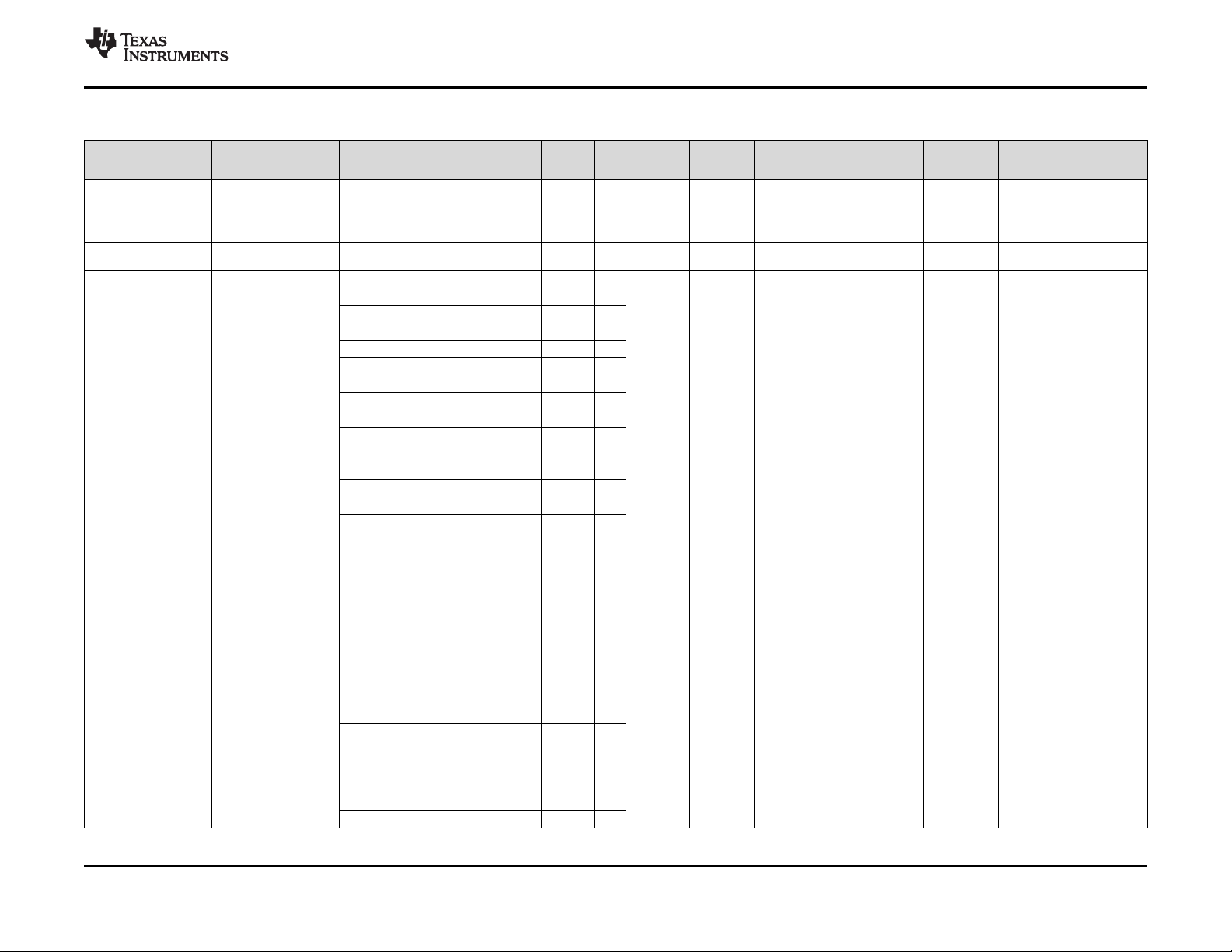

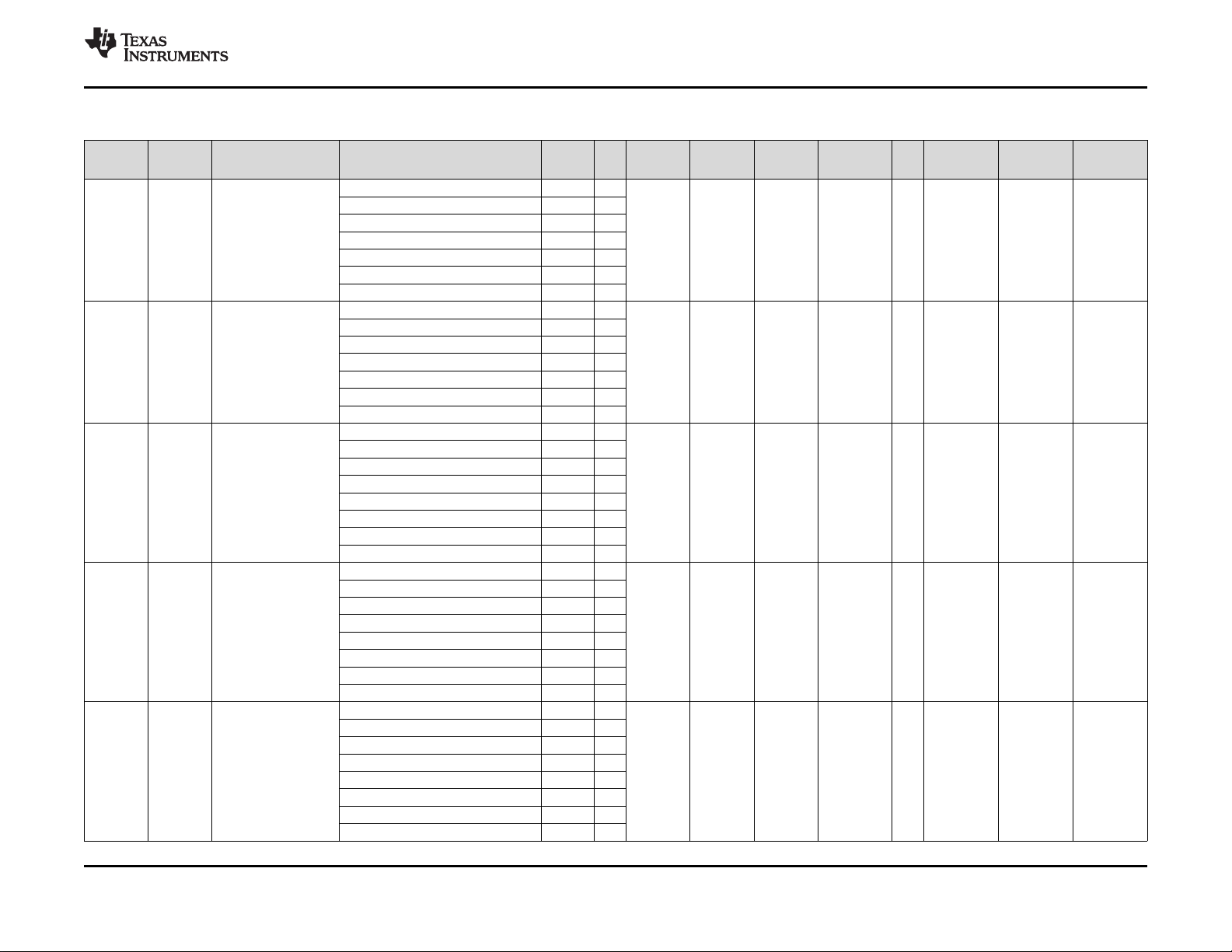

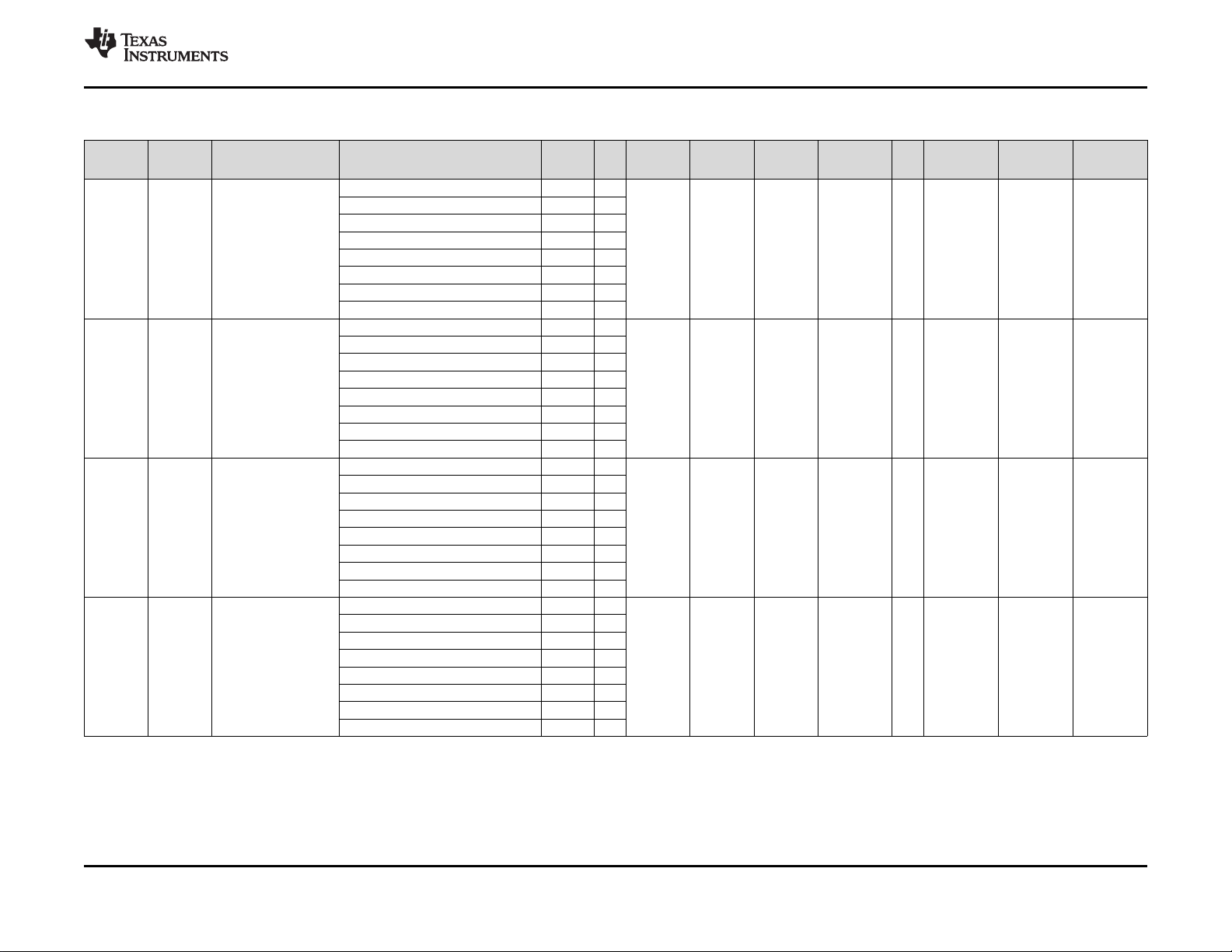

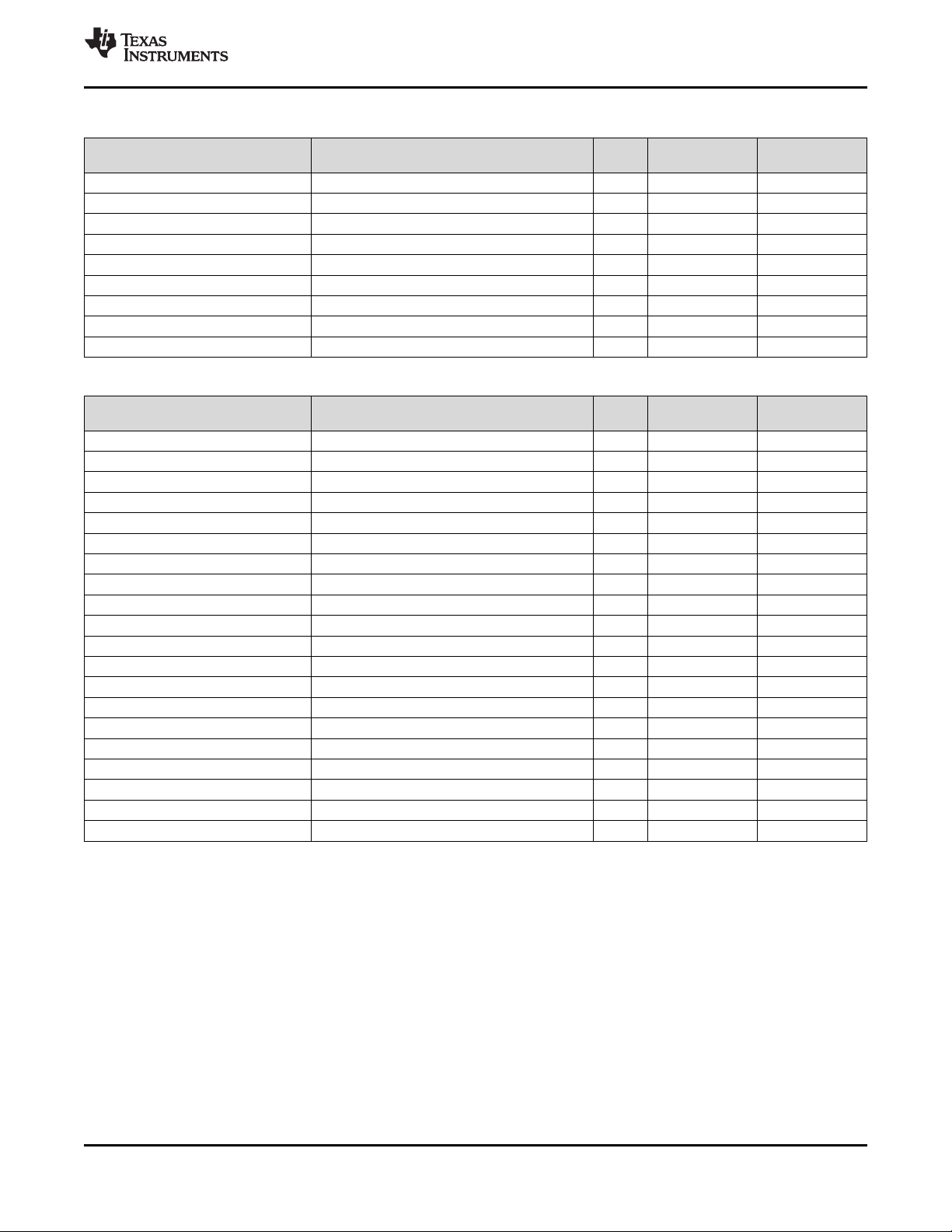

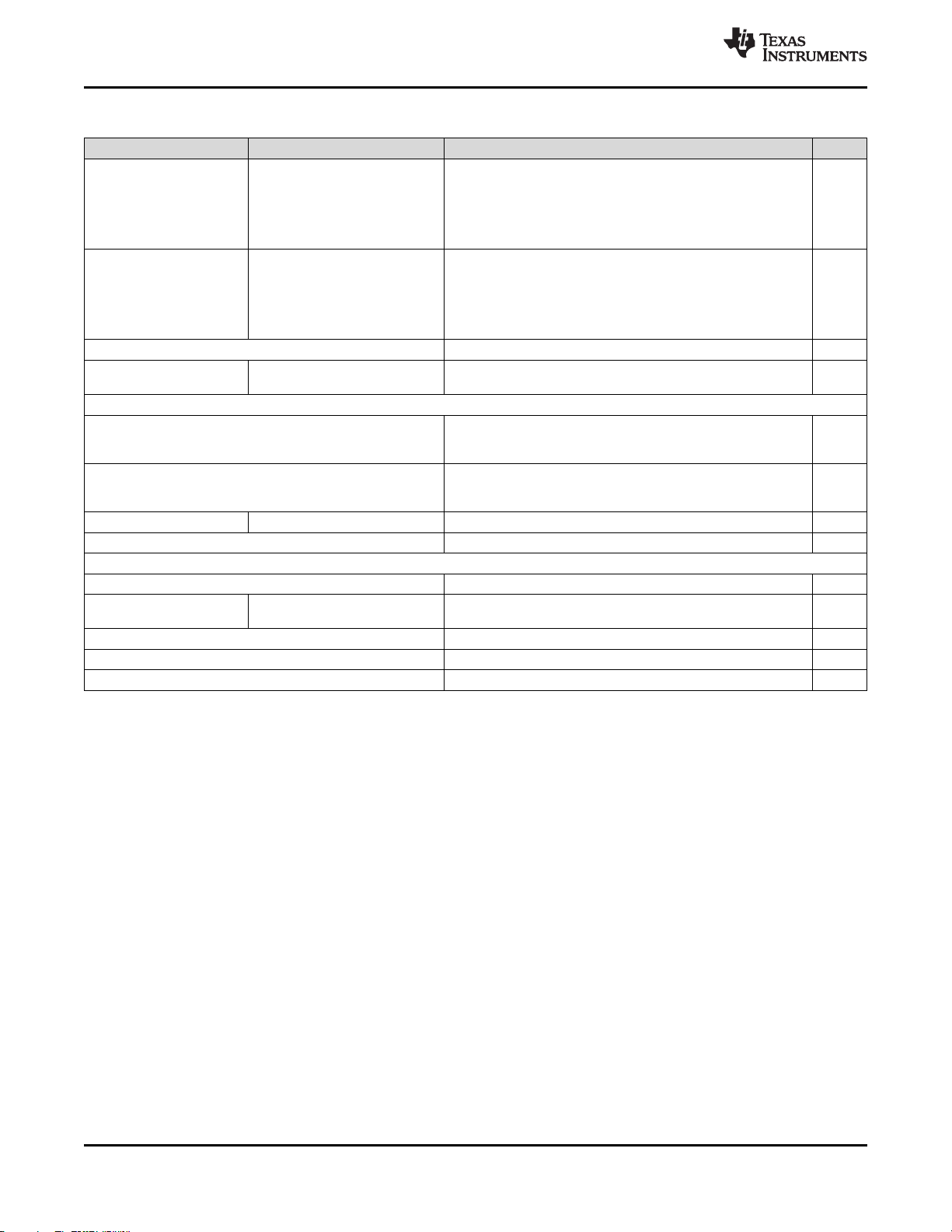

Table 3-1 shows the features supported across different AM335x devices.

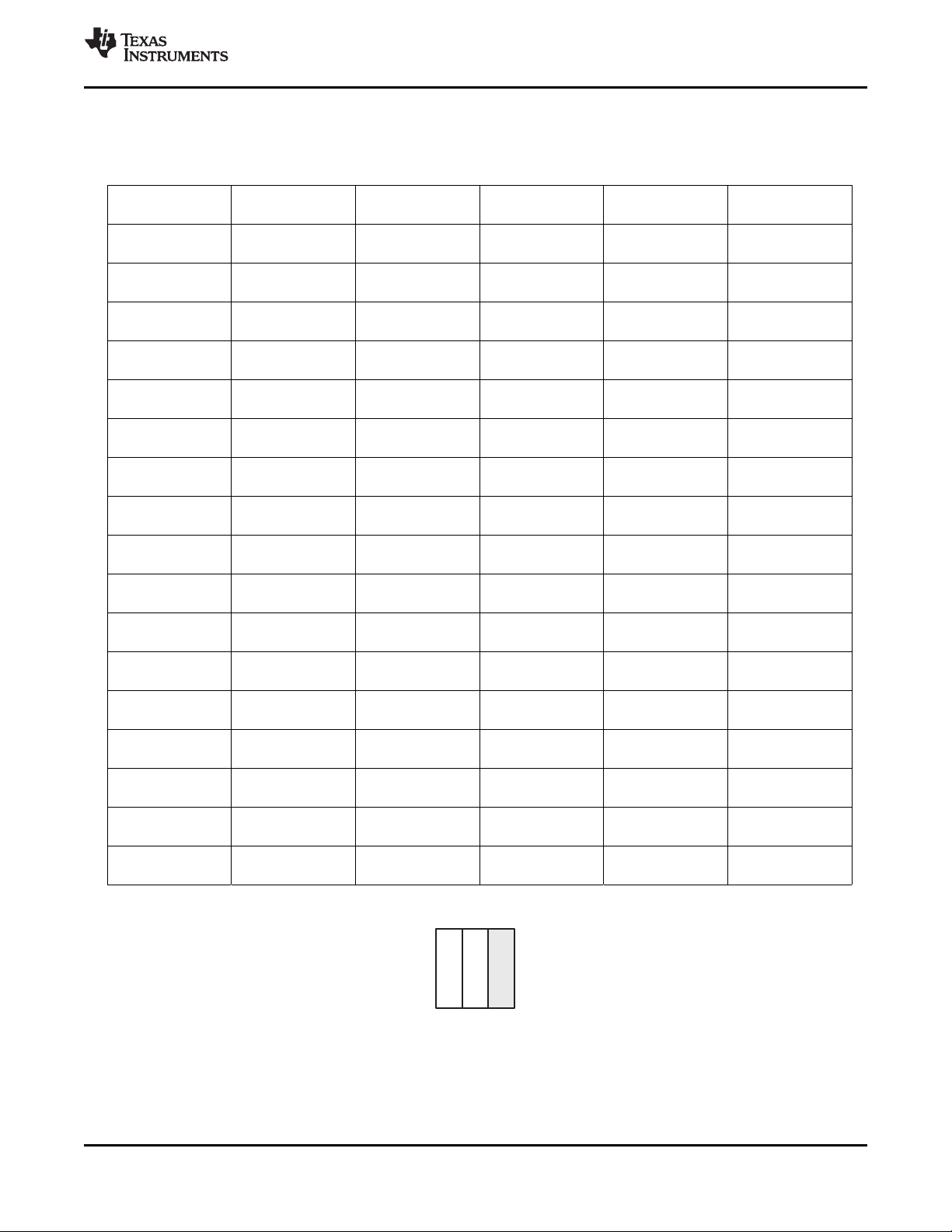

Table 3-1. Device Features Comparison

FUNCTION AM3351 AM3352 AM3354 AM3356 AM3357 AM3358 AM3359

ARM Cortex-A8 Yes Yes Yes Yes Yes Yes Yes

Frequency

MIPS

On-chip L1 cache 64KB 64KB 64KB 64KB 64KB 64KB 64KB

On-chip L2 cache 256KB 256KB 256KB 256KB 256KB 256KB 256KB

Graphics accelerator

(SGX530)

Hardware acceleration Crypto

Programmable real-time

unit subsystem and

industrial communication

subsystem (PRU-ICSS)

On-chip memory 128KB 128KB 128KB 128KB 128KB 128KB 128KB

Display options LCD LCD LCD LCD LCD LCD LCD

General-purpose memory 1 16-bit (GPMC,

DRAM

Universal serial bus (USB) ZCE: 1 port ZCE: 1 port

Ethernet media access

controller (EMAC) with 2port switch

Multimedia card (MMC) 3 3 3 3 3 3 3

Controller-area network

(CAN)

Universal asynchronous

receiver and transmitter

(UART)

Analog-to-digital converter

(ADC)

Enhanced high-resolution

PWM modules

(eHRPWM)

Enhanced capture

modules (eCAP)

Enhanced quadrature

encoder pulse (eQEP)

Real-time clock (RTC) 1 1 1 1 1 1 1

Inter-integrated circuit

(I2C)

(1)

(2)

(3)

300 MHz

600 MHz

600

1200

— — 3D — — 3D 3D

accelerator

— — — Features

NAND flash,

NOR flash,

SRAM)

1 16-bit

(LPDDR-400,

DDR2-532,

DDR3-800)

10/100/1000

ZCE: 1 port

— 2 2 2 2 2 2

6 6 6 6 6 6 6

8-ch 12-bit 8-ch 12-bit 8-ch 12-bit 8-ch 12-bit 8-ch 12-bit 8-ch 12-bit 8-ch 12-bit

3 3 3 3 3 3 3

3 3 3 3 3 3 3

3 3 3 3 3 3 3

3 3 3 3 3 3 3

300 MHz

600 MHz

800 MHz

1000 MHz

600

1200

1600

2000

Crypto

accelerator

1 16-bit (GPMC,

NAND flash,

NOR flash,

SRAM)

1 16-bit

(LPDDR-400,

DDR2-532,

DDR3-800)

ZCZ: 2 ports

10/100/1000

ZCE: 1 port

ZCZ: 2 ports

600 MHz

800 MHz

1000 MHz

1200

1600

2000

Crypto

accelerator

1 16-bit (GPMC,

NAND flash,

NOR flash,

SRAM)

1 16-bit

(LPDDR-400,

DDR2-532,

DDR3-800)

ZCE: 1 port

ZCZ: 2 ports

10/100/1000

ZCE: 1 port

ZCZ: 2 ports

300 MHz

600 MHz

800 MHz

600

1200

1600

Crypto

accelerator

including basic

Industrial

protocols;

ZCE: Limited

PRU I/Os pinned

out

1 16-bit (GPMC,

NAND flash,

NOR flash,

SRAM)

1 16-bit

(LPDDR-400,

DDR2-532,

DDR3-800)

ZCE: 1 port

ZCZ: 2 ports

10/100/1000

ZCE: 1 port

ZCZ: 2 ports

300 MHz

600 MHz

800 MHz

600

1200

1600

Crypto

accelerator

Features

including all

Industrial

protocols

1 16-bit (GPMC,

NAND flash,

NOR flash,

SRAM)

1 16-bit

(LPDDR-400,

DDR2-532,

DDR3-800)

No ZCE

Available

ZCZ: 2 ports

10/100/1000

No ZCE

Available

ZCZ: 2 ports

600 MHz

800 MHz

1000 MHz

1200

1600

2000

Crypto

accelerator

Features

including basic

Industrial

protocols

1 16-bit (GPMC,

NAND flash,

NOR flash,

SRAM)

1 16-bit

(LPDDR-400,

DDR2-532,

DDR3-800)

No ZCE

Available

ZCZ: 2 ports

10/100/1000

No ZCE

Available

ZCZ: 2 ports

600 MHz

800 MHz

1200

1600

Crypto

accelerator

Features

including all

Industrial

protocols

1 16-bit (GPMC,

NAND flash,

NOR flash,

SRAM)

1 16-bit

(LPDDR-400,

DDR2-532,

DDR3-800)

No ZCE

Available

ZCZ: 2 ports

10/100/1000

No ZCE

Available

ZCZ: 2 ports

8

Device Comparison Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 9

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

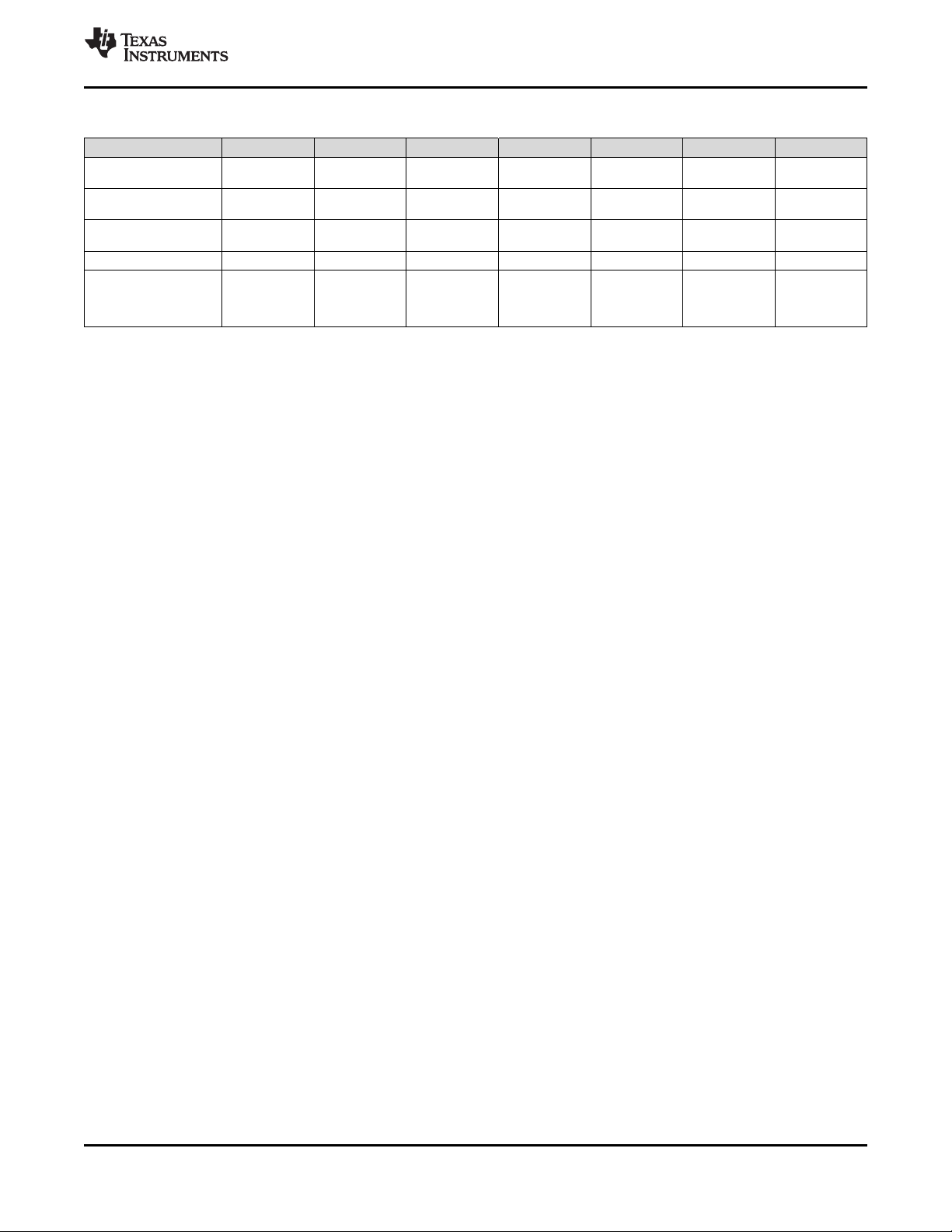

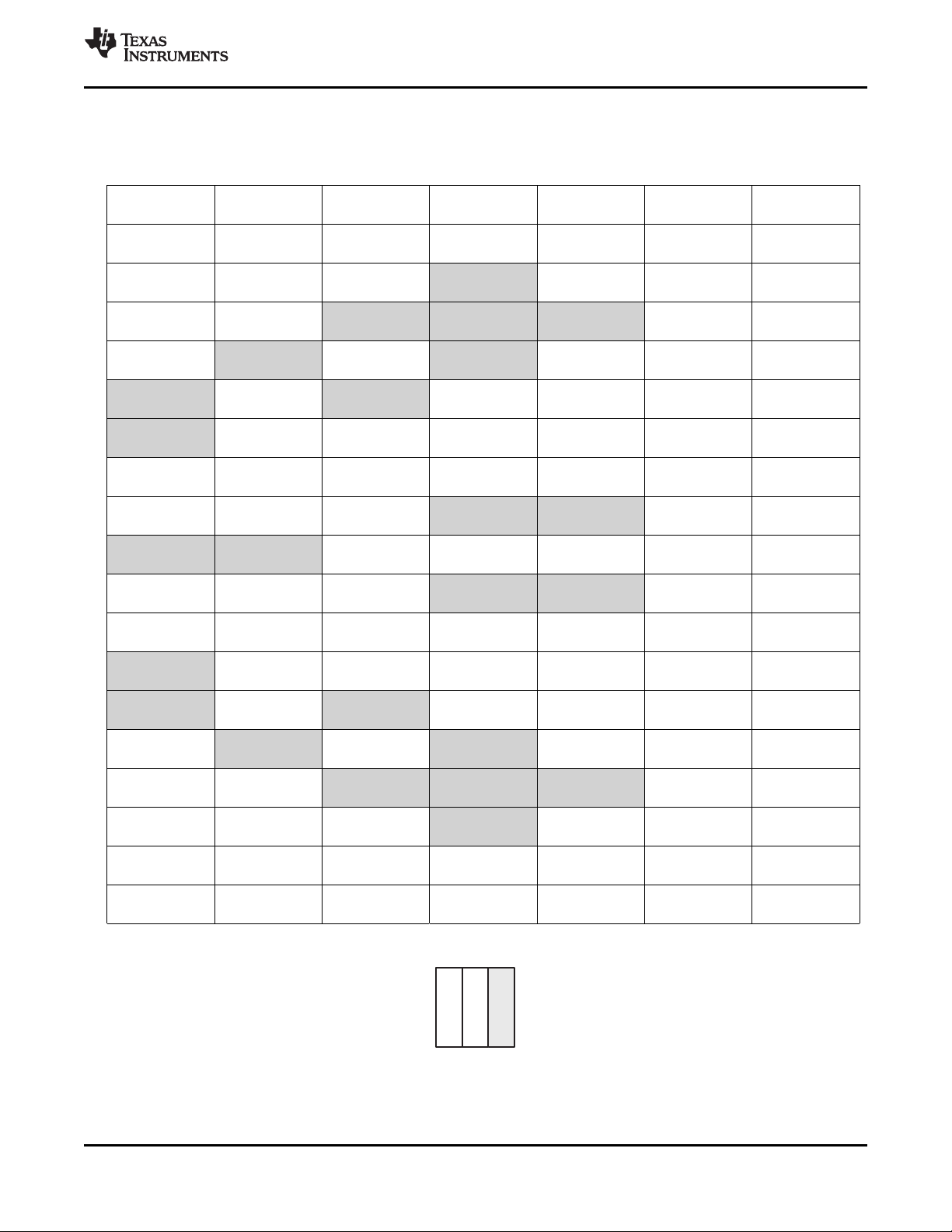

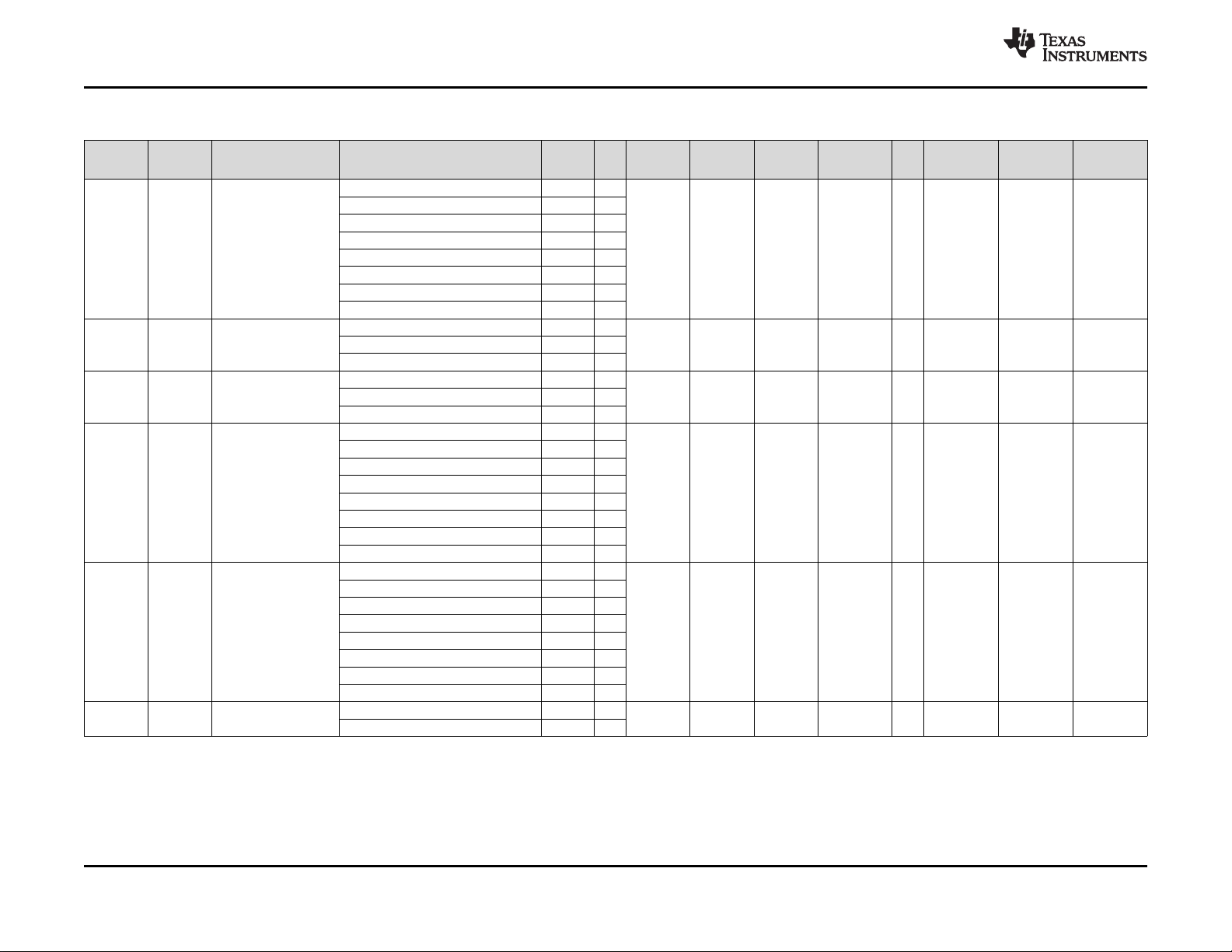

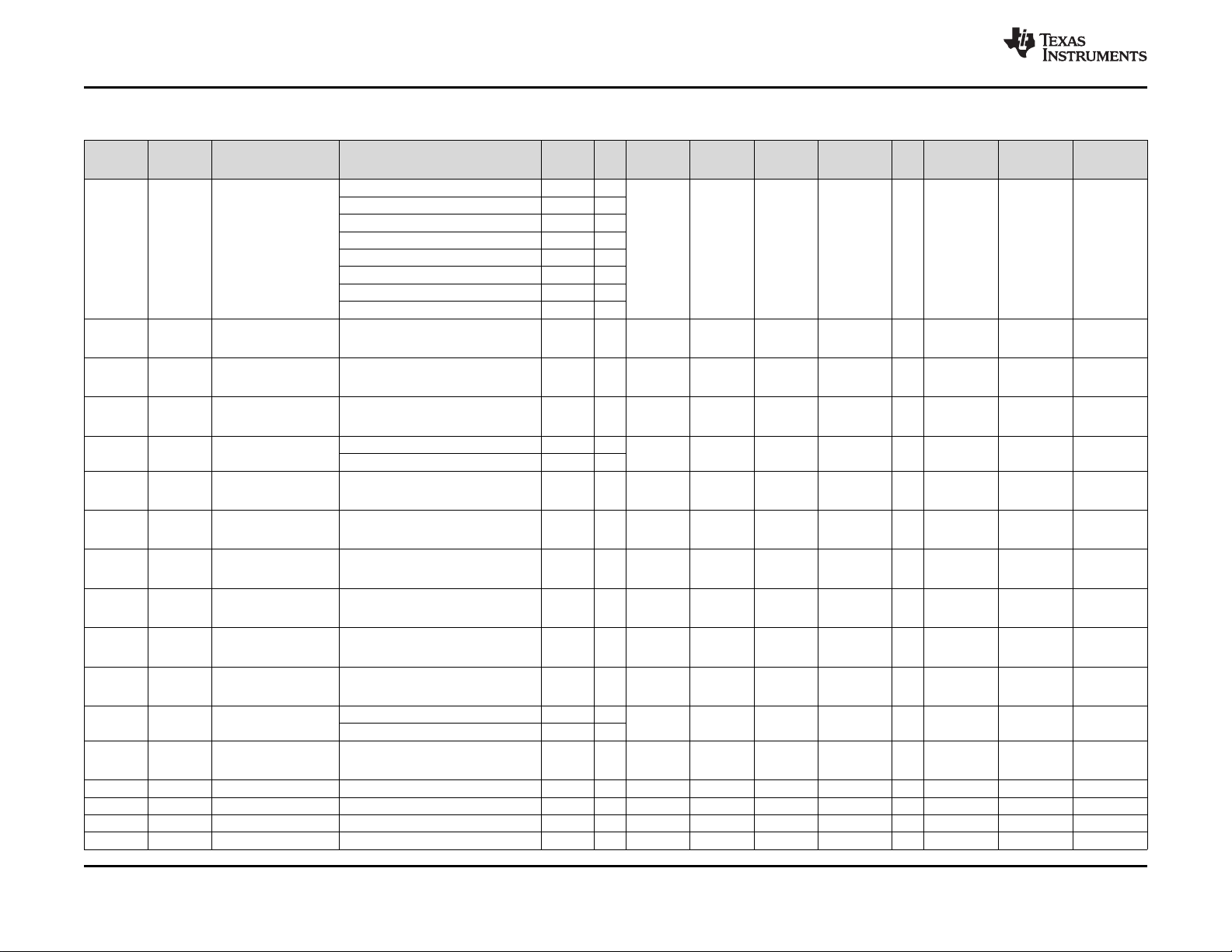

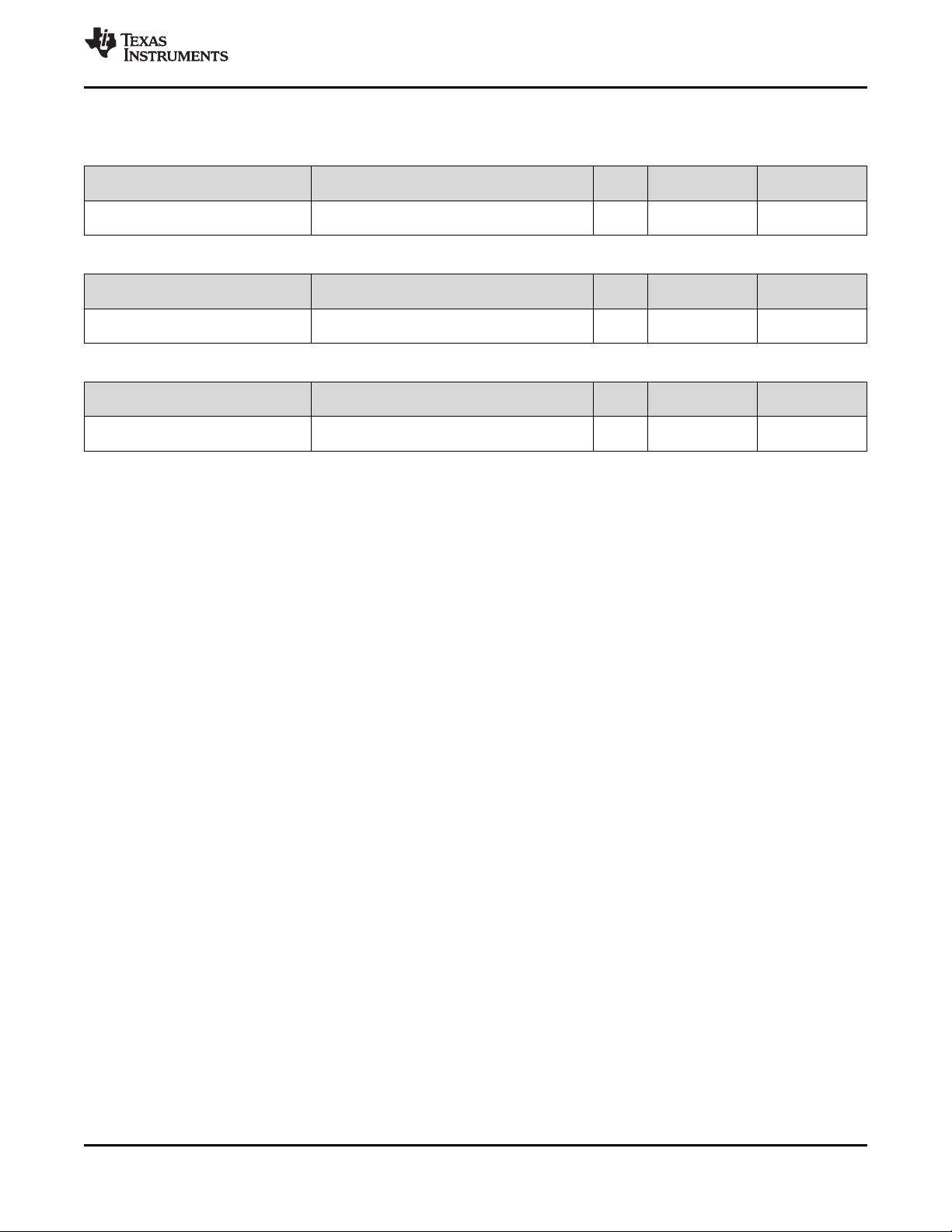

Table 3-1. Device Features Comparison (continued)

FUNCTION AM3351 AM3352 AM3354 AM3356 AM3357 AM3358 AM3359

Multichannel audio serial

port (McASP)

Multichannel serial port

interface (McSPI)

Enhanced direct memory

access (EDMA)

Input/output (I/O) supply 1.8 V, 3.3 V 1.8 V, 3.3 V 1.8 V, 3.3 V 1.8 V, 3.3 V 1.8 V, 3.3 V 1.8 V, 3.3 V 1.8 V, 3.3 V

Operating temperature

range

(1) Frequencies listed correspond to silicon revision 2.x. Earlier silicon revisions support 275 MHz, 500 MHz, 600 MHz, and 720 MHz.

(2) MIPS listed correspond to silicon revision 2.x. Earlier silicon revisions support 560, 1000, 1200, and 1440.

(3) DRAM speeds listed are data rates.

(4) Industrial extended temperature only supported for 300-MHz and 600-MHz frequencies.

2 2 2 2 2 2 2

2 2 2 2 2 2 2

64-Ch 64-Ch 64-Ch 64-Ch 64-Ch 64-Ch 64-Ch

0 to 90°C

–40 to 105°C

-40 to 125°C

–40 to 105°C

–40 to 90°C

0 to 90°C

(4)

–40 to 105°C

–40 to 90°C

0 to 90°C

–40 to 105°C

–40 to 90°C

0 to 90°C

–40 to 105°C

–40 to 90°C

–40 to 105°C

–40 to 90°C

0 to 90°C

–40 to 105°C

–40 to 90°C

3.1 Related Products

For information about other devices in this family of products, see the following links:

Sitara Processors Scalable processors based on ARM Cortex-A cores with flexible peripherals,

connectivity and unified software support – perfect for sensors to servers.

TI's ARM Cortex-A8 Advantage The ARM Cortex-A8 core is highly-optimized by ARM for performance

and power efficiency. With the ability to scale in speed from 300MHz to 1.35GHz, the ARM

Cortex-A8-based processor can meet the requirements for power optimized devices with a

power budget of less than the Cortex-A8 core a dual-issue superscalar, achieving twice the

instructions executed per clock cycle at 2 DMIPS/MHz.

Sitara AM335x Processors Scalable ARM Cortex-A8-based core from 300 MHz up to 1 GHz, 3D

graphics option for enhanced user interface, dual-core PRU-ICSS for industrial Ethernet

protocols and position feedback control, and premium secure boot option.

Companion Products for Sitara AM335x Processors Review products that are frequently purchased or

used in conjunction with this product.

TI Designs for Sitara AM335x Processors TI Designs Reference Design Library is a robust reference

design library spanning analog, embedded processor and connectivity. Created by TI experts

to help you jump start your system design, all TI Designs include schematic or block

diagrams, BOMs and design files to speed your time to market. Search and download

designs at ti.com/tidesigns.

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Device ComparisonCopyright © 2011–2016, Texas Instruments Incorporated

9

Page 10

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

4 Terminal Configuration and Functions

4.1 Pin Diagrams

NOTE

The terms 'ball', 'pin', and 'terminal' are used interchangeably throughout the document. An

attempt is made to use 'ball' only when referring to the physical package.

4.1.1 ZCE Package Pin Maps (Top View)

The pin maps that follow show the pin assignments on the ZCE package in three sections (left, middle,

and right).

www.ti.com

10

Terminal Configuration and Functions Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 11

Left

Pin map section location

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

ZCE Pin Map [Section Left - Top View]

A B C D E F

19 VSS I2C0_SCL UART1_TXD UART1_RTSn UART0_RXD UART0_CTSn

18 SPI0_SCLK SPI0_D0 I2C0_SDA UART1_RXD ECAP0_IN_PWM0_OUT UART0_RTSn

17 SPI0_CS0 SPI0_D1 EXTINTn XXXX UART1_CTSn UART0_TXD

16 WARMRSTn SPI0_CS1 XXXX XXXX XXXX VDDS

15 EMU0 XDMA_EVENT_INTR1 XDMA_EVENT_INTR0 XXXX PWRONRSTn XXXX

14 TDO TCK TMS EMU1 XXXX VDDSHV6

13 TRSTn TDI CAP_VBB_MPU CAP_VDD_SRAM_MPU VDDSHV6 VSS

12 AIN7 AIN5 VDDS_SRAM_MPU_BB VDDS VDDSHV6 VSS

11 AIN1 AIN3 XXXX XXXX VDDSHV6 VDD_CORE

10 AIN6 CAP_VDD_SRAM_CORE VDDS_SRAM_CORE_BG VSS VSS XXXX

9 VREFP VREFN XXXX XXXX VSS VDD_CORE

8 AIN2 AIN0 AIN4 VSSA_ADC VSS VSS

7 RTC_KALDO_ENn RTC_PWRONRSTn PMIC_POWER_EN VDDA_ADC VSS VSS

6 RTC_XTALIN RESERVED VDDS_RTC CAP_VDD_RTC XXXX VSS

5 RTC_XTALOUT EXT_WAKEUP VDDS_PLL_DDR XXXX DDR_A4 XXXX

4 DDR_WEn DDR_BA2 XXXX XXXX XXXX DDR_A12

3 DDR_BA0 DDR_A3 DDR_A8 XXXX DDR_A15 DDR_A0

2 DDR_A5 DDR_A9 DDR_CK DDR_A7 DDR_A10 DDR_RASn

1 VSS DDR_A6 DDR_CKn DDR_A2 DDR_BA1 DDR_CASn

Terminal Configuration and FunctionsCopyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

11

Page 12

Middle

Pin map section location

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

ZCE Pin Map [Section Middle - Top View]

G H J K L M

19 MMC0_CLK MMC0_DAT3 MII1_COL MII1_RX_ER MII1_RX_DV MII1_RX_CLK

18 MMC0_DAT0 MMC0_DAT2 MII1_CRS RMII1_REF_CLK MII1_TXD0 MII1_TXD1

17 MMC0_CMD MMC0_DAT1 XXXX MII1_TX_EN XXXX MII1_TXD3

16 USB0_DRVVBUS VDDS_PLL_MPU XXXX VDD_CORE XXXX VDDS

15 VDDSHV4 VDDSHV4 VSS VDD_CORE VSS VDDSHV5

14 XXXX VDDSHV4 VSS XXXX VSS VDDSHV5

13 XXXX VDD_CORE VDD_CORE XXXX VDD_CORE VDD_CORE

12 VSS VDD_CORE VDD_CORE VSS VDD_CORE VDD_CORE

www.ti.com

11 VDD_CORE VSS VSS VSS VSS VSS

10 XXXX VSS XXXX XXXX XXXX VSS

9 VDD_CORE VSS VSS VSS VSS VSS

8 VSS VDD_CORE VDD_CORE VSS VDD_CORE VDD_CORE

7 XXXX VDD_CORE VDD_CORE XXXX VDD_CORE VDD_CORE

6 XXXX VDDS_DDR VSS XXXX VSS VDDS_DDR

5 VDDS_DDR VDDS_DDR VSS VDDS_DDR VSS VDDS_DDR

4 DDR_A11 DDR_VREF XXXX VDDS_DDR XXXX DDR_D11

3 DDR_CKE DDR_A14 XXXX DDR_DQM1 XXXX DDR_D10

2 DDR_RESETn DDR_CSn0 DDR_A1 DDR_D8 DDR_DQSn1 DDR_D12

1 DDR_ODT DDR_A13 DDR_VTP DDR_D9 DDR_DQS1 DDR_D13

12

Terminal Configuration and Functions Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 13

Right

Pin map section location

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

ZCE Pin Map [Section Right - Top View]

N P R T U V W

19 MII1_TX_CLK MII1_RXD1 MDC USB0_VBUS USB0_DP USB0_ID VSS

18 MII1_TXD2 MII1_RXD0 VDDA3P3V_USB0 USB0_CE USB0_DM GPMC_BEn1 GPMC_WPn

17 MII1_RXD3 MDIO VDDA1P8V_USB0 XXXX GPMC_CSn3 GPMC_AD15 GPMC_AD14

16 MII1_RXD2 VSSA_USB XXXX XXXX XXXX GPMC_CLK GPMC_AD9

15 VDDSHV5 XXXX GPMC_WAIT0 XXXX GPMC_CSn2 GPMC_AD8 GPMC_AD7

14 XXXX VSS XXXX VDDS GPMC_AD6 GPMC_CSn1 GPMC_AD5

13 XXXX VSS VDDSHV1 GPMC_AD13 GPMC_AD12 GPMC_AD4 GPMC_AD3

12 VSS VSS VDDSHV1 GPMC_AD10 GPMC_AD11 GPMC_AD2 XTALOUT

11 VDD_CORE VDD_CORE VDDSHV1 XXXX XXXX VSS_OSC XTALIN

10 XXXX XXXX VSS VSS VDDS_OSC GPMC_ADVn_ALE GPMC_AD0

9 VDD_CORE VDD_CORE VDDSHV1 XXXX XXXX GPMC_AD1 GPMC_OEn_REn

8 VSS VSS VDDSHV1 VDDS_PLL_CORE_LCD GPMC_WEn GPMC_BEn0_CLE GPMC_CSn0

7 XXXX VSS VDDSHV6 LCD_HSYNC LCD_VSYNC LCD_DATA15 LCD_AC_BIAS_EN

6 XXXX VDDSHV6 XXXX VDDS LCD_DATA13 LCD_DATA12 LCD_DATA14

5 VDDS_DDR XXXX VPP XXXX LCD_DATA10 LCD_DATA11 LCD_PCLK

4 DDR_D0 DDR_D1 XXXX XXXX XXXX LCD_DATA8 LCD_DATA9

3 DDR_DQM0 DDR_D4 DDR_D7 XXXX LCD_DATA7 LCD_DATA6 LCD_DATA5

2 DDR_D14 DDR_D2 DDR_DQSn0 DDR_D6 LCD_DATA1 LCD_DATA3 LCD_DATA4

1 DDR_D15 DDR_D3 DDR_DQS0 DDR_D5 LCD_DATA0 LCD_DATA2 VSS

Terminal Configuration and FunctionsCopyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

13

Page 14

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

4.1.2 ZCZ Package Pin Maps (Top View)

The pin maps that follow show the pin assignments on the ZCZ package in three sections (left, middle,

and right).

www.ti.com

14

Terminal Configuration and Functions Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 15

Left

Pin map section location

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

ZCZ Pin Map [Section Left - Top View]

A B C D E F

18 VSS EXTINTn ECAP0_IN_PWM0_OUT UART1_CTSn UART0_CTSn MMC0_DAT2

17 SPI0_SCLK SPI0_D0 I2C0_SDA UART1_RTSn UART0_RTSn MMC0_DAT3

16 SPI0_CS0 SPI0_D1 I2C0_SCL UART1_RXD UART0_TXD USB0_DRVVBUS

15 XDMA_EVENT_INTR0 PWRONRSTn SPI0_CS1 UART1_TXD UART0_RXD USB1_DRVVBUS

14 MCASP0_AHCLKX EMU1 EMU0 XDMA_EVENT_INTR1 VDDS VDDSHV6

13 MCASP0_ACLKX MCASP0_FSX MCASP0_FSR MCASP0_AXR1 VDDSHV6 VDD_MPU

12 TCK MCASP0_ACLKR MCASP0_AHCLKR MCASP0_AXR0 VDDSHV6 VDD_MPU

11 TDO TDI TMS CAP_VDD_SRAM_MPU VDDSHV6 VDD_MPU

10 WARMRSTn TRSTn CAP_VBB_MPU VDDS_SRAM_MPU_BB VDDSHV6 VDD_MPU

9 VREFN VREFP AIN7 CAP_VDD_SRAM_CORE VDDS_SRAM_CORE_BG VDDS

8 AIN6 AIN5 AIN4 VDDA_ADC VSSA_ADC VSS

7 AIN3 AIN2 AIN1 VDDS_RTC VDDS_PLL_DDR VDD_CORE

6 RTC_XTALIN AIN0 PMIC_POWER_EN CAP_VDD_RTC VDDS VDD_CORE

5 VSS_RTC RTC_PWRONRSTn EXT_WAKEUP DDR_A6 VDDS_DDR VDDS_DDR

4 RTC_XTALOUT RTC_KALDO_ENn DDR_BA0 DDR_A8 DDR_A2 DDR_A10

3 RESERVED DDR_BA2 DDR_A3 DDR_A15 DDR_A12 DDR_A0

2 VDD_MPU_MON DDR_WEn DDR_A4 DDR_CK DDR_A7 DDR_A11

1 VSS DDR_A5 DDR_A9 DDR_CKn DDR_BA1 DDR_CASn

Terminal Configuration and FunctionsCopyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

15

Page 16

Middle

Pin map section location

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

ZCZ Pin Map [Section Middle - Top View]

G H J K L M

18 MMC0_CMD RMII1_REF_CLK MII1_TXD3 MII1_TX_CLK MII1_RX_CLK MDC

17 MMC0_CLK MII1_CRS MII1_RX_DV MII1_TXD0 MII1_RXD3 MDIO

16 MMC0_DAT0 MII1_COL MII1_TX_EN MII1_TXD1 MII1_RXD2 MII1_RXD0

15 MMC0_DAT1 VDDS_PLL_MPU MII1_RX_ER MII1_TXD2 MII1_RXD1 USB0_CE

14 VDDSHV6 VDDSHV4 VDDSHV4 VDDSHV5 VDDSHV5 VSSA_USB

13 VDD_MPU VDD_MPU VDD_MPU VDDS VSS VDD_CORE

12 VSS VSS VDD_CORE VDD_CORE VSS VSS

11 VSS VDD_CORE VSS VSS VSS VDD_CORE

www.ti.com

10 VDD_CORE VSS VSS VSS VSS VSS

9 VSS VSS VSS VSS VDD_CORE VSS

8 VSS VSS VSS VDD_CORE VDD_CORE VSS

7 VDD_CORE VSS VSS VSS VDD_CORE VSS

6 VDD_CORE VSS VSS VDD_CORE VDD_CORE VSS

5 VDDS_DDR VDDS_DDR VDDS_DDR VDDS_DDR VDDS_DDR VPP

4 DDR_RASn DDR_A14 DDR_VREF DDR_D12 DDR_D14 DDR_D1

3 DDR_CKE DDR_A13 DDR_VTP DDR_D11 DDR_D13 DDR_D0

2 DDR_RESETn DDR_CSn0 DDR_DQM1 DDR_D10 DDR_DQSn1 DDR_DQM0

1 DDR_ODT DDR_A1 DDR_D8 DDR_D9 DDR_DQS1 DDR_D15

16

Terminal Configuration and Functions Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 17

Right

Pin map section location

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

ZCZ Pin Map [Section Right - Top View]

N P R T U V

18 USB0_DM USB1_CE USB1_DM USB1_VBUS GPMC_BEn1 VSS

17 USB0_DP USB1_ID USB1_DP GPMC_WAIT0 GPMC_WPn GPMC_A11

16 VDDA1P8V_USB0 USB0_ID VDDA1P8V_USB1 GPMC_A10 GPMC_A9 GPMC_A8

15 VDDA3P3V_USB0 USB0_VBUS VDDA3P3V_USB1 GPMC_A7 GPMC_A6 GPMC_A5

14 VSSA_USB VDDS GPMC_A4 GPMC_A3 GPMC_A2 GPMC_A1

13 VDD_CORE VDDSHV3 GPMC_A0 GPMC_CSn3 GPMC_AD15 GPMC_AD14

12 VDD_CORE VDDSHV3 GPMC_AD13 GPMC_AD12 GPMC_AD11 GPMC_CLK

11 VSS VDDSHV2 VDDS_OSC GPMC_AD10 XTALOUT VSS_OSC

10 VSS VDDSHV2 VDDS_PLL_CORE_LCD GPMC_AD9 GPMC_AD8 XTALIN

9 VDD_CORE VDDS GPMC_AD6 GPMC_AD7 GPMC_CSn1 GPMC_CSn2

8 VDD_CORE VDDSHV1 GPMC_AD2 GPMC_AD3 GPMC_AD4 GPMC_AD5

7 VSS VDDSHV1 GPMC_ADVn_ALE GPMC_OEn_REn GPMC_AD0 GPMC_AD1

6 VDDS VDDSHV6 LCD_AC_BIAS_EN GPMC_BEn0_CLE GPMC_WEn GPMC_CSn0

5 VDDSHV6 VDDSHV6 LCD_HSYNC LCD_DATA15 LCD_VSYNC LCD_PCLK

4 DDR_D5 DDR_D7 LCD_DATA3 LCD_DATA7 LCD_DATA11 LCD_DATA14

3 DDR_D4 DDR_D6 LCD_DATA2 LCD_DATA6 LCD_DATA10 LCD_DATA13

2 DDR_D3 DDR_DQSn0 LCD_DATA1 LCD_DATA5 LCD_DATA9 LCD_DATA12

1 DDR_D2 DDR_DQS0 LCD_DATA0 LCD_DATA4 LCD_DATA8 VSS

Terminal Configuration and FunctionsCopyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

17

Page 18

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

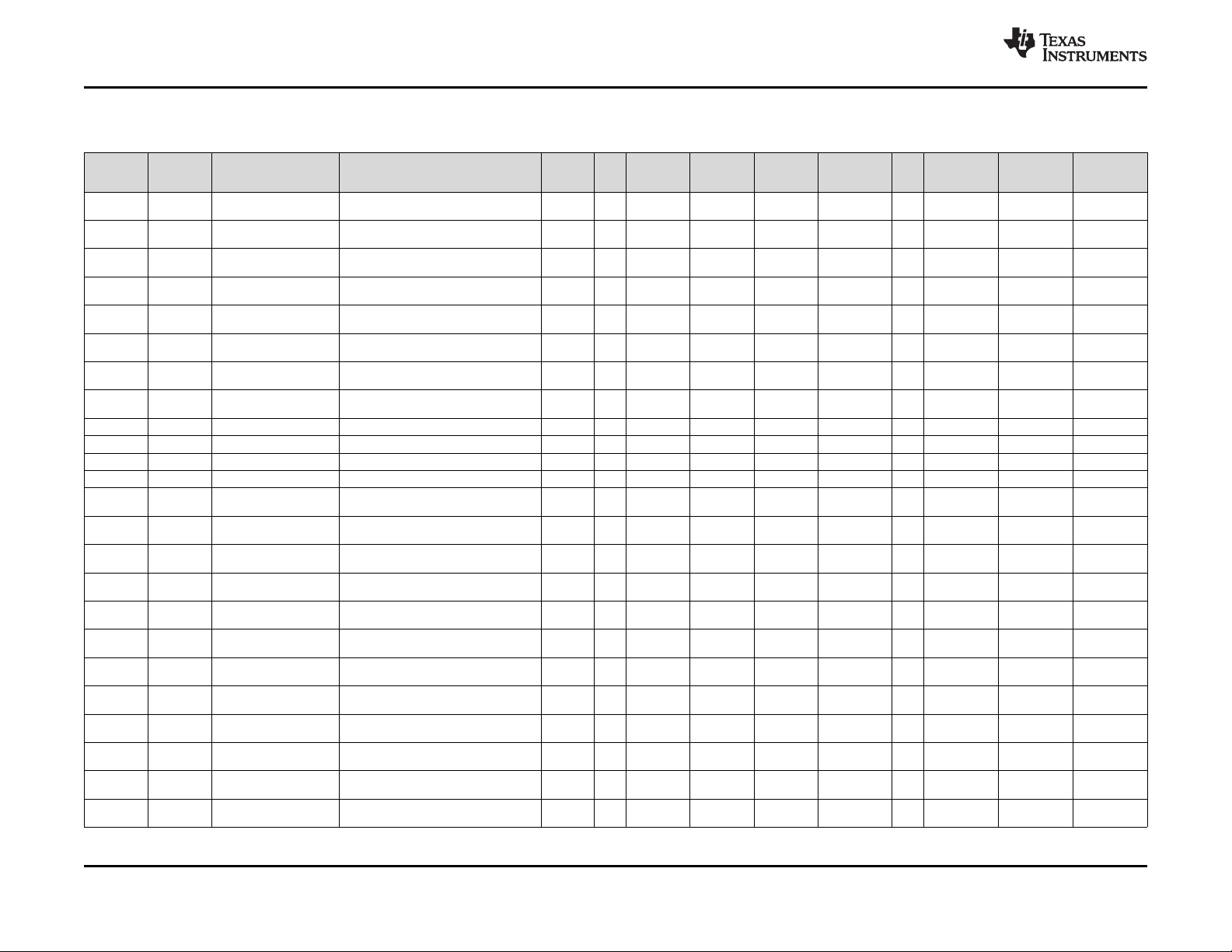

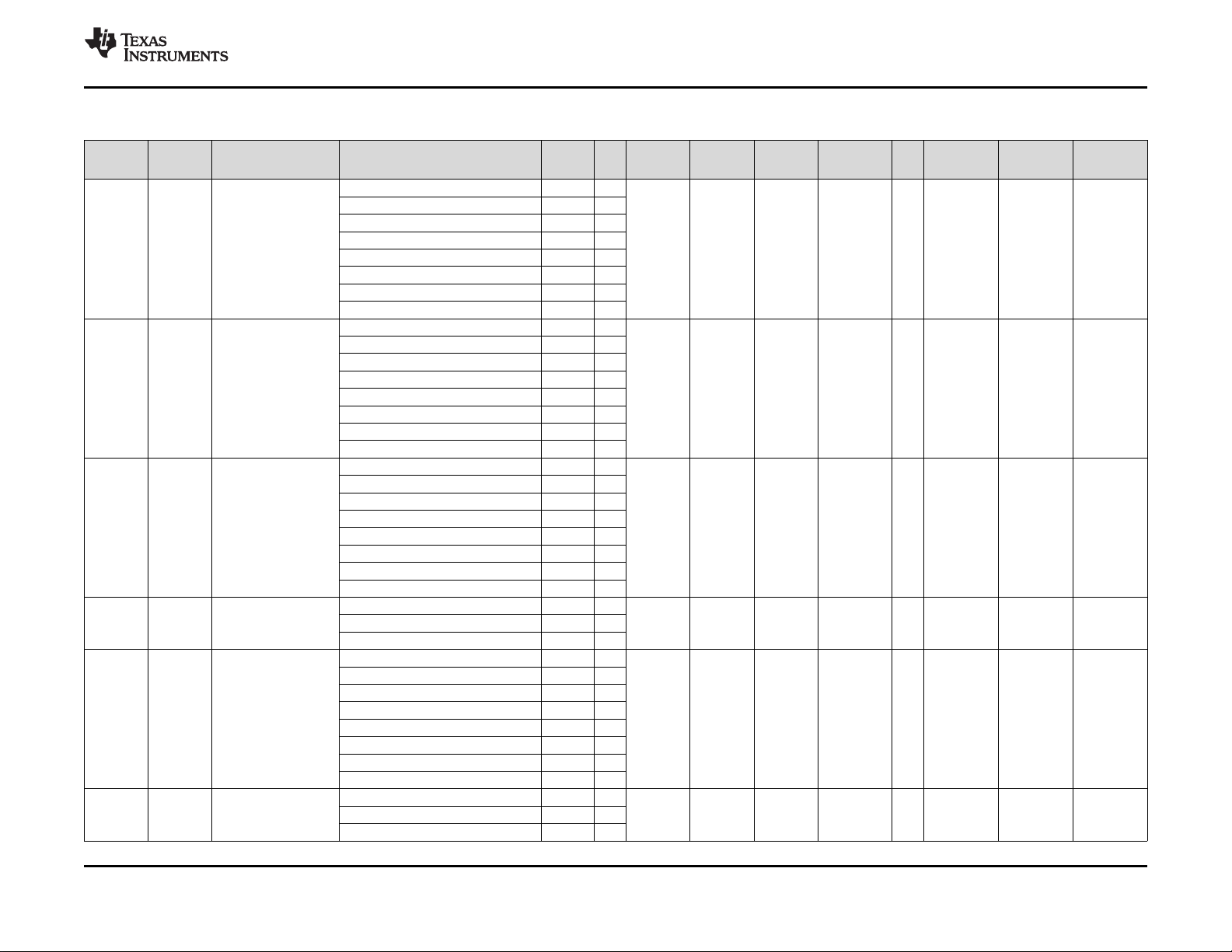

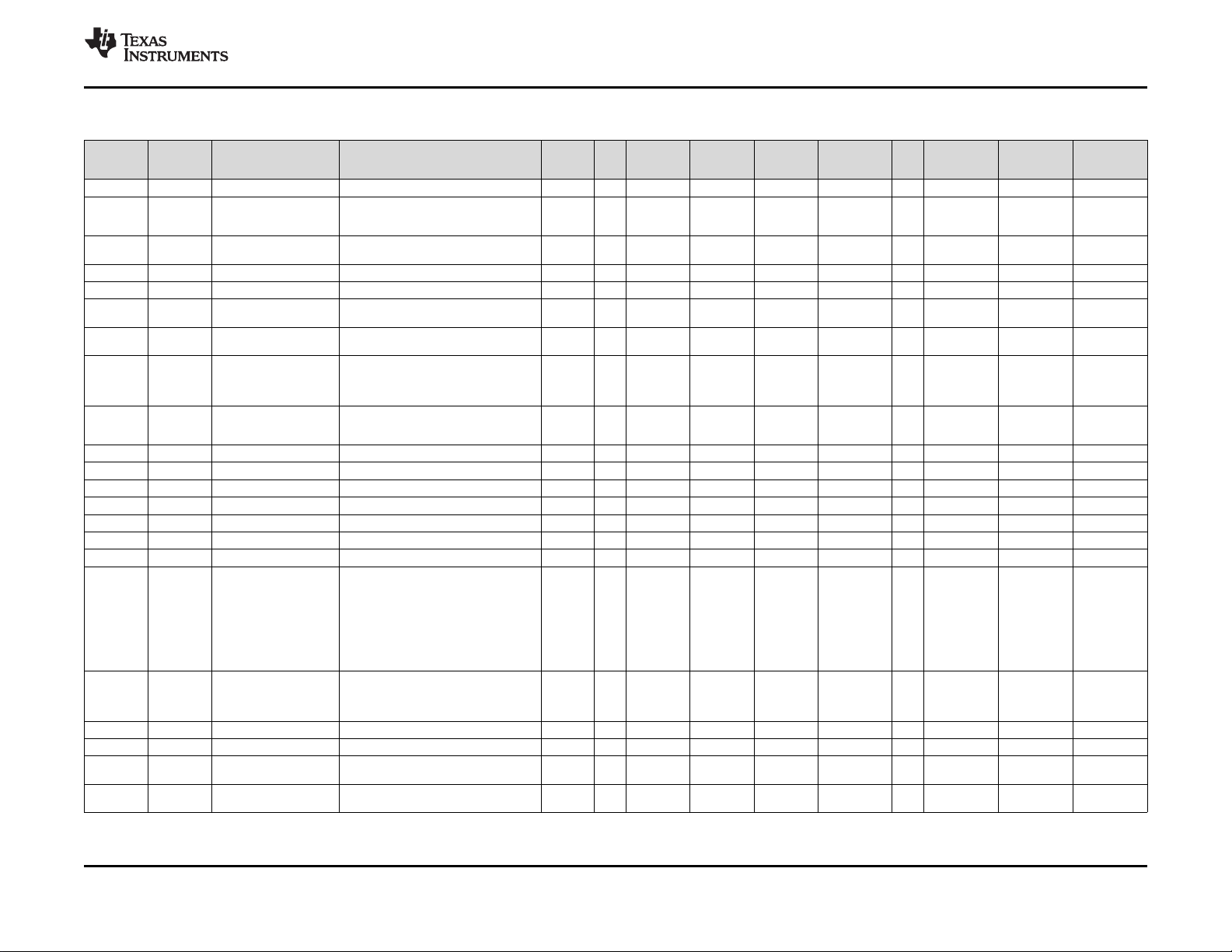

4.2 Pin Attributes

The AM335x Sitara Processors Technical Reference Manual (SPRUH73) and this document may

reference internal signal names when discussing peripheral input and output signals because many of the

AM335x package terminals can be multiplexed to one of several peripheral signals. The following table

has a Pin Name column that lists all device terminal names and a Signal Name column that lists all

internal signal names multiplexed to each terminal which provides a cross reference of internal signal

names to terminal names. This table also identifies other important terminal characteristics.

1. BALL NUMBER: Package ball numbers associated with each signals.

2. PIN NAME: The name of the package pin or terminal.

Note: The table does not take into account subsystem terminal multiplexing options.

3. SIGNAL NAME: The signal name for that pin in the mode being used.

4. MODE: Multiplexing mode number.

(a) Mode 0 is the primary mode; this means that when mode 0 is set, the function mapped on the

terminal corresponds to the name of the terminal. There is always a function mapped on the

primary mode. Notice that primary mode is not necessarily the default mode.

Note: The default mode is the mode at the release of the reset; also see the RESET REL. MODE

column.

(b) Modes 1 to 7 are possible modes for alternate functions. On each terminal, some modes are

effectively used for alternate functions, while some modes are not used and do not correspond to a

functional configuration.

5. TYPE: Signal direction

– I = Input

– O = Output

– I/O = Input and Output

– D = Open drain

– DS = Differential

– A = Analog

– PWR = Power

– GND = Ground

Note: In the safe_mode, the buffer is configured in high-impedance.

6. BALL RESET STATE: State of the terminal while the active low PWRONRSTn terminal is low.

– 0: The buffer drives VOL(pulldown or pullup resistor not activated)

0(PD): The buffer drives VOLwith an active pulldown resistor

– 1: The buffer drives VOH(pulldown or pullup resistor not activated)

1(PU): The buffer drives VOHwith an active pullup resistor

– Z: High-impedance

– L: High-impedance with an active pulldown resistor

– H : High-impedance with an active pullup resistor

7. BALL RESET REL. STATE: State of the terminal after the active low PWRONRSTn terminal

transitions from low to high.

– 0: The buffer drives VOL(pulldown or pullup resistor not activated)

0(PD): The buffer drives VOLwith an active pulldown resistor

– 1: The buffer drives VOH(pulldown or pullup resistor not activated)

1(PU): The buffer drives VOHwith an active pullup resistor

– Z: High-impedance.

– L: High-impedance with an active pulldown resistor

– H : High-impedance with an active pullup resistor

8. RESET REL. MODE: The mode is automatically configured after the active low PWRONRSTn terminal

transitions from low to high.

9. POWER: The voltage supply that powers the terminal’s IO buffers.

www.ti.com

18

Terminal Configuration and Functions Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 19

www.ti.com

10. HYS: Indicates if the input buffer is with hysteresis.

11. BUFFER STRENGTH: Drive strength of the associated output buffer.

12. PULLUP OR PULLDOWN TYPE: Denotes the presence of an internal pullup or pulldown resistor.

13. IO CELL: IO cell information.

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Pullup and pulldown resistors can be enabled or disabled via software.

Note: Configuring two terminals to the same input signal is not supported as it can yield unexpected

results. This can be easily prevented with the proper software configuration.

Terminal Configuration and FunctionsCopyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

19

Page 20

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

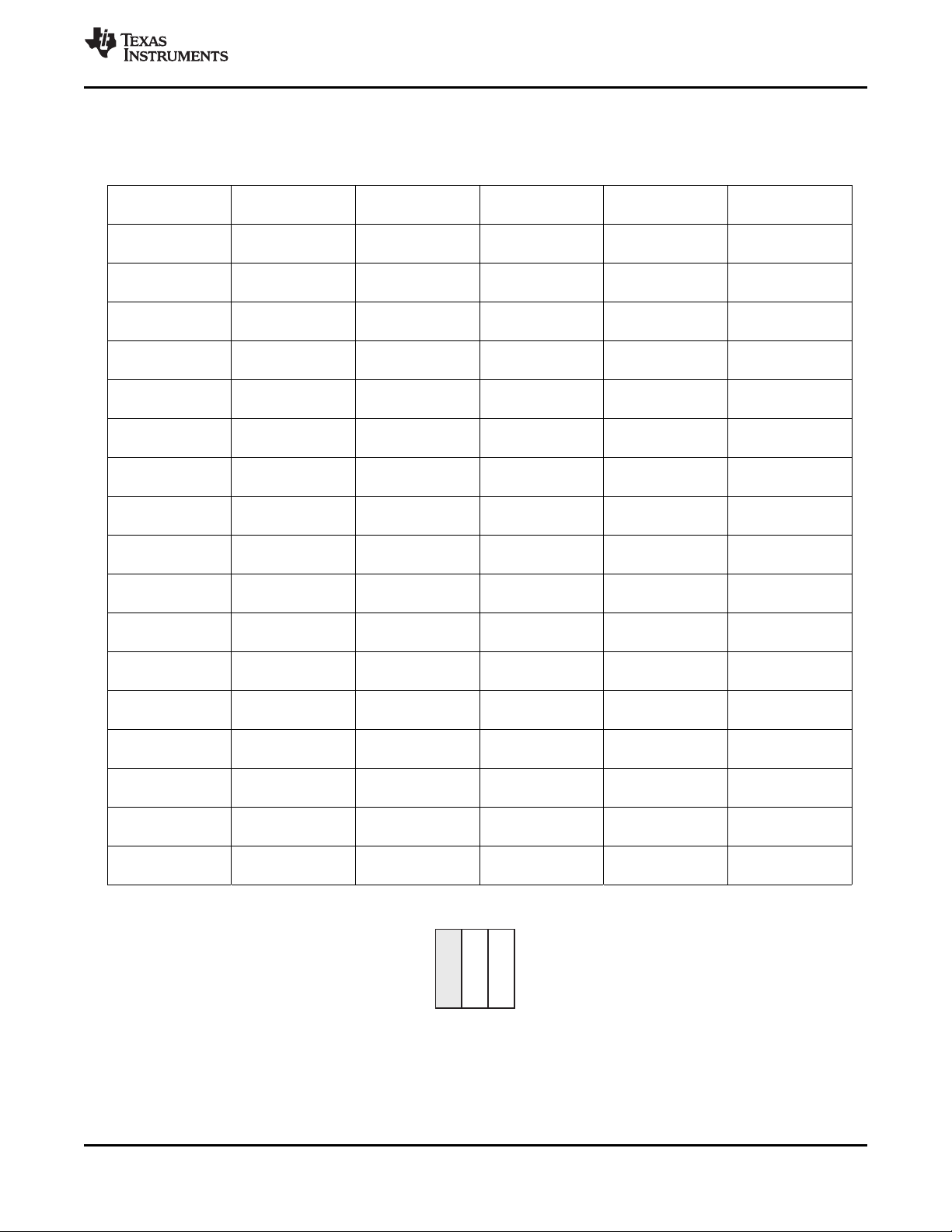

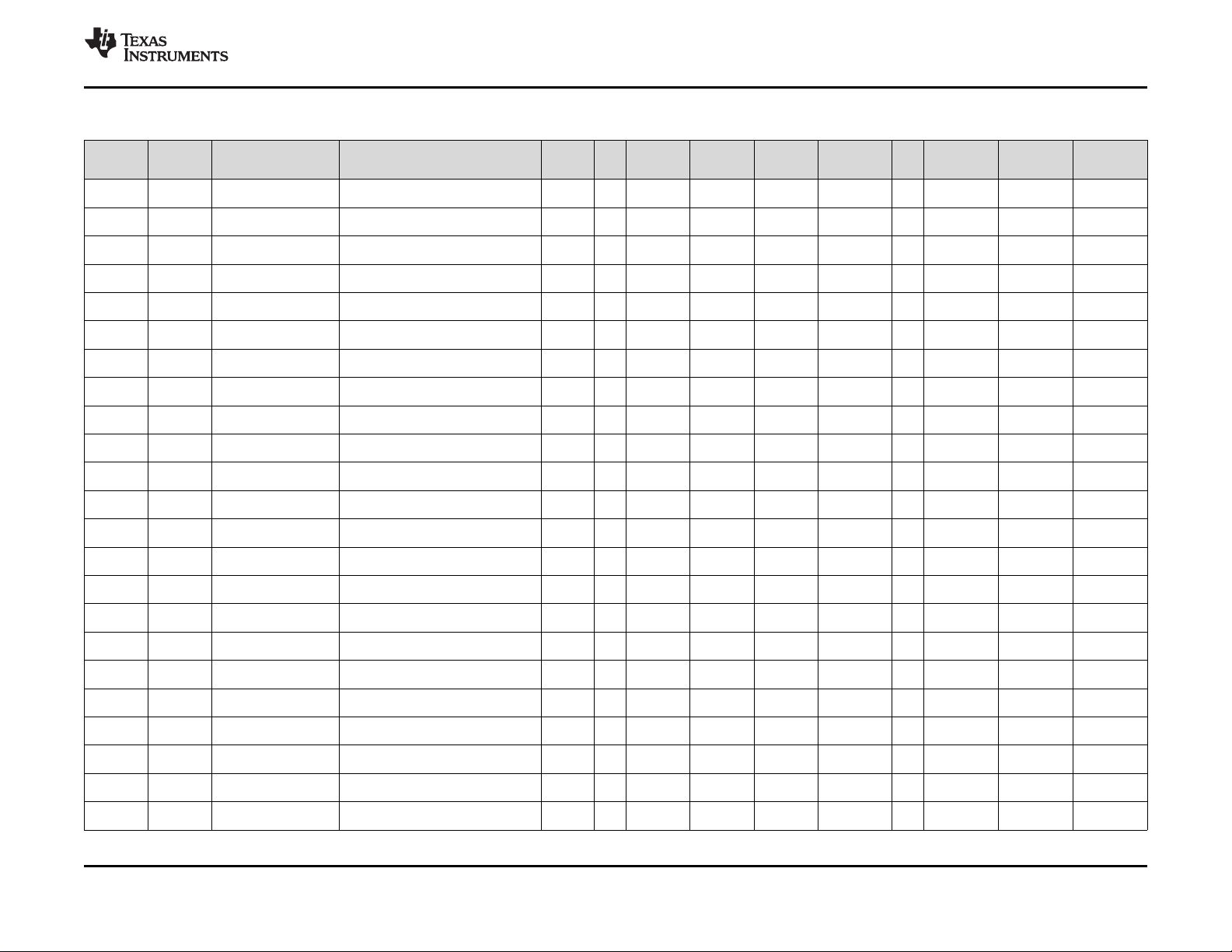

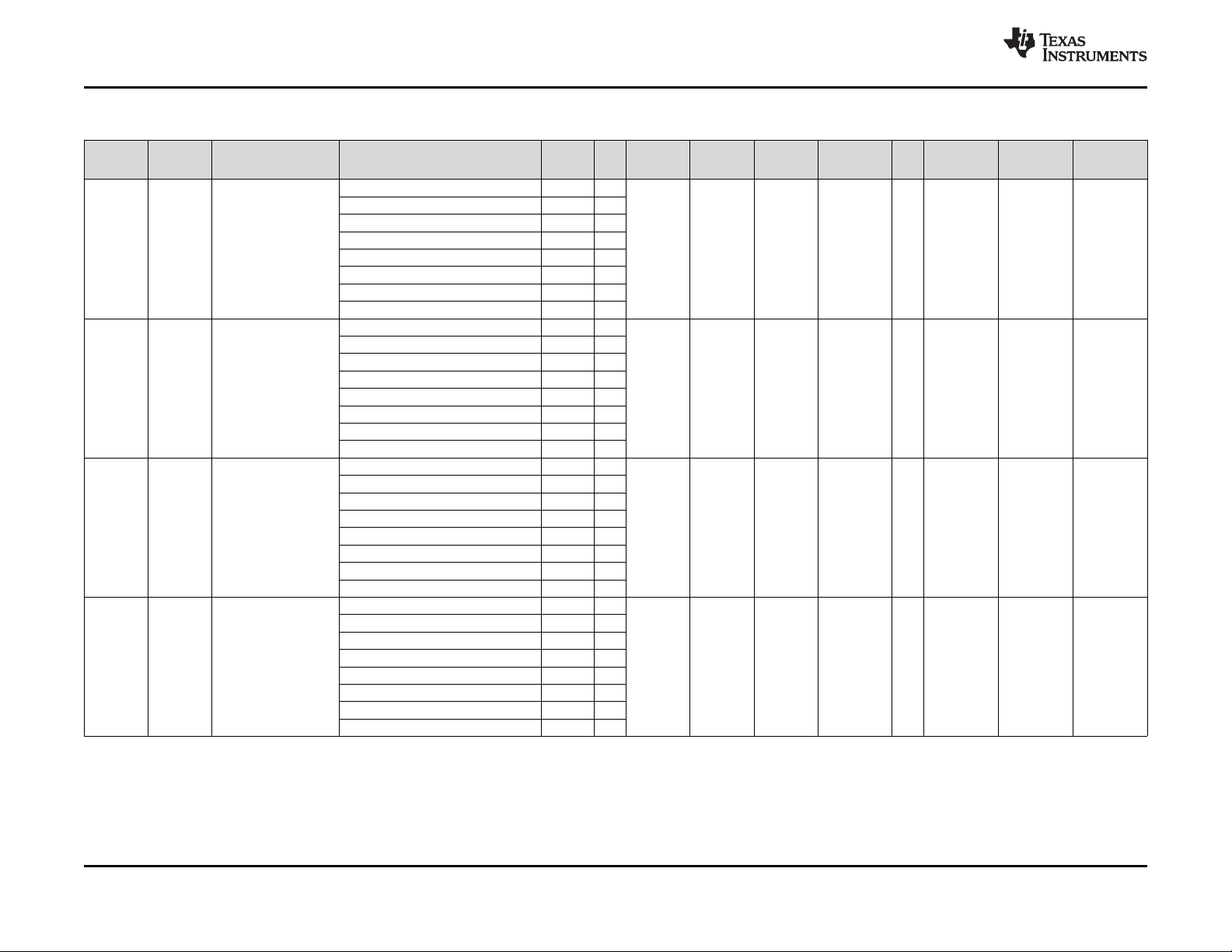

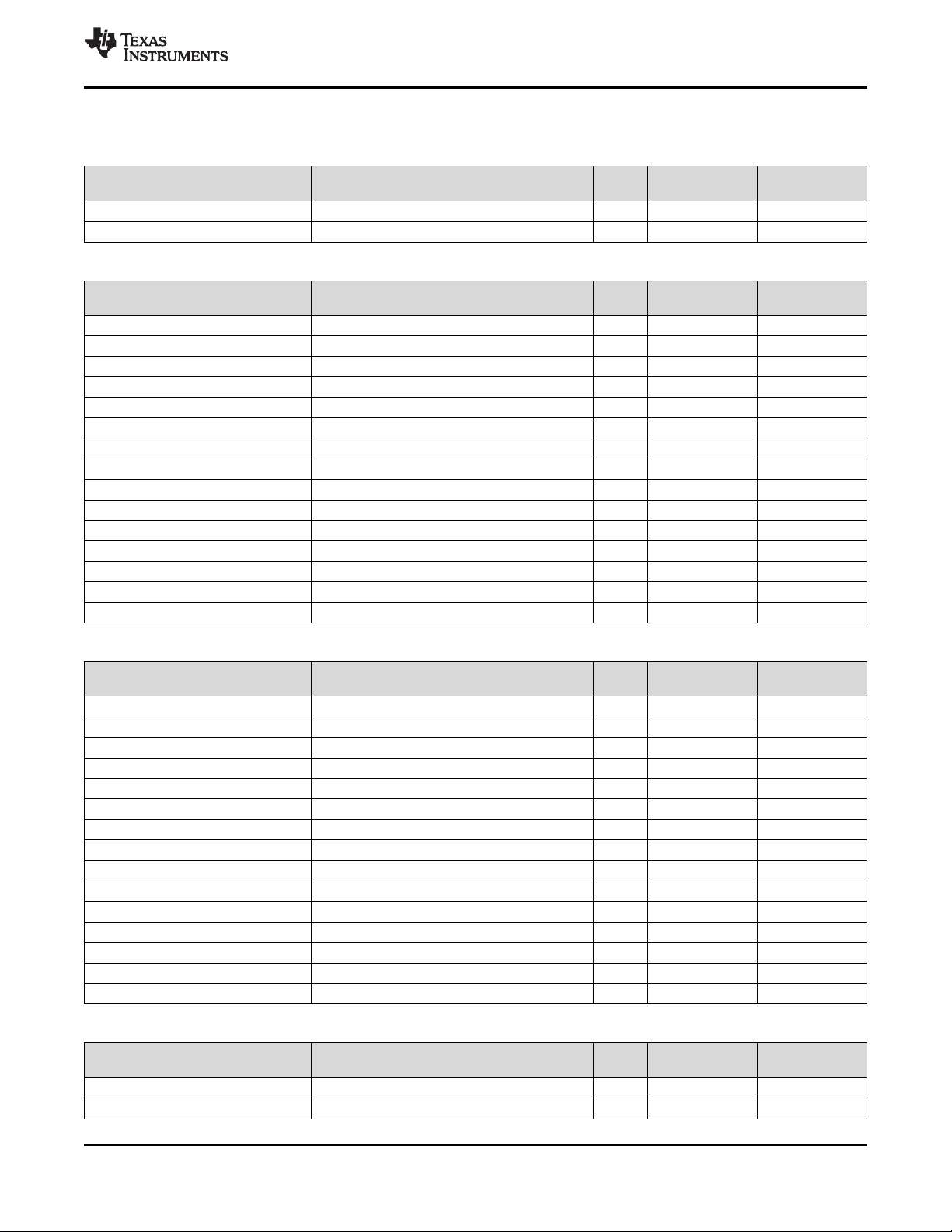

Table 4-1. Pin Attributes (ZCE and ZCZ Packages)

www.ti.com

ZCE BALL

NUMBER [1]

B8 B6 AIN0 AIN0 0 A

A11 C7 AIN1 AIN1 0 A

A8 B7 AIN2 AIN2 0 A

B11 A7 AIN3 AIN3 0 A

C8 C8 AIN4 AIN4 0 A

B12 B8 AIN5 AIN5 0 A Z Z 0 VDDA_ADC /

A10 A8 AIN6 AIN6 0 A Z Z 0 VDDA_ADC /

A12 C9 AIN7 AIN7 0 A Z Z 0 VDDA_ADC /

C13 C10 CAP_VBB_MPU CAP_VBB_MPU NA A

D6 D6 CAP_VDD_RTC CAP_VDD_RTC NA A

B10 D9 CAP_VDD_SRAM_CORE CAP_VDD_SRAM_CORE NA A

D13 D11 CAP_VDD_SRAM_MPU CAP_VDD_SRAM_MPU NA A

F3 F3 DDR_A0 ddr_a0 0 O H 1 0 VDDS_DDR /

J2 H1 DDR_A1 ddr_a1 0 O H 1 0 VDDS_DDR /

D1 E4 DDR_A2 ddr_a2 0 O H 1 0 VDDS_DDR /

B3 C3 DDR_A3 ddr_a3 0 O H 1 0 VDDS_DDR /

E5 C2 DDR_A4 ddr_a4 0 O H 1 0 VDDS_DDR /

A2 B1 DDR_A5 ddr_a5 0 O H 1 0 VDDS_DDR /

B1 D5 DDR_A6 ddr_a6 0 O H 1 0 VDDS_DDR /

D2 E2 DDR_A7 ddr_a7 0 O H 1 0 VDDS_DDR /

C3 D4 DDR_A8 ddr_a8 0 O H 1 0 VDDS_DDR /

B2 C1 DDR_A9 ddr_a9 0 O H 1 0 VDDS_DDR /

E2 F4 DDR_A10 ddr_a10 0 O H 1 0 VDDS_DDR /

G4 F2 DDR_A11 ddr_a11 0 O H 1 0 VDDS_DDR /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

TYPE

BALL RESET

[5]

STATE [6]

(22)

Z Z 0 VDDA_ADC /

(21)

Z Z 0 VDDA_ADC /

(21)

Z Z 0 VDDA_ADC /

(20)

Z Z 0 VDDA_ADC /

(20)

Z Z 0 VDDA_ADC /

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDA_ADC

VDDA_ADC

VDDA_ADC

VDDA_ADC

VDDA_ADC

VDDA_ADC

VDDA_ADC

VDDA_ADC

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

NA 25 NA Analog

NA 25 NA Analog

NA 25 NA Analog

NA 25 NA Analog

NA 25 NA Analog

NA NA NA Analog

NA NA NA Analog

NA NA NA Analog

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

20

Copyright © 2011–2016, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 21

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

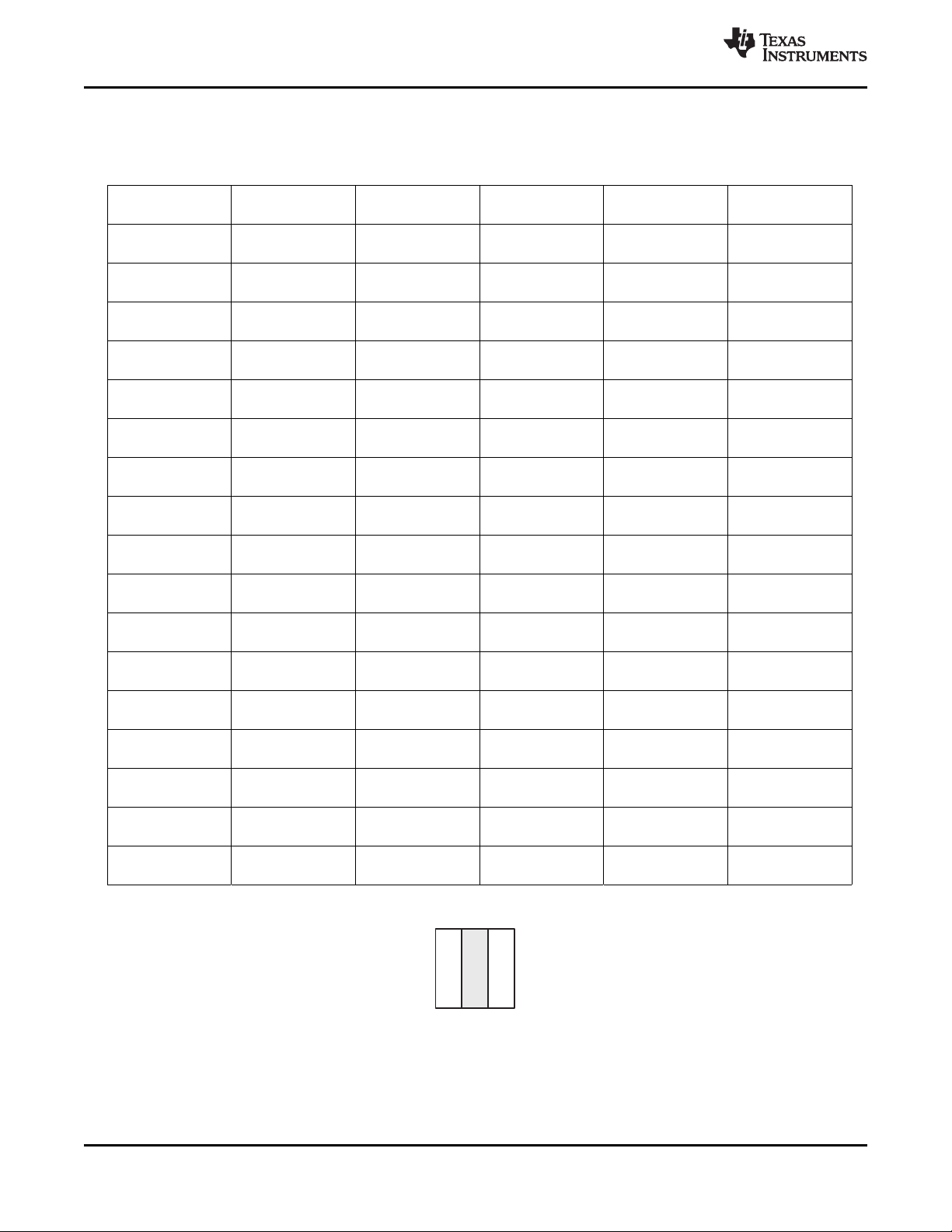

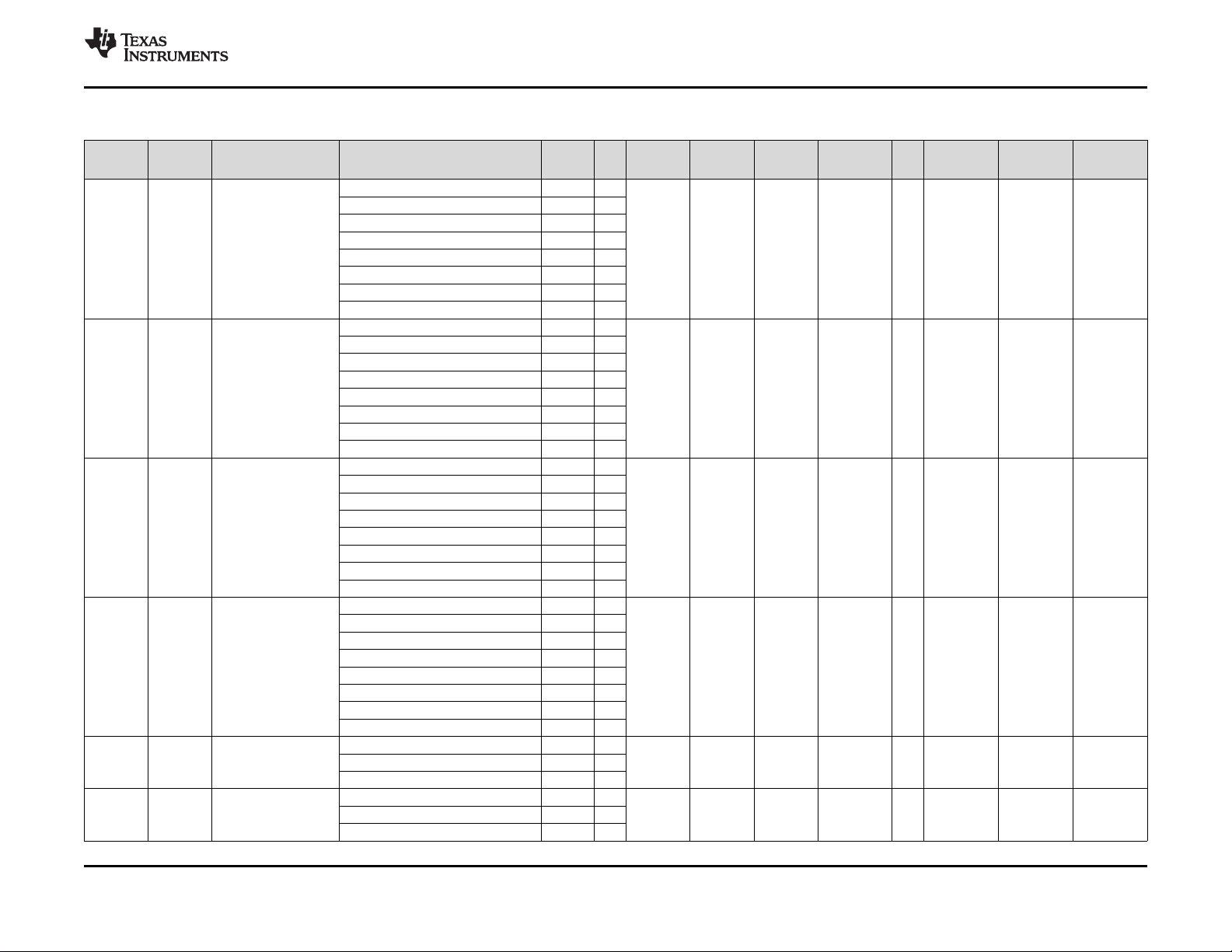

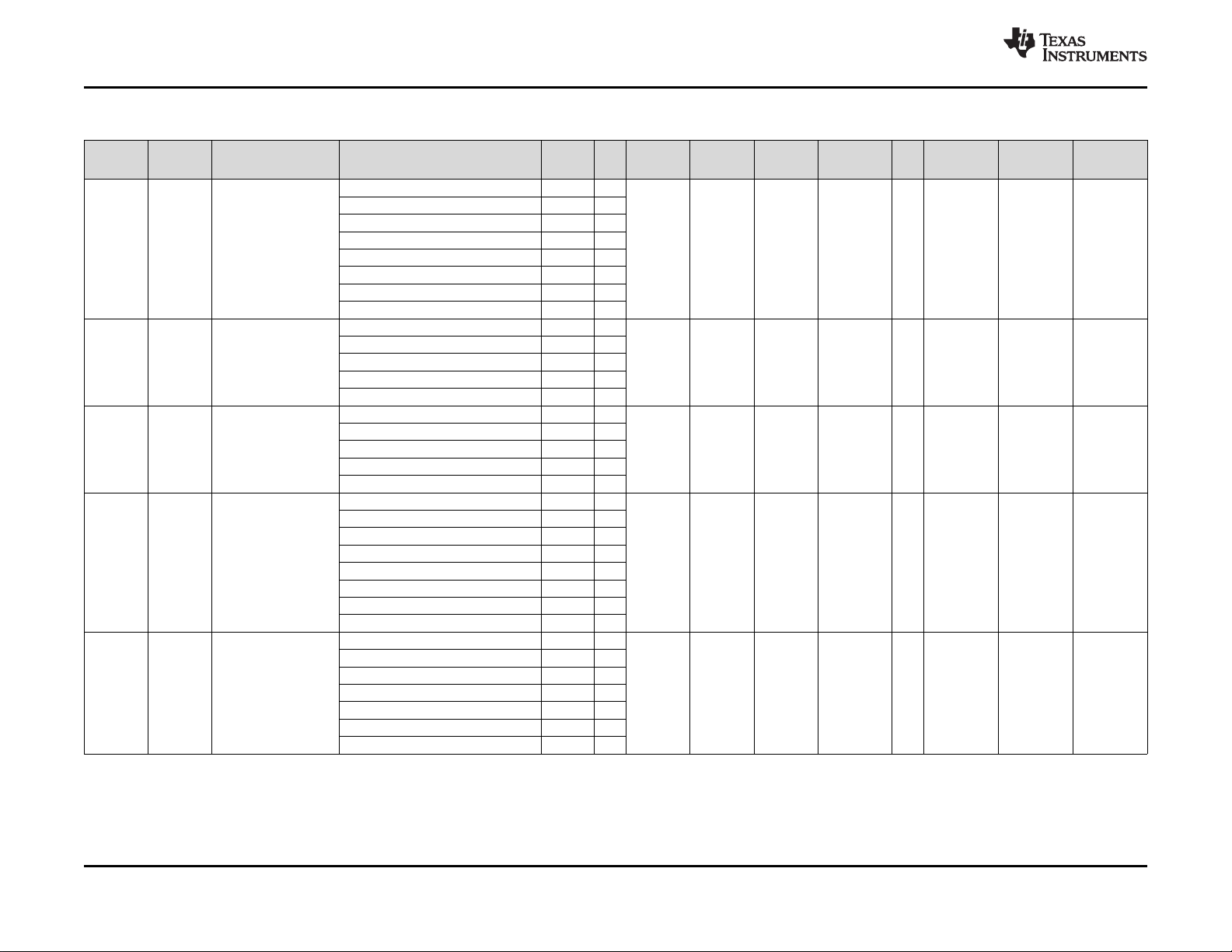

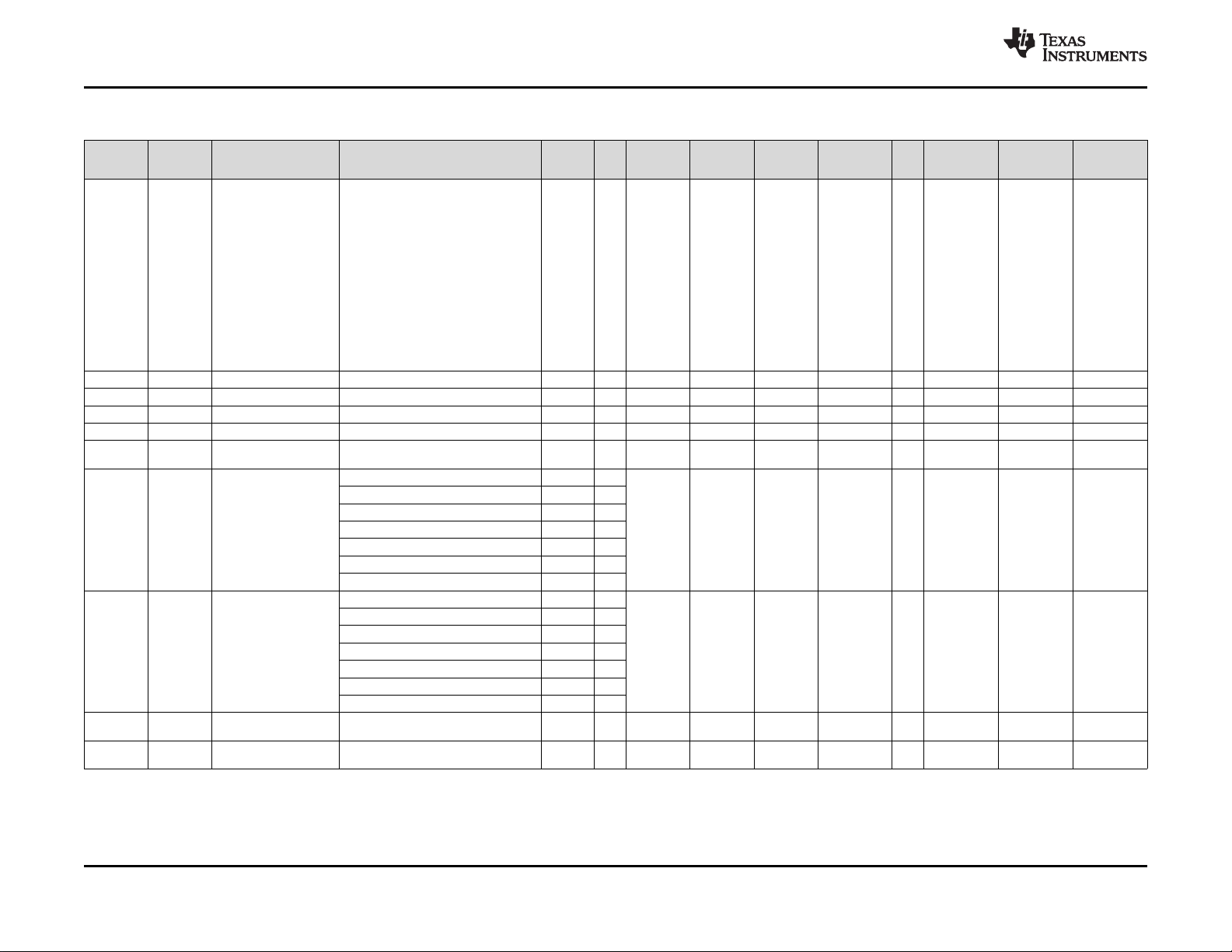

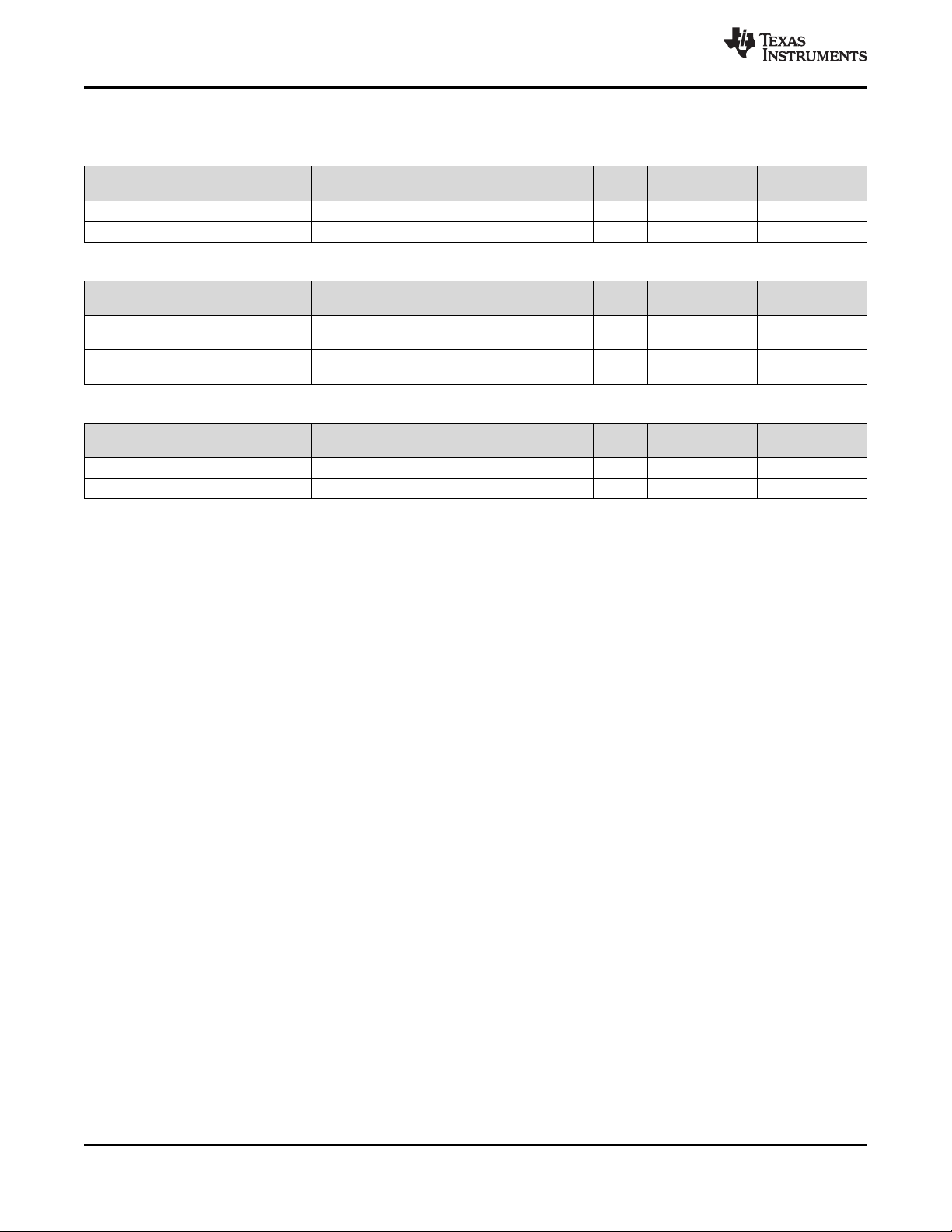

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

F4 E3 DDR_A12 ddr_a12 0 O H 1 0 VDDS_DDR /

H1 H3 DDR_A13 ddr_a13 0 O H 1 0 VDDS_DDR /

H3 H4 DDR_A14 ddr_a14 0 O H 1 0 VDDS_DDR /

E3 D3 DDR_A15 ddr_a15 0 O H 1 0 VDDS_DDR /

A3 C4 DDR_BA0 ddr_ba0 0 O H 1 0 VDDS_DDR /

E1 E1 DDR_BA1 ddr_ba1 0 O H 1 0 VDDS_DDR /

B4 B3 DDR_BA2 ddr_ba2 0 O H 1 0 VDDS_DDR /

F1 F1 DDR_CASn ddr_casn 0 O H 1 0 VDDS_DDR /

C2 D2 DDR_CK ddr_ck 0 O L 0 0 VDDS_DDR /

G3 G3 DDR_CKE ddr_cke 0 O L 0 0 VDDS_DDR /

C1 D1 DDR_CKn ddr_nck 0 O H 1 0 VDDS_DDR /

H2 H2 DDR_CSn0 ddr_csn0 0 O H 1 0 VDDS_DDR /

N4 M3 DDR_D0 ddr_d0 0 I/O L Z 0 VDDS_DDR /

P4 M4 DDR_D1 ddr_d1 0 I/O L Z 0 VDDS_DDR /

P2 N1 DDR_D2 ddr_d2 0 I/O L Z 0 VDDS_DDR /

P1 N2 DDR_D3 ddr_d3 0 I/O L Z 0 VDDS_DDR /

P3 N3 DDR_D4 ddr_d4 0 I/O L Z 0 VDDS_DDR /

T1 N4 DDR_D5 ddr_d5 0 I/O L Z 0 VDDS_DDR /

T2 P3 DDR_D6 ddr_d6 0 I/O L Z 0 VDDS_DDR /

R3 P4 DDR_D7 ddr_d7 0 I/O L Z 0 VDDS_DDR /

K2 J1 DDR_D8 ddr_d8 0 I/O L Z 0 VDDS_DDR /

K1 K1 DDR_D9 ddr_d9 0 I/O L Z 0 VDDS_DDR /

M3 K2 DDR_D10 ddr_d10 0 I/O L Z 0 VDDS_DDR /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

Copyright © 2011–2016, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

21

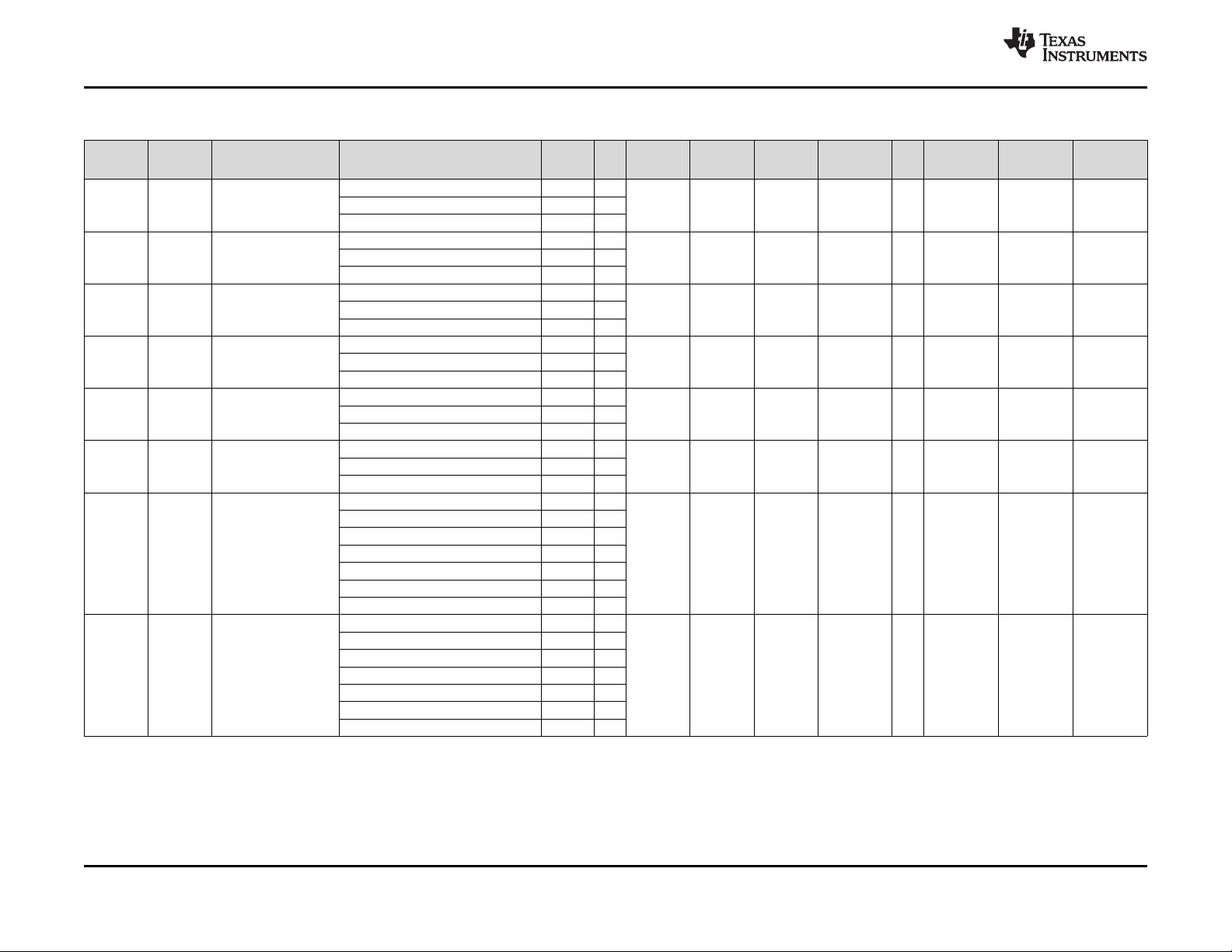

Page 22

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

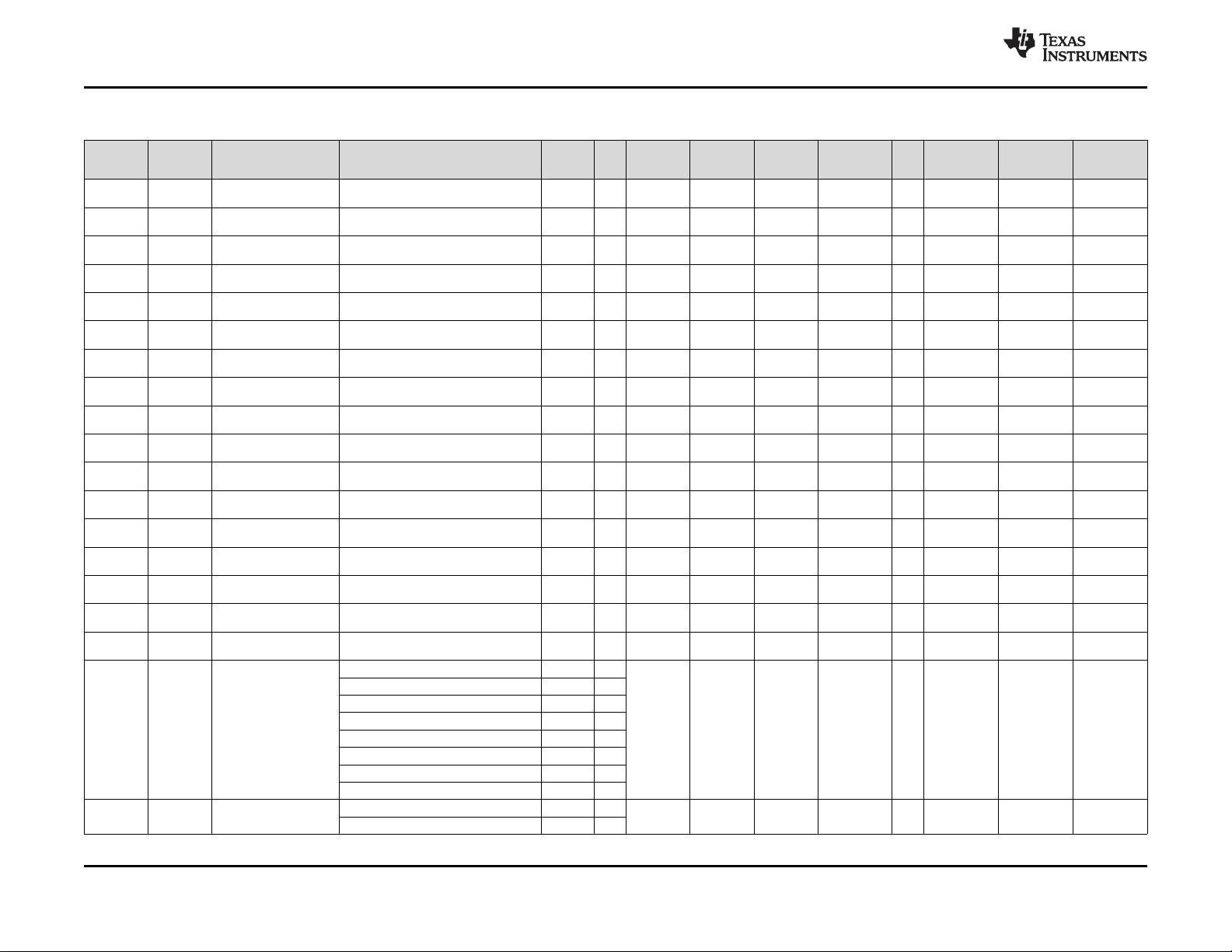

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

M4 K3 DDR_D11 ddr_d11 0 I/O L Z 0 VDDS_DDR /

M2 K4 DDR_D12 ddr_d12 0 I/O L Z 0 VDDS_DDR /

M1 L3 DDR_D13 ddr_d13 0 I/O L Z 0 VDDS_DDR /

N2 L4 DDR_D14 ddr_d14 0 I/O L Z 0 VDDS_DDR /

N1 M1 DDR_D15 ddr_d15 0 I/O L Z 0 VDDS_DDR /

N3 M2 DDR_DQM0 ddr_dqm0 0 O H 1 0 VDDS_DDR /

K3 J2 DDR_DQM1 ddr_dqm1 0 O H 1 0 VDDS_DDR /

R1 P1 DDR_DQS0 ddr_dqs0 0 I/O L Z 0 VDDS_DDR /

L1 L1 DDR_DQS1 ddr_dqs1 0 I/O L Z 0 VDDS_DDR /

R2 P2 DDR_DQSn0 ddr_dqsn0 0 I/O H Z 0 VDDS_DDR /

L2 L2 DDR_DQSn1 ddr_dqsn1 0 I/O H Z 0 VDDS_DDR /

G1 G1 DDR_ODT ddr_odt 0 O L 0 0 VDDS_DDR /

F2 G4 DDR_RASn ddr_rasn 0 O H 1 0 VDDS_DDR /

G2 G2 DDR_RESETn ddr_resetn 0 O L 0 0 VDDS_DDR /

H4 J4 DDR_VREF ddr_vref 0 A

J1 J3 DDR_VTP ddr_vtp 0 I

A4 B2 DDR_WEn ddr_wen 0 O H 1 0 VDDS_DDR /

E18 C18 ECAP0_IN_PWM0_OUT eCAP0_in_PWM0_out 0 I/O Z L 7 VDDSHV6 /

A15 C14 EMU0 EMU0 0 I/O H H 0 VDDSHV6 /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

uart3_txd 1 O

spi1_cs1 2 I/O

pr1_ecap0_ecap_capin_apwm_o 3 I/O

spi1_sclk 4 I/O

mmc0_sdwp 5 I

xdma_event_intr2 6 I

gpio0_7 7 I/O

gpio3_7 7 I/O

TYPE

BALL RESET

[5]

STATE [6]

(18)

NA NA NA VDDS_DDR /

(19)

NA NA NA VDDS_DDR /

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDS_DDR

VDDSHV6

VDDSHV6

www.ti.com

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

Yes 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA 8 PU/PD LVCMOS/SSTL/

NA NA NA Analog

NA NA NA Analog

NA 8 PU/PD LVCMOS/SSTL/

Yes 4 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

HSTL

22

Copyright © 2011–2016, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 23

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

D14 B14 EMU1 EMU1 0 I/O H H 0 VDDSHV6 /

C17 B18 EXTINTn nNMI 0 I Z H 0 VDDSHV6 /

B5 C5 EXT_WAKEUP EXT_WAKEUP 0 I L Z 0 VDDS_RTC /

NA R13 GPMC_A0 gpmc_a0 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

NA V14 GPMC_A1 gpmc_a1 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

NA U14 GPMC_A2 gpmc_a2 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

NA T14 GPMC_A3 gpmc_a3 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

gpio3_8 7 I/O

gmii2_txen 1 O

rgmii2_tctl 2 O

rmii2_txen 3 O

gpmc_a16 4 O

pr1_mii_mt1_clk 5 I

ehrpwm1_tripzone_input 6 I

gpio1_16 7 I/O

gmii2_rxdv 1 I

rgmii2_rctl 2 I

mmc2_dat0 3 I/O

gpmc_a17 4 O

pr1_mii1_txd3 5 O

ehrpwm0_synco 6 O

gpio1_17 7 I/O

gmii2_txd3 1 O

rgmii2_td3 2 O

mmc2_dat1 3 I/O

gpmc_a18 4 O

pr1_mii1_txd2 5 O

ehrpwm1A 6 O

gpio1_18 7 I/O

gmii2_txd2 1 O

rgmii2_td2 2 O

mmc2_dat2 3 I/O

gpmc_a19 4 O

pr1_mii1_txd1 5 O

ehrpwm1B 6 O

gpio1_19 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV6

VDDSHV6

VDDS_RTC

Yes 6 PU/PD LVCMOS

Yes NA PU/PD LVCMOS

Yes NA NA LVCMOS

HYS

[10]

BUFFER

STRENGTH

(mA) [11]

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

Copyright © 2011–2016, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

23

Page 24

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

www.ti.com

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

NA R14 GPMC_A4 gpmc_a4 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

NA V15 GPMC_A5 gpmc_a5 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

NA U15 GPMC_A6 gpmc_a6 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

NA T15 GPMC_A7 gpmc_a7 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

gmii2_txd1 1 O

rgmii2_td1 2 O

rmii2_txd1 3 O

gpmc_a20 4 O

pr1_mii1_txd0 5 O

eQEP1A_in 6 I

gpio1_20 7 I/O

gmii2_txd0 1 O

rgmii2_td0 2 O

rmii2_txd0 3 O

gpmc_a21 4 O

pr1_mii1_rxd3 5 I

eQEP1B_in 6 I

gpio1_21 7 I/O

gmii2_txclk 1 I

rgmii2_tclk 2 O

mmc2_dat4 3 I/O

gpmc_a22 4 O

pr1_mii1_rxd2 5 I

eQEP1_index 6 I/O

gpio1_22 7 I/O

gmii2_rxclk 1 I

rgmii2_rclk 2 I

mmc2_dat5 3 I/O

gpmc_a23 4 O

pr1_mii1_rxd1 5 I

eQEP1_strobe 6 I/O

gpio1_23 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

HYS

[10]

BUFFER

STRENGTH

(mA) [11]

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

24

Copyright © 2011–2016, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 25

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

NA V16 GPMC_A8 gpmc_a8 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

NA U16 GPMC_A9

NA T16 GPMC_A10 gpmc_a10 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

NA V17 GPMC_A11 gpmc_a11 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

W10 U7 GPMC_AD0 gpmc_ad0 0 I/O L L 7 VDDSHV1 /

V9 V7 GPMC_AD1 gpmc_ad1 0 I/O L L 7 VDDSHV1 /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

gmii2_rxd3 1 I

rgmii2_rd3 2 I

mmc2_dat6 3 I/O

gpmc_a24 4 O

pr1_mii1_rxd0 5 I

mcasp0_aclkx 6 I/O

(10)

gpio1_24 7 I/O

gpmc_a9 0 O L L 7 NA / VDDSHV3 Yes 6 PU/PD LVCMOS

gmii2_rxd2 1 I

rgmii2_rd2 2 I

mmc2_dat7 / rmii2_crs_dv 3 I/O

gpmc_a25 4 O

pr1_mii_mr1_clk 5 I

mcasp0_fsx 6 I/O

gpio1_25 7 I/O

gmii2_rxd1 1 I

rgmii2_rd1 2 I

rmii2_rxd1 3 I

gpmc_a26 4 O

pr1_mii1_rxdv 5 I

mcasp0_axr0 6 I/O

gpio1_26 7 I/O

gmii2_rxd0 1 I

rgmii2_rd0 2 I

rmii2_rxd0 3 I

gpmc_a27 4 O

pr1_mii1_rxer 5 I

mcasp0_axr1 6 I/O

gpio1_27 7 I/O

mmc1_dat0 1 I/O

gpio1_0 7 I/O

mmc1_dat1 1 I/O

gpio1_1 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV1

VDDSHV1

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

HYS

[10]

BUFFER

STRENGTH

(mA) [11]

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

Copyright © 2011–2016, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

25

Page 26

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

V12 R8 GPMC_AD2 gpmc_ad2 0 I/O L L 7 VDDSHV1 /

W13 T8 GPMC_AD3 gpmc_ad3 0 I/O L L 7 VDDSHV1 /

V13 U8 GPMC_AD4 gpmc_ad4 0 I/O L L 7 VDDSHV1 /

W14 V8 GPMC_AD5 gpmc_ad5 0 I/O L L 7 VDDSHV1 /

U14 R9 GPMC_AD6 gpmc_ad6 0 I/O L L 7 VDDSHV1 /

W15 T9 GPMC_AD7 gpmc_ad7 0 I/O L L 7 VDDSHV1 /

V15 U10 GPMC_AD8 gpmc_ad8 0 I/O L L 7 VDDSHV1 /

W16 T10 GPMC_AD9 gpmc_ad9 0 I/O L L 7 VDDSHV1 /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

mmc1_dat2 1 I/O

gpio1_2 7 I/O

mmc1_dat3 1 I/O

gpio1_3 7 I/O

mmc1_dat4 1 I/O

gpio1_4 7 I/O

mmc1_dat5 1 I/O

gpio1_5 7 I/O

mmc1_dat6 1 I/O

gpio1_6 7 I/O

mmc1_dat7 1 I/O

gpio1_7 7 I/O

lcd_data23 1 O

mmc1_dat0 2 I/O

mmc2_dat4 3 I/O

ehrpwm2A 4 O

pr1_mii_mt0_clk 5 I

gpio0_22 7 I/O

lcd_data22 1 O

mmc1_dat1 2 I/O

mmc2_dat5 3 I/O

ehrpwm2B 4 O

pr1_mii0_col 5 I

gpio0_23 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV1

VDDSHV1

VDDSHV1

VDDSHV1

VDDSHV1

VDDSHV1

VDDSHV2

VDDSHV2

www.ti.com

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

26

Copyright © 2011–2016, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 27

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

T12 T11 GPMC_AD10 gpmc_ad10 0 I/O L L 7 VDDSHV1 /

U12 U12 GPMC_AD11 gpmc_ad11 0 I/O L L 7 VDDSHV1 /

U13 T12 GPMC_AD12 gpmc_ad12 0 I/O L L 7 VDDSHV1 /

T13 R12 GPMC_AD13 gpmc_ad13 0 I/O L L 7 VDDSHV1 /

W17 V13 GPMC_AD14 gpmc_ad14 0 I/O L L 7 VDDSHV1 /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

lcd_data21 1 O

mmc1_dat2 2 I/O

mmc2_dat6 3 I/O

ehrpwm2_tripzone_input 4 I

pr1_mii0_txen 5 O

gpio0_26 7 I/O

lcd_data20 1 O

mmc1_dat3 2 I/O

mmc2_dat7 3 I/O

ehrpwm0_synco 4 O

pr1_mii0_txd3 5 O

gpio0_27 7 I/O

lcd_data19 1 O

mmc1_dat4 2 I/O

mmc2_dat0 3 I/O

eQEP2A_in 4 I

pr1_mii0_txd2 5 O

pr1_pru0_pru_r30_14 6 O

gpio1_12 7 I/O

lcd_data18 1 O

mmc1_dat5 2 I/O

mmc2_dat1 3 I/O

eQEP2B_in 4 I

pr1_mii0_txd1 5 O

pr1_pru0_pru_r30_15 6 O

gpio1_13 7 I/O

lcd_data17 1 O

mmc1_dat6 2 I/O

mmc2_dat2 3 I/O

eQEP2_index 4 I/O

pr1_mii0_txd0 5 O

pr1_pru0_pru_r31_14 6 I

gpio1_14 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV2

VDDSHV2

VDDSHV2

VDDSHV2

VDDSHV2

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

Copyright © 2011–2016, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

27

Page 28

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

V17 U13 GPMC_AD15 gpmc_ad15 0 I/O L L 7 VDDSHV1 /

V10 R7 GPMC_ADVn_ALE gpmc_advn_ale 0 O H H 7 VDDSHV1 /

V8 T6 GPMC_BEn0_CLE gpmc_be0n_cle 0 O H H 7 VDDSHV1 /

V18 U18 GPMC_BEn1 gpmc_be1n 0 O H H 7 VDDSHV1 /

V16 V12 GPMC_CLK gpmc_clk 0 I/O L L 7 VDDSHV1 /

W8 V6 GPMC_CSn0 gpmc_csn0 0 O H H 7 VDDSHV1 /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

lcd_data16 1 O

mmc1_dat7 2 I/O

mmc2_dat3 3 I/O

eQEP2_strobe 4 I/O

pr1_ecap0_ecap_capin_apwm_o 5 I/O

pr1_pru0_pru_r31_15 6 I

gpio1_15 7 I/O

timer4 2 I/O

gpio2_2 7 I/O

timer5 2 I/O

gpio2_5 7 I/O

gmii2_col 1 I

gpmc_csn6 2 O

mmc2_dat3 3 I/O

gpmc_dir 4 O

pr1_mii1_rxlink 5 I

mcasp0_aclkr 6 I/O

gpio1_28 7 I/O

lcd_memory_clk 1 O

gpmc_wait1 2 I

mmc2_clk 3 I/O

pr1_mii1_crs 4 I

pr1_mdio_mdclk 5 O

mcasp0_fsr 6 I/O

gpio2_1 7 I/O

gpio1_29 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV2

VDDSHV1

VDDSHV1

VDDSHV3

VDDSHV2

VDDSHV1

www.ti.com

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

28

Copyright © 2011–2016, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 29

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

V14 U9 GPMC_CSn1 gpmc_csn1 0 O H H 7 VDDSHV1 /

U15 V9 GPMC_CSn2 gpmc_csn2 0 O H H 7 VDDSHV1 /

U17 T13 GPMC_CSn3

W9 T7 GPMC_OEn_REn gpmc_oen_ren 0 O H H 7 VDDSHV1 /

R15 T17 GPMC_WAIT0 gpmc_wait0 0 I H H 7 VDDSHV1 /

U8 U6 GPMC_WEn gpmc_wen 0 O H H 7 VDDSHV1 /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

gpmc_clk 1 I/O

mmc1_clk 2 I/O

pr1_edio_data_in6 3 I

pr1_edio_data_out6 4 O

pr1_pru1_pru_r30_12 5 O

pr1_pru1_pru_r31_12 6 I

gpio1_30 7 I/O

gpmc_be1n 1 O

mmc1_cmd 2 I/O

pr1_edio_data_in7 3 I

pr1_edio_data_out7 4 O

pr1_pru1_pru_r30_13 5 O

pr1_pru1_pru_r31_13 6 I

(6)

gpio1_31 7 I/O

gpmc_csn3 0 O H H 7 VDDSHV1 /

gpmc_a3 1 O

rmii2_crs_dv 2 I

mmc2_cmd 3 I/O

pr1_mii0_crs 4 I

pr1_mdio_data 5 I/O

EMU4 6 I/O

gpio2_0 7 I/O

timer7 2 I/O

gpio2_3 7 I/O

gmii2_crs 1 I

gpmc_csn4 2 O

rmii2_crs_dv 3 I

mmc1_sdcd 4 I

pr1_mii1_col 5 I

uart4_rxd 6 I

gpio0_30 7 I/O

timer6 2 I/O

gpio2_4 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV1

VDDSHV1

VDDSHV2

VDDSHV1

VDDSHV3

VDDSHV1

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

Copyright © 2011–2016, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

29

Page 30

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

W18 U17 GPMC_WPn gpmc_wpn 0 O H H 7 VDDSHV1 /

C18 C17 I2C0_SDA I2C0_SDA 0 I/OD Z H 7 VDDSHV6 /

B19 C16 I2C0_SCL I2C0_SCL 0 I/OD Z H 7 VDDSHV6 /

W7 R6 LCD_AC_BIAS_EN lcd_ac_bias_en 0 O Z L 7 VDDSHV6 /

U1 R1 LCD_DATA0

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

gmii2_rxerr 1 I

gpmc_csn5 2 O

rmii2_rxerr 3 I

mmc2_sdcd 4 I

pr1_mii1_txen 5 O

uart4_txd 6 O

gpio0_31 7 I/O

timer4 1 I/O

uart2_ctsn 2 I

eCAP2_in_PWM2_out 3 I/O

gpio3_5 7 I/O

timer7 1 I/O

uart2_rtsn 2 O

eCAP1_in_PWM1_out 3 I/O

gpio3_6 7 I/O

gpmc_a11 1 O

pr1_mii1_crs 2 I

pr1_edio_data_in5 3 I

pr1_edio_data_out5 4 O

pr1_pru1_pru_r30_11 5 O

pr1_pru1_pru_r31_11 6 I

(5)

gpio2_25 7 I/O

lcd_data0 0 I/O Z Z 7 VDDSHV6 /

gpmc_a0 1 O

pr1_mii_mt0_clk 2 I

ehrpwm2A 3 O

pr1_pru1_pru_r30_0 5 O

pr1_pru1_pru_r31_0 6 I

gpio2_6 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV3

VDDSHV6

VDDSHV6

VDDSHV6

VDDSHV6

www.ti.com

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

Yes 6 PU/PD LVCMOS

Yes 4 PU/PD LVCMOS

Yes 4 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

30

Copyright © 2011–2016, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 31

www.ti.com

ZCE BALL

NUMBER [1]

U2 R2 LCD_DATA1

V1 R3 LCD_DATA2

V2 R4 LCD_DATA3

W2 T1 LCD_DATA4

W3 T2 LCD_DATA5

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

TYPE

BALL RESET

[5]

STATE [6]

(5)

(5)

(5)

(5)

(5)

lcd_data1 0 I/O Z Z 7 VDDSHV6 /

gpmc_a1 1 O

pr1_mii0_txen 2 O

ehrpwm2B 3 O

pr1_pru1_pru_r30_1 5 O

pr1_pru1_pru_r31_1 6 I

gpio2_7 7 I/O

lcd_data2 0 I/O Z Z 7 VDDSHV6 /

gpmc_a2 1 O

pr1_mii0_txd3 2 O

ehrpwm2_tripzone_input 3 I

pr1_pru1_pru_r30_2 5 O

pr1_pru1_pru_r31_2 6 I

gpio2_8 7 I/O

lcd_data3 0 I/O Z Z 7 VDDSHV6 /

gpmc_a3 1 O

pr1_mii0_txd2 2 O

ehrpwm0_synco 3 O

pr1_pru1_pru_r30_3 5 O

pr1_pru1_pru_r31_3 6 I

gpio2_9 7 I/O

lcd_data4 0 I/O Z Z 7 VDDSHV6 /

gpmc_a4 1 O

pr1_mii0_txd1 2 O

eQEP2A_in 3 I

pr1_pru1_pru_r30_4 5 O

pr1_pru1_pru_r31_4 6 I

gpio2_10 7 I/O

lcd_data5 0 I/O Z Z 7 VDDSHV6 /

gpmc_a5 1 O

pr1_mii0_txd0 2 O

eQEP2B_in 3 I

pr1_pru1_pru_r30_5 5 O

pr1_pru1_pru_r31_5 6 I

gpio2_11 7 I/O

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV6

VDDSHV6

VDDSHV6

VDDSHV6

VDDSHV6

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

HYS

[10]

BUFFER

STRENGTH

(mA) [11]

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

Copyright © 2011–2016, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

31

Page 32

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

V3 T3 LCD_DATA6

U3 T4 LCD_DATA7

V4 U1 LCD_DATA8

W4 U2 LCD_DATA9

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

(5)

(5)

(5)

(5)

lcd_data6 0 I/O Z Z 7 VDDSHV6 /

gpmc_a6 1 O

pr1_edio_data_in6 2 I

eQEP2_index 3 I/O

pr1_edio_data_out6 4 O

pr1_pru1_pru_r30_6 5 O

pr1_pru1_pru_r31_6 6 I

gpio2_12 7 I/O

lcd_data7 0 I/O Z Z 7 VDDSHV6 /

gpmc_a7 1 O

pr1_edio_data_in7 2 I

eQEP2_strobe 3 I/O

pr1_edio_data_out7 4 O

pr1_pru1_pru_r30_7 5 O

pr1_pru1_pru_r31_7 6 I

gpio2_13 7 I/O

lcd_data8 0 I/O Z Z 7 VDDSHV6 /

gpmc_a12 1 O

ehrpwm1_tripzone_input 2 I

mcasp0_aclkx 3 I/O

uart5_txd 4 O

pr1_mii0_rxd3 5 I

uart2_ctsn 6 I

gpio2_14 7 I/O

lcd_data9 0 I/O Z Z 7 VDDSHV6 /

gpmc_a13 1 O

ehrpwm0_synco 2 O

mcasp0_fsx 3 I/O

uart5_rxd 4 I

pr1_mii0_rxd2 5 I

uart2_rtsn 6 O

gpio2_15 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV6

VDDSHV6

VDDSHV6

VDDSHV6

www.ti.com

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

32

Copyright © 2011–2016, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 33

www.ti.com

ZCE BALL

NUMBER [1]

U5 U3 LCD_DATA10

V5 U4 LCD_DATA11

V6 V2 LCD_DATA12

U6 V3 LCD_DATA13

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

TYPE

BALL RESET

[5]

STATE [6]

(5)

(5)

(5)

(5)

lcd_data10 0 I/O Z Z 7 VDDSHV6 /

gpmc_a14 1 O

ehrpwm1A 2 O

mcasp0_axr0 3 I/O

pr1_mii0_rxd1 5 I

uart3_ctsn 6 I

gpio2_16 7 I/O

lcd_data11 0 I/O Z Z 7 VDDSHV6 /

gpmc_a15 1 O

ehrpwm1B 2 O

mcasp0_ahclkr 3 I/O

mcasp0_axr2 4 I/O

pr1_mii0_rxd0 5 I

uart3_rtsn 6 O

gpio2_17 7 I/O

lcd_data12 0 I/O Z Z 7 VDDSHV6 /

gpmc_a16 1 O

eQEP1A_in 2 I

mcasp0_aclkr 3 I/O

mcasp0_axr2 4 I/O

pr1_mii0_rxlink 5 I

uart4_ctsn 6 I

gpio0_8 7 I/O

lcd_data13 0 I/O Z Z 7 VDDSHV6 /

gpmc_a17 1 O

eQEP1B_in 2 I

mcasp0_fsr 3 I/O

mcasp0_axr3 4 I/O

pr1_mii0_rxer 5 I

uart4_rtsn 6 O

gpio0_9 7 I/O

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV6

VDDSHV6

VDDSHV6

VDDSHV6

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

HYS

[10]

BUFFER

STRENGTH

(mA) [11]

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

Copyright © 2011–2016, Texas Instruments Incorporated Terminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

33

Page 34

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

W6 V4 LCD_DATA14

V7 T5 LCD_DATA15

T7 R5 LCD_HSYNC

W5 V5 LCD_PCLK lcd_pclk 0 O Z L 7 VDDSHV6 /

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]

(5)

(5)

(7)

lcd_data14 0 I/O Z Z 7 VDDSHV6 /

gpmc_a18 1 O

eQEP1_index 2 I/O

mcasp0_axr1 3 I/O

uart5_rxd 4 I

pr1_mii_mr0_clk 5 I

uart5_ctsn 6 I

gpio0_10 7 I/O

lcd_data15 0 I/O Z Z 7 VDDSHV6 /

gpmc_a19 1 O

eQEP1_strobe 2 I/O

mcasp0_ahclkx 3 I/O

mcasp0_axr3 4 I/O

pr1_mii0_rxdv 5 I

uart5_rtsn 6 O

gpio0_11 7 I/O

lcd_hsync 0 O Z L 7 VDDSHV6 /

gpmc_a9 1 O

gpmc_a2 2 O

pr1_edio_data_in3 3 I

pr1_edio_data_out3 4 O

pr1_pru1_pru_r30_9 5 O

pr1_pru1_pru_r31_9 6 I

gpio2_23 7 I/O

gpmc_a10 1 O

pr1_mii0_crs 2 I

pr1_edio_data_in4 3 I

pr1_edio_data_out4 4 O

pr1_pru1_pru_r30_10 5 O

pr1_pru1_pru_r31_10 6 I

gpio2_24 7 I/O

TYPE

[5]

BALL RESET

STATE [6]

BALL RESET

REL. STATE

(25)

[7]

RESET REL.

MODE [8]

ZCE POWER /

ZCZ POWER [9]

VDDSHV6

VDDSHV6

VDDSHV6

VDDSHV6

www.ti.com

BUFFER

HYS

STRENGTH

[10]

(mA) [11]

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

Yes 6 PU/PD LVCMOS

PULLUP

/DOWN TYPE

[12]

I/O CELL [13]

34

Copyright © 2011–2016, Texas Instruments IncorporatedTerminal Configuration and Functions

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352 AM3351

Page 35

AM3359, AM3358, AM3357, AM3356, AM3354, AM3352, AM3351

www.ti.com

SPRS717J –OCTOBER 2011–REVISED APRIL 2016

Table 4-1. Pin Attributes (ZCE and ZCZ Packages) (continued)

ZCE BALL

NUMBER [1]

U7 U5 LCD_VSYNC

NA B13 MCASP0_FSX mcasp0_fsx 0 I/O L L 7 NA / VDDSHV6 Yes 6 PU/PD LVCMOS

NA B12 MCASP0_ACLKR mcasp0_aclkr 0 I/O L L 7 NA / VDDSHV6 Yes 6 PU/PD LVCMOS

NA C12 MCASP0_AHCLKR mcasp0_ahclkr 0 I/O L L 7 NA / VDDSHV6 Yes 6 PU/PD LVCMOS

ZCZ BALL

NUMBER [1]

PIN NAME [2] SIGNAL NAME [3] MODE [4]