www.ti.com

FEATURES

APPLICATIONS

DESCRIPTION

PTH08T240F

SLTS277 – DECEMBER 2006

10-A, 4.5-V to 14-V INPUT, NON-ISOLATED

POWER MODULE FOR 3-GHz DSP SYSTEMS

• Up to 10-A Output Current • TurboTrans™ Technology

• 4.5-V to 14-V Input Voltage • Designed to meet Ultra-Fast Transient

Requirements for 3-GHz DSP Systems

• Wide-Output Voltage Adjust (0.69 V to 2.0 V)

• 15 mV Output Voltage Deviation

• ± 1.5% Total Output Voltage Variation

(C

O

= 3000 µ F, ∆ I = 5 A)

• Efficiencies up to 92%

• Output Overcurrent Protection

(Nonlatching, Auto-Reset)

• Wireless Infrastructure Base Stations

• Operating Temperature: –40 ° C to 85 ° C

• Safety Agency Approvals:

– UL/IEC/CSA-C22.2 60950-1

• Prebias Startup

• On/Off Inhibit

• Differential Output Voltage Remote Sense

• Adjustable Undervoltage Lockout

• Auto-Track™ Sequencing

• SmartSync Technology

The PTH08T240F is a high-performance 10-A rated, non-isolated power module designed to meet ultra-fast

transient requirements for 3-GHz DSP systems. This module represent the 2nd generation of the popular PTH

series power modules which include a reduced footprint and additional features.

Operating from an input voltage range of 4.5 V to 14 V, the PTH08T240F requires a single resistor to set the

output voltage to any value over the range, 0.69 V to 2.0 V. The output voltage range makes the PTH08T240F

particularly suitable for the 3-GHz DSP's core voltage requirements between 0.9 V and 1.1 V. Additionally, the

wide input voltage range increases design flexibility by supporting operation with 5-V, 8-V, or 12-V intermediate

bus architectures.

The module incorporates a comprehensive list of features. Output over-current and over-temperature shutdown

protects against most load faults. A differential remote sense ensures tight load regulation. An adjustable

under-voltage lockout allows the turn-on voltage threshold to be customized. Auto-Track™sequencing is a

popular feature that greatly simplifies the simultaneous power-up and power-down of multiple modules in a

power system.

The PTH08T240F includes new patent pending technologies, TurboTrans™ and SmartSync. The TurboTrans

feature optimizes the transient response of the regulator while simultaneously reducing the quantity of external

output capacitors required to meet a target voltage deviation specification. TurboTrans allows PTH08T240F to

meet the tight transient voltage tolerances required by 3-GHz DSPs with minimal output capacitance. SmartSync

allows for switching frequency synchronization of multiple modules, thus simplifying EMI noise suppression tasks

and reducing input capacitor RMS current requirements. The module uses double-sided surface mount

construction to provide a low profile and compact footprint. Package options include both through-hole and

surface mount configurations that are lead (Pb) - free and RoHS compatible.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Auto-Track, TMS320 are trademarks of Texas Instruments.

PRODUCT PREVIEW information concerns products in the

Copyright © 2006, Texas Instruments Incorporated

formative or design phase of development. Characteristic data and

other specifications are design goals. Texas Instruments reserves

the right to change or discontinue these products without notice.

www.ti.com

PRODUCT PREVIEW

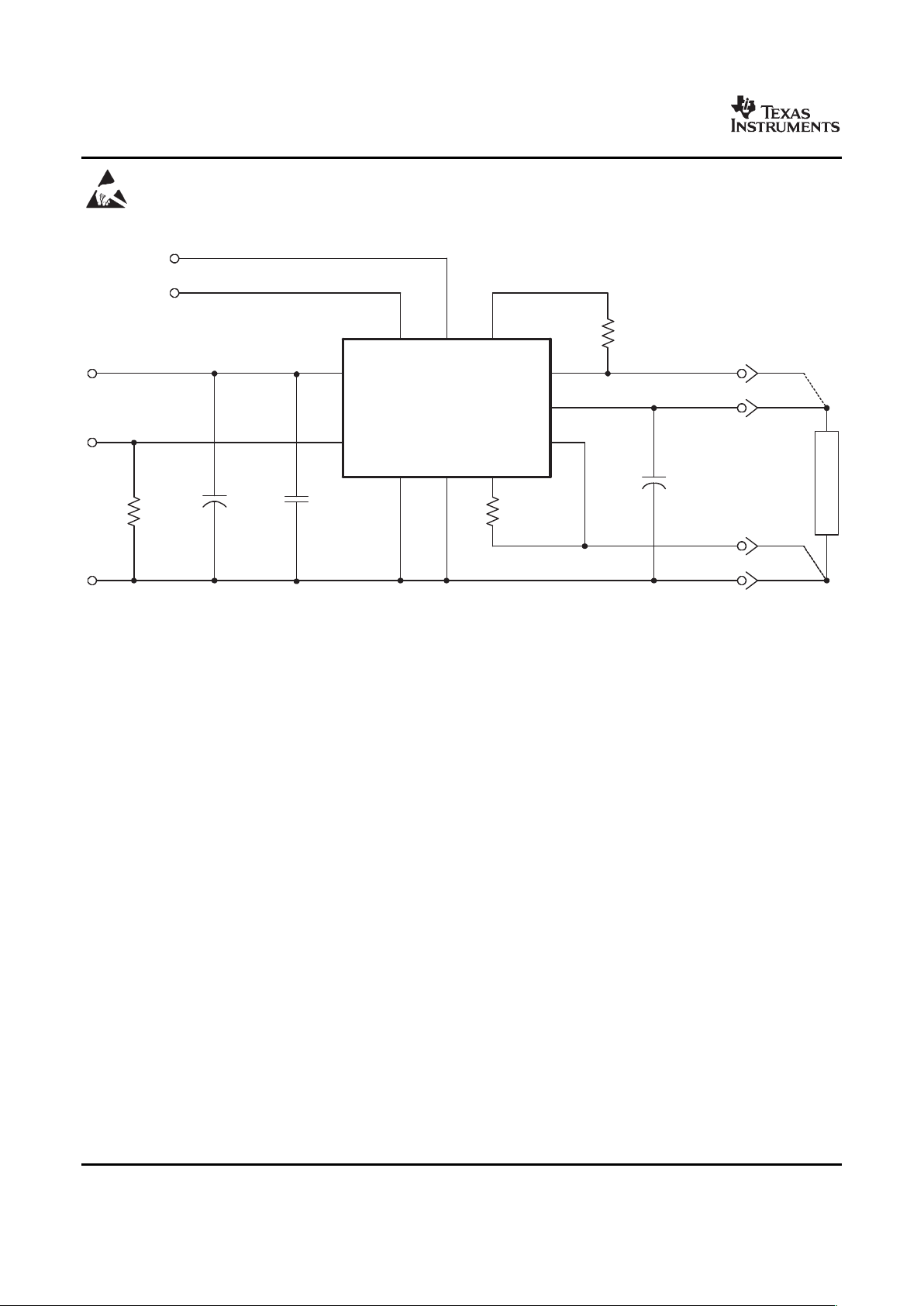

UDG−06005

R

TT

1%

0.05 W

(Optional)

C

O

1000 µF

(Required)

V

O

R

SET

[A]

1%

0.05 W

(Required)

C

I

330 µF

(Required)

R

UVLO

1%

0.05 W

(Optional)

VOAdj

TurboTranst

V

O

V

I

PTH08T240F

5

9

+

8

VI

Track

GND

TT

43

GND

GND

+Sense

6

L

O

A

D

−Sense

GND

+

Inhibit

INH/UVLO

Track

10

7

−Sense

+Sense

SYNC

1

SmartSync

2

11

CI2

22 µF

(Optional)

PTH08T240F

SLTS277 – DECEMBER 2006

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

A. R

SET

required to set the output voltage to a value higher than 0.69 V. See Electrical Characteristics table.

2

Submit Documentation Feedback

www.ti.com

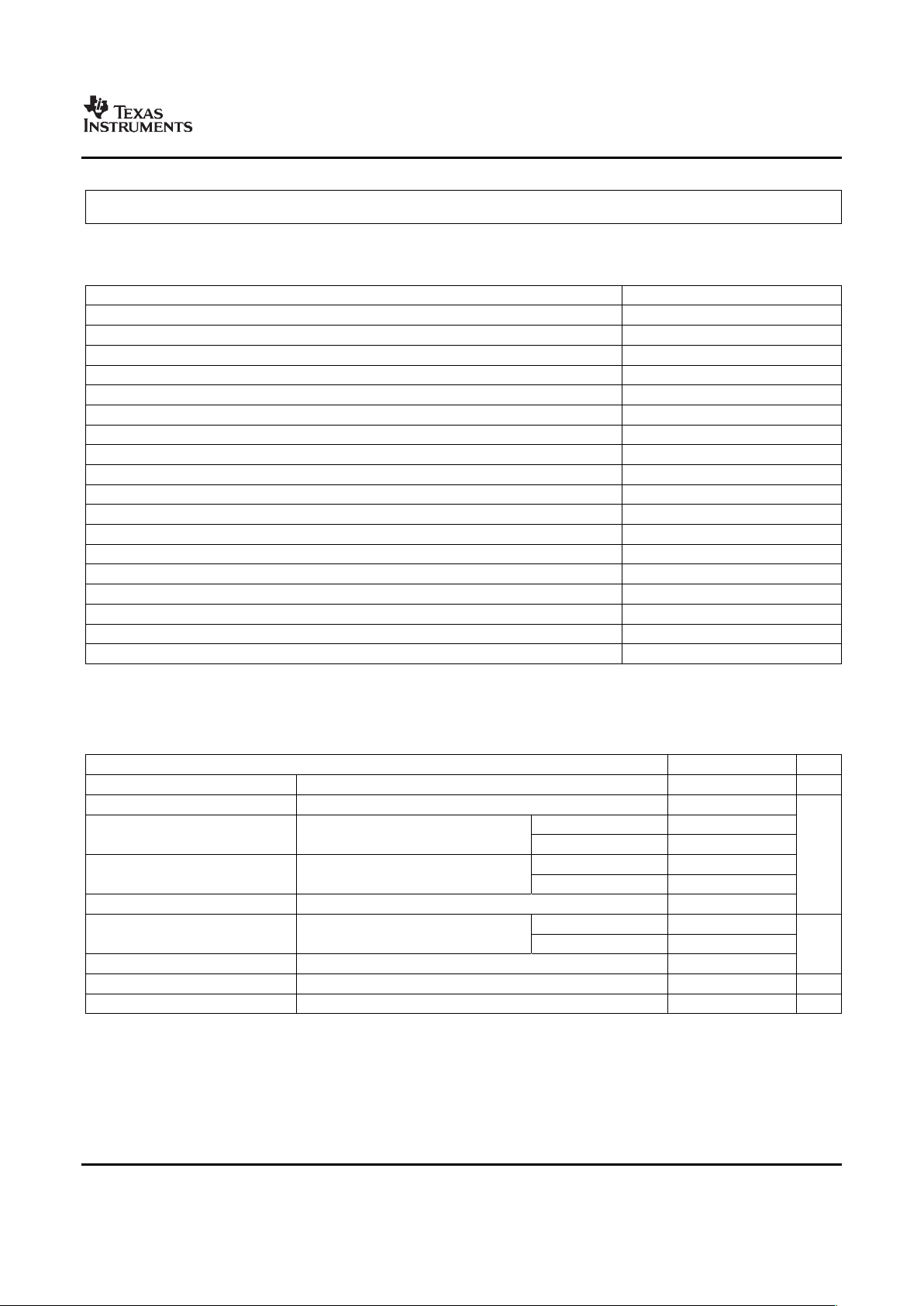

DATASHEET TABLE OF CONTENTS

ENVIRONMENTAL AND ABSOLUTE MAXIMUM RATINGS

PTH08T240F

SLTS277 – DECEMBER 2006

ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum at the end of this datasheet, or see

the TI website at www.ti.com.

DATASHEET SECTION PAGE NUMBER

ENVIRONMENTAL AND ABSOLUTE MAXIMUM RATINGS 3

ELECTRICAL CHARACTERISTICS TABLE 4

TERMINAL FUNCTIONS 6

TYPICAL CHARACTERISTICS (VI= 12V) 7

TYPICAL CHARACTERISTICS (VI= 5V) 8

ADJUSTING THE OUTPUT VOLTAGE 9

INPUT & OUTPUT CAPACITOR RECOMMENDATIONS 11

TURBOTRANS™ INFORMATION 15

UNDERVOLTAGE LOCKOUT (UVLO) 20

SOFT-START POWER-UP 21

OUTPUT INHIBIT 22

OVER-CURRENT PROTECTION 23

OVER-TEMPERATURE PROTECTION 23

REMOTE SENSE 23

SYCHRONIZATION (SMARTSYNC) 24

AUTO-TRACK SEQUENCING 25

PREBIAS START-UP 28

TAPE & REEL AND TRAY DRAWINGS 30

(Voltages are with respect to GND)

UNIT

V

Track

Track pin voltage –0.3 to VI+ 0.3 V

T

A

Operating temperature range Over VIrange –40 to 85

suffix AH 235

Surface temperature of module body or

T

wave

Wave soldering temperature

pins for 5 seconds maximum.

suffix AD 260

° C

suffix AS 235

(1)

Surface temperature of module body or

T

reflow

Solder reflow temperature

pins

suffix AZ 260

(1)

T

stg

Storage temperature –40 to 125

(2)

Mechanical shock Per Mil-STD-883D, Method 2002.3 1 suffix AH & AD 500

msec, 1/2 sine, mounted

suffix AS & AZ 250 G

Mechanical vibration Mil-STD-883D, Method 2007.2 20-2000 Hz 15

Weight 5 grams

Flammability Meets UL94V-O

(1) During reflow of surface mount package version do not elevate peak temperature of the module, pins or internal components above the

stated maximum.

(2) The shipping tray or tape and reel cannot be used to bake parts at temperatures higher than 65°C.

3

Submit Documentation Feedback

www.ti.com

PRODUCT PREVIEW

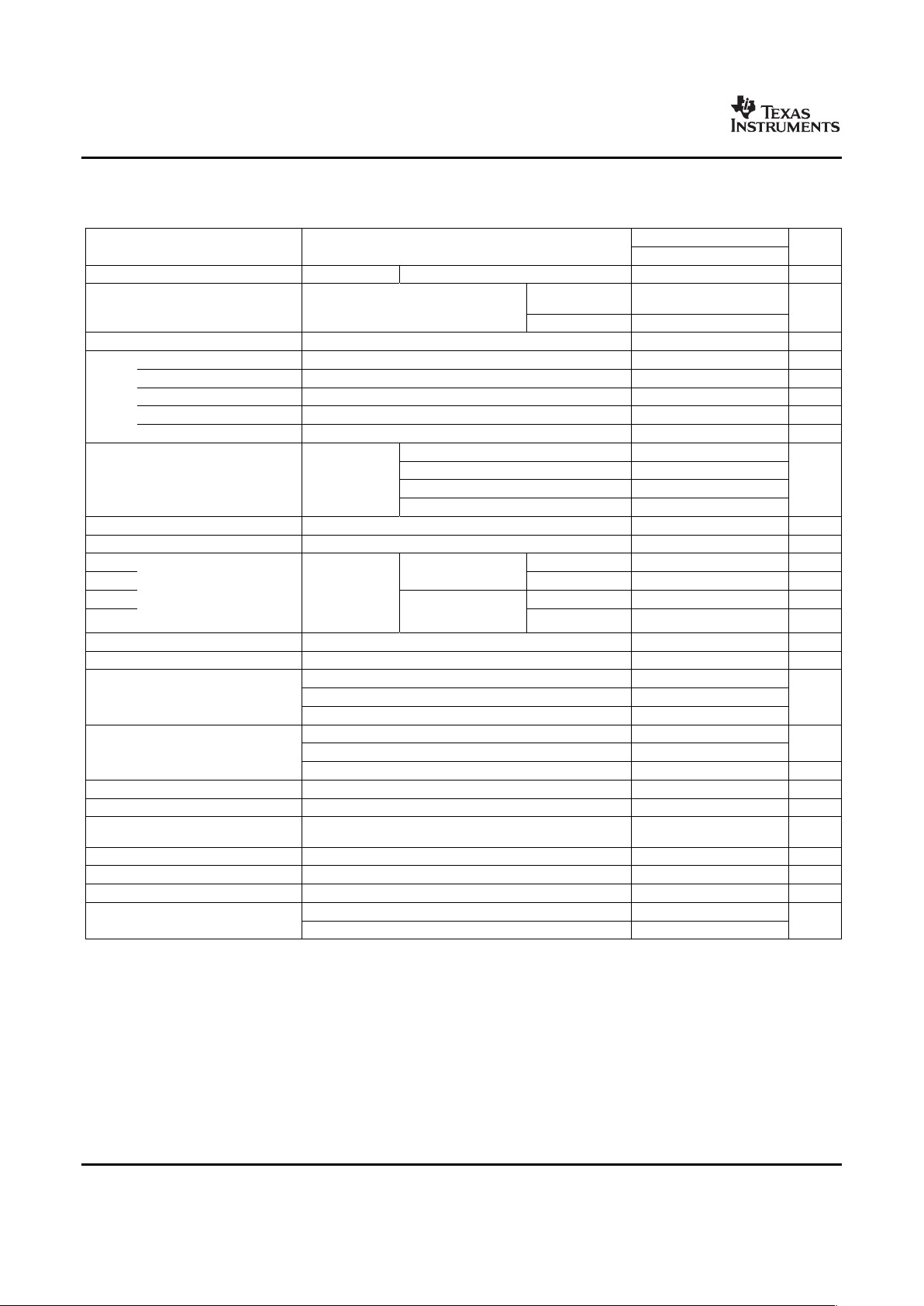

ELECTRICAL CHARACTERISTICS

PTH08T240F

SLTS277 – DECEMBER 2006

PTH08T240F

TA= 25 ° C, VI= 5 V, VO= 1.0 V, CI= 330 µF, CO= 1000 µF, and IO= IOmax (unless otherwise stated)

PARAMETER TEST CONDITIONS PTH08T240F UNIT

MIN TYP MAX

I

O

Output current Over VOrange 25 ° C, natural convection 0 10 A

11 ×

0.69 ≤ VO≤ 1.2 4.5

V

O

(1)

V

I

Input voltage range Over IOrange V

1.2 < VO≤ 2.0 4.5 14

V

OADJ

Output voltage adjust range Over IOrange 0.69 2.0 V

Set-point voltage tolerance ± 0.5 ± 1

(2)

%V

o

Temperature variation –40 ° C < TA< 85 ° C ± 0.3 %V

o

V

O

Line regulaltion Over VIrange ± 3 mV

Load regulation Over IOrange ± 2 mV

Total output variation Includes set-point, line, load, –40 ° C ≤ TA≤ 85 ° C ± 1.5

(2)

%V

o

R

SET

= 4.78 k Ω , VO= 1.8 V 90%

R

SET

= 7.09 k Ω , VO= 1.5 V 88%

η Efficiency IO= 10 A

R

SET

= 12.1 k Ω , VO= 1.2 V 87%

R

SET

= 20.8 k Ω , VO= 1.0 V 85%

VORipple (peak-to-peak) 20-MHz bandwidth 10

(3)

mV

PP

I

LIM

Overcurrent threshold Reset, followed by auto-recovery 20 A

t

tr

Recovery time tbd µs

w/o TurboTrans

CO= 1000 µ F, Type C

∆ V

tr

2.5 A/µs load step VOover/undershoot tbd mV

Transient response 50 to 100% IOmax

t

trTT

w/ TurboTrans Recovery time tbd µs

VO= 2.5 V

CO= tbd µ F, Type C,

mV

∆ V

trTT

VOover/undershoot tbd

RTT = tbd Ω

I

IL

Track input current (pin 10) Pin to GND –130

(4)

µA

dV

track

/dt Track slew rate capability CO≤ CO(max) 1 V/ms

VIincreasing, R

UVLO

= OPEN 4.3 4.45

Adjustable Under-voltage lockout

UVLO

ADJ

VIdecreasing, R

UVLO

= OPEN 4.0 4.2 V

(pin 11)

Hysteresis, R

UVLO

≤ 52.3 k Ω 0.5

Input high voltage (VIH) Open

(5)

V

Inhibit control (pin 11) Input low voltage (VIL) -0.2 0.8

Input low current (IIL), Pin 11 to GND -235 µA

I

in

Input standby current Inhibit (pin 11) to GND, Track (pin 10) open 5 mA

f

s

Switching frequency Over VIand IOranges, SmartSync (pin 1) to GND 260 300 340 kHz

Synchronization (SYNC)

f

SYNC

240 400 kHz

frequency

V

SYNCH

SYNC High-Level Input Voltage 2 5.5 V

V

SYNCL

SYNC Low-Level Input Voltage 0.8 V

t

SYNC

SYNC Minimum Pulse Width 200 nSec

Nonceramic 330

(6)

C

I

External input capacitance µF

Ceramic 22

(6)

(1) The maximum input voltage is duty cycle limited to (VO× 11) or 14 volts, whichever is less. The maximum allowable input voltage is a

function of switching frequency, and may increase or decrease when the SmartSync feature is utilized. Please review the SmartSync

section of the Application Information for further guidance.

(2) The set-point voltage tolerance is affected by the tolerance and stability of R

SET

. The stated limit is unconditionally met if R

SET

has a

tolerance of 1% with 100 ppm/°C or better temperature stability.

(3) For output voltages less than 1.7 V, the ripple may increase (up to 2 × ) when operating at input voltages greater than (VO× 11). See the

SmartSync section of the Application Information for input voltage and frequency limitations.

(4) A low-leakage (<100 nA), open-drain device, such as MOSFET or voltage supervisor IC, is recommended to control pin 10. The

open-circuit voltage is less than 8 Vdc.

(5) This control pin has an internal pull-up. Do not place an external pull-up on this pin. If it is left open-circuit, the module operates when

input power is applied. A small, low-leakage (<100 nA) MOSFET is recommended for control. For additional information, see the related

application information section.

(6) A 330 µF electrolytic input capacitor is required for proper operation. The electrolytic capacitor must be rated for a minimum of 500 mA

rms of ripple current.

4

Submit Documentation Feedback

www.ti.com

PTH08T240F

SLTS277 – DECEMBER 2006

ELECTRICAL CHARACTERISTICS (continued)

PTH08T240F

TA= 25 ° C, VI= 5 V, VO= 1.0 V, CI= 330 µF, CO= 1000 µF, and IO= IOmax (unless otherwise stated)

PARAMETER TEST CONDITIONS PTH08T240F UNIT

MIN TYP MAX

Nonceramic 1000

(7)

5000

(8)

Capacitance Value µF

w/o TurboTrans Ceramic 500

Equivalent series resistance (non-ceramic) 7 m Ω

C

O

External output capacitance

see table

Capacitance Value µF

(7) (9)

w/ TurboTrans

Capacitance × ESR product (CO× ESR) 1000 10000

(9)

µF × m Ω

Per Telcordia SR-332, 50% stress,

MTBF Reliability 6.1

106Hr

TA= 40 ° C, ground benign

(7) 1000 µF of external output capacitance is required for basic operation. The minimum output capacitance requirement increases when

TurboTrans™ (TT) technology is utilized. See related Application Information for more guidance.

(8) This is the calculated maximum disregarding TurboTrans™ technology. When the TurboTrans™ feature is utilized, the minimum output

capacitance must be increased.

(9) When using TurboTrans™ technology, a minimum value of output capacitance is required for proper operation. Additionally, low ESR

capacitors are required for proper operation. See the application notes for further guidance.

5

Submit Documentation Feedback

Loading...

Loading...