Datasheet MSP50P34DWI2D, MSP50P34N16I2D, MSP50P34DWE1A, MSP50P34N16E1A Datasheet (Texas Instruments)

MSP50C32, MSP50C33, MSP50C34

MSP50P34, MSP50C37, MSP50P37

MIXED-SIGNAL PROCESSORS

SPSS019A – MAY 1997 – REVISED OCT OBER 1998

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Dual Programmable LPC-12 Speech

Synthesizers

D

Simultaneous LPC and PCM Waveforms

D

8-Bit Microprocessor with 61 instructions

D

32 Twelve-Bit Words and 224 Bytes of RAM

D

3.3V to 6.5V CMOS Technology for Low

Power Dissipation

D

Direct Speaker Drive Capability

D

Mask Selectable Internal or External Clock

D

Internal Clock Generator that Requires No

External Components

D

Two Software-Selectable Clock Speeds

D

10-kHz or 8-kHz Speech Sample Rate

description

The MSP50x3x family uses a revolutionary architecture to combine an 8-bit microprocessor, two speech

synthesizers, ROM, RAM, and I/O in a low-cost single-chip system. The architecture uses the same arithmetic

logic unit (ALU) for the two synthesizers and the microprocessor, thus reducing chip area and cost and enabling

the microprocessor to do a multiply operation in 0.8 µs. The MSP50x3x family features two independent

channels of linear predictive coding (LPC), which synthesize high-quality speech at a low data rate. Pulse-code

modulation (PCM) can produce music or sound effects. LPC and PCM can be added together to produce a

composite result. For more information, see the MSP50x3x User’s Guide (literature number SPSU006).

T able 1. MSP50x3x Family

DEVICE AMOUNT OF ROM/PROM FEATURES

MSP50C32 16K bytes mask ROM 9/10 I/O lines

MSP50C33 32K bytes mask ROM 9/10 I/O lines

MSP50C34 64K bytes mask ROM 9/10 I/O lines, 24 I/O lines in die form

MSP50P34 64K bytes PROM 9/10 I/O lines

MSP50C37 16K bytes mask ROM 18 I/O lines, A/D converter/analog amplifier

MSP50P37 16K bytes PROM 18 I/O lines, A/D converter/analog amplifier

Copyright 1998, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

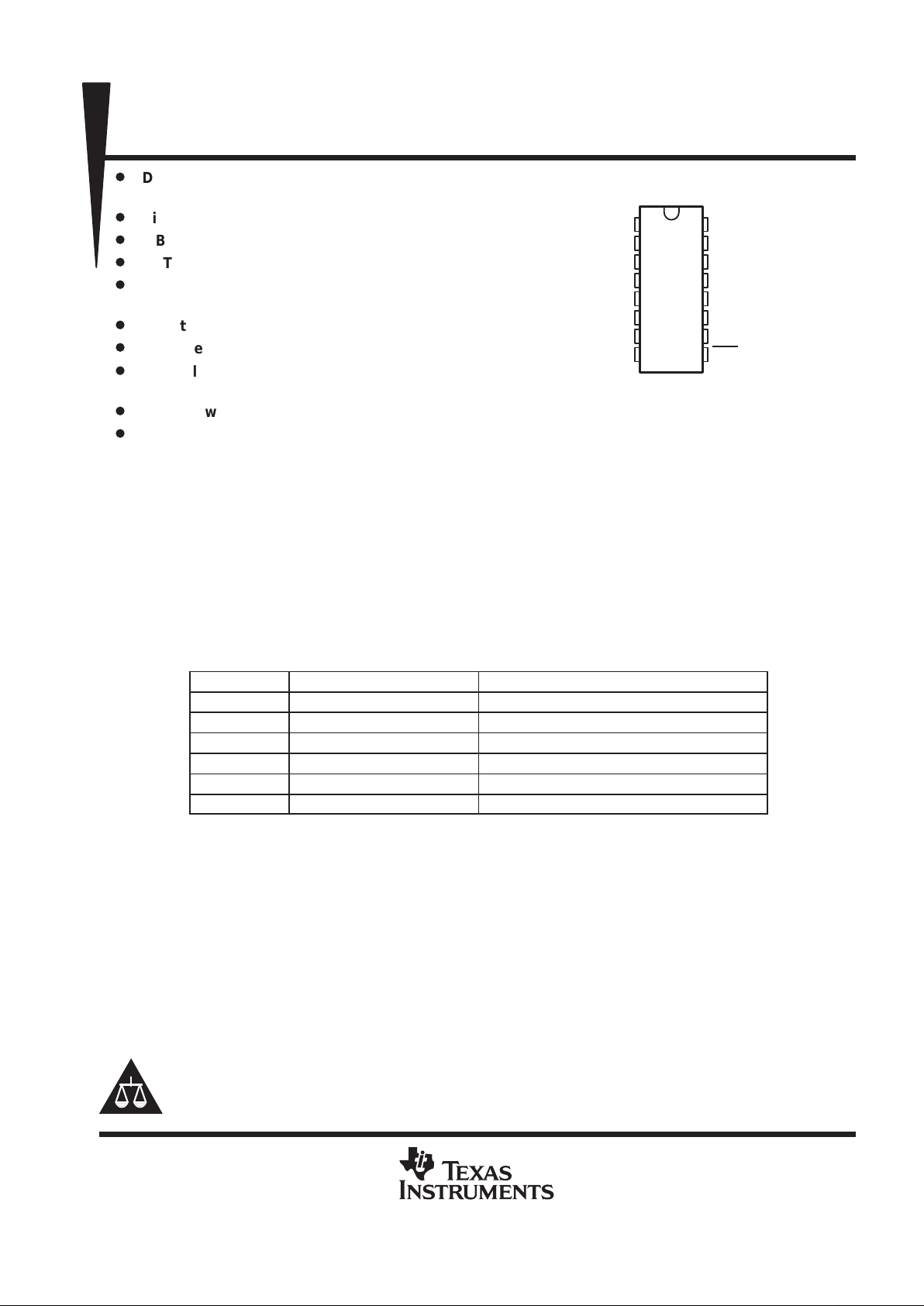

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

N PACKAGE

(TOP VIEW)

OSC IN

PA6

PA5

PA4

PA3

PA2

PA1

PB1/OSC OUT

PA7

PB0

PA0

DAC+

DAC–

V

DD

V

SS

INIT

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MSP50C32, MSP50C33, MSP50C34

MSP50P34, MSP50C37, MSP50P37

MIXED-SIGNAL PROCESSORS

SPSS019A – MAY 1997 – REVISED OCT OBER 1998

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range

†

Supply voltage range, V

DD

(see Note 1) –0.3 V to 8 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply current, IDD or ISS (see Note 2) 100 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, VI (see Note 1) –0.3 V to VDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, VO (see Note 1) –0.3 V to VDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –30°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltages are with respect to ground.

2. The total supply current includes the current out of all the I/O terminals and DAC terminals as well as the operating current of the

device.

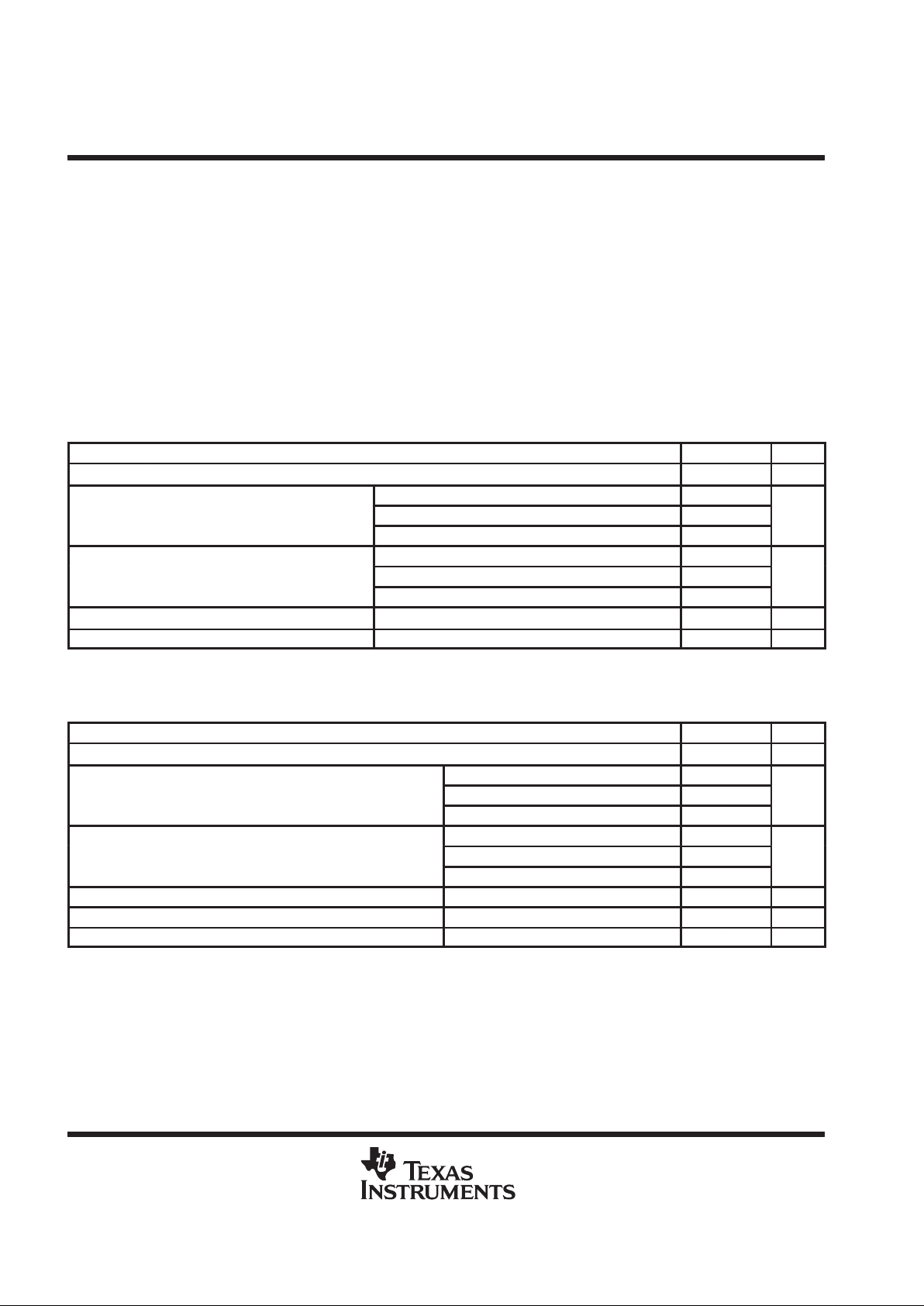

recommended operating conditions (MSP50C32, MSP50C33, MSP50x34)

MAX MAX UNIT

V

DD

Supply voltage

†

3.3 6.5 V

VDD = 3.3 V 2.5 3.3

V

IH

High-level input voltage

VDD = 5 V

3.8 5

V

VDD = 6 V 4.5 6

VDD = 3.3 V 0 0.65

V

IL

Low-level input voltage

VDD = 5 V

0 1

V

VDD = 6 V 0 1.3

T

A

Operating free-air temperature Device functionality 0 70 °C

Rspeaker Minimum speaker impedance Direct speaker drive using 2 pin push-pull DAC option 32 Ω

†

Unless otherwise noted, all voltages are with respect to VSS.

recommended operating conditions (MSP50x37)

MIN MAX UNIT

V

DD

Supply voltage

†

4 6.5 V

VDD = 4 V 3 4

V

IH

High-level input voltage

VDD = 5 V

3.8 5

V

VDD = 6 V 4.5 6

VDD = 4 V 0 1

V

IL

Low-level input voltage

VDD = 5 V

0 1.2

V

VDD = 6 V 0 1.5

MUX input voltage Reference voltage = 6.5 V 0 6.5 V

T

A

Operating free-air temperature Device functionality –10 70 °C

Rspeaker Minimum speaker impedance Direct speaker drive using power amp 8 Ω

MSP50C32, MSP50C33, MSP50C34

MSP50P34, MSP50C37, MSP50P37

MIXED-SIGNAL PROCESSORS

SPSS019A – MAY 1997 – REVISED OCT OBER 1998

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

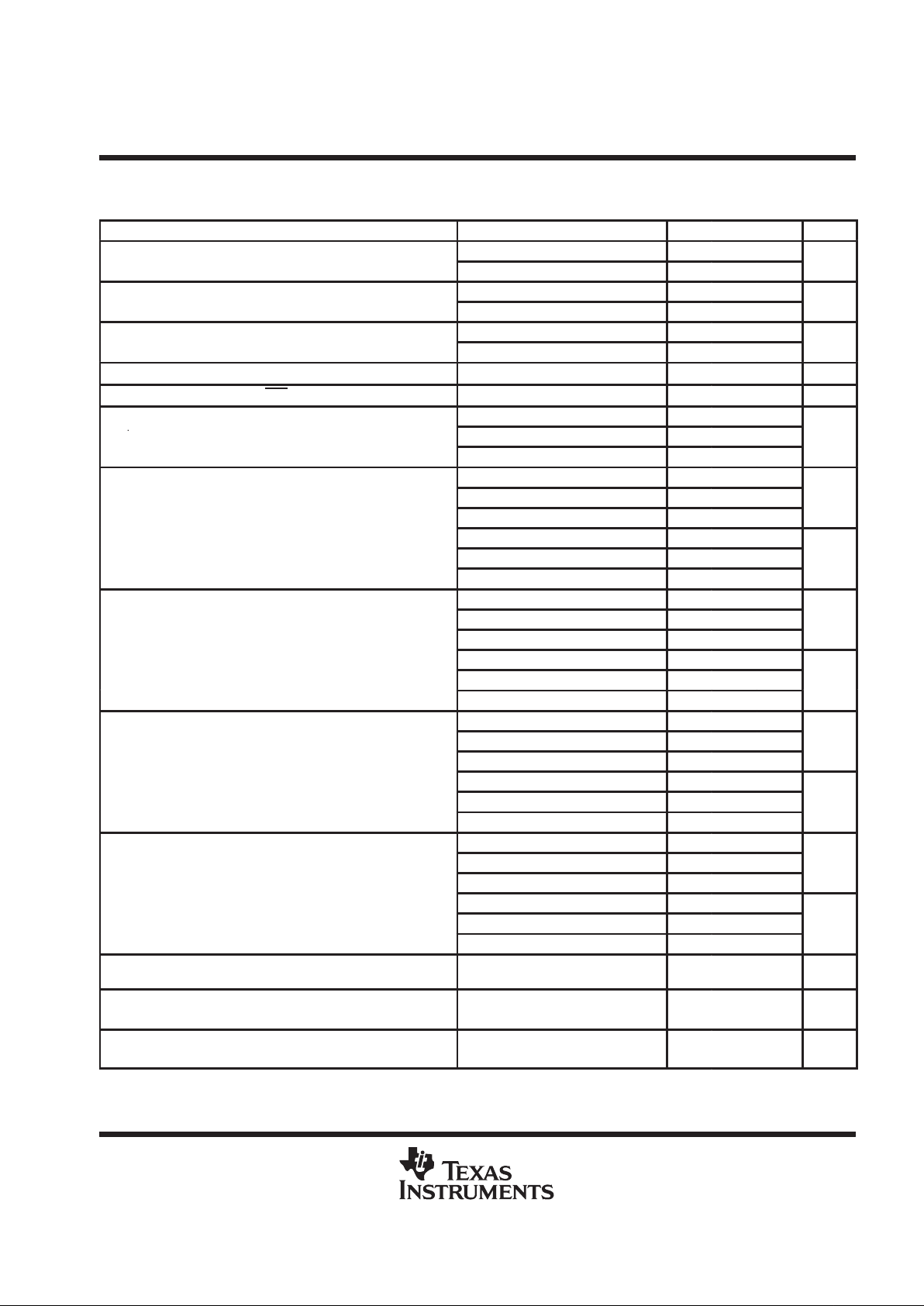

MSP50C32, MSP50C33, MSP50x34 electrical characteristics over recommended ranges of supply

voltage and operating free-air temperature (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

VDD = 3.5 V 2

VT+Positive-going threshold voltage (INIT)

VDD = 6 V 3.4

V

VDD = 3.5 V 1.6

VT–Negative-going threshold voltage (INIT)

VDD = 6 V 2.3

V

VDD = 3.5 V 0.4

V

hys

Hysteresis (V

T+

–

VT–) (INIT)

VDD = 6 V 1.1

V

I

Ikg

Input leakage current (except for OSC IN)

2 µA

I

standby

Standby current (INIT low, SETOFF)

10 µA

VDD = 3.3 V, VOH = 2.75 V 2.1

I

DD

†

Supply current

VDD = 5 V,

VOH = 4.5 V 3.1

mA

DD

VDD = 6 V, VOH = 5.5 V 4.5

VDD = 3.3 V, VOH = 2.75 V –4 –12

VDD = 5 V, VOH = 4.5 V –5 –14

mA

p

VDD = 6 V, VOH = 5.5 V –6 –15

IOHHigh-level output current (PA, PB)

VDD = 3.3 V, VOH = 2.2 V –8 –20

VDD = 5 V, VOH = 3.33 V –14 –40

mA

VDD = 6 V, VOH = 4 V –20 –51

VDD = 3.3 V, VOL = 0.5 V 5 9

VDD = 5 V, VOL = 0.5 V 5 9

mA

p

VDD = 6 V, VOL = 0.5 V 5 9

IOLLow-level output current (PA, PB)

VDD = 3.3 V, VOL = 1.1 V 10 19

VDD = 5 V, VOL = 1.67 V 20 29

mA

VDD = 6 V, VOL = 2 V 25 35

VDD = 3.3 V, VOH = 2.75 V –30 –50

VDD = 5 V, VOH = 4.5 V –35 –60

mA

p

VDD = 6 V, VOH = 5.5 V –40 –65

IOHHigh-level output current (D/A)

VDD = 3.3 V, VOH = 2.3 V –50 –90

VDD = 5 V, VOH = 4 V –90 –140

mA

VDD = 6 V, VOH = 5 V –100 –150

VDD = 3.3 V, VOL = 0.5 V 50 80

VDD = 5 V, VOL = 0.5 V 70 90

mA

p

VDD = 6 V, VOL = 0.5 V 80 110

IOLLow-level output current (D/A)

VDD = 3.3 V, VOL = 1 V 100 140

VDD = 5 V, VOL = 1 V 140

mA

VDD = 6 V, VOL = 1 V 150

Pullup resistance

Resistors selected by software and

connected between terminal and V

DD

10 20 50 kΩ

VDD = 5 V, TA = 25°C,

f

osc(low)

Oscill

ator frequency

‡

Target frequency = 15.36 MHz

14.89

15.36

15.86

MH

z

VDD = 5 V, TA = 25°C,

f

osc(high)

Oscill

ator frequency

‡

Target frequency = 19.2 MHz

18.62

19.2

19.7

MH

z

†

Operating current assumes all inputs are tied to either VSS or VDD with no input currents due to programmed pullup resistors. The DAC output

and other outputs are open circuited.

‡

The frequency of the internal clock has a temperature coefficient of approximately –0.2 %/°C and a VDD coefficient of approximately ±1%/V.

MSP50C32, MSP50C33, MSP50C34

MSP50P34, MSP50C37, MSP50P37

MIXED-SIGNAL PROCESSORS

SPSS019A – MAY 1997 – REVISED OCT OBER 1998

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MSP50x37 electrical characteristics over recommended ranges of supply voltage and operating

free-air temperature (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

VDD = 4.5 V 2.7

VT+Positive-going threshold voltage (INIT)

VDD = 6 V 3.65

V

VDD = 4.5 V 2.3

VT–Negative-going threshold voltage (INIT)

VDD = 6 V 3.15

V

VDD = 4.5 V 0.4

V

hys

Hysteresis (V

T+

–

VT–) (INIT)

VDD = 6 V 0.5

V

I

Ikg

Input leakage current (except for OSC IN)

1 µA

I

standby

Standby current (INIT low, SETOFF)

10 µA

pp

Power amplifier is on 25

I

DD

†

Supply current

Power amplifier is off 10

mA

VDD = 4 V, VOH = 3.5 V –4 –6

VDD = 5 V, VOH = 4.5 V –5 –7.5 mA

p

VDD = 6 V, VOH = 5.5 V –6 –9.2

IOHHigh-level output current (PA, PB, PD)

VDD = 4 V, VOH = 2.65 V –8 –13

VDD = 5 V, VOH = 3.33 V –14 –20 mA

VDD = 6 V, VOH = 4 V –20 –29

VDD = 4 V, VOL = 0.5 V 20 28

VDD = 5 V, VOL = 0.5 V 26 34 mA

p

VDD = 6 V, VOL = 0.5 V 30 39

IOLLow-level output current (PA4

–

PA7)

VDD = 4 V, VOL = 1.33 V 40 54

VDD = 5 V, VOL = 1.67 V 60 74 mA

VDD = 6 V, VOL = 2 V 82 103

VDD = 4 V, VOL = 0.5 V 10 17

VDD = 5 V, VOL = 0.5 V 13 20 mA

p

VDD = 6 V, VOL = 0.5 V 15 25

IOLLow-level output current (PA0

–

PA3, PB, PD))

VDD = 4 V, VOL = 1.33 V 20 32

VDD = 5 V, VOL = 1.67 V 30 52 mA

VDD = 6 V, VOL = 2 V 41 71

Pullup resistance

Resistors selected by software and

connected between terminal and V

DD

15 30 60 kΩ

VDD = 5 V, TA = 25°C,

f

osc(low)

Oscill

ator frequency

‡

Target frequency = 15.36 MHz

14.89

15.36

15.82

MH

z

VDD = 5 V, TA = 25°C,

f

osc(high)

Oscill

ator frequency

‡

Target frequency = 19.2 MHz

18.62

19.2

19.77

MH

z

†

Operating current assumes all inputs are tied to either VSS or VDD with no input currents due to programmed pullup resistors. The DAC output

and other outputs are open circuited.

‡

The frequency of the internal clock has a temperature coefficient of approximately –0.2 %/°C and a VDD coefficient of approximately ±1.4%/V.

MSP50C32, MSP50C33, MSP50C34

MSP50P34, MSP50C37, MSP50P37

MIXED-SIGNAL PROCESSORS

SPSS019A – MAY 1997 – REVISED OCT OBER 1998

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MSP50x37 Power Amplifier Electrical Characteristics Over Recommended Operating

Free-Air Temperature Range

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Differential output power VDD = 5 V, f = 1 kHz, RL = 8 Ω 500 mW

Bandwidth 3.5 kHz

MSP50x37 ADC Electrical Characteristics, VCC = 5 V, TA = 25°C

PARAMETER MIN TYP MAX UNIT

Linearity

±0.5 LSB

Offset

±1.5 LSB

Full scale error ±1.5 LSB

Conversion time 40 Instructions

switching characteristics (MSP50C32, MSP50C33, MSP50x34)

PARAMETER TEST CONDITIONS MIN NOM MAX UNIT

t

r

Rise time, PA, PB, D/A VDD = 3.3 V, CL = 100 pF, 10% to 90%

50 ns

t

f

Fall time, PA, PB, D/A VDD = 3.3 V, CL = 100 pF, 10% to 90%

50 ns

switching characteristics (MSP50x37)

PARAMETER TEST CONDITIONS MIN NOM MAX UNIT

t

r

Rise time, PA, PB, PD VDD = 4 V, CL = 100 pF, 10% to 90%

22 ns

t

f

Fall time, PA, PB, PD VDD = 4 V, CL = 100 pF, 10% to 90%

10 ns

MSP50C32, MSP50C33, MSP50C34

MSP50P34, MSP50C37, MSP50P37

MIXED-SIGNAL PROCESSORS

SPSS019A – MAY 1997 – REVISED OCT OBER 1998

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

timing requirements

MIN MAX UNIT

Initialization

t

INIT

INIT pulsed low while the MSP50x3x has power applied (see Figure 1)

1 µs

Wakeup

t

su(wakeup)

Setup time prior to wakeup terminal negative transition (see Figure 2)

1 µs

External Interrupt

f

clock

= 15.36 MHz 1

t

su(interrupt)

Set

up time prior to B1 terminal negative trans

iti

on (see Figure

3)

f

clock

= 19.2 MHz 1.5

µ

s

Writing (Slave Mode)

t

su1(B1)

Setup time, B1 low before B0 goes low (see Figure 4) 20 ns

t

su(d)

Setup time, data valid before B0 goes high (see Figure 4) 100 ns

t

h1(B1)

Hold time, B1 low after B0 goes high (see Figure 4) 20 ns

t

h(d)

Hold time, data valid after B0 goes high (see Figure 4) 30 ns

t

w

Pulse duration, B0 low (see Figure 4) 100 ns

t

r

Rise time, B0 (see Figure 4) 50 ns

t

f

Fall time, B0 (see Figure 4) 50 ns

Reading (Slave Mode)

t

su2(B1)

Setup time, B1 before B0 goes low (see Figure 5) 20 ns

t

h2(B1)

Hold time, B1 after B0 goes high (see Figure 5) 20 ns

t

dis

Output disable time, data valid after B0 goes high (see Figure 5) 0 30 ns

t

w

Pulse duration, B0 low (see Figure 5) 100 ns

t

r

Rise time, B0 (see Figure 5) 50 ns

t

f

Fall time, B0 (see Figure 5) 50 ns

t

d

Delay time for B0 low to data valid (see Figure 5) 50 ns

PARAMETER MEASUREMENT INFORMATION

t

INIT

INIT

Figure 1. Initialization Timing Diagram

t

su(wakeup)

Wakeup

Figure 2. Wakeup Terminal Setup Timing Diagram

MSP50C32, MSP50C33, MSP50C34

MSP50P34, MSP50C37, MSP50P37

MIXED-SIGNAL PROCESSORS

SPSS019A – MAY 1997 – REVISED OCT OBER 1998

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

t

su(interrupt)

B1

Figure 3. External Interrupt Terminal Setup Timing Diagram

Data Valid

B1

B0

PA

t

su1(B1)

t

w

t

h1(B1)

t

f

t

su(d)

t

r

t

h(d)

Figure 4. Write Timing Diagram (Slave Mode)

Data Valid

B1

B0

PA

t

su2(B1)

t

w

t

h2(B1)

t

f

t

r

t

dis

t

d

Figure 5. Read Timing Diagram (Slave Mode)

MSP50C32, MSP50C33, MSP50C34

MSP50P34, MSP50C37, MSP50P37

MIXED-SIGNAL PROCESSORS

SPSS019A – MAY 1997 – REVISED OCT OBER 1998

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

MECHANICAL DATA

N (R-PDIP-T**) PLASTIC DUAL-IN-LINE PACKAGE

20

0.975

(24,77)

0.940

(23,88)

18

0.920

0.850

14

0.775

0.745

(19,69)

(18,92)

16

0.775

(19,69)

(18,92)

0.745

A MIN

DIM

A MAX

PINS **

0.310 (7,87)

0.290 (7,37)

(23.37)

(21.59)

Seating Plane

0.010 (0,25) NOM

14/18 PIN ONL Y

4040049/C 08/95

9

8

0.070 (1,78) MAX

A

0.035 (0,89) MAX

0.020 (0,51) MIN

16

1

0.015 (0,38)

0.021 (0,53)

0.200 (5,08) MAX

0.125 (3,18) MIN

0.240 (6,10)

0.260 (6,60)

M

0.010 (0,25)

0.100 (2,54)

0°–15°

16 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001 (20 pin package is shorter then MS-001.)

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCT OR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERSTOOD T O

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Loading...

Loading...