Texas Instruments CDC857-3DGG, CDC857-2DGGR, CDC857-2DGG, CDC857-3DGGR Datasheet

CDC857-2, CDC857-3

2.5-/3.3-V PHASE-LOCK LOOP CLOCK DRIVERS

SCAS627A – SEPTEMBER 1999 – DECEMBER 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Phase-Lock Loop Clock Distribution for

Double Data Rate Synchronous DRAM

Applications

D

Distributes One Differential Clock Input to

Ten Differential Outputs

D

External Feedback Pins (FBIN, FBIN) Are

Used to Synchronize the Outputs to the

Clock Input

D

Operates at VCC = 2.5 V and AVCC = 3.3 V

D

Packaged in Plastic 48-Pin (DGG) Thin

Shrink Small-Outline Package (TSSOP)

D

Spread Spectrum Clocking Tracking

Capability to Reduce EMI

description

The CDC857-2 and CDC857-3 are high-performance, low-skew, low-jitter, phase-lock loop

(PLL) clock driver. They use a PLL to precisely

align, in both frequency and phase, the feedback

(FBOUT) output to the clock (CLK) input signal.

The CDC857-3 operates at 3.3 V (PLL) and 2.5 V

(output buffer). The CDC857-2 operates at

2.5 V (PLL and output buffer).

One bank of ten inverting and noninverting

outputs provide ten low-skew, low-jitter copies of

CLK. Output signal duty cycles are adjusted to

50%, independent of the duty cycle at CLK.

All outputs can be enabled or disabled via a single output enable input. When the G input is high, the outputs

switch in phase and frequency with CLK; when the G input is low, the outputs are disabled to high impedance

state (3-state).

Unlike many products containing PLLs, the CDC857 does not require external RC networks. The loop filter for

the PLL is included on-chip, minimizing component count, board space, and cost.

Because it is based on PLL circuity, the CDC857 requires a stabilization time to achieve phase lock of the

feedback signal to the reference signal. This stabilization time is required following power up and application

of a fixed-frequency, fixed-phase signal at CLK, as well as following any changes to the PLL reference or

feedback signals. The PLL can be bypassed for test purposes by strapping A V

CC

to ground. If A VCC is at GND

and VCC = ON, 2 falling edges on G cause the PLL to run with FBOUT being enabled and all other outputs being

disabled, after A VCC ramps up to its specified VCC value, with G being kept low. The CDC857 is characterized

for operation from 0°C to 85°C.

Copyright 1999, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

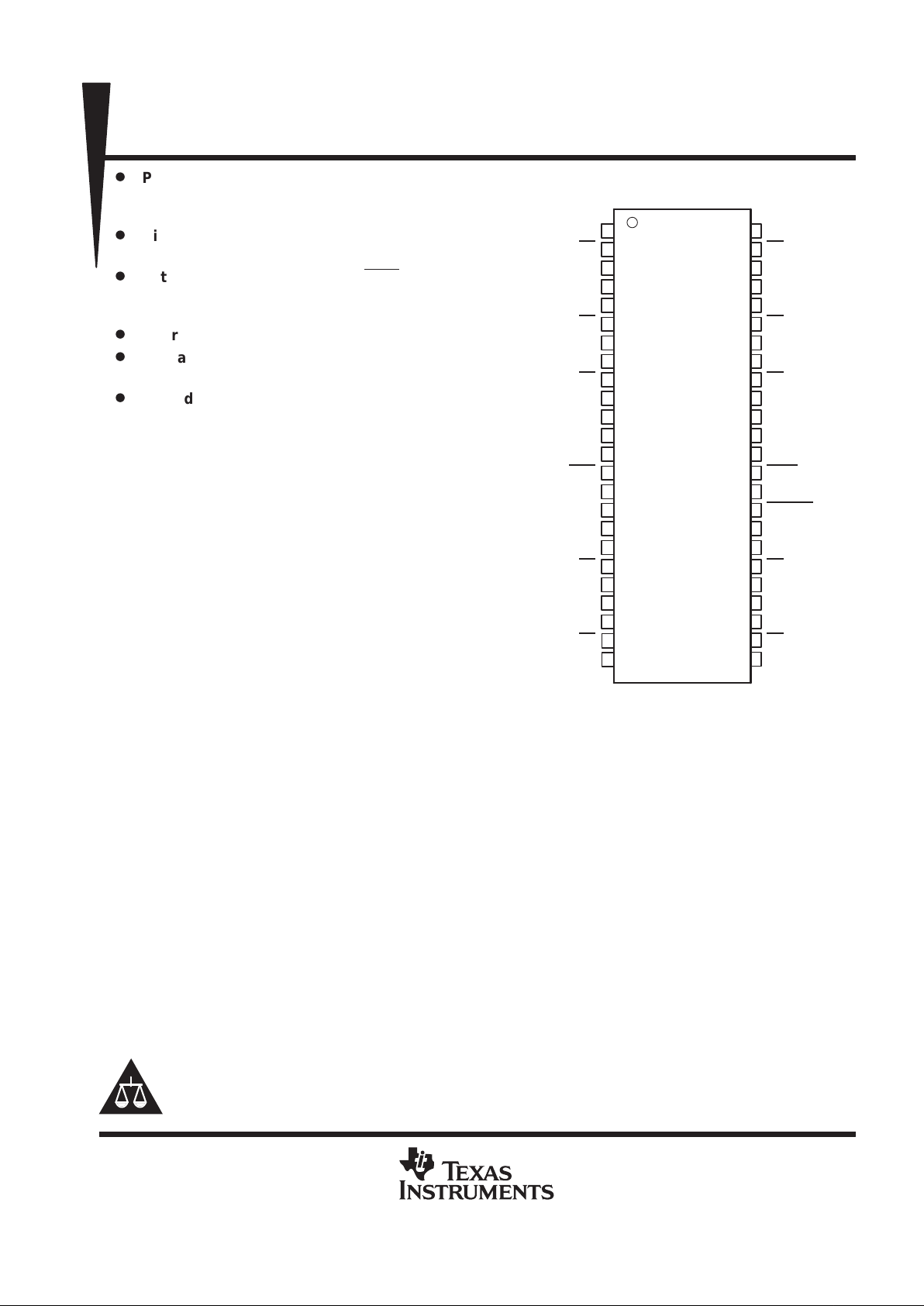

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

GND

Y0

Y0

V

CC

Y1

Y1

GND

GND

Y2

Y2

V

CC

V

CC

CLK

CLK

V

CC

AV

CC

AGND

GND

Y3

Y3

V

CC

Y4

Y4

GND

GND

Y5

Y5

V

CC

Y6

Y6

GND

GND

Y7

Y7

V

CC

G

FBIN

FBIN

V

CC

FBOUT

FBOUT

GND

Y8

Y8

V

CC

Y9

Y9

GND

DGG PACKAGE

(TOP VIEW)

CDC857-2, CDC857-3

2.5-/3.3-V PHASE-LOCK LOOP CLOCK DRIVERS

SCAS627A – SEPTEMBER 1999 – DECEMBER 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

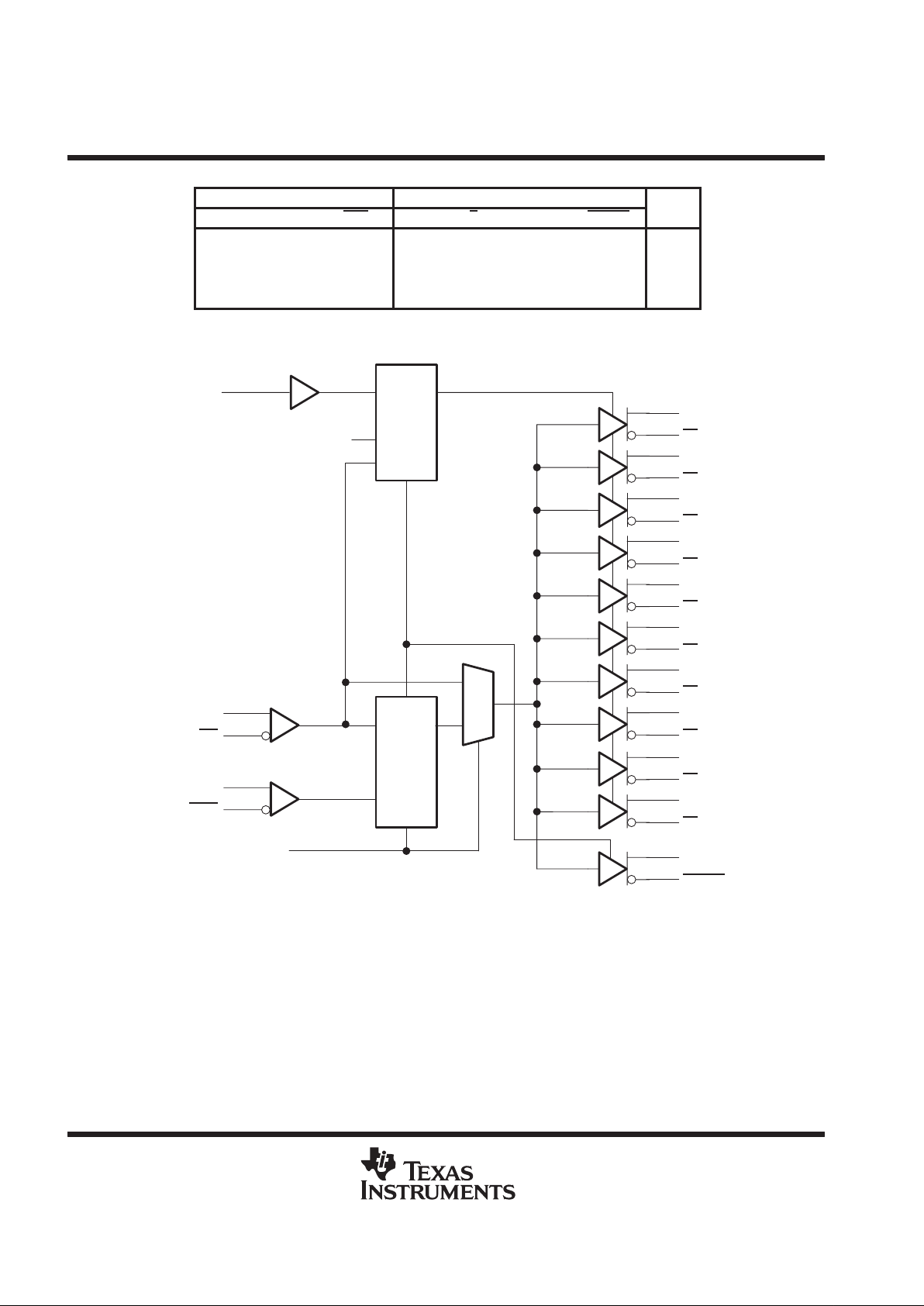

FUNCTION TABLE

INPUTS

OUTPUTS

G CLK CLK Y Y FBOUT FBOUT

PLL

L X X Z Z Z Z OFF

H LHLH L H RUN

H HLHL H L RUN

H < 20 MHz < 20 MHz Z Z Z Z OFF

logic symbol

Y0

Y0

Y1

Y1

Y8

Y8

Y9

Y9

FBOUT

FBOUT

Y2

Y2

Y3

Y3

Y4

Y4

Y5

Y5

Y6

Y6

Y7

Y7

Clk

Clk

FBIN

FBIN

PLL

G

AVCC = 3.3 V

Test

Mode

Logic

AV

CC

NOTE A: All outputs are connected to VCC = 2.5 V.

CDC857-2, CDC857-3

2.5-/3.3-V PHASE-LOCK LOOP CLOCK DRIVERS

SCAS627A – SEPTEMBER 1999 – DECEMBER 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

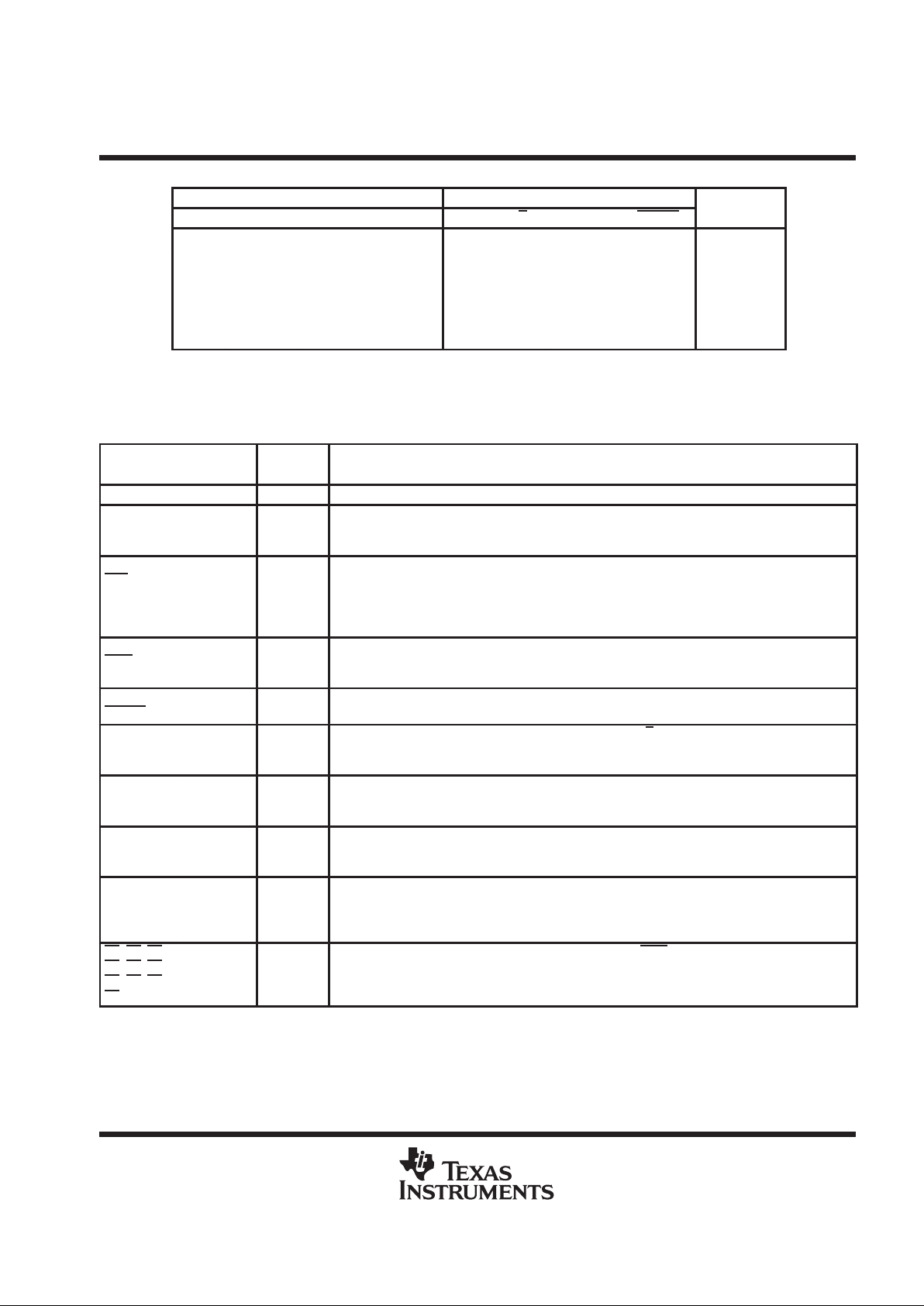

SPECIAL TEST MODES

INPUTS

OUTPUTS

V

CC

AV

CC

G CLK

†

Y Y FBOUT FBOUT

COMMENTS

ON 0 V L L Z Z Z Z Clock Mode

ON 0 V L H Z Z Z Z Clock Mode

ON 0 V H L L H L H Clock Mode

ON 0 V H H H L H L Clock Mode

ON UP

‡

↓

§

LZZ L H PLL Mode

ON UP

‡

↓

§

H Z Z H L PLL Mode

†

Only one signal shown for this differential input.

‡

AVCC ramped up after two (2) high-to-low transitions on G input & G being low.

§

At least two (2) high-to-low transitions during AVCC = 0.

Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

AGND 17 Ground Analog ground. AGND provides the ground reference for the analog circuitry .

AV

CC

16 Power Analog power supply . AVCC provides the power reference for the analog circuitry. In addition, A V

CC

can be used to bypass the PLL for test purposes. When AVCC is strapped to ground, PLL is bypassed

and CLK is buffered directly to the device outputs. During disable (G = 0), the PLL is powered down.

CLK

CLK

13

14

I Clock input, CLK provides the clock signal to be distributed by the CDC857 clock driver. CLK is used

to provide the reference signal to the integrated PLL that generates the clock output signals. CLK

must have a fixed frequency and fixed phase for the PLL to obtain phase lock. Once the circuit is

powered up and a valid CLK signal is applied, a stabilization time is required for the PLL to phase

lock the feedback signal to its reference signal.

FBIN

FBIN

36

35

I Feedback input. FBIN provides the feedback signal to the internal PLL. FBIN must be hard-wired

to FBOUT to complete the PLL. The integrated PLL synchronizes CLK and FBIN so that there is

nominally zero phase error between CLK and FBIN.

FBOUT

FBOUT

32

33

O Feedback output. FBOUT is dedicated for external feedback. It switches at the same frequency as

CLK. When externally wired to FBIN, FBOUT completes the feedback loop of the PLL.

G 37 I Output bank enable. G is the output enable for outputs Y and Y . When G is low outputs Y are disabled

to a high-impedance state. When G is high, all outputs Y are enabled and switch at the same

frequency as CLK.

GND 1, 7, 8, 18,

24, 25, 31,

41, 42, 48

Ground Ground

V

CC

4, 11, 12,

15, 21, 28,

34, 38, 45

Power Power supply

Y0, Y1, Y2,

Y3, Y4, Y5,

Y6, Y7, Y8,

Y9

3, 5, 10,

20, 22, 46,

44, 39, 29,

27

O Clock outputs. These outputs provide low-skew copies of CLK.

Y0, Y1, Y2,

Y3

, Y4, Y5,

Y6

, Y7, Y8,

Y9

2, 6, 9,

19, 23, 47,

43, 40, 30,

26

O Clock outputs. These outputs provide low-skew copies of CLK.

CDC857-2, CDC857-3

2.5-/3.3-V PHASE-LOCK LOOP CLOCK DRIVERS

SCAS627A – SEPTEMBER 1999 – DECEMBER 1999

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

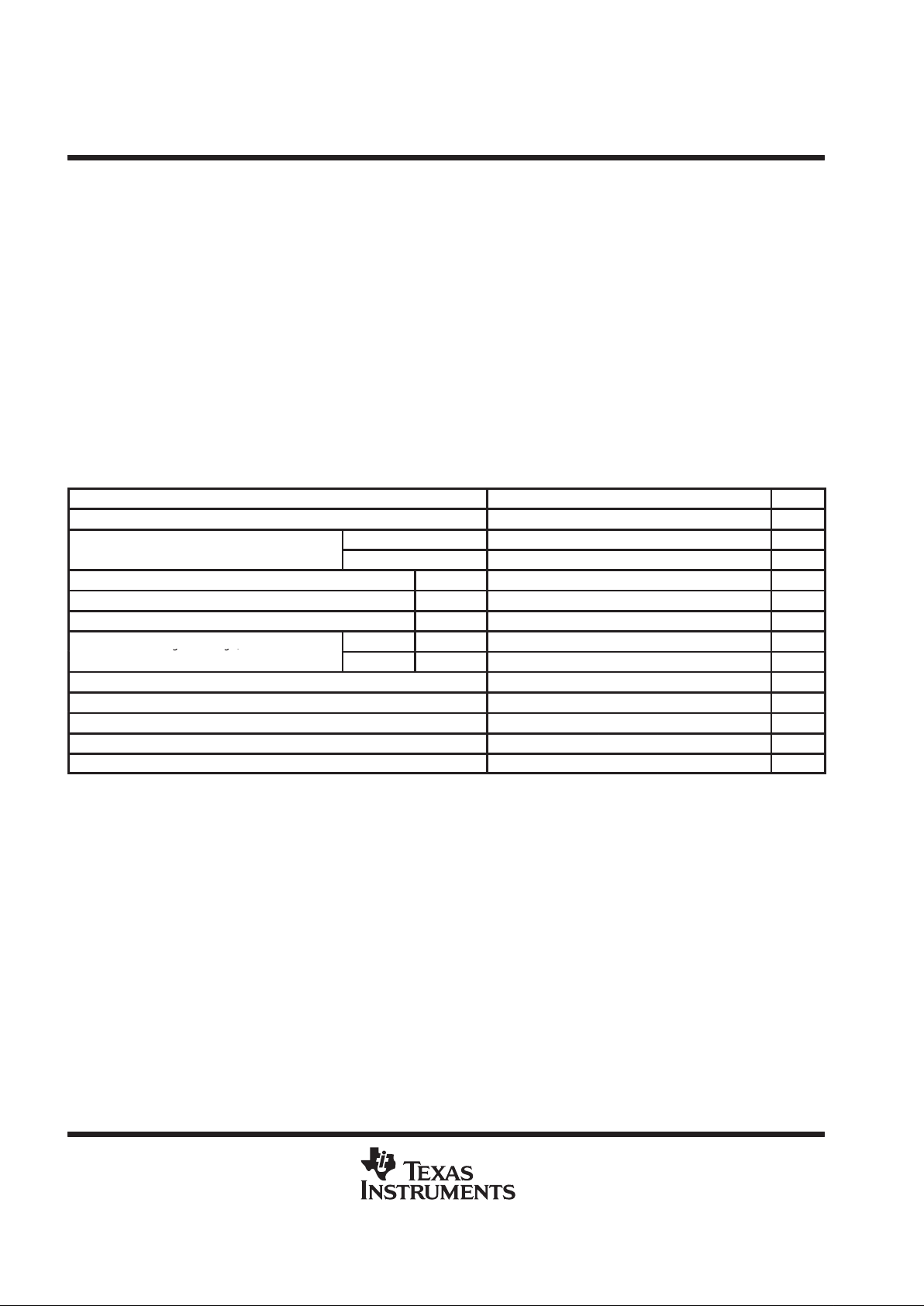

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

†

Supply voltage range, VCC or AVCC –0.5 V to 4.6 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range VI (see Notes 1 and 2) –0.5 V to VCC +0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, VO, (see Notes 1 and 2) –0.5 V to VCC +0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, I

IK

(VI < 0 or VI > VCC) ±50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output clamp current, IOK (VO < 0 or VO > VCC ±50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total output current, IO (VO = 0 to VCC) ±50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package thermal impedance, θJA (see Note 3) 89°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range T

stg

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. This value is limited to 4.6 V maximum.

3. The package thermal impedance is calculated in accordance with JESD 51.

recommended operating conditions (see Note 4)

MIN NOM MAX UNIT

Supply voltage, V

CC

2.3 2.7 V

pp

CDC857–2 2.3 2.7 V

Analog suppl

y v

oltage, AV

CC

CDC857–3 3 3.6 V

Low–level input voltage, VIL(G)

G input 0.3 × V

CC

V

High–level input voltage, VIH(G)

G input 0.7 × V

CC

V

DC input signal voltage (see Note 5) CLK, FBIN –0.3 VCC+0.3 V

Differential input signal voltage, V

dc CLK, FBIN 0.35 VCC+0.6 V

gg,

ID

(see Note 6)

ac CLK, FBIN 0.7 VCC+0.6 V

Differential cross-point input voltage (see Note 7) VCC/2–0.2 VCC/2 VCC/2+0.2 V

High-level output current, I

OH

–12 mA

Low-level output current, I

OL

12 mA

Input slew rate, SR 1 V/ns

Operating free-air temperature, T

A

0 85 °C

NOTES: 4. Unused inputs must be held high or low to prevent them from floating.

5. DC input signal voltage specifies the allowable dc execution of differential input.

6. Differential input signal voltage specifies the differential voltage |VTR – VCP| required for switching, where VTR is the true input level

and VCP is the complementary input level (see figure 3).

7. Differential cross-point voltage is expected to track variations of VCC and is the voltage at which the differential signals must be

crossing.

Loading...

Loading...