Texas Instruments CDC2582PAH Datasheet

D

Low Output Skew for Clock-Distribution

and Clock-Generation Applications

D

Operates at 3.3-V V

D

Distributes Differential LVPECL Clock

CC

Inputs to 12 TTL-Compatible Outputs

D

Two Select Inputs Configure Up to Nine

Outputs to Operate at One-Half or Double

the Input Frequency

D

No External RC Network Required

D

External Feedback Input (FBIN) Is Used to

Synchronize the Outputs With the Clock

Inputs

3.3-V PHASE-LOCK LOOP CLOCK DRIVER

WITH DIFFERENTIAL LVPECL CLOCK INPUTS

SCAS379B – FEBRUARY 1993 – REVISED FEBRUARY 1996

D

Application for Synchronous DRAMs

D

Outputs Have Internal 26-Ω Series

Resistors to Dampen Transmission-Line

Effects

D

D

D

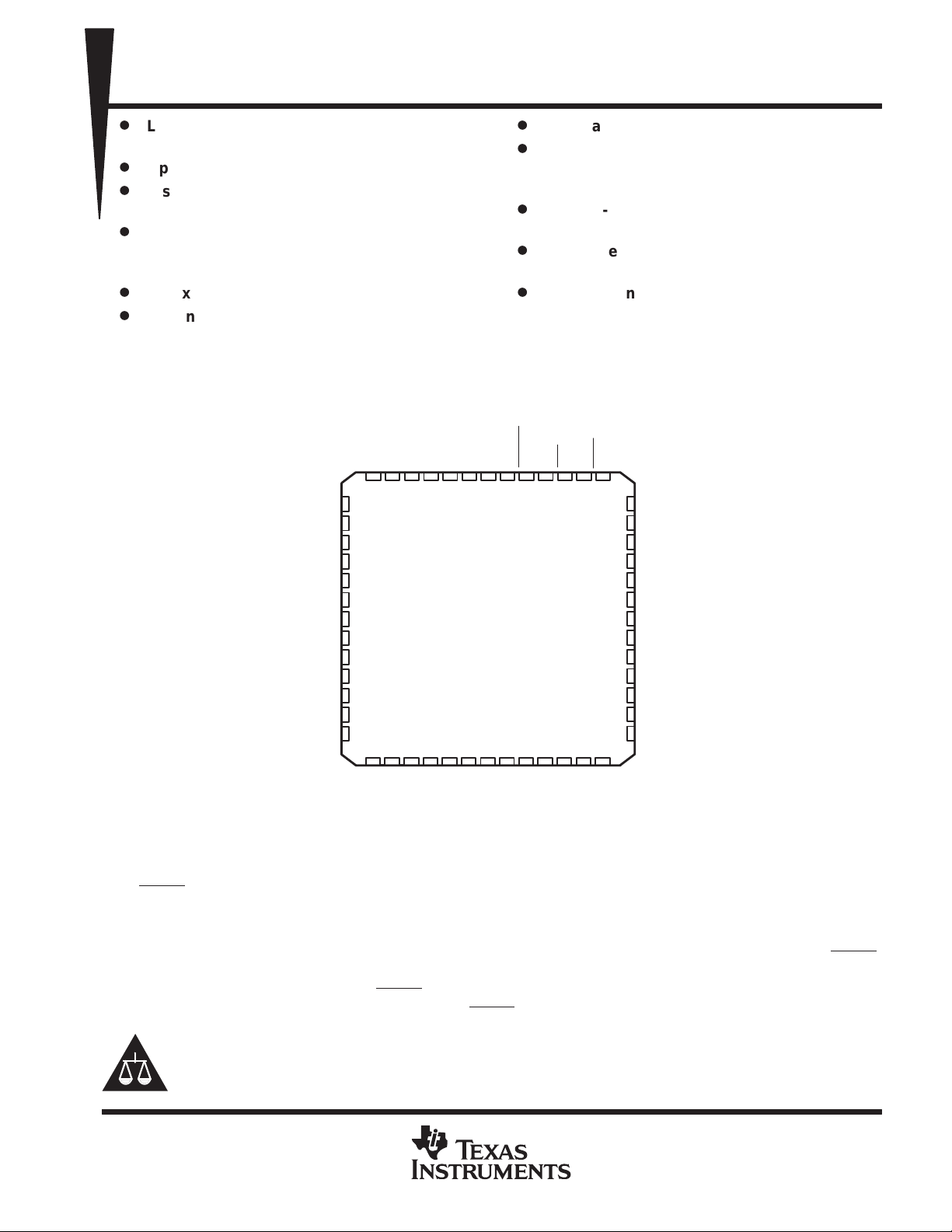

PAH PACKAGE

(TOP VIEW)

State-of-the-Art

Significantly Reduces Power Dissipation

Distributed VCC and Ground Pins Reduce

Switching Noise

Packaged in 52-Pin Quad Flatpack

EPIC-ΙΙB

BiCMOS Design

CDC2582

GND

1Y1

V

CC

GND

1Y2

V

CC

GND

1Y3

V

CC

GND

GND

2Y1

V

CC

GND

SEL1

51 50 49 48 4752 46

1

2

3

4

5

6

7

8

9

10

11

12

13

15 16

14

2Y2

GND

SEL0

AGND

18 19 20 21

17

CC

V

GND

FBIN

AGND

CC

V

2Y3

CC

V

A

GND

CC

V

CLKIN

CLKINAOE

44 43 4245

22 23 24 25 26

3Y1

GND

V

41 40

CC

GND

TEST

CLR

39

38

37

36

35

34

33

32

31

30

29

28

27

CC

V

3Y2

V

CC

4Y3

GND

V

CC

4Y2

GND

V

CC

4Y1

GND

GND

V

CC

3Y3

GND

description

The CDC2582 is a high-performance, low-skew, low-jitter clock driver. It uses a phase-lock loop (PLL) to

precisely align the frequency and phase of the clock output signals to the differential LVPECL clock (CLKIN,

CLKIN

) input signals. It is specifically designed to operate at speeds from 50 MHz to 100 MHz or down to 25 MHz

on outputs configured as half-frequency outputs. Each output has an internal 26-Ω series resistor that improves

the signal integrity at the load. The CDC2582 operates at 3.3-V VCC.

The feedback input (FBIN) synchronizes the frequency of the output clocks with the input clock (CLKIN, CLKIN)

signals. One of the twelve output clocks must be fed back to FBIN for the PLL to maintain synchronization

between the differential CLKIN and CLKIN

inputs and the outputs. The output used as feedback is synchronized

to the same frequency as the clock (CLKIN and CLKIN) inputs.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC-ΙΙB is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1996, Texas Instruments Incorporated

1

CDC2582

3.3-V PHASE-LOCK LOOP CLOCK DRIVER

WITH DIFFERENTIAL LVPECL CLOCK INPUTS

SCAS379B – FEBRUARY 1993 – REVISED FEBRUARY 1996

description (continued)

The Y outputs can be configured to switch in phase and at the same frequency as differential clock inputs (CLKIN

and CLKIN). Select (SEL1, SEL0) inputs configure up to nine Y outputs, in banks of three, to operate at one-half

or double the differential clock input frequency, depending upon the feedback configuration (see Tables 1

and 2). All output signal duty cycles are adjusted to 50% independent of the duty cycle at the input clocks.

Output-enable (OE

) is provided for output control. When OE is high, the outputs are in the low state. When OE

is low, the outputs are active. CLR is negative-edge triggered and can be used to reset the outputs operating

at half frequency . TEST is used for factory testing of the device and can be used to bypass the PLL. TEST should

be strapped to GND for normal operation.

Unlike many products containing a PLL, the CDC2582 does not require external RC networks. The loop filter

for the PLL is included on chip, minimizing component count, board space, and cost.

Because it is based on PLL circuitry, the CDC2582 requires a stabilization time to achieve phase lock of the

feedback signal to the reference signal. This stabilization time is required following power up and application

of a fixed-frequency, fixed-phase signal at CLKIN and CLKIN, as well as following any changes to the PLL

reference or feedback signal. Such changes occur upon change of SEL1 and SEL0, enabling the PLL via TEST ,

and upon enable of all outputs via OE

.

The CDC2582 is characterized for operation from 0°C to 70°C.

detailed description of output configurations

The voltage-controlled oscillator (VCO) used in the CDC2582 has a frequency range of 100 MHz to 200 MHz,

twice the operating frequency range of the CDC2582 outputs. The output of the VCO is divided by 2 and by 4

to provide reference frequencies with a 50% duty cycle of one-half and one-fourth the VCO frequency. SEL0

and SEL1 determine which of the two signals are buffered to each bank of device outputs.

One device output must be externally wired to FBIN to complete the PLL. The VCO operates such that the

frequency of this output matches that of the CLKIN/CLKIN signals. In the case that a VCO/2 output is wired to

FBIN, the VCO must operate at twice the CLKIN/CLKIN frequency , resulting in device outputs that operate at

the same or one-half the CLKIN/CLKIN frequency . If a VCO/4 output is wired to FBIN, the device outputs operate

at the same or twice the CLKIN/CLKIN

frequency.

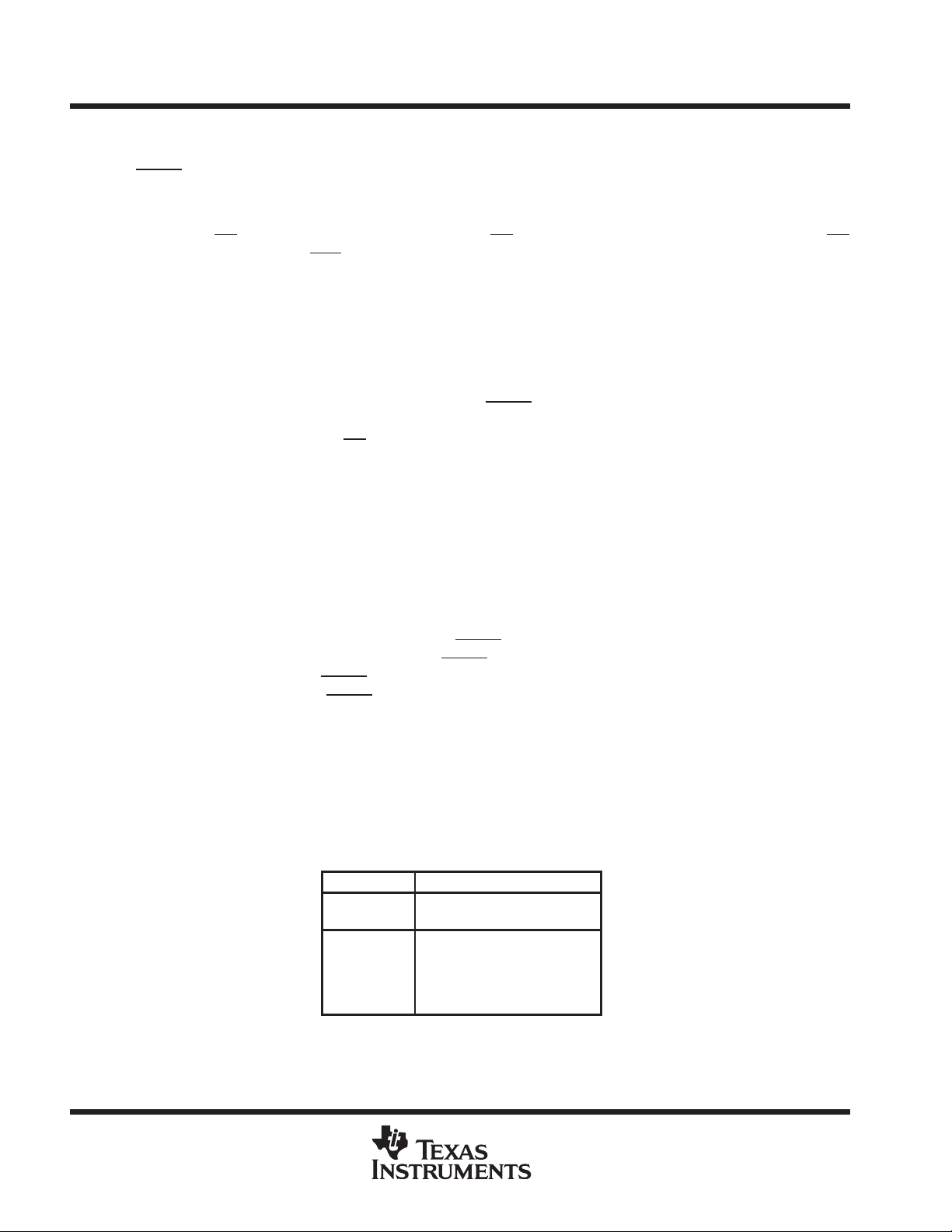

output configuration A

Output configuration A is valid when any output configured as a 1× frequency output in Table 1 is fed back to

FBIN. The frequency range for the differential clock input is 50 MHz to 100 MHz when using output configuration

A. Outputs configured as 1/2× outputs operate at half the input clock frequency , while outputs configured as 1×

outputs operate at the same frequency as the differential clock input.

Table 1. Output Configuration A

INPUTS

SEL1 SEL0

L L None All

L H 1Yn 2Yn, 3Yn, 4Yn

H L 1Yn, 2Yn 3Yn, 4Yn

H H 1Yn, 2Yn, 3Yn 4Yn

NOTE: n = 1, 2, 3

FREQUENCY1×FREQUENCY

OUTPUTS

1/2×

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3.3-V PHASE-LOCK LOOP CLOCK DRIVER

WITH DIFFERENTIAL LVPECL CLOCK INPUTS

SCAS379B – FEBRUARY 1993 – REVISED FEBRUARY 1996

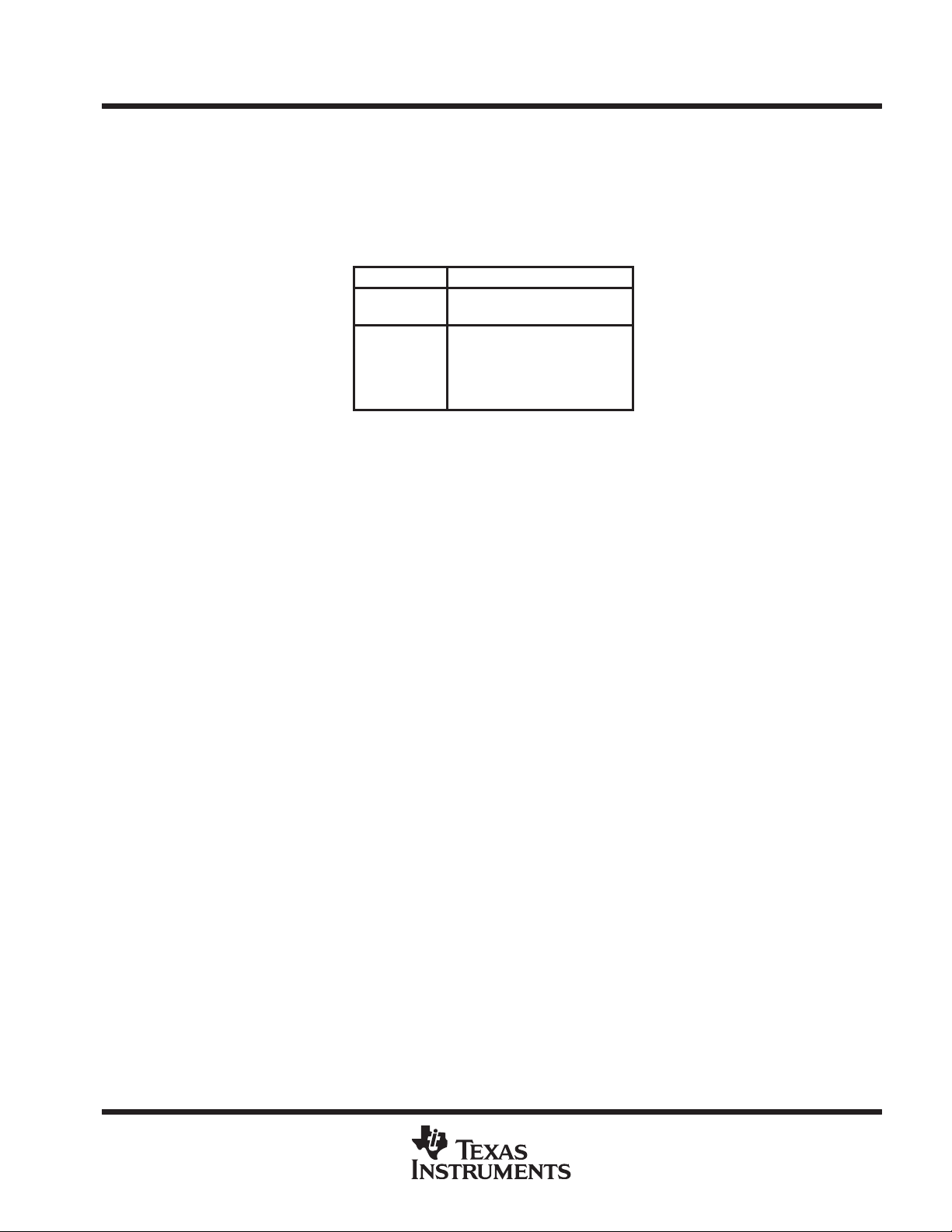

output configuration B

Output configuration B is valid when any output configured as a 1× frequency output in Table 2 is fed back to

FBIN. The frequency range for the differential clock inputs is 25 MHz to 50 MHz when using output configuration

B. Outputs configured as 1× outputs operate at the input clock frequency , while outputs configured as 2× outputs

operate at double the frequency of the differential clock inputs.

Table 2. Output Configuration B

CDC2582

INPUTS

SEL1 SEL0

L L All None

L H 1Yn 2Yn, 3Yn, 4Yn

H L 1Yn, 2Yn 3Yn, 4Yn

H H 1Yn, 2Yn, 3Yn 4Yn

NOTE: n = 1, 2, 3

FREQUENCY2×FREQUENCY

OUTPUTS

1×

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

Loading...

Loading...