Page 1

CD4049UB, CD4050B

[ /Title

(CD40

49UB,

CD405

0B)

/Subject

(CMO

S Hex

Buffer/

Converters)

/Autho

r ()

/Keywords

(Harris

Semiconductor,

CD400

0,

metal

gate,

CMOS

Data sheet acquired from Harris Semiconductor

SCHS046A

CMOS Hex Buffer/Converters

The CD4049UB and CD4050B devices are inverting and

non-inverting hex buffers, respectively, and feature logiclevel conversion using only one supply voltage (V

input-signal high level (V

) can exceed the VCC supply

IH

CC

). The

voltage when these devices are used for logic-level

conversions.These devices are intended for use as CMOS

to DTL/TTL converters and can drive directly two DTL/TTL

loads. (V

= 5V, VOL≤ 0.4V, and IOL≥ 3.3mA.)

CC

The CD4049UB and CD4050B are designated as

replacements for CD4009UB and CD4010B, respectively.

Because the CD4049UB and CD4050B require only one

power supply, they are preferred over the CD4009UB and

CD4010B and should be used in place of the CD4009UB

and CD4010B in all inverter, current driver, or logic-level

conversion applications. In these applications the

CD4049UB and CD4050B are pin compatible with the

CD4009UB and CD4010B respectively, and can be

substituted for these devices in existing as well as in new

designs. Terminal No. 16 is not connected internally on the

CD4049UB or CD4050B, therefore, connection to this

terminal is of no consequence to circuit operation. For

applications not requiring high sink-current or voltage

conversion, the CD4069UB Hex Inverter is recommended.

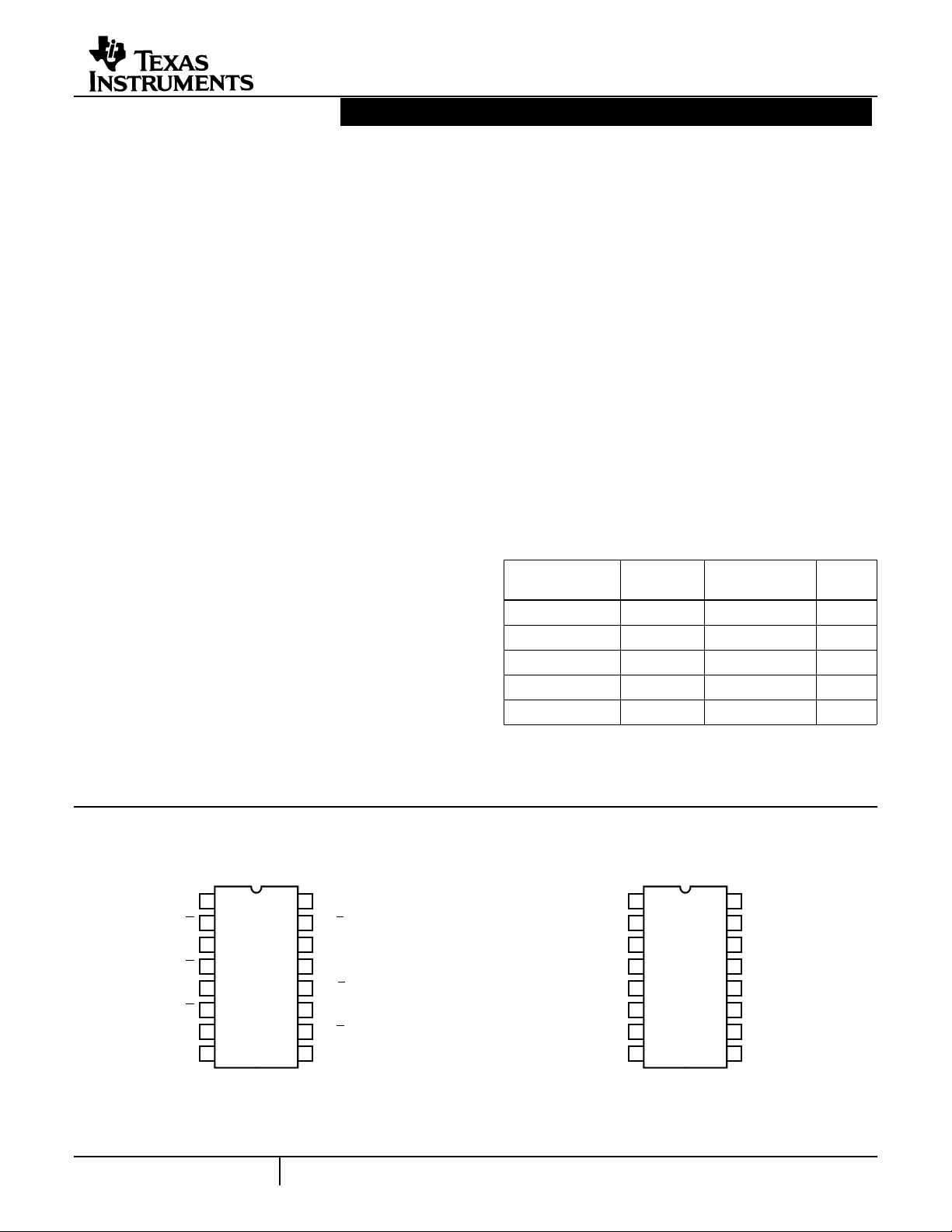

Pinouts

CD4049UB (PDIP, CERDIP)

TOP VIEW

August 1998 - Revised May 1999

Features

• CD4049UB Inverting

• CD4050B Non-Inverting

• High Sink Current for Driving 2 TTL Loads

• High-To-Low Level Logic Conversion

• 100% Tested for Quiescent Current at 20V

• Maximum Input Current of 1µA at 18V Over Full Package

Temperature Range; 100nA at 18V and 25

o

C

• 5V, 10V and 15V Parametric Ratings

Applications

• CMOS to DTL/TTL Hex Converter

• CMOS Current “Sink” or “Source” Driver

• CMOS High-To-Low Logic Level Converter

Ordering Information

TEMP.

PART NUMBER

CD4049UBE -55 to 125 16 Ld PDIP E16.3

CD4050BE -55 to 125 16 Ld PDIP E16.3

CD4049UBF -55 to 125 16 Ld CERDIP F16.3

CD4050BF -55 to 125 16 Ld CERDIP F16.3

CD4050BM -55 to 125 16 Ld SOIC M16.3

NOTE: Wafer and die for this part number is available which meets

all electrical specifications. Please contact your local sales office or

customer service for ordering information.

RANGE (oC) PACKAGE

CD4050B (PDIP, CERDIP, SOIC)

TOP VIEW

PKG.

NO.

V

CC

G = A

H =

I =

V

SS

NC

1

2

A

3

4

B

B

5

6

C

7

C

8

16

15

F

L =

F

14

NC

13

K =

12

E

11

E

10

J = D

9

D

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

V

CC

G = A

H = B

I = C

V

SS

1

2

A

3

4

B

5

6

7

C

8

Copyright

© 1999, Texas Instruments Incorporated

NC

16

L = F

15

F

14

NC

13

K = E

12

E

11

J = D

10

D

9

Page 2

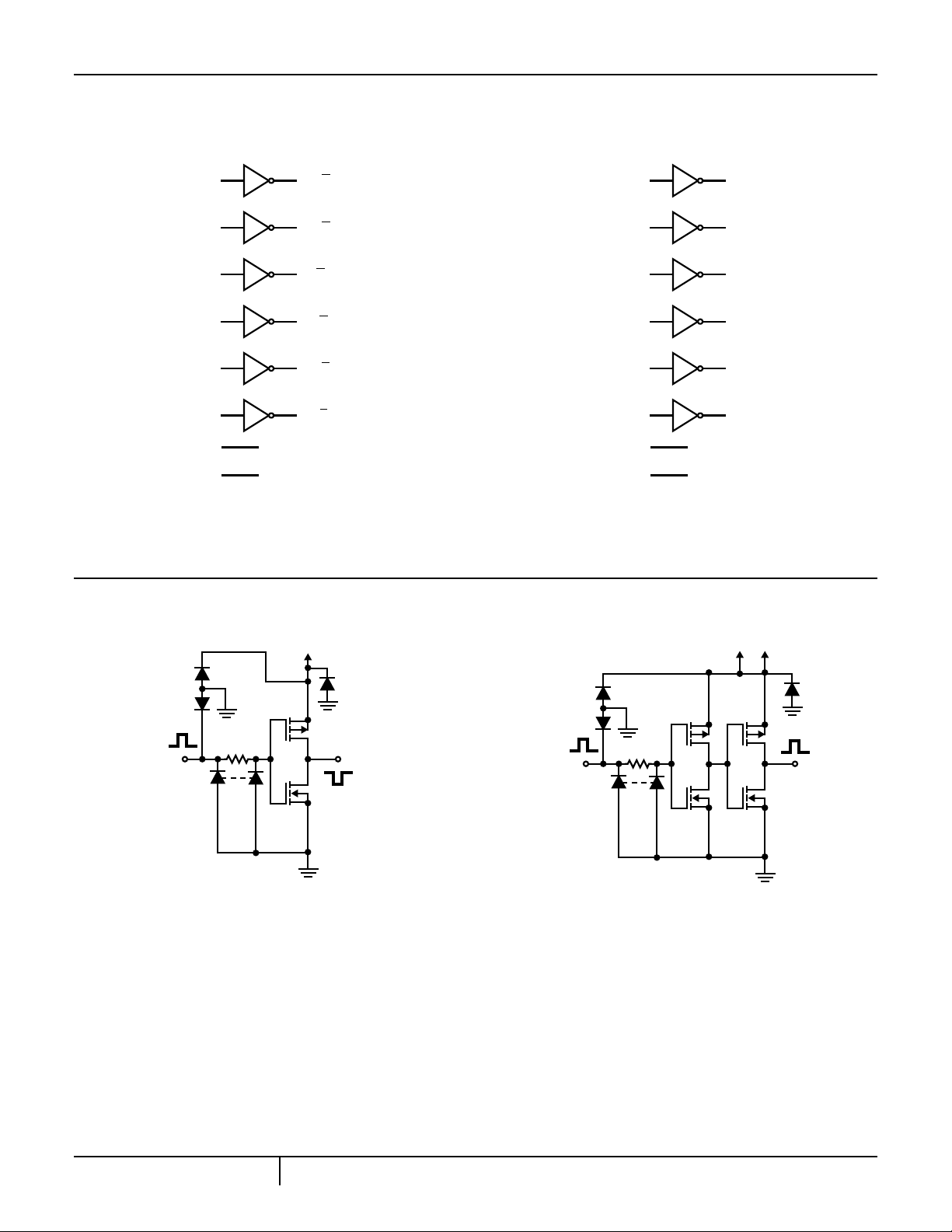

Functional Block Diagrams

CD4049UB CD4050B

CD4049UB, CD4050B

32

AG =

54

BH =

76

CI =

910

DJ =

11 12

EK =

14 15

FL =

1

V

CC

8

V

SS

NC = 13

NC = 16

Schematic Diagrams

A

B

C

D

E

F

32

A G = A

54

B H = B

76

C I = C

910

D J = D

11 12

E K = E

14 15

F L = F

1

V

CC

8

V

SS

NC = 13

NC = 16

V

CC

P

R

IN

OUT

N

V

SS

FIGURE 1A. SCHEMATIC DIAGRAM OF CD4049UB, 1 OF 6

IDENTICAL UNITS

V

CC

P

R

IN

N

P

OUT

N

V

SS

FIGURE 1B. SCHEMATIC DIAGRAM OF CD4050B, 1 OF 6

IDENTICAL UNITS

2

Page 3

CD4049UB, CD4050B

Absolute Maximum Ratings Thermal Information

Supply Voltage (V+ to V-). . . . . . . . . . . . . . . . . . . . . . . -0.5V to 20V

DC Input Current, Any One Input. . . . . . . . . . . . . . . . . . . . . . ±10mA

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operationofthe

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

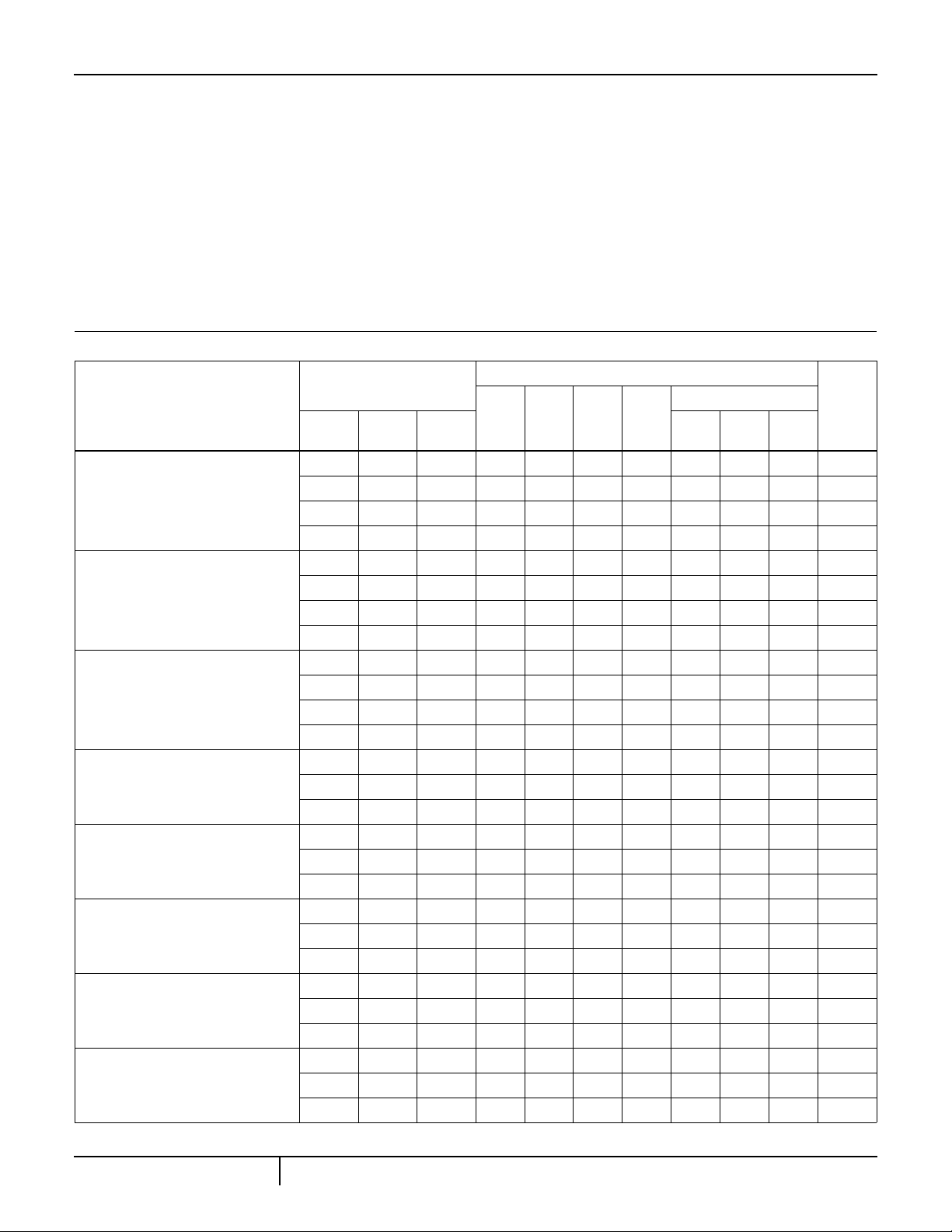

DC Electrical Specifications

TEST CONDITIONS

PARAMETER

Quiescent Device Current

IDD (Max)

Output Low (Sink) Current

IOL (Min)

Output High (Source) Current

IOH (Min)

Out Voltage Low Level

VOL (Max)

Output Voltage High Level

VOH (Min)

Input Low Voltage, VIL (Max)

CD4049UB

Input Low Voltage, VIL (Max)

CD4050B

Input High Voltage, VIH Min

CD4049UB

V

O

(V)

- 0,5 5 1 1 30 30 - 0.02 1 µA

- 0,10 10 2 2 60 60 - 0.02 2 µA

- 0,15 15 4 4 120 120 - 0.02 4 µA

- 0,20 20 20 20 600 600 - 0.04 20 µA

0.4 0,5 4.5 3.3 3.1 2.1 1.8 2.6 5.2 - mA

0.4 0,5 5 4 3.8 2.9 2.4 3.2 6.4 - mA

0.5 0,10 10 10 9.6 6.6 5.6 8 16 - mA

1.5 0,15 15 26 25 20 18 24 48 - mA

4.6 0,5 5 -0.81 -0.73 -0.58 -0.48 -0.65 -1.2 - mA

2.5 0,5 5 -2.6 -2.4 -1.9 -1.55 -2.1 -3.9 - mA

9.5 0,10 10 -2.0 -1.8 -1.35 -1.18 -1.65 -3.0 - mA

13.5 0,15 15 -5.2 -4.8 -3.5 -3.1 -4.3 -8.0 - mA

- 0,5 5 0.05 0.05 0.05 0.05 - 0 0.05 V

- 0,10 10 0.05 0.05 0.05 0.05 - 0 0.05 V

- 0,15 5 0.05 0.05 0.05 0.05 - 0 0.05 V

- 0,5 5 4.95 4.95 4.95 4.95 4.95 5 - V

- 0,10 10 9.95 9.95 9.95 9.95 9.95 10 - V

- 0,15 15 14.95 14.95 14.95 14.95 14.95 15 - V

4.5 - 5 1 1 1 1 - - 1 V

9-102222--2V

13.5 - 15 2.5 2.5 2.5 2.5 - - 2.5 V

0.5 - 5 1.5 1.5 1.5 1.5 - - 1.5 V

1-103333--3V

1.5 - 154444--4 V

0.5 - 5 4 4 4 4 4 - - V

1-1088888--V

1.5 - 15 12.5 12.5 12.5 12.5 12.5 - - V

V

IN

(V) VCC (V) MIN TYP MAX

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

PDIP Package . . . . . . . . . . . . . . . . . . . 90 N/A

CERDIP Package. . . . . . . . . . . . . . . . . 130 55

SOIC Package . . . . . . . . . . . . . . . . . . . 100 N/A

Maximum Junction Temperature (Plastic Package) . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .265oC

(SOIC - Lead Tips Only)

LIMITS AT INDICATED TEMPERATURE (oC)

25

UNITS-55 -40 85 125

3

Page 4

CD4049UB, CD4050B

DC Electrical Specifications (Continued)

LIMITS AT INDICATED TEMPERATURE (

TEST CONDITIONS

V

PARAMETER

Input High Voltage, VIH Min

CD4050B

O

(V)

4.5 - 5 3.5 3.5 3.5 3.5 3.5 - - V

9-1077777--V

13.5 - 15 11 11 11 11 11 - - V

Input Current, IIN Max - 0,18 18 ±0.1 ±0.1 ±1 ±1-±10

V

IN

(V) VCC (V) MIN TYP MAX

o

25

-5

C)

UNITS-55 -40 85 125

±0.1 µA

AC Electrical Specifications T

PARAMETER

Propagation Delay Time

Low to High, t

CD4049UB

Propagation Delay Time

Low to High, t

CD4050B

Propagation Delay Time

High to Low, t

CD4049UB

Propagation Delay Time

High to Low, t

CD4050B

Transition Time, Low to High, t

Transition Time, High to Low, t

Input Capacitance, C

CD4049UB

Input Capacitance, C

CD4050B

PLH

PLH

PHL

PHL

TLH

THL

IN

IN

= 25oC, Input tr, tf = 20ns, CL = 50pF, RL = 200kΩ

A

TEST CONDITIONS LIMITS (ALL PACKAGES)

IN

V

CC

5 5 60 120 ns

10 10 32 65 ns

1054590ns

15 15 25 50 ns

1554590ns

5 5 70 140 ns

10 10 40 80 ns

1054590ns

15 15 30 60 ns

1554080ns

5 5 32 65 ns

10 10 20 40 ns

1051530ns

15 15 15 30 ns

1551020ns

5 5 55 110 ns

10 10 22 55 ns

10 5 50 100 ns

15 15 15 30 ns

15 5 50 100 ns

5 5 80 160 ns

10 10 40 80 ns

15 15 30 60 ns

5 5 30 60 ns

10 10 20 40 ns

15 15 15 30 ns

- - 15 22.5 pF

- - 5 7.5 pF

TYP MAX

UNITSV

4

Page 5

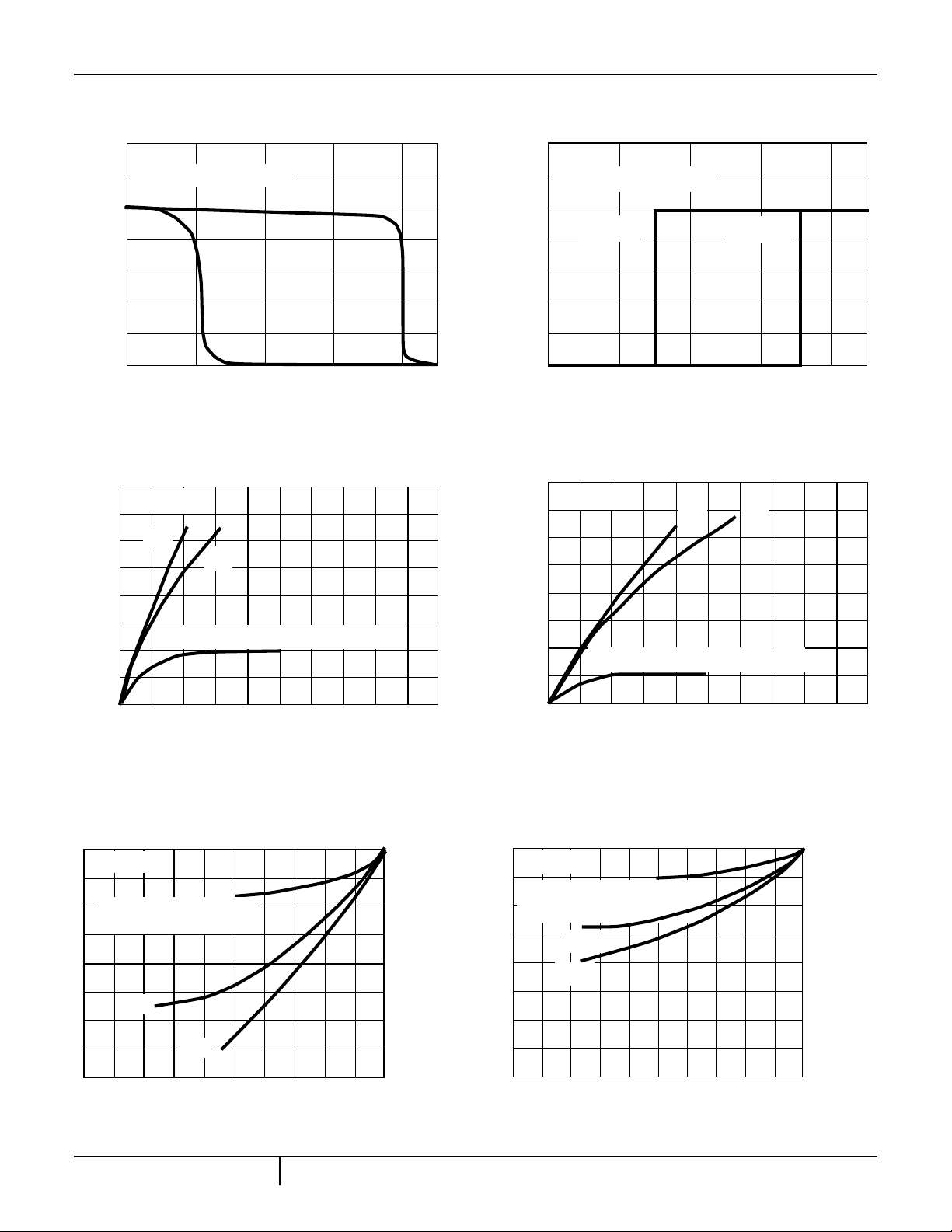

Typical Performance Curves

CD4049UB, CD4050B

TA = 25oC

SUPPLY VOLTAGE (VCC) = 5V

5

4

3

2

, OUTPUT VOLTAGE (V)

O

V

1

01234

V

, INPUT VOLTAGE (V)

I

MAXIMUMMINIMUM

FIGURE 2. MINIMUM AND MAXIMUM VOLTAGE TRANSFER

CHARACTERISTICS FOR CD4049UB

TA = 25oC

70

15V

60

50

40

30

20

10

, OUTPUT LOW (SINK) CURRENT (mA)

OL

I

01234

10V

GATE TO SOURCE VOLTAGE (VGS) = 5V

5678

, DRAIN TO SOURCE VOLTAGE (V)

V

DS

TA = 25oC

SUPPLY VOLTAGE (VCC) = 5V

5

4

3

2

, OUTPUT VOLTAGE (V)

O

V

1

01234

V

, INPUT VOLTAGE (V)

I

MAXIMUMMINIMUM

FIGURE 3. MINIMUM AND MAXIMUM VOLTAGE TRANSFER

CHARACTERISTICS FOR CD4050B

TA = 25oC

70

60

50

40

30

20

10

, OUTPUT LOW (SINK) CURRENT (mA)

OL

I

01234

GATE TO SOURCE VOLTAGE (VGS) = 5V

VDS, DRAIN TO SOURCE VOLTAGE (V)

10V15V

5678

FIGURE 4. TYPICAL OUTPUT LOW (SINK) CURRENT

CHARACTERISTICS

, DRAIN TO SOURCE VOLTAGE (V)

V

DS

-8 -7 -6 -5 -4 -3 -2 -1 0

TA = 25oC

-5

GATE TO SOURCE VOLTAGE

V

= -5V

GS

-10V

-15V

-10

-15

-20

-25

-30

-35

FIGURE 6. TYPICAL OUTPUT HIGH (SOURCE) CURRENT

CHARACTERISTICS

5

FIGURE 5. MINIMUM OUTPUT LOW (SINK) CURRENT DRAIN

TA = 25oC

GATE TO SOURCE VOLTAGE

VGS = -5V

OUTPUT HIGH (SOURCE)

CURRENT CHARACTERISTICS

FIGURE 7. MINIMUM OUTPUT HIGH (SOURCE) CURRENT

CHARACTERISTICS

, DRAIN TO SOURCE VOLTAGE (V)

V

DS

-8 -7 -6 -5 -4 -3 -2 -1 0

-10V

-15V

CHARACTERISTICS

-5

-10

-15

-20

-25

-30

OUTPUT HIGH (SOURCE)

-35

CURRENT CHARACTERISTICS

Page 6

CD4049UB, CD4050B

Typical Performance Curves

(Continued)

10

9

8

7

6

125oC

VCC = 5V

SUPPLY VOLTAGE

= 10V

V

CC

TA = -55oC

5

4

, OUTPUT VOLTAGE (V)

3

O

V

2

125oC

-55oC

1

0

, INPUT VOLTAGE (V)

V

I

876543210

910

FIGURE 8. TYPICALV OLTAGE TRANSFER CHARACTERISTICS

AS A FUNCTION OF TEMPERA TURE FOR CD4049UB

5

10

TA = 25oC

= 15V

10V

POWER DISSIPATION PER INVERTER (µW)

4

10

SUPPLY VOLTAGE V

3

10

2

10

10

10

10

CC

LOAD CAPACITANCE

C

(11pF FIXTURE + 39pF EXT)

C

(11pF FIXTURE + 4pF EXT)

2

f, INPUT FREQUENCY (kHz)

= 50pF

L

= 15pF

L

10

10V

5V

3

4

10

10

9

8

125oC

SUPPLY VOLTAGE

V

= 10V

CC

7

6

5

VCC = 5V

TA = -55oC

4

, OUTPUT VOLTAGE (V)

3

O

V

125oC

2

-55oC

1

0

V

, INPUT VOLTAGE (V)

I

876543210

910

FIGURE 9. TYPICAL V OLTA GETRANSFER CHARACTERISTICS

AS A FUNCTION OF TEMPERA TURE FOR CD4050B

TA = 25oC

5

10

4

10

3

10

2

10

10

POWER DISSIPATION PER INVERTER (µW)

5

10

SUPPLY VOLTAGE VCC = 5V FREQUENCY (f) = 10kHz

2

3

4

10

10

10

10

5

10

tr, tf, INPUT RISE AND FALL TIME (ns)

15V; 1MHz

15V; 100kHz

10V; 100kHz

15V; 10kHz

10V; 10kHz

15V; 1kHz

6

10

7

10

8

10

FIGURE 10. TYPICAL POWER DISSIPATION vs FREQUENCY

CHARACTERISTICS

6

10

TA = 25oC

5

10

4

10

3

10

2

10

10

SUPPLY VOLTAGE VCC = 5V FREQUENCY (f) = 10kHz

POWER DISSIPATION PER INVERTER (µW)

1

10 10

2

10310

tr, tf, INPUT RISE AND FALL TIME (ns)

FIGURE 12. TYPICAL POWER DISSIPATION vs INPUT RISE

AND FALL TIMES PER INVERTER FOR CD4050B

6

FIGURE 11. TYPICAL POWER DISSIPATION vs INPUT RISE

AND FALL TIMES PER INVERTER FOR CD4049UB

15V; 1MHz

15V; 100kHz

10V; 100kHz

15V; 10kHz

10V; 10kHz

15V; 1kHz

4

5

10

10610

7

8

10

Page 7

CD4049UB, CD4050B

Test Circuits

V

V

CC

INPUTS

V

SS

FIGURE 13. QUIESCENT DEVICE CURRENT TEST CIRCUIT

CC

I

DD

V

SS

V

CC

V

IH

OUTPUTSINPUTS

+

V

IL

V

SS

NOTE: Test any one input with other inputs at V

FIGURE 14. INPUT VOLTAGE TEST CIRCUIT

DVM

-

CC

or VSS.

V

CC

V

CC

I

V

SS

V

SS

NOTE: Measure inputs sequentially, to both V

all unused inputs to either VCC or VSS.

FIGURE 15. INPUT CURRENT TEST CIRCUIT

OUTPUTSINPUTS

and VSS connect

CC

100kHz, 1MHz

500µF

C

L

10kHz,

CMOS 10V LEVEL TO DTL/TTL 5V LEVEL

10V = V

IH

In Terminal - 3, 5, 7, 9, 11, or 14

Out Terminal - 2, 4, 6, 10, 12 or 15

VCC Terminal - 1

VSS Terminal - 8

FIGURE 16. LOGIC LEVEL CONVERSION APPLICATION

V

DD

0.1µF

I

1

2

3

4

5

6

7

8

16

15

14

13

12

11

CD4049UB

10

9

COS/MOS

IN

0 = V

IL

VCC = 5V

CD4049

OUTPUT

TO DTL/TTL

INPUTS

V

SS

5V = V

0 = V

OH

OL

INCLUDES FIXTURE CAPACITANCE

C

L

FIGURE 17. DYNAMIC POWER DISSIPATION TEST CIRCUITS

7

Page 8

CD4049UB, CD4050B

Dual-In-Line Plastic Packages (PDIP)

N

D1

-C-

E1

-B-

A1

A2

E

A

L

e

C

C

L

e

A

C

e

B

INDEX

AREA

BASE

PLANE

SEATING

PLANE

D1

B1

1 2 3 N/2

-AD

e

B

0.010 (0.25) C AM BS

NOTES:

1. Controlling Dimensions:INCH.In caseofconflict betweenEnglishand

Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication No. 95.

4. Dimensions A, A1 and L are measured with the package seatedinJEDEC seating plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

6. E and are measured with the leads constrained to beperpendic-

e

A

ular to datum .

-C-

7. eBand eCare measuredatthe lead tips with theleadsunconstrained.

eC must be zero or greater.

8. B1 maximum dimensions do not include dambarprotrusions.Dambar

protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3,

E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E16.3 (JEDEC MS-001-BB ISSUE D)

16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.210 - 5.33 4

A1 0.015 - 0.39 - 4

A2 0.115 0.195 2.93 4.95 -

B 0.014 0.022 0.356 0.558 B1 0.045 0.070 1.15 1.77 8, 10

C 0.008 0.014 0.204 0.355 -

D 0.735 0.775 18.66 19.68 5

D1 0.005 - 0.13 - 5

E 0.300 0.325 7.62 8.25 6

E1 0.240 0.280 6.10 7.11 5

e 0.100 BSC 2.54 BSC -

e

A

e

B

0.300 BSC 7.62 BSC 6

- 0.430 - 10.92 7

L 0.115 0.150 2.93 3.81 4

N16 169

NOTESMIN MAX MIN MAX

Rev. 0 12/93

8

Page 9

CD4049UB, CD4050B

Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

c1

LEAD FINISH

-A-

-B-

bbb C A - B

S

BASE

PLANE

SEATING

PLANE

S1

b2

ccc C A - BMD

D

A

A

b

e

S

S

NOTES:

1. Index area:Anotchor a pinoneidentification mark shall belocated adjacent to pin one and shall be located within the shaded

area shown. The manufacturer’s identification shall not be used

as a pin one identification mark.

2. The maximum limits of lead dimensions b and c or M shall be

measured at the centroid of the finished lead surfaces, when

solder dip or tin plate lead finish is applied.

3. Dimensions b1 and c1 apply to lead basemetalonly.Dimension

M applies to lead plating and finish thickness.

4. Corner leads (1, N, N/2, andN/2+1)may beconfiguredwith a

partial lead paddle. For this configuration dimension b3 replaces

dimension b2.

5. This dimension allows for off-center lid, meniscus, and glass

overrun.

6. Dimension Q shall be measured from the seating plane to the

base plane.

7. Measure dimension S1 at all four corners.

8. N is the maximum number of terminal positions.

9. Dimensioning and tolerancing per ANSI Y14.5M - 1982.

10. Controlling dimension: INCH.

-DBASE

E

D

S

S

Q

A

-CL

METAL

b1

M

(b)

SECTION A-A

α

(c)

M

eA

eA/2

aaa C A - B

M

c

D

S S

F16.3 MIL-STD-1835 GDIP1-T16 (D-2, CONFIGURATION A)

16 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.200 - 5.08 -

b 0.014 0.026 0.36 0.66 2

b1 0.014 0.023 0.36 0.58 3

b2 0.045 0.065 1.14 1.65 b3 0.023 0.045 0.58 1.14 4

c 0.008 0.018 0.20 0.46 2

c1 0.008 0.015 0.20 0.38 3

D - 0.840 - 21.34 5

E 0.220 0.310 5.59 7.87 5

e 0.100 BSC 2.54 BSC eA 0.300 BSC 7.62 BSC -

eA/2 0.150 BSC 3.81 BSC -

L 0.125 0.200 3.18 5.08 -

Q 0.015 0.060 0.38 1.52 6

S1 0.005 - 0.13 - 7

o

α

90

105

o

90

o

105

aaa - 0.015 - 0.38 bbb - 0.030 - 0.76 -

ccc - 0.010 - 0.25 -

M - 0.0015 - 0.038 2, 3

N16 168

NOTESMIN MAX MIN MAX

o

Rev. 0 4/94

-

9

Page 10

CD4049UB, CD4050B

Small Outline Plastic Packages (SOIC)

N

INDEX

AREA

123

-A-

E

-B-

SEATING PLANE

D

A

-C-

0.25(0.010) BM M

H

L

h x 45

o

α

e

B

0.25(0.010) C AM BS

M

NOTES:

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006

inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Interlead

flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater above

the seating plane, shall not exceed a maximum value of 0.61mm (0.024

inch)

10. Controlling dimension: MILLIMETER. Converted inch dimensions are

not necessarily exact.

A1

C

0.10(0.004)

M16.3 (JEDEC MS-013-AA ISSUE C)

16 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.0926 0.1043 2.35 2.65 -

A1 0.0040 0.0118 0.10 0.30 -

B 0.013 0.0200 0.33 0.51 9

C 0.0091 0.0125 0.23 0.32 D 0.3977 0.4133 10.10 10.50 3

E 0.2914 0.2992 7.40 7.60 4

e 0.050 BSC 1.27 BSC H 0.394 0.419 10.00 10.65 h 0.010 0.029 0.25 0.75 5

L 0.016 0.050 0.40 1.27 6

N16 167

o

α

0

o

8

o

0

NOTESMIN MAX MIN MAX

o

8

-

Rev. 0 12/93

10

Page 11

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

Loading...

Loading...