Texas Instruments CC2420 Datasheet

CC2420

2.4 GHz IEEE 802.15.4 / ZigBee-ready RF Transceiver

Applications

2.4 GHz IEEE 802.15.4 systems

ZigBee systems

Home/building automation

Industrial Control

Product Description

The

CC2420

IEEE 802.15.4 compliant RF transceiver

designed for low power and low voltage

wireless applications.

digital direct sequence spread spectrum

baseband modem providing a spreading

gain of 9 dB and an effective data rate of

250 kbps.

CC2420

The

solution for robust wireless communication

in the 2.4 GHz unlicensed ISM band. It

complies with worldwide regulations

covered by ETSI EN 300 328 and EN 300

440 class 2 (Europe), FCC CFR47 Part 15

(US) and ARIB STD-T66 (Japan).

is a true single-chip 2.4 GHz

CC2420

is a low-cost, highly integrated

includes a

Wireless sensor networks

PC peripherals

Consumer Electronics

features reduce the load on the host

controller and allow

low-cost microcontrollers.

The configuration interface and transmit /

receive FIFOs of

an SPI interface. In a typical application

CC2420

microcontroller and a few external passive

components.

CC2420

03 technology in 0.18 m CMOS.

will be used together with a

is based on Chipcon’s SmartRF-

CC2420

CC2420

to interface

are accessed via

CC2420

The

support for packet handling, data

buffering, burst transmissions, data

encryption, data authentication, clear

channel assessment, link quality indication

and packet timing information. These

provides extensive hardware

Key Features

True single-chip 2.4 GHz IEEE

802.15.4 compliant RF transceiver

with baseband modem and MAC

support

DSSS baseband modem with 2

MChips/s and 250 kbps effective data

rate.

Suitable for both RFD and FFD

operation

Low current consumption (RX: 18.8

mA, TX: 17.4 mA)

Low supply voltage (2.1 – 3.6 V) with

integrated voltage regulator

Low supply voltage (1.6 – 2.0 V) with

external voltage regulator

Programmable output power

No external RF switch / filter needed

I/Q low-IF receiver

I/Q direct upconversion transmitter

Very few external components

128(RX) + 128(TX) byte data buffering

Digital RSSI / LQI support

Hardware MAC encryption (AES-128)

Battery monitor

QLP-48 package, 7x7 mm

Complies with ETSI EN 300 328, EN

300 440 class 2, FCC CFR-47 part 15

and ARIB STD-T66

Powerful and flexible development

tools available

SWRS041B Page 1 of 89

CC2420

Table of contents

1 Abbreviations_________________________________________________________________5

2 References ___________________________________________________________________6

3 Features _____________________________________________________________________7

4 Absolute Maximum Ratings_____________________________________________________8

5 Operating Conditions __________________________________________________________8

6 Electrical Specifications ________________________________________________________ 9

6.1 Overall___________________________________________________________________9

6.2 Transmit Section ___________________________________________________________9

6.3 Receive Section___________________________________________________________ 10

6.4 RSSI / Carrier Sense _______________________________________________________11

6.5 IF Section _______________________________________________________________11

6.6 Frequency Synthesizer Section _______________________________________________11

6.7 Digital Inputs/Outputs______________________________________________________12

6.8 Voltage Regulator _________________________________________________________13

6.9 Battery Monitor___________________________________________________________13

6.10 Power Supply ____________________________________________________________13

7 Pin Assignment ______________________________________________________________15

8 Circuit Description ___________________________________________________________17

9 Application Circuit ___________________________________________________________19

9.1 Input / output matching_____________________________________________________19

9.2 Bias resistor______________________________________________________________19

9.3 Crystal __________________________________________________________________19

9.4 Voltage regulator__________________________________________________________19

9.5 Power supply decoupling and filtering _________________________________________19

10 IEEE 802.15.4 Modulation Format ____________________________________________24

11 Configuration Overview _____________________________________________________25

12 Evaluation Software ________________________________________________________26

13 4-wire Serial Configuration and Data Interface__________________________________27

13.1 Pin configuration__________________________________________________________27

13.2 Register access____________________________________________________________27

13.3 Status byte_______________________________________________________________28

13.4 Command strobes _________________________________________________________29

13.5 RAM access______________________________________________________________29

13.6 FIFO access______________________________________________________________31

13.7 Multiple SPI access ________________________________________________________31

14 Microcontroller Interface and Pin Description __________________________________32

14.1 Configuration interface _____________________________________________________32

14.2 Receive mode ____________________________________________________________33

14.3 RXFIFO overflow _________________________________________________________33

14.4 Transmit mode____________________________________________________________34

14.5 General control and status pins _______________________________________________35

15 Demodulator, Symbol Synchroniser and Data Decision ___________________________35

16 Frame Format _____________________________________________________________36

16.1 Synchronisation header _____________________________________________________36

16.2 Length field______________________________________________________________37

16.3 MAC protocol data unit_____________________________________________________37

16.4 Frame check sequence______________________________________________________38

SWRS041B Page 2 of 89

CC2420

17 RF Data Buffering__________________________________________________________39

17.1 Buffered transmit mode_____________________________________________________39

17.2 Buffered receive mode _____________________________________________________39

17.3 Unbuffered, serial mode ____________________________________________________40

18 Address Recognition ________________________________________________________41

19 Acknowledge Frames _______________________________________________________41

20 Radio control state machine__________________________________________________43

21 MAC Security Operations (Encryption and Authentication) _______________________45

21.1 Keys____________________________________________________________________45

21.2 Nonce / counter ___________________________________________________________45

21.3 Stand-alone encryption _____________________________________________________46

21.4 In-line security operations___________________________________________________46

21.5 CTR mode encryption / decryption____________________________________________47

21.6 CBC-MAC_______________________________________________________________47

21.7 CCM ___________________________________________________________________47

21.8 Timing__________________________________________________________________48

22 Linear IF and AGC Settings__________________________________________________48

23 RSSI / Energy Detection _____________________________________________________48

24 Link Quality Indication _____________________________________________________49

25 Clear Channel Assessment ___________________________________________________50

26 Frequency and Channel Programming_________________________________________50

27 VCO and PLL Self-Calibration _______________________________________________51

27.1 VCO____________________________________________________________________51

27.2 PLL self-calibration________________________________________________________51

28 Output Power Programming _________________________________________________51

29 Voltage Regulator __________________________________________________________51

30 Battery Monitor____________________________________________________________52

31 Crystal Oscillator __________________________________________________________53

32 Input / Output Matching ____________________________________________________54

33 Transmitter Test Modes _____________________________________________________54

33.1 Unmodulated carrier _______________________________________________________54

33.2 Modulated spectrum _______________________________________________________55

34 System Considerations and Guidelines _________________________________________57

34.1 Frequency hopping and multi-channel systems___________________________________57

34.2 Data burst transmissions ____________________________________________________57

34.3 Crystal accuracy and drift ___________________________________________________57

34.4 Communication robustness __________________________________________________57

34.5 Communication security ____________________________________________________57

34.6 Low-cost systems _________________________________________________________58

34.7 Battery operated systems____________________________________________________58

34.8 BER / PER measurements___________________________________________________58

35 PCB Layout Recommendations _______________________________________________59

36 Antenna Considerations _____________________________________________________59

37 Configuration Registers _____________________________________________________61

38 Test Output Signals_________________________________________________________81

39 Package Description (QLP 48)________________________________________________83

40 Recommended layout for package (QLP 48) ____________________________________84

SWRS041B Page 3 of 89

CC2420

40.1 Package thermal properties __________________________________________________84

40.2 Soldering information ______________________________________________________84

40.3 Plastic tube specification____________________________________________________85

40.4 Carrier tape and reel specification_____________________________________________85

41 Ordering Information_______________________________________________________85

42 General Information ________________________________________________________86

42.1 Document History_________________________________________________________86

42.2 Product Status Definitions___________________________________________________87

43 Address Information________________________________________________________88

44 TI Worldwide Technical Support _____________________________________________88

SWRS041B Page 4 of 89

CC2420

1 Abbreviations

ADC - Analog to Digital Converter

AES - Advanced Encryption Standard

AGC - Automatic Gain Control

ARIB - Association of Radio Industries and Businesses

BER - Bit Error Rate

CBC-MAC - Cipher Block Chaining Message Authentication Code

CCA - Clear Channel Assessment

CCM - Counter mode + CBC-MAC

CFR - Code of Federal Regulations

CSMA-CA - Carrier Sense Multiple Access with Collision Avoidance

CTR - Counter mode (encryption)

CW - Continuous Wave

DAC - Digital to Analog Converter

DSSS - Direct Sequence Spread Spectrum

ESD - Electro Static Discharge

ESR - Equivalent Series Resistance

EVM - Error Vector Magnitude

FCC - Federal Communications Commission

FCF - Frame Control Field

FIFO - First In First Out

FFCTRL - FIFO and Frame Control

HSSD - High Speed Serial Debug

IEEE - Institute of Electrical and Electronics Engineers

IF - Intermediate Frequency

ISM - Industrial, Scientific and Medical

ITU-T - International Telecommunication Union – Telecommunication

Standardization Sector

I/O - Input / Output

I/Q - In-phase / Quadrature-phase

kbps - kilo bits per second

LNA - Low-Noise Amplifier

LO - Local Oscillator

LQI - Link Quality Indication

LSB - Least Significant Bit / Byte

MAC - Medium Access Control

MFR - MAC Footer

MHR - MAC Header

MIC - Message Integrity Code

MPDU - MAC Protocol Data Unit

MSDU - MAC Service Data Unit

NA - Not Available

NC - Not Connected

O-QPSK - Offset - Quadrature Phase Shift Keying

PA - Power Amplifier

PCB - Printed Circuit Board

PER - Packet Error Rate

PHY - Physical Layer

PHR - PHY Header

PLL - Phase Locked Loop

PSDU - PHY Service Data Unit

QLP - Quad Leadless Package

RAM - Random Access Memory

RBW - Resolution BandWidth

RF - Radio Frequency

RSSI - Receive Signal Strength Indicator

RX - Receive

SWRS041B Page 5 of 89

CC2420

SHR - Synchronisation Header

SPI - Serial Peripheral Interface

TBD - To Be Decided / To Be Defined

T/R - Transmit / Receive

TX - Transmit

VCO - Voltage Controlled Oscillator

VGA - Variable Gain Amplifier

2 References

[1] IEEE std. 802.15.4 - 2003: Wireless Medium Access Control (MAC) and

Physical Layer (PHY) specifications for Low Rate Wireless Personal Area

Networks (LR-WPANs)

http://standards.ieee.org/getieee802/download/802.15.4-2003.pdf

[2] NIST FIPS Pub 197: Advanced Encryption Standard (AES), Federal

Information Processing Standards Publication 197, US Department of

Commerce/N.I.S.T., November 26, 2001. Available from the NIST website.

http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf

[3] R. Housley, D. Whiting, N. Ferguson, Counter with CBC-MAC (CCM),

submitted to NIST, June 3, 2002. Available from the NIST website.

http://csrc.nist.gov/CryptoToolkit/modes/proposedmodes/ProposedModesPa

ge.html

SWRS041B Page 6 of 89

3 Features

CC2420

2400 – 2483.5 MHz RF Transceiver

Direct Sequence Spread

Spectrum (DSSS) transceiver

250 kbps data rate, 2 MChip/s

chip rate

O-QPSK with half sine pulse

shaping modulation

Very low current consumption

(RX: 18.8 mA, TX: 17.4 mA)

High sensitivity (-95 dBm)

High adjacent channel rejection

(30/45 dB)

High alternate channel rejection

(53/54 dB)

On-chip VCO, LNA and PA

Low supply voltage (2.1 – 3.6 V)

with on-chip voltage regulator

Programmable output power

I/Q low-IF soft decision receiver

I/Q direct up-conversion

transmitter

Separate transmit and receive FIFOs

128 byte transmit data FIFO

128 byte receive data FIFO

Very few external components

Only reference crystal and a

minimised number of passives

No external filters needed

Easy configuration interface

4-wire SPI interface

Serial clock up to 10 MHz

802.15.4 MAC hardware support:

Automatic preamble generator

Synchronisation word

insertion/detection

CRC-16 computation and

checking over the MAC payload

Clear Channel Assessment

Energy detection / digital RSSI

Link Quality Indication

Full automatic MAC security

(CTR, CBC-MAC, CCM)

802.15.4 MAC hardware security:

Automated security operations

within the receive and transmit

FIFOs.

CTR mode encryption / decryption

CBC-MAC authentication

CCM encryption / decryption and

authentication

Stand-alone AES encryption

Development tools available

Fully equipped development kit

Demonstration board reference

design with microcontroller code

Easy-to-use software for

generating the

ration data

Small size QLP-48 package, 7 x 7 mm

Complies with EN 300 328, EN 300

440 class 2, FCC CFR47 part 15 and

ARIB STD-T66

CC2420

configu-

SWRS041B Page 7 of 89

CC2420

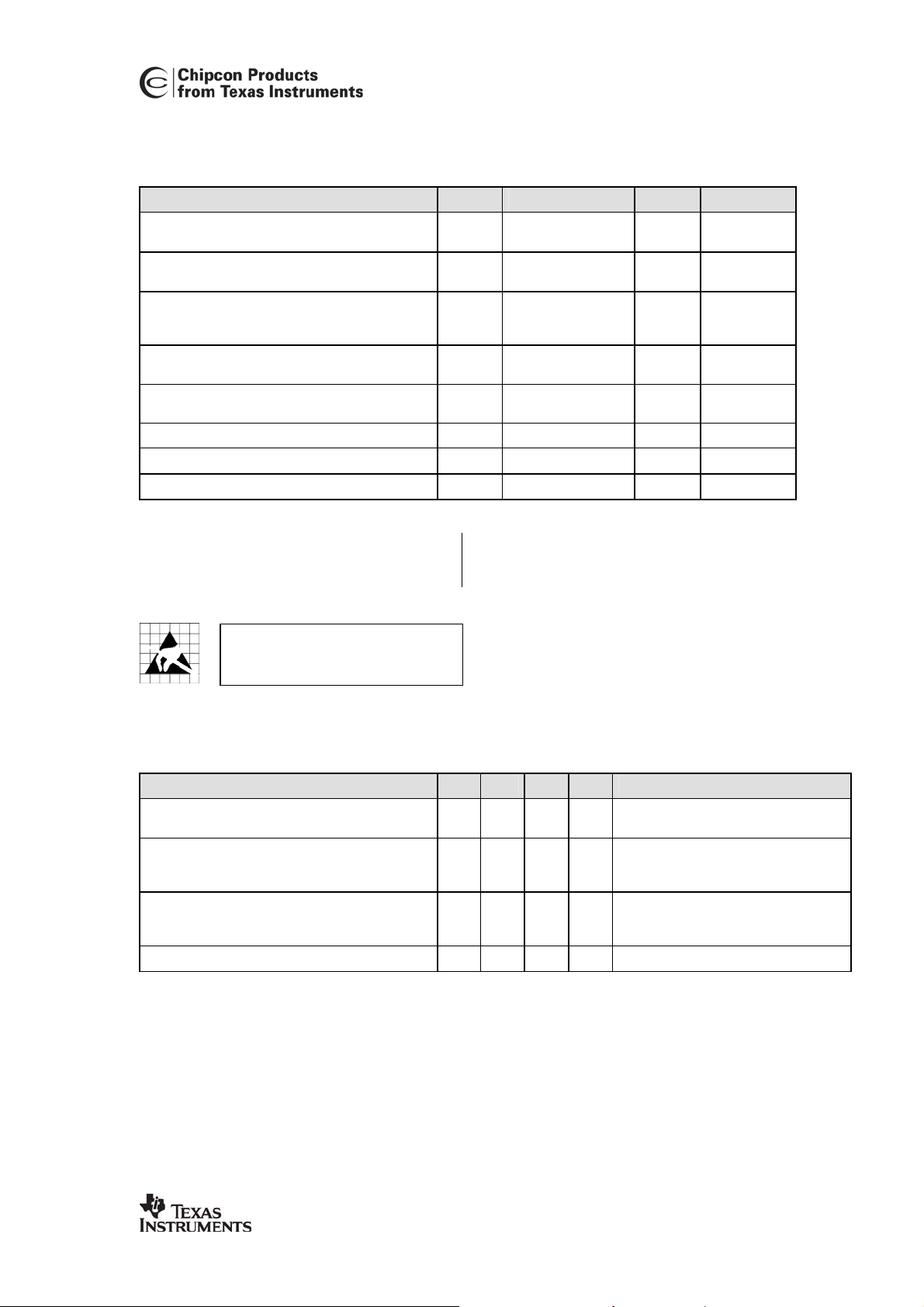

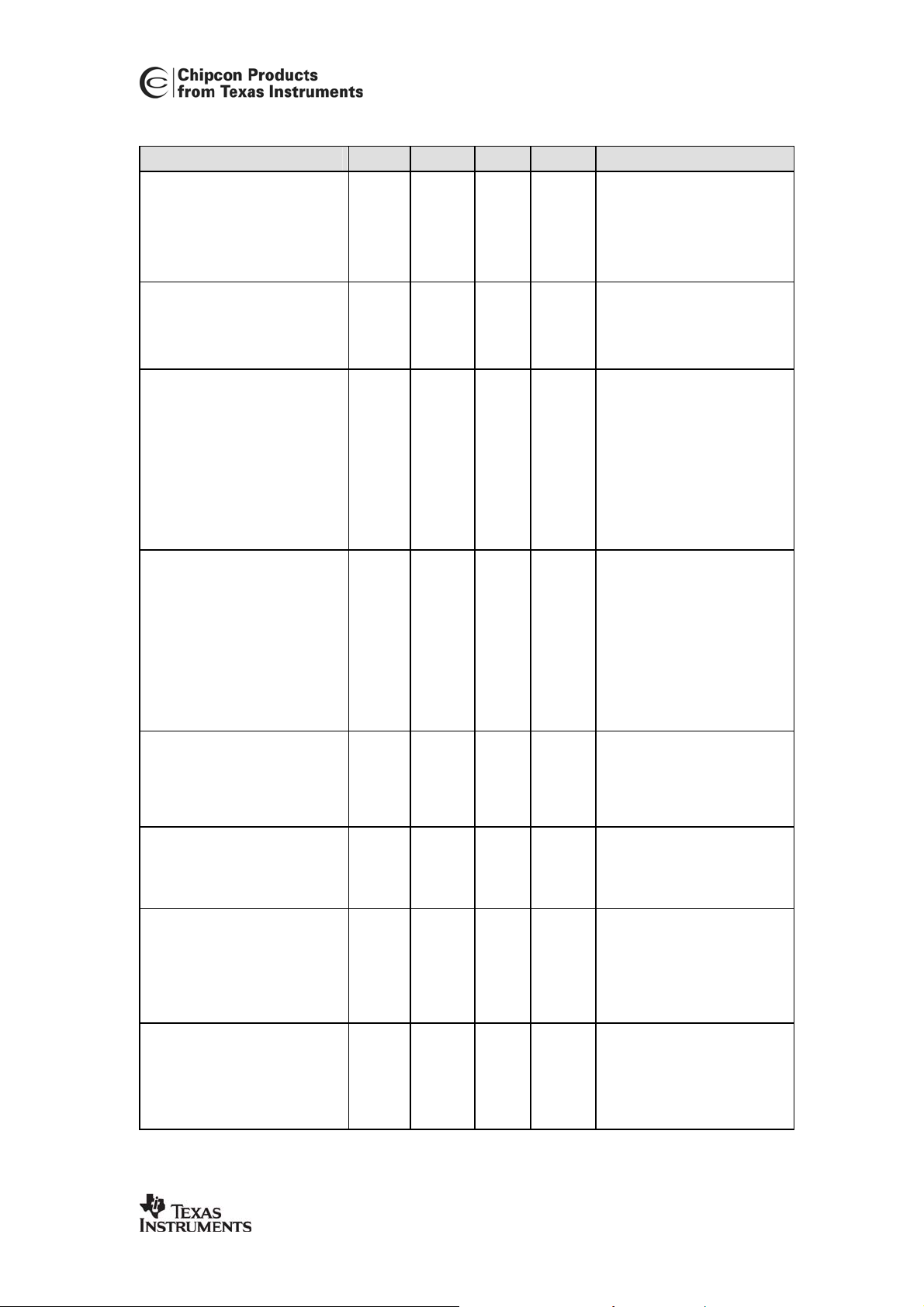

4 Absolute Maximum Ratings

Parameter Min. Max. Units Condition

Supply voltage for on-chip voltage regulator,

VREG_IN pin 43.

Supply voltage (VDDIO) for digital I/Os, DVDD3.3,

pin 25.

Supply voltage (VDD) on AVDD_VCO, DVDD1.8,

etc (pin no 1, 2, 3, 4, 10, 14, 15, 17, 18, 20, 26, 35,

37, 44 and 48)

Voltage on any digital I/O pin, (pin no. 21, 27-34

and 41)

Voltage on any other pin, (pin no. 6, 7, 8, 11, 12,

13, 16, 36, 38, 39, 40, 45, 46 and 47)

Input RF level 10 dBm

Storage temperature range −50 150

Reflow solder temperature 260

-0.3 3.6 V

-0.3 3.6 V

−0.3 2.0 V

-0.3 VDDIO+0.3, max 3.6 V

-0.3 VDD+0.3, max 2.0 V

C

C

T = 10 s

The absolute maximum ratings given

above should under no circumstances be

the limiting values may cause permanent

damage to the device.

violated. Stress exceeding one or more of

Caution! ESD sensitive device.

Precaution should be used when handling

the device in order to prevent permanent

damage.

5 Operating Conditions

Parameter Min. Typ. Max. Units Condition

Supply voltage for on-chip voltage regulator,

VREG_IN pin 43.

Supply voltage (VDDIO) for digital I/Os, DVDD3.3,

pin 25 .

Supply voltage (VDD) on AVDD_VCO, DVDD1.8,

etc (pin no 1, 2, 3, 4, 10, 14, 15, 17, 18, 20, 26, 35,

37, 44 and 48)

Operating ambient temperature range, TA −40 85

2.1 3.6 V

1.6 3.6 V The digital I/O voltage (DVDD3.3 pin)

1.6 1.8 2.0 V The typical application uses regulated

must match the external interfacing

circuit (e.g. microcontroller).

1.8 V supply generated by the on-chip

voltage regulator.

C

SWRS041B Page 8 of 89

CC2420

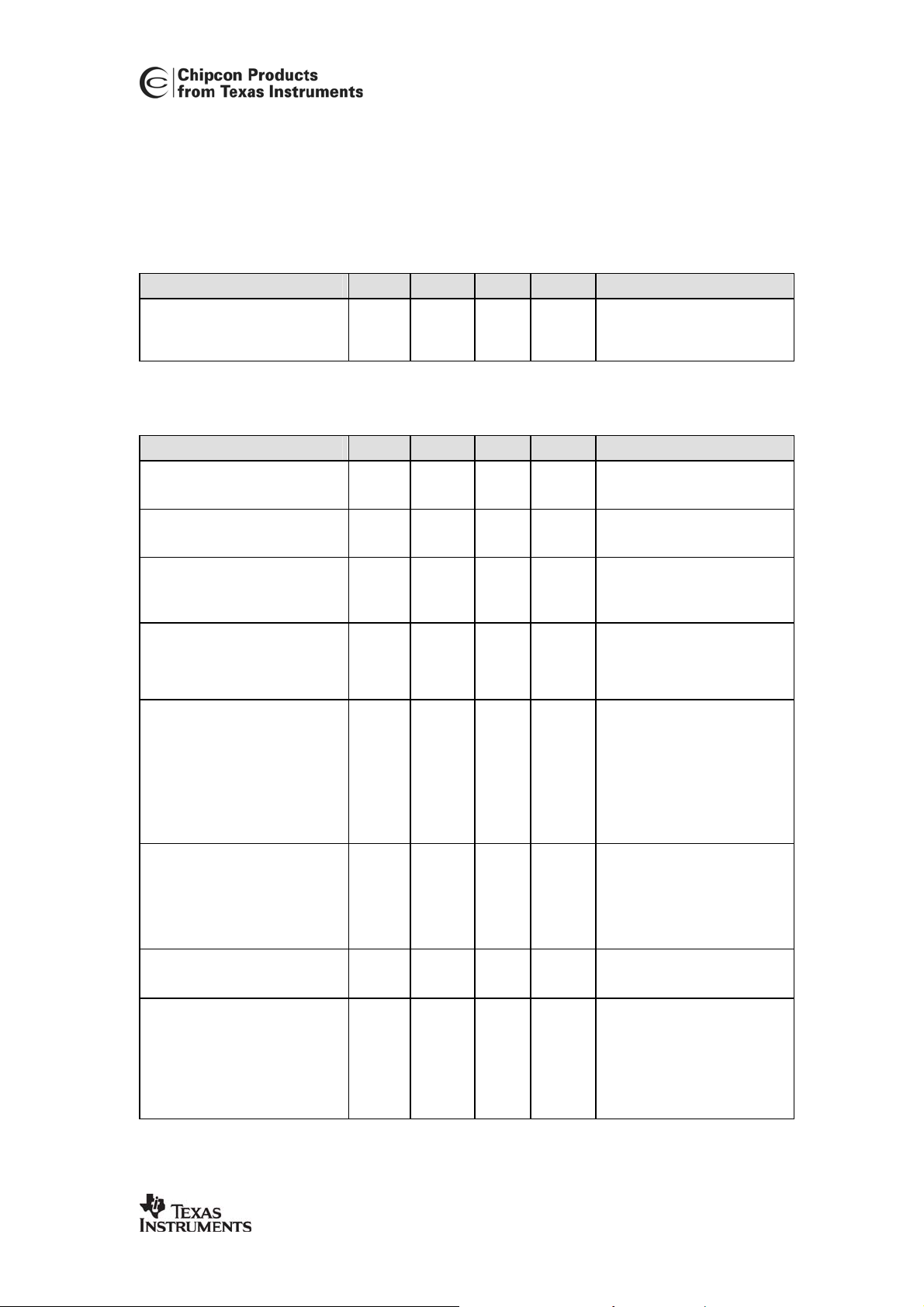

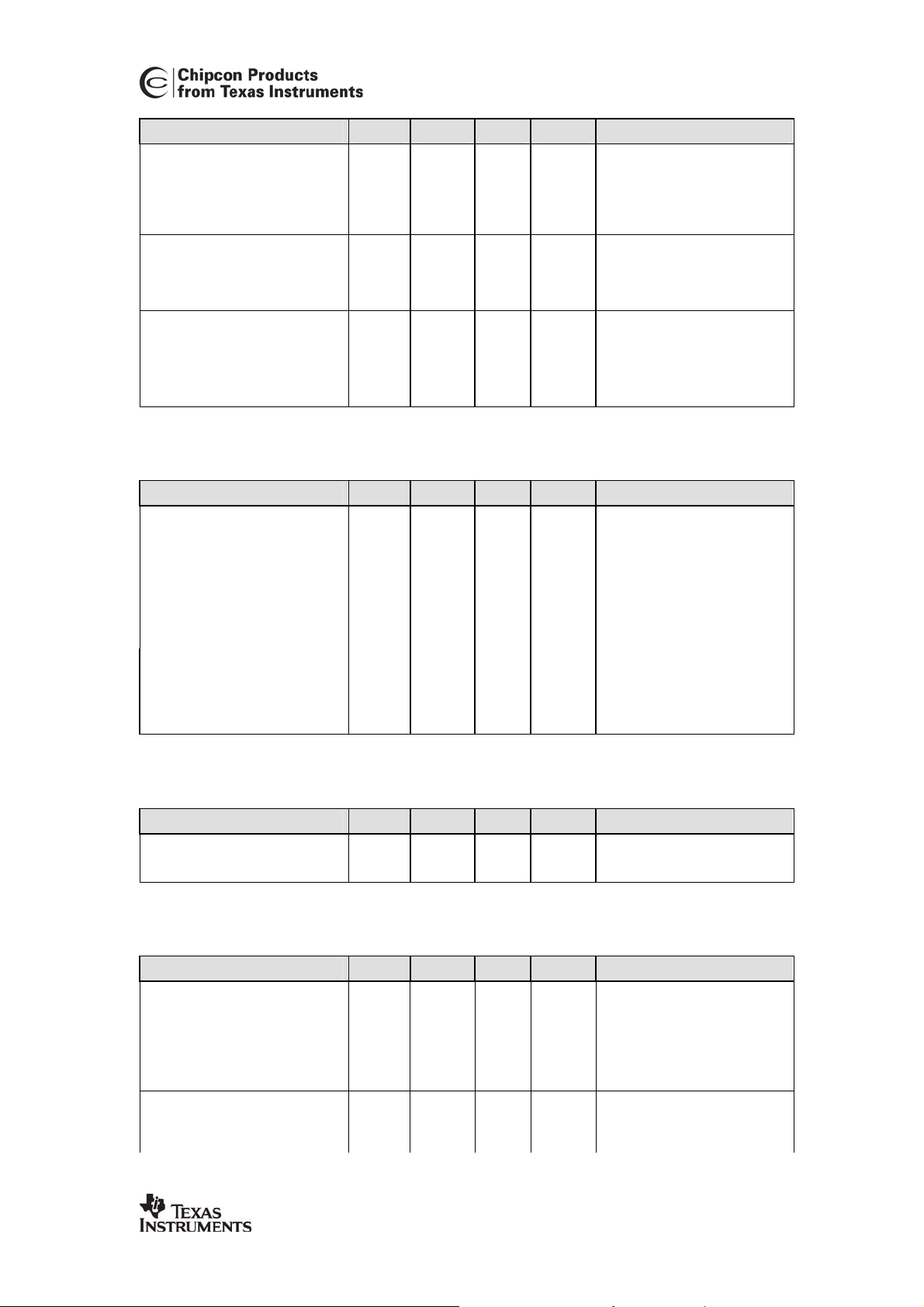

6 Electrical Specifications

Measured on CC2420 EM with transmission line balun, TA = 25 C, DVDD3.3 and VREG_IN = 3.3 V, internal

voltage regulator used if nothing else stated.

6.1 Overall

Parameter Min. Typ. Max. Unit Condition / Note

RF Frequency Range 2400 2483.5 MHz Programmable in 1 MHz steps, 5

6.2 Transmit Section

Parameter Min. Typ. Max. Unit Condition / Note

Transmit bit rate 250

Transmit chip rate

Nominal output power -3 0 dBm

2000 2000 kChips/s As defined by [1]

250 kbps As defined by [1]

MHz steps for compliance with [1]

Delivered to a single ended 50

load through a balun.

[1] requires minimum –3 dBm

Programmable output power range

Harmonics

nd

harmonic

2

rd

harmonic

3

Spurious emission

30 - 1000 MHz

1– 12.75 GHz

1.8 – 1.9 GHz

5.15 – 5.3 GHz

Error Vector Magnitude (EVM) 11 % Measured as defined by [1]

Optimum load impedance 95

24 dB The output power is

-44

-64

-56

-44

-56

-51

+ j187

programmable in 8 steps from

approximately –24 to 0 dBm.

dBm

dBm

dBm

dBm

dBm

dBm

Measured conducted with 1 MHz

resolution bandwidth on spectrum

analyser. At max output power

delivered to a single ended 50

load through a balun. See page

54.

Maximum output power.

Complies with EN 300 328, EN

300 440, FCC CFR47 Part 15

and ARIB STD-T-66

[1] requires max. 35 %

Differential impedance as seen

from the RF-port (RF_P and

RF_N) towards the antenna. For

matching details see the Input /

Output Matching section on page

54.

SWRS041B Page 9 of 89

CC2420

6.3 Receive Section

Parameter Min. Typ. Max. Unit Condition / Note

Receiver Sensitivity

Saturation (maximum input level) 0 10 dBm PER = 1%, as specified by [1]

Adjacent channel rejection

+ 5 MHz channel spacing

Adjacent channel rejection

- 5 MHz channel spacing

Alternate channel rejection

+ 10 MHz channel spacing

Alternate channel rejection

- 10 MHz channel spacing

Channel rejection

≥ + 15 MHz

≤ - 15 MHz

Co-channel rejection

Blocking / Desensitisation

+/- 5 MHz from band edge

+/- 20 MHz from band edge

+/- 30 MHz from band edge

+/- 50 MHz from band edge

Spurious emission

30 – 1000 MHz

1 – 12.75 GHz

-90

-95

45

30

54

53

62

62

-3

-28

-28

-27

-28

-73

-58

dBm

dB

dB

dB

dB

dB

dB

dB

dBm

dBm

dBm

dBm

dBm

dBm

PER = 1%, as specified by [1]

Measured in a 50 single-ended

load through a balun.

[1] requires –85 dBm

Measured in a 50 single–ended

load through a balun.

[1] requires –20 dBm

Wanted signal @ -82 dBm,

adjacent modulated channel at

+5 MHz, PER = 1 %, as specified

by [1].

[1] requires 0 dB

Wanted signal @ -82 dBm,

adjacent modulated channel at

-5 MHz, PER = 1 %, as specified

by [1].

[1] requires 0 dB

Wanted signal @ -82 dBm,

adjacent modulated channel at

+10 MHz, PER = 1 %, as

specified by [1]

[1] requires 30 dB

Wanted signal @ -82 dBm,

adjacent modulated channel at

-10 MHz, PER = 1 %, as

specified by [1]

[1] requires 30 dB

Wanted signal @ -82 dBm.

Undesired signal is an IEEE

802.15.4 modulated channel,

stepped through all channels

from 2405 to 2480 MHz. Signal

level for PER = 1%.

Wanted signal @ -82 dBm.

Undesired signal is an IEEE

802.15.4 modulated at the same

frequency as the desired signal.

Signal level for PER = 1%.

Wanted signal 3 dB above the

sensitivity level, CW jammer,

PER = 1%. Complies with EN

300 440 class 2.

Conducted measurement in a 50

single ended load. Measured

according to EN 300 328, EN 300

440 class 2, FCC CFR47, Part 15

and ARIB STD-T-66

SWRS041B Page 10 of 89

CC2420

Parameter Min. Typ. Max. Unit Condition / Note

Frequency error tolerance -300 300 kHz Difference between centre

Symbol rate error tolerance 120 ppm Difference between incoming

Data latency 3

s

6.4 RSSI / Carrier Sense

Parameter Min. Typ. Max. Unit Condition / Note

Carrier sense level

RSSI dynamic range

RSSI accuracy

RSSI linearity

RSSI average time 128

− 77 dBm Programmable in

100 dB The range is approximately from

6

3

dB See page 48 for details

dB

s

frequency of the received RF

signal and local oscillator

frequency

[1] requires 200 kHz

symbol rate and the internally

generated symbol rate

[1] requires 80 ppm

Processing delay in receiver.

Time from complete transmission

of SFD until complete reception

of SFD, i.e. from SFD goes active

on transmitter until active on

receiver.

RSSI.CCA_THR

–100 dBm to 0 dBm

8 symbol periods, as specified by

[1]

6.5 IF Section

Parameter Min. Typ. Max. Unit Condition / Note

Intermediate frequency (IF) 2 MHz

6.6 Frequency Synthesizer Section

Parameter Min. Typ. Max. Unit Condition / Note

Crystal oscillator frequency

Crystal frequency accuracy

requirement

Crystal operation

16 MHz See page 53 for details.

- 40

Parallel

SWRS041B Page 11 of 89

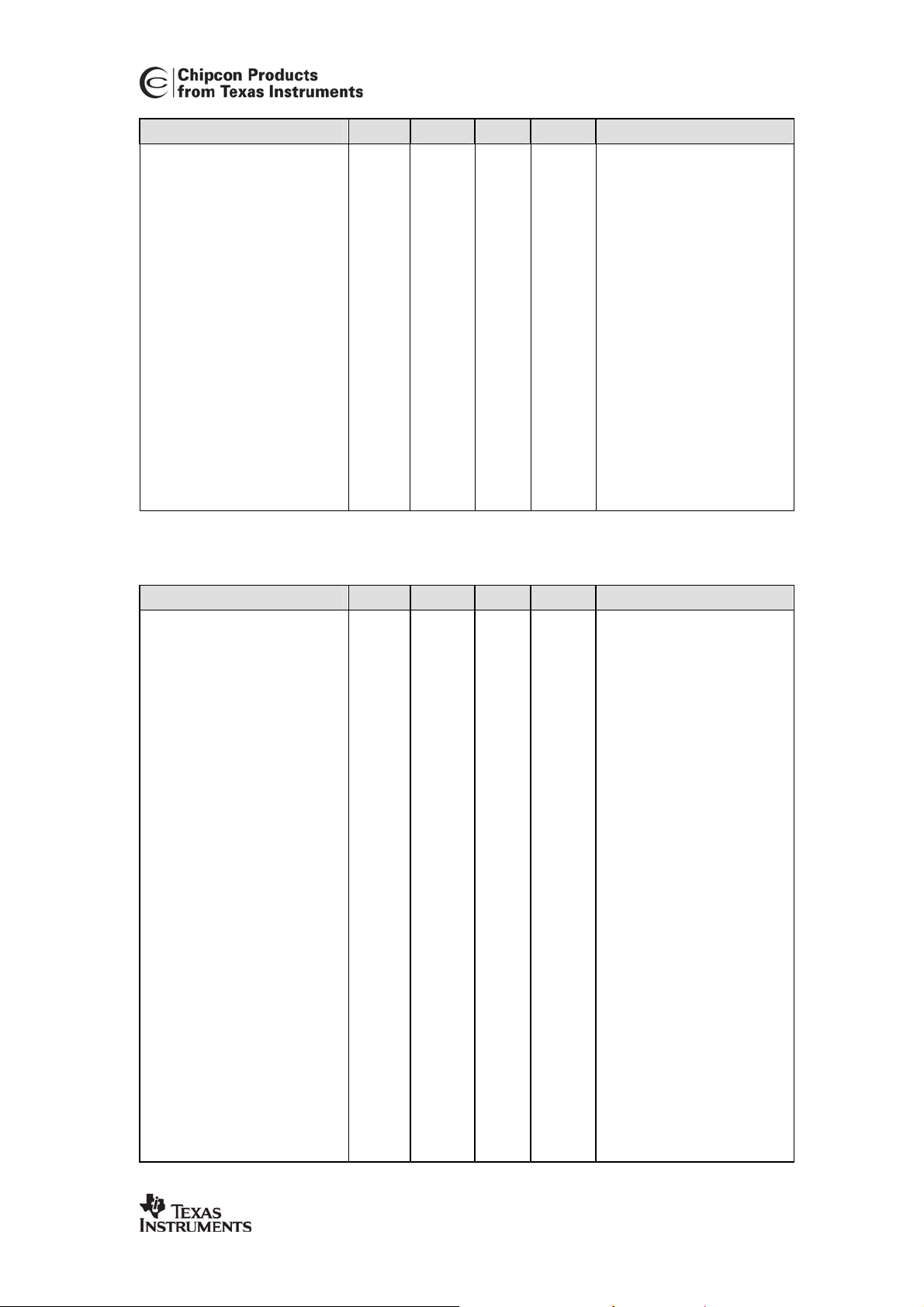

40 ppm Including aging and temperature

dependency, as specified by [1]

C381 and C391 are loading

capacitors, see page 53

CC2420

Parameter Min. Typ. Max. Unit Condition / Note

Crystal load capacitance

Crystal ESR

Crystal oscillator start-up time 1.0 ms

Phase noise

PLL loop bandwidth 100 kHz

12 16 20 pF 16 pF recommended

60

−109

−117

−117

−117

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

16 pF load

Unmodulated carrier

At ±1 MHz offset from carrier

At ±2 MHz offset from carrier

At ±3 MHz offset from carrier

At ±5 MHz offset from carrier

PLL lock time

192

s

The startup time from the crystal

oscillator is running and RX / TX

turnaround time

6.7 Digital Inputs/Outputs

Parameter Min. Typ. Max. Unit Condition / Note

General

Logic "0" input voltage

Logic "1" input voltage

Logic "0" output voltage 0

Logic "1" output voltage 2.5

Logic "0" input current

Logic "1" input current

FIFO setup time 20 ns TX unbuffered mode, minimum

FIFO hold time

Serial interface pins (SCLK, SI, SO

and CSn) timing specification

0 0.3*

0.7*

DVDD

NA −1

NA 1

10 ns TX unbuffered mode, minimum

See Table 4 on page 28

DVDD V

0.4 V Output current −8 mA,

VDD V Output current 8 mA,

DVDD

V

A

A

Signal levels are referred to the

voltage level at pin DVDD3.3

3.3 V supply voltage

3.3 V supply voltage

Input signal equals GND

Input signal equals VDD

time FIFO must be ready before

the positive edge of FIFOP

time FIFO must be held after the

positive edge of FIFOP

SWRS041B Page 12 of 89

CC2420

6.8 Voltage Regulator

Parameter Min. Typ. Max. Unit Condition / Note

General

Input Voltage

Output Voltage

Quiescent current

Start-up time

6.9 Battery Monitor

2.1 3.0 3.6 V On the VREG_IN pin

1.7 1.8 1.9 V On the VREG_OUT pin

13 20 29

0.3 0.6 ms

A

Note that the internal voltage

regulator can only supply

CC2420 and no external circuitry.

No current drawn from the

VREG_OUT pin. Min and max

numbers include 2.1 through 3.6

V input voltage

Parameter Min. Typ. Max. Unit Condition / Note

Current consumption

Start-up time

Settling time

Step size

Hysteresis

Absolute accuracy

Relative accuracy

6 30 90

100

2

50 mV

10 mV

-80 80 mV May be software calibrated for

-50 50 mV

A

s

s

When enabled

Voltage regulator already enabled

New toggle voltage programmed

known reference voltage

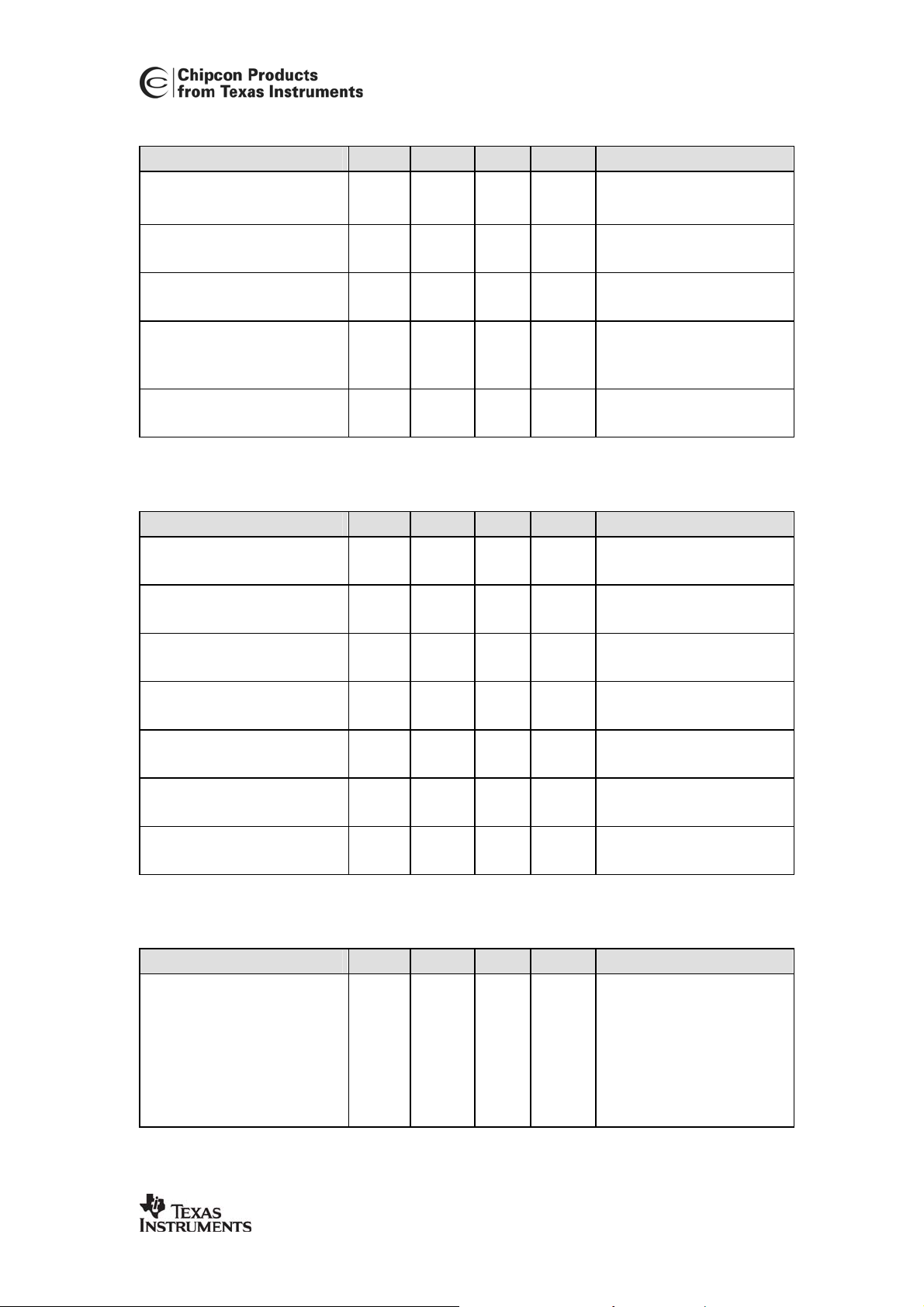

6.10 Power Supply

Parameter Min. Typ. Max. Unit Condition / Note

Current consumption in different

modes (see Figure 25, page 44)

Voltage regulator off (OFF)

Power Down mode (PD)

Idle mode (IDLE)

Current Consumption,

receive mode

0.02

20

426

18.8 mA

1

A

A

A

Current drawn from VREG_IN,

through voltage regulator

Voltage regulator off

Voltage regulator on

Including crystal oscillator and

voltage regulator

SWRS041B Page 13 of 89

CC2420

Parameter Min. Typ. Max. Unit Condition / Note

Current Consumption,

transmit mode:

P = -25 dBm

P = -15 dBm

P = -10 dBm

P = −5 dBm

P = 0 dBm

8.5

9.9

11

14

17.4

mA

mA

mA

mA

mA

The output power is delivered

differentially to a 50 singled

ended load through a balun, see

also page 54.

SWRS041B Page 14 of 89

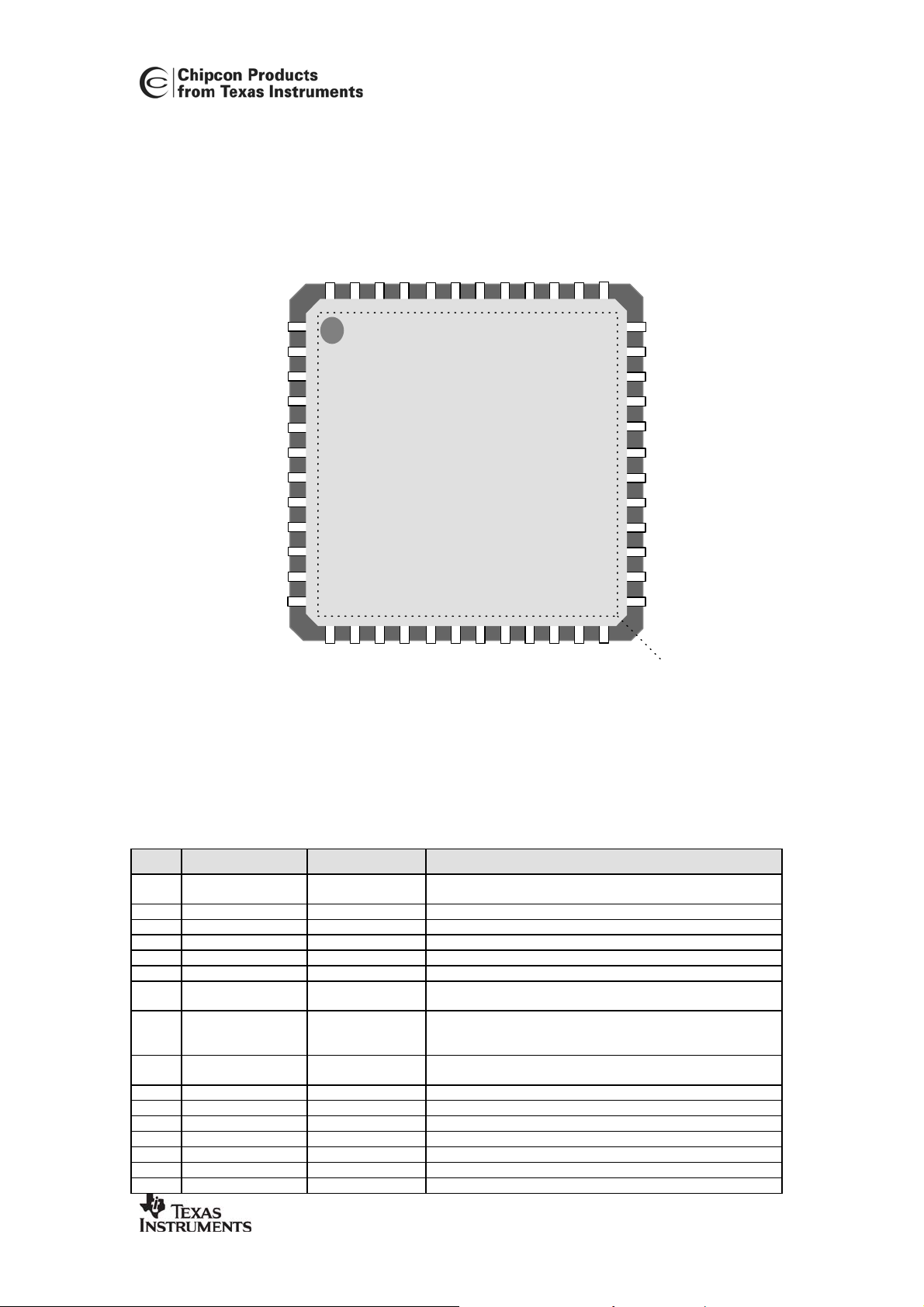

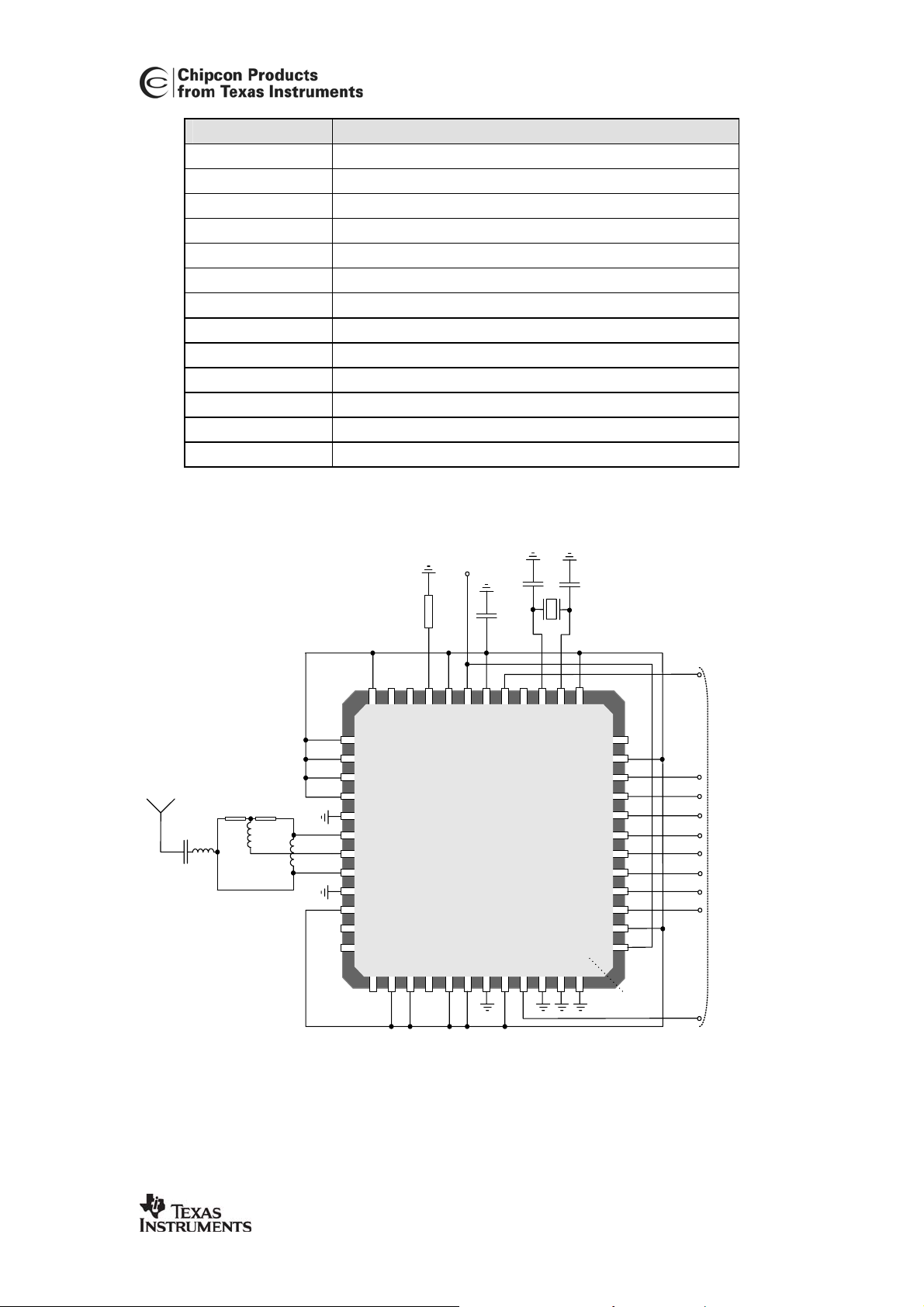

7 Pin Assignment

CC2420

VCO_GUARD

AVDD_VCO

AVDD_PRE

AVDD_RF1

GND

RF_P

TXRX_SWITCH

RF_N

GND

AVDD_SW

NC

NC

VREG_IN

43

QLP48

7x7

18

19

DVDD_ADC

DGND_GUARD

VREG_OUT

VREG_EN

42

41

20

DGUARD

NC

40

21

RESETn

XOSC16_Q1

39

22

DGND

ATEST2

ATEST1

AVDD_CHP

48

47

46

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

NC

AVDD_RF2

AVDD_IF2

AVDD_IF1

R_BIAS

45

44

CC2420

16

17

AVDD_ADC

NC

XOSC16_Q2

38

23

DSUB_PADS

AVDD_XOSC16

37

24

DSUB_CORE

36

35

34

33

32

31

30

29

28

27

26

25

AGND

Exposed die

attach pad

NC

DVDD_RAM

SO

SI

SCLK

CSn

FIFO

FIFOP

CCA

SFD

DVDD1.8

DVDD3.3

Figure 1.

CC2420

Pinout – Top View

Pin Pin Name Pin type Pin Description

-

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

AGND

VCO_GUARD

AVDD_VCO

AVDD_PRE

AVDD_RF1

GND

RF_P

TXRX_SWITCH

RF_N

GND

AVDD_SW

NC

NC

NC

AVDD_RF2

AVDD_IF2

Ground (analog) Exposed die attach pad. Must be connected to solid ground

plane

Power (analog) Connection of guard ring for VCO (to AVDD) shielding

Power (analog) 1.8 V Power supply for VCO

Power (analog) 1.8 V Power supply for Prescaler

Power (analog) 1.8 V Power supply for RF front-end

Ground (analog) Grounded pin for RF shielding

RF I/O Positive RF input/output signal to LNA/from PA in

receive/transmit mode

Power (analog) Common supply connection for integrated RF front-end. Must

be connected to RF_P and RF_N externally through a DC

path

RF I/O Negative RF input/output signal to LNA/from PA in

receive/transmit mode

Ground (analog) Grounded pin for RF shielding

Power (analog) 1.8 V Power supply for LNA / PA switch

- Not Connected

- Not Connected

- Not Connected

Power (analog) 1.8 V Power supply for receive and transmit mixers

Power (analog) 1.8 V Power supply for transmit / receive IF chain

SWRS041B Page 15 of 89

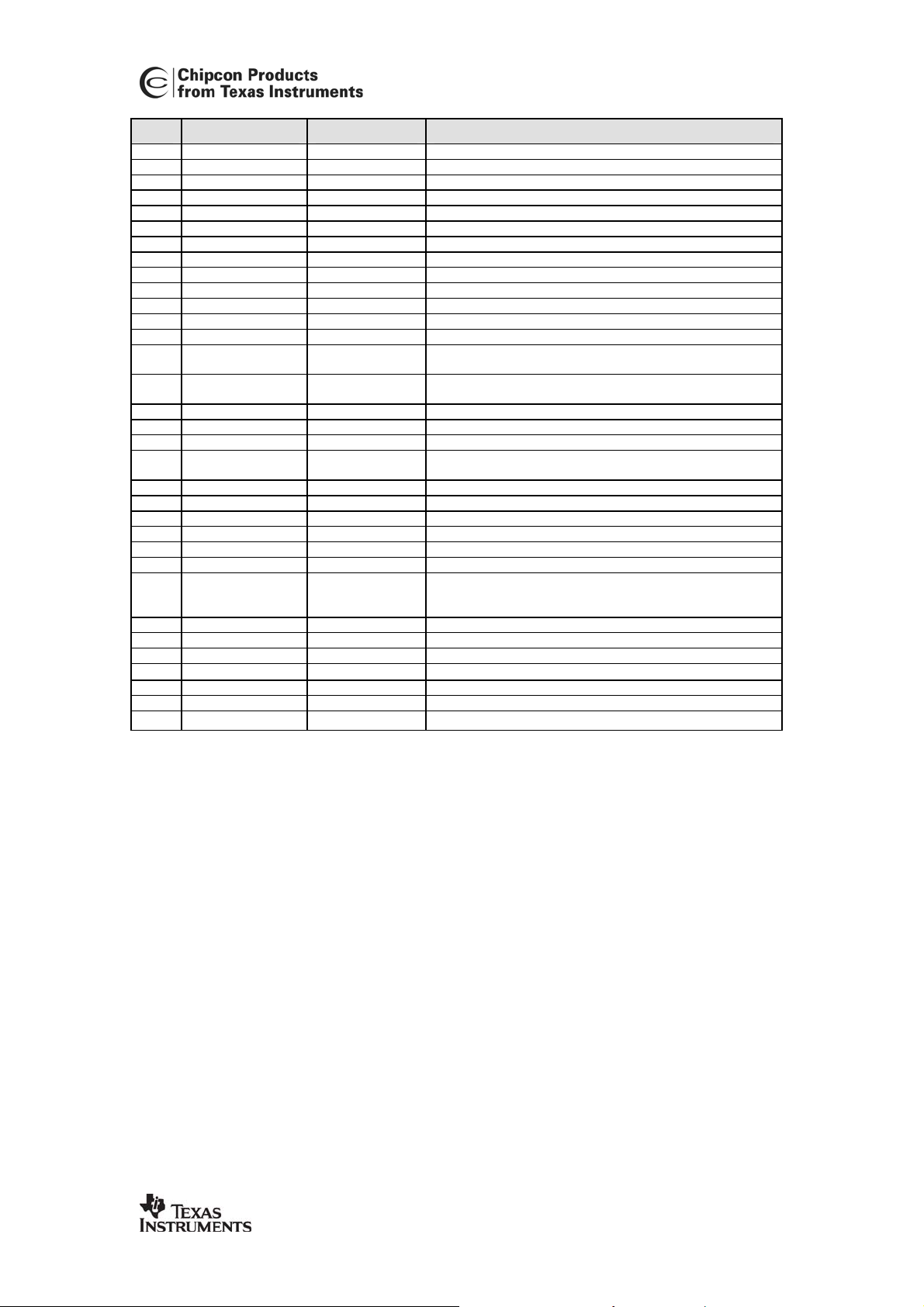

CC2420

Pin Pin Name Pin type Pin Description

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

NOTES:

The exposed die attach pad must be connected to a solid ground plane as this is the main ground connection for the

chip.

NC

AVDD_ADC

DVDD_ADC

DGND_GUARD

DGUARD

RESETn

DGND

DSUB_PADS

DSUB_CORE

DVDD3.3

DVDD1.8

SFD

CCA

FIFOP

FIFO

CSn

SCLK

SI

SO

DVDD_RAM

NC

AVDD_XOSC16

XOSC16_Q2

XOSC16_Q1

NC

VREG_EN

VREG_OUT

VREG_IN

AVDD_IF1

R_BIAS

ATEST2

ATEST1

AVDD_CHP

- Not Connected

Power (analog) 1.8 V Power supply for analog parts of ADCs and DACs

Power (digital) 1.8 V Power supply for digital parts of receive ADCs

Ground (digital) Ground connection for digital noise isolation

Power (digital) 1.8 V Power supply connection for digital noise isolation

Digital Input Asynchronous, active low digital reset

Ground (digital) Ground connection for digital core and pads

Ground (digital) Substrate connection for digital pads

Ground (digital) Substrate connection for digital modules

Power (digital) 3.3 V Power supply for digital I/Os

Power (digital) 1.8 V Power supply for digital core

Digital output SFD (Start of Frame Delimiter) / digital mux output

Digital output CCA (Clear Channel Assessment) / digital mux output

Digital output Active when number of bytes in FIFO exceeds threshold /

Digital I/O Active when data in FIFO /

Digital input SPI Chip select, active low

Digital input SPI Clock input, up to 10 MHz

Digital input SPI Slave Input. Sampled on the positive edge of SCLK

Digital output

(tristate)

Power (digital) 1.8 V Power supply for digital RAM

- Not Connected

Power (analog) 1.8 V crystal oscillator power supply

Analog I/O 16 MHz Crystal oscillator pin 2

Analog I/O 16 MHz Crystal oscillator pin 1 or external clock input

- Not Connected

Digital input Voltage regulator enable, active high, held at VREG_IN

Power output Voltage regulator 1.8 V power supply output

Power (analog) Voltage regulator 2.1 to 3.6 V power supply input

Power (analog) 1.8 V Power supply for transmit / receive IF chain

Analog output

Analog I/O Analog test I/O for prototype and production testing

Analog I/O Analog test I/O for prototype and production testing

Power (analog) 1.8 V Power supply for phase detector and charge pump

serial RF clock output in test mode

serial RF data input / output in test mode

SPI Slave Output. Updated on the negative edge of SCLK.

Tristate when CSn high.

voltage level when active. Note that VREG_EN is relative

VREG_IN, not DVDD3.3.

External precision resistor, 43 k, 1 %

SWRS041B Page 16 of 89

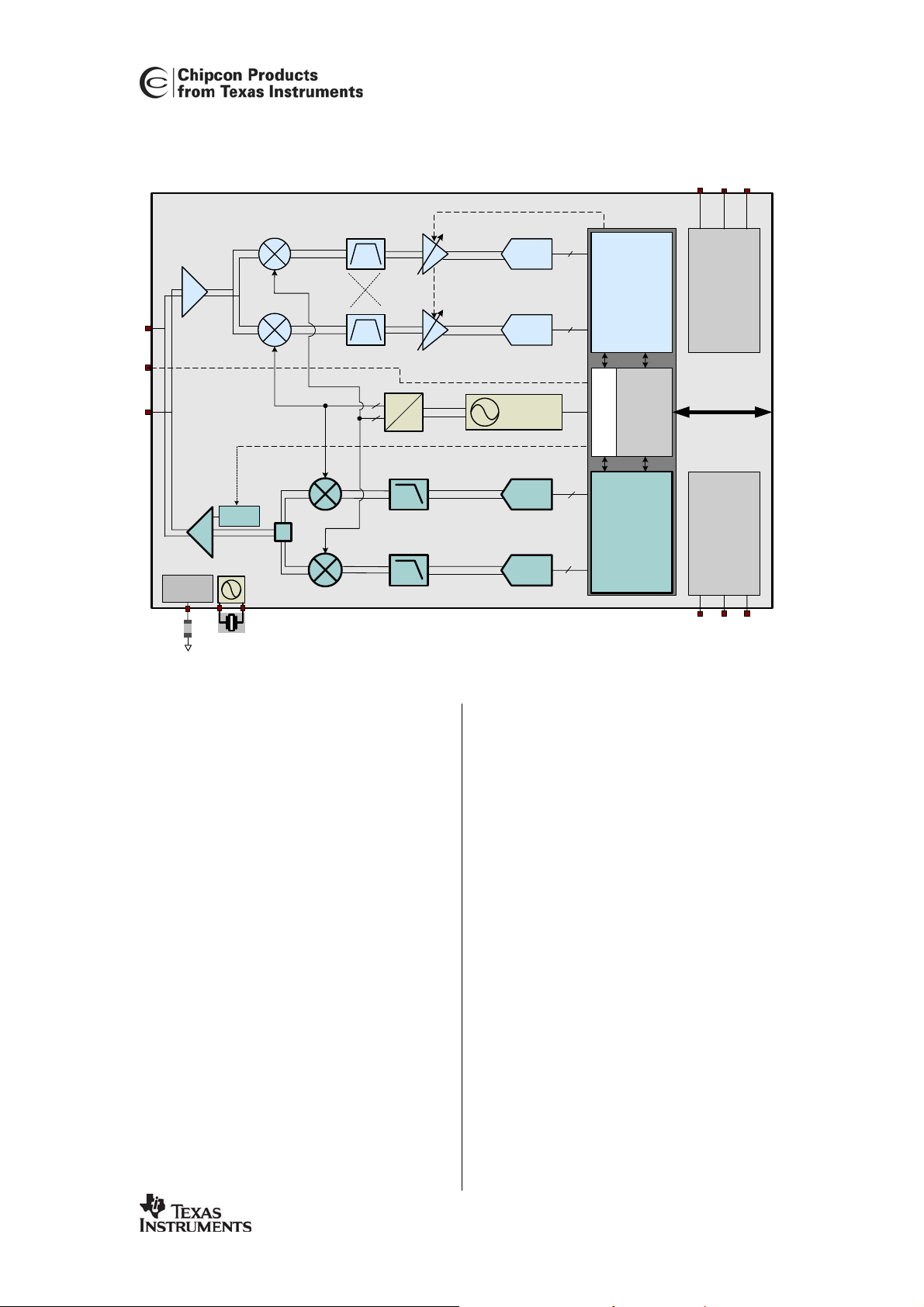

8 Circuit Description

LNA

TX/RX CONTROL

SmartRF

CC2420

CC2420

AUTOMATIC GAIN CONTROL

DIGITAL

ADC

ADC

0

90

FREQ

SYNTH

TX POWER CONTROL

DEMODULATOR

- Digital RSSI

- Gain Control

- Image Suppression

- Channel Filtering

- Demodulation

- Frame

synchronization

DIGITAL

INTERFACE

WITH FIFO

BUFFERS,

CRC AND

ENCRYPTION

CONTROL LOGIC

Serial

voltage

regulator

Serial

interface

microcontroller

Power

Control

PA

BIAS

XOSC

R

16 MHz

Figure 2.

CC2420

CC2420

simplified block diagram

is

On-chip

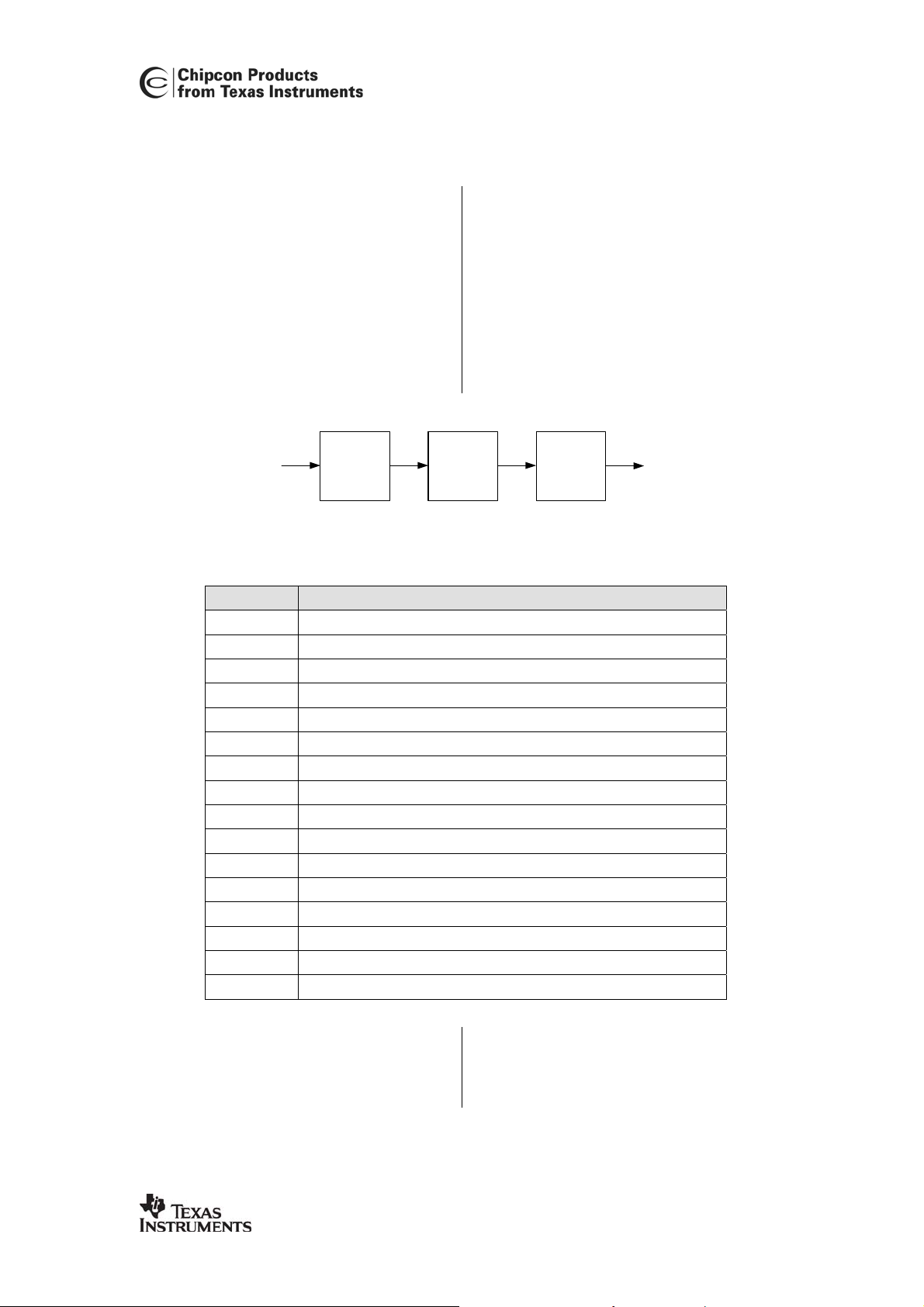

A simplified block diagram of

shown in Figure 2.

CC2420

features a low-IF receiver. The

received RF signal is amplified by the lownoise amplifier (LNA) and down-converted

in quadrature (I and Q) to the intermediate

frequency (IF). At IF (2 MHz), the complex

I/Q signal is filtered and amplified, and

then digitized by the ADCs. Automatic

gain control, final channel filtering, despreading, symbol correlation and byte

synchronisation are performed digitally.

When the SFD pin goes active, this

indicates that a start of frame delimiter has

been detected.

CC2420

buffers the

received data in a 128 byte receive FIFO.

The user may read the FIFO through an

SPI interface. CRC is verified in hardware.

RSSI and correlation values are appended

to the frame. CCA is available on a pin in

receive mode. Serial (unbuffered) data

modes are also available for test

purposes.

SWRS041B Page 17 of 89

DAC

DIGITAL

MODULATOR

- Data spreading

- Modulation

Digital and

Analog test

interface

DAC

The

CC2420

transmitter is based on direct

up-conversion. The data is buffered in a

128 byte transmit FIFO (separate from the

receive FIFO). The preamble and start of

frame delimiter are generated by

hardware. Each symbol (4 bits) is spread

using the IEEE 802.15.4 spreading

sequence to 32 chips and output to the

digital-to-analog converters (DACs).

An analog low pass filter passes the signal

to the quadrature (I and Q) upconversion

mixers. The RF signal is amplified in the

power amplifier (PA) and fed to the

antenna.

The internal T/R switch circuitry makes the

antenna interface and matching easy. The

RF connection is differential. A balun may

be used for single-ended antennas. The

biasing of the PA and LNA is done by

connecting TXRX_SWITCH to RF_P and

RF_N through an external DC path.

The frequency synthesizer includes a

completely on-chip LC VCO and a 90

degrees phase splitter for generating the I

CC2420

and Q LO signals to the down-conversion

mixers in receive mode and up-conversion

mixers in transmit mode. The VCO

operates in the frequency range 4800 –

4966 MHz, and the frequency is divided by

two when split in I and Q.

A crystal must be connected to

XOSC16_Q1 and XOSC16_Q2 and

provides the reference frequency for the

synthesizer. A digital lock signal is

available from the PLL.

The digital baseband includes support for

frame handling, address recognition, data

buffering and MAC security.

The 4-wire SPI serial interface is used for

configuration and data buffering.

An on-chip voltage regulator delivers the

regulated 1.8 V supply voltage. The

voltage regulator may be enabled /

disabled through a separate pin.

A battery monitor may optionally be used

to monitor the unregulated power supply

voltage. The battery monitor is

configurable through the SPI interface.

SWRS041B Page 18 of 89

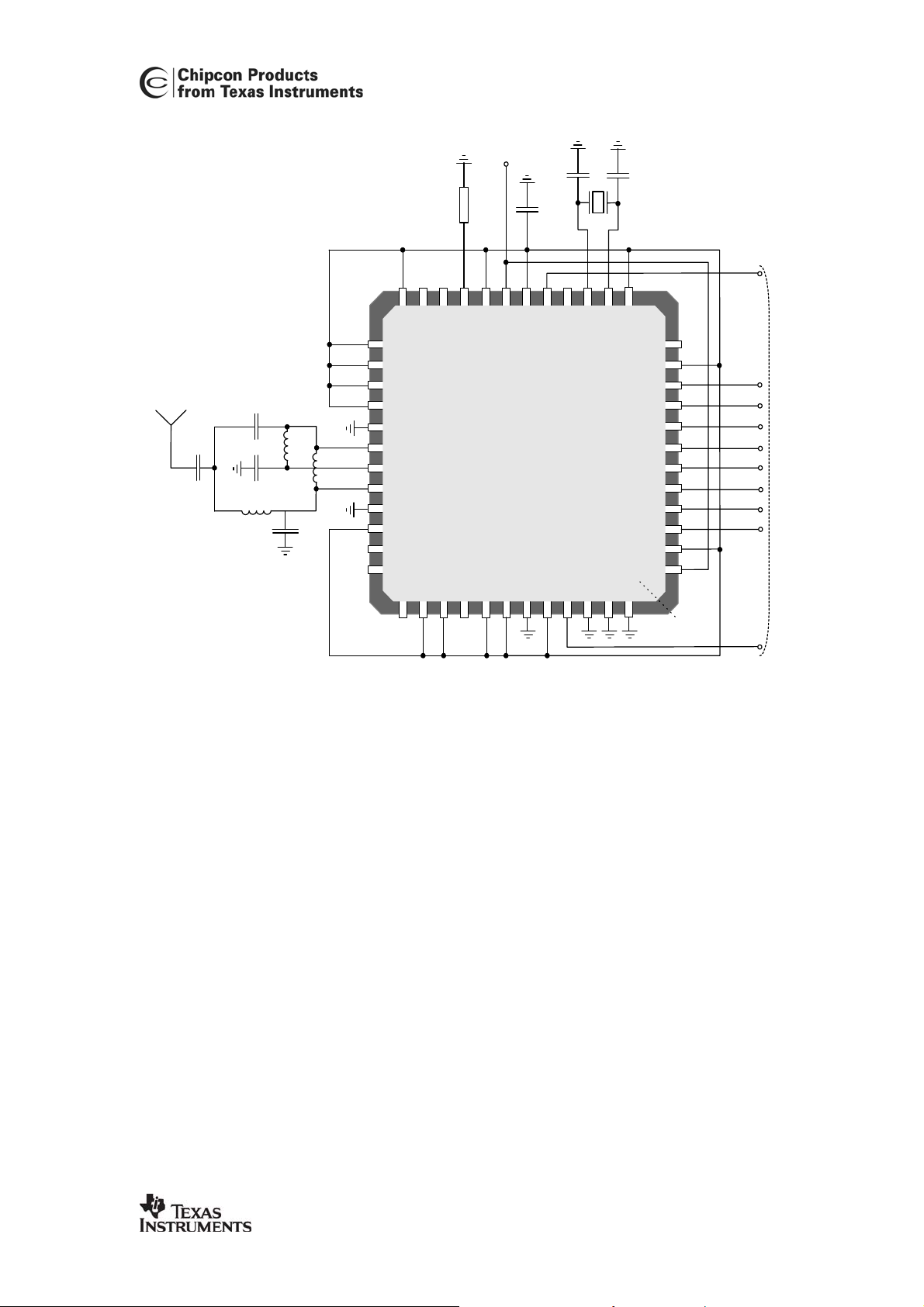

9 Application Circuit

CC2420

Few external components are required for

the operation of

application circuit is shown in Figure 4.

The external components shown are

described in Table 1 and typical values

are given in Table 2. Note that most

decoupling capacitors are not shown on

the application circuits. For the complete

reference design please refer to Texas

Instrument’s web site: http://www.ti.com

9.1 Input / output matching

The RF input/output is high impedance

and differential. The optimum differential

load for the RF port is 95+j187 .

When using an unbalanced antenna such

as a monopole, a balun should be used in

order to optimise performance. The balun

can be implemented using low-cost

discrete inductors and capacitors only or

in combination with transmission lines.

Figure 3 shows the balun implemented in

a two-layer reference design. It consists of

a half wave transmission line, C81, L61,

L71 and L81. The circuit will present the

optimum RF termination to

50 load on the antenna connection. This

circuit has improved EVM performance,

sensitivity and harmonic suppression

compared to the design in Figure 4.

Please refer to the input/output matching

section on page 54 for more details.

CC2420

. A typical

.

CC2420

with a

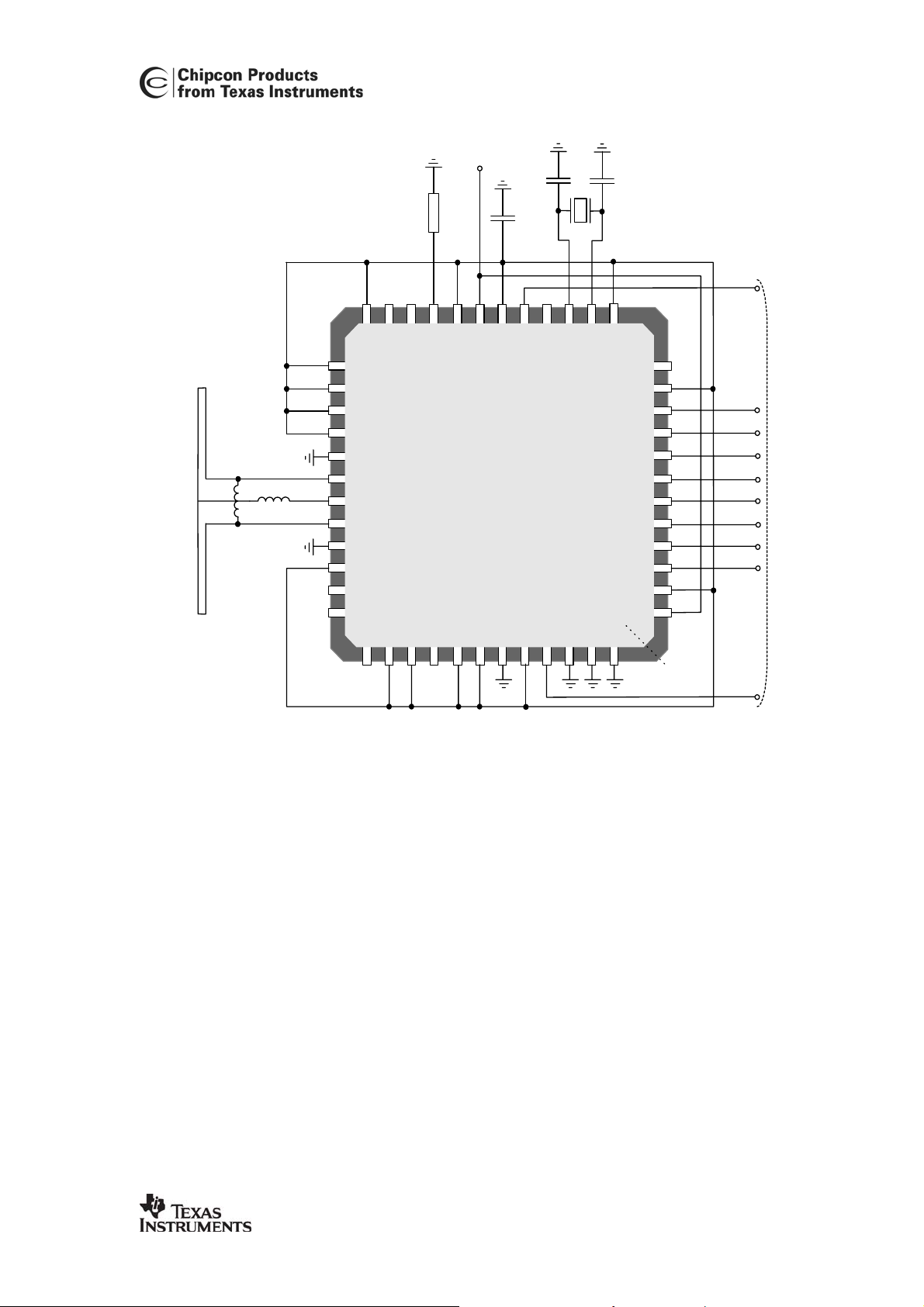

If a balanced antenna such as a folded

dipole is used, the balun can be omitted. If

the antenna also provides a DC path from

the TXRX_SWITCH pin to the RF pins,

inductors are not needed for DC bias.

Figure 5 shows a suggested application

circuit using a differential antenna. The

antenna type is a standard folded dipole.

The dipole has a virtual ground point;

hence bias is provided without

degradation in antenna performance.

9.2 Bias resistor

The bias resistor R451 is used to set an

accurate bias current.

9.3 Crystal

An external crystal with two loading

capacitors (C381 and C391) is used for

the crystal oscillator. See page 53 for

details.

9.4 Voltage regulator

The on chip voltage regulator supplies all

1.8 V power supply inputs. C42 is required

for stability of the regulator. A series

resistor may be used to comply with the

ESR requirement.

9.5 Power supply decoupling and

filtering

The balun in Figure 4 consists of C61,

C62, C71, C81, L61, L62 and L81, and will

present the optimum RF termination to

CC2420

connection. A low pass filter may be

added to add margin to the FCC

requirement on second harmonic level.

with a 50 load on the antenna

SWRS041B Page 19 of 89

Proper power supply decoupling must be

used for optimum performance. The

placement and size of the decoupling

capacitors and the power supply filtering

are very important to achieve the best

performance in an application. Texas

Instruments provides a compact reference

design that should be followed very

closely..

CC2420

Ref Description

C42 Voltage regulator load capacitance

C61 Balun and match

C62 DC block to antenna and match

C71 Front-end bias decoupling and match

C81 Balun and match

C381 16MHz crystal load capacitor, see page 53

C391 16MHz crystal load capacitor, see page 53

L61 DC bias and match

L62 DC bias and match

L71 DC bias and match

L81 Balun and match

R451 Precision resistor for current reference generator

XTAL 16MHz crystal, see page 53

Table 1. Overview of external components

Antenna

(50 Ohm)

C81 L81

L71

3.3 V

Power

supply

R451

C391 C381

C42

XTAL

484746

AVDD_CHP

1

VCO_GUARD

2

AVDD_VCO

3

AVDD_PRE

4

L61

AVDD_RF1

5

GND

RF_P

6

7

TXRX_SWITCH

8

RF_N

GND

9

AVDD_SW

10

NC

11

12

NC

NC

13

45

44434241403938

ATEST2

ATEST1

R_BIAS

VREG_IN

AVDD_IF1

CC2420

QLP48

RF

7x7

NC

VREG_EN

VREG_OUT

Transceiver

DGND_GUARD

AVDD_ADC

NC

16

DVDD_ADC

171819

RESETn

DGUARD

202122

AVDD_IF2

AVDD_RF2

14

15

37

XOSC16_Q1

XOSC16_Q2

DSUB_PADS

DGND

23

AVDD_XOSC16

DVDD_RAM

SCLK

FIFO

FIFOP

DVDD1.8

DSUB_CORE

DVDD3.3

24

CSn

CCA

SFD

36

NC

35

34

SO

33

SI

32

31

30

29

28

27

26

25

Digital Interf ace

Figure 3. Typical application circuit with transmission line balun for single-ended

operation

SWRS041B Page 20 of 89

CC2420

3.3 V

Power

supply

C391 C381

R451

C42

XTAL

DGND

22

39

XOSC16_Q1

38

XOSC16_Q2

DSUB_PADS

23

37

AVDD_XOSC16

DVDD_RAM

SCLK

CSn

FIFO

FIFOP

CCA

SFD

DVDD1.8

DSUB_CORE

DVDD3.3

24

36

NC

35

34

SO

33

SI

32

31

30

29

28

27

26

25

Antenna

(50 Ohm)

C62

C61

C71

L81

C81

L62

L61

1

VCO_GUARD

2

AVDD_VCO

3

AVDD_PRE

4

AVDD_RF1

5

GND

RF_P

6

7

TXRX_SWITCH

8

RF_N

GND

9

AVDD_SW

10

NC

11

12

NC

48

47

46

45

44

43

42

41

40

NC

ATEST2

ATEST1

R_BIAS

VREG_IN

VREG_EN

AVDD_CHP

AVDD_IF1

VREG_OUT

CC2420

QLP48

RF

7x7

Transceiver

DGND_GUARD

AVDD_ADC

AVDD_IF2

AVDD_RF2

NC

13

14

15

DVDD_ADC

NC

18

16

17

RESETn

DGUARD

20

21

19

Figure 4. Typical application circuit with discrete balun for single-ended operation

Digital Interface

SWRS041B Page 21 of 89

CC2420

3.3 V

Power

supply

C391 C381

R451

C42

XTAL

39

XOSC16_Q1

37

38

XOSC16_Q2

AVDD_XOSC16

DVDD_RAM

DVDD1.8

DSUB_CORE

DSUB_PADS

DVDD3.3

24

23

SCLK

CSn

FIFO

FIFOP

CCA

SFD

36

NC

35

34

SO

33

SI

32

31

30

29

28

27

26

25

Folded

dipole

antenna

L61

L71

1

VCO_GUARD

2

AVDD_VCO

3

AVDD_PRE

4

AVDD_RF1

5

GND

RF_P

6

7

TXRX_SWITCH

8

RF_N

GND

9

AVDD_SW

10

NC

11

12

NC

13

48

AVDD_CHP

NC

47

46

ATEST2

ATEST1

AVDD_IF2

AVDD_RF2

14

15

45

44

43

42

R_BIAS

VREG_IN

VREG_OUT

AVDD_IF1

CC2420

QLP48

RF

7x7

Transceiver

DGND_GUARD

AVDD_ADC

DVDD_ADC

NC

18

16

17

19

41

VREG_EN

DGUARD

20

40

NC

RESETn

21

DGND

22

Figure 5. Suggested application circuit with differential antenna (folded dipole)

Digital Interface

SWRS041B Page 22 of 89

CC2420

Item Single ended output,

C42

C61 Not used 0.5 pF, +/- 0.25pF, NP0, 0402 Not used

C62 Not used 5.6 pF, +/- 0.25pF, NP0, 0402 Not used

C71 Not used 5.6 pF, 10%, X5R, 0402 Not used

C81 5.6 pF, +/- 0.25pF, NP0, 0402 0.5 pF, +/- 0.25pF, NP0, 0402 Not used

C381 27 pF, 5%, NP0, 0402 27 pF, 5%, NP0, 0402 27 pF, 5%, NP0, 0402

C391 27 pF, 5%, NP0, 0402 27 pF, 5%, NP0, 0402 27 pF, 5%, NP0, 0402

L61 8.2 nH, 5%,

L62 Not used 5.6 nH, 5%,

L71 22 nH, 5%,

L81 1.8 nH, +/- 0.3nH,

R451

XTAL 16 MHz crystal, 16 pF load

transmission line balun

10 µF, 0.5 < ESR < 5 10 µF, 0.5 < ESR < 5 10 µF, 0.5 < ESR < 5

Monolithic/multilayer, 0402

Monolithic/multilayer, 0402

Monolithic/multilayer, 0402

43 k, 1%, 0402 43 k, 1%, 0402 43 k, 1%, 0402

),

(C

L

ESR < 60

Single ended output,

discrete balun

7.5 nH, 5%,

Monolithic/multilayer, 0402

Monolithic/multilayer, 0402

Not used 12 nH, 5%, Monolithic/multilayer,

7.5 nH, 5%,

Monolithic/multilayer, 0402

16 MHz crystal, 16 pF load

(CL),

ESR < 60

Differential antenna

27 nH, 5%, Monolithic/multilayer,

0402

Not used

0402

Not used

16 MHz crystal, 16 pF load (C

ESR < 60

Table 2. Bill of materials for the application circuits

),

L

SWRS041B Page 23 of 89

CC2420

10 IEEE 802.15.4 Modulation Format

This section is meant as an introduction to

the 2.4 GHz direct sequence spread

spectrum (DSSS) RF modulation format

defined in IEEE 802.15.4. For a complete

description, please refer to [1].

The modulation and spreading functions

are illustrated at block level in Figure 6 [1].

Each byte is divided into two symbols, 4

bits each. The least significant symbol is

transmitted first. For multi-byte fields, the

Transmitted

bit-stream

(LSB first)

Bit-to-

Symbol

Figure 6. Modulation and spreading functions [1]

Symbol Chip sequence (C0, C1, C2, … , C31)

0 1 1 0 1 1 0 0 1 1 1 0 0 0 0 1 1 0 1 0 1 0 0 1 0 0 0 1 0 1 1 1 0

1 1 1 1 0 1 1 0 1 1 0 0 1 1 1 0 0 0 0 1 1 0 1 0 1 0 0 1 0 0 0 1 0

2 0 0 1 0 1 1 1 0 1 1 0 1 1 0 0 1 1 1 0 0 0 0 1 1 0 1 0 1 0 0 1 0

3 0 0 1 0 0 0 1 0 1 1 1 0 1 1 0 1 1 0 0 1 1 1 0 0 0 0 1 1 0 1 0 1

4 0 1 0 1 0 0 1 0 0 0 1 0 1 1 1 0 1 1 0 1 1 0 0 1 1 1 0 0 0 0 1 1

5 0 0 1 1 0 1 0 1 0 0 1 0 0 0 1 0 1 1 1 0 1 1 0 1 1 0 0 1 1 1 0 0

6 1 1 0 0 0 0 1 1 0 1 0 1 0 0 1 0 0 0 1 0 1 1 1 0 1 1 0 1 1 0 0 1

7 1 0 0 1 1 1 0 0 0 0 1 1 0 1 0 1 0 0 1 0 0 0 1 0 1 1 1 0 1 1 0 1

8 1 0 0 0 1 1 0 0 1 0 0 1 0 1 1 0 0 0 0 0 0 1 1 1 0 1 1 1 1 0 1 1

9 1 0 1 1 1 0 0 0 1 1 0 0 1 0 0 1 0 1 1 0 0 0 0 0 0 1 1 1 0 1 1 1

10 0 1 1 1 1 0 1 1 1 0 0 0 1 1 0 0 1 0 0 1 0 1 1 0 0 0 0 0 0 1 1 1

11 0 1 1 1 0 1 1 1 1 0 1 1 1 0 0 0 1 1 0 0 1 0 0 1 0 1 1 0 0 0 0 0

12 0 0 0 0 0 1 1 1 0 1 1 1 1 0 1 1 1 0 0 0 1 1 0 0 1 0 0 1 0 1 1 0

13 0 1 1 0 0 0 0 0 0 1 1 1 0 1 1 1 1 0 1 1 1 0 0 0 1 1 0 0 1 0 0 1

14 1 0 0 1 0 1 1 0 0 0 0 0 0 1 1 1 0 1 1 1 1 0 1 1 1 0 0 0 1 1 0 0

15 1 1 0 0 1 0 0 1 0 1 1 0 0 0 0 0 0 1 1 1 0 1 1 1 1 0 1 1 1 0 0 0

Table 3. IEEE 802.15.4 symbol-to-chip mapping [1]

Symbol-

to-Chip

least significant byte is transmitted first,

except for security related fields where the

most significant byte it transmitted first.

Each symbol is mapped to one out of 16

pseudo-random sequences, 32 chips

each. The symbol to chip mapping is

shown in Table 3. The chip sequence is

then transmitted at 2 MChips/s, with the

least significant chip (C

) transmitted first

0

for each symbol.

O-QPSK

Modulator

Modulated

Signal

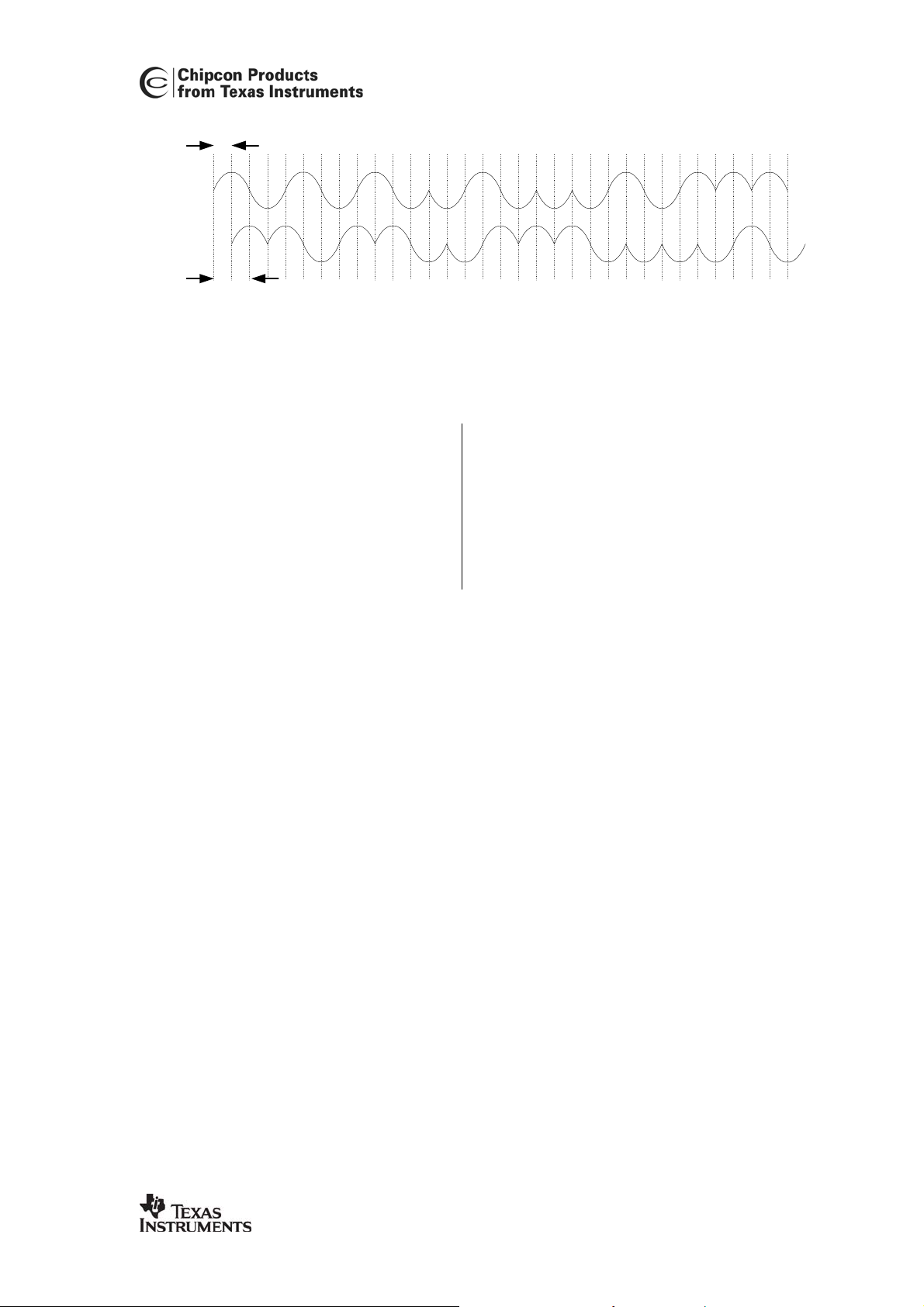

The modulation format is Offset –

Quadrature Phase Shift Keying (O-QPSK)

with half-sine chip shaping. This is

equivalent to MSK modulation. Each chip

SWRS041B Page 24 of 89

is shaped as a half-sine, transmitted

alternately in the I and Q channels with

one half chip period offset. This is

illustrated for the zero-symbol in Figure 7.

CC2420

T

C

I-phase

Q-phase

1

01

1101

2T

C

0

1

00

1001

1

0

00

1100

0

1

0010

Figure 7. I / Q Phases when transmitting a zero-symbol chip sequence, TC = 0.5 µs

11 Configuration Overview

CC2420

best performance for different

applications. Through the programmable

configuration registers the following key

parameters can be programmed:

Receive / transmit mode

RF channel selection

RF output power

can be configured to achieve the

Power-down / power-up mode

Crystal oscillator power-up / power

down

Clear Channel Assessment mode

Packet handling hardware support

Encryption / Authentication modes

11

1

SWRS041B Page 25 of 89

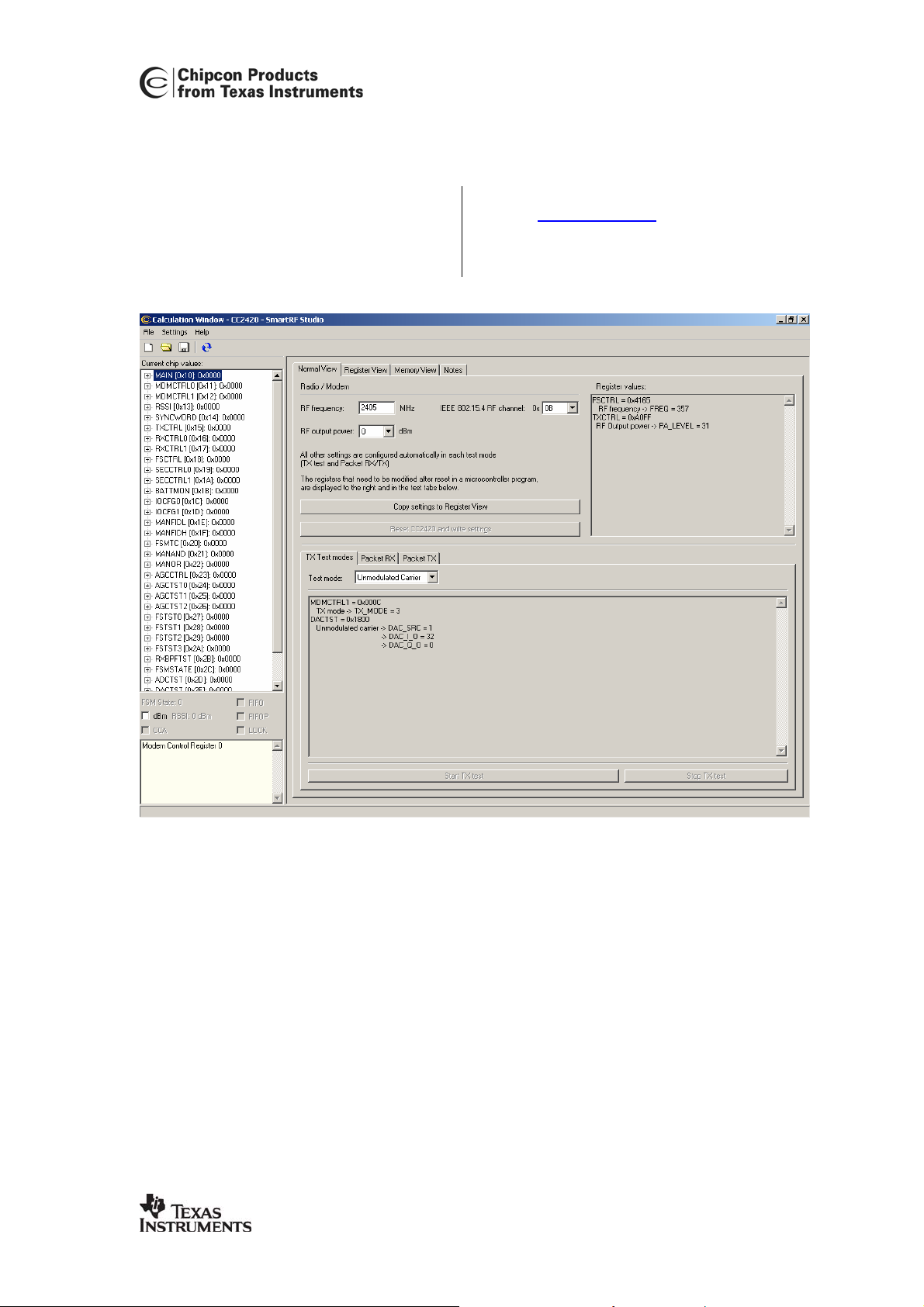

12 Evaluation Software

CC2420

Texas Instruments (TI) provides users of

CC2420

SmartRF

which may be used for radio performance

and functionality evaluation. SmartRF®

with a software program,

®

Studio (Windows interface)

Studio can be downloaded from TI’s web

page: http://www.ti.com

the user interface of the

configuration software.

. Figure 8 shows

CC2420

Figure 8. SmartRF Studio user interface

SWRS041B Page 26 of 89

CC2420

13 4-wire Serial Configuration and Data Interface

CC2420

SPI-compatible interface (pins SI, SO,

SCLK and CSn) where

This interface is also used to read and

write buffered data (see page 39). All

address and data transfer on the SPI

interface is done most significant bit first.

13.1 Pin configuration

The digital inputs SCLK, SI and CSn are

high-impedance inputs (no internal pullup) and should have external pull-ups if

not driven. SO is high-impedance when

CSn is high. An external pull-up should be

used at SO to prevent floating input at

microcontroller. Unused I/O pins on the

MCU can be set to outputs with a fixed ‘0’

level to avoid leakage currents.

13.2 Register access

There are 33 16-bit configuration and

status registers, 15 command strobe

registers, and two 8-bit registers to access

the separate transmit and receive FIFOs.

Each of the 50 registers is addressed by a

6-bit address. The RAM/Register bit (bit 7)

must be cleared for register access. The

Read/Write bit (bit 6) selects a read or a

write operation and makes up the 8-bit

address field together with the 6-bit

address.

In each register read or write cycle, 24 bits

are sent on the SI-line. The CSn pin (Chip

Select, active low) must be kept low during

this transfer. The bit to be sent first is the

is configured via a simple 4-wire

CC2420

is the slave.

RAM/Register bit (set to 0 for register

access), followed by the R/W bit (0 for

write, 1 for read). The following 6 bits are

the address-bits (A5:0). A5 is the most

significant bit of the address and is sent

first. The 16 data-bits are then transferred

(D15:0), also MSB first. See Figure 9 for

an illustration.

The configuration registers can also be

read by the microcontroller via the same

configuration interface. The R/W bit must

be set high to initiate the data read-back.

CC2420

addressed register on the 16 clock cycles

following the register address. The SO pin

is used as the data output and must be

configured as an input by the

microcontroller.

The timing for the programming is also

shown in Figure 9 with reference to Table

4. The clocking of the data on SI into the

CC2420

SCLK. When the last bit, D0, of the 16

data-bits has been written, the data word

is loaded in the internal configuration

register.

Multiple registers may be written without

releasing CSn, as described in the Multiple

SPI access section on page 31.

The register data will be retained during

power down mode, but not when the

power-supply is turned off (e.g. by

disabling the voltage regulator using the

VREG_EN pin). The registers can be

programmed in any order.

then returns the data from the

is done on the positive edge of

SWRS041B Page 27 of 89

Loading...

Loading...