BQ21061

VINLS

PMID

LS/LDO

VDD

BAT

TS

+

±

NTC

GND

IN

VIO

Host

USB

I2C Bus

<150mA

Load

System

MR

PG

INT

LP

CE

C

4

C

5

C

3

C

2

C

1

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

BQ21061

SLUSDU0 –SEPTEMBER 2019

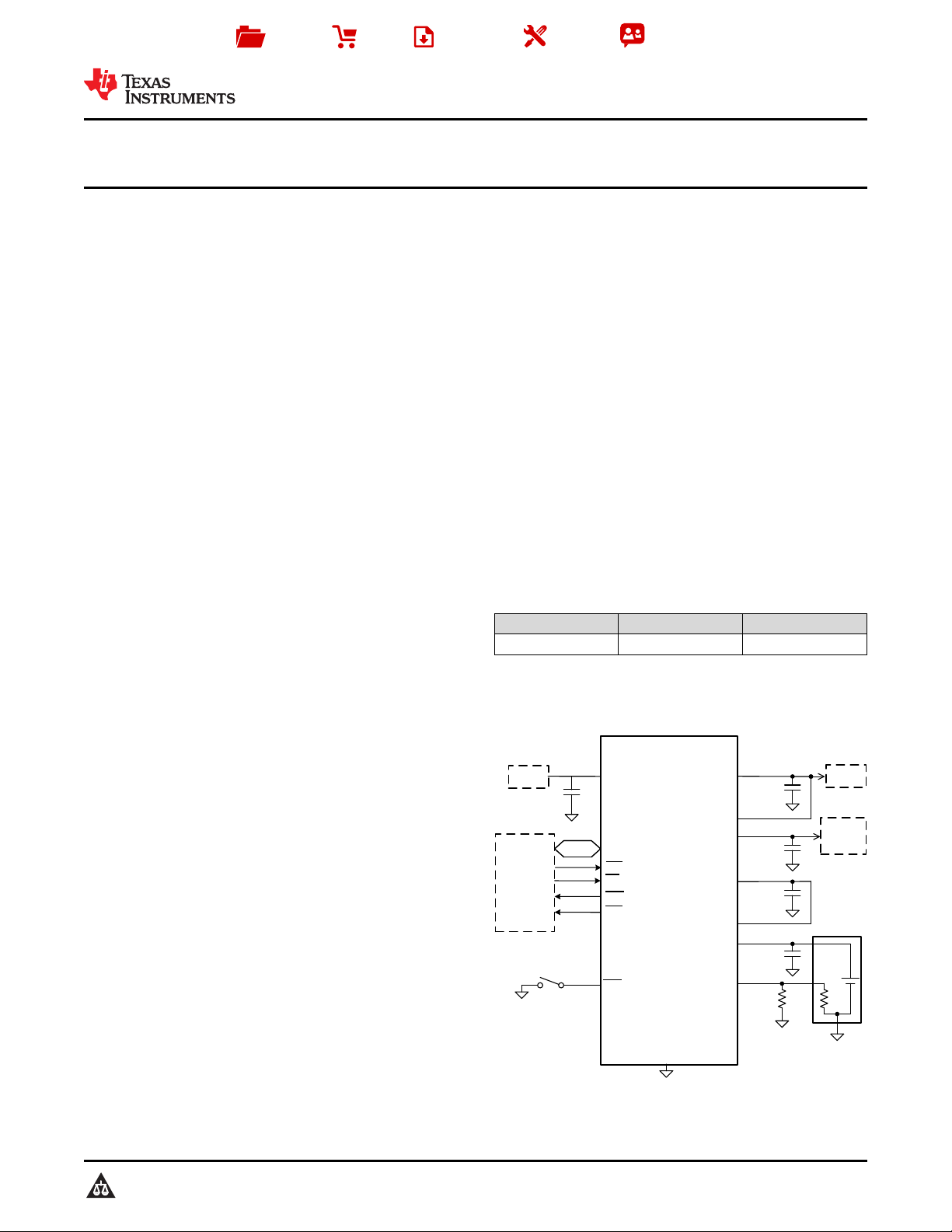

BQ21061 I2C Controlled 1-Cell 500-mA Linear Battery Charger With 10-nA Ship Mode,

Power Path With Regulated System (PMID) Voltage, And LDO

1 Features

1

• Linear battery charger with 1.25-mA to 500-mA

fast charge current range

– 0.5% Accurate I2C programmable battery

regulation voltage ranging from 3.6 V to 4.6 V

in 10-mV steps

– Configurable termination current supporting

down to 0.5 mA

– 20-V Tolerant input with typical 3.4-V to 5.5-V

input voltage operating range

– Programmable thermal charging profile, fully

configurable hot, warm, cool and cold

thresholds

• Power Path management for powering system

and charging battery

– I2C Programmable regulated system voltage

(PMID) ranging from 4.4V to 4.9V in addition to

battery voltage tracking and Input pass-though

options

– Dynamic power path management optimizes

charging from weak adapters

– Advanced I2C control allows host to disconnect

the battery or adapter as needed

• I2C Configurable load switch or up to 150-mA

LDO output

– Programmable range from 0.6 V to 3.7 V in

100-mV steps

• Ultra low Iddq for extended battery life

– 10-nA Ship mode battery Iq

– 400-nA Iq While powering the system (PMID

and VDD on)

• One push-button wake-up and reset input with

adjustable timers

– Supports system power cycle and HW reset

• 20-Pin 2-mm x 1.6-mm CSP package

• 11-mm2Total solution size

1

2 Applications

• Headsets, earbuds and hearing aids

• Smart watches and smart trackers

• Wearable fitness and activity monitors

• Blood glucose monitors

3 Description

The BQ21061 is a highly integrated battery charge

management IC that integrates the most common

functions for wearable, portable and small medical

devices, namely a charger, a regulated output voltage

rail for system power, a LDO, and push-button

controller.

The BQ21061 IC integrates a linear charger with

PowerPath that enables quick and accurate charging

for small batteries while providing a regulated voltage

to the system. The regulated system voltage (PMID)

output may be configured through I2C based on the

recommended operating condition of downstream

IC's and system loads for optimal system operation.

Device Information

PART NUMBER PACKAGE BODY SIZE (NOM)

BQ21061 DSBGA (20) 2.00 mm x 1.60 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Simplified Schematic

(1)

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

BQ21061

SLUSDU0 –SEPTEMBER 2019

www.ti.com

Table of Contents

1 Features.................................................................. 1

2 Applications ........................................................... 1

3 Description ............................................................. 1

4 Revision History..................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 4

6.1 Absolute Maximum Ratings...................................... 4

6.2 ESD Ratings.............................................................. 4

6.3 Recommended Operating Conditions....................... 4

6.4 Thermal Information.................................................. 5

6.5 Electrical Characteristics........................................... 5

6.6 Timing Requirements................................................ 7

6.7 Typical Characteristics.............................................. 9

7 Detailed Description............................................ 12

7.1 Overview................................................................. 12

7.2 Functional Block Diagram....................................... 12

7.3 Feature Description................................................. 13

7.4 Device Functional Modes........................................ 26

4 Revision History

DATE REVISION NOTES

September 2019 * Initial release

7.5 Register Map .......................................................... 29

8 Application and Implementation ........................ 48

8.1 Application Information............................................ 48

8.2 Typical Application ................................................. 48

9 Power Supply Recommendations...................... 53

10 Layout................................................................... 53

10.1 Layout Guidelines ................................................. 53

10.2 Layout Example .................................................... 53

11 Device and Documentation Support................. 54

11.1 Device Support...................................................... 54

11.2 Documentation Support ....................................... 54

11.3 Receiving Notification of Documentation Updates 54

11.4 Support Resources ............................................... 54

11.5 Trademarks........................................................... 54

11.6 Electrostatic Discharge Caution............................ 54

11.7 Glossary................................................................ 54

12 Mechanical, Packaging, and Orderable

Information........................................................... 54

2

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

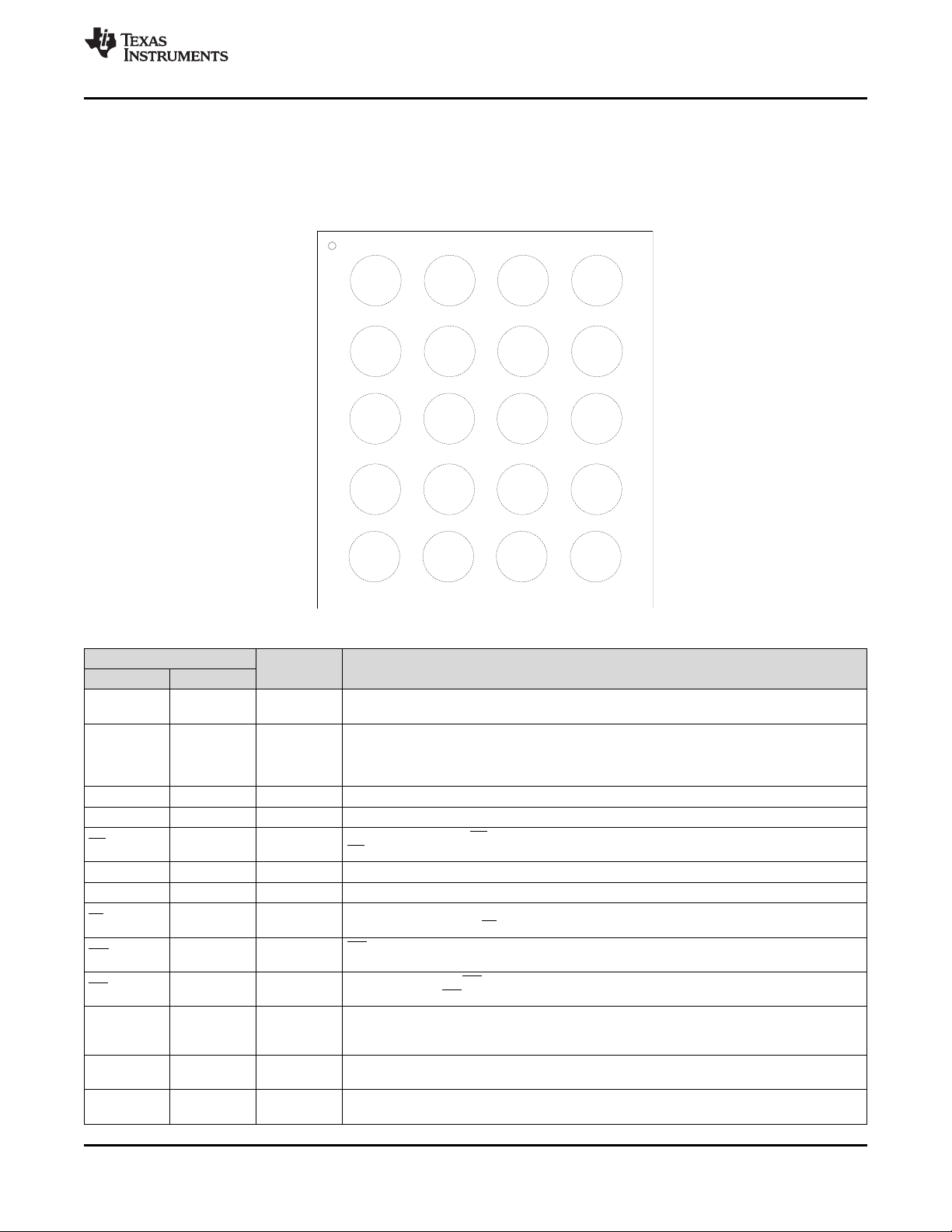

IN PMID BAT GND

/PG PMID BAT TS

/MR /CE NC1 NC2

VDD /INT /LP LSLDO

VIO SDA SCL VINLS

A

B

C

D

E

1 2 3 4

www.ti.com

5 Pin Configuration and Functions

BQ21061

SLUSDU0 –SEPTEMBER 2019

YFP Package

20-Pin DSBGA

Top View

Pin Functions

PIN

NAME NO.

IN A1 I

PMID A2, B2 I/O

GND A4 PWR Ground connection. Connect to the ground plane of the circuit.

VDD D1 O Digital supply LDO. Connect a 2.2-µF from this pin to ground.

CE C2 I

SCL E3 I/O I2C Interface Clock. Connect SCL to the logic rail through a 10-kΩ resistor.

SDA E2 I I2C Interface Data. Connect SDA to the logic rail through a 10-kΩ resistor.

LP D3 I

INT D2 O

MR C1 I

LS/LDO D4 O

VINLS E4 I

BAT A3, B3 I/O

I/O DESCRIPTION

DC Input Power Supply. IN is connected to the external DC supply. Bypass IN to GND with

at least 1-µF of capacitance using a ceramic capacitor.

Regulated System Output. Connect 22-µF capacitor from PMID to GND as close to the PMID

and GND pins as possible. If operating in VIN Pass-Through Mode (PMID_REG = 111) a

lower capacitor value may be used (at least 3-µF of ceramic capacitance with DC bias derating).

Charge Enable. Drive CE low or leave disconnected to enable charging when VIN is valid.

CE is pulled low internally with 900-kΩ resistor.

Low Power Mode Enable. Drive this pin low to enable the device in low power mode when

powered by the battery. LP is pulled low internally with 900-kΩ resistor.

INT is an open-drain output that signals fault interrupts. When a fault occurs, a 128-µs pulse

is sent out as an interrupt for the host.

Manual Reset Input. MR is a general purpose input used to reset the device or to wake it up

from Ship Mode. MR has in internal 125-kΩ pull-up resistor to BAT.

Load Switch or LDO output. Connect 2.2 µF of ceramic capacitance to this pin to assure

stability. Be sure to account for capacitance bias voltage derating when selecting the

capacitor.

Input to the Load Switch / LDO output. Connect at least 1 µF of ceramic capacitance from

this pin to ground.

Battery Connection. Connect to the positive terminal of the battery. Bypass BAT to GND with

at least 1 µF of ceramic capacitance.

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

3

BQ21061

SLUSDU0 –SEPTEMBER 2019

www.ti.com

Pin Functions (continued)

PIN

NAME NO.

TS B4 I

PG B1 O

VIO E1 I

NC1 C3 I

NC2 C4 I

I/O DESCRIPTION

Battery Pack NTC Monitor. Connect TS to a 10-kΩ NTC thermistor in parallel to a 10-kΩ

resistor. If TS function is not to be used connect a 5-kΩ resistor from TS to ground.

Open-drain Power Good status indication output. The PG pin can also be configured as a

general purpose open drain output or level shifter version of MR.

System IO supply. Connect to system IO supply to allow level shifting of input signals (SDA,

SCL, LP and CE) to the device internal digital domain. Connect to VDD when external IO

supply is not available.

No Connect. Connect to ground if possible for better thermal dissipation or leave floating. Do

not connect to a any voltage source or signal to avoid higher quiescent current.

No Connect. Connect to ground if possible for better thermal dissipation. May be shorted to

/LP for easier routing as long as Absolute Maximum Rating requirements are met..

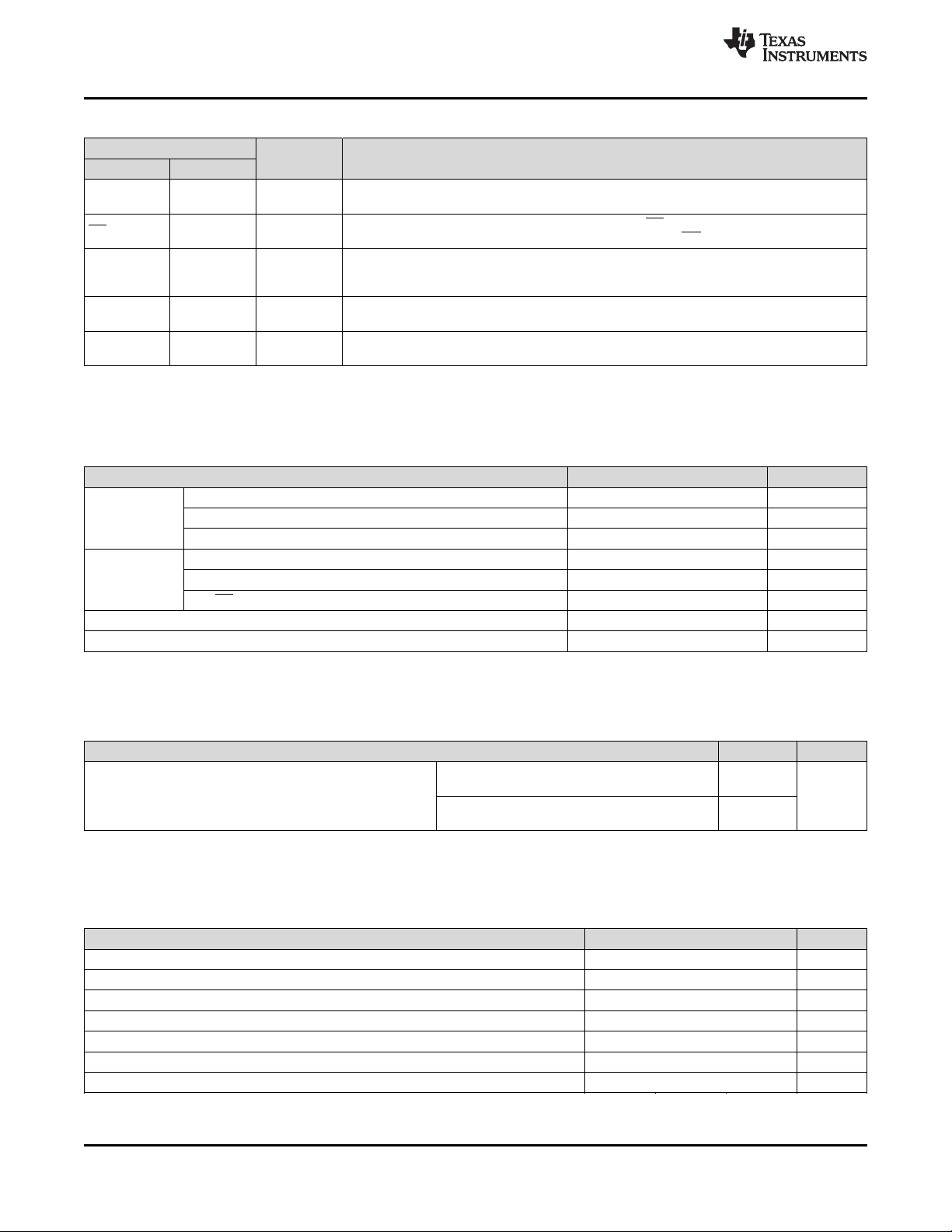

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

IN –0.3 20 V

Voltage

Current

Junction temperature, T

Storage temperature, T

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

TS,VDD, NC –0.3 1.95 V

All other pins –0.3 5.5 V

IN 0 800 mA

BAT, PMID –0.5 1.5 A

INT, PG 0 10 mA

J

stg

(1)

MIN MAX UNIT

–40 125 °C

–55 150 °C

6.2 ESD Ratings

Human body model (HBM), per

V

(ESD)

Electrostatic discharge

ANSI/ESDA/JEDEC JS-001, all pins

Charged device model (CDM), per JEDEC

specification JESD22-C101, all pins

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

(1)

(2)

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

V

BAT

V

IN

V

INLS

V

IO

I

LDO

I

PMID

T

A

(1) Based on minimum V

4

Battery voltage range 2.4 4.6 V

Input voltage range 3.15 5.25

LDO input voltage range 2.2 5.25

IO supply voltage range 1.2 3.6 V

LDO output current 0 100 mA

PMID output current 0 500 mA

Operating free-air temperature range –40 85 °C

value. 5.5V under typical conditions

OVP

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

VALUE UNIT

±2000

V

±500

(1)

(1)

V

V

BQ21061

www.ti.com

SLUSDU0 –SEPTEMBER 2019

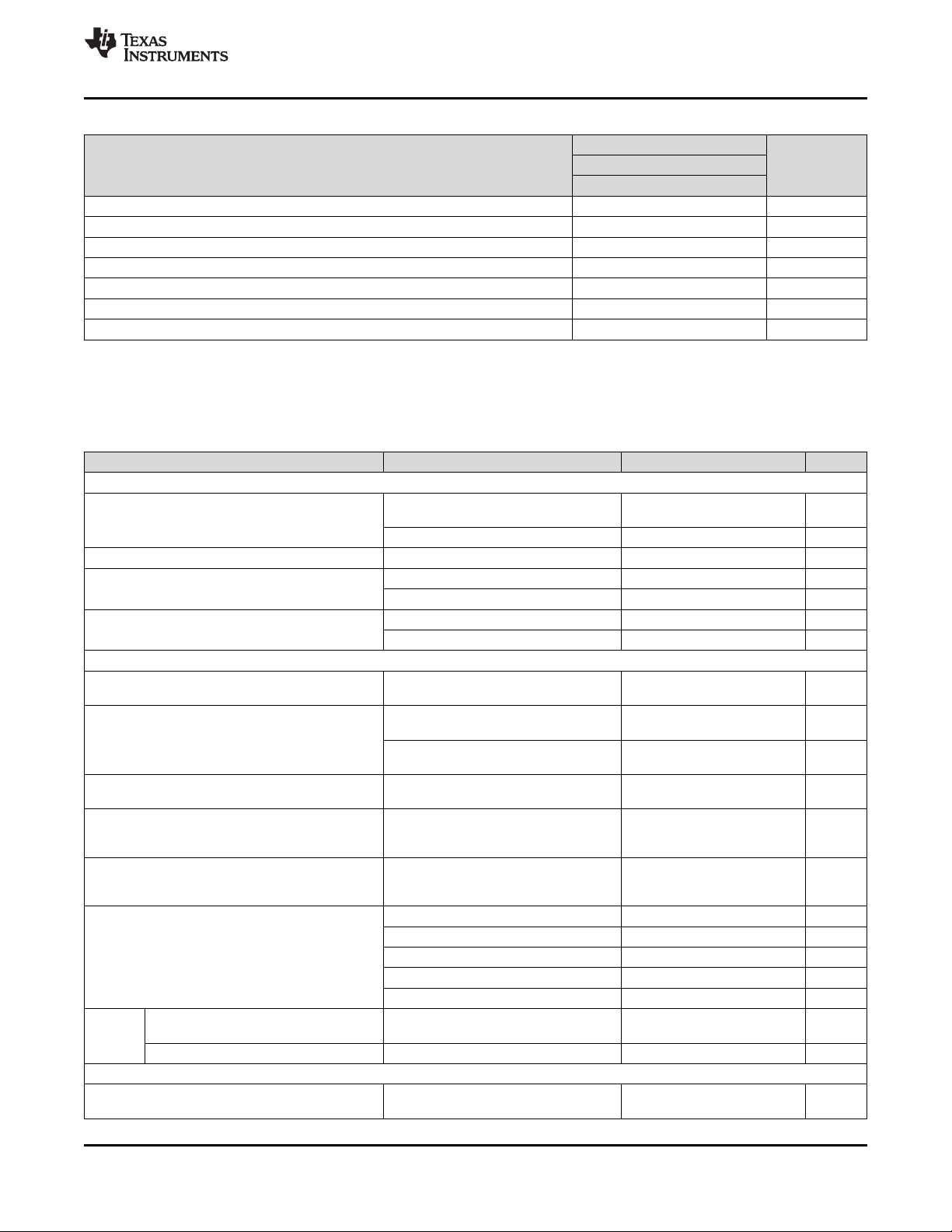

6.4 Thermal Information

BQ21061

THERMAL METRIC

(1)

UNITYFP (DSBGA)

20-PIN

R

θJA

R

θJA

R

θJC(top)

R

θJB

Ψ

JT

Ψ

JB

R

θJC(bot)

Junction-to-ambient thermal resistance

Junction-to-ambient thermal resistance 74.4 °C/W

Junction-to-case (top) thermal resistance 0.5 °C/W

Junction-to-board thermal resistance 17.6 °C/W

Junction-to-top characterization parameter 0.3 °C/W

Junction-to-board characterization parameter 17.7 °C/W

Junction-to-case (bottom) thermal resistance N/A °C/W

(2)

36.1 °C/W

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

(2) Measured in BQ21061EVM board.

6.5 Electrical Characteristics

VIN= 5V, V

INPUT CURRENTS

I

IN

I

BAT_SHIP

I

BAT_LP

I

BAT_ACTI

VE

POWER PATH MANAGEMENT AND INPUT CURRENT LIMIT

V

PMID_RE

G

V

PMID_RE

G_ACC

R

ON(IN-

PMID)

V

BSUP1

V

BSUP2

I

ILIM

V

IN_DPM

BATTERY CHARGER

V

DPPM

= 3.6V. TJ= 25°C unless otherwise noted.

BAT

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

PMID_MODE = 01, VIN= 5V, V

Input supply current

3.6V

VIN= 5V, V

Battery Discharge Current in Ship Mode VIN= 0V , V

Battery Quiescent Current in Low-power

Mode

Battery Quiescent Current in Active

Mode

VIN= 0V , V

VIN= 0V , V

VIN= 0V , V

VIN= 0V , V

Default System (PMID) Regulation

Voltage

VIN= 5V, V

System Regulation Voltage Accuracy

100mA, TJ= 25°C

VIN= 5V, V

500mA

I

= 500mA (ILIM = 110), VIN= 5V, I

Input FET ON resistance

Enter supplements mode threshold

Exit supplements mode threshold

ILIM

= 150mA

V

> V

BAT

BAT

> V

BATUVLO

BATUVLO

Charge disabled

V

Charge disabled

= 3.6V Charge Disabled 1.6 mA

BAT

= 3.6V 10 nA

BAT

= 3.6V, LDO Disabled 0.46 0.9 µA

BAT

= 3.6V, LDO Enabled 1.7 1.9 µA

BAT

= 3.6V, LDO Disabled 18 23 µA

BAT

= 3.6V, LDO Enabled 21 25 µA

BAT

PMID_REG

PMID_REG

= 4.5V. I

= 4.5V. I

, DPPM enabled or

, DPPM enabled or

PMID

PMID

BAT

=

=

= 0-

500 µA

4.5 V

-1 1 %

–3 3 %

IN

280 520 mΩ

V

<

PMID

V

–

BAT

40mV

V

<

PMID

V

–

BAT

20mV

mV

mV

Programmable Range 50 600 mA

I

= 50mA 45 50 mA

ILIM

Input Current Limit

Input DPM voltage threshold where

current in reduced

I

= 100mA 90 100 mA

ILIM

I

= 150mA 135 150 mA

ILIM

I

= 500mA 450 500 mA

ILIM

Programmable Range 4.2 4.9 V

Accuracy –3 3 %

PMID voltage threshold when charge

current is reduced

V

PMID

- V

BAT

200 mV

Product Folder Links: BQ21061

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

5

BQ21061

SLUSDU0 –SEPTEMBER 2019

Electrical Characteristics (continued)

www.ti.com

VIN= 5V, V

= 3.6V. TJ= 25°C unless otherwise noted.

BAT

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

R

ON(BAT-

PMID)

V

BATREG

Battery Discharge FET On Resistance V

Charge Voltage Programmable charge voltage range 3.6 4.6 V

Voltage Regulation Accuracy 0.5 0.5 %

Fast Charge Programmable Current

I

CHARGE

Range

Fast Charge Current Accuracy I

I

PRECHAR

GE

I

TERM

Precharge current Precharge current programmable range 1.25 77.5 mA

Precharge Current Accuracy -40°C < TJ< 85°C –10 10 %

Termination Charge Current

Accuracy I

V

LOWV

V

SHORT

I

SHORT

V

RCH

R

PMID_PD

Programmable voltage threshold for precharge to fast charge transitions

Battery voltage threshold for short

detection

Charge Current in Battery Short

Condition

Recharge Threshold voltage

PMID pull-down resistance V

VDD

V

DD

VDD LDO output voltage 1.8 V

LS/LDO

Input voltage range for Load switch

Mode

V

INLS

Input voltage range for LDO Mode

LDO programmable output voltage range 0.6 3.7 V

V

LDO

ΔV

OUT

ΔV

V

IN

R

DOSN_L

DO

R

DSCH_LS

LDO

I

OCL_LDO

LDO output accuracy

/ΔI

OUT

DC Load Regulation

/Δ

OUT

DC Line Regulation

Switch On resistance V

Discharge FET On-resistance for LS V

Output Current Limit V

LDO VINLS quiescent current in LDO

I

IN_LDO

mode

OFF State Supply Current V

BATTERY PACK NTC MONITOR

V

HOT

V

WARM

V

COOL

High temperature threshold VTSfalling, -10°C < TJ< 85°C 0.182

Warm temperature threshold VTSfalling, -10°C < TJ< 85°C 0.262

Cool temperature threshold VTSrising, -10°C < TJ< 85°C 0.510

= 4.35V, I

BAT

V

< V

LOWV

CHARGE

BAT

> 5mA –5 5 %

Termination Current Programmable

Range

= 10% I

TERM

= 100mA 100 175 mΩ

BAT

< V

BATREG

1.25 500 mA

1 31 %

CHARGE

, I

CHARGE

= 100mA –5

(1)

(1)

5

VBAT rising. Programmable Range 2.8 3 V

VBAT falling, VIN = 5V 2.41 2.54 2.67 V

I

V

< V

BAT

SHORT

V

falling, V

BAT

140mV setting

V

falling, V

BAT

200mV setting

= 3.6V 25 Ω

PMID

BATREG

BATREG

= 4.2V, V

= 4.2V, V

RCH

RCH

=

=

PRECHAR

GE

140 mV

200 mV

mA

0.8 5.5 V

2.2 or

V

LDO

500mV

+

5.5 V

TJ= 25°C –2 2 %

V

= 1.8V, V

LDO

0°C < TJ< 85°C, 1 mA < I

V

= 1.8V

LDO

0°C < TJ< 85°C, Over V

= 100mA, V

= 3.6V 250 450 mΩ

INLS

= 3.6V 40 Ω

INLS

= 0V 200 300 mA

LS/LDO

V

= V

BAT

INLS

= V

BAT

INLS

LDO

INLS

= 1.8V

=3.6V. I

= 1mA –3 3 %

LOAD

< 150mA,

INLS

OUT

range, I

OUT

1.2 %

0.5 %

=3.6V 0.9 µA

=3.6V 0.25 µA

(1)

(1)

(1)

0.185 0.189

0.265 0.268

0.514 0.518

(1)

(1)

(1)

%

V

V

V

(1) Based on Characterization Data

6

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

www.ti.com

Electrical Characteristics (continued)

BQ21061

SLUSDU0 –SEPTEMBER 2019

VIN= 5V, V

= 3.6V. TJ= 25°C unless otherwise noted.

BAT

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

COLD

V

OPEN

V

HYS

I

TS_BIAS

Cold temperature threshold VTSrising, -10°C < TJ< 85°C 0.581

TS Open threshold VTSrising, -10°C < TJ< 85°C 0.9 V

Threshold hysteresis 4.7 mV

TS bias current -10°C < TJ< 85°C 78.4 80 81.6 µA

PROTECTION

V

UVLO

IN active threshold voltage

Battery undervoltage Lockout Threshold

Voltage

V

BATUVLO

Accuracy –3 3 %

Battery undervoltage Lockout Threshold

Voltage at Power Up

V

SLP_ENT

RY

V

SLP_EXIT

V

OVP

Sleep Entry Threshold (VIN- V

Sleep Exit Threshold (VIN- V

Input Supply Over Voltage Threshold

Battery Over Current Threshold

I

BAT_OCP

Programmable range

Current Limit Accuracy –30 30 %

T

SHUTDO

WN

T

HYS

Thermal shutdown trip point 125 °C

Thermal shutdown trip point hysteresis 15 °C

I2C INTERFACE (SCL and SDA)

I2C Frequency 100 400 kHz

V

V

V

I

IL

IH

OL

LKG

Input Low threshold level V

Input High Threshold level V

Output Low threshold level V

High-level leakage Current V

/MR INPUT

R

PU

V

IL

Internal pull up resistance 90 125 170 kΩ

/MR Input Low threshold level V

/INT, /PG OUTPUTS

V

I

OL

LKG

Output Low threshold level V

/INT Hi level leakage Current High Impedance, V

/CE, /LP INPUTS

R

PDOWN

V

IL

V

IH

/CE pull down resistance 900 kΩ

Input Low threshold level VIO= 1.8V 0.45 V

/CE Input High Threshold level VIO= 1.8V 1.35 V

) 2.0V < V

BAT

) 2.0V < V

BAT

(1)

0.585 0.589

(1)

VINrising 3.4 V

VINfalling 3.25 V

Programmable range, 150 mV

Hysteresis

V

rising, VIN= 0V, TJ= 25°C 3.15 V

BAT

BAT

BAT

< V

< V

, VINfalling 80 mV

BATREG

BATREG

2.4 3 V

130 mV

VINrising 5.35 5.5 5.8 V

VINfalling (125mV hysteresis) 5.4 V

I

BAT_OCP

increasing 1200 1600 mA

= VIO= 1.8V

PULLUP

= VIO= 1.8V

PULLUP

= VIO= 1.8V, I

PULLUP

= VIO= 1.8V 1 µA

PULLUP

> V

BAT

BUVLO

= VIO= 1.8V, I

PULLUP

PULLUP

= 5mA

LOAD

= 5mA

LOAD

= VIO= 1.8V 1 µA

0.75 *

V

IO

0.25 *

V

IO

0.25 *

V

IO

0.3 V

0.25 *

V

IO

V

V

V

V

V

6.6 Timing Requirements

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

BATTERY CHARGE TIMERS

t

MAXCHG

t

PRECHG

Charge safety timer Programmable range 180 720 min

Precharge safety timer 0.25 * t

Product Folder Links: BQ21061

MAXCHG

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

7

BQ21061

SLUSDU0 –SEPTEMBER 2019

Timing Requirements (continued)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

WATCHDOG TIMERS

t

WATCHDO

G_SW

t

HW_RESE

T_WD

LDO

t

ON_LDO

t

OFF_LDO

t

PMID_LDO

_DELAY

PUSHBUTTON TIMERS (/MR)

t

WAKE1

t

WAKE2

t

RESET_W

ARN

t

HW_RESE

T

t

RESTART(

AUTOWAK

E)

PROTECTION

t

DGL_SLP

t

DGL_OVP

t

DGL_OCP

t

REC_SC

t

RETRY_S

C

t

DGL_SHT

DWN

I2C INTERFACE

t

WATCHDO

G

t

I2CRESET

INPUT PINS (/CE and /LP)

t

LP_EXIT_I

2C

SW Watchdog timer 25 50 s

HW reset watchdog timer WATCHDOG_15S_ENABLE = 1 15 s

Turn ON time 100mA load, to 90% V

Turn OFF time 100mA load, to 10% V

Delay between PMID and LDO enable

during power up

WAKE1 Timer. Timer for Ship Mode

wake.

WAKE2 Timer. Time from /MR falling

edge to INT being asserted.

RESET_WARN Timer. Time prior to HW

RESET

HW RESET Timer. Time from /MR falling

edge to HW Reset

RESTART Timer. Time from /MR HW

Reset to PMID power up

Deglitch time for supply rising above

V

+ V

SLP

SLP_HYS

Deglitch time for V

Threshold VIN falling below V

OVP

Battery OCP deglitch time 30 µs

Recovery time, BAT Short Circuit during

Discharge Mode

Retry window for PMID or BAT short

circuit recovery

Deglitch time, Thermal shutdown TJrising above T

I2C interface reset timer for host When enabled 50 s

I2C interface inactive reset timer 500 ms

Time for device to exit Low-power mode

and allow I2C communication

www.ti.com

LDO

LDO

500 µs

30 µs

Startup 20 ms

MR_WAKE1_TIMER = 0 106 125 144 ms

MR_WAKE2_TIMER = 1 1.7 2 2.3 s

MR_RESET_WARN = 01 0.85 1 1.15 s

MR_HW_RESET = 01 6.8 8 9.2 s

AUTOWAKE = 01 1.05 1.2 1.35 s

120 µs

OVP

32 ms

250 ms

2 s

SHUTDOWN

10 µs

VIN= 0V. 1 ms

8

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

V

INLS

(V)

R

DSON

(:)

1 1.5 2 2.5 3 3.5 4 4.5 5

0

0.2

0.4

0.6

0.8

1

1.2

D015

TJ = -40C

TJ = 25C

TJ = 85C

I

LOAD

(A)

V

LDO

(V)

0.1 0.11 0.12 0.13 0.14 0.15 0.16 0.17 0.18 0.19 0.2

0.7984

0.7992

0.8

0.8008

0.8016

0.8024

0.8032

0.804

0.8048

0.8056

0.8064

D009

TJ = -40C

TJ = 25C

TJ = 85C

I

PRECHARGE

(A)

Error (%)

0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80

-1.2

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

1.2

D013

TJ = 25C

TJ = 0C

TJ = -40C

TJ = 60C

TJ = 125C

I

PRECHARGE

(mA)

Error (%)

0 5 10 15 20 25 30 35 40

-1.5

-1

-0.5

0

0.5

1

1.5

D012

TJ = 25C

TJ = 0C

TJ = -40C

TJ = 60C

TJ = 125C

V

BATREG

(V)

Error (%)

3.6 3.7 3.8 3.9 4 4.1 4.2 4.3 4.4 4.5 4.6

-0.5

-0.45

-0.4

-0.35

-0.3

-0.25

-0.2

-0.15

-0.1

-0.05

0

D011

TJ = 25C

TJ = 0C

TJ = -40C

TJ = 60C

TJ = 125C

I

CHARGE

(A)

Error (%)

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5

-1.75

-1.5

-1.25

-1

-0.75

-0.5

-0.25

0

0.25

0.5

0.75

1

1.25

D014

TJ = -40C

TJ = 0C

TJ = 25C

TJ = 60C

TJ = 125C

www.ti.com

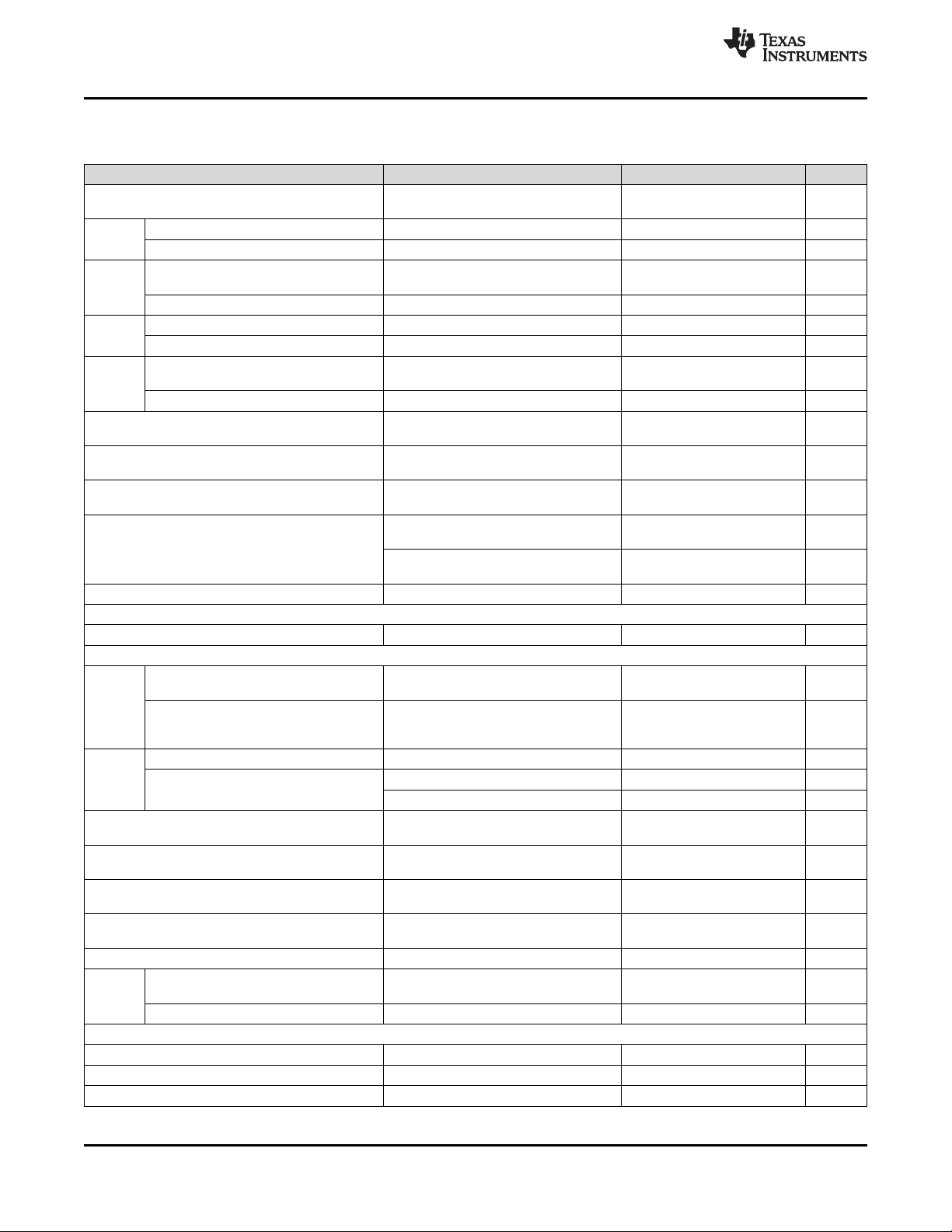

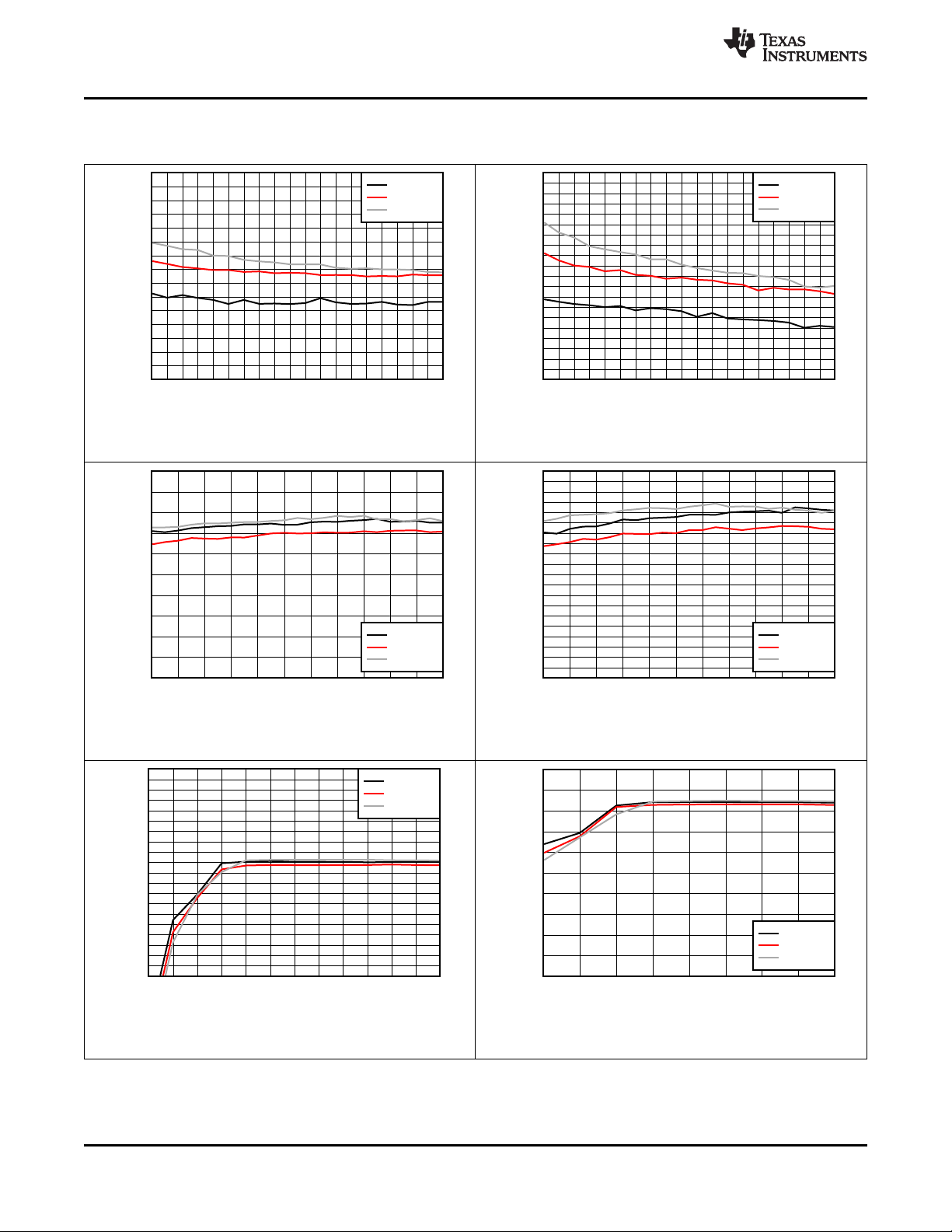

6.7 Typical Characteristics

CIN= 1 µF, C

= 10 µF, C

PMID

LSLDO

= 2.2 µF, C

= 1 µF (unless otherwise specified)

BAT

BQ21061

SLUSDU0 –SEPTEMBER 2019

VIN = 5 V PMID_REG_CTRL = 111 (Pass-Through)

Figure 1. Battery Regulation Voltage Accuracy vs.

VBATREG Setting

VIN = 5 V VBAT = 2.7 V ICHARGE_RANGE = 0

Figure 3. Pre-Charge Current Accuracy vs. IPRECHARGE

setting (ICHARGE_RANGE = 0)

VIN = 5 V VBAT = 3.6 V ICHARGE_RANGE = 1

Figure 2. Charge Current Accuracy vs. ICHARGE Setting

VBUS = 5 V VBAT = 2.7 V ICHARGE_RANGE = 1

Figure 4. Pre-Charge Current Accuracy vs. IPRECHARGE

Setting (ICHARGE_RANGE = 1)

VBUS = 5 V

Figure 5. LS/LDO Switch On Resistance vs. VINLS

Product Folder Links: BQ21061

VIN = 0 V VBAT = 3.6 V VINLS = VPMID

Figure 6. LDO Load Regulation (VLDO = 0.8 V)

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

9

V

INLS

(V)

VLDO (V)

3.2 3.3 3.4 3.5 3.6 3.7 3.8 3.9 4 4.1 4.2 4.3 4.4

3.2

3.22

3.24

3.26

3.28

3.3

3.32

3.34

3.36

3.38

3.4

D006

TJ = -40C

TJ = 25C

TJ = 85C

V

INLS

(V)

V

LDO

(V)

3.6 3.7 3.8 3.9 4 4.1 4.2 4.3 4.4

3.4

3.425

3.45

3.475

3.5

3.525

3.55

3.575

3.6

3.625

3.65

D007

TJ = -40C

TJ = 25C

TJ = 85C

V

INLS

(V)

V

LDO

(V)

2.2 2.4 2.6 2.8 3 3.2 3.4 3.6 3.8 4 4.2 4.4

1.19

1.192

1.194

1.196

1.198

1.2

1.202

1.204

1.206

1.208

1.21

D004

TJ = -40C

TJ = 25C

TJ = 85C

V

INLS

(V)

V

LDO

(V)

2.2 2.4 2.6 2.8 3 3.2 3.4 3.6 3.8 4 4.2 4.4

1.79

1.792

1.794

1.796

1.798

1.8

1.802

1.804

1.806

1.808

1.81

D005

TJ = -40C

TJ = 25C

TJ = 85C

I

LOAD

(A)

V

LDO

(V)

0.01 0.03 0.05 0.07 0.09 0.11 0.13 0.15 0.17 0.19

1.79

1.792

1.794

1.796

1.798

1.8

1.802

1.804

1.806

1.808

1.81

1.812

1.814

1.816

1.818

1.82

D008

TJ = -40C

TJ = 25C

TJ = 85C

I

LOAD

(A)

V

LDO

(V)

0.01 0.03 0.05 0.07 0.09 0.11 0.13 0.15 0.17 0.19

3.29

3.294

3.298

3.302

3.306

3.31

3.314

3.318

3.322

3.326

3.33

D010

TJ = -40C

TJ = 25C

TJ = 85C

BQ21061

SLUSDU0 –SEPTEMBER 2019

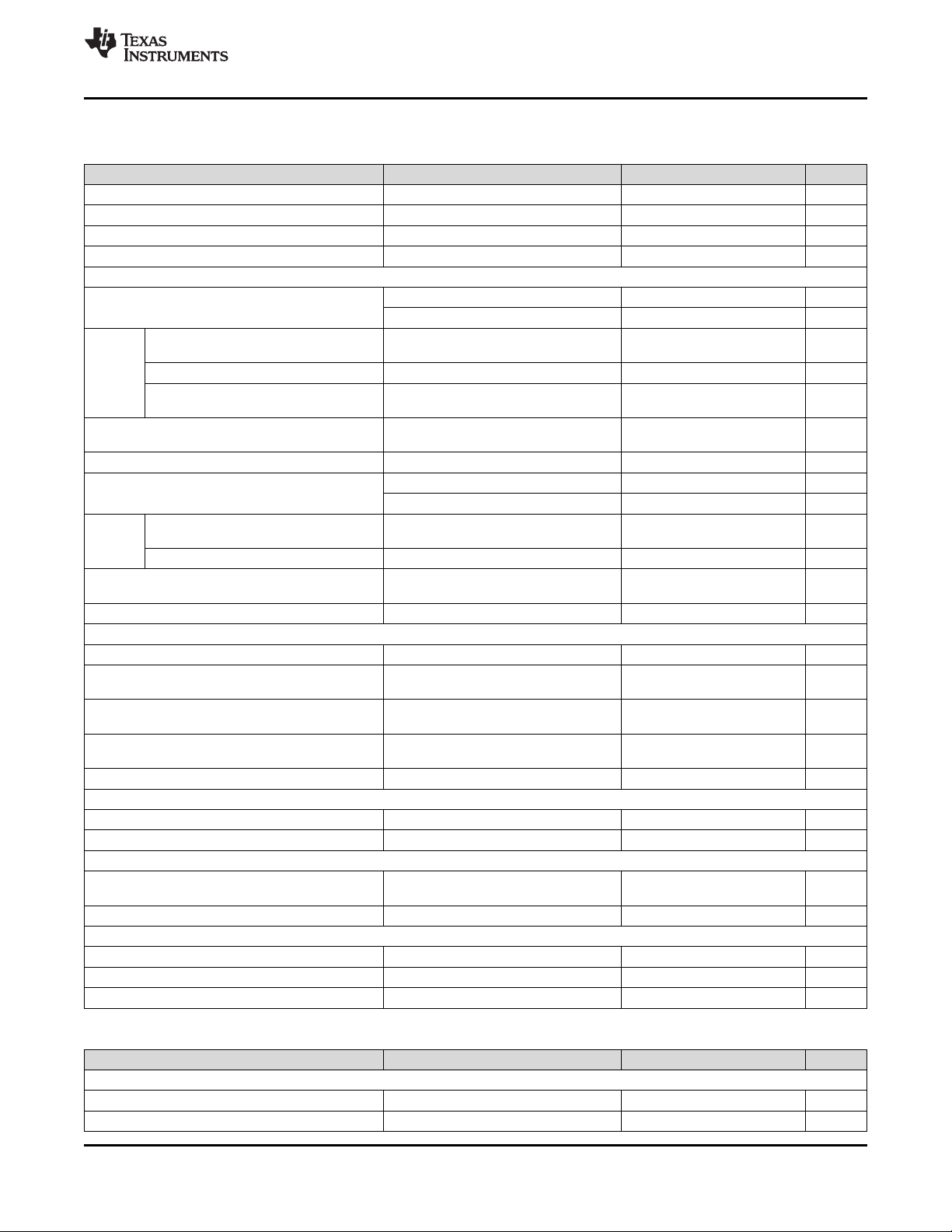

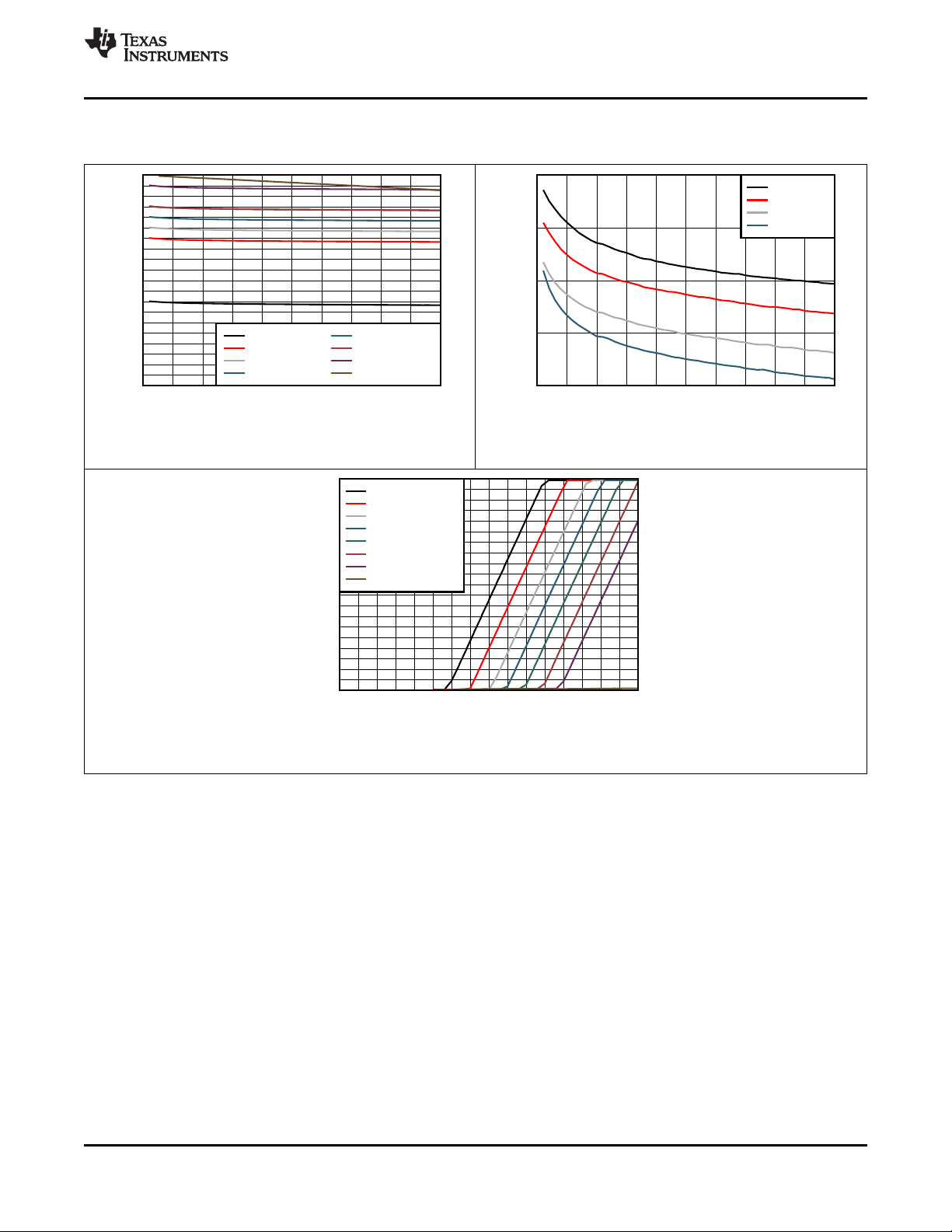

Typical Characteristics (continued)

www.ti.com

CIN= 1 µF, C

= 10 µF, C

PMID

LSLDO

= 2.2 µF, C

= 1 µF (unless otherwise specified)

BAT

VIN = 0 V VBAT = 3.6 V VINLS = VPMID

Figure 7. LDO Load Regulation (VLDO = 1.8 V)

VIN = 0 V VBAT = 3.6 V VINLS= VPMID

Figure 8. LDO Load Regulation (VLDO = 3.3 V)

VBAT = 4.4 V ILOAD = 150 mA

Figure 9. LDO Line Regulation (VLDO = 1.2 V)

10

VBAT = 4.4 V ILOAD = 150 mA

Figure 11. LDO Line Regulation (VLDO = 3.3 V)

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

VBAT = 4.4 V ILOAD = 150 mA

Figure 10. LDO Line Regulation (VLDO = 1.8 V)

VBAT = 4.4 V ILOAD = 150 mA

Figure 12. LDO Line Regulation (VLDO = 3.6 V)

Product Folder Links: BQ21061

Temperature(qC)

Charge Current Reduction (%)

50 60 70 80 90 100 110 120 130

0

10

20

30

40

50

60

70

80

90

100

D004

THERM_REG = 0

THERM_REG = 1

THERM_REG = 2

THERM_REG = 3

THERM_REG = 4

THERM_REG = 5

THERM_REG = 6

THERM_REG = 7

PMID Load Current (A)

V

PMID

(V)

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5

3

3.2

3.4

3.6

3.8

4

4.2

4.4

4.6

4.8

5

D001

PMID_REG = 0

PMID_REG = 1

PMID_REG = 2

PMID_REG = 3

PMID_REG = 4

PMID_REG = 5

PMID_REG = 6

PMID_REG = 7

PMID Load (A)

V

PMID

(V)

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5

4.44

4.46

4.48

4.5

4.52

D003

TJ = -40°C

TJ = 25°C

TJ = 85°C

TJ = 125°C

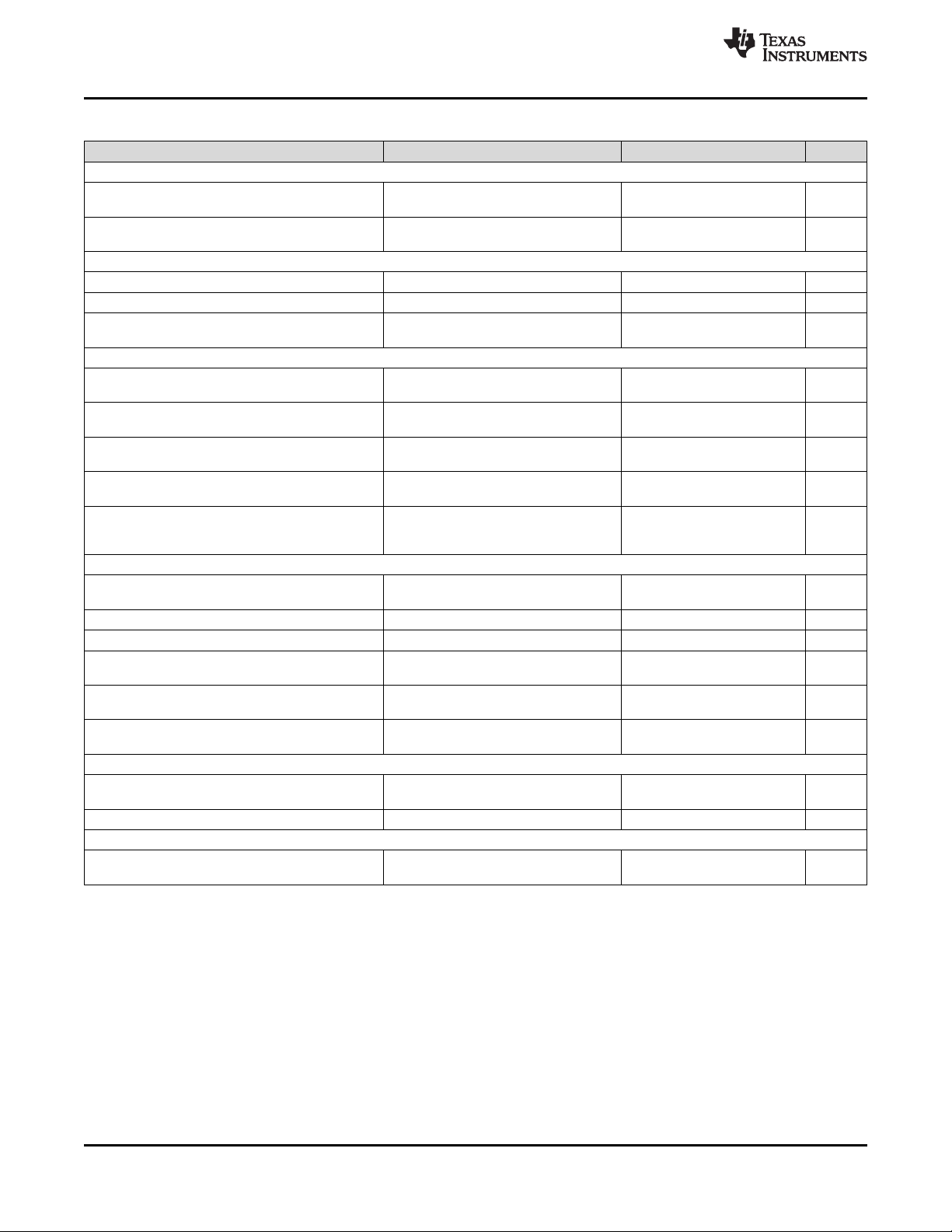

www.ti.com

Typical Characteristics (continued)

BQ21061

SLUSDU0 –SEPTEMBER 2019

CIN= 1 µF, C

= 10 µF, C

PMID

LSLDO

= 2.2 µF, C

VBAT = 0 V

Figure 13. PMID Load Regulation

= 1 µF (unless otherwise specified)

BAT

Figure 14. PMID Load Regulation vs. Temperature

VBAT = 3.6 V VIN = 5 V

VBAT = 3.6 V VIN = 5 V

Figure 15. Charge Current Thermal Regulation

Product Folder Links: BQ21061

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

11

LDO, and BAT FET Control

Device Control

V

IN

Charge

Enable

I2C

Interface

Low Power Mode

Control

Charge Control

LDO / Load Switch

Control

Thermal

Shutdown

I

BATREG

LDO

Control

UVLO

V

BATREG

V

IN_DPM

BAT

VIN

+

±

/Power Good

GP Output

Interrupt

JEITA/Temp

Information

For Charge Control

S

G

D

S

G

D

Q7

Q8

IN

GND

VIO

/CE

SCL

SDA

/LP

/MR

/INT

/PG

PMID

VDD

VINLS

LDO

BAT

TS

V

BATUVLO

Q5/Q6

1.045 x V

BAT

PMID_REG

BQ21061

SLUSDU0 –SEPTEMBER 2019

www.ti.com

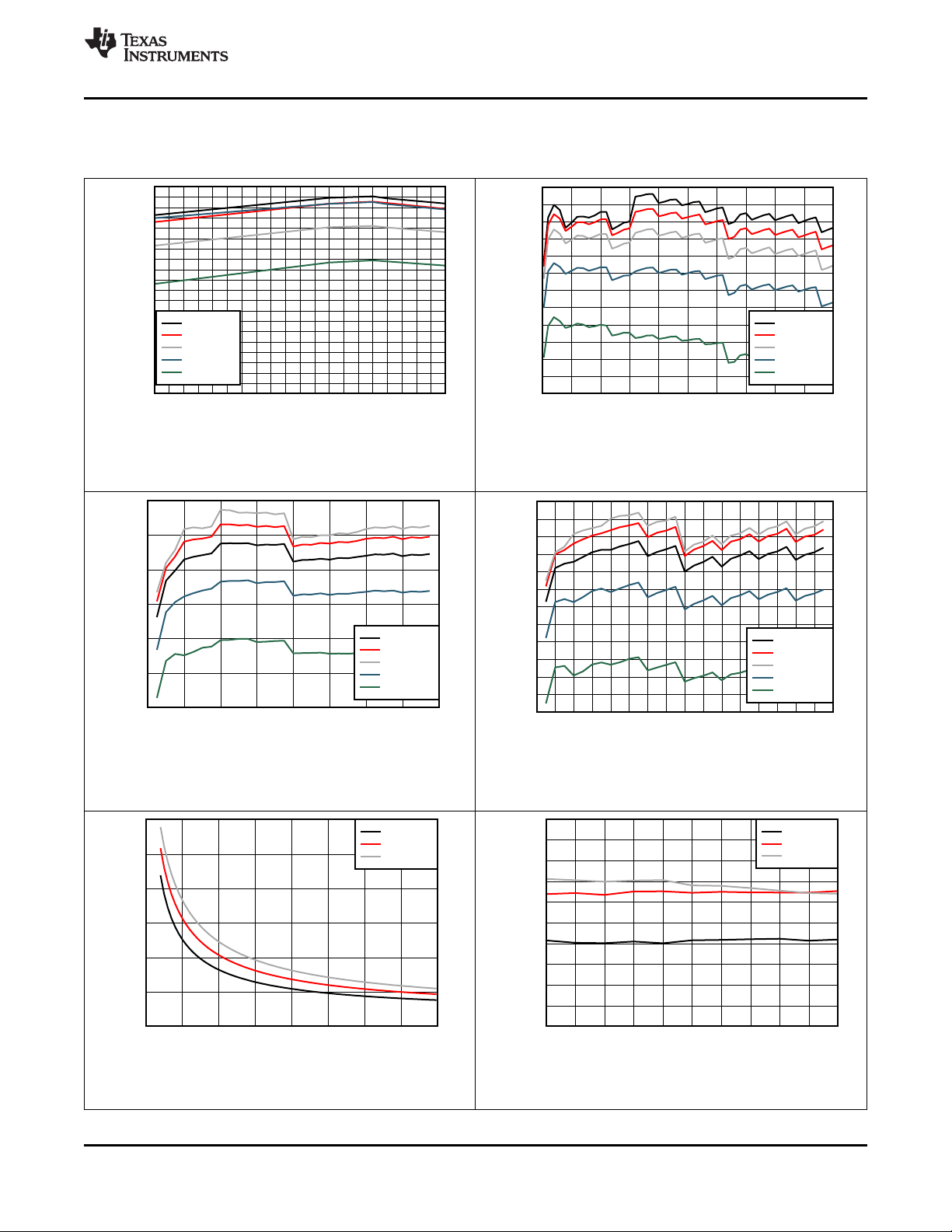

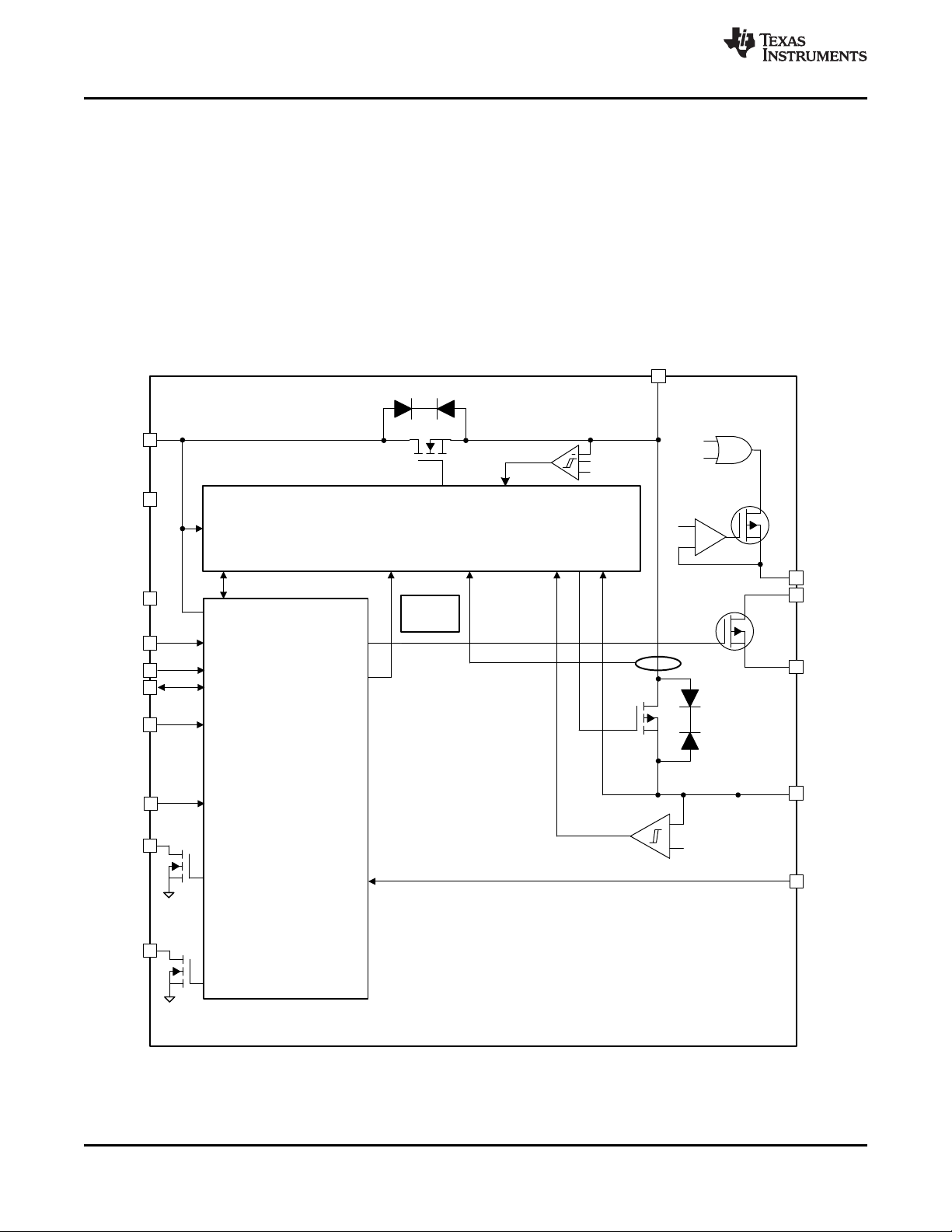

7 Detailed Description

7.1 Overview

The BQ21061 IC is a highly programmable battery management device that integrates a 500-mA linear charger

for single cell Li-Ion batteries, a general purpose LDO that may be configured as a load switch, and a pushbutton controller. Through it's I2C interface the host may change charging parameters such as battery regulation

voltage and charge current, and obtain detailed device status and fault information. The push-button controller

allows the user to reset the system without any intervention from the host and wake up the device from Ship

Mode.

7.2 Functional Block Diagram

12

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

V

BAT

< V

LOWV

Start Precharge

Icharge set by I2C

Connect VIN

Precharge safety

timer expired?

Stop Charging and set

Fault bits

/CE toggled or VIN and

removed and

reconnected?

V

BAT

> V

LOWV

Start FastCharge

Icharge set by I2C

I

BAT

< I

TERM

Fast Charge safety

timer expired?

Charge Done (Set bit

and interrupt and

disconnect BATFET)

V

BAT

< V

BAT

- V

RCH

Yes

No

Yes

No

Yes

No

Yes

No

Yes

No

Yes

No

Yes No

BQ21061

www.ti.com

SLUSDU0 –SEPTEMBER 2019

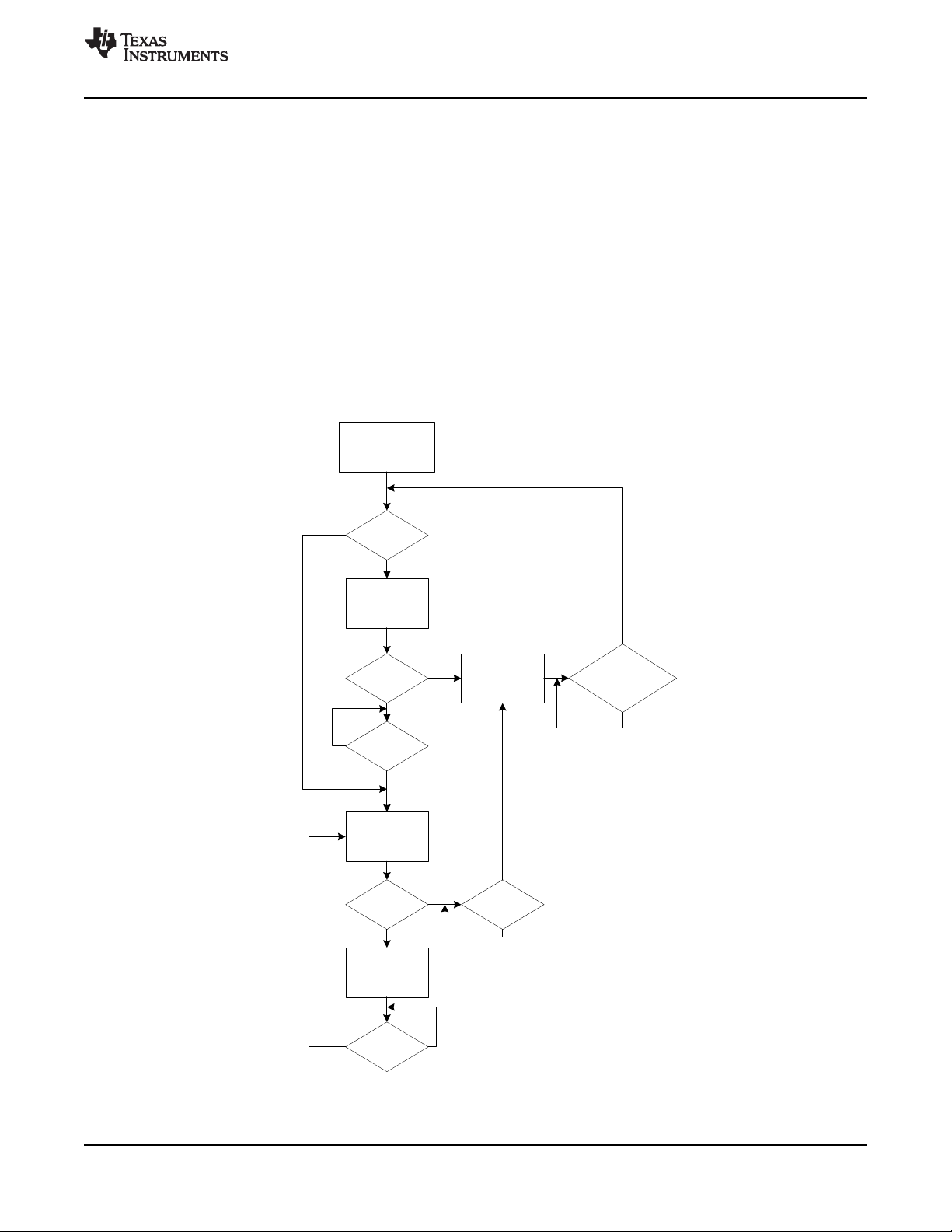

7.3 Feature Description

7.3.1 Linear Charger and Power Path

The BQ21061 IC integrates a linear charger that allows the battery to be charged with a programmable charge

current of up to 500 mA. In addition to the charge current, other charging parameters can be programmed

through I2C such as the battery regulation voltage, pre-charge current, termination current, and input current limit

current.

The power path allows the system to be powered from PMID, even when the battery is dead or charging, by

drawing power from IN pin. It also prioritizes the system load connected to PMID, reducing the charging current,

if necessary, in order support the load when input power is limited. If the input supply is removed and the battery

voltage level is above V

BATUVLO

A more detailed description of the charger functionality is presented in the following sections of this document.

7.3.1.1 Battery Charging Process

The following diagram summarizes the charging process of the BQ21061 charger.

, PMID will automatically and seamlessly switch to battery power.

Figure 16. BQ21061 Charger Flow Diagram

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

13

Product Folder Links: BQ21061

BQ21061

SLUSDU0 –SEPTEMBER 2019

Feature Description (continued)

www.ti.com

When a valid input source is connected (VIN> V

UVLO

and V

BAT+VSLP

< VIN< V

), the state of the CE pin

OVP

determines whether a charge cycle is initiated. When the CE input is high and a valid input source is connected,

the battery charge FET is turned off, preventing any kind of charging of the battery. A charge cycle is initiated

when the CHARGE_DISABLE bit is written to 0 and CE pin in low. Table 1 shows the CE pin and bit priority to

enable/disable charging.

Table 1. Charge Enable Function Through CE Pin and CE Bit

CE PIN CHARGE _DISABLE BIT CHARGING

0 0 Enabled

0 1 Disabled

1 0 Disabled

1 1 Disabled

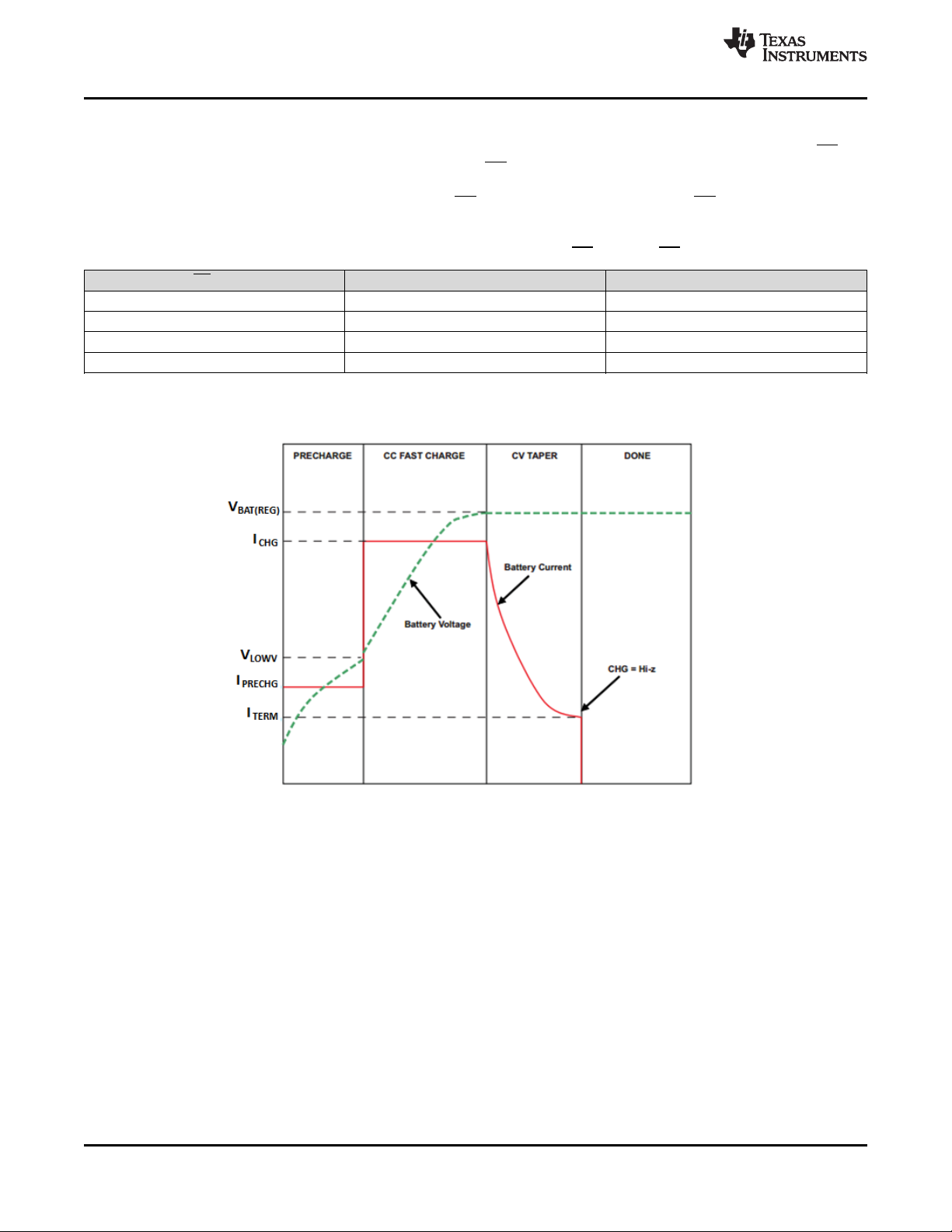

Figure 17 shows a typical charge cycle.

Figure 17. BQ21061 Typical Charge Cycle

During Pre-Charge, where the battery voltage is below the V

level, the battery willl be charge with I

LOWV

PRECHARGE

current which can be programmed through I2C. During pre-charge, the safety timer is set to 25% of the safety

timer value during fast charge. Once the battery voltage reaches V

Charge Mode, charging the battery at I

voltage approaches the V

BATREG

level, the charging current starts tapering off as shown in Figure 17. Once the

CHARGE

charging current reaches the termination current (I

is charged to V

BATREG

level, the regulated PMID voltage should be set to at least 200mV above V

which may also be programmed through I2C. Once the battery

) charging is stopped. Note that to ensure that the battery

TERM

, the charger will then operate in Fast

LOWV

BATREG

Termination is only enabled when the charger CV loop is active in fast charge operation. No termination will

occur if the charge current reaches I

while VINDPM or DPPM is active as well as the thermal regulation

TERM

loop. Termination is also disabled when operating in the TS WARM region. The charger only goes to termination

when the current drops to I

due to the battery reaching the target voltage and not due to the charge current

TERM

limitation imposed by the previously mentioned control loops

Whenever a change in the charge current setting is triggered, whether it occurs due to I2C programming by the

host, Pre-Charge/Fast Charge transition or JEITA TS control, the device will temporarily disable charging (for ~ 1

ms) before updating the charge current value.

14

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

.

BQ21061

www.ti.com

SLUSDU0 –SEPTEMBER 2019

7.3.1.2 JEITA and Battery Temperature Dependent Charging

The charger can be configured through I2C setting to provide JEITA support, automatically reducing the charging

current and voltage depending on the battery temperature as monitored by an NTC thermistor connected to the

BQ21061 TS pin. See External NTC Monitoring (TS) section for details.

7.3.1.3 Input Voltage Based Dynamic Power Management (VINDPM) and Dynamic Power Path Management (DPPM)

The VINDPM loop prevents the input voltage from collapsing to a point where charging would be interrupted by

reducing the current drawn by charger in order to keep VINfrom dropping below V

drops to V

, the VINDPM loops will reduce the input current through the blocking FETs, to prevent the

IN_DPM

. Once the IN voltage

IN_DPM

further drop of the supply voltage. The VINDPM function is disabled by default and may be enabled through I2C

command. The V

IN_DPM

On the other hand, the DPPM loop prevents the system output (PMID) from dropping below V

threshold is programmable through the I2C register from 4.2 V to 4.9 V in 100-mV steps.

+ 200mV when

BAT

the sum of the charge current and system load exceeds the BQ21061 input current limit setting. If PMID drops

below the DPPM voltage threshold, the charging current is reduced. If PMID continues to drop after BATFET

charging current is reduced to zero, the part will enter supplement mode when PMID falls below the supplement

mode threshold (V

BAT

- V

). NOte that DPPM function is disabled when PMID regulation is set to battery

BSUP1

tracking.

When the device enters these modes, the charge current may be lower than the set value and the corresponding

status bits and flags are set. If the 2X timer is set, the safety timer is extended while the loops are active.

Additionally, termination is disabled.

7.3.1.4 Battery Supplement Mode

When the PMID voltage drops below the battery voltage by V

, the battery supplements the system load.

BSUP1

The battery stops supplementing the system load when the voltage on the PMID pin rises above the battery

voltage by V

. During supplement mode, the battery supplement current is not regulated, however, the

BSUP2

Battery Over-Current Protection mechanism is active. Battery charge termination is disabled while in supplement

mode.

7.3.2 Protection Mechanisms

7.3.2.1 Input Over-Voltage Protection

The input over-voltage protection protects the device and downstream components connected to PMID, and BAT

against damage from over-voltage on the input supply. When VIN> V

an OVP fault is determined to exist.

OVP

During the OVP fault, the device turns the input FET off, sends a single 128-µs pulse on INT, and the

VIN_OVP_FAULT FLAG and STAT bits are updated over I2C. Once the OVP fault is removed, the STAT bit is

cleared and the device returns to normal operation. The FLAG bit is not cleared until it is read through I2C after

the OVP condition no longer exists. The OVP threshold for the device is 5.5 V to allow operation from standard

USB sources.

7.3.2.2 Safety Timer and I2C Watchdog Timer

At the beginning of the charge cycle, the device starts the safety timer. If charging has not terminated before the

programmed safety time, t

t

MAXCHG

. When a safety timer fault occurs, a single 128-µs pulse is sent on the INT pin and the

MAXCHG

, expires, charging is disabled. The pre-charge safety time, t

PRECHG

, is 25% of

SAFETY_TMR_FAULT_FLAG bit in the FLAG3 register is updated over I2C. The CE pin or input power must be

toggled in order to reset the safety timer and exit the fault condition. Note that the flag bit will be reset when the

bit is read by the host even if the fault has not been cleared. The safety timer duration is programmable using the

SAFETY_TIMER bits. When the safety timer is active, changing the safety timer duration resets the safety timer.

The device also contains a 2X_TIMER bit that doubles the timer duration prevent premature safety timer

expiration when the charge current is reduced by a high load on PMID (DPPM operation), VIN DPM, thermal

regulation, or a NTC (JEITA) condition. When 2X_TIMER function is enabled, the timer is allowed to run at half

speed when any loop is active other than CC or CV.

In addition, the BQ21061 has a 50s watchdog timer which resets after every I2C transaction. This feature, which

is enabled by default, resets all charger parameters registers to their default values when the timer expires.

Product Folder Links: BQ21061

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

15

J A JA DISS

T T P

T

u

BQ21061

SLUSDU0 –SEPTEMBER 2019

www.ti.com

7.3.2.3 Thermal Protection and Thermal Charge Current Foldback

In order to protect the device from damage due to overheating, the junction temperature of the die, TJ, is

monitored. When TJreaches T

operation when TJfalls below T

SHUTDOWN

SHUTDOWN

During the charging process, the device will reduce the charging current at a rate of (0.04 x I

exceeds the thermal foldback threshold, T

the device stops operation and is turned off. The device resumes

by T

REG

.

HYS

CHARGE

)/°C once T

to prevent further heating. If the charge current is reduced to 0, the

battery supplies the current needed to supply the PMID output. The thermal regulation threshold may be set

through I2C by setting the THERM_REG bits to the desired value.

The die junction temperature, TJ, can be estimated based on the expected board performance using Equation 1:

(1)

Where P

is the total power dissipation in the IC. The θJAis largely driven by the board layout. For more

DISS

information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics

Application Report. Under typical conditions, the time spent in this state is very short.

7.3.2.4 Battery Short and Over Current Protection

In order to protect the device from over current and prevent excessive battery discharge current, the BQ21061

detects if the current on the battery FET exceeds I

(t

DGL_OCP

t

REC_SC

), the battery discharge FET is turned off and start operating in hiccup mode, re-enabling the BATFET

(250 ms) after being turned off by the over-current condition. If the over-current condition is triggered

BAT_OCP

. If the short circuit limit is reached for the deglitch time

upon retry for 3 to 7 consecutive times, the BATFET will then remain off until the part is reset or until Vin is

connected and valid. If the over-current condition and hiccup operation occurs while in supplement mode where

VIN is already present, VIN must be toggled in order for BATFET to be enabled and start another detection

cycle.

In the case where the battery is suddenly shorted while charging and VBAT drops below V

comparator quickly reduces the charge current to I

PRECHARGE

preventing fast charge current to be momentarily

SHORT

, a fast

injected to the battery while shorted.

J

7.3.2.5 PMID Short Circuit

A short on the PMID pin is detected when the PMID voltage drops below 1.6 V (PMID short threshold). PMID

short threshold has a 200-mV hysteresis. When this occurs, the input FET temporarily disconnects IN for up to

200 µs to prevent stress on the device if a sudden short condition happens, before allowing a softstart on the

PMID output.

7.3.3 VDD LDO

The device integrates a low current always-on LDO that serves as the digital I/O supply to the device. This LDO

is supplied by VIN or by BAT. The VDD LDO will remain on through all power states with the exception of Ship

Mode.

7.3.4 Load Switch/LDO Output and Control

The device integrates a low Iq load switch which can also be used as a regulated output. The LDO/LS has a

dedicated input pin VINLS and can support up to 150 mA of load current.

The LS/LDO may be enabled/disabled through I2C. The output voltage is programmable using the LS_LDO bits

in the registers. To limit voltage drop or voltage transients, a small ceramic capacitor must be placed close to

VINLS pin. Due to the body diode of the PMOS switch, it is recommended to have the capacitor on VINLS ten

times larger than the output capacitor on LS/LDO output.

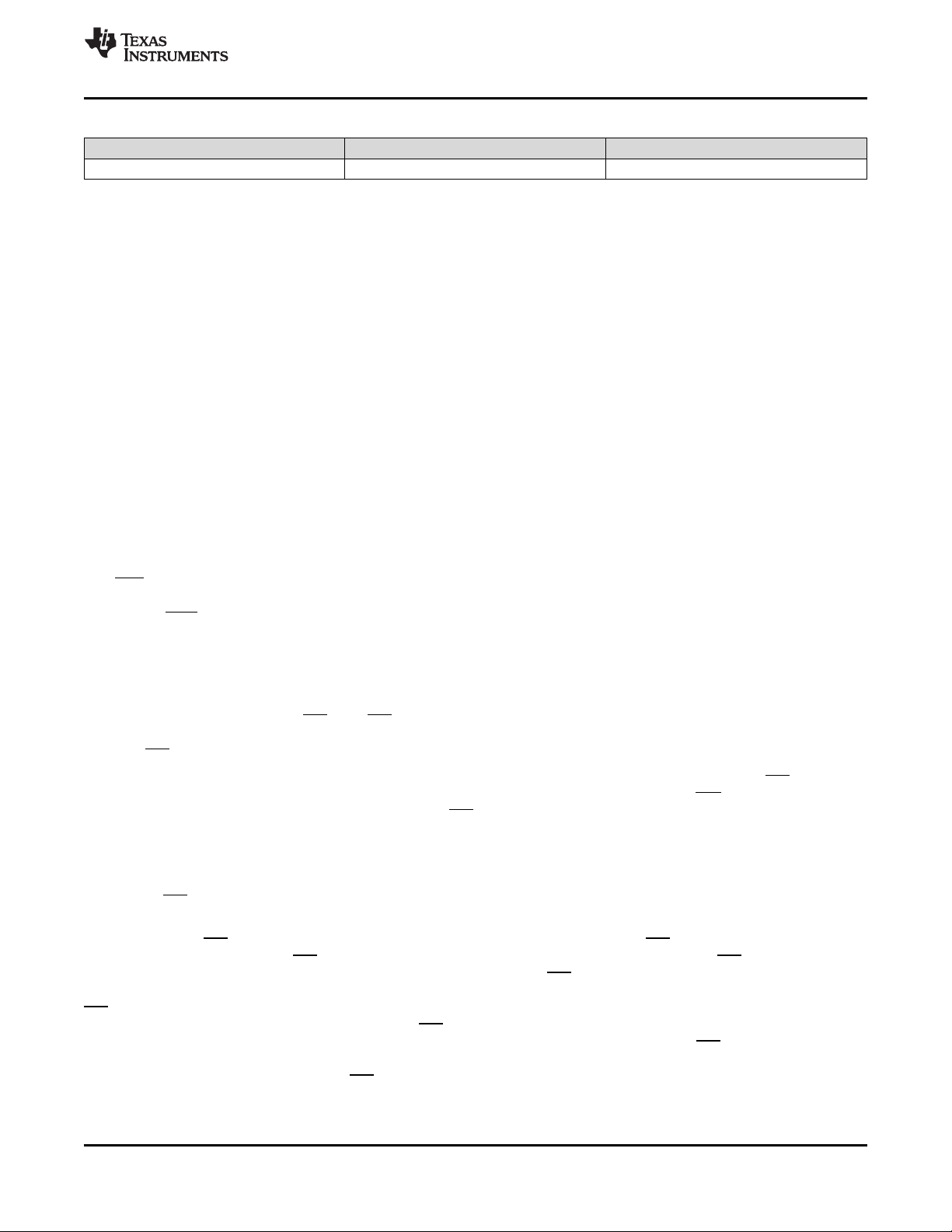

Table 2. LDO Mode Control

I2C EN_LS_LDO LS_CONFIG LS/LDO OUTPUT

0 0 Pulldown

0 1 Pulldown

1 0 LDO

16

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

BQ21061

www.ti.com

SLUSDU0 –SEPTEMBER 2019

Table 2. LDO Mode Control (continued)

I2C EN_LS_LDO LS_CONFIG LS/LDO OUTPUT

1 1 Load Switch

The current capability of the LDO will depend on the VINLS input voltage and the programmed output voltage.

When the LS/LDO output is disabled through the register, an internal pull-down will discharge the output. The

LDO has output current limit protection, limiting the output current in the event of a short in the output. When the

LDO output current limit trips and is active for at least 1 ms, the device will set a flag and send an interrupt to the

host. The host must take action to disable the LDO if desired. The LDO may be set to operate as a load switch

by setting the LS_SWITCH_CONFG bit. Note that in order to change the configuration the LDO must be disabled

first, then the LS_SWITCH_CONFG bit is set for it to take effect.

7.3.5 PMID Power Control

The BQ21061 offers the option to control PMID through the I2C PMID_MODE bits. These bits can force PMID to

be supplied by BAT instead of IN, even if VIN> V

BAT

+ V

. They can also disconnect PMID, pulling it down or

SLP

leaving it floating. SeeTable 30 for details.

7.3.6 System Voltage (PMID) Regulation

The BQ21061 has a regulated system voltage output (PMID) that is programmable through I2C. PMID regulation

is only active when the adapter is connected and VIN> V

UVLO

, VIN> V

BAT

_ V

and VIN< V

SLP

. In Battery

OVP

Tracking operation (PMID_REG_CTRL = 000), the PMID voltage will be regulated to about 4.7% over battery

level (V

be at least 200mV higher than V

PMID

= V

x 1.047) or 3.8 V, whichever is higher. Note that the PMID regulation target should be set to

BAT

BATREG

.

7.3.7 MR Wake and Reset Input

The MR input has three main functions in the BQ21061. First, it serves as a means to wake the device from Ship

Mode. Second, it serves as a short button press detector, sending an interrupt to the host when the button

driving the MR pin has been pressed for a given period of time. This allows the implementation of different

functions in the end application such as menu selection and control. And finally it serves as a mean to get the

BQ21061 to reset the system by performing a power cycle (shut down PMID and automatically powering it back

on) or go to Ship Mode after detecting a long button press. The timing for the short and long button press

duration is programmable through I2C for added flexibility. Note that if a specific timer duration is changed

through I2C while that timer is active and has not expired, the new programmed value will be ignored until the

timer expires and/or is reset by MR. The MR input has an internal pull-up to BAT.

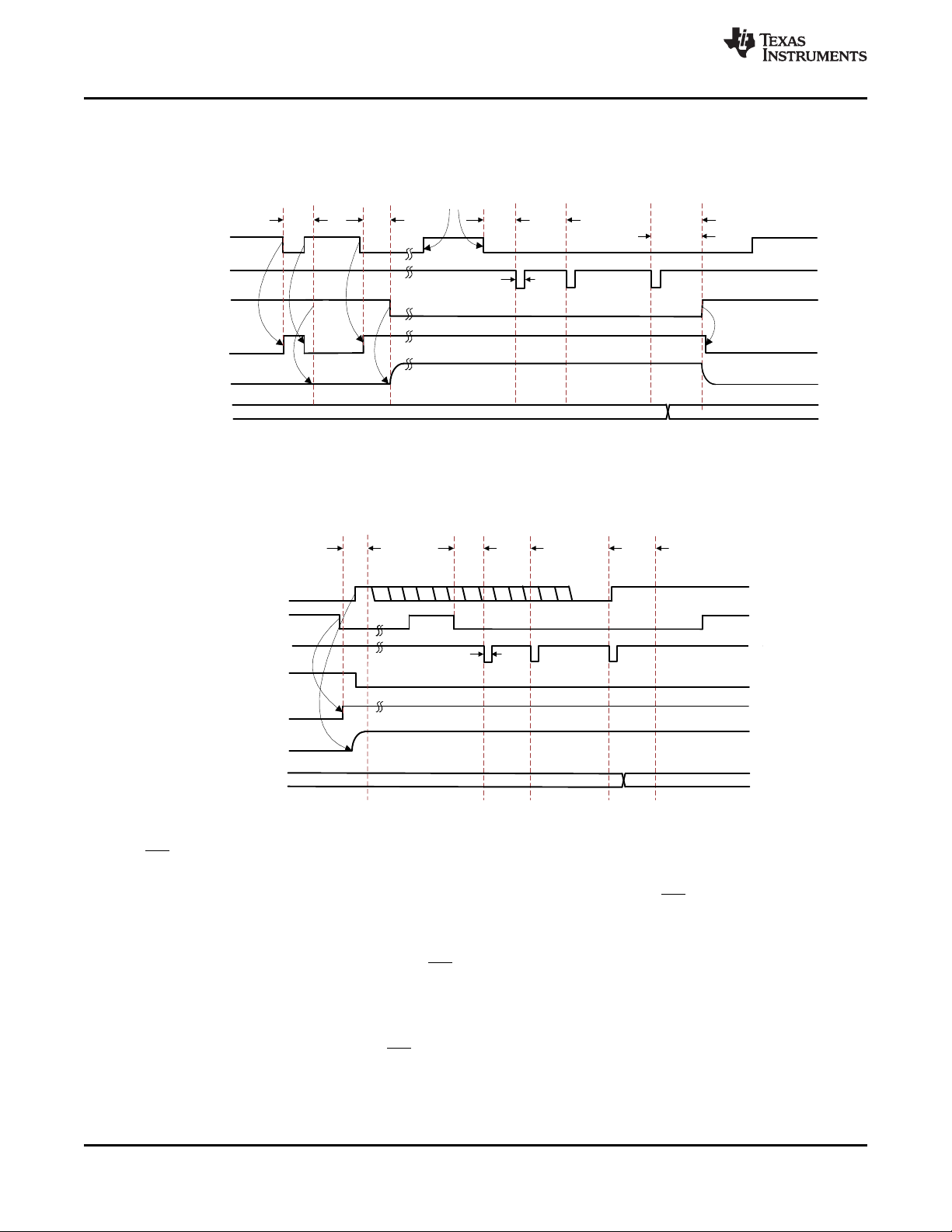

7.3.7.1 MR Wake or Short Button Press Functions

There are two programmable wake or short button press timers, WAKE1 and WAKE2. When the MR pin is held

low for t

WAKE1

the device sends an interrupt (128 µs active low pulse in the INT pin) and sets the

MRWAKE1_TIMEOUT flag when it expires. If the MR pin continues to be driven low after WAKE1 and the

WAKE2 timer expires, the BQ21061 sends a second interrupt and sets the MRWAKE2_TIMOUT flag. WAKE1 is

used as the timer to wake the device from ship mode. WAKE2’s only function is to send the interrupt and has no

effect on other BQ21061 functions. These flags are not cleared until they have been read by the host. Note that

interrupts are only sent when the flags are set and the flags must be cleared in order for another interrupt to be

sent upon MR press. The timer durations can be set through the MR_WAKEx_TIMER bits in the MRCTRL

Register section.

One of the main MR functions is to wake the device from Ship Mode when the MR is asserted. The device will

exit the Ship Mode when the MR pin is held low for at least t

. Immediately after the MR is asserted, VDD

WAKE1

will be enabled and the digital will start the WAKE counter. If the MR signal remains low until after the WAKE1

timer expires, the device will power up PMID and LDO (If enabled) completing the exit from the ship mode. If the

MR signal goes high before the WAKE1 timer expires, the device will go back to the Ship Mode operation, never

powering up PMID or the LDO. Note that if the MR pin remains low after exiting Ship Mode the wake interrupts

will not be sent and the long button press functions like HW reset will not occur until the MR pin is toggled. In the

case where a valid VIN(VIN> V

) is connected prior to WAKE2 timer expiring, the device will exit the ship

UVLO

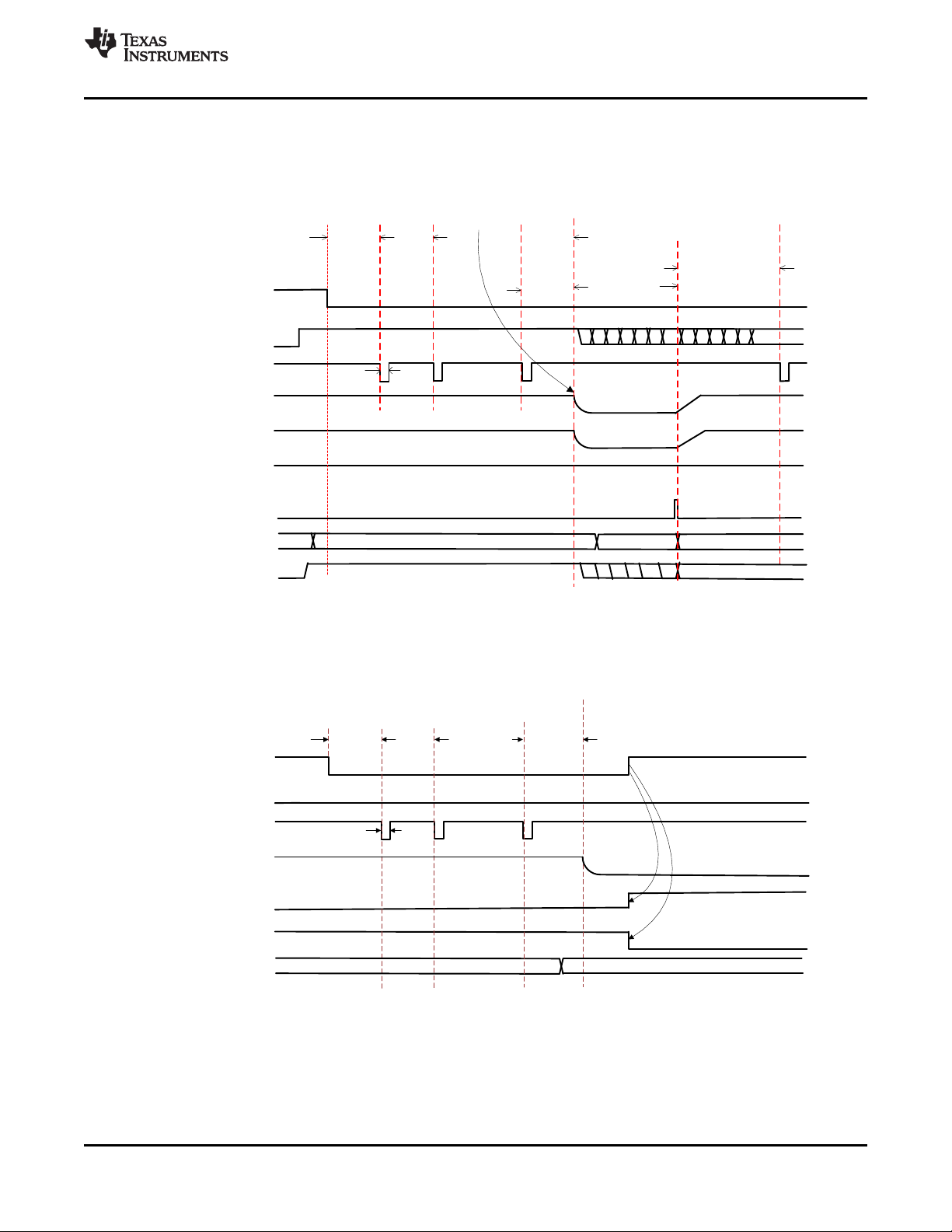

mode immediately regardless of the MR or wake timer state. Figure 18 and Figure 19 show these different

scenarios.

Product Folder Links: BQ21061

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

17

/MR

INT

SHIPMODE

VDD

twake1

twake2

treset_warn

thwreset

128us

twake1

Output Rails

(PMID, LDO if enabled)

VIN

MR_LPRESS_ACTION

Go to Ship Mode

'RQ¶WFDUH

twake1

twake2

thwreset

128us

twake1

No WAKE interrupts

are sent or reset

actions are taken

until /MR is toggled

after Ship Mode exit

Go to Ship Mode

/MR

INT

SHIPMODE

VDD

Output Rails

(PMID, LDO if enabled)

MR_LPRESS_ACTION 'RQ¶WFDUH

twake1

Thwreset_warn

BQ21061

SLUSDU0 –SEPTEMBER 2019

Figure 18. MR Wake from Ship Mode (MR_LPRESS_ACTION = Ship Mode, VIN not valid)

www.ti.com

Figure 19. MR Wake from Ship Mode – VIN Dependencies

7.3.7.2 MR Reset or Long Button Press Functions

The BQ21061 device may be configured to perform a system hardware reset (Power Cycle/Autowake), go into

Ship Mode, or simply do nothing after a long button press (for example, when the MR pin is driven low until the

MR_HW_RESET timer expires).The action taken by the device when the timer expires is configured through the

MR_LPRESS_ACTION bits in the ICCTRL1 Register section. Once the MR_HW_RESET timer expires the

device immediately performs the operation set by the MR_LPRESS_ACTION bits. The BQ21061 sends an

interrupt to the host when the device detects that MR has been pressed for a period that is within t

from reaching t

which would trigger a HW Reset or used as another button press timer interrupt like the WAKE1 and WAKE2

timers. This interrupt is sent before the MR_HW_RESET timer expires and sets the MRRESET_WARN flag. The

t

HW_RESET_WARN

change the reset behavior at any time after MR going low and prior to the MR_HW_RESET timer expiring. It may

not change it however from another behavior to a HW reset (Power Cycle/Autowake) since a HW reset can be

gated by other condition requirements, such as VIN presence (controlled by MR_RESET_VIN bit), throughout the

whole duration of the button press. This flexibility allows the host to abort any reset or power shutdown to the

system by overriding a long button press command.

18

Submit Documentation Feedback Copyright © 2019, Texas Instruments Incorporated

HW_RESET

. This may warn the host that the button has been pressed for a period close to t

may be set through I2C by the MR_RESET_WARN bits in the MRCTRL register. The host may

HW_RESET_WARN

HW_RESET

Product Folder Links: BQ21061

/MR

INT

SHIPMODE

VDD

twake1

twake2

Treset_warn

thwreset

128us

PMID & LDO

Shipmode enabled when both

MR has gone high and

thwreset has expired

VIN

MR_RESET_VIN has no effect

on this mode

MR_LPRESS_ACTION

'RQ¶WFDUH

Go to Shipmode

/MR

INT

PMID

LDO

VDD

SW reset

twake1

twake2

treset_

warn

thwreset

t_restart

128us

twake1

VIN

Once thwreset timer

expires and decision to

power cycle is done,

the device will always

complete the wake

after t_restart, no

matter change in VIN,

or bit control

MR_LPRESS_ACTION

'RQ¶WFDUH

00 - PowerCycle (AutoWake)

MR_RESET_VIN

Default

Default

BQ21061

www.ti.com

SLUSDU0 –SEPTEMBER 2019

A HW reset may also be started by setting the HW_RESET bit. Note that during a HW reset , VDD remains on.

Figure 21. MR Wake and Reset Timing Active Mode When MR_LPRESS_ACTION = 1x (Ship Mode) and

Figure 20. MR Wake and Reset Timing with VIN Present or BAT Active Mode When

MR_LPRESS_ACTION = 00

Only BAT is Present

Submit Documentation FeedbackCopyright © 2019, Texas Instruments Incorporated

Product Folder Links: BQ21061

19

Loading...

Loading...