Page 1

ADS5525/27/45/46/47 EVM User

Guide

User's Guide

November 2006

SLWU028B

Page 2

2 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 3

Contents

1 Overview .................................................................................................................... 5

1.1 EVM Basic Functions ............................................................................................ 5

2 EVM Quick Start Guide ................................................................................................ 6

2.1 EVM LVDS Output Mode Quick Start (Default) .............................................................. 6

2.2 EVM CMOS Output Mode Quick Start ........................................................................ 6

3 Circuit Description ...................................................................................................... 7

3.1 Schematic Diagram .............................................................................................. 7

3.2 Circuit Function ................................................................................................... 7

4 Expansion Options .................................................................................................... 13

4.1 Custom FPGA Code ........................................................................................... 13

4.2 Expansion Slot .................................................................................................. 13

4.3 Optional USB SPI Interface ................................................................................... 13

5 Physical Description .................................................................................................. 14

5.1 PCB Layout ...................................................................................................... 14

5.2 Bill of Materials .................................................................................................. 20

5.3 PCB Schematics ................................................................................................ 25

SLWU028B – January 2006 – Revised November 2006 Table of Contents 3

Submit Documentation Feedback

Page 4

List of Figures

1 ADS5547 SNR Performance vs Decoupling ............................................................................. 8

2 THS4509 + ADS5545 EVM Performance ................................................................................ 9

3 Eye Diagram of Data on Header J4. ..................................................................................... 11

4 Top Layer .................................................................................................................... 14

5 Layer 2, Ground Plane .................................................................................................... 15

6 Layer 3, Power Plane #1 .................................................................................................. 16

7 Layer 4, Power Plane #2 .................................................................................................. 17

8 Layer 5, Ground Plane .................................................................................................... 18

9 Layer 6, Bottom Layer ..................................................................................................... 19

List of Tables

1 DIP Switch SW1 ............................................................................................................. 7

2 EVM Power Options ......................................................................................................... 8

3 Output Connector J4 ....................................................................................................... 10

4 Test Points .................................................................................................................. 12

5 Bill of Materials ............................................................................................................. 21

4 List of Figures SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 5

1 Overview

1.1 EVM Basic Functions

User's Guide

SLWU028B – January 2006 – Revised November 2006

This manual assists users in using the ADS5525/27/45/46/47 evaluation module (EVM) for evaluating the

performance of the ADS5525/27/45/46/47 (ADCs). The EVM provides a powerful and robust capability in

evaluation of the many features of the ADCs and the performance of the device der many conditions.

Analog input to the ADC is provided via external SMA connectors. The user supplies a single-ended input,

which is converted into a differential signal. One input path uses a differential amplifier, while the other

input is transformer-coupled.

The EVM provides an external SMA connector for input of the ADC clock. The single-ended input is

converted into a differential signal at the input of the device.

Digital output from the EVM is via a 40-pin connector.

Power connections to the EVM are via banana jack sockets. Separate sockets are provided for the ADC

analog and digital supplies, the FPGA supply, and the differential amplifier supply.

CAUTION

Exceeding the maximum input voltages can damage EVM components.

Undervoltage may cause improper operation of some or all of the EVM

components.

Xilinx, Spartan, WebPACK are trademarks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

SLWU028B – January 2006 – Revised November 2006 5

Submit Documentation Feedback

Page 6

www.ti.com

EVM Quick Start Guide

2 EVM Quick Start Guide

The ADC has two basic modes of output operation, ensuring compatibility in a broad range of systems.

Follow the steps below to get the EVM operating quickly with the ADC in either DDR LVDS output mode

or CMOS output mode.

Note: Follow the steps in the listed order; not doing so could result in improper operation.

2.1 EVM LVDS Output Mode Quick Start (Default)

1. Ensure a jumper is installed between pins 1 and 2 on JP2.

2. Ensure DIP switch SW1, switch 2 is set to LVDS.

3. Ensure DIP switch SW1, switch 8 is set to PARALLEL.

4. Use a regulated power supply to provide 3.3 VDC to the ADC at J11 and J15, with the corresponding

returns connected to J9 and J16.

5. Use a regulated power supply to provide a 5-VDC input to J14, while connecting the return to J17.

6. Provide a filtered, low-phase-noise, sinusoidal 1.5-Vrms, 170-MHz clock to J7.

7. Provide a filtered, sinusoidal analog input to J3.

8. Using a logic analyzer and Table 3 in this manual, monitor the ADC output on J4.

2.2 EVM CMOS Output Mode Quick Start

1. Ensure a jumper is installed between pins 2 and 3 on JP2.

2. Ensure DIP switch SW1, switch 2 is set to CMOS.

3. Ensure DIP switch SW1, switch 8 is set to PARALLEL.

4. Use a regulated power supply to provide 3.3 VDC to the ADC at J11 and J15, with the corresponding

returns connected to J9 and J16.

5. Use a regulated power supply to provide a 5-VDC input to J14, while connecting the return to J17.

6. Provide a low-phase-noise, sinusoidal 1.5-Vrms, 170-MHz clock to J7.

7. Provide a filtered sinusoidal analog input to J3.

8. Briefly depress S1, which resets the EVM.

9. Using a logic analyzer and Table 3 in this manual, monitor the ADC output on J4.

6 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 7

www.ti.com

3 Circuit Description

3.1 Schematic Diagram

The schematic diagram for the EVM is in Section 5.3 of this document.

3.2 Circuit Function

The following paragraphs describe the function of individual circuits. See the data sheet for complete

device operating characteristics.

3.2.1 Configuration Options

The EVM provides a DIP switch, SW1, to control many of the modes of operation when the EVM is

configured for parallel-mode operation. Table 1 describes the functionality of the DIP switches.

Note: When the device is configured for serial-mode operation (SW1, switch 8), the DIP settings

SW1 SWITCH

NUMBER

Circuit Description

on SW1, switch 1 through SW1, switch 7 are ignored.

Table 1. DIP Switch SW1

OFF ON DESCRIPTION

1 2s complement Offset binary Determines device output format

2 LVDS CMOS Determines device output mode

3 Reserved Reserved Reserved

4 Internal reference External reference When set to External Reference, ADC uses common-mode

voltage on TP1.

5 Edge = 1 Edge = 2 Allows for output edge programmability

6 Edge = 3 Edge = 4 Allows for output edge programmability

7 Normal Power down Allows for power down

8 Serial Parallel Determines mode for register interface

By switching SW1, switch 8 to OFF, the ADC operates in serial mode, using its programmed register

contents. A complete register map can be found in the device datasheet. Three pins on header J6 have

been reserved for programming the device while it operates in serial mode. To program the device

registers using header J6, place SCLK on pin 21, SDATA on pin 23, and SEN on pin 25. A pattern

generator can be used to generate the patterns needed for programming. Alternatively, TI provides an

optional USB daughtercard that plugs into the expansion slot of the EVM. The USB daughtercard allows

ADC register control via a software package loaded onto the PC.

3.2.2 Power

Power is supplied to the EVM via banana jack sockets. The EVM offers the capability to supply analog

and digital 3.3 V independently to the ADC. Table 2 offers a snapshot of the power-supply options. All

supply connections are required for default operation, except J12, J10, J13, and J20.

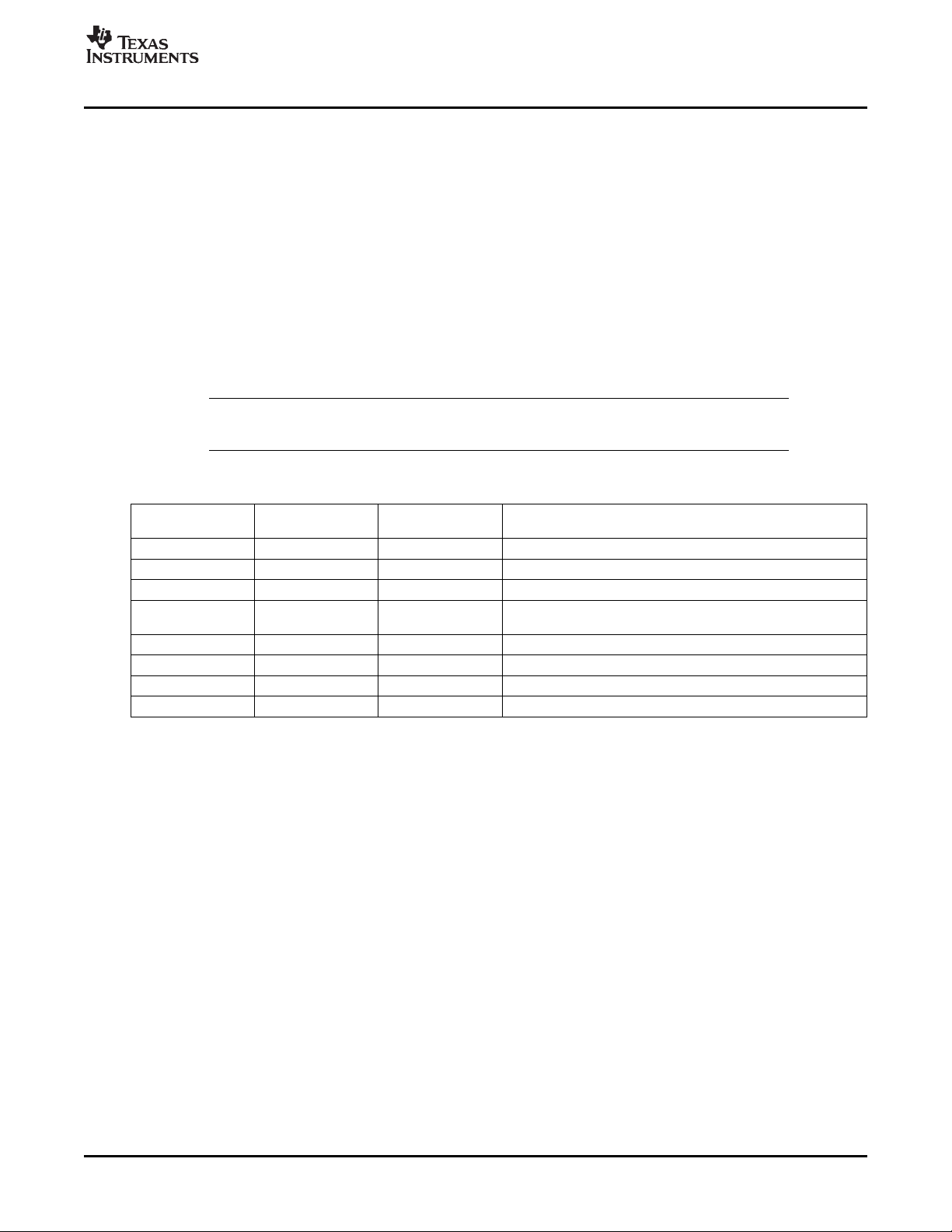

The EVM provides local decoupling for the ADC; however, the ADC features internal decoupling, and in

many cases minimal external decoupling can be used without loss in performance. Users are encouraged

to experiment to find the optimal amount of external decoupling required for their application. Figure 1

shows the ADS5547 LVDS-mode performance with all of the decoupling capacitors installed and the

performance with C4, C5, C6, C7, C8, C9, and C10 removed. By default, the EVM comes with all of the

decoupling capacitors installed.

SLWU028B – January 2006 – Revised November 2006 7

Submit Documentation Feedback

Page 8

www.ti.com

fIN − Input Frequency − MHz

SNR − Signal-to-Noise Ratio − dBFS

G001

9.97 19.94 30.13 40.33 50.13 60.13 69.59 79.87 89.75 100.33 130.13 170.13

68

69

70

71

72

73

74

1 Decoupling Cap

Baseline-All Decoupling Caps

Circuit Description

Table 2. EVM Power Options

BANANA JACK NAME VOLTAGE DESCRIPTION

J9 Device AGND GND

J10 AGND GND

J11 Device AVDD 3.3 Device analog supply

J12 Amplifier negative –5 THS4509 Vs– supply

J13 Amplifier positive rail 5 THS4509 Vs+ supply

J14 Auxiliary power 5 Supplies power to all peripheral circuitry including the FPGA

J15 Device DVDD 3.3 Device internal digital output supply

J16 DGND GND

J17 DGND GND

J20 If TP11, TP12, and TP13 are tied low, the TPS75003 is

rail

and PROM. Voltages rails are created by using TI's TPS75003

voltage regulator.

disabled. In this case, one can supply 3.3 V to pin 1, 1.2 V to

pin 2, and 2.2 V to pin 3 of J20 while connecting the ground to

J17.

Figure 1. ADS5547 SNR Performance vs Decoupling

3.2.3 Analog Inputs

The EVM can be configured to provide the ADC with either transformer-coupled or differential amplifier

inputs from a single-ended source. The inputs are provided via SMA connector J3 for transformer-coupled

input or SMA connector J1 for differential amplifier input. To set up for one of these options, the EVM must

be configured as follows:

1. For a 1:1 transformer-coupled input to the ADC, a single-ended source is connected to J3. Confirm

that SJP4 has pins 2 and 3 shorted, and that SJP5 has pins 2 and 3 shorted. The transformer used,

the Mini-Circuits TC4-1W, forms an inherent band-pass filter with a pass band from 3 MHz to 800 MHz.

This is the default configuration for the EVM.

2. One can use a TI THS4509 amplifier to drive the ADC by applying an input to J1. Reconfigure SJP4

and SJP5 such that both have pins 1 and 2 shorted. A 5-VDC supply must be connected to the board

to provide power to U3 for this configuration.

8 SLWU028B – January 2006 – Revised November 2006

The THS4509 amplifier path converts a single-ended signal presented on J1 into a differential signal.

Submit Documentation Feedback

Page 9

www.ti.com

0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 75 80 85

f − Frequency − MHz

Amplitude − dBFS

G002

1

−135

−120

10

−130

−110

−100

−90

−80

−70

−60

−50

−40

−30

−20

−10

0

2

3

4

5

x

Circuit Description

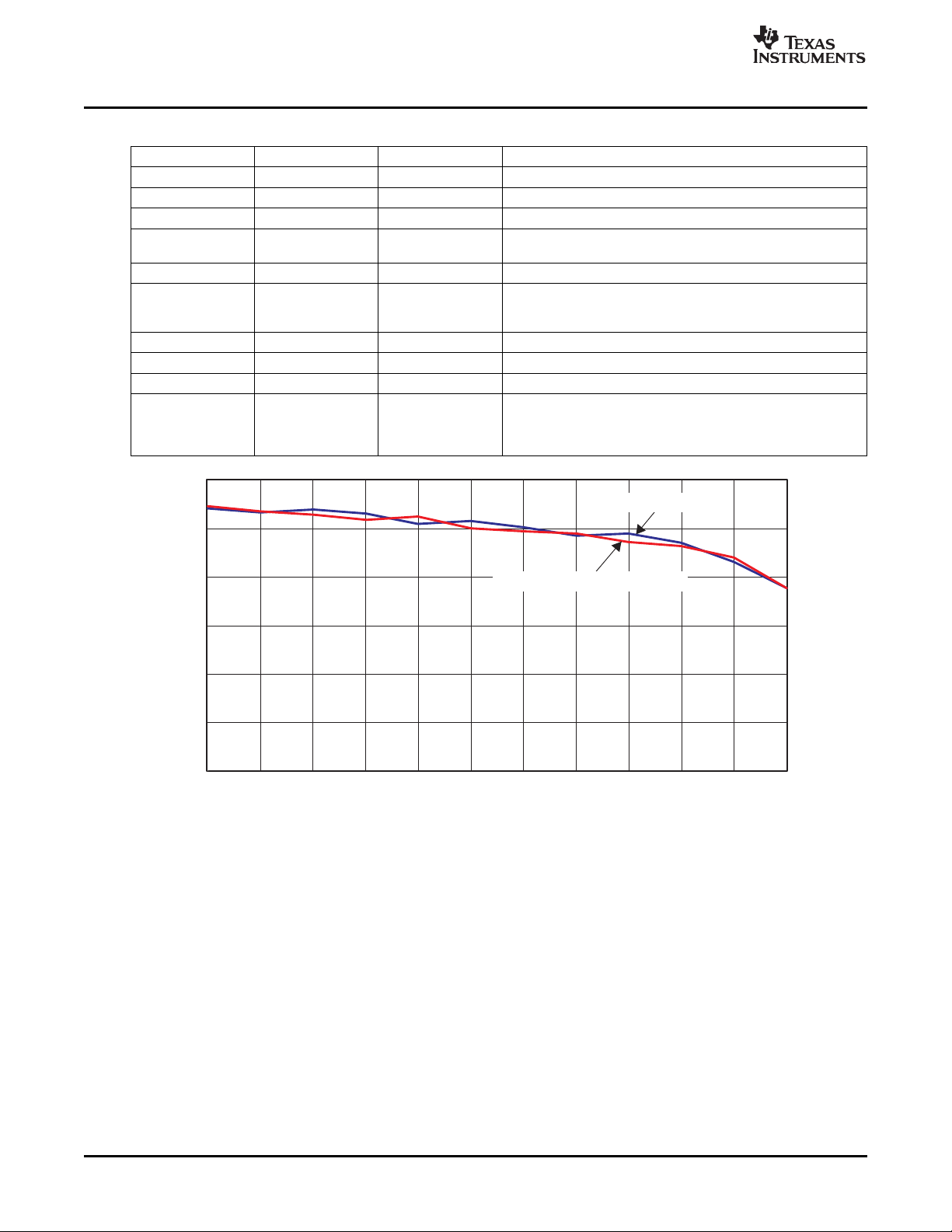

The schematics present various interface options between the amplifier and the ADC. Depending on

the input frequencies of interest, further performance optimization can be had by designing a

corresponding filter. In its default configuration, R43, R44, and C119 form a first-order, low-pass filter

with a cutoff frequency of 70 MHz. Figure 2 shows the performance of the ADS5545 using the

THS4509 path.

3.2.4 Clock Input

3.2.5 Digital Outputs

SLWU028B – January 2006 – Revised November 2006 9

Submit Documentation Feedback

Figure 2. THS4509 + ADS5545 EVM Performance

A single-ended, harmonically filtered, low-phase-noise, 1.5-Vrms sinusoidal input should be applied to J7.

The frequency must not exceed the device specification. In the EVM default configuration, both SPJ1 and

SJP2 must have pins 1 and 2 shorted.

In the board default configuration, the transformer provides single-ended to differential conversion. The

transformer has an impedance ratio of 4.

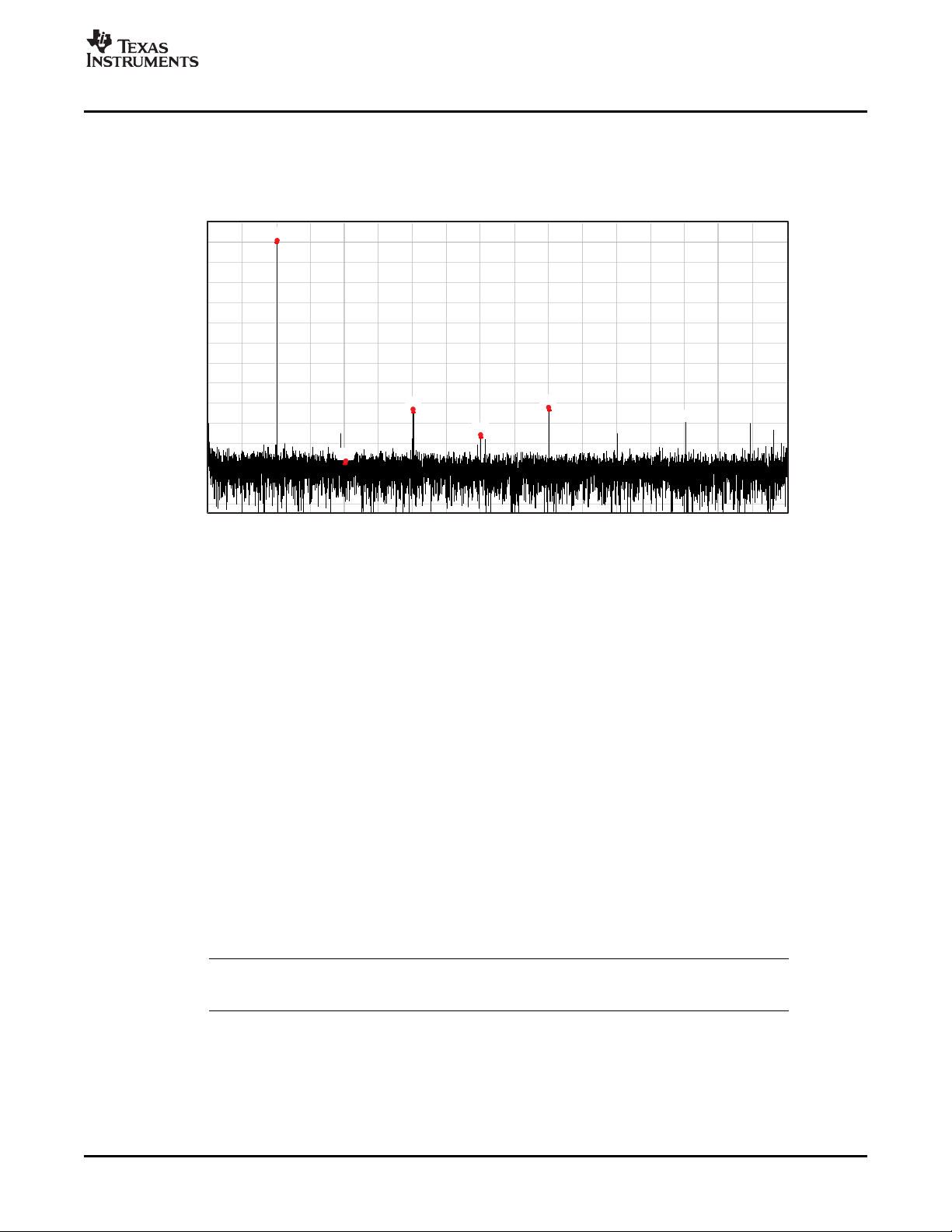

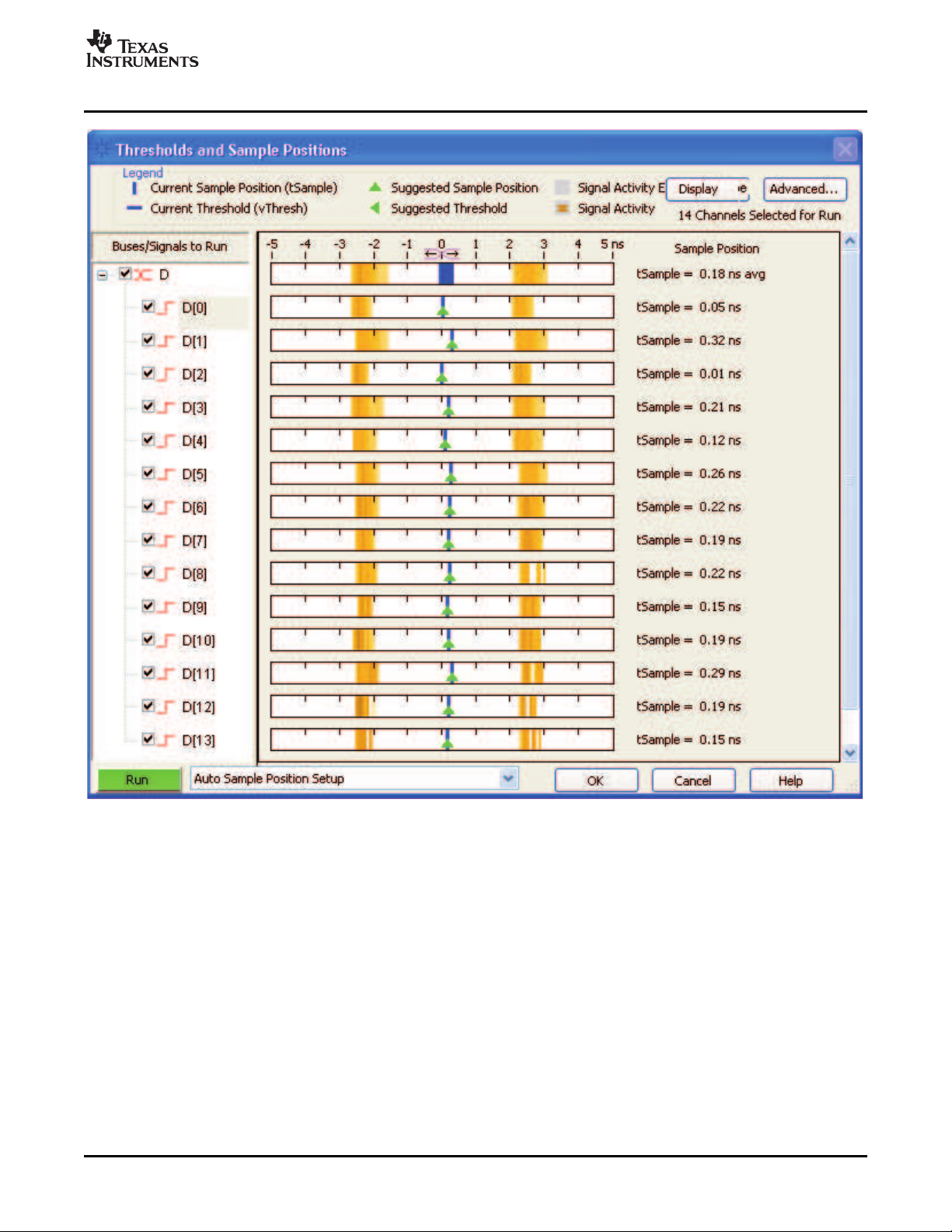

For compatibility with a broad range of logic analyzers, the EVM outputs 3.3-V parallel CMOS data on

header J4, independent of the ADC operational mode. The Xilinx™Spartan™-3E FPGA provides the

necessary translation, and it configures itself using one of two different logic files stored in the PROM,

based on the EVM configuration. The CMOS data output of the FPGA is contained in data header J4 and

is a standard 40-pin header on a 100-mil grid, which allows easy connection to a logic analyzer. The

connector pinout is listed in Table 3 . For quick setup, the eye diagram is shown in Figure 3 . No setup or

hold-time adjustments must be made to the logic analyzer if using the rising edge of the output clock to

latch in the data.

Note: The eye diagram shown is the output of the FPGA at 210 MSPS, not that of the ADC. For

the ADC output timing, see the respective device data sheet.

Page 10

www.ti.com

Circuit Description

Table 3. Output Connector J4

J4 PIN ADS5525/27 DESCRIPTION ADS5545/46/47 DESCRIPTION

1 CLK CLK

2 GND GND

3 NC NC

4 GND GND

5 Reserved Reserved

6 GND GND

7 Reserved Reserved

8 GND GND

9 NC Data bit 0 (LSB)

10 GND GND

11 NC Data bit 1

12 GND GND

13 Data bit 0 (LSB) Data bit 2

14 GND GND

15 Data bit 1 Data bit 3

16 GND GND

17 Data bit 2 Data bit 4

18 GND GND

19 Data bit 3 Data bit 5

20 GND GND

21 Data bit 4 Data bit 6

22 GND GND

23 Data bit 5 Data bit 7

24 GND GND

25 Data bit 6 Data bit 8

26 GND GND

27 Data bit 7 Data bit 9

28 GND GND

29 Data bit 8 Data bit 10

30 GND GND

31 Data bit 9 Data bit 11

32 GND GND

33 Data bit 10 Data bit 12

34 GND GND

35 Data bit 11 (MSB) Data bit 13 (MSB)

36 GND GND

37 NC NC

38 GND GND

39 NC NC

40 GND GND

10 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 11

www.ti.com

C001

Circuit Description

Figure 3. Eye Diagram of Data on Header J4.

3.2.6 Test Points

For added EVM visibility and control, several test points are provided. Table 4 summarizes the test points

available.

SLWU028B – January 2006 – Revised November 2006 11

Submit Documentation Feedback

Page 12

www.ti.com

Circuit Description

3.2.7 LED Operation

Table 4. Test Points

TP DESCRIPTION

TP1 ADC common mode, input or output

depending on the setting of SW1, switch 4

TP3 THS4509 power down

TP4 ADC output enable

TP5 AGND

TP6 AGND

TP7 AGND

TP8 DGND

TP9 FPGA M0 pin; determines which FPGA logic

file to load

TP10 ADC SCLK

TP11 TPS75003 1.2 enable

TP12 TPS75003 2.5 enable

TP13 TPS75003 3.3 enable

To give greater visibility into the EVM operations, two LEDs are provided, D3 and D4. On power up, D4 is

asserted when a successful FPGA boot up is complete. For correct EVM operation, the LED should be

asserted at all times. LED D3 is asserted when the ADC and FPGA are operating and decoding in DDR

LVDS mode, and is not asserted when the ADC is functioning in CMOS mode. Furthermore, in either DDR

LVDS mode or CMOS mode, LED D3 blinks when an ADC overrange condition occurs.

CAUTION

If LED D3 is blinking, the amplitude coming into the ADC input (J3 or J4) must

be attenuated immediately; otherwise, damage to the ADC could occur.

12 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 13

www.ti.com

4 Expansion Options

The EVM offers several exciting possibilities to expand the capabilities of the EVM. This allows the utmost

flexibility when prototyping an ADC circuit under conditions that mimic the end system, without the need to

develop a custom prototype board.

4.1 Custom FPGA Code

Using a standard JTAG interface on JP1, users have the ability to load custom logic onto the FPGA,

rapidly speeding up digital development time. This allows the flexibility of prototyping and debugging an

ADC digital interface design before developing application-specific hardware.

To take advantage of the onboard FPGA, users can download the free Xilinx WebPACK™ from the Xilinx

Web site. Select the XC3S250E-4FT256 as the FPGA and the XCF16PFSG48 as the PROM.

Note: See the Xilinx Spartan-3E Web site for complete documentation of the FPGA at:

Schematically, the FPGA is configured in BPI mode, and it samples FPGA pins M2, M1, and M0 when the

FPGA's INIT_B is brought low. Depending of the status of M0, it boots from either the top or the bottom of

the PROM contents. The PROM allows for the storage of two FPGA bit files. In its default condition, the

EVM stores one file for ADC CMOS output at the beginning of the PROM address space and one file for

ADC LVDS output at the end of the PROM address space.

Note: When creating custom FPGA code, store any custom-developed bit files for ADC CMOS

Expansion Options

http://direct.xilinx.com/bvdocs/publications/ds312.pdf

operation in the PROM revision 0 space, and store any custom-developed FPGA code for

ADC LVDS operation in the PROM revision 1 space.

4.2 Expansion Slot

For those users who make use of a custom FPGA program on the EVM, J5 and J6 provide an

expansion-slot capability. Users can design daughtercards or breakout boards to make use of the unused

FPGA I/O pins which are brought out to the headers.

Note: The EVM provides 5 V from J14 to pin 1 of both J5 and J6. This can be used to provide

4.3 Optional USB SPI Interface

In most cases, users can use the ADC parallel interface mode to change the operational modes of the

ADC. For users requiring SPI control of the ADC, TI has developed an optional USB daughter card that

plugs into the expansion slot. With the USB daughter card, users can use a PC interface to communicate

to the ADC three-wire SPI interface, which allows for complete control of the ADC register map. Contact

the factory for this optional accessory.

power to any designed daughtercards.

SLWU028B – January 2006 – Revised November 2006 13

Submit Documentation Feedback

Page 14

www.ti.com

K001

Physical Description

5 Physical Description

5.1 PCB Layout

This chapter describes the physical characteristics and PCB layout of the EVM.

The EVM is constructed on a 6-layer, 0.062-inch thick PCB using FR-4 material. The individual layers are

shown in Figure 4 through Figure 9 . The layout features split analog and digital ground planes; however,

similar performance can be had with careful layout using a single ground plane. Users can connect the

analog and digital ground planes underneath the EVM by soldering the two exposed tinned strips together.

Figure 4. Top Layer

14 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 15

www.ti.com

K002

Physical Description

Figure 5. Layer 2, Ground Plane

SLWU028B – January 2006 – Revised November 2006 15

Submit Documentation Feedback

Page 16

www.ti.com

K003

Physical Description

Figure 6. Layer 3, Power Plane #1

16 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 17

www.ti.com

K004

Physical Description

Figure 7. Layer 4, Power Plane #2

SLWU028B – January 2006 – Revised November 2006 17

Submit Documentation Feedback

Page 18

www.ti.com

K005

Physical Description

Figure 8. Layer 5, Ground Plane

18 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 19

www.ti.com

K006

Physical Description

Figure 9. Layer 6, Bottom Layer

SLWU028B – January 2006 – Revised November 2006 19

Submit Documentation Feedback

Page 20

www.ti.com

Physical Description

5.2 Bill of Materials

20 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 21

www.ti.com

Physical Description

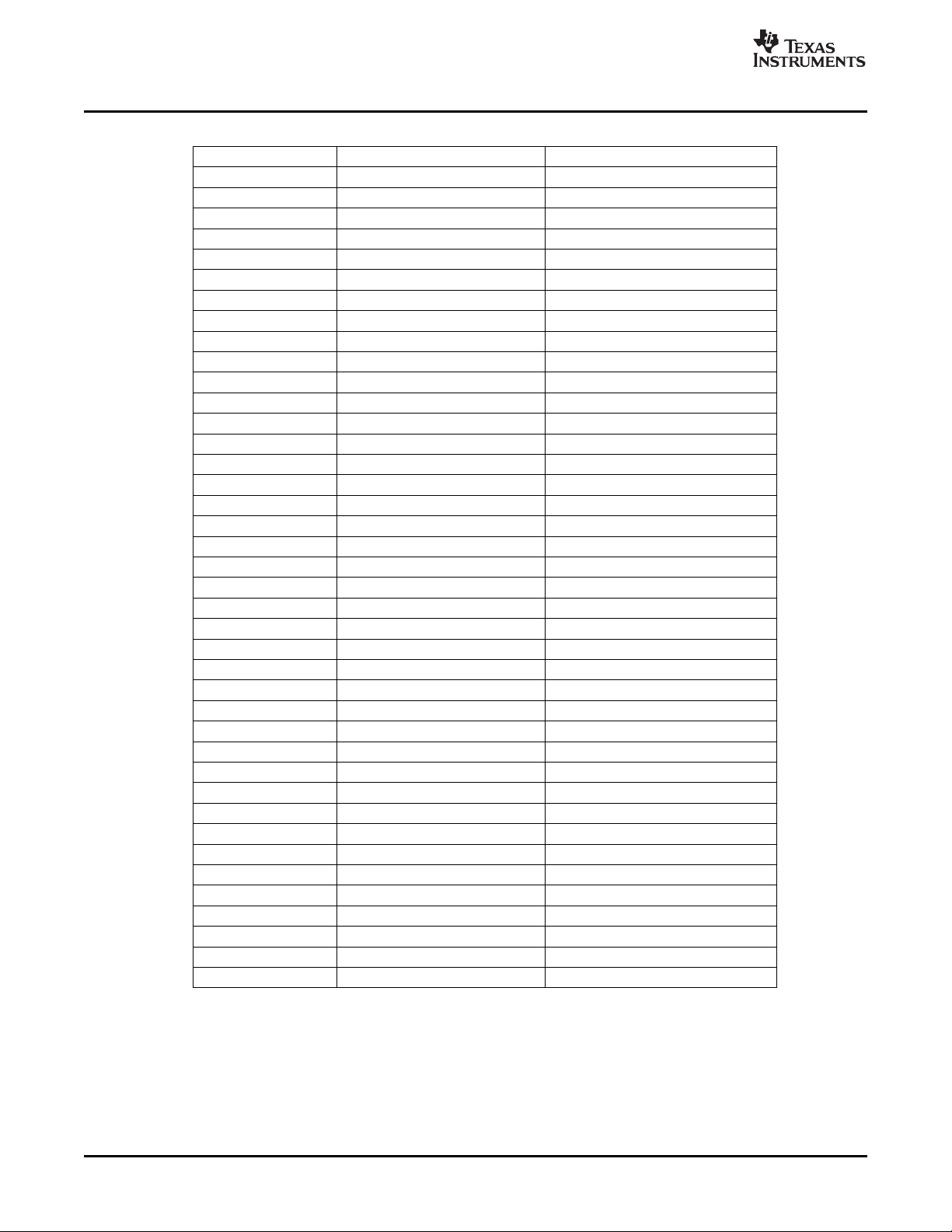

Table 5. Bill of Materials

VALUE FOOTPRINT QTY PART NUMBER VENDOR DIGI-KEY NUMBER REF DESIGNATOR

CAPACITORS

47- µ F, tantalum, 20%, 10-V 7343 4 ECS-T1AD476R Panasonic PCS2476CT-ND C65, C66, C68, C69

10- µ F, 10-V, 20% 3528 5 ECS-T1AX106R Panasonic PCS2106CT-ND C70, C71, C72, C73,

C74

10- µ F, 10-V, 20% 3216 2 ECS-T1AY106R Panasonic P11309CT-ND C8, C9

100- µ F, 6.3-V, 10% 6032 2 TPSC107K006R0150 AVX 478-1764-2-ND C35, C60

0.1- µ F, 16-V, 10% 805 2 ECJ-2VB1C104K Panasonic PCC1812CT-ND C115, C116

2.2- µ F, 6.3-V, 10% 805 1 ECJ-GVB0J225K Panasonic PCC2310CT-ND C117

10- µ F, 6.3-V, 10% 805 4 GRM21BR60J106KE19L Murata 490-1717-1-ND C13, C30, C40, C41

0.01- µ F, 16-V, 10% 603 1 ECJ-1VB1C103K Panasonic PCC1750CT-ND C57

0.1- µ F, 16-V, 10% 603 18 ECJ-1VB1C104K Panasonic PCC1762CT-ND C14, C15, C18, C25, C52

C26, C27, C28, C32,

C33, C34, C36, C37,

C38, C39, C51, C55,

C62, C113

1.5-nF, 50-V, 10% 603 3 C1608X7R1H152K TDX C31, C58, C59

10-pF, 50-V, ± 0.5-pF 603 1 ECJ-1VC1H100D Panasonic PCC100CVCT-ND C53

1- µ F, 6.3-V, 10% 603 1 ECJ-1VB0J105K Panasonic PCC1915CT-ND C64

10- µ F, 6.3-V, 20% 603 1 ECJ-1VB0J106M Panasonic PCC2395CT-ND C63

100- µ F, 4-V, 20% 603 1 NOJC107M004RWJ AVX 478-1824-1-ND C61

2.2- µ F, 6.3-V, 10% 603 13 ECJ-1VB0J225K Panasonic PCC2273CT-ND C85–C96, C114

18-pF, 50-V, 5% 603 1 GRM1885C1H180JA01D Murata 490-1409-1-ND C119 C2, C118

2-pF, 100-V, ± 0.25-pF 603 0 GQM1885C2A2R0CB01D Murata 490-3555-1-ND C20

0.1- µ F, 16-V, +80/–20% 402 14 ECJ-0EF1C104Z Panasonic PCC1731CT-ND C1, C3, C4, C5, C6,

C7, C10, C11, C12,

C16, C17, C19, C29,

C44, C49

0.22- µ F, 6.3-V , ± 10% 402 17 ECJ-0EB0J224K Panasonic PCC2269CT-ND C42, C43, C46, C48,

C50, C54, C67, C75,

C76, C77, C78, C79,

C80, C81, C82, C83,

C84

0.022- µ F, 6.3-V, +80/–20% 201 16 02016G223ZAT2A AVX 478-1054-1-ND C97, C98, C99, C100,

C101, C102, C103,

C104, C105, C106,

C107, C108, C109,

C110, C111, C112

NOT

INSTALLED

SLWU028B – January 2006 – Revised November 2006 21

Submit Documentation Feedback

Page 22

www.ti.com

Physical Description

Table 5. Bill of Materials (continued)

VALUE FOOTPRINT QTY PART NUMBER VENDOR DIGI-KEY NUMBER REF DESIGNATOR

RESISTORS

0- Ω , 1/10-W, 5% 603 7 ERJ-3GEY0R00V Panasonic P0.0GCT-ND R5, R6, R10, R18, R54, R56

R48, R58, R82

0- Ω , 1/10-W, 5% 402 3 ERJ-GE0R00X Panasonic P0.0JCT-ND R11, C45, C47

4.02- Ω , 1/10-W 1% 603 2 9C06031A4R02FGHFT Yageo 311-4.02HCT-ND R37, R38

20- Ω , 1/16-W, 1% 603 1 ERJ-3EKF20R0V Panasonic P20.0HCT-ND R79

24.9- Ω , 1/16-W, 1% 603 1 ERJ-3EKF24R9V Panasonic P24.9HCT-ND R17

4.7- Ω , 1/2-W, 5% 603 2 ERD-S1TJ4R7V Panasonic P4.7BBCT-ND R44, R47

36- Ω , 1/10-W, 1% 603 0 RC0603FR-0736RL Yaego 311-36.0HRCT-ND R12, R13

49.9- Ω , 1/16-W, 1% 603 2 ERJ-3EKF49R9V Panasonic P49.9HCT-ND R35, R36 R34, R59

100- Ω , 1/16-W, 0.1% 603 3 ERA-3YEB100V Panasonic P100YCT-ND R31, R41, R60

200- Ω , 1/16-W, 1% 603 2 ERJ-3EKF2000V Panasonic P200HCT-ND R15, R16 R85, R86

330- Ω , 1/16-W, 5% 603 3 ERA-V33J331V Panasonic P330CHCT-ND R45, R87, R88

499- Ω , 1/16-W, 1% 603 2 ERJ-3EKF4990V Panasonic P499HCT-ND R83, R84

10-k Ω , 1/16-W, 1% 603 11 ERJ-3EKF1002V Panasonic P10.0KHCT-ND R2, R3, R4, R7, R8,

R9, R26, R32, R33,

R39, R40

4.75-k Ω , 1/16-W, 1% 603 2 ERJ-3EKF4751V Panasonic P4.75KHCT-ND R46, R49

15.4-k Ω , 1/16-W, 1% 603 1 ERJ-3EKF1542V Panasonic P15.4KHCT-ND R65

20-k Ω , 1/16-W, 1% 603 3 ERJ-3EKF2002V Panasonic P20.0KHCT-ND R30, R80, R81

36.5-k Ω , 1/16-W, 1% 603 1 ERJ-3EKF3652V Panasonic P36.5KHCT-ND R66

56.2-k Ω , 1/16-W, 1% 603 1 ERJ-3EKF5622V Panasonic P56.2KHCT-ND R1

4.99-k Ω , 1/16-W, 1% 603 3 ERJ-3EKF4991V Panasonic P4.99KHCT-ND R27, R28, R29

61.9-k Ω , 1/16-W, 1% 603 2 ERJ-3EKF6192V Panasonic P61.9KHCT-ND R63, R64

0.033- Ω , 1/4-W, 5% 805 2 RL1220T-R033-J Susumu Co,. Ltd. RL12T.033JCT-ND R61, R62

348- Ω , 1/16-W, 1% 402 2 ERJ-2RKF3480X Panasonic P348LCT-ND R24, R25

49.9- Ω , 1/16-W, 1% 402 3 ERJ-2RKF49R9X Panasonic P49.9LCT-ND R19, R42, R43

78.7- Ω , 1/16-W, 1% 402 2 ERJ-2RKF78R7X Panasonic P78.7LCT-ND R20, R21

100- Ω , 1/16-W, 1% 402 2 ERJ-2RKF1000X Panasonic P100LCT-ND R22, R23

20- Ω R-pack, 5%, 0.063-W CTS-742_8RES 2 742C163220JTR CTS 742C163220JCT-ND RP1, RP2

10-k Ω resistor pack CTS_742_8RES 1 742C163103JTR CTS 742C163103JCT-ND RP3

NOT

INSTALLED

22 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 23

www.ti.com

Physical Description

Table 5. Bill of Materials (continued)

VALUE FOOTPRINT QTY PART NUMBER VENDOR DIGI-KEY NUMBER REF DESIGNATOR

FERRITE BEADS, CONNECTORS, JUMPERS, JACKS, ICs, ETC.

Ferrite bead 1206 5 EXC-ML32A680U Panasonic P10437CT-ND FB2, FB3, FB4, FB6, FB8, FB9,

Inductor, SMT, 15- µ H, 2.6-A COIL-CDRH8D43 1 CDRH8D43-150 Sumida L1

Inductor, SMT, 5- µ H, 2.9-A COIL-CDRH6D38 1 CDRH6D38-5R0 Sumida CDRH6D38-5R0NC-ND L2

0.0- Ω , 1/8-W, 5% resistor 805 2 ERJ-6GEY0R00V Panasonic P0.0ACT-ND L3, L4

Red test point Test_point2 8 5000k Keystone 5000K-ND TP1, TP4, TP9, TP10 TP3 TP11

Black test point Test_point2 4 5001k Keystone 5000K-ND TP5 TP6 TP7 TP8

40-pin header 20 × 2 × .1 1 HTSW-120-07-L-D Samtec J4

40-pin header smt 20X2_SMT_MMS_ 2 MMS-120-02-T-DV Samtec J5, J6

SAMTEC

Red banana jacks BANANA_JACK 5 ST-351A Allied N/A J11, J12, J13, J14,

Black banana jacks BANANA_JACK 4 ST-351B Allied N/A J9, J10, J16, J17

SMA connectors SMA_Jack 3 901-144-8RFX AMP ARFX1231-ND J1, J3, J7 J8

3POS_header 3pos_jumper 1 HTSW-150-07-L-S Samtec JP2

6-pin header 6 × 1 × .1 1 HTSW-120-07-L-D Samtec JP1

3-pin power connector 3term_screw_con 0 93F7124 Newark J20

Transformer TC4-1W_ 3 TC4-1W Mini-Circuits T1, T2, T3

TRANSFORMER

Diode, Schottky, 1-A, 20-V DIODE-MBRM120 1 MBRM120E ON Semiconductor D2

Diode, Schottky, 3-A, 20-V DO-214AB(SMC) 1 SS32 Vishay D1

Green SM_LED_1206 LED-1206 2 CMD15-21VGC/TR8 Panasonic L62205CT-ND D3, D4

MOSFET, P-CH, 20-V, 4.7-A, 3-SOT-23 2 SI2323DS Vishay Q1, Q2

39-M Ω

TRANS BIAS NPN, 50-V SOT416 1 DTC114EET1 ON Semiconductor DTC114EET1OS-ND Q3

Switch EVQ-PJ 1 EVQ-PJX04M Panasonic P8050SCT-ND S1

Switch, 8-Pos, half-pitch SMT SWITCH_8POS_ 1 TDA08H0SK1 ITT CKN1365-ND SW1

SMT

3-circuit jumpers SJP3_RESISTOR 2 ERJ-3GEY0R00V Panasonic P0.0GCT-ND SJP4

3-circuit jumpers SJP3_402 2 ERJ-2GE0R00X Panasonic P0.0JCT-ND SJP1

(1)

Add jumper for JP2 between pins 1 to 2.

(2)

Add jumper for SJP4 between pins 2 and 3 (use a 0- Ω resistor to short pins).

(3)

Add jumper for SJP5 between pins 2 and 3 (use a 0- Ω resistor to short pins).

(4)

Add jumper for SJP1 between pins 1 and 2 (use a 0- Ω resistor to short pins).

(5)

Add jumper for SJP2 between pins 1 and 2 (use a 0- Ω resistor to short pins).

FB7 FB10

J15

(1)

(2)

(4)

(3)

, SJP5

(5)

, SJP2

NOT

INSTALLED

TP12 TP13

SLWU028B – January 2006 – Revised November 2006 23

Submit Documentation Feedback

Page 24

www.ti.com

Physical Description

Table 5. Bill of Materials (continued)

VALUE FOOTPRINT QTY PART NUMBER VENDOR DIGI-KEY NUMBER REF DESIGNATOR

ADS5525/27, ADS5545/46/47 48-QFN_MOD 1 ADS5525/27, TI U1

ADS5545/46/47

Spartan-3E XC3S250E 256-BGA- XC3S250E-4FT256CES Xilinx U2

1mm_XILINX

IC amp, fully-diff, wideband 16-QFN(RGT) 1 THS4509RGTT TI 296-17730-1-ND U3

XCF16PFSG48 48PIN_BGA_XILINX 1 XCF16PFSG48 Xilinx U4

IC, pwr-mgmt, triple-supply 20-pin-QFN 1 TPS75003RHLR TI 296-17835-2-ND U6

IC, LDO reg, hi-PSRR, 1.8-V 5-SOT(DBV) 1 TPS73018DBVT TI 296-17577-1-ND U7

IC, comparator, R-R, hi-spd 8-TSSOP(DCN) 1 TLV3502AIDCNT TI 296-18147-2-ND U9

IC, EX-OR gate, 2-in 5-SOT(DBV) 1 SN74LVC1G86DBVR TI 296-9853-1-ND U10

2-pos shunt Shorting jumper 1 N/A 3M 929955-06-ND

Screw 4-40 × 3/8" 4 N/A Building Fasteners H781-ND

Standoff, hex (1/4 x .5") 4-40 screw 4 N/A Keystone 1902CK-ND

NOT

INSTALLED

24 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 25

www.ti.com

Physical Description

5.3 PCB Schematics

The schematics for the EVM are on the following pages.

SLWU028B – January 2006 – Revised November 2006 25

Submit Documentation Feedback

Page 26

U2A

XILINX XC3S 500E_FT256

A14

IO_L01N_0

B14

IO_L01P_0

A13

IO_L03N_0/VREF_0

B13

IO_L03P_0

2.5V

E11

IO_L04N_0

D11

U1-G2

U1-H4

U1-H3

MODE

B11

C11

E10

D10

A10

C13

C12

D12

C10

A12

B10

U1-G3

F8

E8

F9

E9

A9

B8

A8

D8

C8

D7

E7

D6

C6

E6

D5

A4

A5

C4

C5

B3

C3

A3

C9

A7

B4

B6

D9

SEN

(Sh 4)

(Sh 4)

(Sh 4)

IO_L04P_0

IO_L05N_0/VREF_0

IO_L05P_0

IO_L06N_0

IO_L06P_0

IO_L12N_0

IO_L12P_0

IO_L08N_0/GCLK5

IO_L08P_0/GCLK4

IO_L09N_0/GCLK7

IO_L09P_0/GCLK6

IP_L10N_0/GCLK9

IP_L10P_0/GCLK8

IO_L11N_0/GCLK11

IO_L11P_0/GCLK10

IO_L14N_0/VREF_0

IO_L14P_0

IO_L15N_0

IO_L15P_0

IP_L16N_0

IP_L16P_0

IO_L17N_0/VREF_0

IO_L17P_0

IO_L18N_0

IO_L18P_0

IO_L19N_0/HSWAP

IO_L19P_0

IP

IP

IP_L02N_0

IP_L02P_0

IP_L07N_0

IP_L07P_0

IO

IO

IO

IP

IP

IO_VREF_0

U1-G2

U1-G3

SEN

D

C9

+

10uF

U1-H6

U1-H5

DFS

TLV3502

U1-H6

U1-H5

R3

C115

10K

3.3V

C117

.1uF

2.2uF

5

1

2

3

DFS

3.3V

U9

8

V+

7

OUT A

6

OUT B

5

(Sh 4)

C

B

DRVDD

R32

10K

R33

10K

R39

10K

(Sh 4)

(Sh 4)

DFS

1

2

3

+IN A

-IN A

+IN B

-IN B4V-

DRVDD

C10

.1uF

R5

(Sh 2)

(Sh 2)

C8

+

10uF

D12_D13P

D12_D13M

D10_D11P

D10_D11M

D8_D9P

D8_D9M

D6_D7P

RESET

SCLK

SDATA

AVDD

AGND

SEN

D6_D7M

D4_D5P

D4_D5M

D2_D3P

D2_D3M

36

TP10

35

34

33

32

N/C

31

N/C

30

29

28

27

26

25

IREF

D0_D1P

D0_D1M

R41 100

R48 0

R6 0

R2

10K

R1

56.2K

R18 0

S1

SW-PB

3.3V

R80

20K

RESET

SCLK

SDATA

DRVDD

R28

4.99KR410K

AVDD

C19

.1uF

38

40

42

44

45

47

46

48

1

2

3

4

5

0

INP

INM

6

7

8

9

TP4

10

11

12

TP1

0

C14

.1uF

INP

INM

D12_D13P

DRGND

DRVDD

OVR

CLKOUTM

CLKOUTP

DFS

OE

AVDD

AGND

CLKP

CLKPM

AGND

CM13AGND14INP15INM16AGND17AVDD18AGND19AVDD20IREF21AVDD22MODE23AVDD

D10_D11P

D10_D11M

D12_D13M

ADS5545_48PIN-QF N

43

D8_D9P

D8_D9M

U1

41

D6_D7P

D6_D7M

39

D4_D5P

D4_D5M

37

D2_D3P

D2_D3M

D0_D1P

D0_D1M

24

DRGND

DRVDD

C1

C3

.1uF

.1uF

C4

.1uFC5.1uF

R27

4.99K

(Sh 4)

(Sh 4) (Sh 4)

(Sh 4)

(Sh 4)

C116

.1uF

U10

4

SN74LVC1G86

C6

.1uFC7.1uF

3.3V

R30

20K

OVR

OVR

OE

CLKP

CLKM

(Sh 2)

VCM

(Sh 2)

CM

TP9

M0

OE

CLKP

CLKM

M0

VCM

CM

R10

(Sh 4)

CLKOUTM

CLKOUTP

RESET

SCLK

SDATA

CLKOUTM

CLKOUTP

(Sh 4)

(Sh 4)

3.3V

R81

20K

U1-H4

U1-H3

MODE

R29

4.99KR710K

(Sh 4)

(Sh 4)

(Sh 4)

VCCO_0

VCCO_0

VCCO_0

VCCO_0

GND

GND

GND

GND

GND

GND

GND

NC

NC

VCCO_0

B5

B12

F7

F10

C7

B7

A1

B9

F6

G7

G8

G9

H8

3.3V

2.5V

1

2

JP2

(1-2)

3

D

C

B

R40

A

10K

Note 1. Part not installed

Engineer:

Drawn By:

FILE:

J. VENABLE

Y. DEWONCK

ti

12500 TI Boulevard. Dallas, Texas 75243

Title:

SIZE:

ADS5545

DATE: REV:

11-Jul-2006

B

SHEET: OF:

17

A

Page 27

54321

N

6

D

C

B

A

Note 1. Part not installed

+VCC

C11

C12

C13

.1uF

.1uF

R24

348

J1

SMA_END

5

(Sh 1)

VCM

J3

AIN

1

3 4

2

5

1 2 3 4 56

R34

49.9

(Note 1)

T1

4

6

TC4-1W

C44 .1uF

1

3 4

2

VCM

C16

.1uF

3

R15

2

200

1

C62

.1uF

R22

100

R20

69.8

C49

.1uF

R21

69.8

R19

49.9

C46

.22uF

R16

200

R83

499

R84

499

R23

100

T2

1

2

3

TC4-1W

C51

.1uF

TP3

12

PD

1

N/C

2

Vin-

11

Vin+

4

CM

CM

9

C15

6

.1uF

C113

4

.1uF

Vs+5Vs+6Vs+7Vs+

U3

THS4509

Vs-13Vs-14Vs-15Vs-

C17

C29

.1uF

.1uF

R35

49.9

8

Vout+

16

R25

348

Vout-

C30

10uF

3

10

-VCC

C41

10uF

R17

24.9

R36

49.9

C55

.1uF

10uF

C40

10uF

C45

R42

0 ohm

C47

R43

0 ohm

CM

CM

SJP4

C52

.1uF

(Note 1)

L3

49.9

0 ohm

L4

49.9

0 ohm

AMP_M

2

(2-3)

3 1

SJP5

3 1

R37

4.02

AMP_P

R38

2

(2-3)

4.02

C2

20pF

C118

20pF

INM

R12

36

C20

2pF

R13

36

R44

4.7

C119

20pF

R47

4.7

(Sh 1)

INM

INP

(Sh 1)

INP

Engineer:

Drawn By:

FILE:

AMP_P

R85

200

CM

R86

200

AMP_M

ote : R12, C20, and R13 are to be un-populated

on ADS5525/45/46 EVMs.

R12, C20, and R13 may be populated for

future ADC boards; contact factory for details.

Title:

J. VENABLE

Y. DEWONCK

DOCUMENTCONTROL #

DATE:

AMPLIFIER PATH:

AC Couple (default)

C45 C47 = 0.1uF

R26 R27 = 200 Ohms

R5 = 0 Ohms

VCC= 5 V, VEE = GND

DC Couple

C45 C47 = 0 Ohms

R26 R27 = Unpopulated

R5 = Unpopulated

VCC= 4 V, VEE = -1V

ti

12500 TI Boulevard. Dallas, Texas 75243

ADS5545

17-Jul-2006

SIZE:

SHEET: OF:

REV:

B

27

D

C

B

A

Page 28

54321

6

D

J7

CLK_INP

1

3 4

5

J8

CLK_INM

(Note 1)

C

B

1

3 4

5

2

R59

2

49.9

(Note 1)

R58

0

(Note 1)

R54

1 2

0

T3

6

4

TC4-1W

R56

(Note 1)

1

2

3

0

R60

100

R31

100

C25

.1uF

SJP2

CLKP

2

CLKM

(1-2)

3 1

(Sh 1)

CLKM

C26

.1uF

2

SJP1

(1-2)

3 1

CLKP

(Sh 1)

D

C

B

A

Note 1. Part not installed

REV:

B

37

A

ti

12500 TI Boulevard. Dallas, Texas 75243

Engineer:

J. VENABLE

Drawn By:

Y. DEWONCK

1 2 3 4 56

FILE:

Title:

DOCUMENTCONTROL #

DATE:

11-Jul-2006

ADS5545

SIZE:

SHEET: OF:

Page 29

D

C

B

(Sh 1)

(Sh 5)

(Sh 5)

(Sh 5)

A

Note 1. Part not installed

54321

J4

40PIN_IDC

M0

CCLK

A23

D0

D1

D2

D3

D4

D5

D6

D7

XILINX XC3S 500E_FT256

R15

IO_L01N_1/A15

R16

IO_L01P_1/A16

P15

IO_L02N_1/A13

P16

IO_L02P_1/A14

M16

IO_L04N_1/VREF_1

N16

IO_L04P_1

L15

IO_L06N_1

L14

IO_L06P_1

J16

IO_L09N_1/A9/RHCLK1

K16

IO_L09P_1/A10/RHCLK0

H14

IO_L11N_1/A5/RHCLK5

H15

IO_L11P_1/A6/RHCLK4/IRDY1

G16

IO_L13N_1/A1

G15

IO_L13P_1/A2

F15

IO_L15N_1

F14

IO_L15P_1

D14

IO_L18N_1/LDC0

D15

IO_L18P_1/HDC

C15

IO_L19N_1/LDC2

C16

IO_L19P_1/LDC1

K12

IO_L07N_1/A11

K13

IO_L07P_1/A12

K14

IO_L08N_1/VREF_1

K15

IO_L08P_1

J13

IO_L10N_1/A7/RHCLK3/TRDY1

J14

IO_L10P_1/A8/RHCLK2

H11

IO_L12N_1/A3/RHCLK7

H12

IO_L12P_1/A4/RHCLK6

G14

IO_L14N_1/A0

G13

IO_L14P_1

F12

IO_L16N_1

F13

IO_L16P_1

B16

IP

E14

IP

G12

IP

H16

IP

J11

IP

J12

IP

M13

IP

M14

IO

D16

IO/VREF_1

H13

IP/VREF_1

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8

9

VCCO_1

VCCO_1

VCCO_1

VCCO_1

SW1

SW16

SW15

SW14

SW13

SW12

SW11

SW10

SW9

VCCO_2

VCCO_2

VCCO_2

VCCO_2

GND

GND

GND

GND

GND

GND

J5

1112

1314

1516

1718

1920

2122

2324

2526

2728

2930

3132

3334

3536

3738

3940

40PIN SMT MMS

L7

L10

R5

R12

P7

NC

N7

NC

P10

NC

R10

NC

K8

K9

K10

L11

R8

T16

12

34

56

78

910

SW16

SW15

SW14

SW13

SW12

SW9

OVR

DFS

IO/HDC

SW10

SW11

CTRL_LE

CTRL_DATA

CTRL_CLK

OE

OE

OVR

DFS

3.3V

(Sh 5)

D3

LED_1206

IO/HDC

CTRL_LE

CTRL_DATA

CTRL_CLK

(Sh 1)

(Sh 1)

(Sh 1)

R87

330

3.3V

R79

12

34

56

78

910

1112

1314

1516

1718

1920

2122

2324

2526

2728

2930

3132

3334

3536

3738

3940

(Sh 5)

(Sh 5)

20

BUSY

INIT_B

CLKOUT

INIT_B

M0

CCLK

A23

D0

D1

D2

D3

D4

D5

D6

D7

RP1

20 Ohm

1 16

2 15

3 14

4 13

5

6

7

8

1 16

2 15

3 14

4 13

5

6

7

8

RP2

20 Ohm

ADC_D14

ADC_D15

ADC_D0

ADC_D1

ADC_D2

ADC_D3

ADC_D4

12

ADC_D5

11

ADC_D6

10

ADC_D7

9

ADC_D8

ADC_D9

ADC_D10

ADC_D11

ADC_D12

12

ADC_D13 ADC_D0

11

ADC_D14

10

ADC_D15

9

U2C

XILINX XC3S 500E_FT256

IP

IP

IO/D5

IO/M1

IO/VREF_2

IO/VREF_2

IP_L11N_2/M2/GCLK1

IP_L11P_2/RDWR_B/GCLK0

IO/L03N_2/MOSI/CSI_B

IO/L03P_2/DOUT/BUSY

IO/L01N_2/INIT_B

IO/L01P_2/CSO_B

IP_L02N_2

IP_L02P_2

IO/L04N_2

IO/L04P_2

IO/L05N_2

IO/L05P_2

IO/L06N_2

IO/L06P_2

IP_L08N_2/VREF_2

IP_L08P_2

IO/L12N_2/D1/GCLK3

IO/L12P_2/D2/GCLK2

IO/L16N_2/A22

IO/L16P_2/A23

IO/L18N_2/A20

IO/L18P_2/A21

IO/L19N_2/VS1/A18

IO/L19P_2/VS2/A19

IO/L09N_2/D6/GCLK13

IO/L09P_2/D7/GCLK12

IO/L10N_2/D3/GCLK15

IO/L10P_2/D4/GCLK14

IO/L13N_2/DIN/D0

IO/L13P_2/M0

IO/L15N_2

IO/L15P_2

IP_L17P_2

IP_L17N_2

IO/L20N_2/CCLK

IO/L20P_2/VS0/A17

IP

IP

BUSY

ADC_D7

ADC_D8

ADC_D9

ADC_D10

ADC_D13

ADC_D12

ADC_D11

3.3V

M7

T12

T8

T10

P13

R4

R9

T9

N5

P5

P4

P3

R3

T3

T5

T4

N6

M6

P6

R6

T7

R7

N9

P9

P11

R11

N12

P12

R13

T13

L8

M8

P8

N8

M9

L9

M10

N10

N11

M11

R14

P14

T2

T14

GND

GND

GND

GND

GND

GND

GND

GND

3.3V

E15

G11

K11

M15

N15

NC

N14

NC

L13

NC

L12

NC

E16

NC

E13

NC

A16

F11

G10

H9

H10

J9

J10

J15

RP3

10K Ohm

1 16

2 15

3 14

4 13

5

6

7

8

U2B

SWITCH_8POS_SMT

1 2 3 4 56

J6

40PIN_IDC

5V5V

12

34

56

78

910

1112

1314

1516

1718

1920

2122

2324

2526

2728

2930

3132

3334

3536

3738

3940

(Sh 1)

MODE

(Sh 1)

U1-G2

(Sh 1)

U1-G3

(Sh 1)

U1-H6

(Sh 1)

U1-H5

(Sh 1)

U1-H4

(Sh 1)

U1-H3

(Sh 1)

RESET

(Sh 1)

SCLK

(Sh 1)

SDATA

(Sh 1)

SEN

12

11

10

9

Engineer:

Drawn By:

FILE:

ADC_D6

ADC_D5

ADC_D4

ADC_D3

ADC_D2

ADC_D1

MODE

U1-G2

U1-G3

U1-H6

U1-H5

U1-H4

U1-H3

RESET

CLKOUT

SCLK

SDATA

SEN

J. VENABLE

Y. DEWONCK

XILINX XC3S 500E_FT256

R1

IO_L19N_3

R2

IO_L19P_3

P1

IO_L18N_3

P2

IO_L18P_3

N1

IO_L16N_3

M1

IO_L16P_3

L5

IO_L15N_3

K5

IO_L15P_3

K1

IO_L12N_3

J1

IO_L12P_3

E1

IO_L05N_3

D1

IO_L05P_3

E4

IO_L03N_3

E3

IO_L03P_3

C2

IO_L02N_3/VREF_3

C1

IO_L02P_3

B2

IO_L01N_3

B1

IO_L01P_3

G4

IO_L06N_3

G5

IO_L06P_3

G2

IO_L07N_3

G3

IO_L07P_3

H6

IO_L08N_3/LHCLK1

H5

IO_L08P_3/LHCLK0

H4

IO_L09N_3/LHCLK3/IRDY2

H3

IO_L09P_3/LHCLK2

J3

IO_L10N_3/LHCLK5

J2

IO_L10P_3/LHCLK4/TRDY2

J4

IO_L11N_3/LHCLK7

J5

IO_L11P_3/LHCLK6

K2

IO_L13P_3

K3

IO_L13N_3

D2

IP

F2

IP

H1

IP

J6

IP

K4

IP

M3

IP

N3

IP

F5

IO

G1

IP/VREF_3

N2

IO/VREF_3

12500 TI Boulevard. Dallas, Texas 75243

Title:

DOCUMENTCONTROL #

DATE:

11-Jul-2006

ti

U2D

ADS5545

SIZE:

6

3.3V

E2

VCCO_3

VCCO_3

VCCO_3

VCCO_3

GND

GND

GND

GND

GND

GND

GND

SHEET: OF:

NC

NC

NC

NC

NC

NC

G6

K6

M2

F4

F3

L2

L3

L4

M4

H2

H7

J7

J8

K7

L6

T1

REV:

B

47

D

C

B

A

Page 30

D

C

(Sh 3)

3.3V

1.8V

54321

3.3V

2.5V

R49

INIT_B

CCLK

BUSY

D0

D1

D2

D3

D4

D5

D6

D7

IO/HDC

A23

4.75K

(Sh 4)

INIT_B

(Sh 4)

CCLK

(Sh 4)

BUSY

D0

D1

D2

D3

(Sh 4)

D4

D5

D6

D7

A23

R11

0

(Sh 4)

IO/HDC

(Sh 4)

U4

XCF16PFSG48

B1

E1

G6

B2

C6

D6

G5

H2

A4

C3

C4

D3

D4

E3

E4

F2

F3

F4

G2

A1

A2

B6

F1

F5

F6

H1

VCCINT

VCCINT

VCCINT

VCCO

VCCO

VCCO

VCCO

VCCJ

DNC

DNC

DNC

DNC

DNC

DNC

DNC

DNC

DNC

DNC

DNC

GND

GND

GND

GND

GND

GND

GND

OE/RESET__

EN_EXT_SEL__

CLK

CE__

BUSY

CLKOUT

CF__

CEO__

TMS

TDO

REV_SEL0

REV_SEL1

TCK

A3

B3

B4

C1

C2

H6

D0

H5

D1

E5

D2

D5

D3

C5

D4

B5

D5

A5

D6

A6

D7

D1

D2

E2

E6

G1

TDI

G3

G4

H3

H4

R88

330

D4

LED_1206

Q3

DTC114EET1

JP1

6X1X.1

2.5V

R45

R46

4.75K

330

12345

TMS

TDI

TDO

DONE

PROG_B

3.3V

6

GND

3.3V

TCLK

T15

D3

A15

A2

C14

B15

U2E

XILINX XC3S 500E_FT256

DONE

PROG_B

TCK

TDI

TDO

TMS

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

VCCAUX

1.2V

D4

D13

E5

E12

M5

M12

N4

N13

2.5V

A6

A11

F1

F16

L1

L16

T6

T11

6

D

C

B

A

Note 1. Part not installed

B

REV:

B

57

A

ti

12500 TI Boulevard. Dallas, Texas 75243

Engineer:

J. VENABLE

Drawn By:

Y. DEWONCK

1 2 3 4 56

FILE:

Title:

DOCUMENTCONTROL #

DATE:

11-Jul-2006

ADS5545

SIZE:

SHEET: OF:

Page 31

54321

6

D

C57

C58

D

5V

R8

10K

C61

100uF

J20

C

B

CON_3TERM_SCREW

2.5V

3

1.2V

3.3V

C63

10uF

5V

2

1

15.4K

R63

61.9K

R65

.01uF

TP11

5V

C64

1uF

20

IN3

R82

1

0

R9

10K

R26

10K

OUT3

FB3

TP12

TP13

C31

1.5nF

1.5nF

SS3

SS1

17

19

18

SS116EN1

SS3

AGND

U6

TPS75003

FB32EN33EN24SS25DGND6SW27IN28IS2

C59

1.5nF

FET-SI2323DS

SW1

13

14

15

IN1

SW1

DGND

R62

.033

SW2

3

D

FET-SI2323DS

2

S

Q1

IS1

12

IS1

11

FB1

10

FB2

9

IS2

Q2

S

G

R61

.033

5V

C27

.1uF

FB2

5V

C28

.1uF

2

1

D2

MBRM120

1

G

3

CDRH8D43-150

D1

SS32

2 1

L2

1

CDRH6D38-5R0

5uH

L1

1

15uH

2

C53

10pF

2

R64

61.9K

100uF

1.2V

C60

+

100uF

R66

36.5K

3.3V

C35

+

1.2V

C89

C90

2.2uF

2.2uF

VCCO_0

3.3V

3.3V

3.3V

C91

2.2uF

BANK 0 DECOUPLING

C85

C42

2.2uF

.22uF

BANK 1 DECOUPLING

C86

C43

2.2uF

.22uF

BANK 2 DECOUPLING

C87

C54

2.2uF

.22uF

BANK 3 DECOUPLING

C88

C67

2.2uF

.22uF

C92

2.2uF

C48

.22uF

C50

.22uF

C75

.22uF

C76

.22uF

VCCINT DECOUPLING

C77

C78

.22uF

.22uF

C97

.022uF

C98

.022uF

C101

.022uF

C102

.022uF

C79

.22uF

C99

.022uF

C100

.022uF

C103

.022uF

C104

.022uF

C80

.22uF

C105

.022uF

C106

.022uF

C107

.022uF

D

C

B

C108

.022uF

IN

EN

U7

TPS73018DBV

GND

2

OUT

2.2uF

C81

C96

.22uF

VCCAUX CORE DECOUPLING

C82

C83

.22uF

.22uF

C84

.22uF

Engineer:

Drawn By:

FILE:

C109

.022uF

J. VENABLE

Y. DEWONCK

C110

.022uF

C111

C112

.022uF

.022uF

ti

12500 TI Boulevard. Dallas, Texas 75243

Title:

DATE: REV:

SIZE:

ADS5545

11-Jul-2006

B

67

SHEET: OF:

A

5

C114

2.2uF

4

NR

2.5V

2.2uF

C93

C94

C95

2.2uF

2.2uF

5V 1.8V

1

C18

.1uF

3

A

Note 1. Part not installed

1 2 3 4 56

Page 32

54321

Diff Amp Positive Supply (+5.0V)

J13

D

+3.3VA-PS

J11

RED

J9

BLACK

FB2

C32

.1uF

C65

+

47uF

ADC Analog Supply (+3.3V)

AVDD

C33

C70

+

.1uF

10uF

RED

J10

BLACK

J12

RED

FB3

C34

.1uF

FB4

C37

.1uF

+VCC

C71

C66

+

+

10uF

47uF

Diff Amp Negative Supply (-5.0V)

-VCC

C73

C68

+

+

10uF

47uF

6

D

C

B

A

Note 1. Part not installed

C

TP5 TP6

(Note 1) (Note 1)

FB8 FB9 FB10

C69

+

47uF

ADC DIGITAL SUPPLY(3.3V)

DRVDD

C39

C74

+

.1uF

10uF

TP8

OUTPUT_BUFFER

J15

RED

J16

BLACK

1 2 3 4 56

FB7

C38

.1uF

TP7

FB6

(Note 1)

J14

RED

J17

BLACK

FPGA POWER SUPPLY(5V)

5V

C36

C72

+

.1uF

10uF

Engineer:

J. VENABLE

Drawn By:

Y. DEWONCK

FILE:

ti

12500 TI Boulevard. Dallas, Texas 75243

Title:

DOCUMENTCONTROL #

DATE:

11-Jul-2006

ADS5545

SIZE:

77

SHEET: OF:

B

A

REV:

B

Page 33

www.ti.com

Physical Description

EVALUATION BOARD/KIT IMPORTANT NOTICE

Texas Instruments (TI) provides the enclosed product(s) under the following conditions:

This evaluation board/kit is intended for use for ENGINEERING DEVELOPMENT,

DEMONSTRATION, OR EVALUATION PURPOSES ONLY and is not considered by TI to be a

finished end-product fit for general consumer use. Persons handling the product(s) must have

electronics training and observe good engineering practice standards. As such, the goods being

provided are not intended to be complete in terms of required design-, marketing-, and/or

manufacturing-related protective considerations, including product safety and environmental

measures typically found in end products that incorporate such semiconductor components or

circuit boards. This evaluation board/kit does not fall within the scope of the European Union

directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling

(WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these

directives or other related directives.

Should this evaluation board/kit not meet the specifications indicated in the User’s Guide, the

board/kit may be returned within 30 days from the date of delivery for a full refund. THE

FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER

AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY,

INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR

PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further,

the user indemnifies TI from all claims arising from the handling or use of the goods. Due to the

open construction of the product, it is the user’s responsibility to take any and all appropriate

precautions with regard to electrostatic discharge.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY

SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR

CONSEQUENTIAL DAMAGES.

TI currently deals with a variety of customers for products, and therefore our arrangement with the

user is not exclusive.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein.

Please read the User’s Guide and, specifically, the Warnings and Restrictions notice in the User’s

Guide prior to handling the product. This notice contains important safety information about

temperatures and voltages. For additional information on TI’s environmental and/or safety

programs, please contact the TI application engineer or visit www.ti.com/esh .

No license is granted under any patent right or other intellectual property right of TI covering or

relating to any machine, process, or combination in which such TI products or services might be

or are used.

SLWU028B – January 2006 – Revised November 2006 33

Submit Documentation Feedback

Page 34

www.ti.com

Physical Description

FCC Warning

This evaluation board/kit is intended for use for ENGINEERING DEVELOPMENT,

DEMONSTRATION, OR EVALUATION PURPOSES ONLY and is not considered by TI to be a

finished end-product fit for general consumer use. It generates, uses, and can radiate radio

frequency energy and has not been tested for compliance with the limits of computing devices

pursuant to part 15 of FCC rules, which are designed to provide reasonable protection against

radio frequency interference. Operation of this equipment in other environments may cause

interference with radio communications, in which case the user at his own expense will be

required to take whatever measures may be required to correct this interference.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated

EVM WARNINGS AND RESTRICTIONS

It is important to operate this EVM within the AVDD voltage range of –0.3 V to 3.8 V and the

DVDD voltage range of –0.3 V to 3.8 V.

Exceeding the specified input range may cause unexpected operation and/or irreversible damage

to the EVM. If there are questions concerning the input range, please contact a TI field

representative prior to connecting the input power.

Applying loads outside of the specified output range may result in unintended operation and/or

possible permanent damage to the EVM. Please consult the EVM User's Guide prior to

connecting any load to the EVM output. If there is uncertainty as to the load specification, please

contact a TI field representative.

During normal operation, some circuit components may have case temperatures greater than

25 ° C. The EVM is designed to operate properly with certain components above 50 ° C as long as

the input and output ranges are maintained. These components include but are not limited to

linear regulators, switching transistors, pass transistors, and current sense resistors. These types

of devices can be identified using the EVM schematic located in the EVM User's Guide. When

placing measurement probes near these devices during operation, please be aware that these

devices may be very warm to the touch.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated

34 SLWU028B – January 2006 – Revised November 2006

Submit Documentation Feedback

Page 35

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to

discontinue any product or service without notice. Customers should obtain the latest relevant information

before placing orders and should verify that such information is current and complete. All products are sold

subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent

TI deems necessary to support this warranty. Except where mandated by government requirements, testing

of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible

for their products and applications using TI components. To minimize the risks associated with customer

products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent

right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine,

or process in which TI products or services are used. Information published by TI regarding third-party

products or services does not constitute a license from TI to use such products or services or a warranty or

endorsement thereof. Use of such information may require a license from a third party under the patents or

other intellectual property of the third party, or a license from TI under the patents or other intellectual

property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices.

Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not

responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for

that product or service voids all express and any implied warranties for the associated TI product or service

and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application

solutions:

Products

Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Interface interface.ti.com Digital Control www.ti.com/digitalcontrol

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

Low Power Wireless www.ti.com/lpw Telephony www.ti.com/telephony

Video & Imaging www.ti.com/video

Wireless www.ti.com/wireless

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2007, Texas Instruments Incorporated

Loading...

Loading...