73S8023C

Smart Card Interface

Simplifying System Integration™

DESCRIPTION

The Teridian 73S8023C is a low-power, high efficiency,

single smart card interface IC suitable for 3V and 5V

cards. It provides full electrical compliance with ISO7816-3 and EMV 4.0 (EMV2000) specifications.

Hardware support for any type of synchronous cards

(memory cards) is provided.

Interfacing with the system controller is done through the

control bus; composed of digital input s to control the

interface, and one interrupt output to inform the system

controller of the card presence and faul ts. Data exchange

with the card is managed from the system controller using

the I/O line (and eventually the auxi l iary I/O lines).

A chip select input allows multiple 73S8023C ICs to share

the same control bus. When chip select is set low, the

host microcontroller inputs are latch ed and outputs are

taken to a high impedance state.

The card clock signal can be generated by an on-chip

oscillator using an external crystal or by connecting an

external clock signal.

The 73S8023C device incorporat es an ISO-7816-3

activation/deactivation sequencer that controls the card

signals. Emergency card deactivatio n i s i nitiated upon

card extraction or upon any fault generated by the

protection circuitry.

The 73S8023C requires only a single 2.7 V to 3.6 V power

supply, and features a high-efficiency embedded DC-DC

converter. This architecture, plus a Power Down digital

input that allow placing the IC in a very low-power mode

making the 73S8023C particularly sui table for low-power

applications (cell-phones, PDAs, payphones, hand-held

POS terminals…).

ADVANTAGES

• Supports both synchronous and asynchronous smart

cards

• Replacement for TDA8002, with up to 60 0 mW in

power savings (@ EMV ICCmax condition) !

• The inductor-based DC-DC converter provides higher

current and efficiency

Ideal for battery-powered applications

Suitable for high current cards and SAM s: (100 mA

max)

Single 2.7 V to 3.6 V power supply allows removal

of 5 V from the system

• Power down mode: 2 µA typical

• Package: Small Format (5x5mm) 32-QFN

DATA SHEET

April 2009

FEATURES

• Card Interface:

Complies with ISO-7816-3, EMV 4.0

A DC-DC Converter provides 3V / 5V to the card

from an external power supply input

High-efficiency converter: > 80% @ V

=5 V and I

V

CC

= 65 mA

CC

Up to 100 mA supplied to the card

ISO-7816-3 Activation / Deactivation sequencer

with emergency automated deactivation

Protection includes 2 voltage supervisors which

detect voltage drops on card V

CC

power supply

The V

voltage supervisor threshold value can be

DD

externally adjusted

True over-current detection (150 mA max.)

2 card detection inputs, 1 for either possible switch

configuration

Full support of synchronous cards

• System Controller Interface:

3 Digital inputs control the card ac tivation /

deactivation, card reset and card voltage

3 Digital inputs control the card clock (division rate

and card clock source selection)

1 Digital output, interrupt to the system controller,

allows the system controller to monitor the card

presence and faults

1 Power down digital input (places the 73S8023C

in a very low-power mode (card deactivated)

1 Chip select digital input for parall el operation of

several 73S8023C ICs.

1 External clock input (STROBE), used for

synchronous operation

1 Digital output clock, buffered version of signal on

XTALIN

Crystal oscillator or host clock (XTALIN), up to

27 MHz

• Power Supply: V

2.7 V to 3.6 V

DD

• 6 kV ESD Protection on the card interface

APPLICATIONS

• Point of Sales and Transaction Terminals

• Payphones

• Set-Top-Boxes, DVD / HDD Recorders

• Payment card interfaces in portable devices (PDAs,

mobile phones…)

=3.3 V,

DD

and on V

DD

Rev. 1.5 © 2009 Teridian Semiconductor Corporation 1

73S8023C Data Sheet DS_8023C_019

ICC I/O BUFFERS

VDD VOLTAGE SUPERVISOR

VOLTAGE REFERENCE

XTAL

OSC

CLOCK

GENERATION

DIGITAL

CIRCUITRY

&

FAULT LOGIC

V

DD

FAULT

V

CC

FAULT

Int_Clk

VDD VDD

VCC

RST

CLK

PRES

PRES

XTALIN

XTALOUT

CLKDIV1

CLKDIV2

GND

TEMP FAULT

NC

29

30

31

2

6

4

6

7

9

10

11

12

13

15

14

20

19

18

17

26

24

23

22

28

27

ISO-7816-3

SEQUENCER

R-C

OSC.

DC-DC

CONVERTER

ICC RESET

BUFFER

ICC CLOCK

BUFFER

OVER

TEMP

PWRDN

I/O

AUX1

AUX2

IOUC

AUX1UC

AUX2UC

VDDF_ADJ

RSTIN

CMDVCC

5V/3V

OFF

5

GND

1

3

LIN

6

21

GND

ICC FAULT

CLKOUT

32

8

CS

CLKSEL

16

STROBE

25

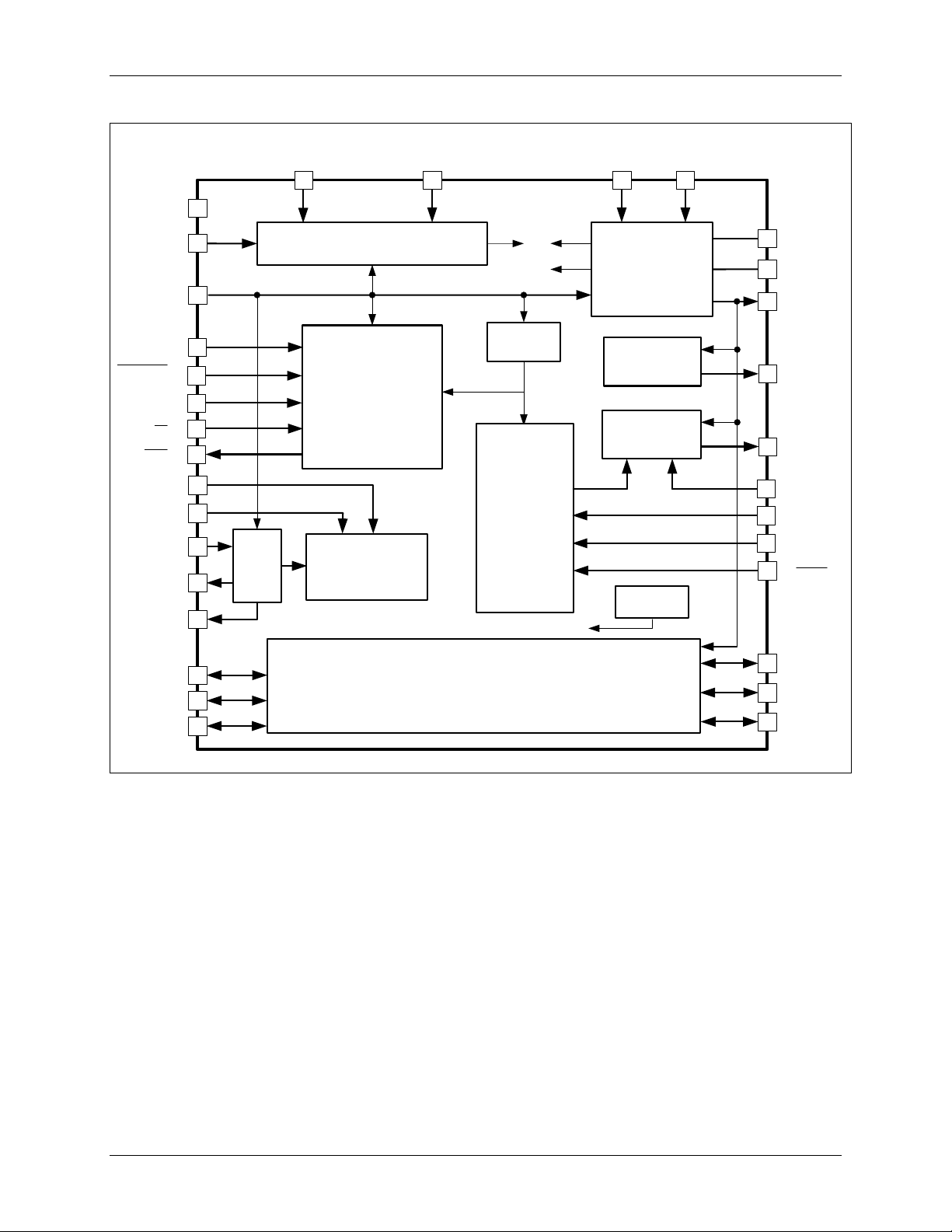

FUNCTIONAL DIAGRAM

Figure 1: 73S8023C Block Diagram

2 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

Table of Contents

1 Pin Description .................................................................................................................................... 5

1.1

Card I nterface ............................................................................................................................... 5

Miscellaneous Inputs and Outputs ................................................................................................ 5

1.2

Power S upply and Ground ............................................................................................................ 5

1.3

Microc ontroller Interface ............................................................................................................... 6

1.4

System Controller Interface ............................................................................................................... 7

2

Oscillator .............................................................................................................................................. 8

3

DC-DC Converter – Card Power Supply .......................................................................................... 8

4

Voltage Supervision ........................................................................................................................... 9

5

Power Down ....................................................................................................................................... 10

6

Over-Temperature Monitor ............................................................................................................... 10

7

Activation and Deactivation ............................................................................................................. 11

8

8.1

Activation Sequence (Synchronous Mode) ................................................................................ 11

Deactiv ati on Sequen ce (Synchr ono us Mode) ............................................................................ 11

8.2

Activation Sequence (Asynchronous Mode) ............................................................................... 12

8.3

Deactiv ati on Sequen ce (Async hronou s Mode ) .......................................................................... 14

8.4

OFF and Fault Detection .................................................................................................................. 14

9

I/O Circuitry and Timing ................................................................................................................... 15

10

Typical Application Schematic ........................................................................................................ 17

11

Electrical Specification ..................................................................................................................... 18

12

12.1

Absolute Maximum Ratings ........................................................................................................ 18

Recommended Operating Conditions ......................................................................................... 18

12.2

Package Thermal Parameters .................................................................................................... 18

12.3

Card Interface Characteristics .................................................................................................... 19

12.4

Digital Signals ............................................................................................................................. 22

12.5

DC Characteristics ...................................................................................................................... 23

12.6

Voltage / Temperature Fault Detection Circuits .......................................................................... 23

12.7

Mechanical Drawing (32-QFN) ......................................................................................................... 24

13

Package Pin Designation (32-QFN) ................................................................................................. 25

14

Ordering Information ........................................................................................................................ 26

15

Related Documentation .................................................................................................................... 26

16

Contact Information .......................................................................................................................... 26

17

Revision History

........................................................................................................................................ 27

Rev. 1.5 3

73S8023C Data Sheet DS_8023C_019

Figures

Figure 1: 73S8023C Block Diagram ............................................................................................................. 2

Figure 2: Power Down Mode Operation: CS = high

Figure 3: Activation Sequence – Synchronous Mod e

Figure 4: Synchronous Deactivation Operation – CKSEL = High

Figure 5: Asynchronous Activation Sequence – RS T IN Low When CMDVCC Goes Low

Figure 6: Asynchronous Activation Sequence – Timing Diagram #2

Figure 7: Asynchronous Deactivation Sequence

Figure 8: Timing Diagram – Management of the Interrupt Line OFF

Figure 9: I/O and I/OUC State Diagram

Figure 10: I/O – I/OUC Delays Timing Diagram

Figure 11: 73S8023C – Typical Application Schematic

Figure 12: DC – DC Converter efficiency (V

Figure 13: DC – DC Converter Efficienc y (V

Figure 14: 32-QFN Mechanical Drawing

Figure 15: 32-QFN 73S8023C Pin Out

= 5 V) ................................................................................ 20

CC

= 3 V) ................................................................................ 20

CC

Table

Table 1: Choice of VCC Pin Capacitor .......................................................................................................... 8

.................................................................................... 10

................................................................................. 11

............................................................... 12

......................... 13

......................................................... 13

........................................................................................ 14

.......................................................... 15

...................................................................................................... 16

.......................................................................................... 16

.............................................................................. 17

..................................................................................................... 24

....................................................................................................... 25

4 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

CC.

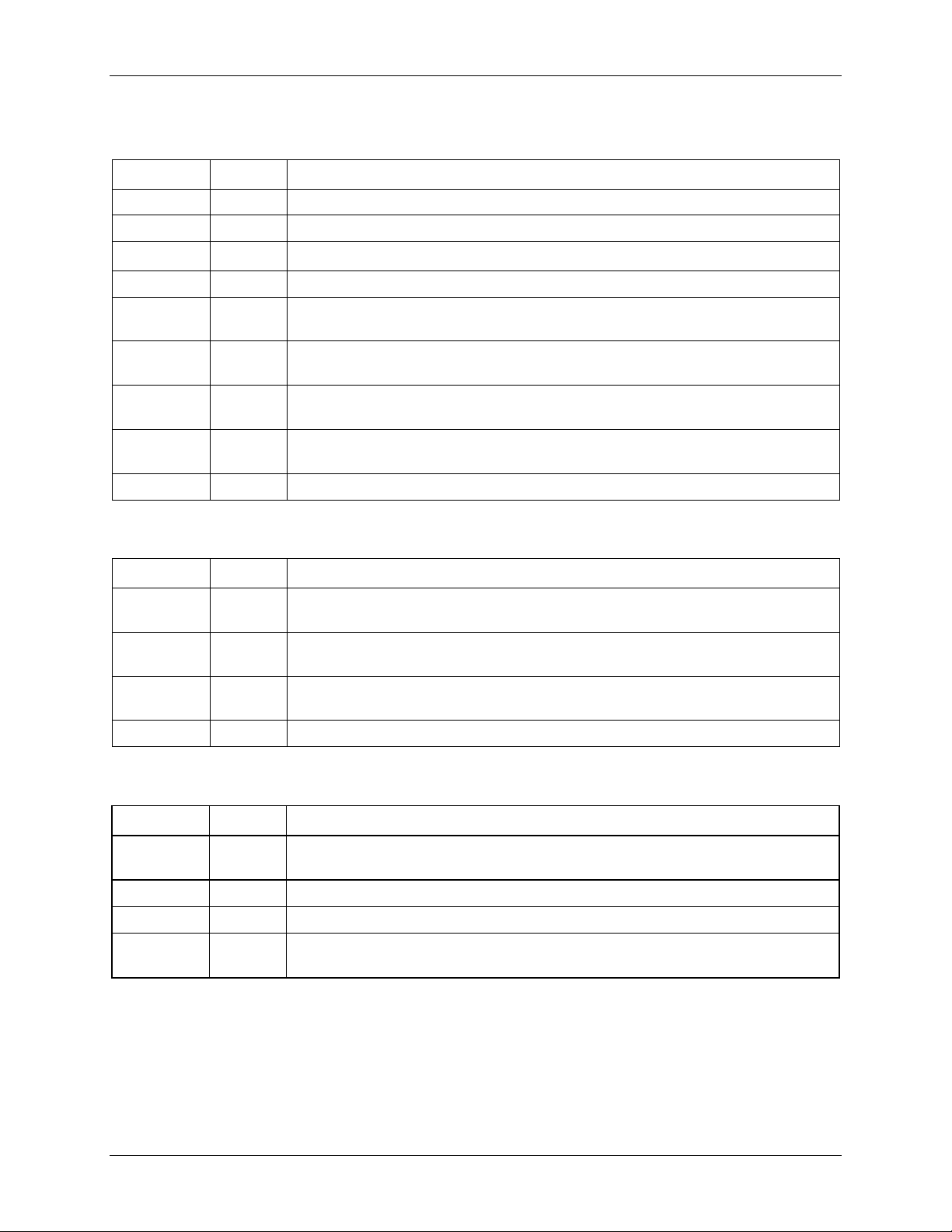

1 Pin Description

1.1 Card Interface

Name Pin Description

I/O 9 Card I/O: Data signal to/from card. Includes a pull-up resistor to V

AUX1 11 AUX1: Auxiliary data signal to/from card. Includes a pull-up resistor to V

AUX2 10 AUX2: Auxiliary data signal to/from card. Includes a pull-up resistor to V

RST 14 Card reset: Provides reset (RST) signal to card.

CLK 13

Card clock: Provides clock (CLK) signal to card. The r ate of this clock is

determined by crystal oscillator frequency and CLKDIV selections.

PRES 7

Card Presence switch: Active high indicates card is present. Includes a

pull-down current source.

PRES

6

Card Presence switch: Active low indicates card is present. Includes a pull-up

current source.

VCC 15

Card power supply: Logically controlled by sequ encer, output of DC-DC

converter. Requires an external filter capacitor to the card GND.

GND 12 Card ground.

1.2 Miscellaneous Inputs and Outputs

Name Pin Description

XTALIN 23

XTALOUT 24

VDDF_ADJ 17

NC 4 Non-connected pin. Must be left open.

Crystal oscillator input: can either be conne ct ed to crystal or driven as a

source for the card clock.

Crystal oscillator output: connected to cry st al. Left open if XTALIN is being

used as external clock input.

fault threshold adjustment input: this pin can be used to adjust V

V

DD

value (that controls deactivation of the card ). M ust be left open if unused.

DDF

CC.

CC.

1.3 Power Supply and Ground

Name Pin Description

VDD 3, 20

GND 1 DC-DC converter ground.

GND 21 Digital ground.

LIN 2

Rev. 1.5 5

System controller interface supply voltage: Supply voltage for internal power

supply and DC-DC converter power supply source.

External inductor. Connect external inductor from pin 2 to V

. Keep the

DD

inductor close to pin 2.

73S8023C Data Sheet DS_8023C_019

0 0 XTALIN/8

0 1 XTALIN/4

1 1 XTALIN/2

1 0 XTALIN

DD.

DD.

1.4 Microcontroller Interface

Name Pin Description

CMDVCC 18

Command V

converter to ramp the V

(negative assertion): Logic low on this pin causes the DC-DC

CC

supply to the card and initiates a card activati on

CC

sequence.

5V/#V

31

5 volt / 3 volt card selection: Logic one selects 5 volts for V

and card

CC

interface, logic low selects 3 volt operation. When the part is to be used with

a single card voltage, this pin should be tied to either GND or V

. However,

DD

it includes a high impedance pull-up resistor to default this pin high (selection

of 5V card) when unconnected

PWRDN 5

Power Down control input: Active High. When Power Down (PD) mode is

activated, all internal analog functions are disabl ed to place the 73S8023C in

its lowest power consumption mode. The PD mode is allowed only out of a

card session (PWRDN high is ignored when CMDVCC = 0). Must be tied to

ground when power down function is not used.

CLKDIV1

CLKDIV2

29

30

Sets the divide ratio from the XTALIN oscillator (or external clock input) to the

card clock. These pins include pull-down resisto rs.

CLKDIV1 CLKDIV2 Clock Rate

OFF 22

Interrupt signal to the processor: Active Low. Multi-function indicating fault

conditions and card presence. Open drain output configuration; it includes an

internal 20 kΩ pull-up to V

RSTIN 19 Reset Input: This signal controls the RST signal to the card.

I/OUC 26

AUX1UC 27

AUX2UC 28

CS 8

System controller data I/O to/from the card. Includes internal pull-up resistor

to V

DD.

System controller auxiliary data I/O to/ from the card. Includes internal pull-up

resistor to V

DD.

System controller auxiliary data I/O to/from the card. Includes internal pull-up

resistor to V

When CS = 1, the control and signal pins are configured normally. When CS

is set low, signals CMDVCC, RSTIN, PWRDN, 5V/#V, CLKDIV1, CLKDIV2,

CLKSEL are latched. I/OUC, AUX1UC, and AUX2UC are set to high

impedance pull-up mode and won’t pass data to or from the smart card. OFF

output is tri-stated.

CLKSEL 16

Selects CLK and RST operational mode. When CLKSEL is low (default), the

circuit is configured for asynchronous card ope ration and the sequencer

manages the control of CLK and RST. When CLKSEL is high, the signal

CLK is a buffered copy of STROBE and the signal R S T i s directly controlled

by RSTIN.

STROBE 25 When CLKSEL = 1, the signal CLK is controlled directly by STROBE.

CLKOUT 32 CLKOUT is the buffered version of the signal on pi n XTALIN.

6 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

2 System Controller Interface

• The CS (chip select) input allows multiple devices to operate in parallel. When CS is high, the system

interface signals operate as described. When CS is taken low, the system interface signals are

latched internally. The pins I/OUC, AUX1UC, an d AUX2UC are weakly pulled up and the OFF signal

is put into a high impedance state.

• The CLKSEL signal selects between synchronous and asynchronous operation. When CLKSE L i s

low, asynchronous operation is selected. When CLKSEL is high, synchronous operation i s selected.

• Digital inputs allow direct control of the card interface from the host as follows:

Pin CMDVCC: When set low, starts an activation sequence if a card is present.

Pin 5V/#V: Defines the card voltage.

• The card I/O and Reset signals have their corresponding controller I/Os to be connected directly to

the host:

Pin RSTIN: controls the card RST signal. When enabled by the sequencer, RST is equal to

RSTIN for both synchronous and asynchronous m odes.

Pin I/OUC: data transfer to card I/O contact.

Pins AUX1UC and AUX2UC (auxiliary I/O l i nes as sociated to the auxiliary I/Os which are

connected to the C4 and C8 card connector contact s).

• Two digital inputs control the card clock frequency division rate: CLKDIV1 and CLKDIV2 define the

card clock frequency from the input clock f requency (crystal or external clock). The division rate is

defined as follows:

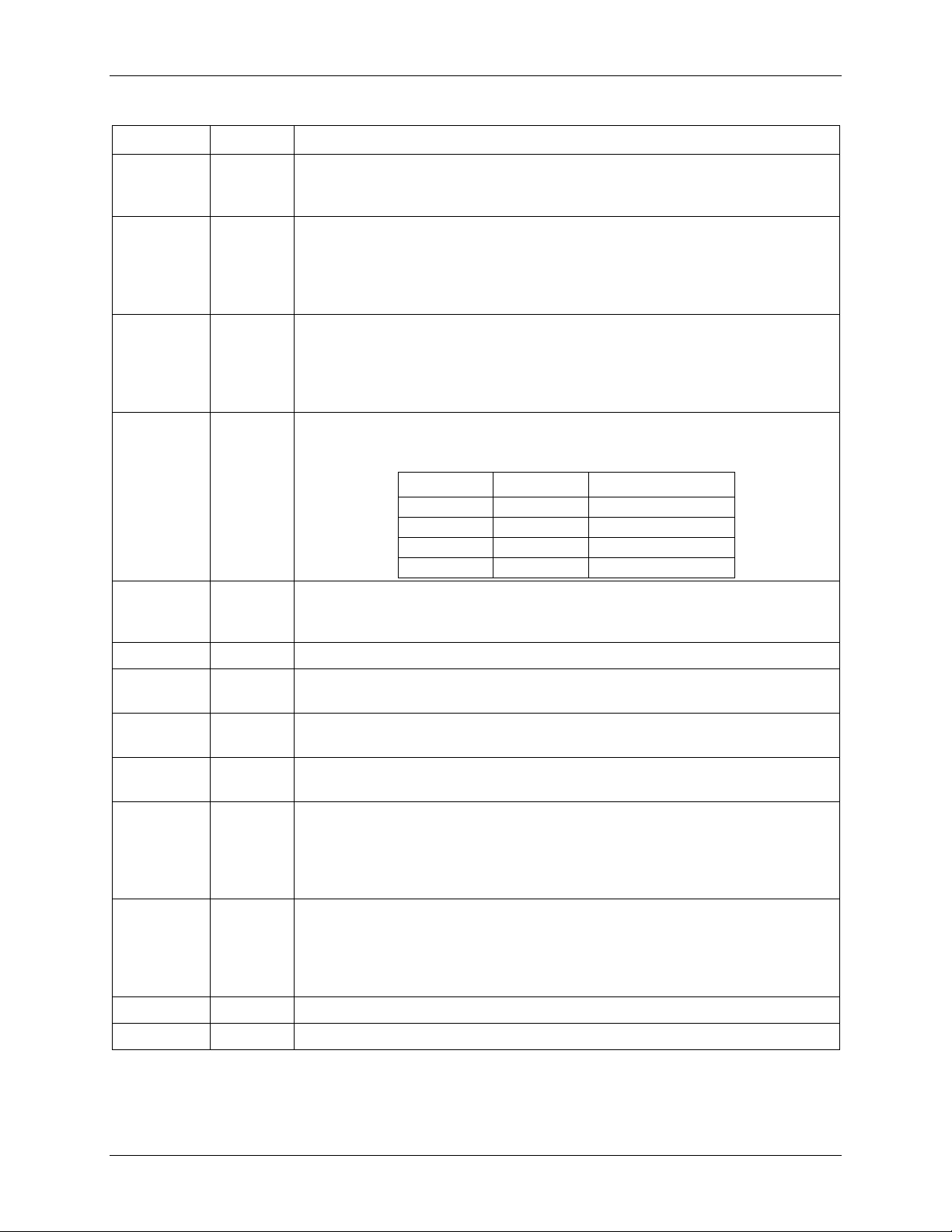

CLKDIV2 CLKDIV1 CLK

0 0

0 1 XTAL

1 0 ¼ XTAL

1 1 ½ XTAL

When the division rate is equal to 1 (CLKDIV2 =0 and CLKDIV 1 = 1), the duty-cycle of the

card clock depends on the duty-cycle and wavefor m of the signal applied on the pin XTALIN.

When other division rates are used, the 73S8023C circuitry guarantees a duty-cycle in the

range 45% to 55%, conforming to ISO-7816-3 and E M V 4.1 specifications.

• Interrupt output to the host: As long as the card is not activated, the OFF pin informs the host about

the card presence only (low = no card in the reader). When CMDVCC is set low (Card activation

sequence requested from the host), a low level on OFF means a fault has been detected (e.g. card

removedl during a card session, or voltage fault, or thermal / over-current fault) that automatically

initiates a deactivation sequence.

• Power Down: The PWRDN pin is a digital input that allows the host controller to put the 73S8023C in

its Power Down state. This pin can only be activated outside of a card session.

• The CLKOUT signal is a buffered output of the signal applied to the XTALIN pin whether it is an

external clock source or it is configured as a cry st al oscillator. CLKOUT can be used when using

multiple 73S8023C devices to share a single clock signal.

• The STROBE input directly drives the smart card CLK signal when operating in synchronous mode.

STROBE is ignored in asynchronous mode.

⅛ XTAL

Rev. 1.5 7

73S8023C Data Sheet DS_8023C_019

Specification

3 Oscillator

The 73S8023C device has an on-chip oscillator that can generate the smart card clock using an ext ernal

crystal (connected between the pins XTALIN and X TALOUT) to set the oscillator frequency. When the

card clock signal is available from another source, i t can be connected to the pin XTALIN, and t he pi n

XTALOUT should be left unconnected. Signal CLKOUT is the buffered version of the signal on XTALIN.

4 DC-DC Converter – Card Power Supply

An internal DC-DC converter provides the card powe r supply. This converter is able to provide either 3 V

or 5 V card voltage from the power supply applied on the V

controls the converter. Card voltage selection is carried out by the digital input 5V/#V.

The circuit is an inductive step-up converter/regulator. The external components required are 2 filter

capacitors on the power-supply input V

output filter capacitor on the card power supply V

step-up operation when V

and the input supply V

= 3.6 V, VCC =3 V) the circuit operates as a linear regulator.

(V

DD

is below a set point of 5.0 or 3.0 volts minus a comparator hysteresis voltage

CC

is less than the set point for VCC. When VDD is greater than the set point for VCC

DD

(next to the LIN pin, 100 nF + 10 µF), an inductor, and an

DD

. The circuit performs regulation by activat ing the

CC

Depending on the inductor values, the voltage converter can provide current on V

The circuit provides over-current protect i on and l im i ts I

sensed, the circuit initiates a deactivation sequence from the control logic and reports back t o the host

controller a fault on the interrupt output OFF.

Choice of the inductor

The nominal inductor value is 10 µH, rated for 400 mA. The inductor is connected between LIN (pin 2)

and the V

(I

CC_MAX

supply voltage. The inductor value can be opt i m ized to meet a particular configuration

DD

). The inductor should be located on the PCB as close a s possible to the LIN pin of the IC.

Choice of the V

capacitor

CC

Depending on the applications, the requirements in terms of both the V

transient currents that the interface must provide t o the card are different. shows the

recommended capacitors for each V

power supply configuration and applicabl e specification.

CC

Table 1: Choice of VCC Pin Capacitor

pin. The digital ISO-7816-3 sequencer

DD

as high as 100 mA.

CC

to 150 mA. When an over-current condition is

CC

minimum voltage and the

CC

Table 1

Specification Requirement Application

Min V

Allowed During

Transient Current

EMV 4.1 4.6 V 30 nAs

ISO-7816-3 4.5 V 20 nAs

NDS 4.65 V 40 nAs

Voltage

CC

Max Transient

Current Charge

Capacitor

Type

X5R/X7R w/

ESR < 100 mΩ

Capacitor

Value

3.3 µF

1 µF

3.3 µF

8 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

5 Voltage Supervision

Two voltage supervisors constantly check the presence of the voltages VDD and VCC. A card deactivation

sequence is triggered upon a fault detected by these voltage supervisors.

The digital circuitry is powered by the power supply applied on the VDD pin. V

range for the interface with the system controll er. The V

Voltage supervisor is also used to initialize the

DD

ISO-7816-3 sequencer at power-on, and also to deactivate the card at power-off or upon a fault. The

voltage threshold of the V

voltage supervisor is internally set by default to 2.3 V nominal. However, it

DD

may be desirable, in some applications, to m odi fy this threshold value. The pin VDDF_ADJ (pin 17) is

used to connect an external resistor R

to ground to raise the VDD fault voltage to another value, V

EXT

The resistor value is defined as follows:

= 180 kΩ /(V

R

EXT

- 2.33)

DDF

An alternative (more accurate) method of adjusting the V

R3 from the pin to supply and R1 from the pin to ground (see

Schematic

). In order to set the new threshold voltage, the equivalent resistance must be determined.

fault voltage is to use a resistive network of

DD

Figure 11: 73S8023C – Typical Application

This resistance value will be designated Kx. Kx is defined as R1/(R1+R3). Kx is calculated as:

Kx = (2.649 / V

) - 0.6042 where VTH is the desired new threshold voltage.

TH

To determine the values of R1 and R3, use the follo wing formulas:

R3 = 72000 / Kx R1 = R3*(Kx / (1 – Kx))

Taking the example above, where a V

fault threshold voltage of 2.7 V is desired, solv i ng for Kx gives:

DD

Kx = (2.649 / 2.7) - 0. 6042 = 0.377

Solving for R3 gives: R3 = 72000 / 0.377 = 191 kΩ.

Solving for R1 gives: R1 = 191000 *(0.377 / (1 – 0.377)) = 115.6 kΩ.

Using standard 1 % resistor values gives R3 = 191 kΩ and R1 = 1 15 kΩ. These values give an

equivalent resistance of Kx = 0.376, a 0.3% error.

Using 1% external resistors and a parallel resistance of 72 k ohms will result in a +/- 6% tolerance in the

value of VDD Fault. The sources of variation due to integrated circuit process variations and mismatches

include the internal reference voltage (less than +/- 1%), the internal comparator hysteresis and offset

(less than +/- 1.7% for part-to-part, processing and env i ronm ent), the internal resistor value mismatch and

value variations (less than 1.8%), and the external resistor values (1%).

If the 2.3 V default threshold is acceptable, this pin must be left un connected.

also defines the voltage

DD

DDF

.

Rev. 1.5 9

73S8023C Data Sheet DS_8023C_019

PRES

OFF

PWRDN

Internal RC OSC

CMDVCC

OFF follows PRES regardless of PWRDN

PWRDN during a card

session has no effect

After setting PWRDN = 0,

the controller must wait at

least 10ms before setting

CMDVCC=0

EMV / ISO deactivation

time ~= 100 uS

~10ms

PWRDN has effect when

the cardi s deactivated

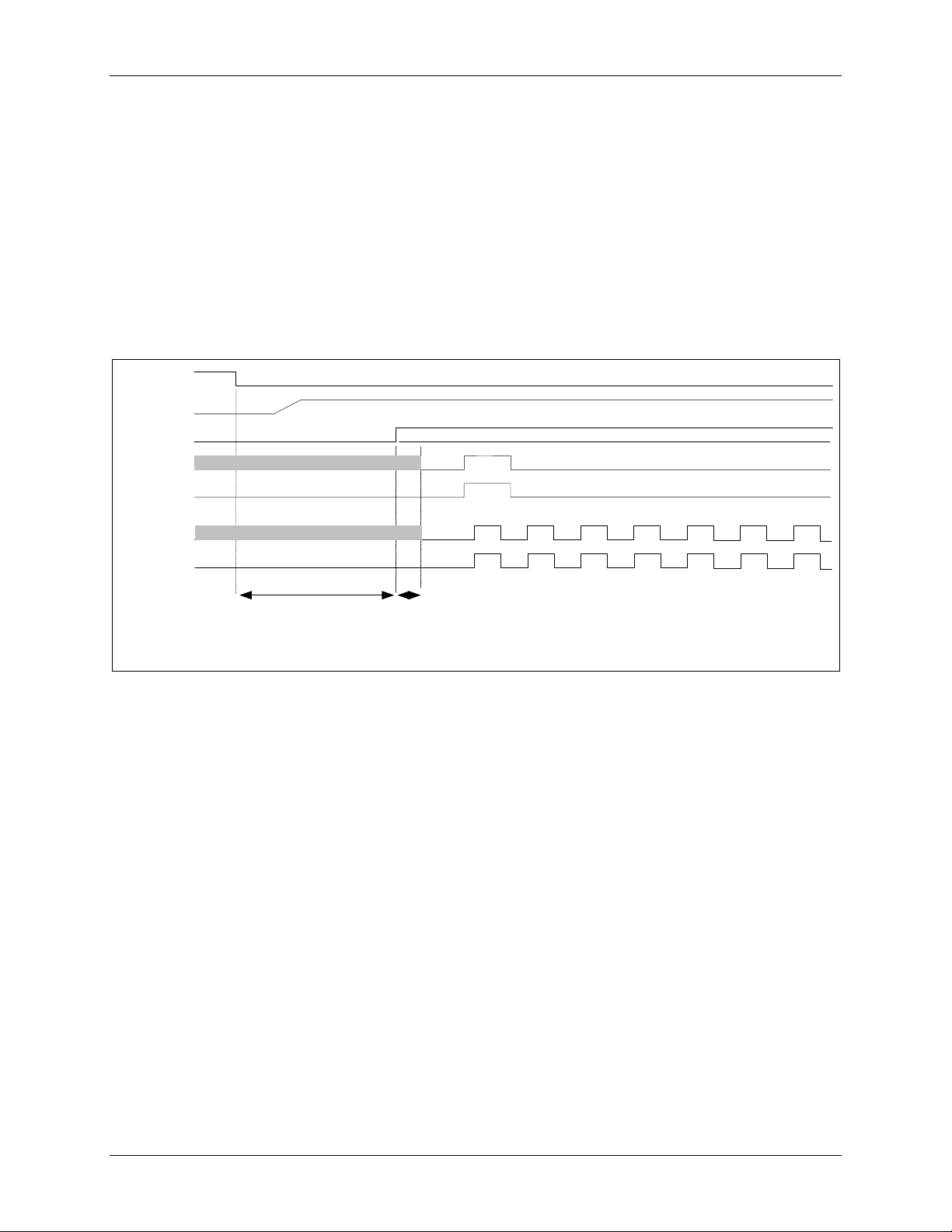

6 Power Down

A power down function is provided via the PWRDN pin (active high). When activated, the Power Down

(PD) mode disables all the internal analog functions, including the card analog interface, t he oscillators

and the DC-DC converter, to put the 73S8023C i n its lowest power consumption mode. PD mode is only

allowed in the deactivated condition (out of a card session, when the CMDVCC signal is driven high from

the host controller).

The host controller invokes the power down state when it is desirable to save power. The signals PRES

and PRES remain functional in PD mode such that a card ins ertion sets OFF high. The micro-controller

must then set PWRDN low and wait for the internal stabilization time prior to starting any car d session

(prior to turning CMDVCC low).

Resumption of the normal mode occurs approximately 10 ms (stabilization of the internal oscillators and

reset of the circuitry) after PWRDN is set low. No card activation should be invoked during this 10 ms

time period. If a card is present, OFF can be used as an indication that the circuit has completed its

recovery from power-down state. OFF will go high at the end of t he stabilization period. Should

CMDVCC go low during PWRDN = 1, or wi thin the 10 ms internal stabilization / reset time, it will not be

taken into account and the card interface will remain inactive. Since CMDVCC is taken into account on

its edges, it should be toggled high and low again after the 10 ms to activate a card.

Figure 2 illustrates the sequencing of the P D and Normal modes. PWRDN must be connected to G ND if

the power down function is not used.

Figure 2: Power Down Mode Operation: CS = high

7 Over-temperature Monitor

A built-in detector monitors die temperature. When an over-temperat ure condition occurs, a card

deactivation sequence is initiated, and an error or fault condition is reported to the system controller.

10 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

CMDVCC

VCC

IO

CLK

RSTIN

t

ACT

t

1

RST

STROBE

t

~= 500µs

t1 > 0.5µs after t

ACT

, RST = RSTIN, CLK = STROBE

8 Activation and Deactivation

8.1 Activation Sequence (Synchronous Mode)

The 73S8023C smart card interface IC has an internal ~10 ms delay at power-on reset or on application

> V

of V

DD

activate the card.

The following steps list the activation sequence and the timing of the card control signals when the

system controller sets CMDVCC low:

1. CMDVCC is set low.

2. Turn on VCC and I/O (AUX1, AUX2) to reception mode at the end of (t

3. RST is a copy of RSTIN and CLK is a copy of STROBE after (t

. No activation is allowed at this time. CMDVCC (edge triggered) must then be set low to

DDF

).

ACT

).

1

ACT

Figure 3: Activation Sequence – Synchronous Mode

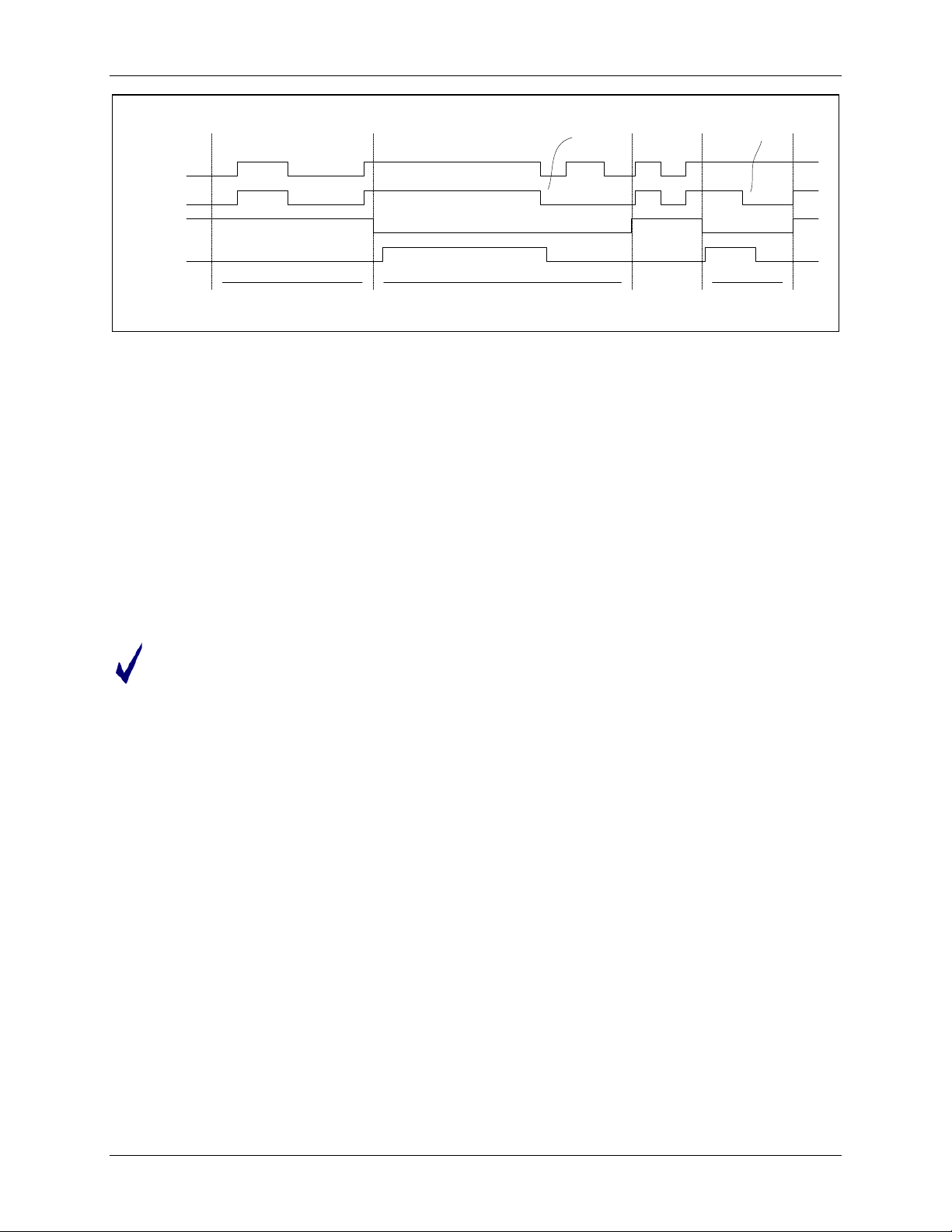

8.2 Deactivation Sequence (Synchronous Mode)

Deactivation is initiated either by the system controller by setting the CMDVCC high, or automatically in

the event of hardware faults. Hardware faults are ov er-current, overheating, V

during the session and are indicated to the system controller by the fall of OFF.

The following steps list the deactivation sequence and the timing of the card control signals when the

system controller sets the CMDVCC high or a fault condition sets OFF low:

1. RST goes low at time t

2. CLK stops low at time t

3. I/O goes low at time t

4. V

is shut down at time t4. After a delay t5 (discharge of the VCC capacitor), V

CC

.

1

.

2

. Out of reception mode.

3

fault and card extraction

DD

is low.

CC

Rev. 1.5 11

73S8023C Data Sheet DS_8023C_019

CMDVCC

VCC

IO

OFF

RSTIN

RST

STROBE

CLK

t0 - Deactivation starts after CMDVCC is set high or OFF falls due to card removal or fault

t

4

- VCC is shut down

(Note: Host should set STROBE low when CMDVCC is set high, otherwise CLK may be truncated.

CLK truncation may occur if an OFF event is triggered)

t

3

- IO falls approx 2us after CLK falls

t1 - RST falls approx. 0.5us after deactivation begins

t

2

- CLK falls approx. 7.5us after RST falls

-- OR --

t

0t1t2t3

t

5

t

4

t5 - VCC goes to 0 after discharge of VCC capacitor, approx 100us after deactivation begins

Figure 4: Synchronous Deactivation Operation – CKSEL = High

8.3 Activation Sequence (Asynchronous Mode)

The 73S8023C smart card interface IC has an internal 10 ms delay at power-on reset or upon application

> V

of V

DD

high which indicates a card is present. No activati on i s all owed at this time. CMDVCC (edge triggered )

must then be set low to activate the card.

or upon exit of Power Down mode. The card interface may onl y be activated when OFF is

DDF

The following steps list the activation sequence and the timing of the card control signals when the

system controller sets CMDVCC low while the RSTIN is low:

1. CMDVCC is set low.

2. Next, the internal VCC control circuit checks the presence of VCC at the end of t1. In normal operation,

the voltage V

low to report a fault to the system controller, and the power V

3. Turn I/O (AUX1, AUX2) to reception mode at the end of t

4. CLK is applied to the card at the end of t

5. RST is a copy of RSTIN after t

to the card becomes valid during t1. If VCC does not become valid, then OFF goes

CC

to the card is turned off.

CC

.

2

.

3

. RSTIN may be set high before t4, however the sequencer won’t set

4

RST high until 42000 clock cycles after the start of CLK.

12 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

CMDVCC

VCC

IO

CLK

RSTIN

t

1

t

2

t

3

t

4

RST

CMDVCC

VCC

IO

CLK

RSTIN

t

1

t

2

t

3

t

4

RST

t1 = 0.510 ms (timing by 1.5 MHz internal Oscillator)

t2 = 1.5 µs, I/O goes to reception state

≥ 0.5 µs, CLK starts

t

3

≥ 42000 card clock cycles. Time for RST to become the copy of RSTIN

t

4

Figure 5: Asynchronous Activation Sequence – RSTIN Low When CMDVCC Goes Low

The following steps list the activation sequence and the timing of the card control signals when the

system controller pulls the CMDVCC low while the RSTIN is high:

1. CMDVCC is set low.

2. Next, the internal V

voltage V

to the card becomes valid during this time. If not, OFF goes low to report a fault to the

CC

system controller, and the power V

3. Due to the fall of RSTIN at t

4. CLK is applied to the card at the end of t

5. RST is to be a copy of RSTIN after t

control circuit checks the presence of VCC at t1. In normal operation, the

CC

to the card is turned off.

CC

, turn I/O (AUX1, AUX2) to reception mode.

2

after I/O is in reception mode.

3

. RSTIN may be set high before t

4

, however the sequencer

4

won’t set RST high until 42000 clock cycles after the start of CLK.

t1 = 0.510 ms (timing by 1.5MHz internal Oscillator)

t

= 1.5µs, I/O goes to reception state

2

t3 = > 0.5µs, CLK active

t

≥ 42000 card clock cycles. Time for RST to become t he copy of RSTIN

4

Figure 6: Asynchronous Activation Sequence – Tim ing Diagram #2

Rev. 1.5 13

73S8023C Data Sheet DS_8023C_019

RST

CLK

I/O

VCC

t

1

t

2

t

3

t

4

t

5

CMDVCC

-- OR --

OFF

8.4 Deactivation Sequence (Asynchronous Mode)

Deactivation is initiated either by the system controller by setting CMDVCC high, or automatically in the

event of hardware faults. Hardware faults are ove r-current, overheating, V

fault, V

DD

extraction during the session.

The following steps list the deactivation sequence and the timing of the card control signals when the

system controller sets the CMDVCC high or OFF goes low due to a fault or card removal:

1. RST goes low at the end of time t

2. CLK stops low at the end of time t

3. I/O goes low at the end of time t

4. V

is shut down at the end of time t4. After a delay t5 (discharge of the VCC capacitor), V

CC

.

1

.

2

. Out of reception mode.

3

fault, and card

CC

is low.

CC

t1 ≥ 0.5 µs, timing by 1.5 MHz internal Oscillator

≥ 7.5 µs t3 ≥ 0.5 µs t4 ≥ 0.5 µs

t

2

= depends on VCC filter capacitor.

t

5

+ t2 + t3 + t4 + t5 ~= 100 µs

t

1

Figure 7: Asynchronous Deactivation Sequence

9 OFF and Fault Detection

There are two cases for which the system controller can monitor the OFF signal: to query regarding the

card presence outside card sessions, or for fault detection during card sessions.

Monitoring Outside a Ca rd Session

In this condition, CMDVCC is alway s high, OFF is low if the card is not present, and high if the card is

present. Because it is outside a card session, any fault detection will not act upon the OFF signal. No

deactivation is required during this time.

Monitoring During a Card Session

CMDVCC is always low, and OFF falls low if the card is extracted or if any fault is detected. A t the same

time that OFF is set low, the sequencer starts the deactivation pro cess.

Figure 8 shows the timing diagram for the signals CMDVCC, PRES, and OFF during a card session and

outside the card session:

14 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

PRES

OFF

CMDVCC

VCC

outside card session within card session

OFF is low by

card extracted

OFF is low by

any fault

within card

session

Figure 8: Timing Diagram – Management of the Interrupt Line OFF

10 I/O Circuitry and Timing

The I/O, AUX1, and AUX2 pins are in the low state after power-on reset and they are in the high state

when the activation sequencer turns on the I/O reception state. See Section 8 Activation and

Deactivation for more details on when the I/O reception is on.

The state of the I/OUC, AUX1UC, and AUX2UC pins is high after power-on reset. Within a card session

and when the I/O reception state is on, the first I /O line on which a falling edge is detected becomes the

input I/O line and the other becomes the output I/O line. When the input I/O line rising edge is detected,

both I/O lines return to their neutral state.

Figure 9 shows the state diagram of how the I /O and I/OUC lines are managed to become input or output.

The delay between the I/O signals is shown in Figure 10.

In order to be compliant to the NDS specifications, a 27 pF c apacitor must be added between pins

I/O (C7) and GND (C5) at the smart card connector.

Rev. 1.5 15

73S8023C Data Sheet DS_8023C_019

Neutral

State

I/OUC

in

I/O

reception

I/OICC

in

No

Yes

No No

No

Yes

No

Yes

I/O

&

not I/OUC

I/OUC

&

not I/O

I/OUC

I/O

yesyes

IO

IOUC

t

IO_HL

t

IO_LH

t

IOUC_HL

t

IOUC_LH

Figure 9: I/O and I/OUC State Diagram

Delay from I/O to I/OUC: t

Delay from I/OUC to I/O: t

Figure 10: I/O – I/OUC Delays Timing Diagram

= 100ns t

IO_HL

I/OUC_HL

= 100ns t

= 25ns

IO_LH

I/OUC_LH

= 25ns

16 Rev. 1.5

73S8023C Data Sheet DS_8023C_019

32QFN

73S8023C

1

4

3

8

6

7

121314

15

24

23

GND

NC

VDD

PRES

PRES

GND

CLK

RST

VCC

XTALOUT

XTALIN

2

LIN

5

PWRDN

CS

16

CLKSEL

29

30

31

28

27

26

CLKDIV1

CLKDIV2

5V/3V

AUX2UC

AUX1UC

I/OUC

25

STROBE

32

CLKOUT

17

18

19

20

21

22

VDDF_ADJ

CMDVCC

RSTIN

VDD

GND

OFF

10911

AUX2

I/O

AUX1

See NOTE 4

VDD

PWRDN_from_uC

Y1

CRYSTAL

C2

22pF

C1

SO7816=1uF,

NDS/EMV=3.3uF

See NOTE 5

RSTIN_from_uC

CLKDIV2_from_uC

CLK track should be routed

far from RST, I/O, C4 and

C8.

I/OUC_to/from_uC

R1

Rext1

See NOTE 1

VDD

C9

100nF

External_clock_from uC

C4

100nF

C3

22pF

AUX1UC_to.from_uC

See NOTE 6

C5

10uF

AUX2UC_to/from_uC

See NOTE 3

See NOTE 1

CLKOUT_to_uC

VDD

CLKDIV1_from_uC

CMDVCC_from_uC

5V/3V_select_from_uC

OFF_interrupt_to_uC

R3

Rext2

- OR -

See note 7

Smart Card Connector

123

4

567

8

9

VCC

RST

CLK

C4

GND

VPP

I/O

C8

SW-1

SW-2

VDD

L1

10uH

CS_from_uC

CLKSEL_from_uC

STROBE_from_uC

See note 2

NOTES:

1) VDD supply must be = 2.7V to 3.6V DC).

3) Required if external clock from uP is used.

4) Required if crystal is used.

Y1, C2 and C3 must be removed if external clock is used.

5) Pin can not float. Must be driven or connected to GND if

power down function is not used.

6) Internal pull-up allows it to be left open if unused.

7) Rext1 and Rext2 are external resistors to ground and

VDD to modify the VDD fault voltage. Can be left open.

2) Keep L1 close to pin 2.

VDD

R2

20K

10

Card detection

switch is

normally

closed.

Low ESR (<100mohms) C1

should be placed near the SC

connecter contact

C8C7

C6

27pF

27pF

27pF

8) Capacitors C7 and C8 are optional. C6 is mandatory for NDS.

11 Ty pical Application Schematic

Rev. 1.5 17

Figure 11: 73S8023C – Typical Application Schematic

73S8023C Data Sheet DS_8023C_019

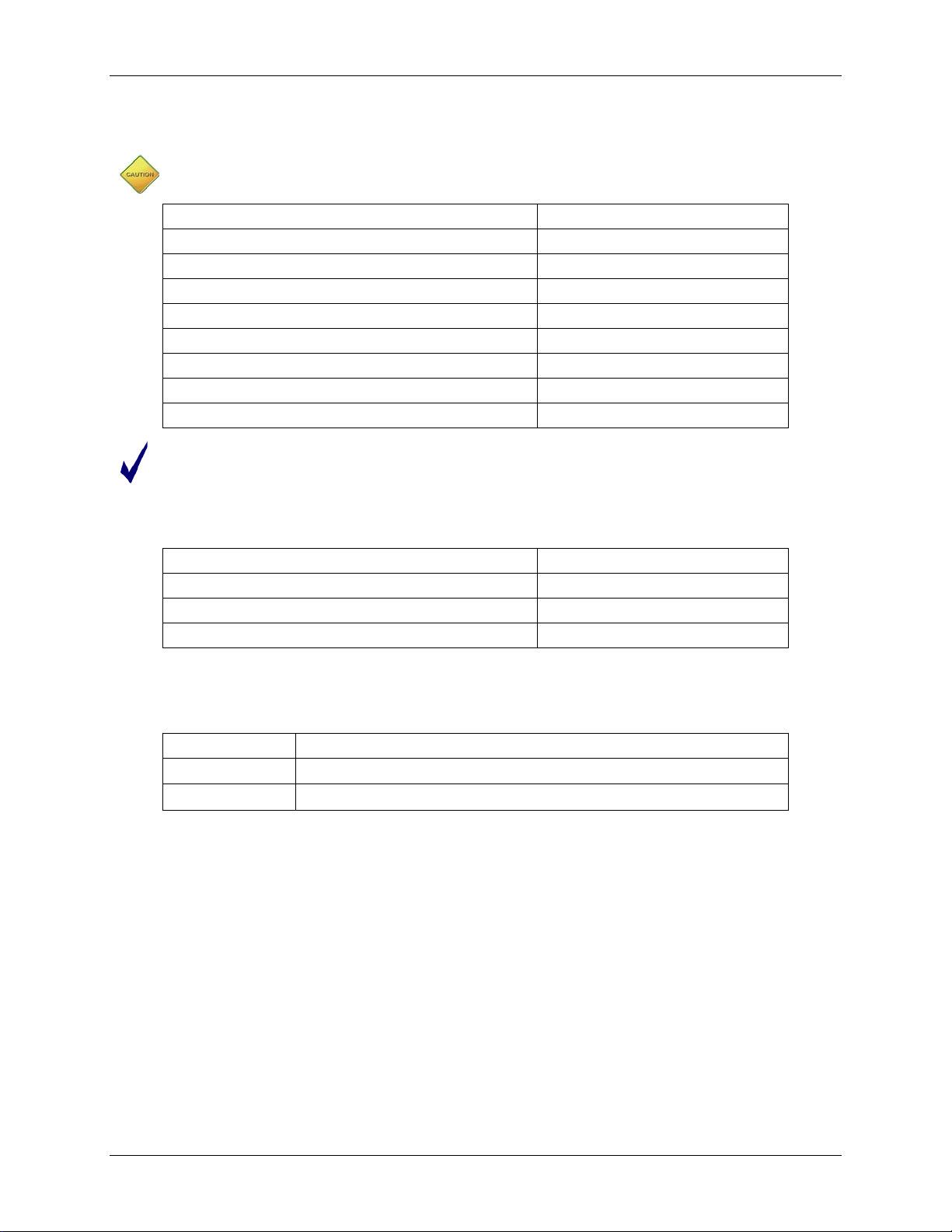

12 Electrical Specification

12.1 Absolute Maximum Ratings

Operation outside these rating limits may cause permanent damage to the device.

Parameter Rating

Supply Voltage V -0.5 to 4.0 VDC

Input Voltage for Digital Inputs -0.3 to (VDD +0.5) VDC

Storage Temperature -60 °C to 150 °C

Pin Voltage (except LIN and card interface) -0.3 to (VDD +0.5) VDC

Pin Voltage (LIN) -0.3 to 6.0 VDC

Pin Voltage (card interface) -0.3 to (VCC + 0.5) VDC

ESD Tolerance – Card interface pins +/- 6 kV

ESD Tolerance – Other pins +/- 2 kV

ESD testing on Card pins uses the HBM condition, 3 pul ses, each polarity referenced to ground.

The smart card pins are protected against shorting between any combination of smart card pins.

12.2 Recommended Operat ing Conditions

DD

Parameter Rating

Supply Voltage V

Ambient Operating Temperature -40 °C to +85 °C

Input Voltage for Digital Inputs 0 V to VDD + 0.3 V

DD

12.3 Package Thermal Parameters

Package Rating

32QFN

32QFN

47 °C / W (with bottom pad soldered)

78 °C / W (without bottom pad soldered)

2.7 to 3.6 VDC

18 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

12.4 Card Interface Characteristics

Symbol Parameter Condition Min Typ Max Unit

Card Power Supply (VCC) DC-DC Converter

General conditions, -40 °C < T < 85 °C, 2.7 V < VDD < 3.6 V

Inactive mode -0.1 0.1 V

Inactive mode

=1 mA

I

CC

Active mode

< 65 mA; 5 V

I

CC

Active mode

< 65 mA; 3 V

I

CC

-0.1

4.75

2.8

0.4 V

5.25 V

3.2 V

Active mode

V

CC

single pulse of 100 mA

for 2 µs; 5 V,

Card supply voltage

including ripple and noise

fixed load = 25 mA

Active mode

single pulse of 100 mA

for 2 µs; 3 V,

4.65 5.25 V

2.76 3.2 V

fixed load = 25 mA

Active mode

current pulses of 40 nAs

with peak |I

| < 200 mA,

CC

4.65

5.25 V

t < 400 ns; 5 V

Active mode

current pulses of 40 nAs

with peak |I

| < 200 mA,

CC

2.76

3.2 V

t < 400 ns; 3 V

V VCC Ripple

350 mV

CCR

I

CCmax

I I

CCF

V

SR

V

SF

C

F

Maximum supply current

to the card

CC

V

slew rate – Rise rate

CC

on activate

V

slew rate – Fall rate

CC

on deactivate

External filter capacitor

(V

to GND)

CC

L Inductor (LIN to V

Limax Imax in inductor

η

Efficiency

DD

Static load current

V

CC

100 > 4.6 or 2.7 V as

mA

selected, L=10 µH

fault current 100 125 180 mA

C

C

on V

F

on V

F

CC

CC

0.05 = 1 uF 0.15 0.25

0.1 = 1 uF 0.3 0.5

0.47 3.3 4.7

) 10

V

CC

V

CC

= 5 V, I

V

DD

= 5 V, I

V

DD

= 65 mA,

CC

= 2.7 V

= 65 mA,

CC

= 3.3 V

400 mA

87 %

V/µs

V/µs

µF

µH

Rev. 1.5 19

73S8023C Data Sheet DS_8023C_019

1011B01 Converter efficiency (VCC 5V)

50

55

60

65

70

75

80

85

90

95

100

0 20 40 60 80 100

Icc [mA]

Efficiency [%]

2.7V

3.0V

3.3V

3.6V

1011B01 Converter efficiency (VCC 3V)

50

55

60

65

70

75

80

85

90

95

100

0 20 40 60 80 100

Icc [mA]

Efficiency [%]

2.7V

3.0V

3.3V (Linear)

3.6V (Linear)

Converter Efficiency (VCC 3 V)

Converter Efficiency (VCC 5 V)

Figure 12: DC – DC Converter effici ency (V

Output current on Vcc at 5 V. Input voltage on V

= 5 V)

CC

at 2.7, 3.0, 3.3 and 3.6 volts.

DD

20 Rev. 1.5

Output current on Vcc at 3 V. Input voltage on V

Figure 13: DC – DC Converter Efficiency (V

at 2.7, 3.0, 3.3 and 3.6 volts.

DD

= 3 V)

CC

DS_8023C_019 73S8023C Data Sheet

Symbol Parameter Condition Min Typ Max Unit

Interface Requirements – Data Signals: I/O, AUX1, AUX2, and host interfaces: I/OUC, AUX1UC,

AUX2UC. I

V

OH

V

OH

V Output level, low

OL

V

IH

V

IH

V Input level, low

-0.3 0.8 V

IL

V

INACT

I Input leakage

LEAK

Output level, high (I/O, AUX1,

AUX2)

Output level, high (I/OUC,

AUX1UC, AUX2UC)

I

Input level, high (I/O, AUX1,

1.8 V

AUX2)

Input level, high (I/OUC,

1.8 V

AUX1UC, AUX2UC)

Output voltage when outside

of session

VIH = V

Input current, low (I/OUC,

AUX1UC, AUX2UC)

I

IL

Input current, low (I/O, AUX1,

AUX2)

SHORTL

, I

SHORTH

, and V

requirements do not pertain to I//OUC, A UX1UC, and AUX2UC.

INACT

I

I

OH

I

OH

OL

I

OL

V

IL

V

IL

1

= 0

OH

= -40 µA

I

OH

= -40 µA

I

OL

CC

V

IL

0.9 V

0.75 V

0.9 V = 0

0.75 V

V

CC

V

CC

V

DD

V

DD

CC

CC

DD

DD

=1 mA 0.3 V

CC

DD

= 0 0.1 V

= 1 mA 0.3 V

10

= 0, CS = 1 0.65 mA

= 0, CS = 0 5

= 0 2 mA

V + 0.1

V + 0.1

V + 0.1

V + 0.1

V + 0.30

V + 0.30

µA

µA

For output low,

I Short circuit output current

SHORTL

shorted to V

CC

15 mA

through 33 Ω

For output high,

I Short circuit output current

SHORTH

shorted to ground

15 mA

through 33 Ω

C

= 80 pF, 10% to

L

tR, t Output rise time, fall times

F

tIR, t Input rise, fall times

1

IF

R Internal pull-up resistor

PU

90%. For I/OUC,

AUX1UC, AUX2UC,

= 50 pF

C

L

Output stable for

> 200 ns

100 ns

8 11 14

µs

kΩ

For pins IOUC,

Ipuhiz Pull-up current, Hi-Z state

AUX1UC, AUX2UC

5

µA

when CS = 0

FD Maximum data rate

1

MAX

MHz

Delay, I/O to I/OUC,

I/OUC to I/O

100 Started

(falling edge to falling edge)

T

FDIO

Delay, I/O to I/OUC,

I/OUC to I/O

10

ns

(rising edge to rising edge)

C Input capacitance

10 pF

IN

1

NDS applications require a 27 pF capacitor on I/O pl aced at the smart card connector.

Rev. 1.5 21

73S8023C Data Sheet DS_8023C_019

Symbol Parameter Condition Min Typ Max Unit

Reset and Clock for card interface, RST, CLK

V Output level, high

OH

V Output level, low

OL

V

INACT

I Output current limit, RST

RST_LIM

I Output current limit, CLK

CLK_LIM

Output voltage when outside

of a session

30 mA

70 mA

I

= -200 µA

OH

I

= 200 µA

OL

I

OL

I

OL

= 35 pF for

C

L

CLK, 10% to 90%

tR, t Output rise time, fall time

F

= 200 pF for

C

L

RST, 10% to 90%

0.9 V

0

CC

V V

CC

0.2 V

= 0 0.1 V

= 1 mA 0.3 V

8 ns

100 ns

CLKSEL = 1, Cap.

load on CLK and

RST is minimal,

else rise, fall times

20 ns

Td

Delay time STROBE to CLK,

RSTIN to RST

are a factor

C

= 35 pF,

δ

Duty cycle for CLK

L

48% < δ

< 52%

IN

45

55 %

12.5 Digital Signals

Symbol Parameter Condition Min Typ Max Unit

Digital I/O Except for OSC I/O

VIL Input Low Voltage -0.3 0.8 V

VIH Input High Voltage 1.8 VDD + 0.3 V

VOL Output Low Voltage IOL = 2 mA 0.45 V

VOH Output High Voltage IOH = -1 mA VDD - 0.45 V

R

OUT

tSL

tDZ

tIS

tSI

tID

tDI

|I

| Input Leakage Current GND < VIN < VDD -5 5 μA

IL1

Pull-up resistor, OFF

Time from CS going high to

interface active

Time from CS going low to

interface inactive, Hi-Z

Set-up time, control signals

to CS rising edge

Hold time, control signals

from CS rising edge

Set-up time, control signals

to CS fall

Hold time, control signals

from CS fall

20

50 ns

50 ns

50 ns

50 ns

50 ns

50 ns

kΩ

22 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

Symbol Parameter Condition Min Typ Max Unit

Oscillator (XTALIN) I/O Parameters

V

Input Low Voltage - XTALIN -0.3 0.3 VDD V

ILXTAL

V

Input High Voltage - XTALIN 0.7 VDD VDD+0.3 V

IHXTAL

I

Input Current - XTALIN GND < VIN < VDD -30 30 μA

ILXTAL

f

Max freq. Osc or external clock 27 MHz

MAX

δin

External input duty cycle limit

tR/F < 10% fIN,

45% < δ

CLK

< 55%

48 52 %

12.6 DC Characteristics

Symbol Parameter Condition Min Typ Max Unit

I Supply Current on V

DD

DD

Linear mode, ICC = 0

I/O, AUX1, AUX2 = high

Step up mode, ICC = 0

I/O, AUX1, AUX2 = high

4.9 mA

4.7 mA

PWRDN = 1,

I

DD_PD

Supply Current on V

Power Down mode

DD

in

Start/stop bit = 0

All digital inputs driven

0.11 2.5

µA

with a true logical 0 or 1

12.7 Voltage / Temperature Faul t Detection Circuits

Symbol Parameter Condition Min Typ Max Unit

V

fault – V

V

DDF

V

CCF

T Die over temperature fault

115 145

F

I Card over current fault

100 150 mA

CCF

DD

supervisor threshold)

V

fault – V

CC

supervisor threshold

Voltage

DD

Voltage

CC

No external resistor on

VDDF_ADJ

V

CC

V

CC

2.15 2.4 V

4.20 = 5 V 4.6 V

2.5 = 3 V 2.7 V

°C

Rev. 1.5 23

73S8023C Data Sheet DS_8023C_019

2.5

5

2.5

5

TOP VIEW

1

2

3

0.85 NOM.

/

0.9MAX.

0.00 / 0.005

0.20 REF.

SEATING

PLANE

SIDE VIEW

0.2 MIN.

0.35 / 0.45

1.5 / 1.875

3.0 / 3.75

0.18 / 0.3

BOTTOM VIEW

1

2

3

0.25

0.5

0.5

0.25

3.0 / 3.75

1.5 / 1.875

0.35 / 0.45

CHAMFERED

0.30

13 Mechanical Drawing (32-QFN)

Figure 14: 32-QFN Mechanical Drawing

24 Rev. 1.5

DS_8023C_019 73S8023C Data Sheet

6

7

8

9

5

4

3

2

1

17

18

19

20

24

23

22

21

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

GND

LIN

VDD

NC

PRDWN

PRES

PRES

I/O

XTALOUT

XTALIN

OFF

GND

VDD

RSTIN

CMDVCC

VDDF_ADJ

AUX2

AUX1

GND

CLK

RST

VCC

CLKSEL

TERIDIAN

73S8023C

STROBE

CLKOUT

5V/3V

CLKDIV2

CLKDIV1

AUX2UC

AUX1UC

I/OUC

CS

14 Package Pin Designation (32-QFN)

Use handling procedures necessary for a static sensitive component.

(Top View)

Figure 15: 32-QFN 73S8023C Pin Out

Rev. 1.5 25

73S8023C Data Sheet DS_8023C_019

15 Ordering Inf ormation

Part Description Order Number Packaging Mark

73S8023C-QFN 32-pin Lead-Free QFN 73S8023C-IM/F 73S8023C

73S8023C-QFN 32-pin Lead-Free QFN Tape / Reel 73S8023C-IMR/F 73S8023C

16 Related Documentation

The following 73S8023C documents are availabl e from Teridian Semiconductor Corporation:

73S8023C Data Sheet (this document)

73S8023C QFN Demo Board User’s Guide

17 Contact Information

For more information about Teridian Semiconductor products or to check the availability of the

73S8023C, contact us at:

6440 Oak Canyon Road

Suite 100

Irvine, CA 92618-5201

Telephone: (714) 508-8800

FAX: (714) 508-8878

Email: scr.support@teridian.com

For a complete list of worldwide sales offices, go to http://www.teridian.com.

26 Rev. 1.5

Loading...

Loading...