Simplifying System IntegrationTM

73S8009C

Demo Board User Manual

February 10, 2010

Rev. 1.3

UM_8009C_059

73S 8009C D emo Board User Man ual UM_8009C_059

© 2010 Teridian Semicond uctor Corporation. A ll rights reserved.

Terid i an Semiconductor Corpor ation i s a registered trademark of Teridi an Semiconductor Cor poration.

Simplifying Syst em Integrat i on is a trademark of Teridian Semi condu ct or Corporat ion .

All other t r ademar ks are the property of their respective owners.

Terid i an Semiconductor Corpor ation makes no warrant y for the use of i ts pr oducts, other than exp r essly

contained in the Company’s warranty detailed in the Teridian Semiconduct or C or poration standard Terms

and C onditi ons. The company assumes no respon sibility for any errors which may appear in this

document, reserves the right to change devices or specifi cations detailed herein at any tim e without

notice and does not make any co mm i tment to update the information contained herein. Accordingly, the

reader is cautioned to veri fy that th i s document is current by comp ar i ng it to the latest version on

http://www.teridian.com or by checking with your sales r epresentative.

Terid i an Semiconductor Corp., 6440 Oak Canyon, Suite 100 , Irvine, CA 92618

TEL (714) 508-8800, FAX (714) 508-8877, http://www.teridian.com

2 Rev. 1.3

UM_8009C_059 73S8009C Demo Board User Man ual

Table of Contents

1 Introduction ................................................................................................................................... 5

1.1 Packa ge Contents.................................................................................................................... 5

1.2 Safety and ESD Notes ............................................................................................................. 5

1.3 Recommend ed Operating Conditions and Absolute Maximum Ratings ..................................... 6

1.4 Notes When Using a 73S12xxF Evaluation Board .................................................................... 6

2 Connections ................................................................................................................................... 7

3 Jumpers, Switches and Test Poin t s ............................................................................................. 9

4 Design Considerations ................................................................................................................ 12

4.1 Gener al Layout Rules ............................................................................................................ 12

4.2 Optimization for C ompl i ance with EMV ................................................................................... 12

4.3 Power Supply Input Configurations ........................................................................................ 12

4.3.1 USB Power ................................................................................................................. 12

4.3.2 Single Supply Power ................................................................................................... 12

4.4 ON/OFF Switch Operation ..................................................................................................... 13

5 73S8009C Demo Board Schematics, PCB Layouts and Bill of Materials .................................. 14

5.1 Schematics ............................................................................................................................ 14

5.2 73S8009C PCB Layouts ........................................................................................................ 15

5.3 73S 8009C D emo Board Bill of Material s................................................................................. 18

6 Errata ............................................................................................................................................ 18

7 Ordering Information ................................................................................................................... 19

8 Related Documentation ............................................................................................................... 19

9 Contact Information ..................................................................................................................... 19

Revision History .................................................................................................................................. 20

Rev. 1.3 3

73S 8009C D emo Board User Man ual UM_8009C_059

Figures

Figure 1: 73S800 9C Demo Board

Figure 2: 73S800 9C Demo Board External Con nector s

Figure 3: 73S8009C Demo Board Description

Figure 4: 73S8009C Electrical Schematic

Figure 5: 73S800 9C Demo Board: Top View

Figure 6: 73S800 9C Demo Board: Bottom V iew

Figure 7: 73S8009C Demo Board: Top Signal Layer

Figure 8: 73S8009C Demo Board: Middle Layer 1, Ground Plane

Figure 9: 73S8009C Demo Board: Middle Layer 2, Supply Plane

Figure 10: 73S80 09C Demo Board: Bottom Signal Layer

Tables

Table 1: Recommended Oper ating Condi tions

Table 2: Absolute Maximum Rati ngs

Table 3: J4 Pin Descriptions

Table 4: J2 Pin Descriptions

Table 5: 73S8009C Demo Board Descr i ption

Table 6: 73S8009C Demo Board Bill of Materials

Table 7: 73S8009C Demo Board Order Number

............................................................................................................ 5

............................................................................ 7

.......................................................................................... 9

.............................................................................................. 14

.......................................................................................... 15

..................................................................................... 15

.............................................................................. 16

.......................................................... 16

........................................................... 17

....................................................................... 17

......................................................................................... 6

........................................................................................................ 6

.................................................................................................................... 7

.................................................................................................................... 8

......................................................................................... 10

................................................................................... 18

.................................................................................... 19

4 Rev. 1.3

UM_8009C_059 73S8009C Demo Board User Man ual

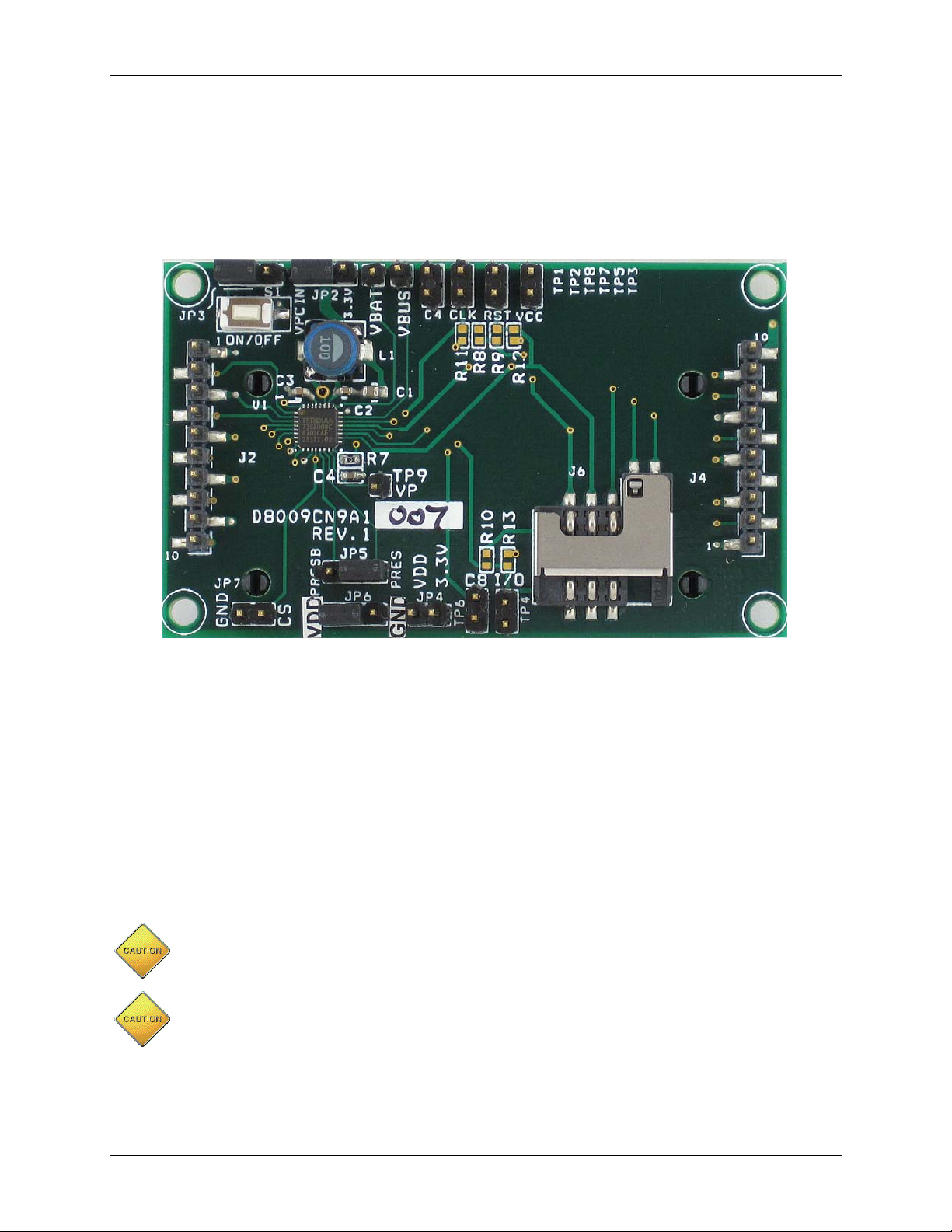

1 Introduction

The Teridian Semiconductor Corpor ation 73S8009C Demo Board is a platform for evaluating the Teridian

73S8009C 32-pin QFN Smart Card Interface IC . It incorporates the 7 3S8009C integrated ci r cuit, and it is

desi gned to operate either as a standalone platform (t o be used in conjunction with an external

microcontroller) or as a d aughter car d to be used in conjunction with the 73S12xxF evaluation platform.

1.1 Package Contents

Figure 1: 73S8009C Demo Board

The 73S8009C Demo Board Kit includes:

• A 73 S8009C D emo Board (R ev. 1)

• The following d ocument s:

• 73S8009C Data Sheet

• 73S8009C Demo Board User Ma n ual (this document)

1.2 Safety and ESD Notes

Connecting live voltages to the 73S8009C Demo Board system will result i n potentially hazardous

voltages on the boards.

Extreme caution should be taken when handling the 73S8009C Demo Board after

connection to live voltages!

The 73S8009C De mo Board is ESD sensitive! ESD precautions should be taken when

handling this board!

Rev. 1.3 5

73S 8009C D emo Board User Man ual UM_8009C_059

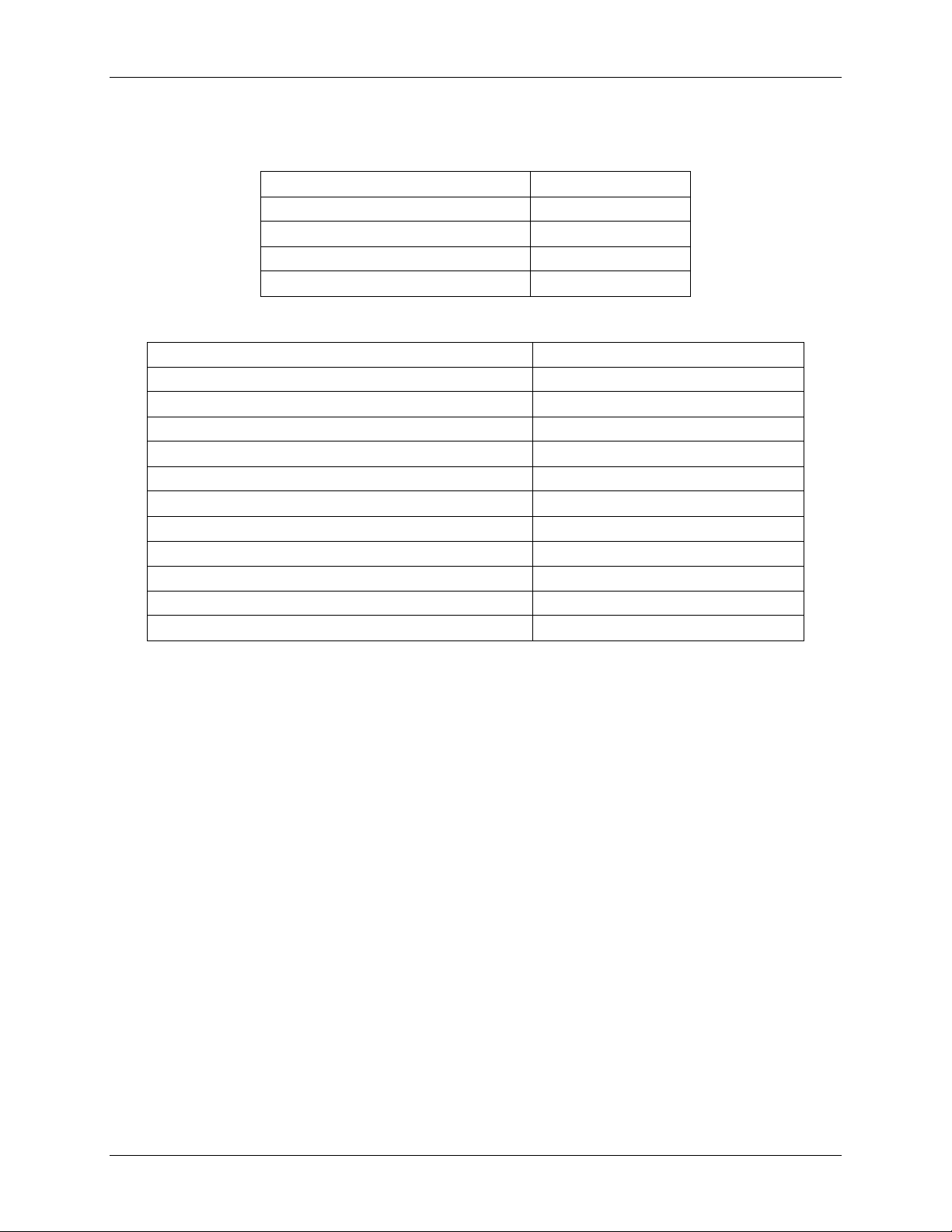

1.3 Recommended Operating Conditions and Absolute Maximum Ratings

Table 1: Recommended Operati ng Conditions

Parameter Rating

Sup ply Voltage VPC 2.7 to 6.5 VDC

Sup ply Voltage V

Sup ply Voltage V

4.4 to 5.5 VD C

BUS

4.0 to 6. 5 °C

BAT

Ambient Operating Temperature -40 °C to +85 °C

Table 2: Absolute Maximum Ratings

Parameter Rating

Sup ply Voltage V

Sup ply Voltage V

-0.5 to 6. 6 VDC

BUS

-0.5 to 6. 6 VDC

BAT

Sup ply Voltage VPC -0.5 to 6. 6 VDC

Input Voltage for Digital Inputs -0.3 to (VDD+0.5) VDC

Stor age Temp er ature -60 to 150 °C

Pin Voltag e ( except card interface) -0.3 to (VDD+0.5) VDC

Pin Voltag e ( card interface) -0.3 to (VCC+0.3) VDC

Pin Voltage, LIN pin 0.3 to 6.5 VD C

ESD Tolerance – Card interface pins ± 6 kV

ESD Tolerance – Other pins ± 2 kV

Pin Current ± 200 mA

Oper ation outsi de these r ating limits may cau se permanent damage to the d evice.

ESD test ing on Card pins is HBM condition, 3 pul ses, each pol ar ity referenced to ground .

1.4 Notes When Using a 73S12xxF Evaluation B oar d

The 73S12xxF Evaluation B oar d has two power supplies; 3.3 V and 5.0 V. Normally, t he 5.0 V supply is

tied to VPC IN on the 73S8009C board. The 73S8009C can supply the 3.3 V to the remainder of the

system by configuring the jumpers accordingly. The 73S8009C VDD output can be disconnected from

the r est of the evaluation board i f desired and the 3.3 V supply on the 73S12xxF Evalu ation Board ca n be

used. See t he jump er descri ptions for more details.

6 Rev. 1.3

UM_8009C_059 73S8009C Demo Board User Man ual

2 Connections

This se ction descr i bes the 73S8009C Dem o Board external co nnectors. All t he digital signals and power

supply connection s are made through 10-pin header connectors labeled J2 and J4 i n Fig ur e 2.

Figure 2: 73S8009C Demo Board External Connectors

Table 3 describes the pins for the J4 connector. There is one power pin (Pin 1) and one ground pin (Pin 9).

Table 3: J4 Pin Descriptions

Pin Pin N ame

1 CMDVCC%

2 CMDVCC#

Controls the turn-on, output voltage value, and turn-off of V

Function

CC

.

3 RSTIN Controls the card reset signal.

4 RDY Indicates when smart card power supply is stable and ready.

5 OFF_ACK

6 OFF_REQ

Setti n g OFF_AC K hi g h powers “off” all analog functions and

disconnects the 73S8009C from V

or VPC.

BAT

Digi tal output . Request to the h ost system controller to tur n

the 73S8009C off.

7 CS Chip Select – active hi gh.

8 N/C No Connect.

9 GND Ground.

10 VDD

System in terface supply voltage and supply voltage for

companion controller circuitry.

Rev. 1.3 7

73S 8009C D emo Board User Man ual UM_8009C_059

Table 4 descri bes the J2 connector pin s.

Table 4: J2 Pi n Descr iptions

Pin Pin Name Function

1 SCLK Clock source input.

2 I/OUC System controller data I /O to/from the card.

3 SC4 System controller auxili ary dat a C4 to/ from the card .

4 SC8 System controller auxili ary dat a C8 to/ from the card .

5 OFF Interrupt signal to the processor. Indicator of card presence

and any card fault conditions.

6 GND Ground.

7 GND Ground.

8 GND Ground.

9 VPC IN Must be between 2.7 V and 6.5 V.

10 VPC IN Must be between 2.7 V and 6.5 V.

Connections should be made in this order:

• Power Supplies: Apply 3.3 V to pin 10 of J4 or 5 V to pins 9 and 10 of J2 dependi ng on the setting of

JP2.

• Press the ON/OFF button.

• Control signals to the device can be connected through J2 and J4. See Figure 2 and Figure 4.

• Appl y t he clock signal.

8 Rev. 1.3

UM_8009C_059 73S8009C Demo Board User Man ual

3 Jumpers, Switches and Test Points

The items marked in Figure 3 are described in Table 5.

Figure 3: 73S8009C Demo Board Description

Rev. 1.3 9

73S 8009C D emo Board User Man ual UM_8009C_059

Table 5: 73S8009C Demo Board Description

Item #

(Figure 3)

Electrical

Schematic &

PCB Silkprint

Name Use

Reference

1 S1 ON/OFF switch Push-button swit ch to turn on/off the 73S8009C.

Note: OFF_ACK must be set high to turn off.

2 JP3 ON_OFF Jumper When set to 1-2, the ON_ OF F input i s set to ground

which turns on th e 73S8009C when power is

applied. When set to 2-3, the push button switch is

connected to the ON_OF F p in.

When using VBUS as an always on configuration,

JP3 must be set to the 1-2 position and the

OFF_ACK inp ut m ust be gro unded .

3 JP2 VPC Sel e ct The VPC input can select between the VPC_I N and

the 3.3 V inputs. When selecting the VPC_IN, the

VDD outpu t can source the 3.3 V supply on the

evalu ation board. See the descri ption for JP4.

4

5

6

7

8

9

12

13

TP1

TP2

TP8

TP7

TP5

TP3

TP4

TP6

Test Poi nts:

VBAT Test point

VBUS Test point

C4

CLK

RST

VCC

I/O

C8

VBAT Input

VBUS Input

Two-pin test points for each r espective smar t card

sig nal. Th e pin lab el name is the respect ive signal

(i.e. VCC, CLK) and the other pi n i s GND.

10 J4 Board 3.3 V

supply and digital

control signals

Connector that ei ther gathers or supp l ies the 3.3 V

supply. It includes the 73S8009C host control

signal pins RDY, CS, OFF_REQ, OFF_ACK,

CMDVCC%, CMDVCC#, and RSTIN.

11 J6 Smart Card

Connector

SIM /SAM sm ar t card format connector.

Note t hat J6 i s wired in parall el to the smart card

connector J5 (underneat h the PCB). J5 and J6 are

never to be used at t he same time.

14 JP4 VDD Select When the jumper is inserted, th e 73S8009C VDD

output is connected to the 3.3 V power pl ane.

When using in conjunction with a 73S12xxF

Evaluat ion Boar d or other host, it supplies the 3.3 V

source on the on that platform if it is so configured.

Caution must be taken as d amage could occur if the

73S12xxF Evaluation Board or host i s sourcing

3.3 V with this jumper in serted . R emoval of t he

jumper provides proper isolation with any host

platform.

10 Rev. 1.3

UM_8009C_059 73S8009C Demo Board User Man ual

this demo board, the switch is nominally open. The

Item #

(Figure 3)

15

18

16 J5 Smart Card

17 JP7 CS Disable CS Disab le Jumper. Inser tion of jumper disables

19 TP9 Vp Test Point Test point to monitor the int er nal int er medi ate

20 J3 Board VPC_IN

Electrical

Schematic &

PCB Silkprint

Reference

JP6

JP5

Name Use

Card Polarity

detect select

Connector

supply, smart

card data signals

and OFF

The setting of these two jumpers depends on the

type of smart card connector used (whether switch

is n ominally open or cl osed ) , and which of the card

presence switch input of the 73S8009C is used. In

jumpers can be set i n one of t wo ways:

1. Default setting: Use of PRES: JP5 must be

set to PRES , and JP6 set to VDD

2. Alternative use: Use of PRES: JP5 must be

set to PREB , and JP6 set to GND

Note: see board errata in t he appendix for JP6

Smart card connector.

When inser ting a card (credit card size format),

contacts must face up.

the 73S8009CN. The state of the CMDVCC#,

CMDVCC% and RSTIN i nputs will be lat ched and

the I/OUC, AUX1UC and AUX2 UC ar e tri-stated.

The OFF and RDY outputs are also tri-stated.

voltage regulator. This regulator output takes the

VPC voltage and step it up to more t han 5 V (if

necessary) as the input source for the VCC and

VDD output regulators.

Connector that supplies the VPC input supply

voltage, t he smart card data interface signals and

the OFF interrupt output.

Rev. 1.3 11

73S 8009C D emo Board User Man ual UM_8009C_059

4 Design Considerations

4.1 General Layout Rules

Follow these layout rules:

• Route I/O and auxiliary si gnals away from card interface signals.

• Keep C LK trace as sh or t as possib l e and with m i nimal bends i n the trace . If possible, keep routin g of

the CLK trace to one layer (avoid vias to other laye r s). Keep CL K trace away from other traces

especially RST, I/O and VCC. Filt er i ng of t he CLK trace is allowed for noise purposes. Up to 30 pF

to gr ound is allowed at the CLK pin of t he smart card conn ector. Al so, the zero Ω series resistor (R7)

can be replaced with a small resistor for ad diti onal fi l tering (no more than 100 Ω).

• Keep VCC tr ace as short as possibl e. Make tr ace a minimum of 0.5 mm thick. Also, keep VCC away

from ot her traces especial ly RST an d CL K.

• Keep R ST trace away from VCC and CLK traces. Up to 30 pF to grou nd is all owed for filtering.

• Keep 0.1 µF close to VD D pin of the device and directly take other end to g r ound.

• Keep 0.1 µF and 10 µF close to VPC pin of the d evice and directly take other en d to ground.

• Keep 4.7 µF close to VP pin of the device and d i r ectly take other end to ground.

• Keep 0.47 µF close to VCC pin of the smart card connector and direct l y take other end to ground.

4.2 Optimization for Compliance with EMV

Default configuration of the D emo boar d con tains a 27 pF capacitor (C 12) from the CLK pin of the smart

connector to ground and a 27 pF cap acitor (C 13) from the RST pin of the smart connector to ground.

These capacit ors serve as fi l ters for CLK and RST si gnals in the case of long traces or test equipm ent

pert ur ba ti o ns. T he capacitor on CLK r educes ringing on the trace, r educe s coupl i ng to ot her traces and

slo ws down the edg e of the CLK sign al . The capacitor on RST h elps the pertur bation specifi cation in a

noisy environment. Th e filter capacitor s can be useful in the EMV t est en vironment and have no effect on

NDS testing

C12 and C13 are represented on both sch em atic and BOM. These cap acitors ar e optional fil ter

capacitors on the smart card li nes CLK and RST, respectively for each card interface. These capacitors

may be adjusted ( value, n ot to exceed 30 p F) or removed to op timi ze performance in each specific

app l ication (PCB, card clock frequen cy , comp liance with applicable standard s etc).

4.3 Power Supply Input Configurations

4.3.1 USB Power

The USB confi guration use s the po we r supplied by the VBUS (4.4 to 5.5 V) and an opt ional VBAT input

that automatically switches from the VBUS to VBAT when the V BUS power is removed. This swi tch over

is d one smoot hly and does not cause any di srupt i on of th e operati on of th e 73S8009C and the VD D

output supply. The operat i on of t he ON/OFF switch is overridden when VBUS is applied. The 73S8009C

and VDD output will always be active while the VBUS voltage i s applied. The ON/OFF switch is enabled

when running off VBAT. When using this configuration, the VPC input should not be connected to an y

other power source.

4.3.2 Single Supply Power

The single supply configuration should leave the VBUS and VBAT pins unconnected and only connect

the power supply to VPC (2.7 to 6.0 V).

12 Rev. 1.3

UM_8009C_059 73S8009C Demo Board User Man ual

4.4 ON/OFF Switch Operation

The ON/OF F switch uses a pushbutton to toggle between tur ning the 73S8009C on and off. The switch

input contains a debounce circuit for protection. The 73S8009C defaults to the OFF stat e when the

power source is applied. When the 8009C is in the OFF state, a switch closure turns on the 73S8009C.

When the 73S8009C is ON, a swit ch cl osure does not turn off the 73S8009C by itself, but it activates the

OFF_REQ signal by setting it high. The 73S8009C does not shut off until the OFF_ACK is set high. The

purpose of this sequen ce is to al low the h ost pr ocessor to perform any necessary sh ut down tasks before

losing power. When the host is finished, it can set the OFF_ACK signal high to shut off the 73S8009C. If

ther e is no need for the host to perform any shutd own tasks, the OFF_ACK pin ca n be left open an d it

follows t he state of the OFF_REQ output by means of an i nternal resistor connection between the

OFF_REQ and OFF_ACK pins.

When power is applied to VBUS, the 73S8009C automat i cally turns on and the ON/OFF switch is

overidden. However, care must be taken as the ON_OFF in put is internally latched while th e VBUS

is ap plied . When VBUS is removed, the latched state of the ON/OFF switch input dictates the state

of the 73S8009C. If t he switch input was not closed, the state of t his latch will not chang e. It will b e

in th e same state before the VBUS power was applied. If it has changed it holds the last toggled

state. The OFF_REQ output follows this toggling. If the OFF_REQ output is high when VBUS

power is removed and the OFF_ACK is high, the 73S8009C shuts off.

Rev. 1.3 13

73S 8009C D emo Board User Man ual UM_8009C_059

1 2

S1 SW

1

2

JP7

CS

Disable

Note: VPCIN

must be

between 2.7

and 6.5V

3.3V

1

2

3

4

5

6

7

8

9

10

J4

TSM_110_01_L_SV

C12

30pF

C3

0.1uF

IOUC

1

AUX1UC

2

AUX2UC

3

CMDVCC5

4

CMDVCC3

5

RSTIN

6

CLKIN

7

RDY

8

OFF_ACK

9

TEST1

10

OFF_REQ

11

CS

12

PRES

13

PRES

14

VP

15

GND

17

RST

18

VCC

19

AU X2

20

AU X1

21

IO

22

VBUS

23

ON/OFF

24

VBAT

25

VPC

26

LIN

27

GND

28

VDD

29

TEST2

30

GND

31

OFF

32

CLK

16

SLUG

33

U1

73S8009C

VPCIN

+

C1 10uF

3.3V

VPC

SELECT

L1

3.3V

1

2

3

4

5

6

7

8

9

10

J3

SSM_110_L_SV

AUX1UC

AUX2UC

IOUC

RDY

OFF_ACK

R13

Rd

R10

Ru

1

TP9

AU X1

AU X2

IO

CMDVCC#CMDVCC#CMDVCC#CMDVCC#CMDVCC#CMDVCC#CMDVCC#CMDVCC#CMDVCC#CMDVCC#CMDVCC#

CLKIN

C9

30pF

OFF

C11

0.47uF

C1

1

C2

2

C33C5

4

C65C7

6

SW1

7

SW2

8

J6

SIM/SAM Connect or

RST

CLK

CMDVCC%CMDVCC%CMDVCC%CMDVCC%CMDVCC%

1

TP1

C2 0.1uF

RSTIN

1

2

TP3

VCC

1

RST

2

CLK

3

C4

4

GND

5

VPP

6

I/O

7

C8

8

SW-1

9

SW-2

10

J5

Smart C ard C onnec t or

VCC

R8RuR9

Ru

R11

Rd

VPCIN

R12

Rd

R7 0

USR7

CMDVCC#

1

2

3

4

5

6

7

8

9

10

J1

SSM_110_L_SV

CMDVCC3

OFF_REQ

CS

C4

4.7uF

1

2

3

JP6

1

2

3

JP5

1

2

TP5

123

JP3

1

2

TP7

1

2

TP8

1

2

TP4

1

2

TP6

1

2

JP4

3.3VNote: JP4 pins 1

and 2 must not be

connected with JP2

pins 1 and 2 at the

same time.

GND

C8

DNI

SC4

TP3 to TP8, C9, C11 and

C12 are to be placed

very close to the pads

of J5

PRES

PRES

CARD DETECT

POLARITY

SELECT

CLK

RDY

VDD

VDD

1

2

3

JP2

OFF_ACK

GND

R8 to R13 and C36 to be

placed within 1cm of

J7.

DNI

PRES

J1 must be aligned with J2 and J3 must be

aligned with J4 in order for this daughter

board to be stacked on another.

OFF_REQ

+3.3V

DNI

CS

DNI

RSTIN

VPCIN

PRES

J1 and J3 are placed on the bottom. J2 and J4

are placed on the top side.

RST

VPCIN

GND

1

TP2

J1 and J3 must be aligned with J8 and J9 on the

1121 evaluation board (E1121T8) respectivly in

order for this board to be stacked on it.

CMDVCC5

DNI

VCC

SCLK

C4

C1, C2, C3 and L1 must be placed

within 5mm of the U1 pins and

connected by thick track (wider

than 0.5mm)

VDD

SC8

DNI

GND

SIO

Note: JP4 pins 1

and 2 should only

be connected when

3.3V is not sourced

from the mating

board (if

applicable)

OFF

GND

1

2

3

4

5

6

7

8

9

10

J2

TSM_110_01_L_SV

I/O

5 73S8009C Demo Board Schematics, PCB Layouts and Bill of Materials

5.1 Schematics

14 Rev. 1.3

Figure 4: 73S8009C Electrical Schematic

UM_8009C_059 73S8009C Demo Board User Man ual

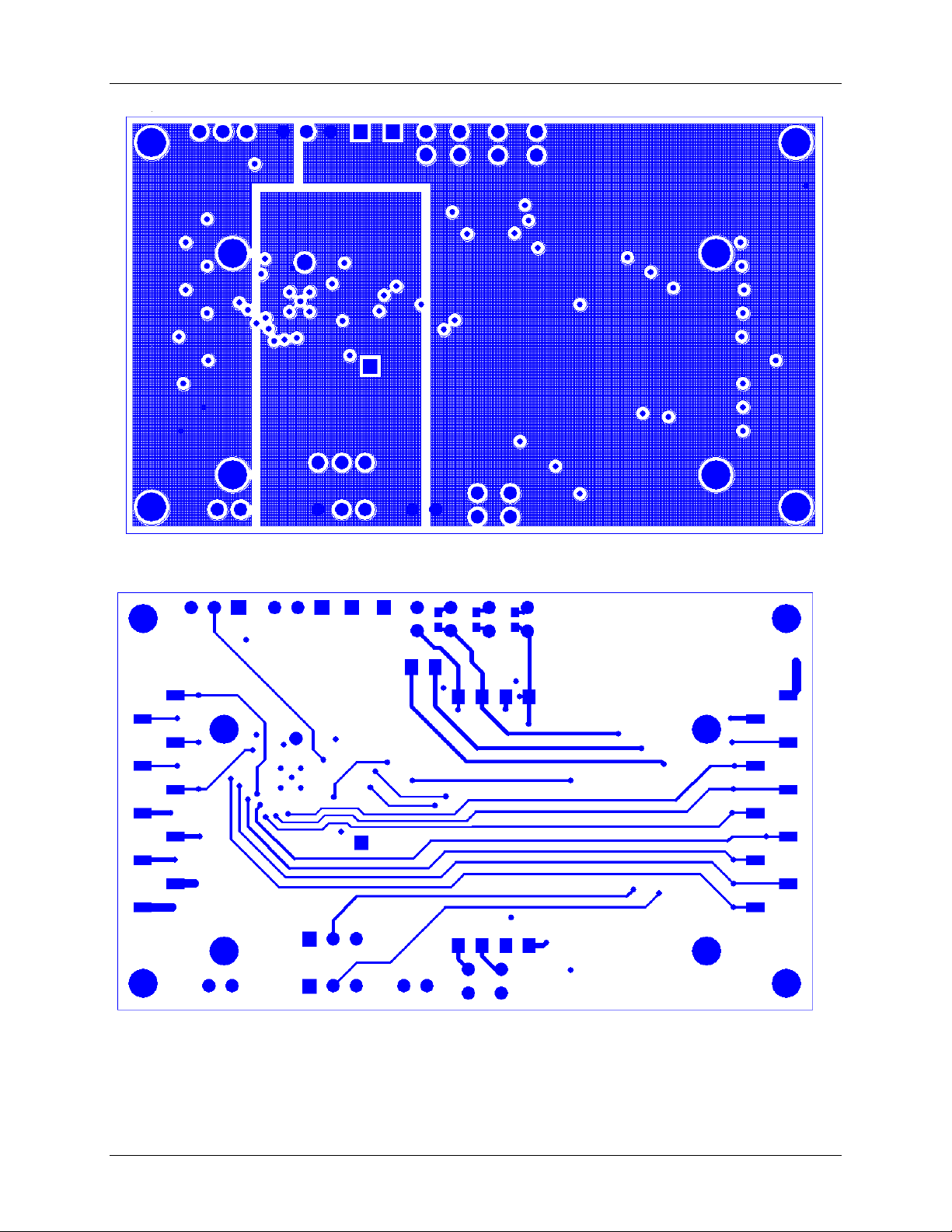

5.2 73S8009C PC B L a youts

Figure 5: 73S8009C Demo Board: Top View

Figure 6: 73S8009C Demo Boar d: Bottom View

Rev. 1.3 15

73S 8009C D emo Board User Man ual UM_8009C_059

Figure 7: 73S8009C Demo Boar d: Top Signal Layer

Figure 8: 73S8009C Demo Board: Middle Layer 1, Ground Plane

16 Rev. 1.3

UM_8009C_059 73S8009C Demo Board User Man ual

Figure 9: 73S8009C Demo Boar d: Middle Layer 2, Supply Plane

Figure 10: 73S8009C Demo Board: Bottom Signal Layer

Rev. 1.3 17

73S 8009C D emo Board User Man ual UM_8009C_059

TSM_110_01_L_SV

TSM_110_01_L_SV

5.3 73S80 09 C De mo Bo ar d B ill o f M aterials

Table 6: 73S8009C Demo Boa rd Bill of Materia ls

Qnt Reference Part PCB Footpri nt

1 C1

2 C2, C3

1 C4

2 C9, C12 27 pF 603 PCC270ACVCT-

1 C11

4 JP2, JP3,

JP5, JP6

2 JP4, JP7 Header 2 2pins, 2.54m m pit ch S1011E-36-ND PBC36SAAN Sullins

2 J1, J3 SSM_110_L_SV SSM_110_L_SV X SSM_110_L_SV Samtec

2 J2, J4 TSM_110_01_L_SV

1 J5 Smart C ar d Connector ITT_CCM02-2504 401-1715-ND CCM02-2504LFT ITTCannon

1 J6 SIM/ SAM Connector ITT_CCM03-3754 CCM03-3754CT-

1 L1 Inductor 445-1998-1-ND SLF7032T-

2 R7 0 603 P0.0GCT-ND ERJ-3GEY0R00V Panasonic

1 S1 Switch Panasonic EVQ P8051SCT EVQ-PJX05M Panasonic

8 TP 1, TP2,

TP3, TP4,

TP5, TP6,

TP7, TP8

1 U1 73S8009C 32QFN X 73S8009C Teridian

Note: The resistors noted Ru and Rd in the schematic are n ot populated on the board. They can be

imple mented t o adj ust the feat ures of t he smart card reader.

10 µF

0.1 µF

4.7 µF

0.47 µF

Header 3 3pins, 2.54m m pit ch S1011E-36-ND PBC36SAAN Sullins

TP 2X1_Header S1011E-36-ND PBC36SAAN Sullins

805 PCC2225CT-ND ECJ-2FB0J106M Panasonic

603 PCC1762CT-ND ECJ-1VB1C104K Panasonic

603 PCC2396CT-ND ECJ-1VB0J475K Panasonic

603 PCC2275CT-ND ECJ-1VB0J475K Panasonic

Digikey Part

Number

ND

X

ND

Part Number Manufacturer

ECJ-1VC1H270J Panasonic

Samtec

CCM03-3754 ITTCannon

TDK

100M1R4-2-PF

6 Errata

The 73S800 9C Demo Board contains a silk screen err or on JP 6. The VD D and GND are reversed and

have co r r ective decals attached to show t he proper labeling.

18 Rev. 1.3

UM_8009C_059 73S8009C Demo Board User Man ual

7 Ordering Information

Table 7 lists the order number used to id entify the 73S8009C Demo Board.

Table 7: 73S8009C Demo Boa rd Order Number

Part Description Order Number

73S8009C 32-Pin QFN Demo Board 73S8009C-DB

8 Related Documentation

The following 73S8009C docum ents are avai l able from Teridian Semi condu ctor Corporation:

73S8009C Data Sheet

73S8009C Demo Board User Manual

9 Contact Information

For m or e i nformation about Teridian Semiconductor products or t o check t he availability of the

73S8009C, contact us at:

644 0 Oak Canyon Road

Suite 100

Irvin e, CA 92618-5201

Telephone: (714) 508-8800

FAX: (714) 508-8878

Email: scr .support@teridian.com

For a complete list of worldwide sales offices, go to http://www.teridian.com.

Rev. 1.3 19

Loading...

Loading...