71M6543F/H

和 71M6543G/GH

电表 IC

数据资料

A Maxim Integrated Products Brand

MPU

RTC

TIMERS

IADC0

VADC8 (VA)

IADC2

VADC9 (VB)

XIN

XOUT

RX

TX

TX

RX

COM0...5

V3P3A V3P3SYS

VBAT

VBAT_RTC

IADC4

VADC10 (VC)

SEG

GNDA GNDD

SEG/DIO

DIO

ICE

C

B

A

NEUTRAL

LOAD

8888.8888

PULSES,

DIO

IR

AMR

POWER FAULT

COMPARATOR

MODUL-

ATOR

SERIAL PORTS

OSCILLATOR/

PLL

MUX and ADC

LCD DRIVER

DIO, PULSES

COMPUTE

ENGINE

FLASH

MEMORY

RAM

32 kHz

REGULATOR

Shunt Current Sensors

POWER SUPPLY

TERIDIAN

71M6543F/

71M6543H/

71M6543G/

71M6543GH

TEMPERATURE

SENSOR

VREF

IADC6

BATTERY

PWR MODE

CONTROL

WAKE-UP

NEUTRAL

I2C or µWire

EEPROM

9/17/2010

IADC1

IADC3

IADC5

IADC7

RTC

BATTERY

V3P3D

BATTERY

MONITOR

SPI INTERFACE

HOST

LCD DISPLAY

Resistor Dividers

Pulse Transformers

3x TERIDIAN

71M6xx3

Note: This system is referenced to Neutral

71M6xx3

71M6xx3

71M6xx3

}IN*

}IA

}IB

}IC

*IN = Neutral Current

19-5375; Rev 1.2; 4/11

2011 年 4 月

概述

71M6543F、71M6543H、71M6543G 和 71M6543GH 是 Teridian 的

第 4 代多相电表片上系统(SoC),包括:8051 兼容 MPU、带有数字

补偿的低功耗实时时钟(RTC)、闪存存储器和 LCD 驱动器。采用我们

的单转换器技术(Single Converter Technology®),内置一路 22 位 Σ-

Δ ADC 数字温度传感器、七路模拟输入、数字温度补偿、精密电压基

准和 32 位计算引擎(CE),只需少数外部元件即可支持各种电表设计。

71M6543F、71M6543H、71M6543G 和 71M6543GH 支持 71M6xx3

系列隔离传感器的接口选项,有效降低 BOM 成本、提高抗电磁干扰

能力,进而增强系统可靠性。器件特性包括:超低功耗有效工作和电池

供电模式、5KB 公用 RAM 和 64KB (71M6543F、71M6543H)或

128KB (71M6543G、71M6543GH)闪存存储器(电表工作期间可编程

程序和/或数据)。较强的处理能力、较高的采样速率,结合差分输入

级,提供强大的计量功能,理想用于 0.2 精度等级的商业电表和工业

电表设计(71M6543H、71M6543GH)。

完整的软件开发工具、演示程序以及参考设计有助于加速计量产品的

开发和认证,以满足 ANSI、IEC 等全球范围的电表计量标准。

Single Converter Technology是Maxim Integrated Products, Inc.

MICROWIRE是National Semiconductor Corp.

v1.2 © 2008–2011 Teridian Semiconductor Corporation 1

的商标。

的注册商标。

特性

• 2000:1 电流范围内,精度高达 0.1%

• 优于 IEC 62053/ANSI C12.20标准要求

• 带有零相电流测量的七路传感器输入,电流输

入可选择差分模式

• 一路电流输入可选择增益 1 或 8,支持分流器

• 高速 Wh/VARh脉冲输出,可编程脉冲宽度

• 64KB 闪存、5KB RAM (71M6543F/H)

• 128KB 闪存、5KB RAM (71M6543G/GH)

• 多达四路脉冲输出,带有脉冲计数

• 四象限表计,支持相排序

• 数字温度补偿:

计量补偿

高精度 RTC 用于晶振自动温度补偿的 TOU

功能,支持所有功率模式

• 独立的 32位计算引擎

• 46-64Hz 电网频率范围,采用相同校准

• 相位补偿(±7°)

• 三种备份电池供电模式:

掉电模式

LCD 模式

休眠模式

• 引脚事件唤醒和定时器唤醒

• 休眠模式电流损耗仅为 1μA

• 闪存加密

• 在系统编程

• 8 位 MPU (80515),高达 5 MIPS

• 掉电模式下的全速 MPU 时钟

• LCD 驱动器:

6 个公共段驱动器

多达 56 个可选引脚

• 多达 51个多功能 DIO 引脚

• 硬件看门狗定时器(WDT)

2

C/MICROWIRE™ EEPROM接口

• I

• 通过 SPI接口提供闪存编程

• 两个 UART 用于 IR和 AMR

• IR LED 调制驱动器

• 工业级温度范围

• 100 引脚无铅 LQFP 封装

71M6543F/H和 71M6543G/GH数据资料

目录

1 引言 ..................................................................................................................................................... 10

2

硬件说明 .............................................................................................................................................. 11

2.1

硬件概述 ..................................................................................................................................... 11

2.2

模拟前端(AFE) ........................................................................................................................... 12

2.2.1

信号输入引脚 ................................................................................................................. 13

2.2.2

输入复用器 ..................................................................................................................... 14

2.2.3

延时补偿 ......................................................................................................................... 19

2.2.4

ADC前置放大器 ............................................................................................................. 20

2.2.5

A/D转换器(ADC) ............................................................................................................ 20

2.2.6

FIR滤波器 ...................................................................................................................... 20

2.2.7

电压基准 ......................................................................................................................... 20

2.2.8

71M6xx3隔离传感器接口 .............................................................................................. 22

2.3

数字计算引擎(CE) ...................................................................................................................... 25

2.3.1

CE程序存储器 ................................................................................................................ 25

2.3.2

CE数据存储器 ................................................................................................................ 25

2.3.3

CE与MPU通信 ............................................................................................................... 25

2.3.4

电表公式 ......................................................................................................................... 26

2.3.5

实时监测器(RTM) ........................................................................................................... 26

2.3.6

脉冲发生器 ..................................................................................................................... 26

2.3.7

CE功能综述 .................................................................................................................... 28

2.4

80515 MPU核 ............................................................................................................................ 30

2.4.1

存储器架构和寻址 .......................................................................................................... 30

2.4.2

特殊功能寄存器(SFR) .................................................................................................... 32

2.4.3

通用 80515 特殊功能寄存器 ........................................................................................... 33

2.4.4

指令集 ............................................................................................................................ 35

2.4.5

80515 低功耗模式 .......................................................................................................... 35

2.4.6

UART ............................................................................................................................. 36

2.4.7

定时器和计数器 .............................................................................................................. 38

2.4.8

WD定时器(软件看门狗定时器) ....................................................................................... 40

2.4.9

中断 ................................................................................................................................ 40

2.5

片上资源 ..................................................................................................................................... 47

2.5.1

物理存储器 ..................................................................................................................... 47

2.5.2

振荡器 ............................................................................................................................ 49

2.5.3

PLL和内部时钟 ............................................................................................................... 50

2.5.4

实时时钟(RTC) ............................................................................................................... 51

2.5.5

71M6543温度传感器 ..................................................................................................... 55

2.5.6

71M6xx3温度传感器 ..................................................................................................... 56

2.5.7

71M6543电池监测器 ..................................................................................................... 57

2.5.8 71M6xx3 VCC检测器 ..................................................................................................... 57

2.5.9

UART和光接口 ............................................................................................................... 57

2.5.10

数字I/O和LCD段驱动器 .................................................................................................. 58

2.5.11

EEPROM接口 ................................................................................................................ 66

2.5.12

SPI从机端口 ................................................................................................................... 68

2.5.13

硬件看门狗定时器 .......................................................................................................... 72

2.5.14

测试端口(TMUXOUT和TMUX2OUT引脚) ..................................................................... 73

3

功能说明 .............................................................................................................................................. 75

2 © 2008–2011 Teridian Semiconductor Corporation v1.2

71M6543F/H和 71M6543G/GH 数据资料

3.1 工作原理 ..................................................................................................................................... 75

3.2

电池供电模式 ............................................................................................................................. 75

3.2.1

BRN模式 ........................................................................................................................ 78

3.2.2

LCD模式 ......................................................................................................................... 78

3.2.3

SLP模式 ......................................................................................................................... 79

3.3

故障和复位操作 .......................................................................................................................... 80

3.3.1

掉电事件 ......................................................................................................................... 80

3.3.2

低电池电压下的IC .......................................................................................................... 81

3.3.3

复位序列 ......................................................................................................................... 81

3.3.4

看门狗定时器(WDT)复位 ............................................................................................... 81

3.4

唤醒操作 ..................................................................................................................................... 82

3.4.1

硬件唤醒 ......................................................................................................................... 82

3.4.2

定时器唤醒 ..................................................................................................................... 84

3.5

数据流和MPU/CE通信 ............................................................................................................... 84

4

应用信息 .............................................................................................................................................. 86

4.1

连接 5V器件 ............................................................................................................................... 86

4.2

直接连接传感器 .......................................................................................................................... 86

4.3

使用 71M6xx3 隔离传感器和分流器的系统架构 ......................................................................... 87

4.4

使用电流变压器的系统 架构 ....................................................................................................... 88

4.5

计量温度补偿 ............................................................................................................................. 89

4.5.1

标准和高精度器件的区别 ............................................................................................... 89

4.5.2

71M6543F和 71M6543G温度系数 ................................................................................. 90

4.5.3

71M6543H和 71M6543GH的温度系数 .......................................................................... 90

4.5.4

71M6xx3的温度系数 ..................................................................................................... 90

4.5.5

VREF和分流传感器的温度补偿 ...................................................................................... 90

4.5.6

VREF和电流变压器的温度补偿 ...................................................................................... 92

4.6

连接I

4.7

连接 3 线EEPROM ..................................................................................................................... 94

4.8

UART0 (TX/RX) ......................................................................................................................... 94

4.9

光接口(UART1) .......................................................................................................................... 94

4.10

4.11

4.12

4.13

4.14

4.15

5

固件接口 .............................................................................................................................................. 98

5.1

I/O RAM映射—按功能排序 ........................................................................................................ 98

5.2

I/O RAM映射—按字母排序 ...................................................................................................... 104

5.3

读信息页(71M6543H和 71M6543GH) ..................................................................................... 118

5.4

CE接口说明 .............................................................................................................................. 120

2

C EEPROM ...................................................................................................................... 94

连接复位引脚 ............................................................................................................................. 95

连接仿真器端口 .......................................................................................................................... 96

闪存编程 ..................................................................................................................................... 96

4.12.1

通过ICE端口编程闪存 .................................................................................................... 96

4.12.2

通过SPI端口编程闪存 .................................................................................................... 96

MPU演示程序 ............................................................................................................................. 96

晶振 ............................................................................................................................................ 97

电表校准 ..................................................................................................................................... 97

5.4.1

CE程序 ......................................................................................................................... 120

5.4.2

CE数据格式 .................................................................................................................. 120

5.4.3

常量 .............................................................................................................................. 120

5.4.4

环境 .............................................................................................................................. 121

5.4.5

CE计算 ......................................................................................................................... 121

v1.2 © 2008–2011 Teridian Semiconductor Corporation 3

71M6543F/H和 71M6543G/GH数据资料

5.4.6 CE前端数据(原始数据) ................................................................................................. 122

5.4.7

CE状态和控制 .............................................................................................................. 123

5.4.8

CE传输变量 .................................................................................................................. 125

5.4.9

脉冲发生 ....................................................................................................................... 127

5.4.10

CE校准参数 .................................................................................................................. 130

5.4.11

CE流程图 ..................................................................................................................... 131

6

71M6543 电气规格 ............................................................................................................................ 133

6.1

绝对最大额定值 ........................................................................................................................ 133

6.2

推荐外部元件 ........................................................................................................................... 134

6.3

推荐工作条件 ........................................................................................................................... 134

6.4

性能指标 ................................................................................................................................... 135

6.4.1

输入逻辑电平 ............................................................................................................... 135

6.4.2

输出逻辑电平 ............................................................................................................... 135

6.4.3

电池监测器 ................................................................................................................... 136

6.4.4

温度监测器 ................................................................................................................... 137

6.4.5

电源电流 ....................................................................................................................... 138

6.4.6

V3P3D开关 .................................................................................................................. 139

6.4.7

内部电源故障比较器 .................................................................................................... 139

6.4.8

2.5 V稳压器—系统电源 ................................................................................................ 139

6.4.9

2.5 V稳压器—电池供电 ................................................................................................ 140

6.4.10

晶振 .............................................................................................................................. 140

6.4.11

锁相环(PLL) ................................................................................................................. 140

6.4.12

LCD 驱动器 .................................................................................................................. 140

6.4.13

VLCD发生器 ................................................................................................................. 141

6.4.14

71M6543 VREF ........................................................................................................... 143

6.4.15 ADC转换器 ................................................................................................................... 144

6.4.16

IADC0-IADC1 的前置放大器 ........................................................................................ 145

6.5

时序规格 ................................................................................................................................... 146

6.5.1

闪存 .............................................................................................................................. 146

6.5.2

SPI从机 ........................................................................................................................ 146

6.5.3

EEPROM接口 .............................................................................................................. 146

6.5.4

RESET引脚 .................................................................................................................. 147

6.5.5

实时时钟(RTC) ............................................................................................................. 147

6.6

100 引脚LQFP封装图 ............................................................................................................... 148

6.7

71M6543引脚图 ...................................................................................................................... 149

6.8

71M6543引脚说明 ................................................................................................................... 150

6.8.1

71M6543电源和接地引脚 ............................................................................................ 150

6.8.2

71M6543模拟电路引脚 ............................................................................................... 151

6.8.3

71M6543数字电路引脚 ............................................................................................... 152

6.8.4

I/O等效电路 .................................................................................................................. 154

7

定购信息 ............................................................................................................................................ 155

7.1

71M6543选型指南 ................................................................................................................... 155

8

相关信息 ............................................................................................................................................ 155

9

联络信息 ............................................................................................................................................ 155

附录A:缩写符号 ...................................................................................................................................... 156

附录B:修订历史 ...................................................................................................................................... 157

4 © 2008–2011 Teridian Semiconductor Corporation v1.2

71M6543F/H 和 71M6543G/GH数据资料

图

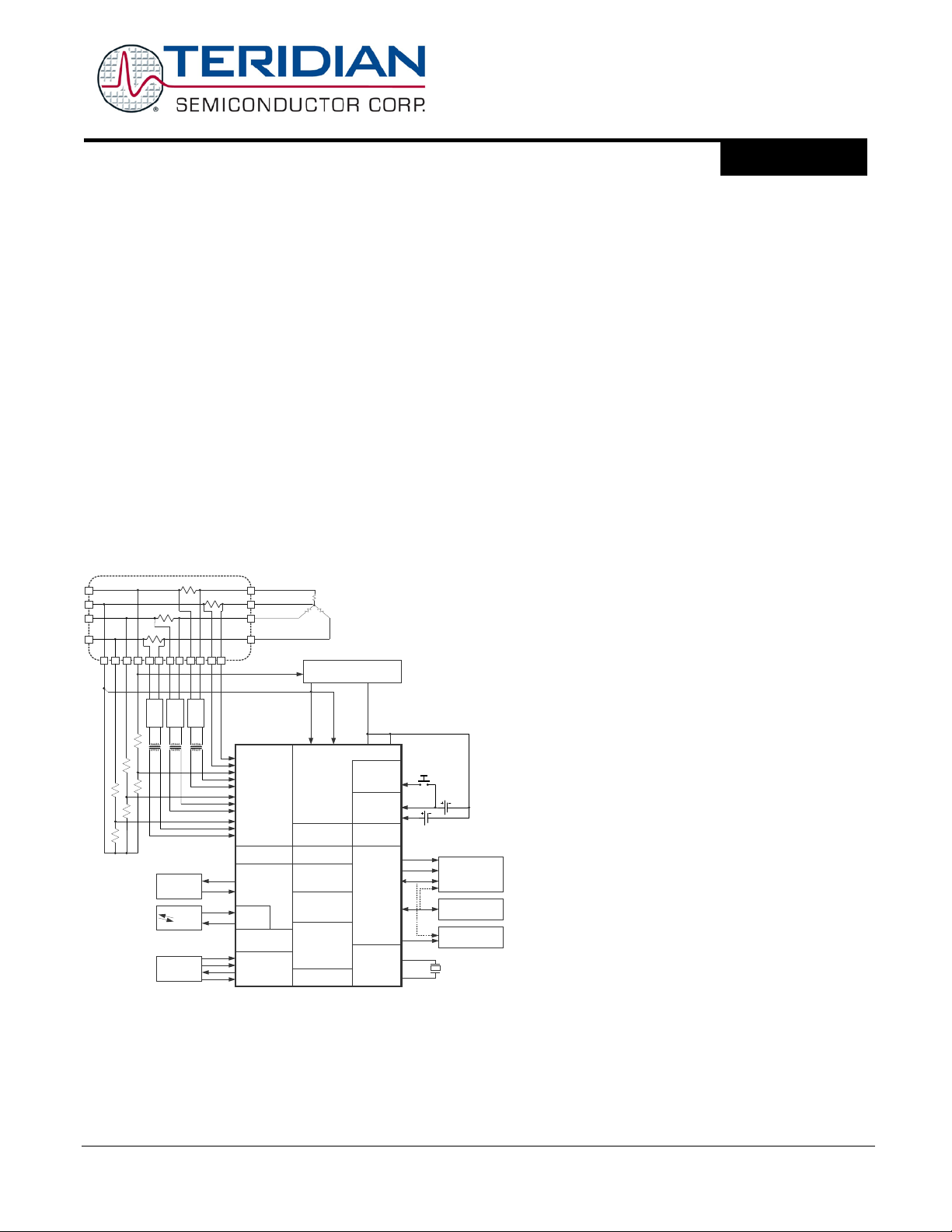

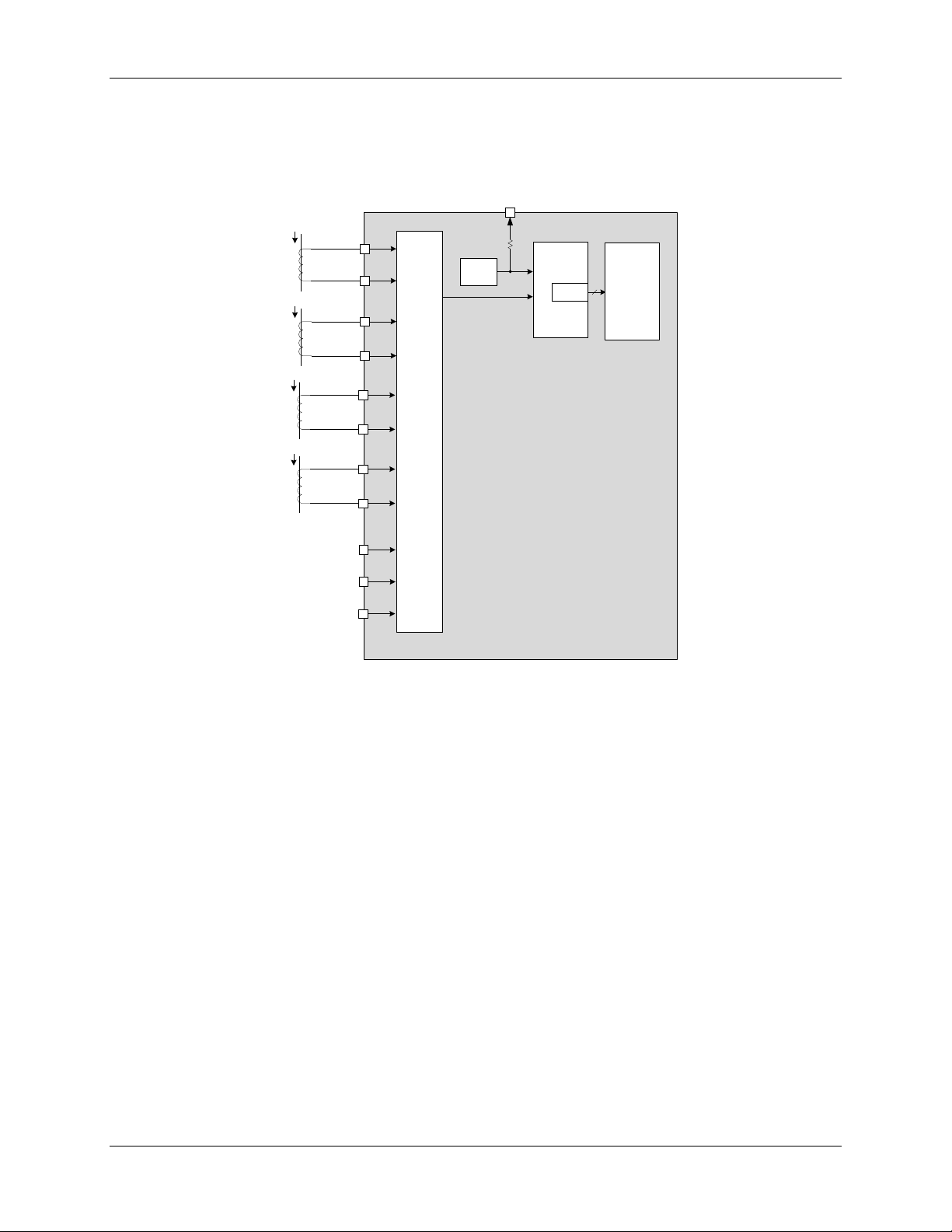

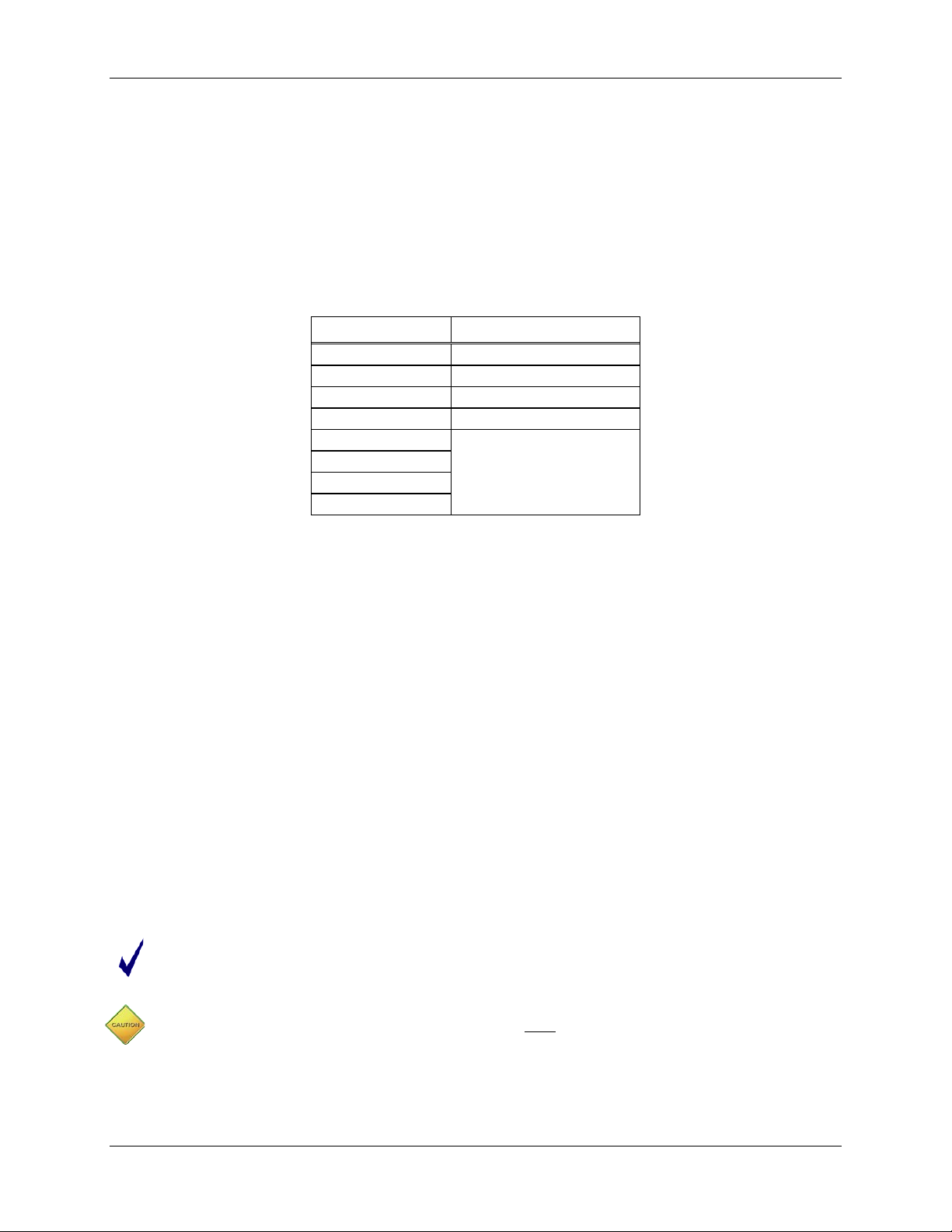

图 1. IC功能框图 ............................................................................................................................................ 9

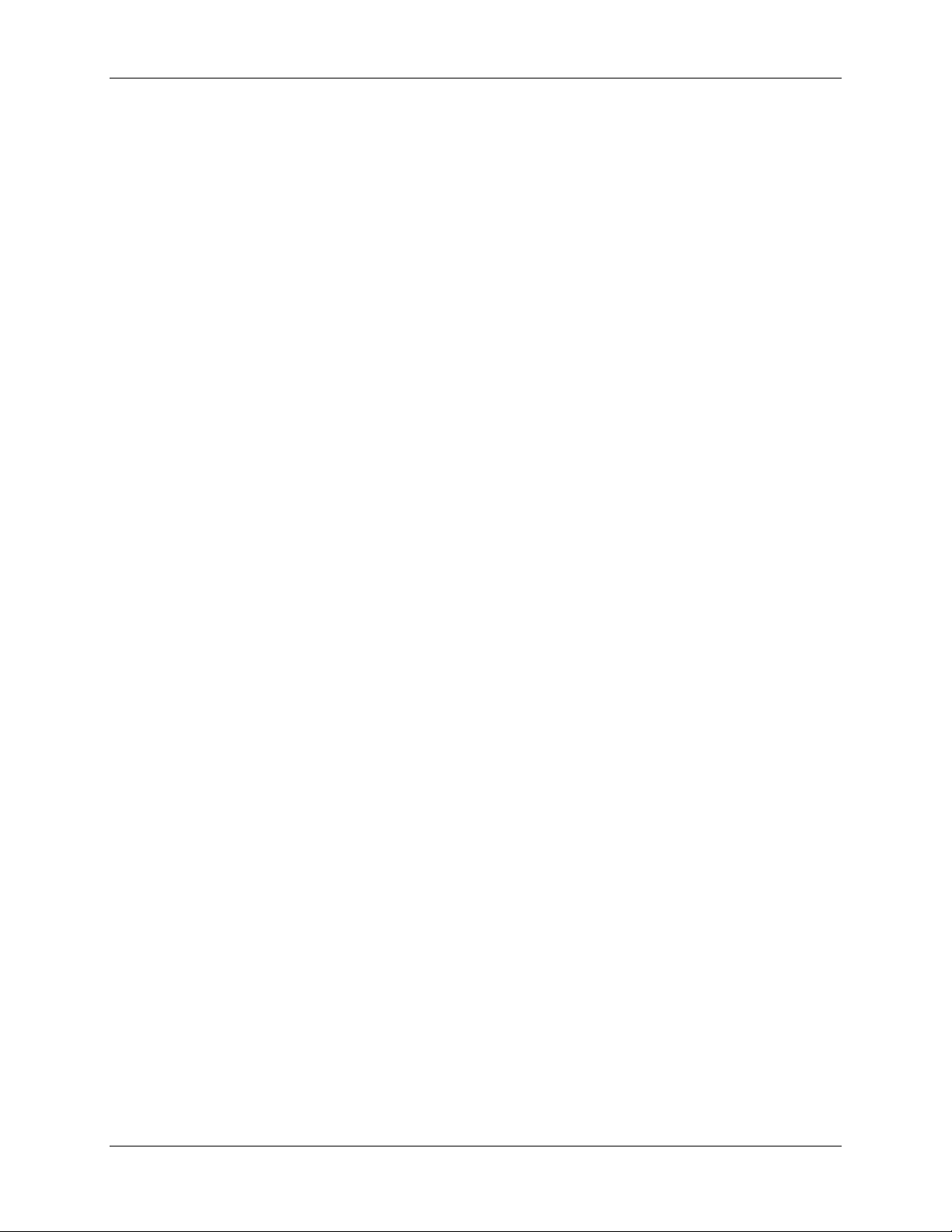

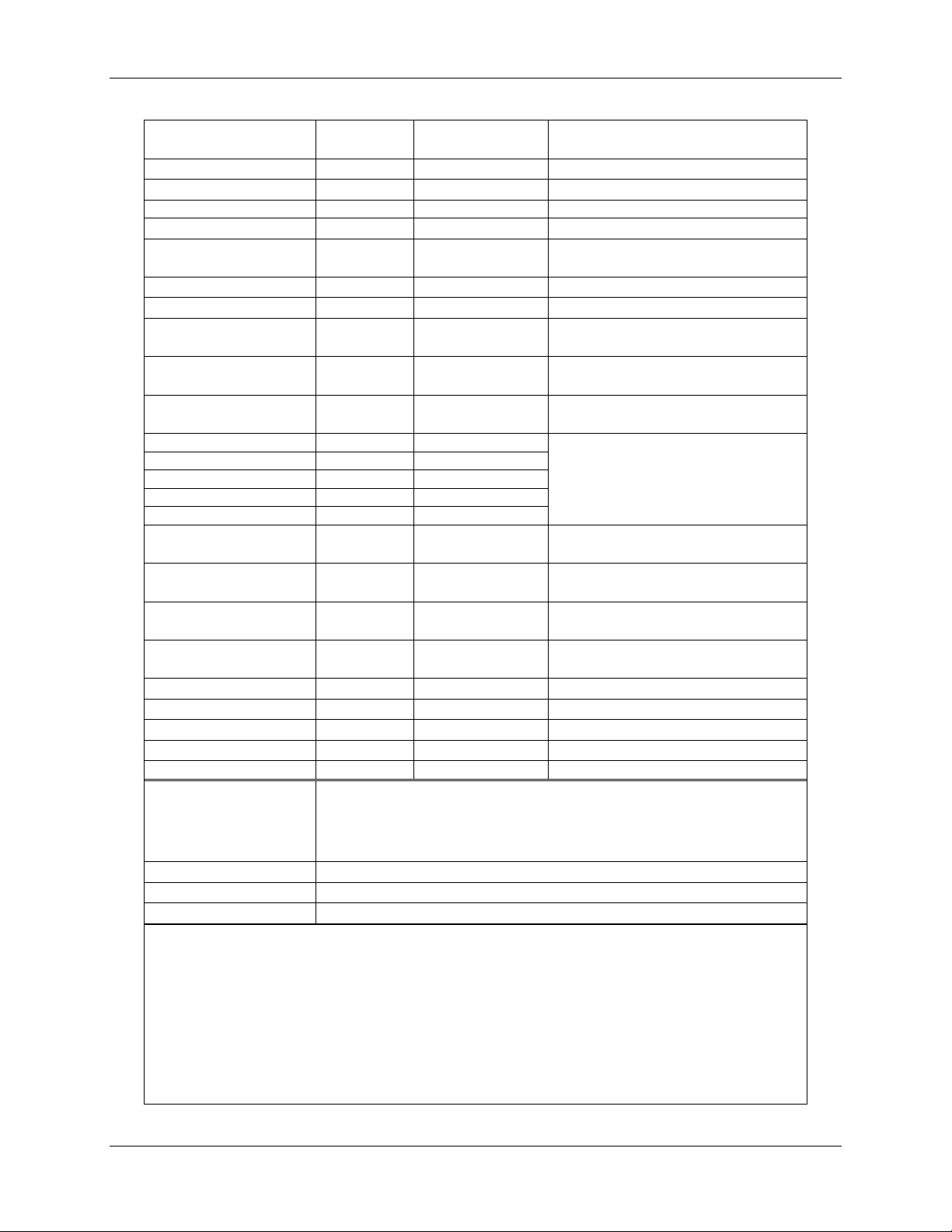

图 2. AFE 方框图(分流器:一个本地传感器、三个远端传感器)……………………………………………… 12

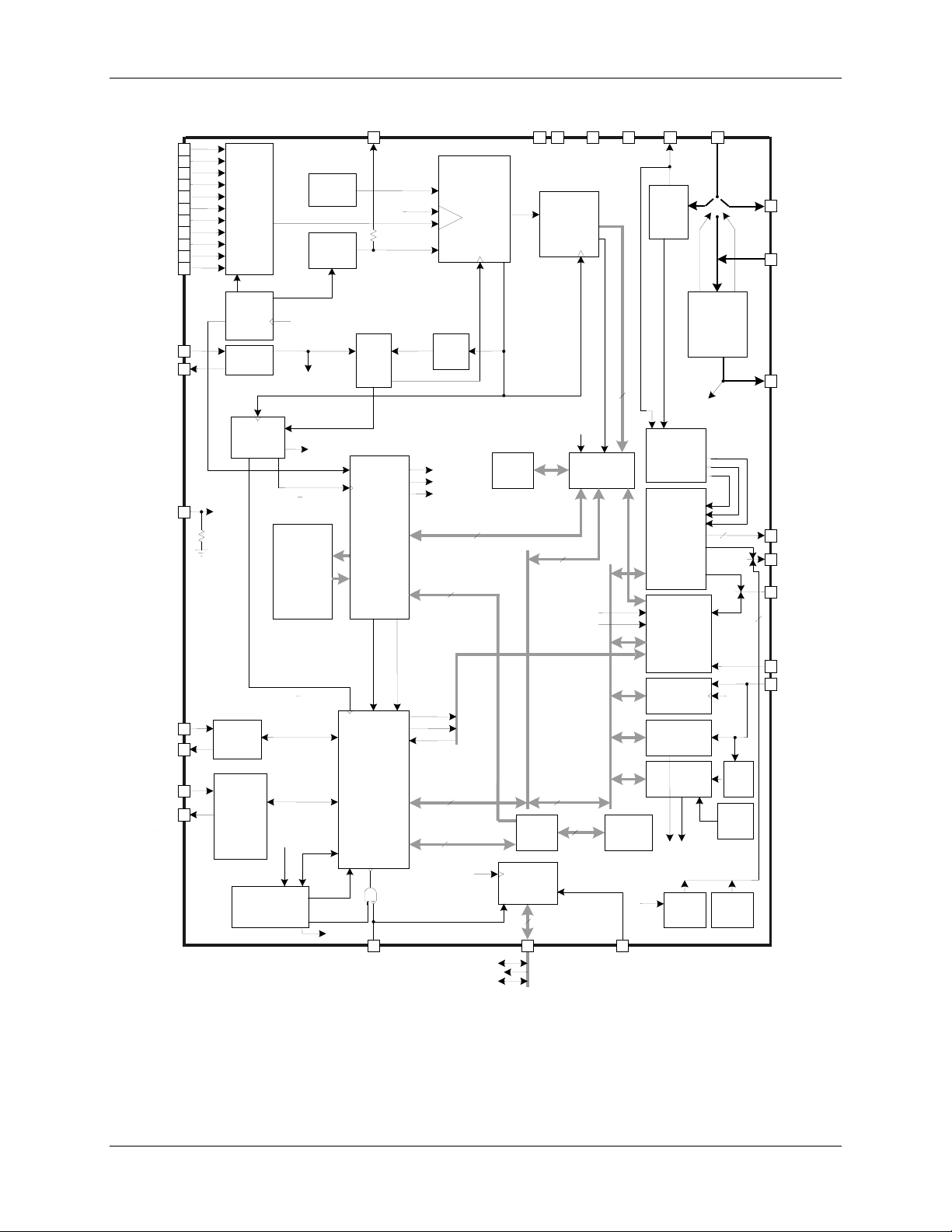

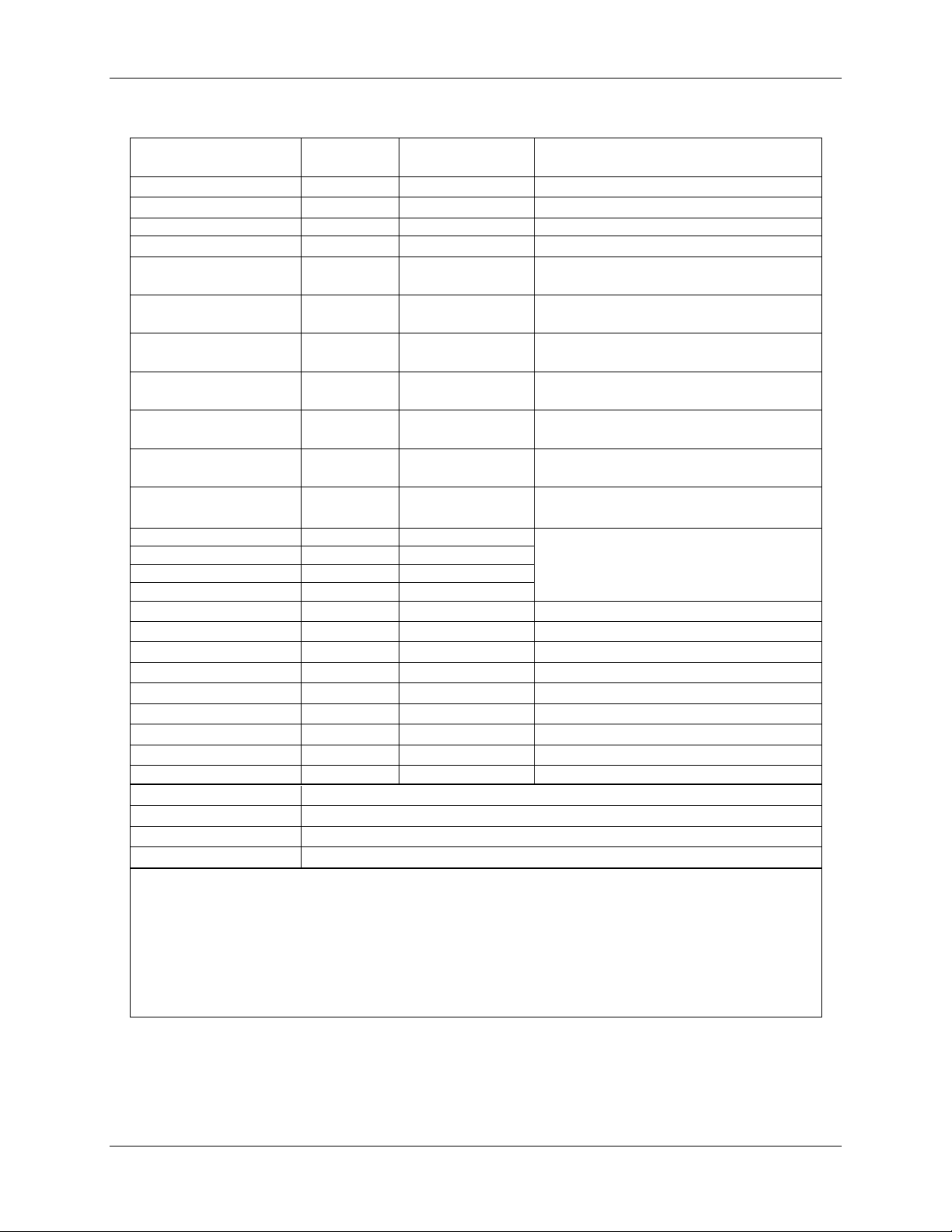

图 3. AFE 原理框图 (四个 CT)……………………………………………………………………………………. 13

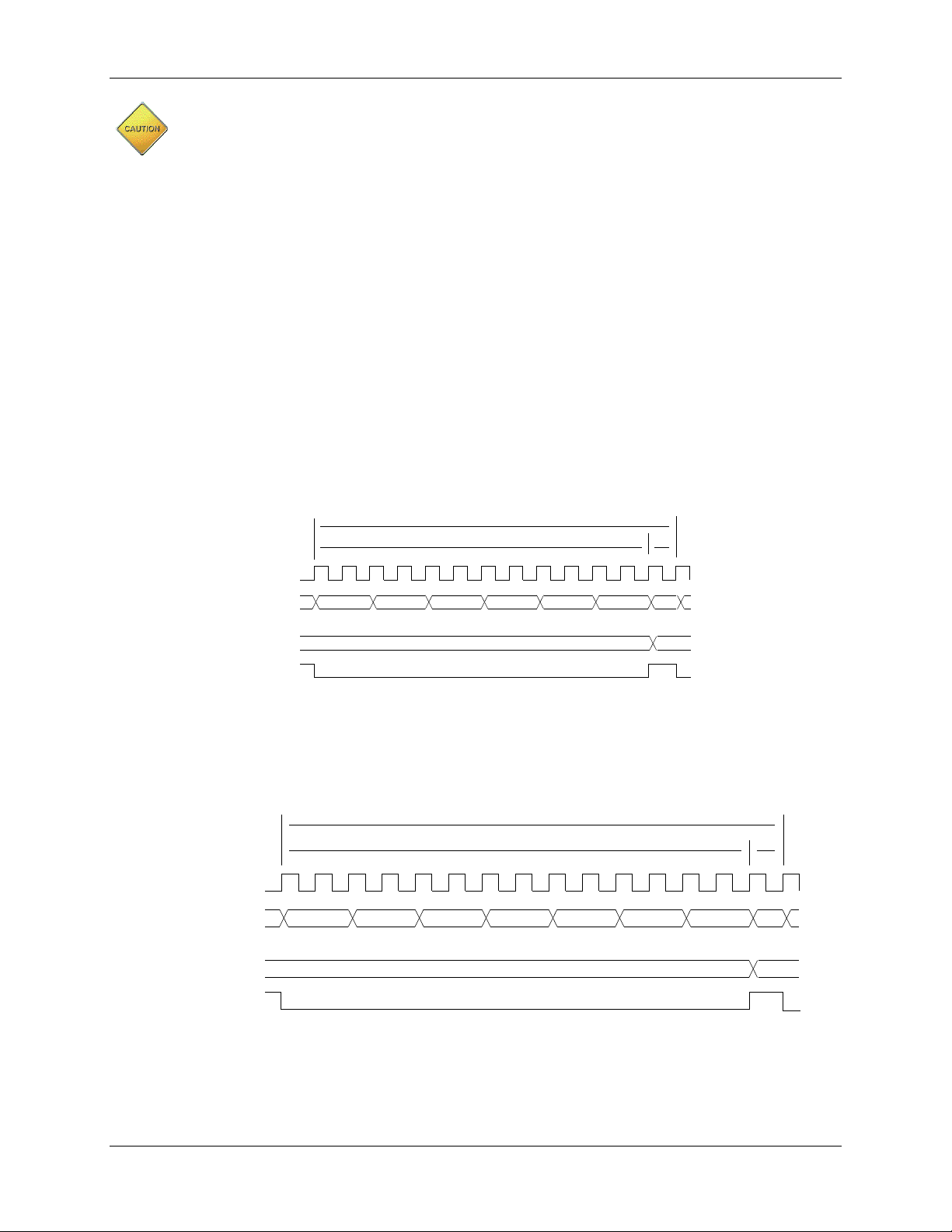

图 4. 复用帧状态(MUX_DIV[3:0] = 6)

图 5. 复用帧状态(MUX_DIV[3:0] = 7) .......................................................................................................... 17

图 6. 斩波放大器通用拓扑………………………………………………………………………………………… 21

图 7. CROSS信号, CHOP_E = 00

图 8. RTM时序

图 9. 脉冲发生器FIFO时序

图 10. 复用周期内采样(帧)

图 11. 累积间隔

图 12. 中断结构

图 13. 自动温度补偿

图 14. 光接口

图 15. 光接口(UART1)

图 16. 连接外部负载至DIO引脚

图 17. LCD波形

图 18. 3 线接口:写命令,HiZ=0

图 19. 3 线接口:写命令,HiZ=1

图 20. 3 线接口:读命令

图 21. 3 线接口:写命令,CNT=0

图 22. 3 线接口:写命令,HiZ=1,WFR=1 ................................................................................................ 68

图 23. SPI从机端口—典型的多字节读、写操作

图 24. 电压、电流、瞬时能量和累积能量

图 25. 工作模式状态图

图 26. MPU/CE数据流

图 27. 电阻分压(电压检测)

图 28. 单端输入CT (电流检测)

图 29. 差分输入CT (电流检测)

图 30. 差分输入锰铜分流器(电流检测)

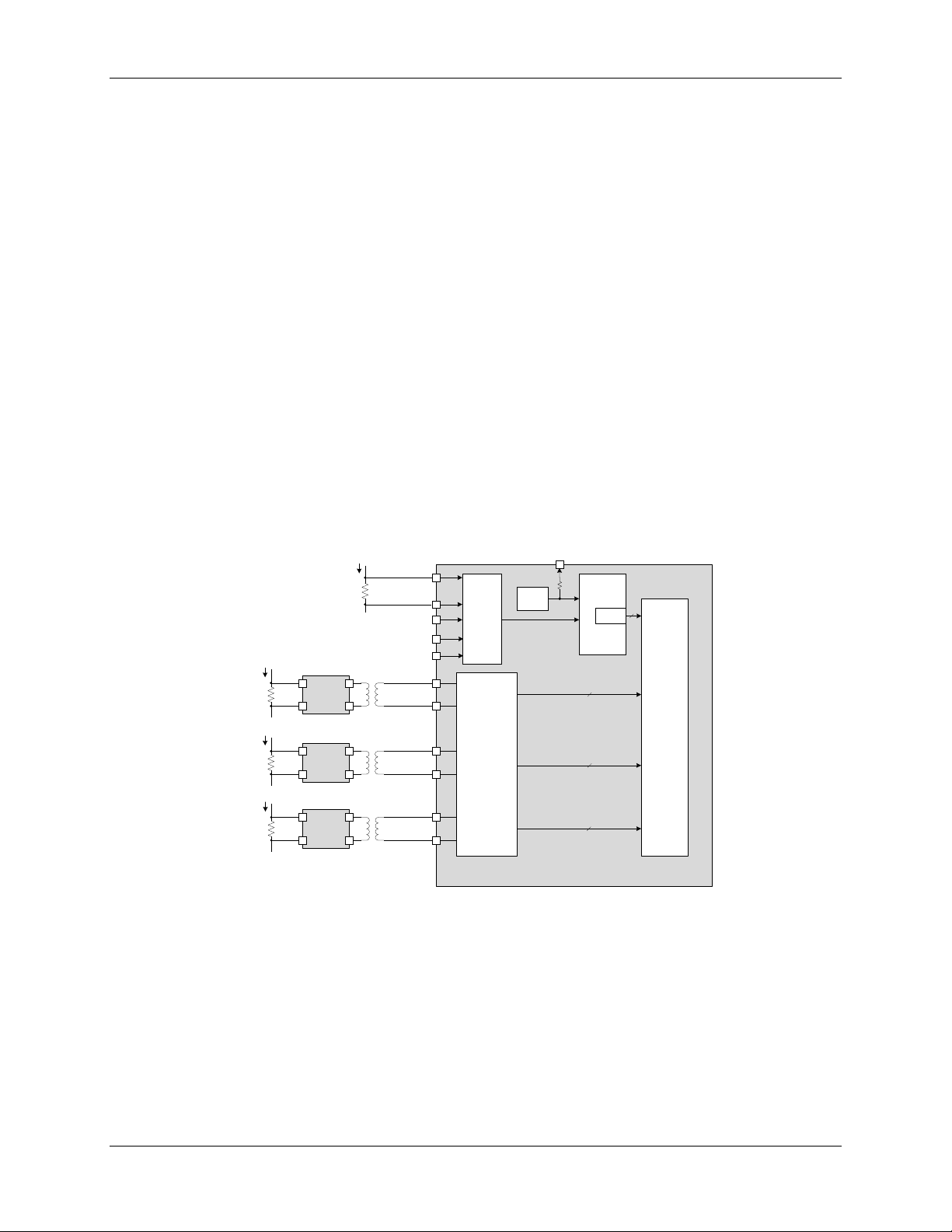

图 31. 使用三个远端和一个本地(零相)传感器的系统架构

图 32. 使用电流变压器的系统

图 33. I

图 34. UART0 连接

图 35. 光元件连接

图 36. RESET引脚外部电路:按钮(左侧)、生产电路(右侧)

图 37. 仿真器接口的外部电路

图 38. 熔丝位映射

图 39. CE数据流:复用器和ADC

图 40. CE数据流:单相的缩放、增益控制、中间变量

图 41. CE数据流:平方、求和运算级

图 42. 100 引脚LQFP封装图

图 43. LQFP-100 封装引脚排列

图 44. I/O等效电路

v1.2 © 2008–2011 Teridian Semiconductor Corporation 5

2

C EEPROM连接 ............................................................................................................................. 94

.......................................................................................................... 17

............................................................................................................. 21

............................................................................................................................................. 26

.......................................................................................................................... 28

.......................................................................................................................... 29

........................................................................................................................................... 29

........................................................................................................................................... 46

.................................................................................................................................... 54

............................................................................................................................................... 58

................................................................................................................................. 58

................................................................................................................... 60

........................................................................................................................................... 65

................................................................................................................ 67

................................................................................................................ 68

.............................................................................................................................. 68

.............................................................................................................. 68

.......................................................................................... 70

.................................................................................................... 75

................................................................................................................................ 76

................................................................................................................................. 85

.......................................................................................................................... 86

..................................................................................................................... 86

..................................................................................................................... 86

........................................................................................................ 86

........................................................................... 87

...................................................................................................................... 88

...................................................................................................................................... 94

........................................................................................................................................ 95

....................................................................... 96

...................................................................................................................... 96

...................................................................................................................................... 118

.............................................................................................................. 131

.............................................................................. 131

....................................................................................................... 132

..................................................................................................................... 148

................................................................................................................. 149

..................................................................................................................................... 154

71M6543F/H和 71M6543G/GH数据资料

表

表 1. CE代码和设置(1 个本地/3 个远端传感器) .......................................................................................... 15

表 2. CE 代码和设置(CT 传感器)………………………………………………………………………………… 16

表 3. 复用器和 ADC 配置位………………………………………………………………………………………. 19

表 4. RCMD[4:0] 位 ..................................................................................................................................... 23

表 5. 远程接口读命令……………………………………………………………………………………………… 23

表 6. 用于远端传感器的I/O RAM控制位 ...................................................................................................... 24

表 7. 复用器输入选择……………………………………………………………………………………………… 26

表 8. CKMPU时钟频率

表 9. 存储器映射

表 10. 内部数据存储器映射

表 11. 特殊功能寄存器映射

表 12. 通用 80515 SFR—地址和复位值

表 13. PSW位功能(SFR 0xD0)

表 14. 端口寄存器(SEGDIO0-15)

表 15. 展宽存储周期宽度

表 16. 80515 PCON SFR寄存器(SFR 0x87)

表 17. 波特率发生器

表 18. UART模式

表 19. S0CON (UART0)寄存器(SFR 0x98)

表 20. S1CON (UART1)寄存器(SFR 0x9B)

表 21. PCON寄存器位说明(SFR 0x87)

表 22. 定时器/计数器模式说明 ..................................................................................................................... 39

表 23. 定时器/计数器模式组合

表 24. TMOD寄存器位说明(SFR 0x89)

表 25. TCON寄存器位功能(SFR 0x88)

表 26. IEN0 位功能(SFR 0xA8)

表 27. IEN1 位功能(SFR 0xB8)

表 28. IEN2 位功能(SFR 0x9A)

表 29. TCON位功能(SFR 0x88)

表 30. T2CON位功能(SFR 0xC8)

表 31. IRCON位功能(SFR 0xC0)

表 32. 外部MPU中断

表 33. 中断使能和标识位

表 34. 中断优先级组

表 35. 中断优先级

表 36. 中断优先级寄存器(IP0 和IP1)

表 37. 中断轮询排序

表 38. 中断向量

表 39. 闪存访问

表 40. 71M6543G/GH中利用FL_BANK[1:0] (SFR 0xB6[1:0])进行存储区切换

表 41. 闪存加密

表 42. 时钟系统汇总

表 43. RTC控制寄存器

表 44. 用于RTC温度补偿的I/O RAM寄存器

6 © 2008–2011 Teridian Semiconductor Corporation v1.2

................................................................................................................................ 30

.......................................................................................................................................... 31

......................................................................................................................... 32

......................................................................................................................... 32

...................................................................................................... 33

..................................................................................................................... 34

................................................................................................................ 35

............................................................................................................................. 35

................................................................................................. 36

.................................................................................................................................... 36

......................................................................................................................................... 37

.................................................................................................. 37

.................................................................................................. 38

......................................................................................................... 38

..................................................................................................................... 39

....................................................................................................... 39

........................................................................................................ 40

.................................................................................................................... 41

.................................................................................................................... 41

.................................................................................................................... 41

................................................................................................................... 41

................................................................................................................. 42

................................................................................................................. 42

................................................................................................................................... 42

............................................................................................................................. 43

.................................................................................................................................... 43

........................................................................................................................................ 44

............................................................................................................ 44

.................................................................................................................................... 45

........................................................................................................................................... 45

........................................................................................................................................... 47

............................................. 48

........................................................................................................................................... 49

.................................................................................................................................... 51

................................................................................................................................ 52

................................................................................................ 53

71M6543F/H 和 71M6543G/GH数据资料

表 45. 用于RTC中断的I/O RAM寄存器 ........................................................................................................ 55

表 46. 用于温度和电池测量的I/O RAM寄存器

表 47. 通过DIO_Rn[2:0]位的能够选择的资源

表 48. SEGDIO0 至SEGDIO15 数据/方向寄存器及内部资源

表 49. SEGDIO16 至SEGDIO31 数据/方向寄存器

表 50. SEGDIO32 至SEGDIO45 数据/方向寄存器

表 51. SEGDIO51 至SEGDIO55 数据/方向寄存器

表 52. LCD_VMODE配置

表 53. LCD配置

表 54. SEGDIO46 至SEGDIO55 LCD数据寄存器

表 55. 2 线接口对应的EECTRL位

表 56. 3 线接口对应的EECTRL 位

表 57. SPI操作字段

表 58. SPI命令时序

表 59. SPI 寄存器

表 60. TMUX[4:0]选择

表 61. TMUX2[4:0] 选择

表 62. 电路功能

表 63. VSTAT[2:0] (SFR 0xF9[2:0])

表 64. 唤醒使能和标识位 ............................................................................................................................. 82

表 65. 唤醒位

表 66. WAKE标识清除事件

表 67. GAIN_ADJn补偿通道(图 2、图 31、表 1)

表 68. GAIN_ADJx补偿通道(图 3、图 32、表 2)

表 69. I/O RAM映射—按功能排序,基本配置

表 70. I/O RAM映射—按功能排序

表 71. I/O RAM映射—按字母排序

表 72. 信息页熔丝调整

表 73. CE EQU[2:0]公式和单元输入映射

表 74. CE原始数据访问地址

表 75. CESTATUS 寄存器

表 76. CESTATUS位定义

表 77. CECONFIG寄存器

表 78. CECONFIG位定义(CE RAM 0x20)

表 79. 电压跌落门限、相测量和增益调节控制

表 80. CE传递变量(含分流器)

表 81. CE传递变量(CT)

表 82. CE能量测量变量(含分流器)

表 83. CE能量测量变量(CT)

表 84. 其它传递变量

表 85. CE脉冲参数

表 86. 用于噪声抑制和代码版本的CE参数

表 87. CE校准参数

表 88. 绝对最大额定值

表 89. 推荐外部元件

............................................................................................. 56

.............................................................................................. 59

...................................................................... 60

...................................................................................... 61

...................................................................................... 61

...................................................................................... 61

............................................................................................................................. 63

........................................................................................................................................... 64

....................................................................................... 65

................................................................................................................. 66

................................................................................................................ 67

...................................................................................................................................... 69

...................................................................................................................................... 70

........................................................................................................................................ 70

................................................................................................................................. 73

.............................................................................................................................. 74

........................................................................................................................................... 77

............................................................................................................. 80

............................................................................................................................................... 83

......................................................................................................................... 84

........................................................................................ 91

......................................................................................... 93

............................................................................................. 98

............................................................................................................. 100

............................................................................................................. 104

.............................................................................................................................. 118

.................................................................................................. 121

...................................................................................................................... 122

........................................................................................................................... 123

............................................................................................................................ 123

........................................................................................................................... 123

.................................................................................................. 124

.......................................................................................... 125

................................................................................................................... 125

............................................................................................................................. 126

............................................................................................................ 126

...................................................................................................................... 126

.................................................................................................................................. 127

.................................................................................................................................... 128

................................................................................................ 129

.................................................................................................................................... 130

.............................................................................................................................. 133

.................................................................................................................................. 134

v1.2 © 2008–2011 Teridian Semiconductor Corporation 7

71M6543F/H和 71M6543G/GH数据资料

表 90. 推荐工作条件 .................................................................................................................................. 134

表 91. 输入逻辑电平

表 92. 输出逻辑电平

表 93. 电池监测器技术指标(TEMP_BAT = 1)

表 94. 温度监测器

表 95. 电源电流指标

表 96. V3P3D开关性能指标

表 97. 内部电源故障比较器性能指标

表 98. 2.5V稳压器性能指标

表 99. 低功耗稳压器性能指标

表 100. 晶振性能指标

表 101. PLL性能指标

表 102. LCD驱动器性能指标

表 103. VLCD发生器技术指标

表 104. 71M6543 VREF性能指标

表 105. ADC转换器性能指标

表 106. 前置放大器性能指标

表 107. 闪存时序指标

表 108. SPI从机时序指标

表 109. EEPROM接口时序

表 110. RESET引脚时序

表 111. RTC的日期范围

表 112. 71M6543 电源和接地引脚

表 113. 71M6543 模拟电路引脚

表 114. 71M6543 数字电路引脚

表 115. 71M6543 选型指南

.................................................................................................................................. 135

.................................................................................................................................. 135

............................................................................................. 136

...................................................................................................................................... 137

.................................................................................................................................. 138

....................................................................................................................... 139

......................................................................................................... 139

....................................................................................................................... 139

.................................................................................................................... 140

................................................................................................................................ 140

................................................................................................................................. 140

..................................................................................................................... 140

................................................................................................................... 141

.............................................................................................................. 143

..................................................................................................................... 144

..................................................................................................................... 145

................................................................................................................................ 146

.......................................................................................................................... 146

........................................................................................................................ 146

........................................................................................................................... 147

............................................................................................................................ 147

............................................................................................................. 150

................................................................................................................ 151

................................................................................................................ 152

....................................................................................................................... 155

8 © 2008–2011 Teridian Semiconductor Corporation v1.2

71M6543F/H 和 71M6543G/GH数据资料

IADC

0

XOUT

CKADC

32 - bit Compute

Engine

OPT _ TX / SEGDIO

51 / WPULSE

/

VPULSE

RESET

VBIAS

EMULATOR

PORT

C

E _ B

S

OPTICAL

TX

X

F

E

U

S

6

COM 0 ..

5

CEDATA

PROG

0 x 000

... 0 x 3 FF

DATA

0 x 0000

... 0 xFFFF

0 x 00000

…

CONFIGURATION

RAM ( I / O RAM

)

0 x 2000

... 0 x

20

FF

I

O

R

A

M

RTCLK

(

32

KHz

)

CKMPU

CK

32

8

8

8

POWER FAULT

4 . 9

MHZ

4 .

9

V 3 P 3 A V 3 P 3 D

VBAT

Voltage

Regulator

VDD

32

KHz

MPU _ RSTZ

CON - FIGURATION

VBIAS

Oscillator

32

KHz

CK

32

MCK

DIV

ADC

VARPULSE

WPULSE

TEST

TEST

MODE

VLC

0

CKMPU

_ 2 x

CKMPU

_ 2 x

SDCK

E _ TCLK / SEG

49

E _ RST / SEG

50

FLASH

V 3 P 3 A

EEPROM

INTERFACE

PB

RTC

MEMORY

17

E _

E _

ICE _ E

+ - VREF

VLCD

Voltage

Boost

MPU RAM

(

5

KB

)

S

P

VSTAT

VBAT

_

RTC

IADC 1 IADC 2 IADC

3

IADC

5

IADC

6

VADC

8 ( VA

)

9

VADC

10 ( VC

)

2

TEST MUX

2

CONFIGURATION

RAM

BAT

TEST

TEMP

SENSOR

IADC 4

MUX

and

PREAMP

VREF

VBIAS

∆Σ_

AD CONVERTER

FIR

GNDA

GNDD

VLCD

V 3 P 3 SYS

VADC

IADC 7

( VB )

XIN

RX

MUX

MUX CTRL

CLOCK GEN

UART 0

CROSS

MHz

CK _ 4 X

MUX _ SYNC

CKCE

< 4 . 9 MHz

CE CONTROL

< 4 . 9 MHz

VREF

STRT

PLL

CE

Y

U

MPU

( 80515 )

CKFIR

WPULSE

RTM

32

0 x 000 ... 0 x 2 FF

0 x 0000 ... 0 x 13 FF

8

16

Y

B

R

SDOUT

SDIN

VARPULSE

22

MUX

MEMORY SHARE

I

/

2 . 5 V to logic

LCD _ GEN

LCD DRIVER

DIGITAL I / O

Non - Volatile

VLC 2

VLC 1

SEG Pins

SEGDIO Pins

RTCLK

OPT _ RX /

SEGDIO 55

INTERFACE

DETECTION

WAKE

FAULTZ

0 x 0000 ... 0 xFFFF

PROGRAM

E _ RXTX / SEG 48

SHARE

3

0 X1FFFF

E _ RXTX

TCLK

RST ( Open Drain )

128 KB

RTM

PARAMETERS

TEST MUX

9 / 20 / 2010

图 1. IC 功能框图

v1.2 © 2008–2011 Teridian Semiconductor Corporation 9

71M6543F/H和 71M6543G/GH数据资料

1 引言

本数据资料介绍 71M6543F (64KB,0.5%)、71M6543H (64KB,0.1%)、71M6543G (128KB,0.5%)和

71M6543GH (128KB,0.1%)第四代 Teridian 多相电表片上系统(SoC)。以下讨论适用于所有器件特性或性

能时,将用“71M6543”表示;讨论内容仅适用于特定型号的特性或性能时,将标明相应型号。本数据资

料还介绍了配套的 71M6xx3 隔离电流传感器的基本信息。

本文介绍了 71M6543 配合 71M6xx3 隔离电流传感器的使用方法。71M6543 配合 71M6xx3 IC,可以利用

低成本分流电阻,使用一个非隔离和三个隔离电流传感器构建多相电表,获得这类传感器技术前所未有的

性能。71M6543 SoC还支持电流变压器(CT)配置。

为方便阅读,本文采用超级链接,链接到相关的参考图、表格和章节。本文所有超级链接均以蓝色突出显

示。文中使用了大量的超级链接,提供详细的参考内容,以增强每一部分的细节描述。此外,本文制作成

书签 PDF 格式,便于浏览。

建议读者参考本文第 155 页 8 相关信息部分列出的文件。

10 © 2008–2011 Teridian Semiconductor Corporation v1.2

71M6543F/H 和 71M6543G/GH数据资料

2 硬件说明

2.1 硬件概述

Teridian 71M6543单芯片计量 IC 集成了实现固态电表所需的全部功能模块,包括:

• 模拟前端(AFE),具有 22 位二阶 Σ-Δ ADC

• 独立的 32 位 DSP 数字计算引擎(CE),实现计量功能

• 8051 兼容微处理器(MPU),每个时钟周期执行一条指令(80515)

• 精密电压基准(VREF)

• 用于数字温度补偿的温度传感器:

- 计量(MPU)

- 所有功率模式下,自动补偿 RTC

- MPU 辅助 RTC 补偿

• LCD 驱动器

• RAM 和闪存

• 实时时钟(RTC)

• 多种 I/O 引脚

• 电源故障中断

• 过零中断

• 可选的电流传感器接口,用于本地连接传感器及远端传感器(即使用带有检流电阻的 71M6xx3配套 IC)

• 支持锰铜分流器和电流变压器

为了构建带有或不带零相电流测量功能的多相电表,可直接将一个电阻分流器电流传感器连接至 71M6543

器件(非隔离方案),而采用配套的 71M6xx3 隔离传感器 IC 隔离另外三个分流器。采用低成本、小尺寸脉冲

变压器电气隔离 71M6xx3 远端传感器与 71M6543。71M6543 与 71M6xx3 进行双向数字通信,并通过隔

离脉冲变压器为 71M6xx3 供电。隔离(远端)分流传感器连接至 71M6xx3 的差分输入。71M6543 也可以与

电流变压器配合使用,此时不需要 71M6xx3 隔离传感器。利用 71M6xx3 配套隔离器,系统可提供:

• 数字隔离通信接口

• 模拟前端(AFE),具有 22 位二阶 Σ-Δ ADC

• 精密电压基准(VREF)

• 温度传感器(用于数字温度补偿)

• 全差分分流传感器输入

• 前置放大器,用于优化分流传感器性能

• 隔离电源电路,从 71M6543 发送的脉冲获取直流电源

典型应用中,71M6543 的 32 位计算引擎(CE)顺序处理从模拟输入引脚采集的电压信号,计算有功能量

(Wh)和无功能量(VARh),以及四象限表计的 A

MPU 的外围器件输出。

除了高级测量功能外,实时时钟(RTC)功能允许 71M6543 分时计价(TOU),用于多费率电表以及防时标窃

电或其它窃电事件。在所有工作模式下,包括 MPU 暂停时,RTC 都将自动进行温度补偿,并在断电期间

利用备份电池连续进行补偿。

测量信息可以显示在工作在低温环境的 3.3V。MPU 可以利用集成电荷泵和温度传感器增强 3.3 V LCD 在

低温下的性能。片上电荷泵也可驱动 5 V LCD。灵活的 LCD 段显示方式便于整合现有的定制 LCD。通过软

件调节 LCD 段和 DIO 引脚,以满足各种不同需求。

2

h 和 V2h。然后 MPU 存取这些测量值,进一步处理并通过

v1.2 © 2008–2011 Teridian Semiconductor Corporation 11

71M6543F/H和 71M6543G/GH数据资料

∆Σ ADC

CONVERTER

VREF

MUX

VREF

VREF

VADC

22

FIR

IADC2

VADC9 (VB)

IADC0

VADC8 (VA)

IADC1

IADC3

71M6543

CE RAM

71M6xx3

SP

SN

INP

INN

Remote

Shunt

IB

Digital

Isolation

Interface

Local

Shunt

IN*

22

IADC4

IADC5

71M6xx3

SP

SN

INP

INN

Remote

Shunt

IC

VADC10 (VC)

22

IADC6

IADC7

71M6xx3

SP

SN

INP

INN

Remote

Shunt

IA

22

*IN = Neutral Current

9/17/2010

除了带有温度微调的超高精度电压基准外,片上数字温度补偿机制还包括温度传感器和相关控制,用于修

正温度对测量值和 RTC 精度的影响,以满足 ANSI 和 IEC 标准的要求。与温度相关的外部元件,例如:晶

振、电流变压器(CT)、分流器及其相应的信号调理电路,定义其温度特性并编程修正因子,使得电表在整

个工业温度范围内达到高精度计量的要求。

可利用两个内部 UART 其中之一支持红外 LED,提供内部驱动和检测配置,亦可作为标准 UART 使用。可

选择 38kHz 调制输出。这种灵活性方便了利用 IR 接口实现 AMR 电表的设计,图 1 所示为 IC 方框图。

2.2 模拟前端(AFE)

AFE 作为数据采集系统,由 MPU 控制。为了支持低功耗分流传感器,71M6543 AFE 也可以配合隔离

71M6xx3 传感器工作。图 2 和图 3 所示为两种最常见的配置,也可以根据实际需求采用其它配置。直接连

接至 71M6543 (即 IADC0-IADC1、VADC8、VADC9 和 VADC10)的传感器复用至单个二阶 Σ-Δ ADC 输入,

由 71M6543 进行采样。71M6543的 ADC 输出经 FIR 滤波后储存到 CE RAM 中,由 CE进行后续处理。

采用 71M6xx3 器件隔离的分流传感器由 71M6xx3中的二阶 Σ-Δ ADC 采样,信号样本通过低成本隔离脉冲

变压器传输。

图 2 所示为配合分流传感器和 71M6xx3 隔离传感器使用的 71M6543。图 2 支持零相电流测量,在 IADC0-

IADC1 输入连接本地分流器,器件还连接了三个远端(隔离)分流传感器。如图 2 所示,远端隔离分流传感

器通过 71M6xx3 连接,该电流通道的采样不会切换到复用器,而是通过数字隔离接口直接传送给

71M6543,并直接储存在 CE RAM。MUX_SELn[3:0] I/O R AM 控制字段允许 MPU 将 AFE 配置成相应的多

路复用器采样序列。关于 CE 代码和对应的 AFE设置,请参考表 1和表 2。

图 31 所示为对应于图 2 配置的电表接线。

12 © 2008–2011 Teridian Semiconductor Corporation v1.2

图 2. AFE 方框图(分流器:一个本地传感器、三个远端传感器)

71M6543F/H 和 71M6543G/GH数据资料

∆Σ ADC

CONVERTER

VREF

MUX

VREF

VREF

VADC

22

FIR

IADC4

VADC9 (VB)

IADC2

VADC8 (VA)

IADC3

IADC5

71M6543

CE RAM

IB

CT

IA

CT

IADC6

IADC7

IC

CT

IADC0

IADC1

IN*

CT

VADC10 (VC)

9/17/2010

*IN = Neutral Current

71M6543 AFE 也可以直接连接到电流变压器(CT),如图 3 所示。在这种情况下,所有电压、电流均复用至

71M6543 的单路二阶 Σ-Δ ADC,没有使用 71M6xx3 远端隔离传感器。可选择第四个 CT,通过 IADC0IADC1 电流通道测量零相电流。

图 32 所示为对应于图 3 的接线配置。

图 3. AFE 原理框图 (四个 CT)

2.2.1 信号输入引脚

71M6543具有 11 路 ADC 输入。

IADC0 至 IADC7 用作电流传感器输入。这 8 路电流传感器输入可配置为 8 路单端输入,或配对构成 4 路差

分输入。为获得最佳性能,建议将电流传感器输入配置为差分输入(即:IADC0-IADC1、IADC2-IADC3、

IADC4-IADC5 和 IADC6-IADC7)。第 1 路差分输入(IADC0-IADC1)具有前置放大器,增益可选择 1 或 8,

直接连接分流电阻传感器,还可使用电流变压器(CT)。剩下的三路差分对(即:IADC2-IADC3、IADC4-

IADC5 和 IADC6-IADC7)可用于 CT 或连接远端 71M6xx3 隔离电流传感器,使用低成本脉冲变压器为分流

电阻传感器提供隔离。

其余三路输入:VADC8 (VA)、VADC9 (VB)和 VADC10 (VC)为单端配置,在多相电表应用中检测每一相的

电压。这三路单端输入以 V3P3A引脚为参考。

所有 ADC 输入引脚均测量电压。使用分流电流传感器时,通过分流电阻传感器的压降测量电流。使用电流

变压器(CT)时,通过连接在 CT 次级线圈的负载电阻的电压测量电流。同时,通过电阻分压器检测电网电

压。VADC8 (VA)、VADC9 (VB)和 VBVADC10 (VC)引脚为单端,返回至 V3P3A 引脚。每种传感器的连接

方法请参见图 27、图 28、图 29 和图 30。另请参考 71M6543 演示板原理图及类似电路的典型元器件参数

材料清单。

v1.2 © 2008–2011 Teridian Semiconductor Corporation 13

71M6543F/H和 71M6543G/GH数据资料

引脚 IADC0-IADC1 可独立设置为差分或单端输入,由 DIFF0_E (I/O RAM 0x210C[4])控制位决定。然而,

对于大多数应用,IADC0-IADC1 配置为差分输入,需要相应的外部信号调整电路。

利用 I/O RAM 控制位 PRE_E (I/O RAM 0x2704[5])使能固定增益为 8 的前置放大器,可增强 IADC0-IADC1

引脚的性能。PRE_E = 1 时,IADC0-IADC1 配置为 8 倍增益的前置放大器输入,放大器输出送至复用器。

使用低灵敏度电流传感器时,例如锰铜分流器,8 倍放大器非常适合。PRE_E 置位时,IADC0-IADC1 输入

信号幅度峰值限制在 31.25mV。PRE_E = 0 (增益 = 1)时,IADC0-IADC1 输入信号峰值限制在 250mV。

使用锰铜分流传感器的 71M6543 (图 2),通过置位 DIFF0_E 控制位将 IADC0-IADC1 引脚配置为差分模式,

连接至本地分流器。同时,通过置位 RMTx_E 控制位(I/O RAM 0x2709[5:3]),将 IADC2-IADC3、IADC4-

IADC5 和 IADC6-IADC7 引脚重新配置为数字远端传感器接口,与 Teridian 71M6xx3 隔离传感器通信。

71M6xx3 通过隔离脉冲变压器,利用双向数字流与 71M6543 通信。71M6543 还通过隔离变压器为

71M6xx3 供电。本章末尾对这一类型的接口进行了更深入的说明,参见第 2.2.8 节 71M6xx3 隔离传感器接

口。

如图 3 所示,为了使用电流变压器(CT),将 RMTx_E 控制位复位,从而使 IADC2-IADC3、IADC4-IADC5

和 IADC6-IADC7 配置为本地模拟输入。ADC0-IADC1 引脚不能配置为远端传感器接口。

2.2.2 输入复用器

使用本地传感器工作时,输入复用器按照 11 个 MUXn_SEL[3:0]控制字段确定的采用顺序,将模拟输入信号

依次作用到 ADC 输入(见图 3)。一个完整的采用过程称为复用帧。电流传感器输入配置为单端模式时,

71M6543 的复用器可选择多达 11 路输入信号;电流传感器输入配置为差分模式时(推荐采用这种配置,以

获得最佳性能),每个复用帧的输入信号为 7 个 (即:IADC0-IADC1、IADC2-IADC3、IADC4-IADC5、

IADC6-IADC7、VADC8、VADC9 和 VADC10)。复用帧时隙数量由 I/O RAM 控制字段 MUX_DIV[3:0] (I/O

RAM 0x2100[7:4])控制(见图 4)。复用器总是从状态 0 开始,直到转换完成 MUX_DIV[3:0]决定的所有状态。

71M6543 需要针对特定电表配置编写的 CE 代码。此外,每个 CE 代码都需要特定的 AFE 和 MUX 设置才

能正常工作。表 1 列出了与图 2 中 1 个本地传感器/3 个远端传感器配置相对应的 CE 代码和设置;表 2 列

出了与图 3 CT 配置相对应的 CE 代码和设置。

14 © 2008–2011 Teridian Semiconductor Corporation v1.2

71M6543F/H 和 71M6543G/GH数据资料

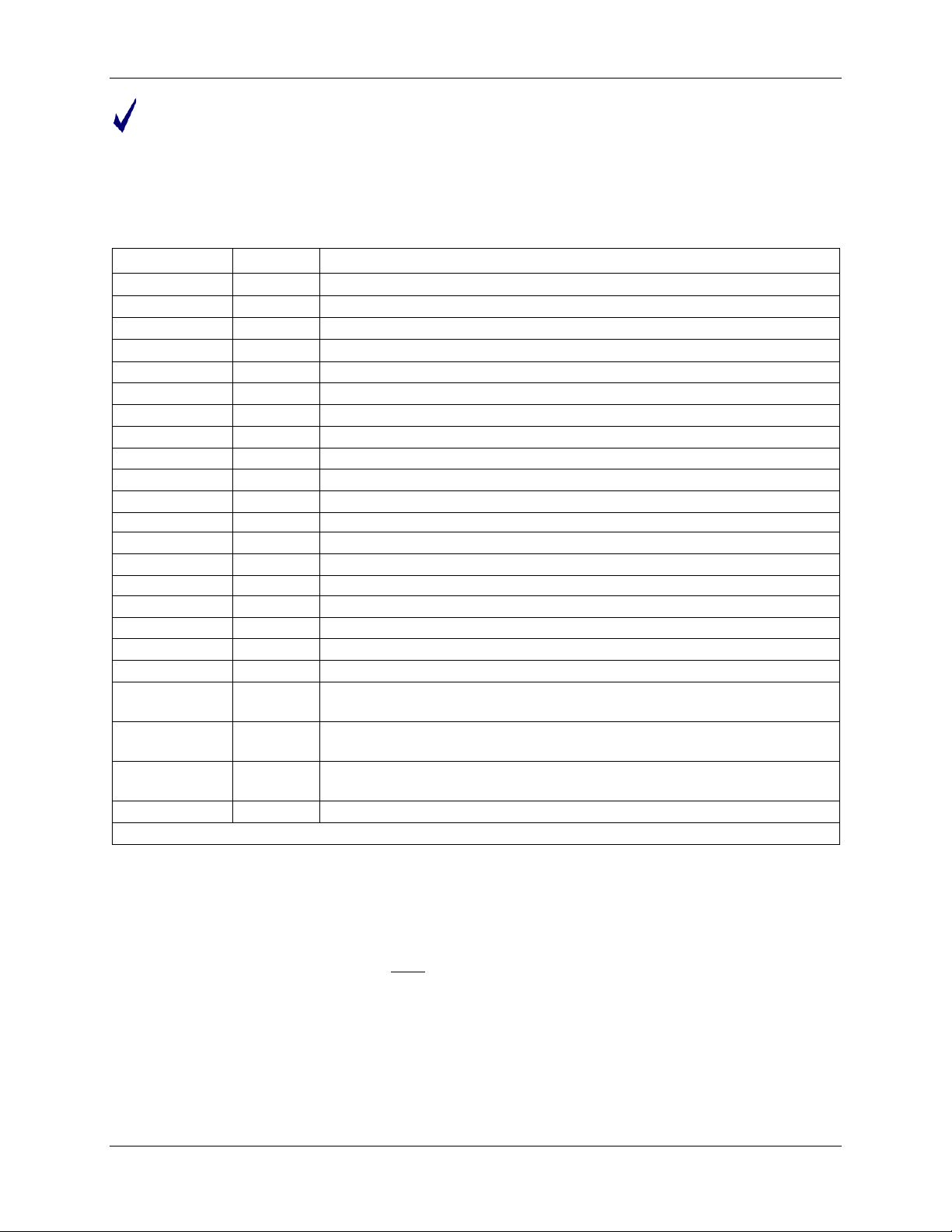

I/O RAM

助记符

I/O RAM

位置

设置 注释

FIR_LEN[1:0]

210C[2:1]

1

ADC_DIV

2200[5]

0

PLL_FAST

2200[4] 1 19.66MHz

MUX_DIV[3:0]

2100[7:4]

6

MUX0_SEL[3:0]

2105[3:0]

0

MUX1_SEL[3:0]

2105[7:4]

1

MUX2_SEL[3:0]

2104[3:0]

1

MUX3_SEL[3:0]

2104[7:4]

8

(VA)

MUX4_SEL[3:0]

2103[3:0]

9

(VB)

MUX5_SEL[3:0]

2103[7:4]

A

(VC)

MUX6_SEL[3:0]

2102[3:0]

0

MUX7_SEL[3:0]

2102[7:4]

0

MUX8_SEL[3:0]

2101[3:0]

0

MUX9_SEL[3:0]

2101[7:4]

0

MUX10_SEL[3:0]

2100[3:0]

0

RMT2_E

2709[3]

1

(IA)

RMT4_E

2709[4]

1

(IB)

RMT6_E

2709[5]

1

(IC)

DIFF0_E

210C[4]

1

(IN)

DIFF2_E

210C[5]

0

DIFF4_E

210C[6]

0

3

DIFF6_E

3

PRE_E

2704[5]

1

EQU[2:0]

2106[7:5]

5

IA*VA + IB*VB + IC*VC

5

31

注:

CE

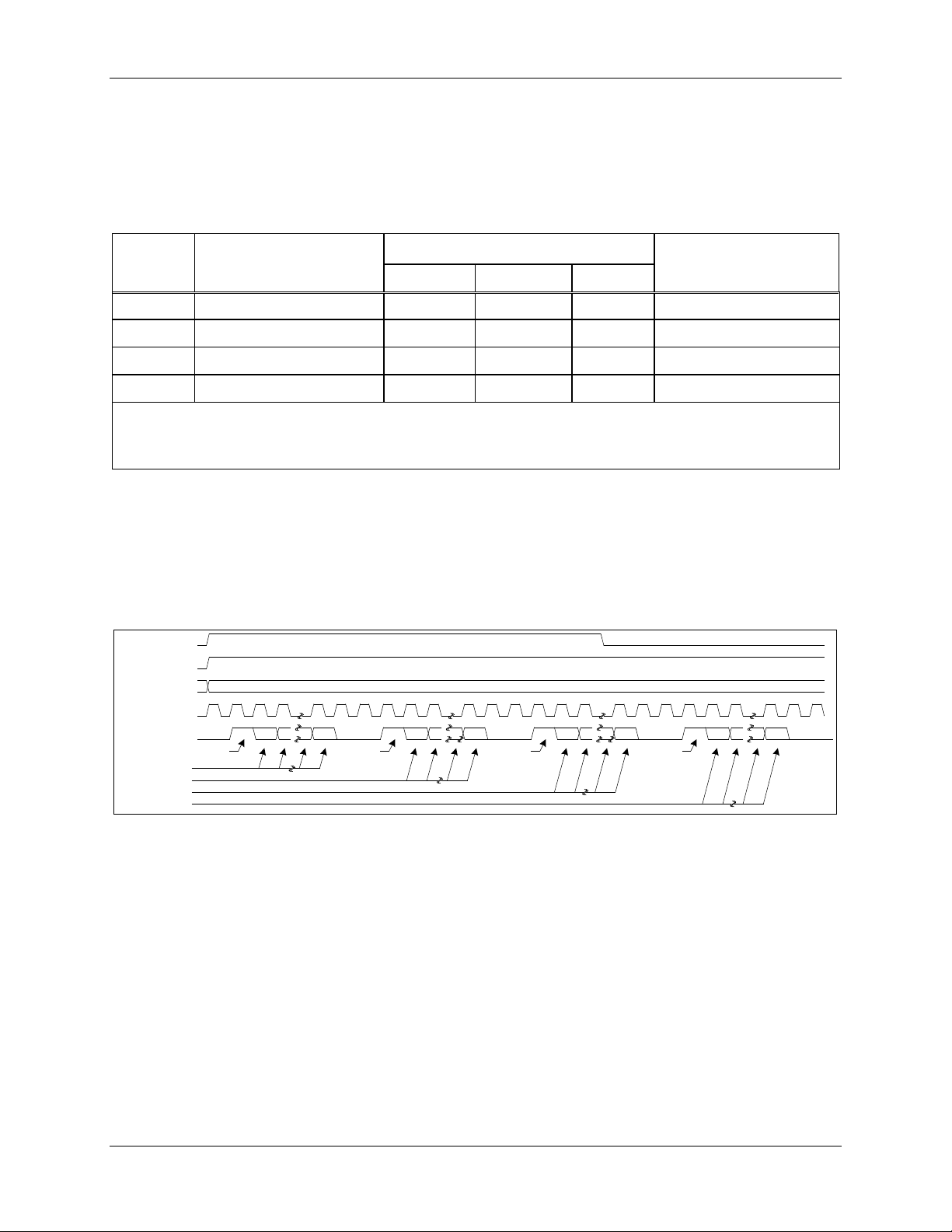

表 1. CE 代码和设置(1 个本地/3 个远端传感器)

I/O RAM

288 周期

快速

见注 1

时隙 0 为 IADC0-IADC1

(IN)

未使用(见注 2)

未使用(见注 2)

时隙 3 为 VADC8

时隙 4 为 VADC9

时隙 5 为 VADC10

时隙未使能

使能远端 IADC2-IADC3

使能远端 IADC4-IADC5

使能远端 IADC6-IADC7

差分 IADC0-IADC1

见注 3

见注

210C[7] 0

见注

IADC0-IADC1 增益 = 8

ce43b016603 (与 71M6603 配合使用)

CE 代码

(见注 4)

ce43b016103 (与 71M6103 配合使用)

ce43b016113 (与 71M6113 配合使用)

ce43b016203 (与 71M6203 配合使用)

公式

电流传感器类型 1个本地分流器和 3 个远端分流器

对应电路图

图2、图4 和图

1. 该表中写入其它数值时,MUX_DIV[3:0]应该置 0;然后,在写 MUXn_SEL[3:0]字段之前置

入需要的数值。

2. 每个不用的时隙必须分配有效数值(0至 A),但不进行 ADC 操作。

3. 该通道为远端检测(71M6xx3),与 DIFFx_E 不相关。

4. 必须使用 71M6xx3 器件特定的 CE 代码。

Teridian 定期更新 CE 代码。关于最新的 CE 代码和相关设置,请联系当地的 Teridian 代表处

获取最新的

代码和相关设置。

v1.2 © 2008–2011 Teridian Semiconductor Corporation 15

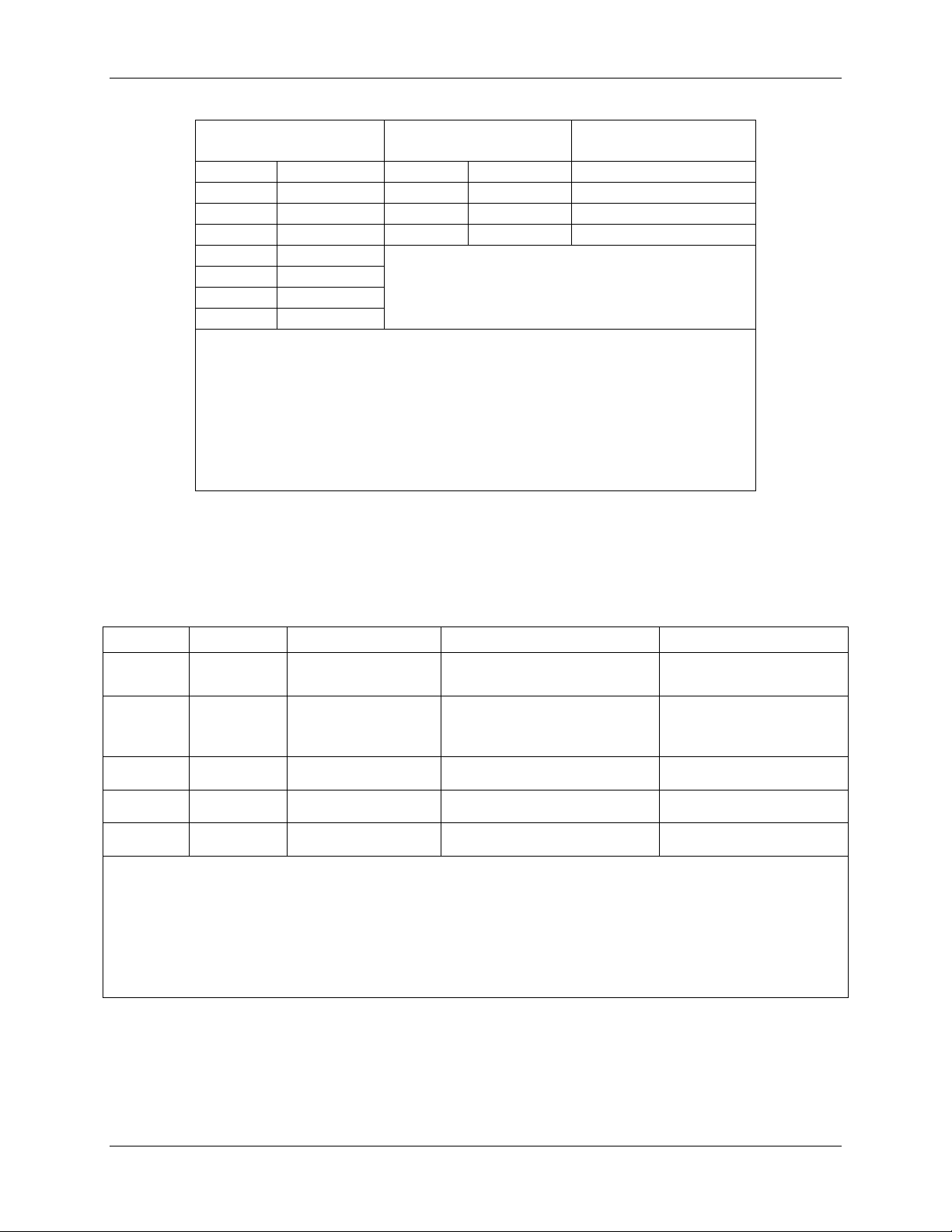

71M6543F/H和 71M6543G/GH数据资料

助记符

位置

设置

(Hex)

注释

FIR_LEN[1:0]

210C[2:1]

1

ADC_DIV

2200[5]

0

PLL_FAST

2200[4] 1 19.66MHz

MUX_DIV[3:0]

2100[7:4]

7

1

MUX0_SEL[3:0]

2105[3:0]

2

(IA)

MUX1_SEL[3:0]

2105[7:4]

8

(VA)

MUX2_SEL[3:0]

2104[3:0]

4

(IB)

MUX3_SEL[3:0]

2104[7:4]

9

(VB)

MUX4_SEL[3:0]

(IC)

MUX5_SEL[3:0]

2103[7:4]

A

(VC)

MUX6_SEL[3:0]

2102[3:0]

0

MUX7_SEL[3:0]

2102[7:4]

0

MUX8_SEL[3:0]

2101[3:0]

0

MUX9_SEL[3:0]

2101[7:4]

0

MUX10_SEL[3:0]

2100[3:0]

0

RMT2_E

2709[3]

0

RMT4_E

2709[4]

0

IADC4-IADC5

RMT6_E

IADC6-IADC7

DIFF0_E

210C[4]

1

DIFF2_E

210C[5]

1

DIFF4_E

210C[6]

1

DIFF6_E

210C[7]

1

IADC6-IADC7

PRE_E

2704[5]

0

EQU[2:0]

2106[7:5] 5 IA*VA + IB*VB + IC*VC

5

4

(CT)

32

注:

CE

表 2. CE 代码和设置(CT 传感器)

I/O RAM

I/O RAM

I/O RAM

288 周期

快速

见注

时隙 0 为 IADC2-IADC3

时隙 1 为 VADC8

时隙 2 为 IADC4-IADC5

时隙 3 为 VADC9

2103[3:0] 6

时隙 4 为 IADC6-IADC7

时隙 5 为 VADC10

时隙 6 为 IADC0-IADC1

(IN – 见注 2)

时隙未使能

本地传感器 IADC2-IADC3

本地传感器

2709[5] 0

本地传感器

差分 IADC0-IADC1

差分 IADC2-IADC3

差分 IADC4-IADC5

差分

IADC0-IADC1 增益 = 1

CE 代码

ce43a02

公式

电流传感器类型

对应电路图

个电流传感器

图3、图4和图

1. 该表中写入其它数值时,MUX_DIV[3:0]应该置 0;然后,在写 MUXn_SEL[3:0]字段之前置入需

要的数值。

2. IN 为可选择的零相电流。

Teridian 定期更新 CE 代码。关于最新的 CE 代码和相关设置,请联系当地的 Teridian 代表处获取

最新的

16 © 2008–2011 Teridian Semiconductor Corporation v1.2

代码和相关设置。

71M6543F/H 和 71M6543G/GH数据资料

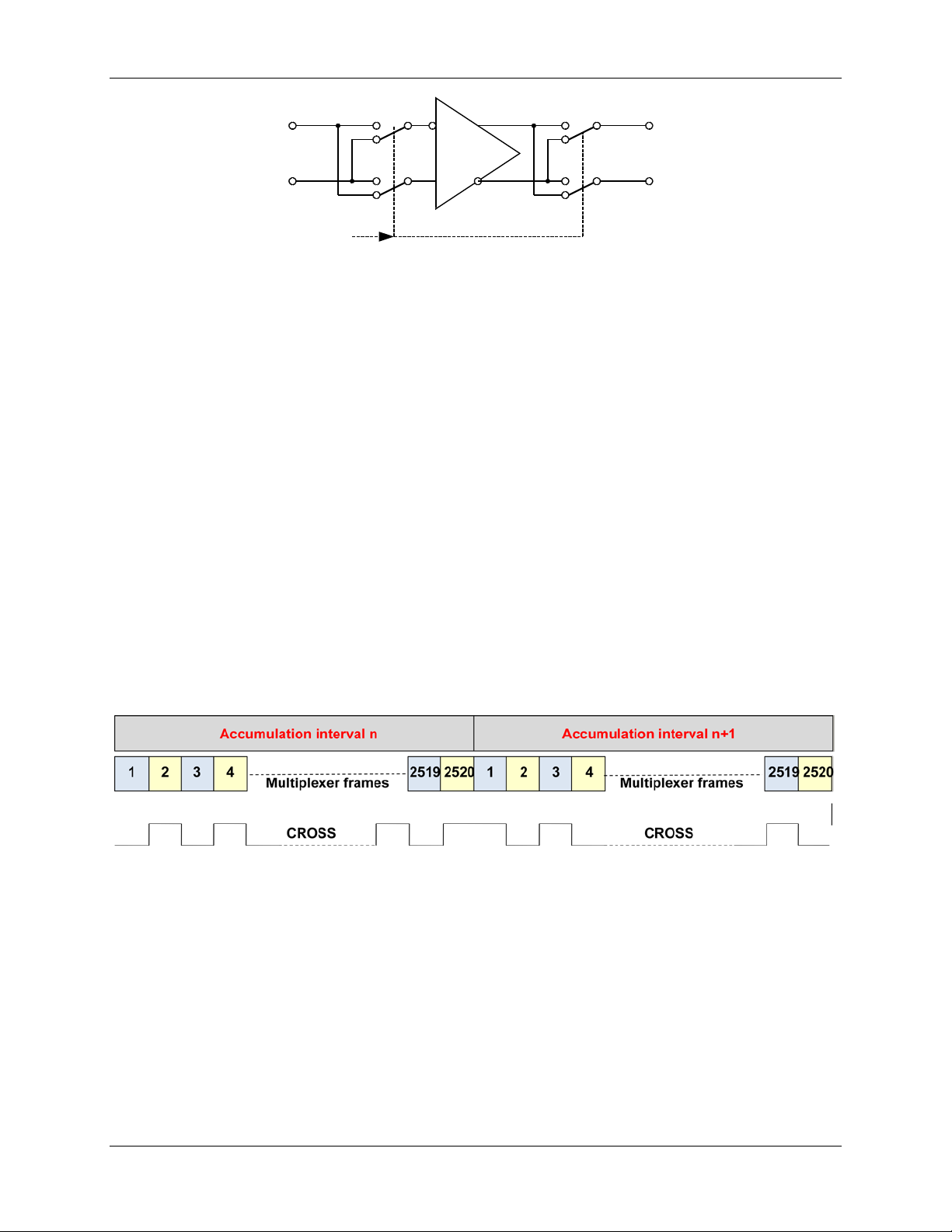

CK32

MUX STATE 0 1 2 3 4

5

MUX_DIV[3:0] = 6 Conversions

Settle

Multiplexer Frame

S

CROSS

MUX_SYNC

S

IN

Unused

Unused VA VB VC

CK32

MUX STATE

0 1 2 3 4

5

MUX_DIV[3:0] = 7 Conversions

Settle

Multiplexer Frame

S

CROSS

MUX_SYNC

S

6

IA

VA

IB VB

IC VC IN

如果使用表 1 和表 2 列出的 I/O RAM 助记符设置与对应的 CE代码不匹配,则会产生负面影响,

MPU 不会选中。请联系当地的 TERIDIAN 代表处获取与之对应的正确 CE 代码和 AFE/MUX 设

置。

图 2 所示给出了使用锰铜电流传感器和 71M6xx3 隔离传感器、带有零相检测功能的多相配置,IADC0-

IADC1 输入必须配置为差分输入,连接到本地分流器(详细的分流器连接方法如图 30 所示)。连接至

IADC0-IADC1 输入的本地分流器用于检测零相电流。电压传感器(VADC8、VADC9 和 VADC10)也直接连

接到 71M6543 (详细的连接方法如图 27 所示),通过多路复用器传输,如图 2 所示。同时,IADC2-IADC3、

IADC4-IADC5 和 IADC6-IADC7 电流输入配置为远端传感器数字接口,相应的采样不通过复用器。这种配

置的复用器时序如图 4 所示。

对于使用电流变压器(CT)传感器、可选择零相检测功能的多相配置,如图 3 所示,所有四路电流传感器输

入必须配置为差分输入,连接到对应的 CT (详细的差分 CT 连接方法如图 29 所示)。IADC0-IADC1 电流传

感器输入可选择用于检测零相电流,用于防窃电设计。电压传感器(VADC8、VADC9 和 VADC10)直接连接

至 71M6543 (详细的电压传感器连接方法如图 27 所示)。这种配置下不使用 71M6xx3 隔离传感器,所有传

感器通过复用器连接,如图 3所示。这种配置的复用器时序如图 5 所示。

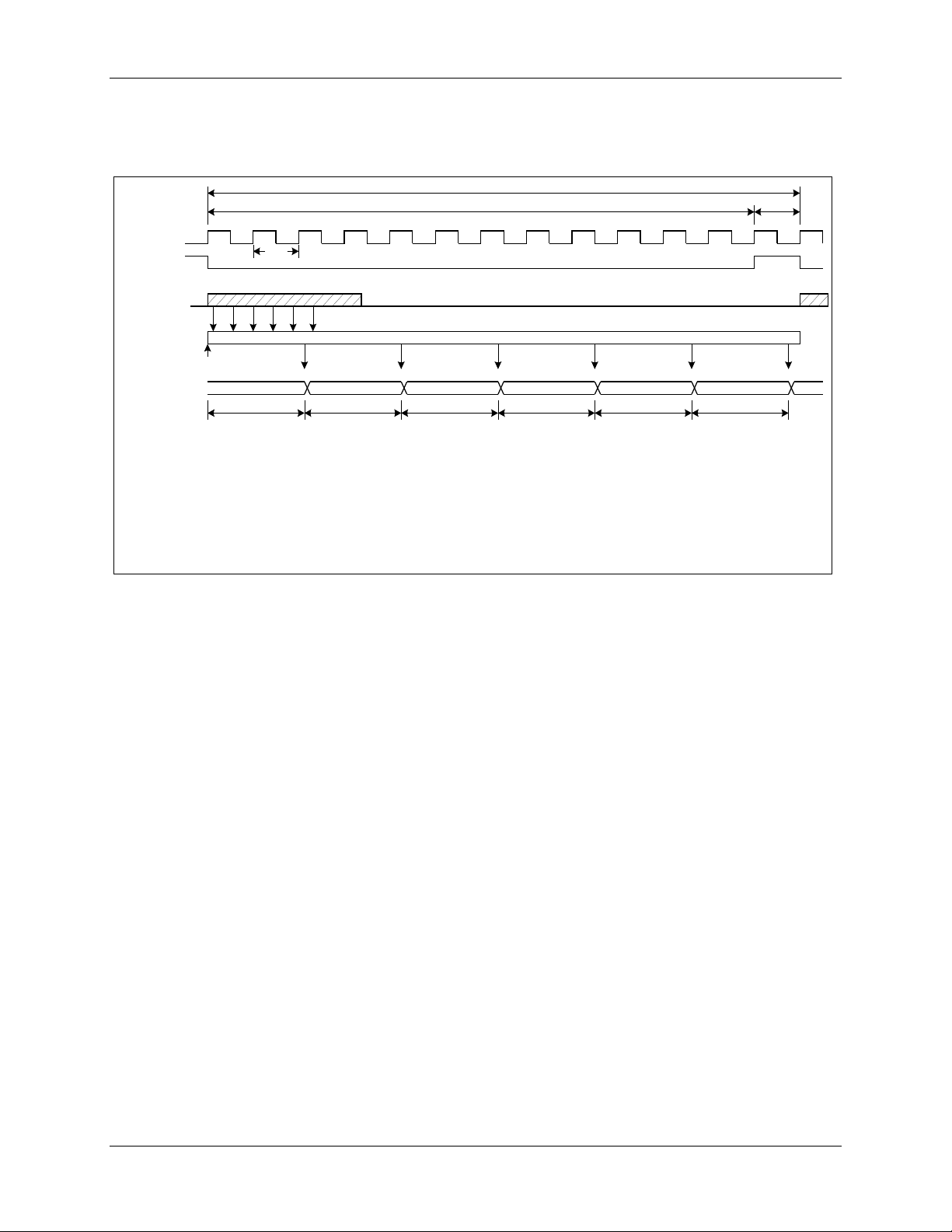

图 4 所示的复用器时序与图 2配置相对应。帧持续时间为 13 个 CK32 周期(其中 CK32 = 32,768 Hz),因此,

采样率为 32,768 Hz / 13 = 2,520.6 Hz。注意,图 4仅显示了通过 71M6543 复用器的电流,未显示直接从

远端传感器保存到 CE RAM 的电流(图 2),这些电流在复用帧的下半周期采样获得。图中两个未使用的转

换时隙是支持 2,520.6 Hz采样率所必需的。

图 4. 复用帧状态(MUX_DIV[3:0] = 6)

图 5 所示复用器时序与图 3 的 CT 配置相对应。由于所有电流传感器本地连接至 71M6543,电流均通过复

用器传送,如图 3 所示。对于复用器时序,帧持续时间为 15 个 CK32 周期(其中 CK32 = 32,768 Hz),采用

率为 32,768 Hz / 15 = 2,184.5 Hz。

图 5. 复用帧状态(MUX_DIV[3:0] = 7)

v1.2 © 2008–2011 Teridian Semiconductor Corporation 17

71M6543F/H和 71M6543G/GH数据资料

复用器切换、FIR 启动以及选择 ADC 基准电压(使用内部 CROSS 信号,参见第 2.2.7 节电压基准)由内部

MUX_CTRL 电路控制。此外,MUX_CTRL 控制每次 CE 代码的执行。MUX_CTRL 由 PLL 模块的 32768

Hz 时钟 CK32 驱动。下面是 MUX_CTRL 电路管理寄存器:

• CHOP_E[1:0] (I/O RAM 0x210 6[3:2])

• MUX_DIV[3:0] (I/O RAM 0x2100[7: 4])

• FIR_LEN[1:0] (I/O RAM 0x210C[2:1])

• ADC_DIV (I/O RAM 0x2200[5 ])

每个复用器状态的持续时间取决于 FIR 处理的 ADC 采样通道数量,由 FIR_LEN[1:0] (I/O RAM 0x210C[2:1]

控制字段决定。每个复用器状态从 32kHz 时钟 CK32 的上升沿开始。

建议在更改 ADC 配置时将 MUX_DIV[3:0] (I/O RAM 0x2200[2:0])设置为 0,虽然不是必须要求,这样做有

助于将 ADC 输入之间可能产生瞬间短路而引起的系统瞬变降至最小,特别是在更改 DIFFn_E 控制位(I/O

RAM 0x210C[5:4])的情况下。设置该配置位后,MUX_DIV[3:0]应设置在所要求的数值。

CK32 周期中每个时隙的持续时间取决于 FIR_LEN[1:0]

Time_Slot_Duration = (3-2*PLL_FAST)*(FIR_LEN[1:0]+1) * (ADC_DIV+1)

CK32 周期中复用帧的持续时间为:

MUX_Frame_Duration = 3-2*PLL_FAST + Time_Slot_Duration * MUX_DIV[3:0]

CK_FIR 周期中复用帧的持续时间为:

MUX frame duration (CK_FIR cycles) =

[3-2*PLL_FAST + Time_Slot_Duration * MUX_DIV] * (48+PLL_FAST*102)

可通过 MUXx_SEL 控制字段(I/O RAM 0x2100 至 0x2105)编程 ADC 转换时序。如上所述,71M6543有 11 个

ADC 时隙,由 MUX_DIV[3:0] (I/O RAM 0x2100[7:4] )设置。表达式 MUXx_SEL[3:0] = x 中,“n”指复用帧时

隙数量,x 代表对应 ADC 输入编号或序号(即 IADC0 至 VADC10,或简单的 0 至 10 十进制数)。由此,在

71M6543 器件中共有 11 个有效的 ADC 序号。例如,如果 MUX0_SEL[3:0] = 0,那么 IADC0,对应于

IADC0-IADC1 输入(配置为差分输入)的采样,定位在复用帧的时隙 0。关于相应的 MUXx_SEL[3:0]设置及

适合的电表配置和 CE 代码,请参见表 1和表 2。

注意,启用远端传感器接口时,远端传感器电流的采样不通过 71M6543 复用器,在复用帧后半周期采样远

端电流传感器。在复用帧的最后分配给 VA、VB、VC 电压三个时隙,VA、VB、VC 根据这一时隙安排对

相应的远端传感器电流进行采样,遵循严格的相位电压、延时补偿关系,确保高精度指标(参见第 19 页

2.2.3节延时补偿)。

、

ADC_DIV和 PLL_FAST。

使用远端传感器时,有必要引入不使用的时隙,以满足 MUX_DIV[3:0] (I/O RAM 0x2100[7:4])字段设置规定

的时隙数量(见

ADC 序号(即十进制 0 至 10)。按照这种方式,未使用的 ADC 序号将作为复用帧中的“空操作”占位符,

产生正确的复用帧时序持续时间,并满足所要求的采样率。CE 程序将忽略 CE RAM 中储存的对应于“控

操作”ADC 序号的采样结果。同时,数字隔离接口负责自动将远端接口电流传感器的采样储存到相应的

CE RAM 中。

18 © 2008–2011 Teridian Semiconductor Corporation v1.2

图 4 和图 5)。这些未使用(“空操作”)时隙的 MUXn_SEL[3:0]控制字段必须写入一个有效的

71M6543F/H 和 71M6543G/GH数据资料

名称

位置

说明

ADC_DIV

2200[5]

ADC和FIR

o

delay

o

delay

ft

T

t

360360 ⋅⋅=⋅=

φ

CE 代码中的延迟补偿和其它功能要求 MUX_DIV[3:0]、MUXx_SEL[3:0]、RMT_E、FIR_LEN[1:0]

ADC_DIV 和 PLL_FAST 的设置对于给定的 CE 代码是固定的。关于 71M6543 的合理设置,请参见

表 1 和表 2。

表 3 汇总了用于配置复用器、信号引脚和 ADC 的 I/O RAM 寄存器。所有列出的寄存器在复位及从电池模

式唤醒后清零,可进行读、写操作。

表 3. 复用器和 ADC 配置位

MUX0_SEL[3:0]

MUX1_SEL[3:0]

MUX2_SEL[3:0]

MUX3_SEL[3:0]

MUX4_SEL[3:0]

MUX5_SEL[3:0]

MUX6_SEL[3:0]

MUX7_SEL[3:0]

MUX8_SEL[3:0]

MUX9_SEL[3:0]

MUX10_SEL[3:0]

MUX_DIV[3:0]

PLL_FAST

FIR_LEN[1:0] 210C[2:1]

DIFF0_E

DIFF2_E

DIFF4_E

DIFF6_E

RMT2_E

RMT4_E

RMT6_E

PRE_E

关于这些 I/O RAM位置的详细信息,请参见从第 104 页开始的表 71。

2105[3:0] 选择在时隙 0 期间转换 ADC输入。

2105[7:4] 选择在时隙 1 期间转换 ADC输入。

2104[3:0] 选择在时隙 2 期间转换 ADC输入。

2104[7:4] 选择在时隙 3 期间转换 ADC输入。

2103[3:0] 选择在时隙 4 期间转换 ADC输入。

2103[7:4] 选择在时隙 5 期间转换 ADC输入。

2102[3:0] 选择在时隙 6 期间转换 ADC输入。

2102[7:0] 选择在时隙 7 期间转换 ADC输入。

2101[3:0] 选择在时隙 8 期间转换 ADC输入。

2101[7:0] 选择在时隙 9 期间转换 ADC输入。

2100[3:0] 选择在时隙 10 期间转换 ADC输入。

2100[7:4] 每个复用帧中 ADC 时隙的数量(最大 = 11)。

2200[4]

210C[4] 使能模拟输入引脚 IADC0-IADC1 的差分配置。

210C[5] 使能模拟输入引脚 IADC2-IADC3.的差分配置。

210C[6] 使能模拟输入引脚 IADC4-IADC5 的差分配置。

210C[7] 使能模拟输入引脚 IADC6-IADC7 的差分配置。

2709[3]

2709[4]

2709[5]

2704[5] 使能 8x前置放大器。

控制

控制 PLL 和 MCK 速率。

决定 ADC抽样 FIR 滤波器中的 ADC周期数。

使能远程传感器接口,将引脚 IADC2-IADC3 转换为数字接口,与 71M6xx3 传感

器通信。

使能远程传感器接口,将引脚 IADC4-IADC5转换为数字接口,与 71M6xx3 传感

器通信。

使能远程传感器接口,将引脚 IADC6-IADC7转换为数字接口,与 71M6xx3 传感

器通信。

时钟速率。

2.2.3 延时补偿

、

测量单相能量(即 Wh 和 VARh)时,必须对该相电压和电流同步采样。否则,会产生相位差 Ф,进而引入误

差。

式中,f 为输入信号的频率,T = 1/f,t

为电流和电压之间的采样延迟。

delay

传统设计中,采样是通过控制每相的两个 A/D 转换器(一个用于电压,另一个用于电流)同时采样实现的。

而 Teridian 的单转换器技术(Single-Converter Technology

®

)利用其 CE 的 32 位信号处理能力,实现了“固

定延迟”全通滤波器。全通滤波器修正采用单路复用 A/D 转换器引起的电压和对应电流采样之间的转换时

间差。

v1.2 © 2008–2011 Teridian Semiconductor Corporation 19

71M6543F/H和 71M6543G/GH数据资料

“固定延迟”全通滤波器提供 360° - θ 宽频带延迟,它与给定相的电压和电流之间的采样时间差精确匹配。

该数字滤波器不影响信号幅值,但提供精确受控的相位响应。

推荐 ADC 复用序列首先采样电流,随后采样对应相的电压,由此,电压比电流延迟一个相位角 Ф。CE 内

执行的延迟补偿首先将电流采样延迟一个完整的采样间隔(即 360°),然后使电压采样通过全通滤波器,由

此将电压采样延迟 360

样本对齐。剩余相位误差可忽略不计,100Hz时,误差通常小于±1.5 毫度,所以不会引起能量测量误差。

使用远程传感器时,CE 执行与上述相同的延迟补偿,将每个电压采样与对应的电流采样对齐。即使远程电

流采样不通过 71M6543 复用器,如果按照表 1 对 MUXn_SEL[3:0]时隙分配字段编程,它与对应电压的定

时关系也是固定且精确可知的。注,这些时隙分配使得 VA、VB 和 VC 分别占用复用时隙 3、4 和 5 (见图

4)。

o

- θ,造成电流与对应电压之间的相位误差为 θ – Ф,从而将电压样本与对应的电流

2.2.4 ADC前置放大器

ADC 前置放大器为低噪声差分放大器,固定增益 8 仅可用于 IADC0-IADC1 传感器输入引脚。通过置位

PRE_E = 1 (I/O RAM 0x2704[5])使能 8倍增益。禁用时,前置放大器的电源电流< 10nA,增益为单位增益。

正确设置 PRE_E 和 DIFF0_E (I/O RAM 0x210C[4])位,无论是否选择差分模式,均可使用前置放大器。为获

得最佳性能,建议使用差分模式。为节约功率,根据 ADC_DIV 控制位(I/O RAM 0x2200[5])调节前置放大器

和 ADC 的偏置电流。

2.2.5 A/D转换器(ADC)

利用 2 阶 Σ-Δ A/D 转换器量化输入电压和电流。ADC 分辨率(包括符号位)为 21 位(FIR_LEN[1:0] = 01,I/O

RAM 0x210C[2:1])或 22 位(FIR_LEN[1:0] = 10)。ADC 时钟由 CKADC 驱动。

由 MUX_CTRL 内部电路控制每次 ADC 转换的启动。ADC 转换结束时,FIR 滤波器输出数据储存至 CE

RAM,地址由复用器选项决定。

2.2.6 FIR滤波器

有限冲击响应滤波器是 ADC 的一部分,针对复用器进行优化,使 ADC 输出达到所要求的分辨率。每次

ADC 转换结束时,输出数据储存至固定的 CE RAM 地址,由存储在 MUXn_SEL[3:0]

FIR 数据经过左移 9 位后储存。

的

复用器选项决定,

2.2.7 电压基准

带隙基准为 ADC 提供基准电压,基准幅值为斩波稳定,可由 MPU 利用 I/O RAM 控制字段 CHOP_E[1:0]

(I/O RAM 0x2106[3:2])使能或禁用斩波电路。CHOP_E[1:0]字段中的两位使能 MPU,将斩波电路置于标准

模式或反相模式,或者自动切换模式(推荐)。斩波电路在复用周期之间切换时,VREF 的直流失调被自动调

整为零,因此,斩波电路必须配置成其中一种自动切换模式。

电压基准(VREF)的后级放大器通常存在长期漂移电压,通过斩波电路可以自动消除失调电压的影响,提供

稳定的 VREF。71M6543 和 71M6xx3 均具有斩波电路,用于各自的 VREF 电压基准。

斩波放大器的典型拓扑如图 6 所示。CROSS 信号为内部信号,不能通过引脚或寄存器进行直接操作。

20 © 2008–2011 Teridian Semiconductor Corporation v1.2

71M6543F/H 和 71M6543G/GH数据资料

G

-

+V

inp

V

outp

V

outn

V

inn

CROSS

A

B

A

B

A

B

A

B

图 6. 斩波放大器通用拓扑

假设在放大器正极输入上有一个偏移电压 Voff。由 CROSS (内部信号)控制所有开关处于 A 位置时,输出

电压为:

Voutp – Voutn = G (Vinp + Voff – Vinn) = G (Vinp – V i nn) + G Voff

通过施加反相 CROSS 信号将所有开关处于 B 位置时,输出电压为:

Voutn – Voutp = G (Vinn – Vinp + Voff) = G (Vinn – Vinp) + G Voff, or

Voutp – Voutn = G (Vinp – Vinn) - G Voff

因此,CROSS 切换时,例如每个复用周期之后,输出偏移表现为正、负交替,从而消除漂移,不受极性或

幅值影响。

CROSS 为高电平时,放大器输入连接反转。维持放大器增益的总体极性,将输入失调电压反相。通过交替

反转连接,对放大器失调取平均,结果为零。这样就消除了电压基准中常见的长期失调。CHOP_E[1:0] (I/O

RAM 0x2106[3:2])控制字段使能 CROSS 功能。在复用序列的最后一个转换状态之后的第一个 CK32 上升沿,

复用器在开始新帧之前额外等待一个 CK32 周期。该周期开始时,根据 CHOP_E[1:0]字段更新 CROSS 数

值。额外的 CK32 周期使斩波 VREF 有时间达到稳定。在此期间,MUXSYNC 保持为高电平。MUXSYNC

的前沿启动一次 CE 程序的运行。

CHOP_E[1:0]有四个状态:同相、反相和两个自动切换状态。同相状态下,CHOP_E[1:0] = 01,CROSS

保持为低电平;反相状态下,CHOP_E[1:0] = 10,CROSS 保持为高电平。两种自动切换状态通过设置

CHOP_E=11或 CHOP_E=00配置。

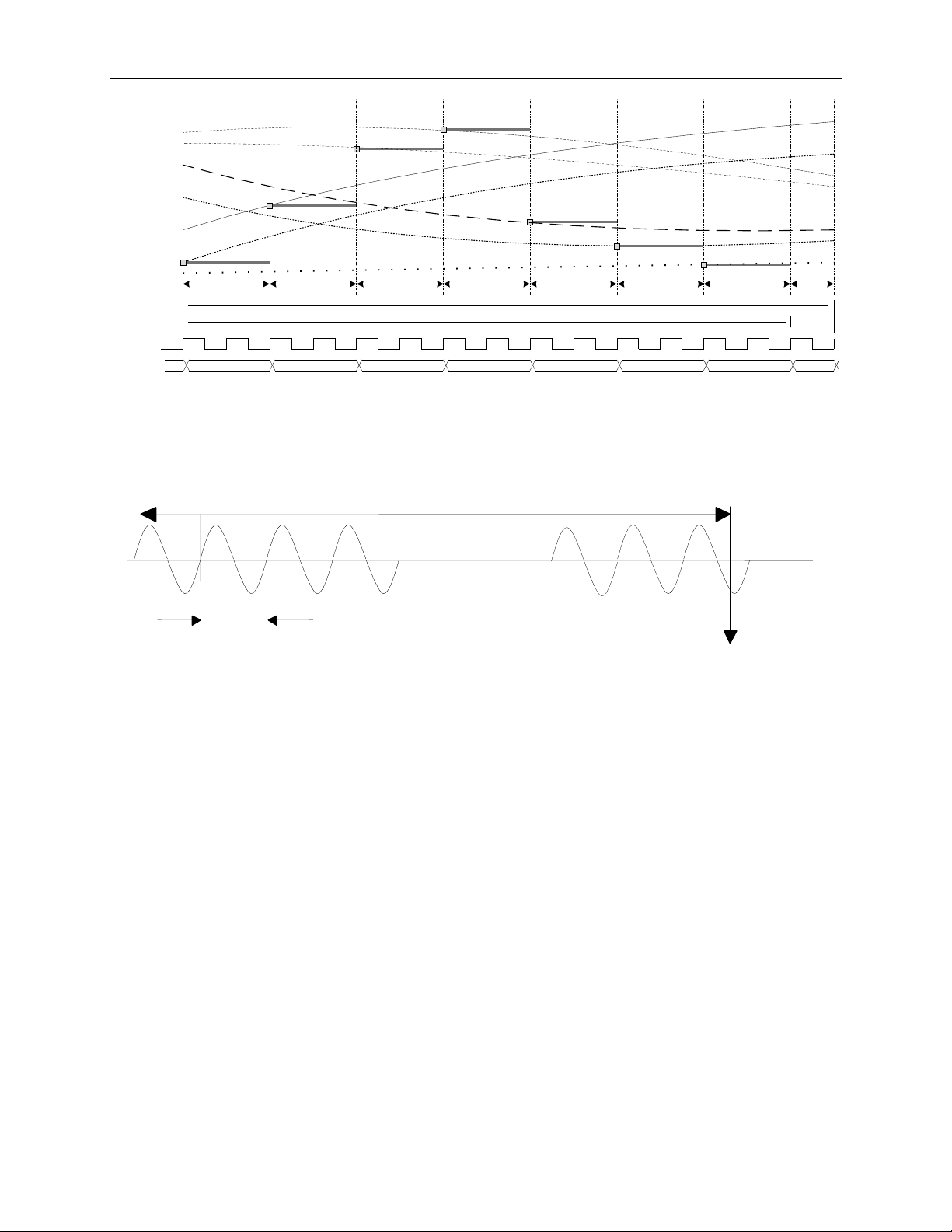

图 7. CROSS 信号, CHOP_E = 00

图 7 所示为 CHOP_E[1:0] = 00 时两个累积间隔的 CROSS 信号。第一个间隔末尾,CROSS 为高电平;第

二个间隔末尾,CROSS 为低电平。CHOP_E[1:0] = 00 时,不需要 MPU 控制斩波器。

在第二个自动切换状态,CHOP_E[1:0] = 11,CROSS在累积间隔的最后一个复用周期结束时不切换。

v1.2 © 2008–2011 Teridian Semiconductor Corporation 21

71M6543F/H和 71M6543G/GH数据资料 8

2.2.8 71M6xx3 隔离传感器接口

2.2.8.1 概述

非隔离传感器,例如电阻分流器,可通过 71M6xx3 和脉冲变压 (图 31 所示为该传感器接口的顶层方框图)

的组合连接至 71M6543。71M6xx3 通过脉冲变压器直接从 71M6543 取 电,无需专用的供电电路。

71M6xx3 建立与 71M6543 的双向通信,通过串行数据流提供电流采样和辅助信息(例如:传感器温度)。

71M6543 支持多达三个 71M6xx3 隔离传感器。使能远端传感器接口时,两个模拟电流输入引脚重新配置

为数字远端传感器接口。例如,控制位 RMT2_E = 1 时,IADC2-IADC3 模拟引脚重新配置为连接至远端的

数字接口引脚。

每个 71M6xx3 远端传感器由以下模块组成:

• 电源,从 71M6543 接收的脉冲产生电源

• 双向数字通信接口

• 分流信号前置放大器

• 22 位 2 阶 Σ-Δ ADC 转换器,带有高精度带隙基准(斩波放大器)

• 温度传感器(用于数字补偿 VREF)

• 熔丝器件,包含部件相关信息

在常规的复用周期内,71M6543 利用 MUX_DIV[3:0] (I/O RAM 0x2100[7:4])决定使能哪个通道。同时,对

远端传感器的调制器输出进行采样。每个转换结果在 CE操作时隙写入 CE RAM。

2.2.8.2 71M6543 和 71M6xx3 隔离传感器之间的通信 71M6xx3 的 ADC 定时时钟来自 71M6543 产生的脉冲信号。电源脉冲的产生,以及 71M6543 和 71M6xx3

远端传感器之间的通信协议通过硬件自动完成,用户无需进行任何操作,本数据资料不作详细介绍。

2.2.8.3 71M6xx3 隔离传感器的控制 71M6543可读、写每个 71M6xx3 远端传感器的特定字节信息。

读取数据由 RCMD[4:0]和 TMUXRn[2:0]组合选择。为执行对 71M6xx3 器件的读操作,MPU 首先写

TMUXRn[2:0]字段(其中 n = 2、4、6,分别位于 I/O RAM 0x270A[2:0]

MPU 根据所要求的命令和相选择写入 RCMD[4:0] (SFR 0xFC[4:0])。RCMD[4:2]位清零时,操作完成,请

求发送的数据位于 RMT_RD[15:0] (I/O RAM 0x2602[7:0]为 MSB,0x2603[7:0]为 LSB)。操作期间还更新读

取奇偶校验位 PERR_RD (SFR 0xFC[6])。如果 MPU 在完成上次读操作之前写入 RCMD[4:0],则忽略命令。

因此,MPU 在继续发出下一条读命令之前必须等待 RCMD[4:2] = 0。

如果正在运行 CE (CE_E=1),MPU 必须在 CE_BUSY 上升沿之后立即写入 RCMD[4:0] 。RCMD[4:0]必须

在下一个 MUX_SYNC 上升沿之前写入。否则,会造成读取数据不正确。

RCMD[4:0]字段分为两个子域:COMMAND=RCMD[4:2]和 PHASE=RCMD[1:0],如表 4 所示。

.

、

0x270A[6:4]和 0x2709[2:0])。接着,

22 © 2008-2010 MAXIM/TERIDIAN Semiconductor Corporation v1.2

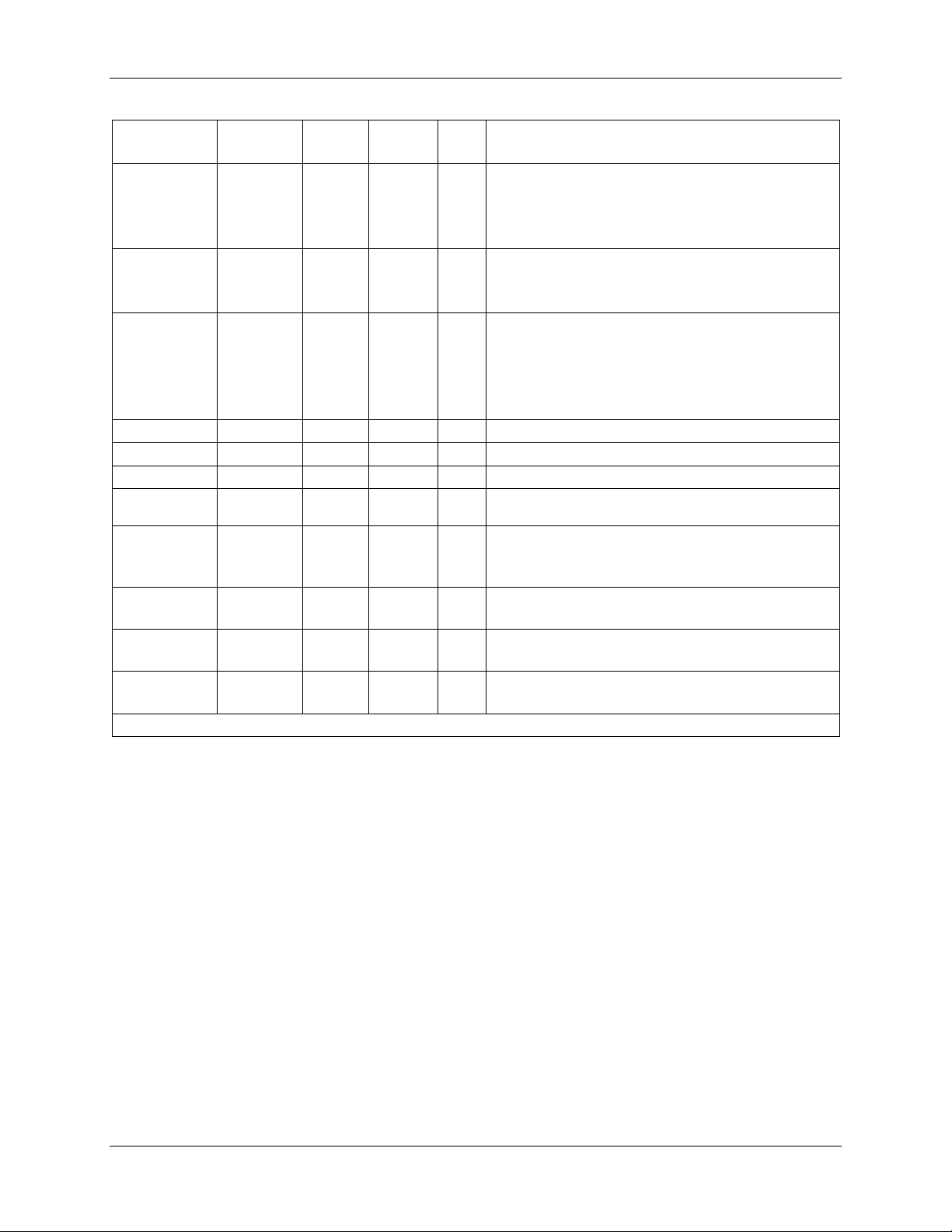

8 71M6543F/H和 71M6543G/GH 数据资料

命令

相选择器

相关的

控制字段

000

00

---

001

01

010

2

10

TMUXR4[2:0]

011

11

101

111

注:

读操作

表 4. RCMD[4:0] 位

RCMD[4:2]

100

RCMD[1:0]

无效

命令 1

命令

保留

保留

无效

IADC2-IADC3

IADC4-IADC5

IADC6-IADC7

TMUXRn

TMUXR2[2:0]

TMUXR6[2:0]

无效

110

保留

保留

1. 只有两个 RCMD[4:2] (SFR 0xFC[4:2]) 码与常规工作有关,为

RCMD[4:2] = 001 和 010。000 和 101 吗无效,如果使用,将被忽略。

其余编码为保留,不得使用。

2. 对于 RCMD[1:0]控制字段,编码 01、10 和 11 有效,00 无效,不得使

用。

3. 与每个 TMUXRn[2:0]字段相关联的相(A、B 或 C)由 IADCn 输入引脚的

连接方式及电表设计决定。

表 5 所示为所允许的 RCMD[4:2]和 TMUXRn[2:0]数值组合、71M6xx3远端传感器返回的对应数据类型和格

式,并显示了数据如何储存至 RMT_RD[15:8]和 RMT_RD[7:0]。MPU 通过设置 RCMD[1:0]字段中的有效编

码,选择读取三相电中的一相,如表 4 所示。

.

表 5. 远程接口读命令

RCMD[4:2] TMUXRn[2:0]

001 00X

001 11X

010 00X

010 01X

010 10X

Notes:

1. TRIMT[7:0] 是 所有 71M6xx3 器件的 VREF 调整值。注意,TRIMT[7:0] 8 位 数 值由 RMT_RD[8] 和

RMT_RD[7:1]组成。TRIMT[7:0]

2. TRIMBGB[7:0]和 TRIMBGD[7:0]是用于 71M6113 (0.5%)和 71M6203 (0.1%)的过温调整值。TRIMBGB[7:0]的

相关公式和 TRIMBGD[7:0]的对应温度系数,请参考 71M6xxx 的数据资料。

3. 参见第 56 页的 2.5.6节

4. 参见第 57 页的 2.5.8节 71M6xx3 VCC 监测器。

TRIMT[7:0]

(熔丝寄存器,适用于全部

71M6xx3)

TRIMBGB[7:0] 和

TRIMBGD[7:0]

(71M6113 和 71M6203 附加熔丝

调节)

STEMP[10:0]

(检测的 71M6xx3 温度)

VSENSE[7:0]

(检测的 71M6xx3 供电电压)

VERSION[7:0]

(芯片版本)

71M6xx3温度传感器。

对应的

等式及温度系数,请参考 71M6xxx 数据资料。

RMT_RD [15:8] RMT_RD [7:0]

TRIMT[7]=RMT_RD[8] TRIMT[6:0]=RMT_RD[7:1]

TRIMBGB[7:0] TRIMBGD[7:0]

STEMP[10:8]=RMT_RD[10:8]

(RMT_RD[15:11] are sign extended)

全零

VERSION[7:0]

STEMP[7:0]

VSENSE[7:0]

全零

71M6543获取每个隔离传感器 71M6xx3 的硬件和相关信息,MPU 根据 71M6xx3 隔离传感器的温度特性实

现电能测量的温度补偿。详情参见 4.5 节计量温度补偿。

表 6 列出了用于控制外部 71M6xx3 隔离传感器的全部 I/O RAM 寄存器,详情参见 71M6xx3数据资料。

v1.2 © 2008–2011 Teridian Semiconductor Corporation 23

71M6543F/H和 71M6543G/GH数据资料 8

名称

地址

默认值

默认值

读/写

说明

向由

RMT_RD[15:8]

RMT_RD[7:0]

2602[7:0]

2603[7:0]

表 6. 用于远端传感器的 I/O RAM 控制位

RST

WAKE

MPU 向 RCMD 写非零值时,71M6543

RCMD[4:0]

SFR

FC[4:0]

0 0 R/W

RCMD[1:0]选中的相应远端传感器发出一条命令。

完成命令后,71M6543 清除 RCMD[4:2]。命令码

本身位于 RCMD[4:2]。

PERR_RD

PERR_WR

SFR FC[6]

SFR FC[5]

0 0 R/W

71M6543 将这些位置位,表示在远端传感器上检

测到奇偶校验错误。这些位一旦置位,则被记忆,

直到由 MPU 清除。

用于远端传感器的 CHOP。

00 – 自动斩波,每个复用帧变化。

CHOPR[1:0]

2709[7:6] 00 00 R/W

01 – 正

10 – 负

11 – 同 00

TMUXR2[2:0]

TMUXR4[2:0]

TMUXR6[2:0]

270A[2:0] 000 000 R/W TMUX 位,用于控制远端传感器。

270A[6:4] 000 000 R/W TMUX 位,用于控制远端传感器。

2709[2:0] 000 000 R/W TMUX位,用于控制远端传感器。

0 0 R

用于 71M6xx3 读操作的读缓冲器。

控制 71M6543 驱动 71M6xx3 电源脉冲的方式。置

RFLY_DIS

210C[3]

0 0 R/W

1,脉冲驱动为高或低电平;清 0,驱动至高电

平,后接一个开路反激间隔。

RMT2_E

RMT4_E

RMT6_E

2709[3] 0 0 R/W

2709[4] 0 0 R/W

2709[5] 0 0 R/W

使能隔离远程传感器,重新将引脚 IADC2-IADC3

配置为平衡线对的数字远程接口。

使能隔离远程传感器,重新将引脚 IADC4-IADC5

配置为平衡线对的数字远程接口。

使能隔离远程传感器,重新将引脚 IADC6-IADC7

配置为平衡线对的数字远程接口。

关于这些 I/O RAM 地址的详细信息,请参见从第 104 页开始的表 71。

24 © 2008-2010 MAXIM/TERIDIAN Semiconductor Corporation v1.2

71M6543F/H 和 71M6543G/GH数据资料

2.3 数字计算引擎(CE)

CE 是一个专用的 32 位数字信号处理器,用来执行电量计量所需的精确运算。CE运算和处理包括:

• 每个电流采样值与其对应电压采样值相乘,以获得每次采样的电能(与固定的采样时间相乘)。

• 对四个通道的非同步采样所产生的延迟进行算法补偿(不受频率影响)。

• 90°相移(用于无功计算)。

• 脉冲发生器。

• 输入信号频率监测(用于频率和相位信息)。

• 输入信号幅值监测(用于电压跌落检测)。

• 根据校准参数对采样进行缩放处理。

• 根据温度补偿信息对采样进行缩放处理。

2.3.1 CE程序存储器

CE 程序存储在程序存储器(FLASH)。CE 和 MPU 对 FLASH 的公共访问由存储器公用电路控制。每个 CE

指令为 2 字节长度。为 CE 程序分配的闪存空间不得超过 4096 个 16 位字(8KB)。CE 程序在复用器状态 0

开始启动。执行到 HALT 指令时,程序结束。为确保 CE 的正确运行,程序必须在复用周期结束之前执行

完毕。

CE 程序必须在闪存地址以 1KB 为边界处开始。71M6543F/H 的 I/O RAM 控制字段 CE_LCTN[6/5:0] (I/O

RAM 0x2109[6/5:0])和 71M6543G/GH的 CE_LCTN[6:0] (I/O RAM 0x2109 [6:0])定义哪个 1KB 边界为 CE 代

码的起始地址。所以,第一条 CE 指令位于 71M6543F/H 的 1024*CE_LCTN[5:0]和 71M6543G/GH 的

1024*CE_LCTN[6:0]。

2.3.2 CE数据存储器

CE 和 MPU 共用数据存储器(RAM)。CE 和 MPU 对 XRAM 的公共访问由存储器公用电路控制。CE 最多可

访问 3KB 数据 RAM (XRAM)中的全部 5KB,即从 RAM 地址 0x0000 至 0x0C00。

XRAM 可由 FIR 滤波器模块、RTM 电路、CE 和 MPU 访问。分别为 FIR 和 MPU 保留分配的时隙,以防止

CE 访问 XRAM 数据时发生总线冲突。

MPU 读、写 CE 和 MPU 之间共用的 XRAM 是两个处理器之间数据通信的主要途径。

CE 通过支持硬件实现计量运算、脉冲计数和累加。通过 I/O RAM 控制字段 EQU[2:0] (计量公式辅助字段,

I/O RAM 0x2106[7:5])、DIO_PV 位(I/O RAM 0x2457[6])、DIO_PW 位 (辅助脉冲计数,I/O RAM 0x2457[7])

和 SUM_SAMPS[12:0] (累积辅助,(I/O RAM 0x2107[4:0]和 0x2108[7:0])控制硬件。

使用标准 CE 代码时,每个能量输出的积分时间为 SUM_SAMPS[12:0]/2184.53 (MUX_DIV[3:0] = 7,I/O

RAM 0x2100[7:4]。完成累积时,CE 硬件触发 XFER_BUSY 中断。

2.3.3 CE与MPU通信

CE 向 MPU 输出 6 种中断信号:CE_BUSY、XFER_BUSY、XPULSE、YPULSE、WPULSE 和 VPULSE。

这些信号在芯片内部已连接至 MPU 中断服务。CE_BUSY 表示 CE 正在处理数据,该信号每个复用帧出现

一次。XFER_BUSY 表示 CE 正在更新 CE RAM 的输出区域,累积循环结束时产生中断。CE 执行 HALT

指令后,CE_BUSY 和 XFER_BUSY 自动清零。

XPULSE 和 YPULSE 也可配置成中断,监测电网电压跌落故障、过零和脉冲事件中断。此外,这些信号也

可直接输出至 DIO 引脚,CE 提供直接输出。这些信号对应的中断为上升沿触发。

v1.2 © 2008–2011 Teridian Semiconductor Corporation 25

71M6543F/H和 71M6543G/GH数据资料

说明

有功和无功计量公式

推荐的复用器序列

单元

单元

注:

CKTEST

RTM

FLAG

RTM DATA0 (32 bits)

LSB

SIGN

LSB

SIGN

RTM DATA1 (32 bits)

LSB

LSB

SIGN

SIGN

RTM DATA2 (32 bits)

RTM DATA3 (32 bits)

0 1

30 31

0 1

30 31

0 1

30 31

0 1

30 31

FLAG

FLAG

FLAG

MUX_STATE

S