Page 1

Page 2

HAN Pilot Platform

Hardware Manual

1 www.terasic.com

July 5, 2019

TABLE OF CONTENTS

Chapter 1 Overview ....................................................................................................................... 3

1.1 The Package Contents ................................................................................................................................ 4

1.2 HAN Pilot Platform System CD ................................................................................................................. 4

1.3 Getting Help ............................................................................................................................................... 4

Chapter 2 Board Components ........................................................................................................ 6

2.1 Components and Layout ............................................................................................................................. 6

2.2 Block Diagram ............................................................................................................................................ 9

Chapter 3 Board Settings and Status Component ........................................................................ 11

3.1 Board Setting Switches ............................................................................................................................. 11

3.2 Board Setting Headers .............................................................................................................................. 12

3.3 Status LED ................................................................................................................................................ 15

3.4 JTAG Interface ......................................................................................................................................... 17

Chapter 4 FPGA Fabric Components ........................................................................................... 19

4.1 User Interface (LED/7-SEG/Button/Switch) ............................................................................................ 19

4.2 USB Type-C Port ...................................................................................................................................... 21

4.3 SFP+ Connector........................................................................................................................................ 26

4.4 SATA ........................................................................................................................................................ 29

4.5 PCIe .......................................................................................................................................................... 32

4.6 DDR4 ........................................................................................................................................................ 34

4.7 HDMI Transmitter and Receiver .............................................................................................................. 43

4.8 Gigabit Ethernet ........................................................................................................................................ 45

4.9 FMC Connector ........................................................................................................................................ 46

4.10 Temperature Sensor, Fan Control and Power Monitor ........................................................................... 54

4.11 Gyroscope, Accelerometer and Magnetometer ....................................................................................... 55

Chapter 5 HPS Fabric Components ............................................................................................. 57

5.1 User Push-buttons and LEDs .................................................................................................................... 57

Page 3

HAN Pilot Platform

Hardware Manual

2 www.terasic.com

July 5, 2019

5.2 Gigabit Ethernet ........................................................................................................................................ 57

5.3 UART to USB ........................................................................................................................................... 59

5.4 Micro SD Card Socket .............................................................................................................................. 60

5.5 USB OTG ................................................................................................................................................. 60

5.6 GPIO Header ............................................................................................................................................ 61

5.7 DDR4 (HPS) ............................................................................................................................................. 62

Chapter 6 System Clocks ............................................................................................................. 67

Chapter 7 Power .......................................................................................................................... 69

Chapter 8 HAN Pilot Platform System Builder .............................................................................. 70

8.1 Introduction .............................................................................................................................................. 70

8.2 General Design Flow ................................................................................................................................ 70

8.3 Using HAN Pilot Platform System Builder .............................................................................................. 71

Chapter 9 Appendix ..................................................................................................................... 79

Page 4

HAN Pilot Platform

Hardware Manual

3 www.terasic.com

July 5, 2019

Chapter 1

Overview

The HAN Pilot Platform provides users a combination of ARM software and FPGA hardware

development platforms. It has a vast memory device and peripherals on the hardware. This kit also

includes resourceful reference designs to help users to accomplish their design needs. The hardware

offers in the HAN Pilot Platform has the maximum capacity with 660K LEs in Arria 10 SoC FPGA

and featuring various types of high-speed image interface such as: HDMI, Display Port, and

12G-SDI and a large capacity of DDR4 memory. The board’s high speed network interface, Gigabit

Ethernet and SFP+10GbE, provides hardware resources for network communications related

applications.

The HPS can be reboot with any of these three removable daughter cards: MicroSD Card, Nand

Flash, and QSPI Flash. The FPGA on the main board can be connected to DDR4-SODIMM Socket

in addition to the DDR4 memory module. The FPGA on the main board can also be connected to

the Terasic QDR Memory Module as well. Beside the DDR4 memory module, you can also directly

connect to the FPGA on the main board via the High Pin Count FMC expansion port to expand

variety of functions.

The PCIe Gen3 x4 Connector interface comes with the Terasic PCA PCIe and PCIe Cable, which

can be used to connect the Host PC to allow data between the FPGA and the Host PC. The USB

Type-C interface on the motherboard allows the motherboard to obtain power for the host PC. The

Host PC displays information and images through the high-speed transmission USB 3.0 or the

Display Port.

Page 5

HAN Pilot Platform

Hardware Manual

4 www.terasic.com

July 5, 2019

11..1

1

TThhee PPaacckkaaggee CCoonntteennttss

Figure 1-1 Package Contents

1. HAN Pilot Platform Kit

2. MicroSD Card (Installed) and Card Reader

3. Fan (Installed)

4. Two Type A to Mini-B USB Cables

5. 12V DC Power Supply (Installed)

6. AC Power Cord (USA)

7. One 4GB DDR4 ECC SO-DIMM Module (Installed)

8. Screws, Copper Stands, and Silicon Footstands

11..2

2

HHAANN PPiilloott PPllaattffoorrmm SSyysstteemm CCDD

The HAN Pilot Platform System CD contains all the documents and supporting materials associated

with HAN Pilot Platform, including the user manual, system builder, reference designs and device

datasheets.

Users can download this system CD from the link: http://HAN Pilot Platform.terasic.com/cd.

11..3

3

GGeettttiinngg HHeellpp

Here are the addresses where you can get help if you encounter any problems:

▪ Terasic Technologies

▪ 9F., No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, 30070. Taiwan

▪ Email: support@terasic.com

Page 6

HAN Pilot Platform

Hardware Manual

5 www.terasic.com

July 5, 2019

▪ Tel.: +886-3-575-0880

▪ Website: HAN Pilot Platform.terasic.com

Page 7

HAN Pilot Platform

Hardware Manual

6 www.terasic.com

July 5, 2019

Chapter 2

Board Components

This chapter provides an introduction to the features and design characteristics of the board.

22..1

1

CCoommppoonneennttss aanndd LLaayyoouutt

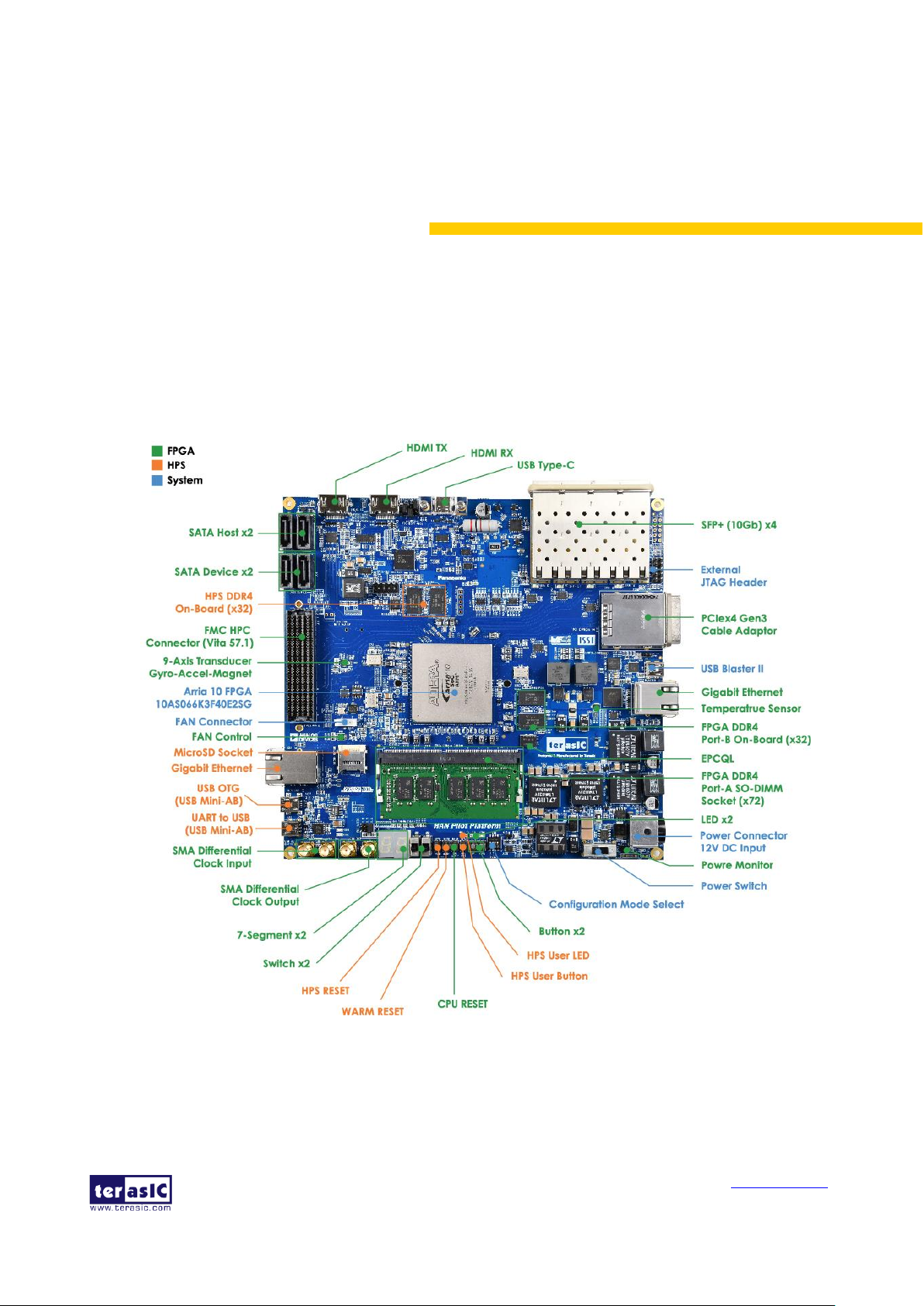

Figure 2-1 and Figure 2-2 shows a photograph of the board. It depicts the layout of the board and

indicates the location of the connectors and key components.

Figure 2-1 HAN Pilot Platform (top view)

Page 8

HAN Pilot Platform

Hardware Manual

7 www.terasic.com

July 5, 2019

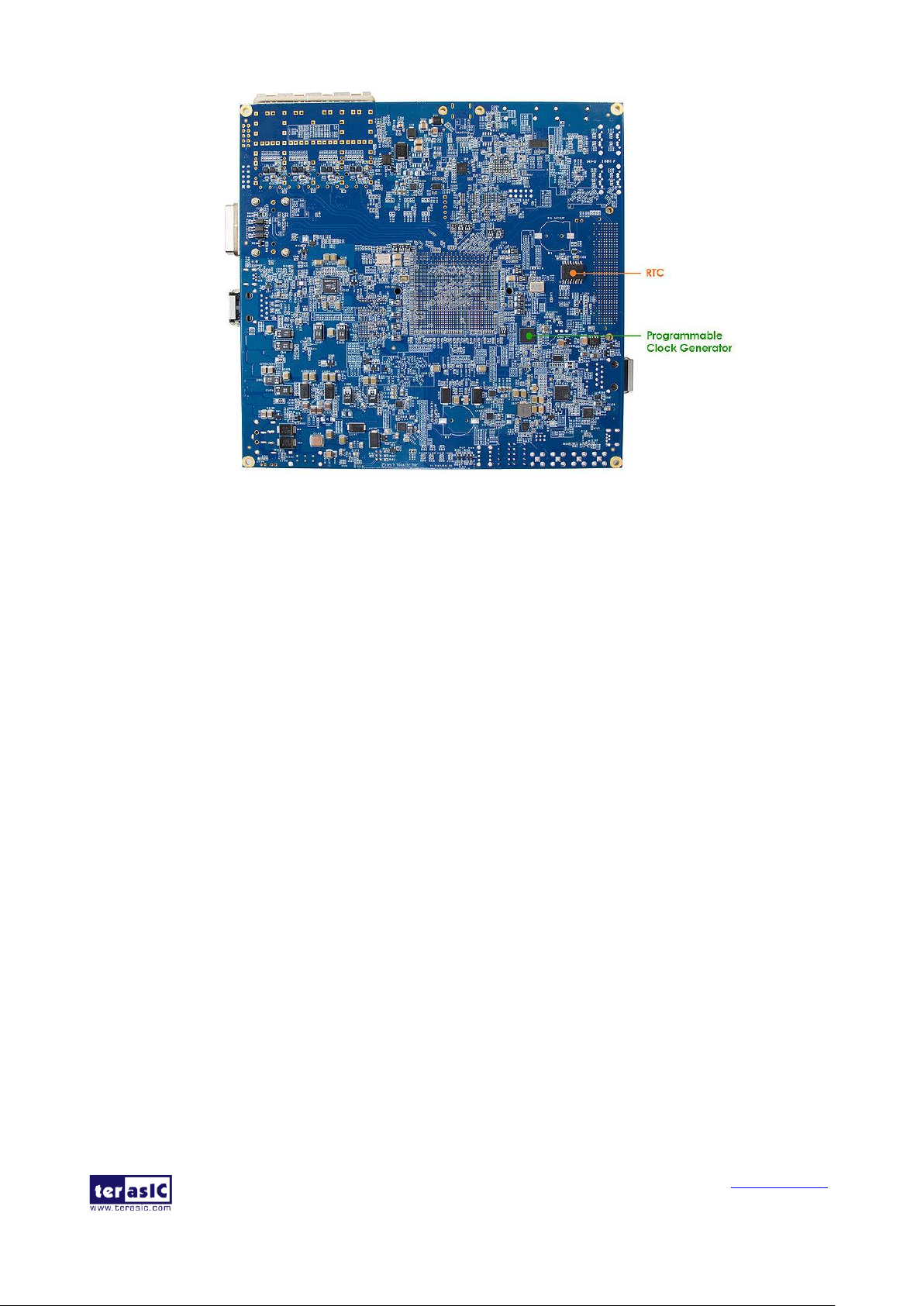

Figure 2-2 HAN Pilot Platform (bottom view)

The HAN Pilot Platform has many features that allow users to implement a wide range of designed

circuits, from simple circuits to various multimedia projects.

The following hardware are provided on the board:

◼ FPGA Device

• Intel ® Arria10® SoC 10AS066K3F40E2SG device (660K LEs)

• USB-Blaster II onboard for programming; JTAG Mode

• Serial configuration device – EPCQL1024

• One DDR4 SO-DIMM Socket, support ECC

• On-board 1GB DDR4-2400, 32-bit data width

• USB Type-C Interface

• Power Delivery

• DisplayPort TX/RX with 4 lanes

• USB 3.0/2.0

• HDMI TX/RX 2.0 for 4K2K@60- FPGA Transceiver

• PCIe Cabling Socket at Gen3 x4

Page 9

HAN Pilot Platform

Hardware Manual

8 www.terasic.com

July 5, 2019

• SFP+ Socket x4, 40Gbps

• SATA 3.0 Host and SATA Device x2 (SATA Connector x4)

• One Gigabit Ethernet Port

• SMA Clock-In and Clock-Out

• High Pin Count FMC Connector. Support VADJ 1.2V/1.5V/1.8V.

• Accelerometer, Gyroscope and Magnetometer

• Temperature Sensor

• Fan Control

• LED x2, KEY x2, Switch x2, 7-Segment x2

◼ HPS (Hard Processor System)

• 1.5GHz Dual-core ARM Cortex-A9 processor

• Boost Flash Slot:

• 1024 Mb QSPI Flash

• Nand Flash

• MicroSD Socket

• On-board 1GB DDR4-2400, 32-bit data width

• 1 Gigabit Ethernet PHY with RJ45 connector

• USB OTG Port, USB mini-AB connector

• UART to USB, USB Mini-B connector

• RTC

• One user button and one user LED

• Warm reset button and cold reset button

Page 10

HAN Pilot Platform

Hardware Manual

9 www.terasic.com

July 5, 2019

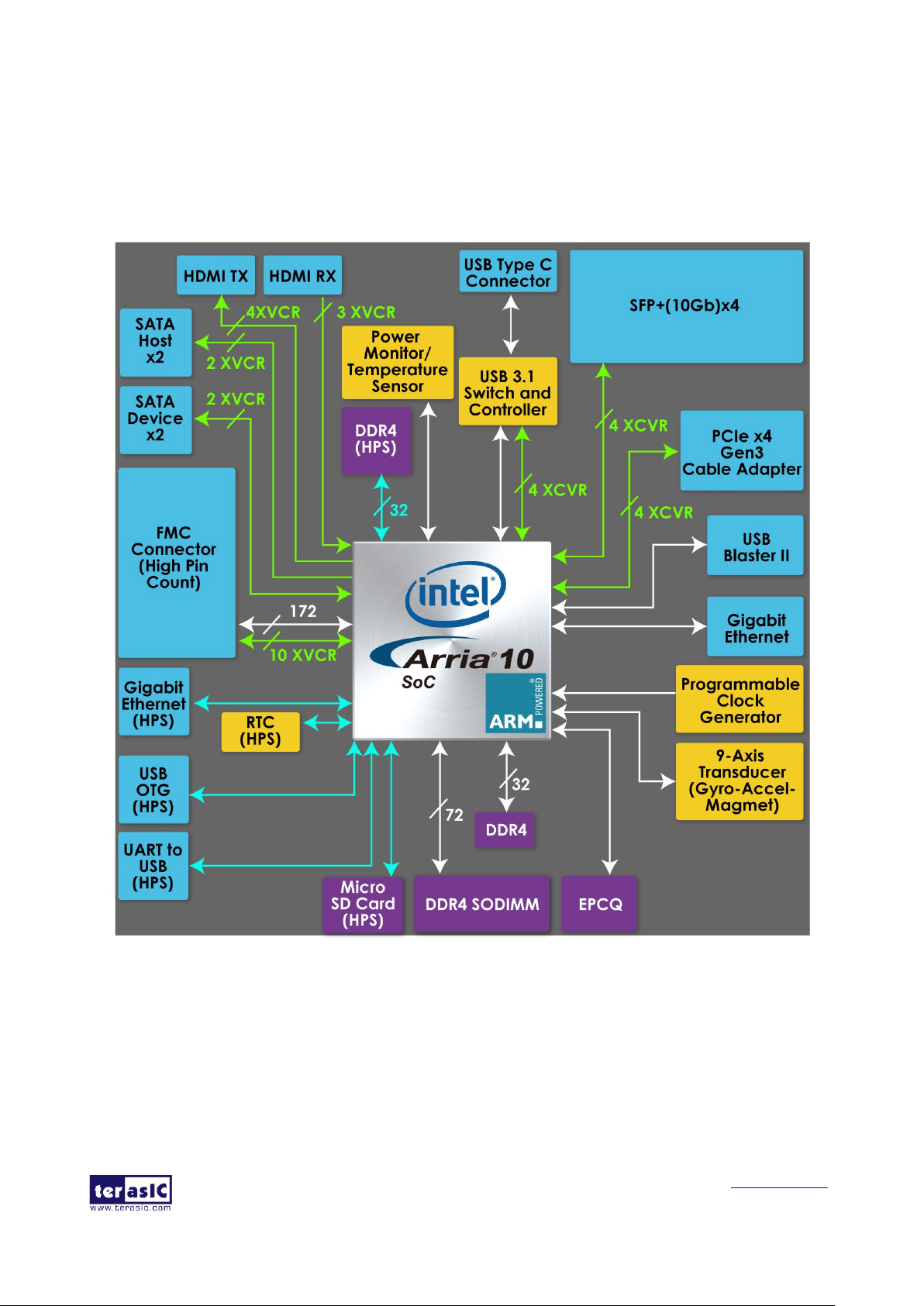

2.2 Block Diagram

Figure 2-3 is the block diagram of the board. All the connections are established through the Arria

10 SoC FPGA device to provide maximum flexibility for users. Users can configure the FPGA to

implement any system design.

Detailed information about Figure 2-3 are listed below.

▪ Arria 10 SoC 10AS066K3F40E2SG/10AS057K3F40E2SG FPGA

▪ Dual-core ARM Cortex-A9 (HPS)

▪ 660K programmable logic elements

▪ 42,660 Kbits embedded memory

▪ Hard memory controllers x5

▪ Transceivers x48(17.4 Gbps)

▪ 18-bit x 19-bit multipliers x3,356

▪ Accelerometer & Gyroscope Device MPU9250

▪ Configuration

▪ EPCQ1024L Serial Configuration Device

▪ Onboard USB-Blaster II (Mini-B USB connector)

▪ Memory Device

▪ On-board 1GB DDR4-2400, 32-bit data width

▪ Two DDR4 SO-DIMM SDRAM socket

▪ Micro SD card socket

▪ Communication

▪ USB OTG (Mini-AB USB connector)

▪ UART-to-USB (Mini-B USB Connector)

▪ Giga Ethernet x2

▪ PCIe Gen3 x4 Cabling Socket

▪ Expansion Ports

▪ FMC connector

▪ one HPC (high-pin count) FMC connector with xcvr

▪ Adjustable VADJ:1.2V/1.5V/1.8V

▪ Multimedia Interface

▪ HDMI TX and RX ports

▪ Clock

▪ Two SMA connectors for SMA Clock-In and Clock-Out

▪ On-board PLLs

▪ General user input/output

▪ Buttons x3 (FPGA x2, HPS x1)

▪ Switches x2 on FPGA

▪ LEDs x3 (FPGA x2, HPS x1)

▪ 7-segment displays x2

▪ System Monitor and Control

▪ Temperature Sensor on FPGA

▪ 12V Power Monitor

Page 11

HAN Pilot Platform

Hardware Manual

10

www.terasic.com

July 5, 2019

▪ Power Controller

▪ I2C Fan Control

▪ Power

▪ 12V DC input

Figure 2-3 Block diagram of HAN Pilot Platform

Page 12

HAN Pilot Platform

Hardware Manual

11

www.terasic.com

July 5, 2019

Chapter 3

Board Settings and Status

Component

This chapter describes all the setting devices on HAN Pilot Platform board and their functions, such

as Switches and Headers. We also will describe the function of some status LEDs. The JTAG

interface will be described at the end of this chapter.

33..1

1

BBooaarrdd SSeettttiinngg SSwwiittcchheess

◼ Mode Select Switches

Mode Select Switch (SW5) is used to set the HAN Pilot Platform FPGA MSEL pin value. These

MSEL pins determined the Configuration Mode of the FPGA. Table 3-1 list the MSEL setting for

configuration scheme of FPGA, when MSEL is set to AS mode (Factory default setting), FPGA will

be booted from EPCQ device (See Figure 3-1). When MSEL is set to FPP mode (See Figure 3-2),

FPGA can be configured by HPS Fabric (From Micro SD Card).

Table 3-1 MSEL setting for configuration scheme of FPGA

Configuration Scheme

SW5 MSEL[2..0] Setting

Description

AS Mode (Factory Default)

010

FPGA boot from EPCQ

FPP Mode

000

FPGA boot from Micro SD Card

Page 13

HAN Pilot Platform

Hardware Manual

12

www.terasic.com

July 5, 2019

Figure 3-1 The AS mode setting of SW5

Figure 3-2 The FPP mode setting of SW5

33..2

2

BBooaarrdd SSeettttiinngg HHeeaaddeerrss

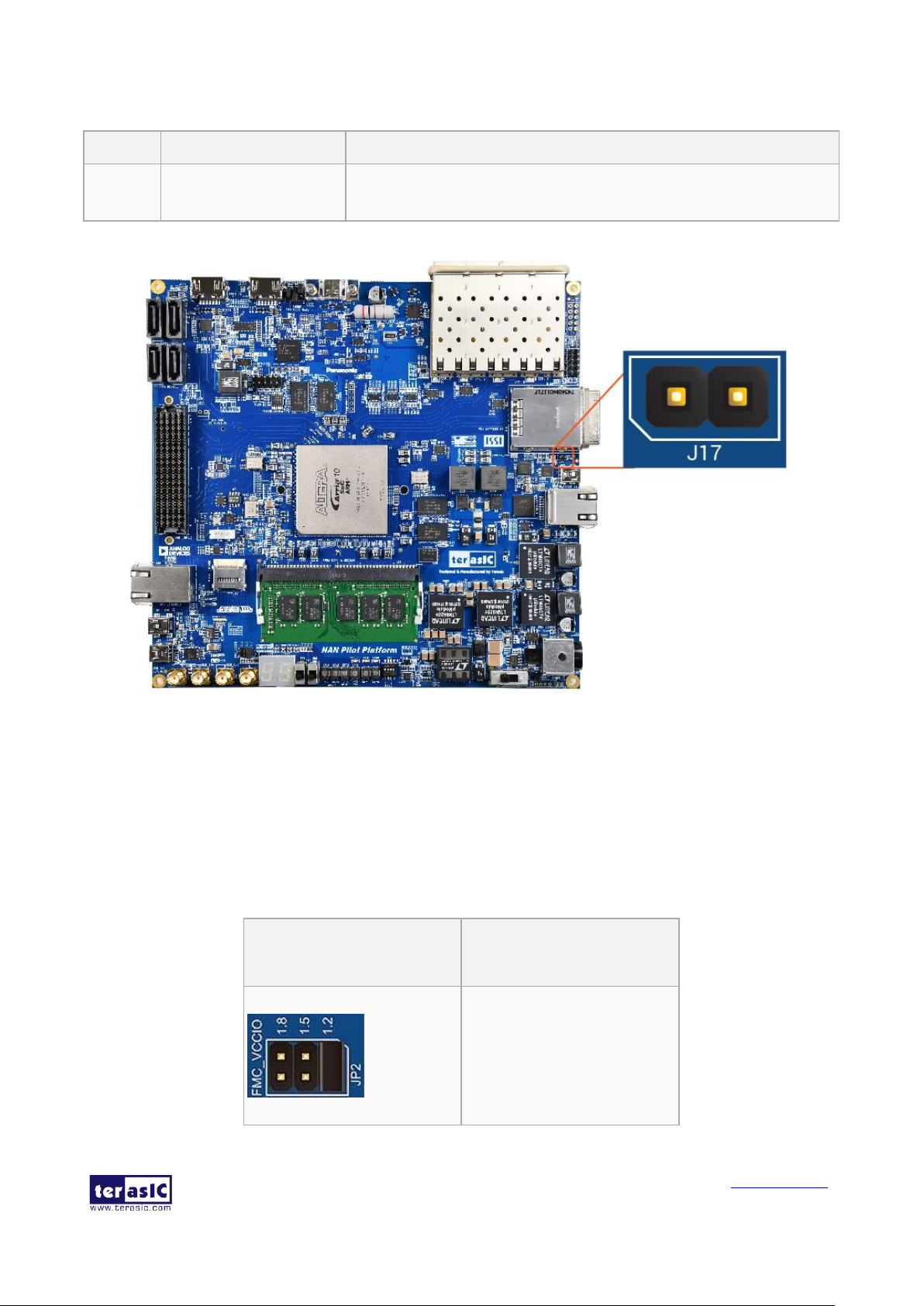

◼ JTAG Interface Header

J17 is the header used to set the JTAG bus of FMC connector connect to JTAG interface of HAN

Pilot Platform system. The FMC connector will not be included in the JTAG chain if the headers are

set to open (See Figure 3-3). Table 3-2 list the setting of the J17 header.

Page 14

HAN Pilot Platform

Hardware Manual

13

www.terasic.com

July 5, 2019

Table 3-2 JTAG Interface Headers Setting

Header

Setting

Descriptions

J17

Open (Default Setting)

Disable the JTAG interface of the FMC connector into the JTAG

chain

Figure 3-3 The FMC JTAG Header

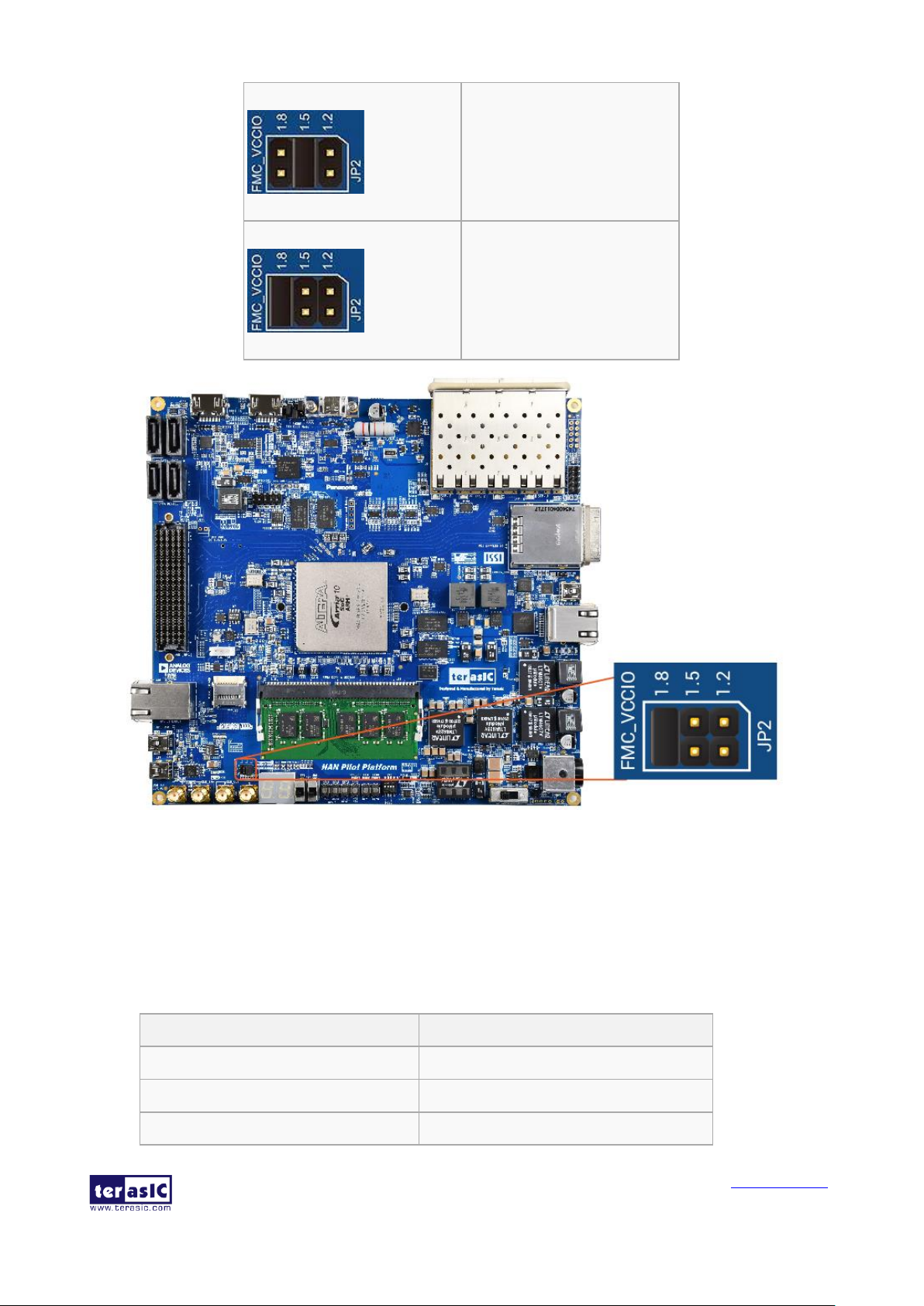

◼ FMC_VCCIO Select Header

JP2 is used to set the VCCIO voltage of FPGA I/O on FMC connector, as 1.2V/1.5V/1.8V are

supported, the FMC connector can support various I/0 standard FMC daughtercards. Table 3-3 list

the FMC_VCCIO Headers Setting.

Table 3-3 FMC_VCCIO Headers Setting

JP2 Setting

FMC VCCIO Voltage

1.2V

Page 15

HAN Pilot Platform

Hardware Manual

14

www.terasic.com

July 5, 2019

1.5V

1.8V (Default Setting)

Figure 3-4 The FMC VCCIO select header

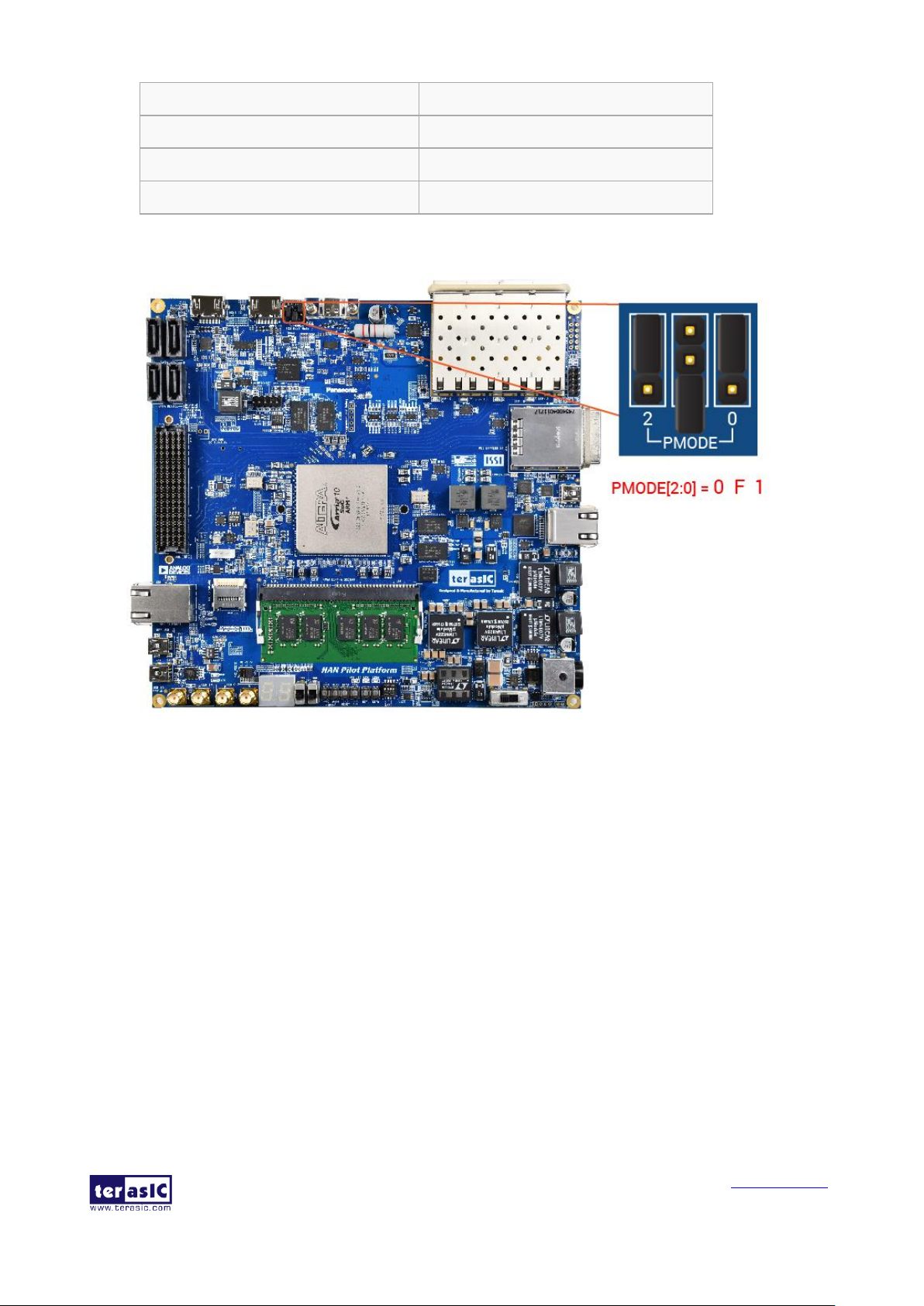

◼ PMODE Select Header

The USB 3.0 Controller (Cypress FX3) on the HAN Pilot Platform can be booted from the

different sources, selected by the configuration of the PMODE header (JP4/JP5/JP6) on HAN

Pilot Platform. Table 3-4 shows the boot options and associated settings. The default boot device

is the from a serial flash via SPI interface.

Table 3-4 PMODE Headers Setting

PMODE [2:0] (JP6/JP5/JP4) Setting

Boot Source

F00

Sync ADMux (16-bit)

F01

Async ADMux (16-bit)

F11

USB boot

Page 16

HAN Pilot Platform

Hardware Manual

15

www.terasic.com

July 5, 2019

F0F

Async SRAM (16-bit)

F1F

I2C, On Failure, USB Boot is Enabled

1FF

I2C only

0F1(Default)

SPI, On Failure, USB Boot is Enabled

◼ Note: F indicates Floating

Figure 3-5 The PMODE select header

33..3

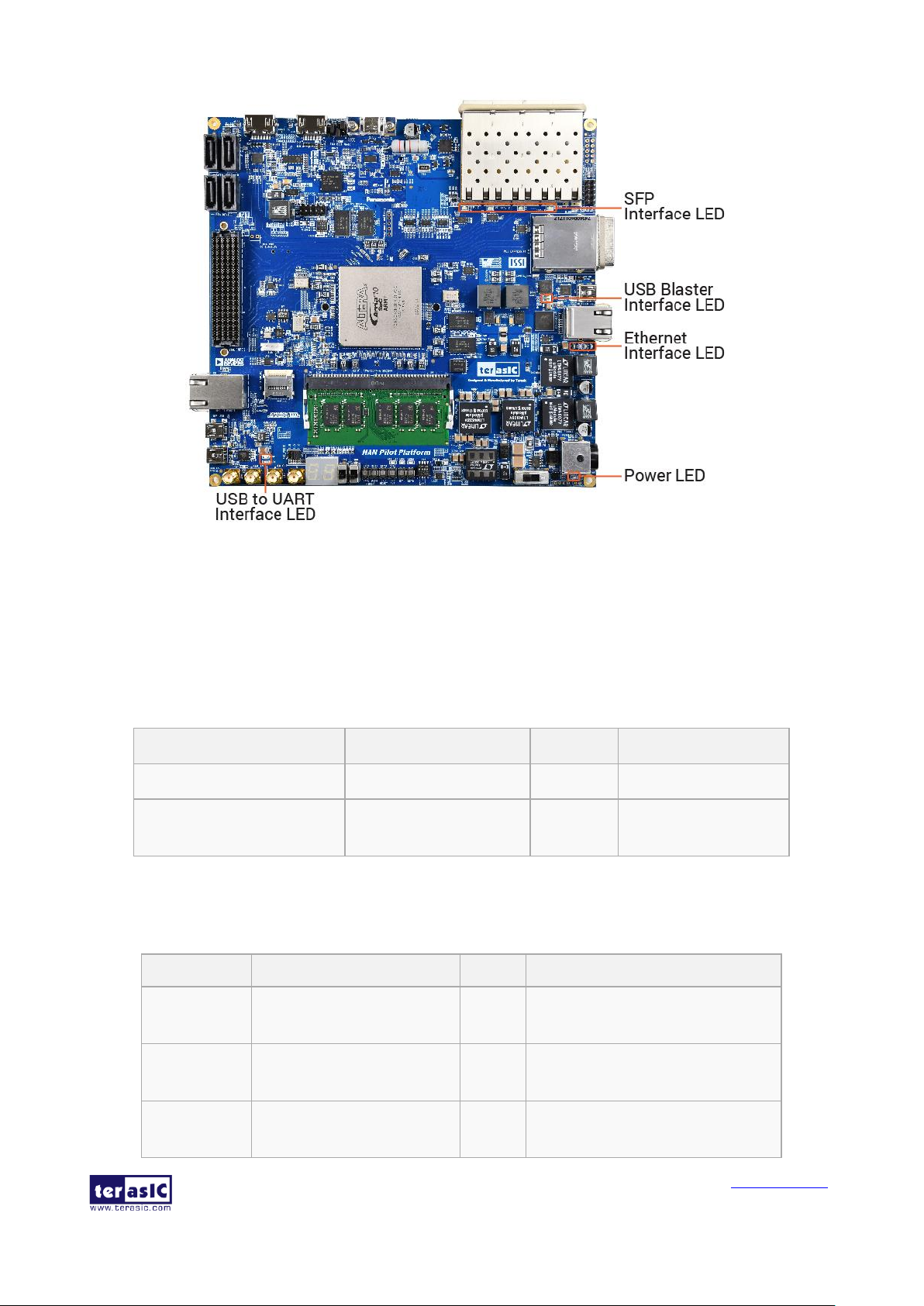

3

SSttaattuuss LLEEDD

This section describes the all status LED for the interfaces on HAN Pilot Platform board. Figure

3-6 shows all the status LED on the HAN Pilot Platform. Following are the detailed descriptions of

these interface LED.

Page 17

HAN Pilot Platform

Hardware Manual

16

www.terasic.com

July 5, 2019

Figure 3-6 The status LED on the HAN Pilot Platform board

◼ UART Interface

Table 3-5 list the two status LEDs for UART interface.

Table 3-5 Status LED for UART Interface

Component

Reference

Status

Descriptions

TXD1

UART_TXD

ON

Transmitting

RXD1

UART_RXD

ON

Receiving

◼ SFP Interface

Table 3-6 list the four status LEDs for SFP interface.

Table 3-6 Indicator LED for SFP Interface

Component

Reference

Status

Descriptions

D4

SFPA_MOD0_PRSNT_n

ON

Indicate that the SFP module is

present on the SFPA

D3

SFPB_MOD0_PRSNT_n

ON

Indicate that the SFP module is

present on the SFPB

D2

SFPC_MOD0_PRSNT_n

ON

Indicate that the SFP module is

present on the SFPC

Page 18

HAN Pilot Platform

Hardware Manual

17

www.terasic.com

July 5, 2019

D1

SFPD_MOD0_PRSNT_n

ON

Indicate that the SFP module is

present on the SFPD

◼ Ethernet Interface

Table 3-7 list the four status LEDs for Ethernet interface.

Table 3-7 Status LED for Ethernet Interface

Component

Reference

Status

Descriptions

D8

ETH_LED_TX

ON

Transmitting

D9

ETH_LED_RX

ON

Receiving

D10

ETH_LINK1000

ON

1000Mbps Link UP

D11

ETH_LINK100

ON

100Mbps Link UP

◼ Power

Table 3-8 list the two status LEDs for power.

Table 3-8 Status LED for Power

Component

Reference

Status

Descriptions

D31

12V~20V Power Indicator

ON

Illuminates when 12V~20V Power Supply is active

◼ USB Blaster

Table 3-9 list the two status LEDs for USB Blaster interface.

Table 3-9 Status LED for USB Blaster Interface

Component

Reference

Status

Descriptions

D5

JTAG_TX

ON

Illuminates when JTAG interface is transmitting data

D6

JTAG_RX

ON

Illuminates when JTAG interface is receiving data

33..4

4

JJTTAAGG IInntteerrffaaccee

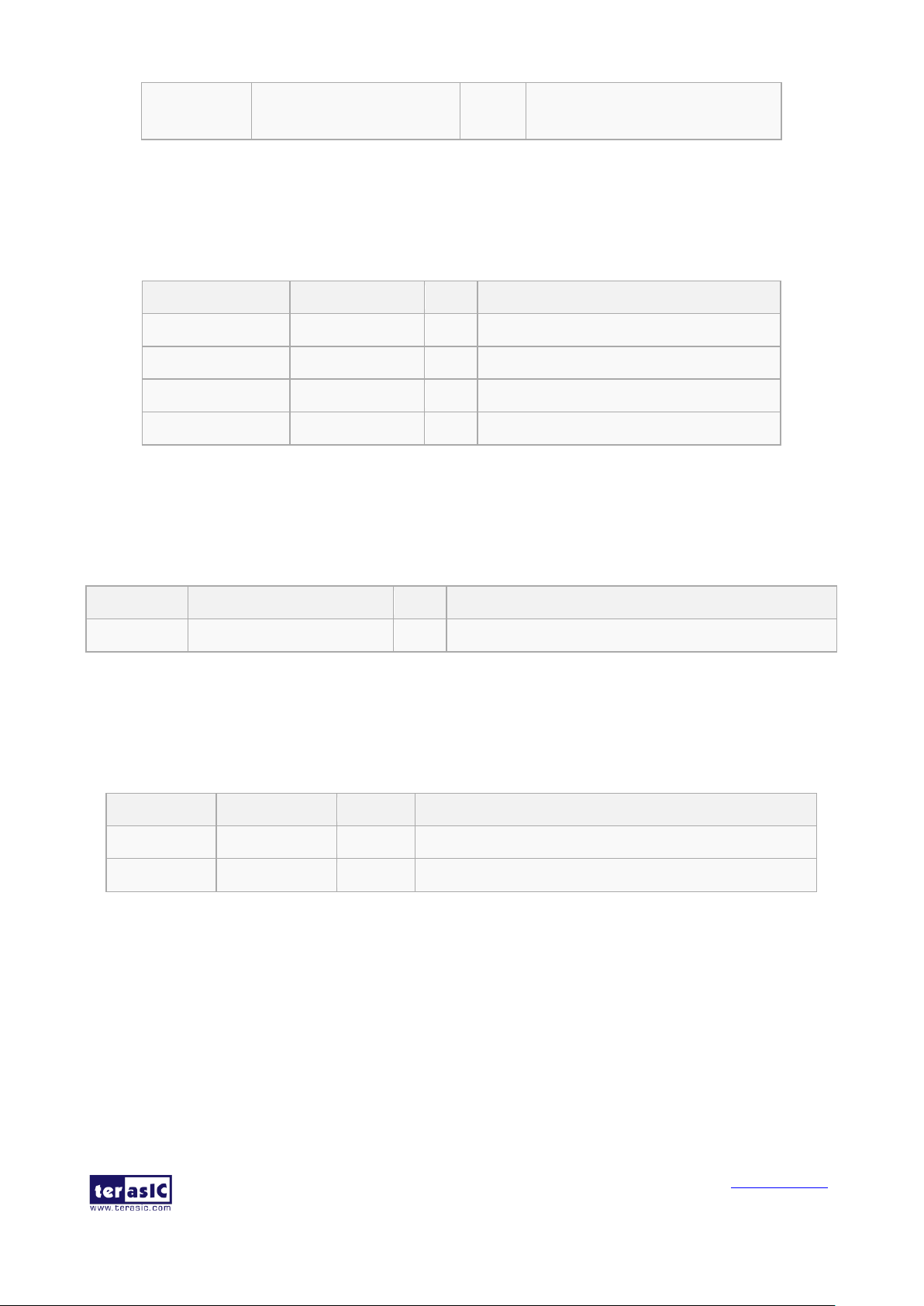

Figure 3-7 shows the JTAG interface of HAN Pilot Platform. Users can access to the JTAG

interface through the USB Blaster II circuit or connect external blaster to external blaster header. All

the devices which implement JTAG are connect to MAX II device, and switch via MAX II internal

switch logic. By using headers J17, users can include FMC connector JTAG interface in the HAN

Pilot Platform JTAG Chain, or exclude them from the JTAG Chain. The default JTAG path for

HAN Pilot Platform is: USB Blaster II ==> HPS ==> FPGA ==> (Bypass FMC connector) ==>

USB Blaster II. When the External JTAG connector is connected to the external blaster, the On

board's USB blaster II function will be replaced by the external blaster.

Page 19

HAN Pilot Platform

Hardware Manual

18

www.terasic.com

July 5, 2019

Figure 3-7 JTAG interface of HAN Pilot Platform

Page 20

HAN Pilot Platform

Hardware Manual

19

www.terasic.com

July 5, 2019

Chapter 4

FPGA Fabric Components

44..1

1

UUsseerr IInntteerrffaaccee ((LLEEDD//77--SSEEGG//BBuuttttoonn//SSwwiittcchh))

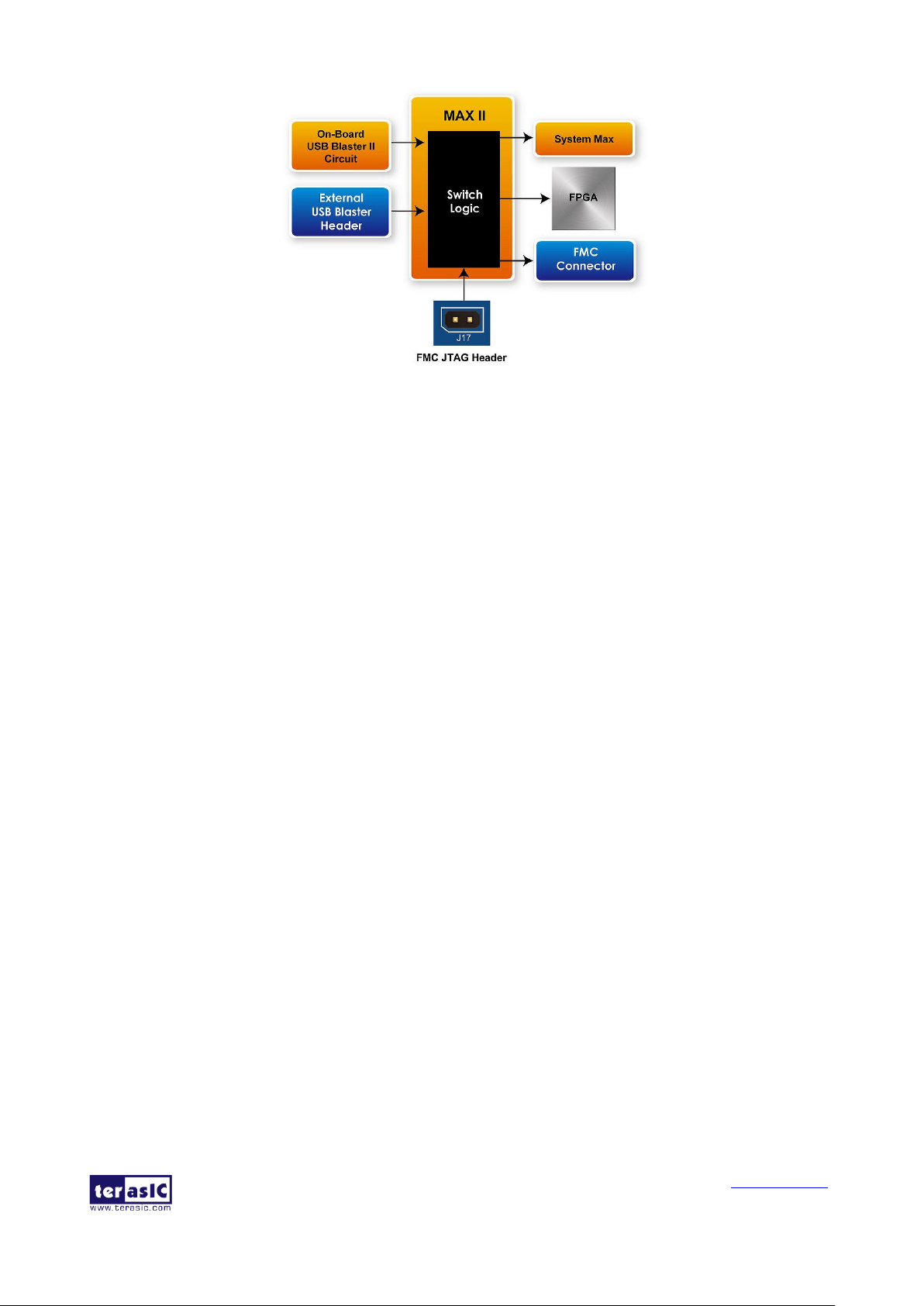

The board has two push-buttons connected to the FPGA, as shown in Figure 4-1. The two

push-buttons named KEY0 and KEY1 are connected directly to the Arria 10 SoC FPGA. Table 4-1

list the pin assignment of user push-buttons.

Figure 4-1 Connections between the push-buttons and the Arria 10 SoC FPGA

Table 4-1 Pin Assignment of Push-buttons

Signal Name

FPGA Pin Number

Description

I/O Standard

KEY[0]

PIN_AU15

Push-button[0]

1.8V

KEY[1]

PIN_AT15

Push-button[1]

1.8V

CPU_RESET_n

PIN_AN18

CPU_RESET button

1.8V

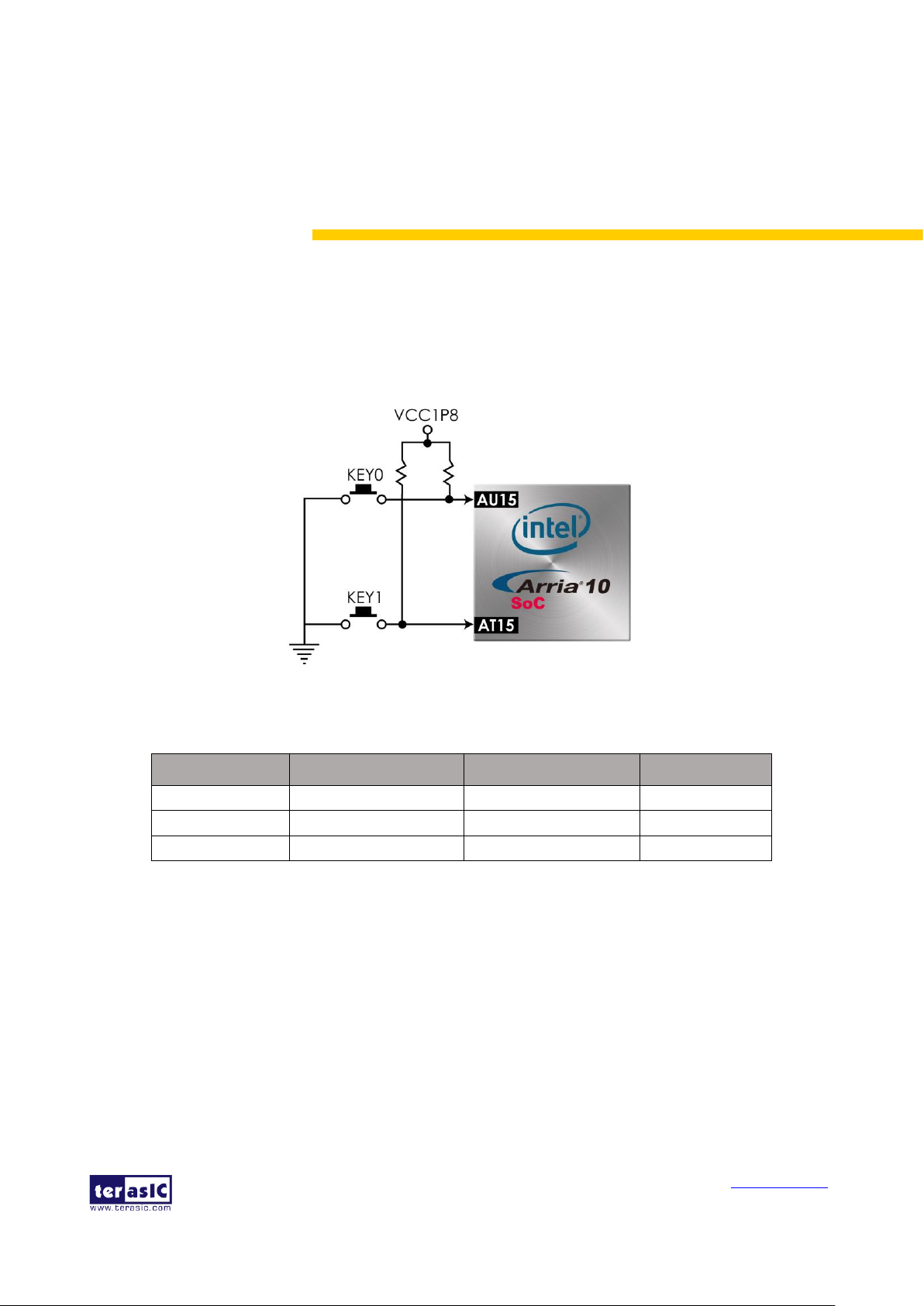

There are two slide switches connected to the FPGA, as shown in Figure 4-2. These switches are

not debounced and to be used as level-sensitive data inputs to a circuit. Each switch is connected

directly and individually to the FPGA. When the switch is set to the DOWN position (towards the

edge of the board), it generates a low logic level to the FPGA. When the switch is set to the UP

position, a high logic level is generated to the FPGA. Table 4-2 list the pin assignment of switches.

Page 21

HAN Pilot Platform

Hardware Manual

20

www.terasic.com

July 5, 2019

Figure 4-2 Connections between the switches and the Arria 10 SoC FPGA

Table 4-2 Pin Assignment of Switches

Signal Name

FPGA Pin Number

Description

I/O Standard

SW[0]

PIN_AJ19

Slide Switch[0]

1.8 V

SW[1]

PIN_AV16

Slide Switch[1]

1.8 V

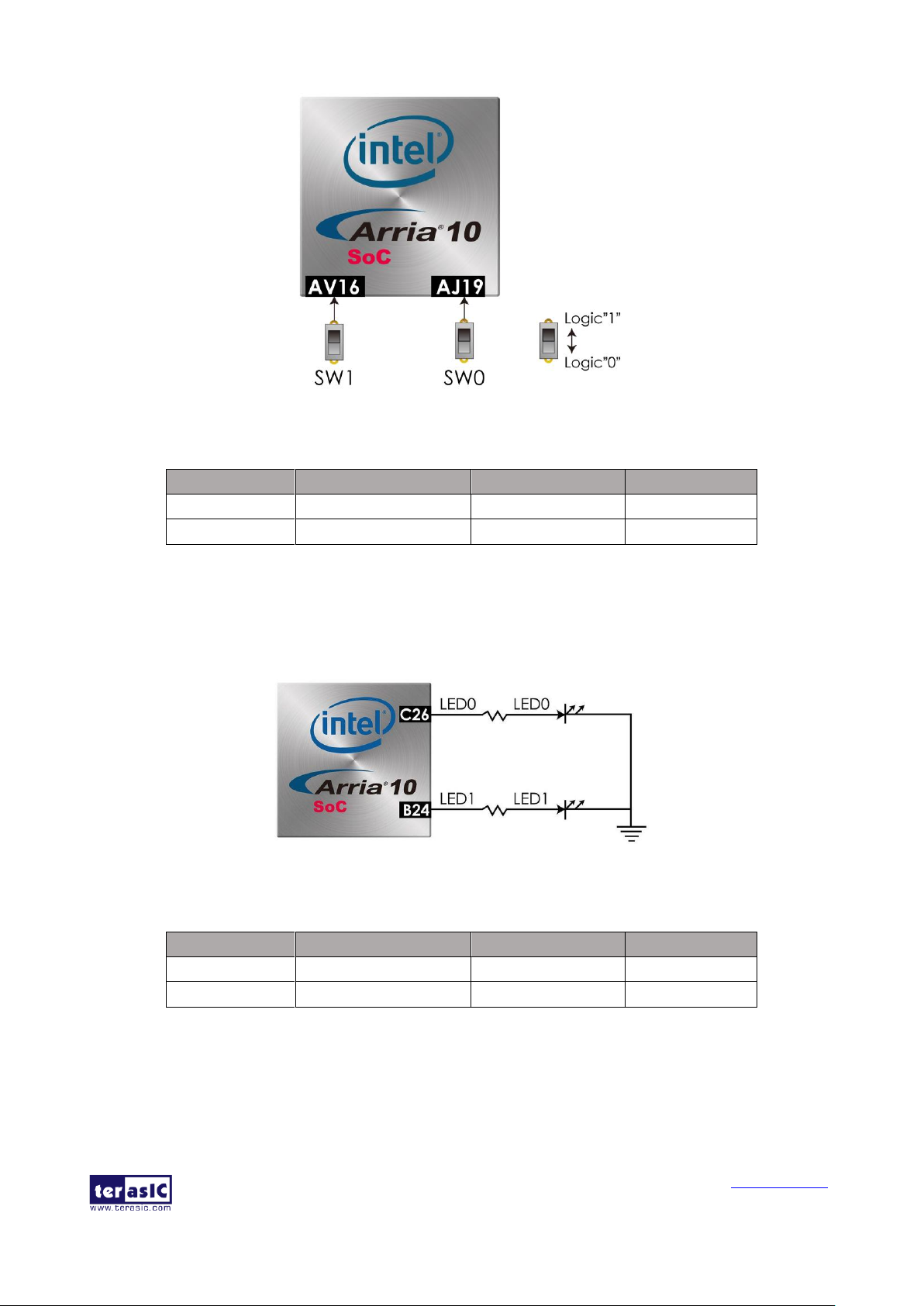

There are also two user-controllable LEDs connected to the FPGA. Each LED is driven directly and

individually by the Arria 10 SoC FPGA; driving its associated pin to a high logic level or low level

to turn the LED on or off, respectively. Figure 4-3 shows the connections between LEDs and Arria

10 SoC FPGA. Table 4-3 list the pin assignment of LEDs.

Figure 4-3 Connections between the LEDs and the Arria 10 SoC FPGA

Table 4-3 Pin Assignment of LEDs

Signal Name

FPGA Pin Number

Description

I/O Standard

LEDG[0]

PIN_C26

LED [0]

1.8 V

LEDG[1]

PIN_B24

LED [1]

1.8 V

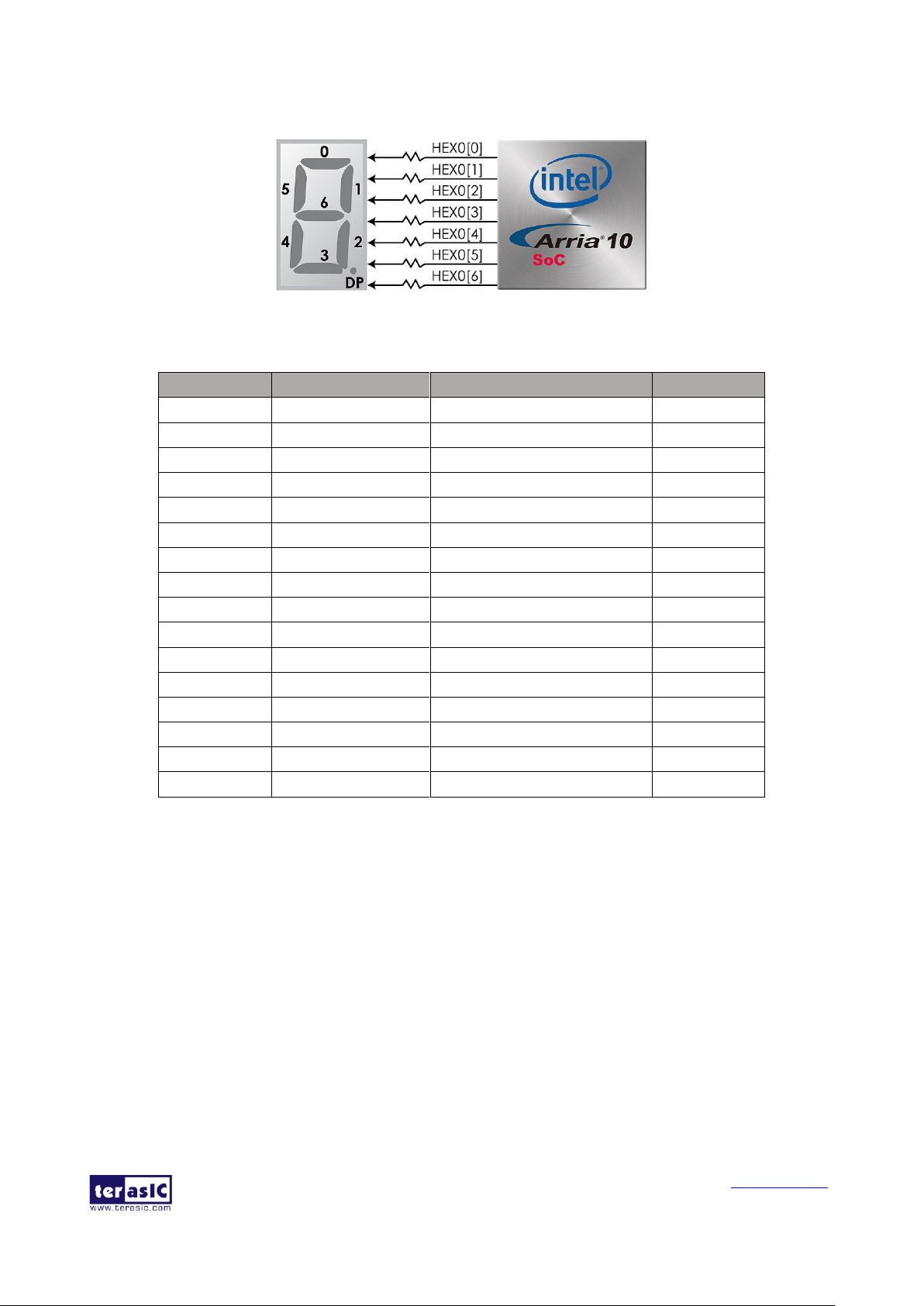

The DE10-Advanced board has two 7-segment displays. These displays are paired to display

numbers in various sizes. Figure 4-4 shows the connection of seven segments (common anode) to

pins on Arria 10 SoC FPGA. The segment can be turned on or off by applying a low logic level or

high logic level from the FPGA, respectively. Each segment in a display is indexed from 0 to 6,

Page 22

HAN Pilot Platform

Hardware Manual

21

www.terasic.com

July 5, 2019

with corresponding positions given in Figure 4-4. Table 4-4 shows the pin assignment of FPGA to

the 7-segment displays.

Figure 4-4 Connections between the 7-segment and the Arria 10 SoC FPGA

Table 4-4 Pin Assignment of 7-segment

Signal Name

FPGA Pin Number

Description

I/O Standard

HEX0[0]

PIN_AT32

Seven Segment Digit 0[0]

1.8V

HEX0[1]

PIN_AR32

Seven Segment Digit 0[1]

1.8V

HEX0[2]

PIN_AU32

Seven Segment Digit 0[2]

1.8V

HEX0[3]

PIN_AU30

Seven Segment Digit 0[3]

1.8V

HEX0[4]

PIN_AT30

Seven Segment Digit 0[4]

1.8V

HEX0[5]

PIN_AU29

Seven Segment Digit 0[5]

1.8V

HEX0[6]

PIN_AV29

Seven Segment Digit 0[6]

1.8V

HEX0_DP

PIN_AU31

Seven Segment Digit 0_DP

1.8V

HEX1[0]

PIN_AT28

Seven Segment Digit 1[0]

1.8V

HEX1[1]

PIN_AT29

Seven Segment Digit 1[1]

1.8V

HEX1[2]

PIN_AR30

Seven Segment Digit 1[2]

1.8V

HEX1[3]

PIN_AM27

Seven Segment Digit 1[3]

1.8V

HEX1[4]

PIN_AL27

Seven Segment Digit 1[4]

1.8V

HEX1[5]

PIN_AK27

Seven Segment Digit 1[5]

1.8V

HEX1[6]

PIN_AM26

Seven Segment Digit 1[6]

1.8V

HEX1_DP

PIN_AR31

Seven Segment Digit 1_DP

1.8V

44..2

2

UUSSBB TTyyppee--CC PPoorrtt

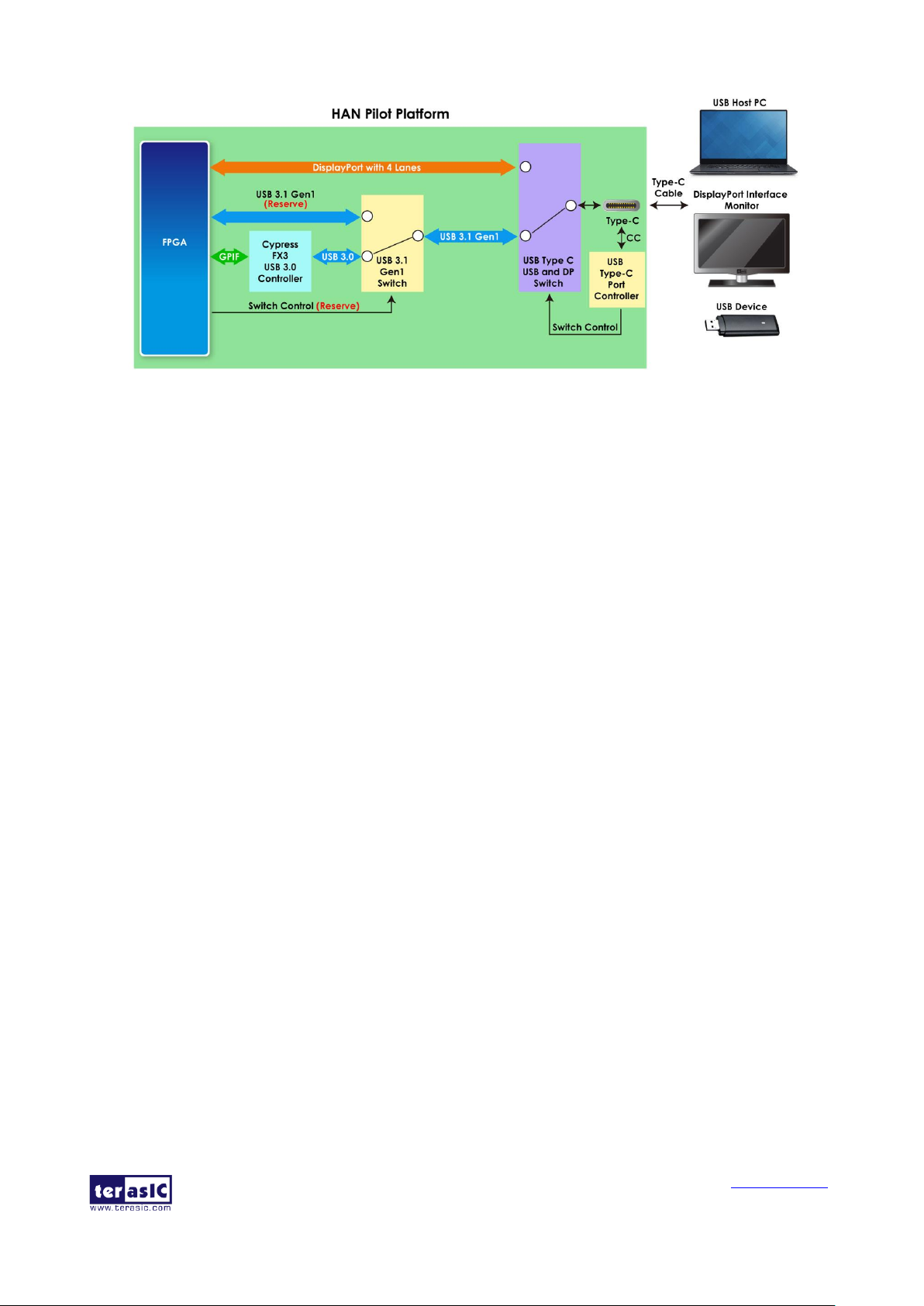

The HAN Pilot Platform board features one USB Type-C connector. It is designed for high-speed

data transmission with computers and image output applications. Figure 4-5 shows the block

diagram of the connection between USB Type-C port and FPGA.

Page 23

HAN Pilot Platform

Hardware Manual

22

www.terasic.com

July 5, 2019

Figure 4-5 Block diagram of the connection between USB Type-C port and FPGA

As shown in Figure 4-5, it connects to FPGA through several switch circuits and USB controllers,

users can switch USB Type-C connector to a variety of applications as below:

▪ USB 3.0 Device to USB Host PC

▪ USB 2.0 OTG

▪ DisplayPort Source Application (Need DP Source IP)

The USB Type-C Port Controller will detect the type of USB device connected to the Type-C

connector, automatically switches the "USB and DP" switch (U11), and connects the USB Type-C

connector to the appropriate application in the HAN Pilot kit. If user connects a Display port

monitor to the USB type-C connector of the Han Pilot kit, the "USB and DP" switch will be

switched to the transceiver path of the FPGA by the USB type-C Port Controller, which is useful for

the Display port output application. Similarly, when a USB 3.0 host device is connected to the USB

Type-C connector, the "USB and DP" switch will be switched to the path of the cypress FX3.0 USB

controller for USB 3.0 applications.

We will describe the circuits diagram and these functions in detail below.

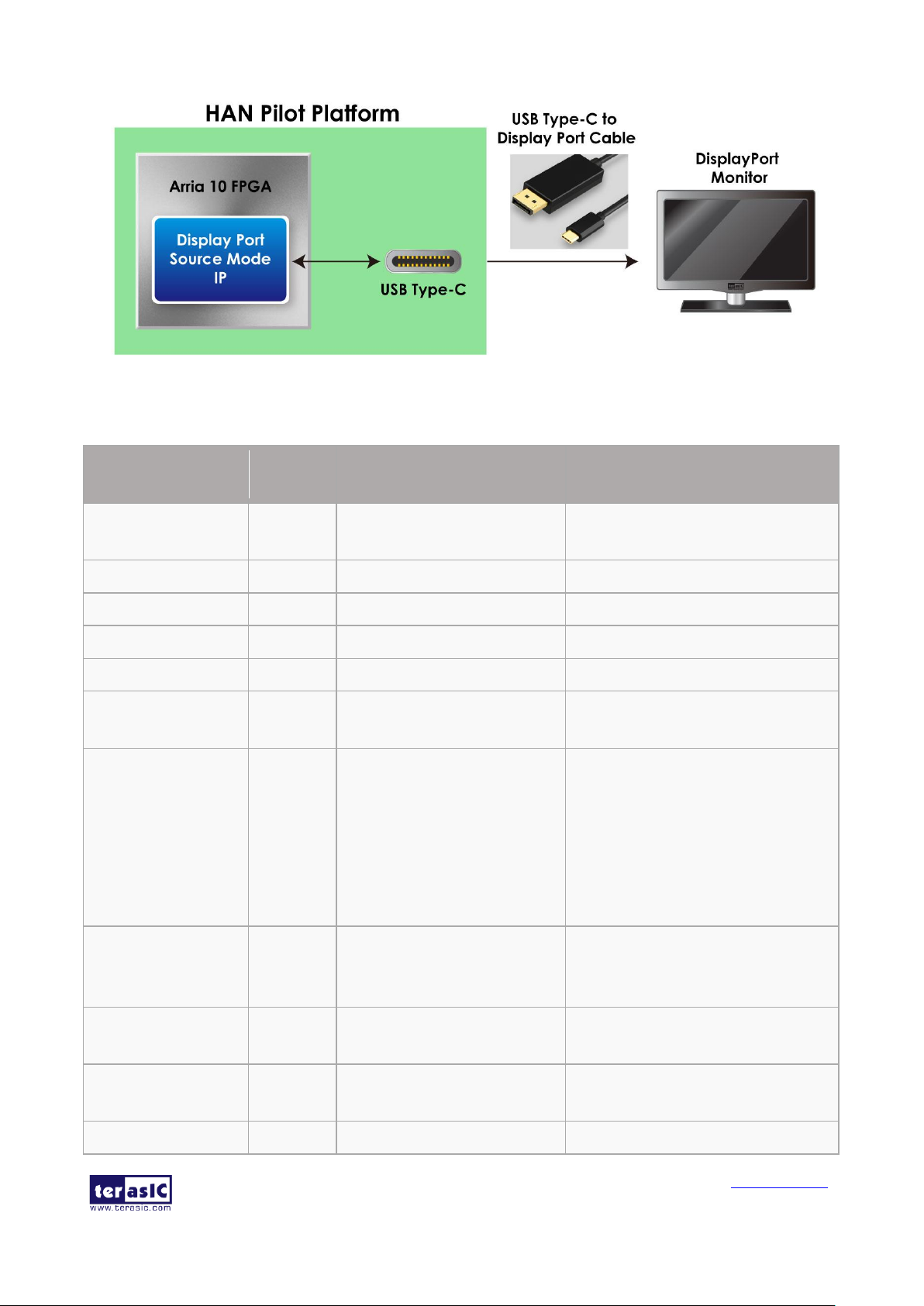

◼ Display Port

As shown in Figure 4-6, USB Type-C port can connect to FPGA transceiver. Users can implement

a Display port source mode IP in the FPGA, the HAN Pilot Platform board will implement the

features of display port source. Through the USB Type-C cable, users can connect HAN Pilot

Platform board to the monitor which supports Display port interface. Then the image processed by

FPGA can be displayed on the monitor. The display port provides data rate up to 5.4Gbps per lane

and 4 lanes in total, it supports DisplayPort 1.2a Spec. Table 4-5 list the pin assignment of

DisplayPorts.

Page 24

HAN Pilot Platform

Hardware Manual

23

www.terasic.com

July 5, 2019

Figure 4-6 USB Type-C Application: DisplayPort TX Source

Table 4-5 DisplayPort Signal Names and Functions

Signal Name

FPGA Pin

Number

Description

I/O Standard

DP_REFCLK_p

AM31

Display reference clock form

PLL

LVDS

DP_TX_p[0]

AW37

TX Lane 1

HSSI Differential I/O

DP_TX_p[1]

AV39

TX Lane 2

HSSI Differential I/O

DP_TX_p[2]

AU37

TX Lane 3

HSSI Differential I/O

DP_TX_p[3]

AT39

TX Lane 4

HSSI Differential I/O

DP_AUX_p

AM22

Display port AUX port

DIFFERENTIAL 1.8-V SSTL

CLASS I

DP_DX_SEL

AB27

Display Port channel TX or

RX(Reserve) select.

DP_DX_SEL = 0 : USB

TypeC in Display TX mode .

DP_DX_SEL = 1(Reserve):

USB TypeC in Display RX

mode

1.8 V

DP_AUX_SEL

AC28

AUX/DDC Selection Control

Pin in Conjunction with

Dx_SEL Pin

1.8 V

USBDP_SW_CNF0

AA27

Display port Switch

Configure 0

1.8 V

USBDP_SW_CNF1

AB26

Display port Switch

Configure 1

1.8 V

USBDP_SW_CNF2

AB25

Display port Switch

1.8 V

Page 25

HAN Pilot Platform

Hardware Manual

24

www.terasic.com

July 5, 2019

Configure 2

◼ USB 3.0 Device

The HAN Pilot Platform board has one Cypress FX3 USB Controller (CYUSB3014). The USB

controller is connected to FPGA through the programmable GPIF II interface, and connect to the

external USB Type-C connector, it provides USB 3.0 Device application for HAN Pilot Platform

board.

As shown in Figure 4-7, users can connect FX3 USB Controller to PC through USB Type-C cable,

and transfer USB 3.0 data between FPGA and USB Host PC with transfer rate 320MByte/s (Using

the demonstration provided by Cypress). Table 4-6 list the pin assignment of FX3 USB 3.0

Controller.

Figure 4-7 FX3 USB 3.0 Controller application

◼ USB 2.0 OTG

The Cypress FX3 USB controller also has a USB 2.0 OTG controller. It allows the HAN Pilot

Platform board function as an OTG Host to MSC as well as HID-class devices, as shown in Figure

4-8.

Figure 4-8 USB 2.0 OTG Controller application

Table 4-6 FX3 USB 3.0 Controller Signal Names and Functions

Signal Name

FPGA Pin Number

Description

I/O Standard

USBFX3_DQ[0]

AU21

GPIF II Data Bus 0

1.8 V

Page 26

HAN Pilot Platform

Hardware Manual

25

www.terasic.com

July 5, 2019

USBFX3_DQ[1]

AW23

GPIF II Data Bus 1

1.8 V

USBFX3_DQ[2]

AW24

GPIF II Data Bus 2

1.8 V

USBFX3_DQ[3]

AW25

GPIF II Data Bus 3

1.8 V

USBFX3_DQ[4]

AW26

GPIF II Data Bus 4

1.8 V

USBFX3_DQ[5]

AV24

GPIF II Data Bus 5

1.8 V

USBFX3_DQ[6]

AW28

GPIF II Data Bus 6

1.8 V

USBFX3_DQ[7]

AW30

GPIF II Data Bus 7

1.8 V

USBFX3_DQ[8]

AW29

GPIF II Data Bus 8

1.8 V

USBFX3_DQ[9]

AV27

GPIF II Data Bus 9

1.8 V

USBFX3_DQ[10]

AV28

GPIF II Data Bus 10

1.8 V

USBFX3_DQ[11]

AU26

GPIF II Data Bus 11

1.8 V

USBFX3_DQ[12]

AV23

GPIF II Data Bus 12

1.8 V

USBFX3_DQ[13]

AU25

GPIF II Data Bus 13

1.8 V

USBFX3_DQ[14]

AR25

GPIF II Data Bus 14

1.8 V

USBFX3_DQ[15]

AP24

GPIF II Data Bus 15

1.8 V

USBFX3_DQ[16]

AL23

GPIF II Data Bus 16

1.8 V

USBFX3_DQ[17]

AM24

GPIF II Data Bus 17

1.8 V

USBFX3_DQ[18]

AK25

GPIF II Data Bus 18

1.8 V

USBFX3_DQ[19]

AM25

GPIF II Data Bus 19

1.8 V

USBFX3_DQ[20]

AT24

GPIF II Data Bus 20

1.8 V

USBFX3_DQ[21]

AR26

GPIF II Data Bus 21

1.8 V

USBFX3_DQ[22]

AP26

GPIF II Data Bus 22

1.8 V

USBFX3_DQ[23]

AP25

GPIF II Data Bus 23

1.8 V

USBFX3_DQ[24]

AN24

GPIF II Data Bus 24

1.8 V

USBFX3_DQ[25]

AN26

GPIF II Data Bus 25

1.8 V

USBFX3_DQ[26]

AK23

GPIF II Data Bus 26

1.8 V

USBFX3_DQ[27]

AJ25

GPIF II Data Bus 27

1.8 V

USBFX3_DQ[28]

AJ23

GPIF II Data Bus 28

1.8 V

USBFX3_DQ[29]

AH23

GPIF II Data Bus 29

1.8 V

USBFX3_DQ[30]

AR20

GPIF II Data Bus 30

1.8 V

USBFX3_DQ[31]

AP20

GPIF II Data Bus 31

1.8 V

USBFX3_CTL0_SLCS_n

AV26

GPIF II Control Bus 0

1.8 V

USBFX3_CTL1_SLWR_n

AT22

GPIF II Control Bus 1

1.8 V

Page 27

HAN Pilot Platform

Hardware Manual

26

www.terasic.com

July 5, 2019

USBFX3_CTL2_SLOE_n

AT25

GPIF II Control Bus 2

1.8 V

USBFX3_CTL3_SLRD_n

AR27

GPIF II Control Bus 3

1.8 V

USBFX3_CTL4_FLAGA

AN22

GPIF II Control Bus 4

1.8 V

USBFX3_CTL5_FLAGB

AN23

GPIF II Control Bus 5

1.8 V

USBFX3_CTL6

AL24

GPIF II Control Bus 6

1.8 V

USBFX3_CTL7_PKTEND_n

AL25

GPIF II Control Bus 7

1.8 V

USBFX3_CTL8

AV21

GPIF II Control Bus 8

1.8 V

USBFX3_CTL9

AV22

GPIF II Control Bus 9

1.8 V

USBFX3_CTL10

AU24

GPIF II Control Bus

10

1.8 V

USBFX3_CTL11_A1

AU22

GPIF II Control Bus

11

1.8 V

USBFX3_CTL12_A0

AT23

GPIF II Control Bus

12

1.8 V

USBFX3_CTL15_INT_n

AW21

GPIF II Control Bus

15

1.8 V

USBFX3_RESET_n

AJ24

FX3 reset

1.8 V

USBFX3_PCLK

AT27

FX3 clok

1.8 V

USBFX3_UART_TX

AP23

USB to UART

transmitter

1.8 V

USBFX3_UART_RX

AU27

USB to UART

receiver

1.8 V

USBFX3_OTG_ID

AG26

OTG ID pin

1.8 V

44..3

3

SSFFPP++ CCoonnnneeccttoorr

The development board has four independent 10G SFP+ connectors that use one transceiver

channel each from the Arria 10 SoC FPGA device. These modules take in serial data from the Arria

10 SoC FPGA device and transform them to optical signals. The board includes cage assemblies for

the SFP+ connectors. Figure 4-9 shows the connections between the SFP+ and Arria 10 SoC

FPGA.

Page 28

HAN Pilot Platform

Hardware Manual

27

www.terasic.com

July 5, 2019

Figure 4-9 Connection between the SFP+ and Arria 10 SoC FPGA

Table 4-7, Table 4-8, Table 4-9 and Table 4-10 list the four QSF+ connectors assignments and

signal names relative to the Arria 10 SoC FPGA.

Table 4-7 SFP+ A Pin Assignments, Signal Names and Functions

Signal Name

FPGA Pin

Number

Description

I/O Standard

SFPA_TXDISABLE

PIN_AV6

Turns off and disables the

transmitter output

1.2V

SFPA_TXFAULT

PIN_AP3

Transmitter fault

1.2V

SFPA_TX_p

PIN_AG37

Transmitter data

HSSI DIFFERENTIAL

I/O

SFPA_RX_p

PIN_AD35

Receiver data

HSSI DIFFERENTIAL

I/O

SFPA_LOS

PIN_AN6

Signal loss indicator

1.2V

SFPA_MOD0_PRSNT_n

PIN_AU4

Module present

1.2V

SFPA_RATESEL0

PIN_AM19

Rate select 0

1.8V

SFPA_RATESEL1

PIN_AN17

Rate select 1

1.8V

SFPA_MOD1_SCL

PIN_AW6

Transmitter data

1.2V

SFPA_MOD2_SDA

PIN_AW5

Receiver data

1.2V

Table 4-8 SFP+ B Pin Assignments, Signal Names and Functions

Signal Name

FPGA Pin

Number

Description

I/O Standard

SFPB_TXDISABLE

PIN_AU5

Turns off and disables the

transmitter output

1.2V

SFPB_TXFAULT

PIN_AE10

Transmitter fault

1.2V

Page 29

HAN Pilot Platform

Hardware Manual

28

www.terasic.com

July 5, 2019

SFPB_TX_p

PIN_AF39

Transmiter data

HSSI DIFFERENTIAL

I/O

SFPB_RX_p

PIN_AC37

Receiver data

HSSI DIFFERENTIAL

I/O

SFPB_LOS

PIN_AN12

Signal loss indicator

1.2V

SFPB_MOD0_PRSNT_n

PIN_AT5

Module present

1.2V

SFPB_RATESEL0

PIN_AR18

Rate select 0

1.8V

SFPB_RATESEL1

PIN_AP18

Rate select 1

1.8V

SFPB_MOD1_SCL

PIN_AW4

Transmitter data

1.2V

SFPB_MOD2_SDA

PIN_AV4

Receiver data

1.2V

Table 4-9 SFP+ C Pin Assignments, Signal Names and Functions

Signal Name

FPGA Pin

Number

Description

I/O Standard

SFPC_TXDISABLE

PIN_AP30

Turns off and disables the

transmitter output

1.2V

SFPC_TXFAULT

PIN_AP28

Transmitter fault

1.2V

SFPC_TX_p

PIN_AE37

Transmiter data

HSSI DIFFERENTIAL

I/O

SFPC_RX_p

PIN_AC33

Receiver data

HSSI DIFFERENTIAL

I/O

SFPC_LOS

PIN_AN28

Signal loss indicator

1.2V

SFPC_MOD0_PRSNT_n

PIN_B27

Module present

1.2V

SFPC_RATESEL0

PIN_AK18

Rate select 0

1.8V

SFPC_RATESEL1

PIN_AR17

Rate select 1

1.8V

SFPC_MOD1_SCL

PIN_AV3

Transmitter data

1.2V

SFPC_MOD2_SDA

PIN_AW3

Receiver data

1.2V

Table 4-10 SFP+ D Pin Assignments, Signal Names and Functions

Signal Name

FPGA Pin

Number

Description

I/O Standard

SFPD_TXDISABLE

PIN_AR28

Turns off and disables the

transmitter output

1.2V

SFPD_TXFAULT

PIN_AP21

Transmitter fault

1.2V

SFPD_TX_p

PIN_AD39

Transmiter data

HSSI DIFFERENTIAL

I/O

Page 30

HAN Pilot Platform

Hardware Manual

29

www.terasic.com

July 5, 2019

SFPD_RX_p

PIN_AB35

Receiver data

HSSI DIFFERENTIAL

I/O

SFPD_LOS

PIN_D26

Signal loss indicator

1.2V

SFPD_MOD0_PRSNT_n

PIN_AL28

Module present

1.2V

SFPD_RATESEL0

PIN_AH18

Rate select 0

1.8V

SFPD_RATESEL1

PIN_AW19

Rate select 1

1.8V

SFPD_MOD1_SCL

PIN_AV2

Transmitter data

1.2V

SFPD_MOD2_SDA

PIN_AV1

Receiver data

1.2V

SFP_REFCLK_p

PIN_AD31

SFP Reference clock

LVDS

44..4

4

SSAATTAA

Four Serial ATA (SATA) ports are available on the FPGA development board which are computer

bus standard with a primary function of transferring data between the motherboard and mass storage

devices (such as hard drives, optical drives, and solid-state disks). Supporting a storage interface is

just one of many different applications an FPGA can be used in storage appliances. The Arria 10

SoC device can bridge different protocols such as bridging simple bus I/Os like PCI Express (PCIe)

to SATA or network interfaces such as Gigabit Ethernet (GbE) to SATA. The SATA interface

supports SATA 3.0 standard with connection speed of 6 Gbps based on Arria 10 SoC device with

integrated transceivers compliant to SATA electrical standards.

The four Serial ATA (SATA) ports include two available ports for device and two available ports for

host capable of implementing SATA solution with a design that consists of both host and target

(device side) functions. Figure 4-10 depicts the host and device design examples.

Figure 4-10 PC and storage device connection to the Arria 10 SoC FPGA

Page 31

HAN Pilot Platform

Hardware Manual

30

www.terasic.com

July 5, 2019

The transmitter and receiver signals of the SATA ports are connected directly to the Arria 10 SoC

transceiver channels to provide SATA IO connectivity to both host and target devices. To verify the

functionality of the SATA host/device ports, a connection can be established between the two ports

by using a SATA cable as Figure 4-11 depicts the associated signals connected. Table 4-11 lists the

SATA pin assignments, signal names and functions.

Figure 4-11 Pin connection between SATA connectors

Table 4-11 SATA Pin Assignments, Signal Names and Functions

Signal Name

FPGA Pin

Number

Description

I/O Standard

Device

SATA_DEVICE_REFCLK_p

PIN_M31

SATA Device reference

clock

LVDS

SATA_DEVICE_REFCLK_n

PIN_M30

SATA Device reference

clock

LVDS

SATA_DEVICE_RX_n0

PIN_D34

Differential receive data

input after DC blocking

capacitor

HSSI

DIFFERENTIAL

I/O

SATA_DEVICE_RX_n1

PIN_B34

Differential receive data

input after DC blocking

capacitor

HSSI

DIFFERENTIAL

I/O

SATA_DEVICE_TX_n0

PIN_B38

Differential transmit data

output before DC

blocking capacitor

HSSI

DIFFERENTIAL

I/O

SATA_DEVICE_TX_n1

PIN_A36

Differential transmit data

output before DC

blocking capacitor

HSSI

DIFFERENTIAL

I/O

SATA_DEVICE_TX_p0

PIN_B39

Differential transmit data

output before DC

HSSI

DIFFERENTIAL

Page 32

HAN Pilot Platform

Hardware Manual

31

www.terasic.com

July 5, 2019

blocking capacitor

I/O

SATA_DEVICE_TX_p1

PIN_A37

Differential transmit data

output before DC

blocking capacitor

HSSI

DIFFERENTIAL

I/O

SATA_DEVICE_RX_p0

PIN_D35

Differential receive data

input after DC blocking

capacitor

HSSI

DIFFERENTIAL

I/O

SATA_DEVICE_RX_p1

PIN_B35

Differential receive data

input after DC blocking

capacitor

HSSI

DIFFERENTIAL

I/O

Host

SATA_HOST_REFCLK_p

PIN_AF31

SATA Host reference

clock

LVDS

SATA_HOST_REFCLK_n

PIN_AF30

SATA Host reference

clock

LVDS

SATA_HOST_TX_p0

PIN_AJ37

Differential transmit data

output before DC

blocking capacitor

HSSI

DIFFERENTIAL

I/O

SATA_HOST_TX_p1

PIN_AH39

Differential transmit data

output before DC

blocking capacitor

HSSI

DIFFERENTIAL

I/O

SATA_HOST_RX_p0

PIN_AE33

Differential receive data

input after DC blocking

capacitor

HSSI

DIFFERENTIAL

I/O

SATA_HOST_RX_p1

PIN_AF35

Differential receive data

input after DC blocking

capacitor

HSSI

DIFFERENTIAL

I/O

SATA_HOST_TX_n0

PIN_AJ36

Differential transmit data

output before DC

blocking capacitor

HSSI

DIFFERENTIAL

I/O

SATA_HOST_TX_n1

PIN_AH38

Differential transmit data

output before DC

blocking capacitor

HSSI

DIFFERENTIAL

I/O

SATA_HOST_RX_n0

PIN_AE32

Differential receive data

input after DC blocking

capacitor

HSSI

DIFFERENTIAL

I/O

SATA_HOST_RX_n1

PIN_AF34

Differential receive data

input after DC blocking

capacitor

HSSI

DIFFERENTIAL

I/O

Page 33

HAN Pilot Platform

Hardware Manual

32

www.terasic.com

July 5, 2019

44..5

5

PPCCIIee

The HAN Pilot Platform board features one PCIe Express downstream interfaces (x4 lane) which

are designed to interface with a PC motherboard x4 slot via PCIe cable and PCIe adapter card.

Utilizing built-in transceivers on an Arria 10 SoC device, it is able to provide a fully integrated PCI

Express-compliant solution for multi-lane (x4) applications. With the PCI Express hard IP block

incorporated in the Arria 10 SoC device, it will allow users to implement simple and fast protocols,

as well as saving logic resources for logic applications.

The PCI Express interface supports complete PCI Express Gen1 at 2.5Gbps/lane, Gen2 at

5.0Gbps/lane, and Gen3 at 8.0Gbps/lane protocol stack solution compliant to PCI Express base

specification 3.0 that includes PHY-MAC, Data Link, and transaction layer circuitry embedded in

PCI Express hard IP blocks.

To use PCIe interface, two external associated devices will be needed to establish a link with PC.

First, a PCIe half-height add-in host card with a PCIe x4 cable connector called PCA (PCIe Cabling

Adapter Card and See Figure 4-12) will be used to plug into the PCIe slot on a mother board. Then,

a PCIe x4 cable (See Figure 4-13) will be used to connect HAN Pilot Platform board and PCIe

add-in card as shown in Figure 4-14, the longest length is up to 3 meters. These two associated

devices are not included in HAN Pilot Platform kit. To purchase the PCA card as well as the

external cable, please refer to Terasic website pca.terasic.com and PCIe_Cable.terasic.com.

Figure 4-12 PCIe Cabling Adaptor(PCA) card

Page 34

HAN Pilot Platform

Hardware Manual

33

www.terasic.com

July 5, 2019

Figure 4-13 PCIe External Cable

Figure 4-14 PCIe Link Setup between HAN Pilot Platform and PC

Table 4-12 summarizes the PCI Express pin assignments of the signal names relative to the Arria 10

FPGA.

Table 4-12 PCI Express pin assignments of the signal names

Schematic

Signal Name

Description

I/O Standard

Arria 10 Pin

Number

PCIE_REFCLK_p

PCIe reference clock

LVDS

PIN_AH31

PCIE_PREST_n

PCIe present, active low

1.8-V

PIN_AW20

PCIE_WAKE_n

PCIe wake

1.8-V

PIN_AL19

PCIE_TX_p[0]

PCIe Transmitter data p0

HSSI DIFFERENTIAL

I/O

PIN_AR37

PCIE_RX_p[0]

PCIe Receiver data p0

HSSI DIFFERENTIAL

I/O

PIN_AL33

PCIE_TX_p[1]

PCIe Transmitter data p1

HSSI DIFFERENTIAL

I/O

PIN_AP39

PCIE_RX_p[1]

PCIe Receiver data p1

HSSI DIFFERENTIAL

I/O

PIN_AM35

PCIE_TX_p[2]

PCIe Transmitter data p2

HSSI DIFFERENTIAL

I/O

PIN_AN37

PCIE_RX_p[2]

PCIe Receiver data p2

HSSI DIFFERENTIAL

PIN_AJ33

Page 35

HAN Pilot Platform

Hardware Manual

34

www.terasic.com

July 5, 2019

I/O

PCIE_TX_p[3]

PCIe Transmitter data p3

HSSI DIFFERENTIAL

I/O

PIN_AM39

PCIE_RX_p[3]

PCIe Receiver data p3

HSSI DIFFERENTIAL

I/O

PIN_AK35

44..6

6

DDDDRR44

The board supports 1GB of DDR4 SDRAM comprising of two x16 bit DDR4 devices on FPGA

side. The DDR4 devices shipped with this board are running at 1067 MHz, for a total theoretical

bandwidth of over 66Gbps. Figure 4-15 shows the connections between the DDR4 and Arria 10

SoC FPGA. Table 4-13 lists the pin assignments of DDR4 and its description with I/O standard.

Figure 4-15 The connection between DDR4 and Arria 10 SoC FPGA

Table 4-13 The pin assignments of DDR4 component and its description with I/O standard

FPGA Pin Number

Signal Name

Description

I/O Standard

PIN_AU7

DDR4B_REFCLK_p

DDR4 A port Reference Clock

p

LVDS

PIN_AJ11

DDR4B_A[0]

Address [0]

SSTL-12

PIN_AH12

DDR4B_A[1]

Address [1]

SSTL-12

PIN_AP11

DDR4B_A[2]

Address [2]

SSTL-12

PIN_AN11

DDR4B_A[3]

Address [3]

SSTL-12

PIN_AM10

DDR4B_A[4]

Address [4]

SSTL-12

PIN_AM11

DDR4B_A[5]

Address [5]

SSTL-12

PIN_AP9

DDR4B_A[6]

Address [6]

SSTL-12

PIN_AN9

DDR4B_A[7]

Address [7]

SSTL-12

PIN_AR10

DDR4B_A[8]

Address [8]

SSTL-12

Page 36

HAN Pilot Platform

Hardware Manual

35

www.terasic.com

July 5, 2019

PIN_AP10

DDR4B_A[9]

Address [9]

SSTL-12

PIN_AM9

DDR4B_A[10]

Address [10]

SSTL-12

PIN_AL10

DDR4B_A[11]

Address [11]

SSTL-12

PIN_AV8

DDR4B_A[12]

Address [12]

SSTL-12

PIN_AT8

DDR4B_A[13]

Address [13]

SSTL-12

PIN_AT9

DDR4B_A[14]

Address [14]/WE_n

SSTL-12

PIN_AR7

DDR4B_A[15]

Address [15]/CAS_n

SSTL-12

PIN_AR8

DDR4B_A[16]

Address [16]/RAS_n

SSTL-12

PIN_AU6

DDR4B_BA[0]

Bank Select [0]

SSTL-12

PIN_AP8

DDR4B_BA[1]

Bank Select [1]

SSTL-12

PIN_AN8

DDR4B_BG[0]

Bank Group Select[0]

SSTL-12

PIN_AJ14

DDR4B_BG[1]

Bank Group Select[1]

SSTL-12

PIN_AL13

DDR4B_CK

Clock p0

DIFFERENTIAL

1.2-V SSTL

PIN_AK13

DDR4B_CK_n

Clock n0

DIFFERENTIAL

1.2-V SSTL

PIN_AK10

DDR4B_CKE

Clock Enable pin

SSTL-12

PIN_AE12

DDR4B_DQS[0]

Data Strobe p[0]

DIFFERENTIAL

1.2-V POD

PIN_AL7

DDR4B_DQS[1]

Data Strobe p[1]

DIFFERENTIAL

1.2-V POD

PIN_AR6

DDR4B_DQS[2]

Data Strobe p[2]

DIFFERENTIAL

1.2-V POD

PIN_AT2

DDR4B_DQS[3]

Data Strobe p[3]

DIFFERENTIAL

1.2-V POD

PIN_AF13

DDR4B_DQS_n[0]

Data Strobe n[0]

DIFFERENTIAL

1.2-V POD

PIN_AK8

DDR4B_DQS_n[1]

Data Strobe n[1]

DIFFERENTIAL

1.2-V POD

PIN_AP6

DDR4B_DQS_n[2]

Data Strobe n[2]

DIFFERENTIAL

1.2-V POD

PIN_AT3

DDR4B_DQS_n[3]

Data Strobe n[3]

DIFFERENTIAL

1.2-V POD

PIN_AF10

DDR4B_DBI_n[0]

Data Bus Inversion [0]

1.2-V POD

PIN_AL8

DDR4B_DBI_n[1]

Data Bus Inversion [1]

1.2-V POD

Page 37

HAN Pilot Platform

Hardware Manual

36

www.terasic.com

July 5, 2019

PIN_AN7

DDR4B_DBI_n[2]

Data Bus Inversion [2]

1.2-V POD

PIN_AN4

DDR4B_DBI_n[3]

Data Bus Inversion [3]

1.2-V POD

PIN_AF10

DDR4B_DBI_n[0]

Data Bus Inversion [0]

1.2-V POD

PIN_AJ9

DDR4B_DQ[0]

Data [0]

1.2-V POD

PIN_AG11

DDR4B_DQ[1]

Data [1]

1.2-V POD

PIN_AF9

DDR4B_DQ[2]

Data [2]

1.2-V POD

PIN_AG12

DDR4B_DQ[3]

Data [3]

1.2-V POD

PIN_AG9

DDR4B_DQ[4]

Data [4]

1.2-V POD

PIN_AF12

DDR4B_DQ[5]

Data [5]

1.2-V POD

PIN_AJ10

DDR4B_DQ[6]

Data [6]

1.2-V POD

PIN_AG10

DDR4B_DQ[7]

Data [7]

1.2-V POD

PIN_AL9

DDR4B_DQ[8]

Data [8]

1.2-V POD

PIN_AH9

DDR4B_DQ[9]

Data [9]

1.2-V POD

PIN_AK6

DDR4B_DQ[10]

Data [10]

1.2-V POD

PIN_AK7

DDR4B_DQ[11]

Data [11]

1.2-V POD

PIN_AH8

DDR4B_DQ[12]

Data [12]

1.2-V POD

PIN_AH7

DDR4B_DQ[13]

Data [13]

1.2-V POD

PIN_AJ8

DDR4B_DQ[14]

Data [14]

1.2-V POD

PIN_AE11

DDR4B_DQ[15]

Data [15]

1.2-V POD

PIN_AT4

DDR4B_DQ[16]

Data [16]

1.2-V POD

PIN_AM7

DDR4B_DQ[17]

Data [17]

1.2-V POD

PIN_AP5

DDR4B_DQ[18]

Data [18]

1.2-V POD

PIN_AL5

DDR4B_DQ[19]

Data [19]

1.2-V POD

PIN_AM5

DDR4B_DQ[20]

Data [20]

1.2-V POD

PIN_AM6

DDR4B_DQ[21]

Data [21]

1.2-V POD

PIN_AM4

DDR4B_DQ[22]

Data [22]

1.2-V POD

PIN_AR5

DDR4B_DQ[23]

Data [23]

1.2-V POD

PIN_AP1

DDR4B_DQ[24]

Data [24]

1.2-V POD

PIN_AR3

DDR4B_DQ[25]

Data [25]

1.2-V POD

PIN_AN3

DDR4B_DQ[26]

Data [26]

1.2-V POD

PIN_AR1

DDR4B_DQ[27]

Data [27]

1.2-V POD

PIN_AU2

DDR4B_DQ[28]

Data [28]

1.2-V POD

PIN_AP4

DDR4B_DQ[29]

Data [29]

1.2-V POD

Page 38

HAN Pilot Platform

Hardware Manual

37

www.terasic.com

July 5, 2019

PIN_AR2

DDR4B_DQ[30]

Data [30]

1.2-V POD

PIN_AU1

DDR4B_DQ[31]

Data [31]

1.2-V POD

PIN_AF10

DDR4B_DM[0]

DDR3 Data Mask[0]

1.2-V POD

PIN_AL8

DDR4B_DM[1]

DDR3 Data Mask[1]

1.2-V POD

PIN_AN7

DDR4B_DM[2]

DDR3 Data Mask[2]

1.2-V POD

PIN_AN4

DDR4B_DM[3]

DDR3 Data Mask[3]

1.2-V POD

PIN_AJ13

DDR4B_CS_n[0]

Chip Select

SSTL-12

PIN_AH14

DDR4B_RESET_n

Chip Reset

1.2 V

PIN_AL12

DDR4B_ODT

On Die Termination

SSTL-12

PIN_AM12

DDR4B_PAR

Command and Address Parity

Input

SSTL-12

PIN_AH11

DDR4B_ALERT_n

Register ALERT_n output

SSTL-12

PIN_AH13

DDR4B_ACT_n

Activation Command Input

SSTL-12

PIN_AW8

DDR4B_RZQ

External reference ball for

output drive calibration

1.2 V

The development board also supports one bank of DDR4 SDRAM SO-DIMM on FPGA side. It is

wired to support a maximum capacity of 8GB with a 72-bit data bus. Using differential DQS

signaling for the DDR4 SDRAM interfaces, it is capable of running at up to 1067MHz memory

clock for a maximum theoretical bandwidth up to 132Gbps. Figure 4-16 shows the connections

between the DDR4 SDRAM SODIMM and Arria 10 SoC FPGA. The pin assignments for DDR4

SDRAM SO-DIMM are listed in Table 4-14.

Figure 4-16 The connection between the DDR4 SDRAM SO-DIMM and Arria 10 SoC FPGA

Page 39

HAN Pilot Platform

Hardware Manual

38

www.terasic.com

July 5, 2019

Table 4-14 The pin assignments for DDR4 SDRAM SO-DIMM

FPGA Pin Number

Signal Name

Description

I/O Standard

PIN_AB12

DDR4A_REFCLK_p

DDR4 A port Reference Clock p

LVDS

PIN_AC1

DDR4A_A[0]

Address [0]

SSTL-12

PIN_AB1

DDR4A_A[1]

Address [1]

SSTL-12

PIN_AB4

DDR4A_A[2]

Address [2]

SSTL-12

PIN_AA5

DDR4A_A[3]

Address [3]

SSTL-12

PIN_AA3

DDR4A_A[4]

Address [4]

SSTL-12

PIN_AA4

DDR4A_A[5]

Address [5]

SSTL-12

PIN_Y2

DDR4A_A[6]

Address [6]

SSTL-12

PIN_AA2

DDR4A_A[7]

Address [7]

SSTL-12

PIN_AB5

DDR4A_A[8]

Address [8]

SSTL-12

PIN_AB6

DDR4A_A[9]

Address [9]

SSTL-12

PIN_W5

DDR4A_A[10]

Address [10]

SSTL-12

PIN_Y5

DDR4A_A[11]

Address [11]

SSTL-12

PIN_AA9

DDR4A_A[12]

Address [12]

SSTL-12

PIN_AB7

DDR4A_A[13]

Address [13]

SSTL-12

PIN_AA7

DDR4A_A[14]

Address [14]/WE_n

SSTL-12

PIN_AB10

DDR4A_A[15]

Address [15]/CAS_n

SSTL-12

PIN_AB11

DDR4A_A[16]

Address [16]/RAS_n

SSTL-12

PIN_Y7

DDR4A_BA[0]

Bank Select [0]

SSTL-12

PIN_AB9

DDR4A_BA[1]

Bank Select [1]

SSTL-12

PIN_AA10

DDR4A_BG[0]

Bank Group Select[0]

SSTL-12

PIN_AE2

DDR4A_BG[1]

Bank Group Select[1]

SSTL-12

PIN_AD3

DDR4A_CK

Clock p0

DIFFERENTIAL

1.2-V SSTL

PIN_AD4

DDR4A_CK_n

Clock n0

DIFFERENTIAL

1.2-V SSTL

PIN_AC2

DDR4A_CKE

Clock Enable pin

SSTL-12

PIN_AE8

DDR4A_DQS[0]

Data Strobe p[0]

DIFFERENTIAL

1.2-V POD

PIN_AF7

DDR4A_DQS[1]

Data Strobe p[1]

DIFFERENTIAL

1.2-V POD

PIN_AN1

DDR4A_DQS[2]

Data Strobe p[2]

DIFFERENTIAL

Page 40

HAN Pilot Platform

Hardware Manual

39

www.terasic.com

July 5, 2019

1.2-V POD

PIN_AH2

DDR4A_DQS[3]

Data Strobe p[3]

DIFFERENTIAL

1.2-V POD

PIN_P1

DDR4A_DQS[4]

Data Strobe p[4]

DIFFERENTIAL

1.2-V POD

PIN_J3

DDR4A_DQS[5]

Data Strobe p[5]

DIFFERENTIAL

1.2-V POD

PIN_R5

DDR4A_DQS[6]

Data Strobe p[6]

DIFFERENTIAL

1.2-V POD

PIN_V9

DDR4A_DQS[7]

Data Strobe p[7]

DIFFERENTIAL

1.2-V POD

PIN_V2

DDR4A_DQS[8]

Data Strobe p[8]

DIFFERENTIAL

1.2-V POD

PIN_AD8

DDR4A_DQS_n[0]

Data Strobe n[0]

DIFFERENTIAL

1.2-V POD

PIN_AE7

DDR4A_DQS_n[1]

Data Strobe n[1]

DIFFERENTIAL

1.2-V POD

PIN_AN2

DDR4A_DQS_n[2]

Data Strobe n[2]

DIFFERENTIAL

1.2-V POD

PIN_AH3

DDR4A_DQS_n[3]

Data Strobe n[3]

DIFFERENTIAL

1.2-V POD

PIN_R1

DDR4A_DQS_n[4]

Data Strobe n[4]

DIFFERENTIAL

1.2-V POD

PIN_K3

DDR4A_DQS_n[5]

Data Strobe n[5]

DIFFERENTIAL

1.2-V POD

PIN_R6

DDR4A_DQS_n[6]

Data Strobe n[6]

DIFFERENTIAL

1.2-V POD

PIN_W9

DDR4A_DQS_n[7]

Data Strobe n[7]

DIFFERENTIAL

1.2-V POD

PIN_V3

DDR4A_DQS_n[8]

Data Strobe n[8]

DIFFERENTIAL

1.2-V POD

PIN_AC11

DDR4A_DQ[0]

Data [0]

1.2-V POD

PIN_AD10

DDR4A_DQ[1]

Data [1]

1.2-V POD

PIN_AC9

DDR4A_DQ[2]

Data [2]

1.2-V POD

PIN_AG7

DDR4A_DQ[3]

Data [3]

1.2-V POD

PIN_AD13

DDR4A_DQ[4]

Data [4]

1.2-V POD

PIN_AD11

DDR4A_DQ[5]

Data [5]

1.2-V POD

Page 41

HAN Pilot Platform

Hardware Manual

40

www.terasic.com

July 5, 2019

PIN_AC8

DDR4A_DQ[6]

Data [6]

1.2-V POD

PIN_AF8

DDR4A_DQ[7]

Data [7]

1.2-V POD

PIN_AE6

DDR4A_DQ[8]

Data [8]

1.2-V POD

PIN_AJ6

DDR4A_DQ[9]

Data [9]

1.2-V POD

PIN_AG6

DDR4A_DQ[10]

Data [10]

1.2-V POD

PIN_AD6

DDR4A_DQ[11]

Data [11]

1.2-V POD

PIN_AG5

DDR4A_DQ[12]

Data [12]

1.2-V POD

PIN_AK5

DDR4A_DQ[13]

Data [13]

1.2-V POD

PIN_AC7

DDR4A_DQ[14]

Data [14]

1.2-V POD

PIN_AH6

DDR4A_DQ[15]

Data [15]

1.2-V POD

PIN_AK1

DDR4A_DQ[16]

Data [16]

1.2-V POD

PIN_AL4

DDR4A_DQ[17]

Data [17]

1.2-V POD

PIN_AJ4

DDR4A_DQ[18]

Data [18]

1.2-V POD

PIN_AM1

DDR4A_DQ[19]

Data [19]

1.2-V POD

PIN_AK3

DDR4A_DQ[20]

Data [20]

1.2-V POD

PIN_AL2

DDR4A_DQ[21]

Data [21]

1.2-V POD

PIN_AJ3

DDR4A_DQ[22]

Data [22]

1.2-V POD

PIN_AM2

DDR4A_DQ[23]

Data [23]

1.2-V POD

PIN_AF2

DDR4A_DQ[24]

Data [24]

1.2-V POD

PIN_AH1

DDR4A_DQ[25]

Data [25]

1.2-V POD

PIN_AG4

DDR4A_DQ[26]

Data [26]

1.2-V POD

PIN_AE5

DDR4A_DQ[27]

Data [27]

1.2-V POD

PIN_AF3

DDR4A_DQ[28]

Data [28]

1.2-V POD

PIN_AH4

DDR4A_DQ[29]

Data [29]

1.2-V POD

PIN_AG1

DDR4A_DQ[30]

Data [30]

1.2-V POD

PIN_AF4

DDR4A_DQ[31]

Data [31]

1.2-V POD

PIN_K1

DDR4A_DQ[32]

Data [32]

1.2-V POD

PIN_P4

DDR4A_DQ[33]

Data [33]

1.2-V POD

PIN_N2

DDR4A_DQ[34]

Data [34]

1.2-V POD

PIN_K2

DDR4A_DQ[35]

Data [35]

1.2-V POD

PIN_M2

DDR4A_DQ[36]

Data [36]

1.2-V POD

PIN_P3

DDR4A_DQ[37]

Data [37]

1.2-V POD

PIN_N1

DDR4A_DQ[38]

Data [38]

1.2-V POD

Page 42

HAN Pilot Platform

Hardware Manual

41

www.terasic.com

July 5, 2019

PIN_J1

DDR4A_DQ[39]

Data [39]

1.2-V POD

PIN_N3

DDR4A_DQ[40]

Data [40]

1.2-V POD

PIN_P5

DDR4A_DQ[41]

Data [41]

1.2-V POD

PIN_M5

DDR4A_DQ[42]

Data [42]

1.2-V POD

PIN_R2

DDR4A_DQ[43]

Data [43]

1.2-V POD

PIN_N4

DDR4A_DQ[44]

Data [44]

1.2-V POD

PIN_P6

DDR4A_DQ[45]

Data [45]

1.2-V POD

PIN_L4

DDR4A_DQ[46]

Data [46]

1.2-V POD

PIN_R3

DDR4A_DQ[47]

Data [47]

1.2-V POD

PIN_V6

DDR4A_DQ[48]

Data [48]

1.2-V POD

PIN_T7

DDR4A_DQ[49]

Data [49]

1.2-V POD

PIN_U5

DDR4A_DQ[50]

Data [50]

1.2-V POD

PIN_U7

DDR4A_DQ[51]

Data [51]

1.2-V POD

PIN_T4

DDR4A_DQ[52]

Data [52]

1.2-V POD

PIN_W6

DDR4A_DQ[53]

Data [53]

1.2-V POD

PIN_T3

DDR4A_DQ[54]

Data [54]

1.2-V POD

PIN_U6

DDR4A_DQ[55]

Data [55]

1.2-V POD

PIN_W8

DDR4A_DQ[56]

Data [56]

1.2-V POD

PIN_Y12

DDR4A_DQ[57]

Data [57]

1.2-V POD

PIN_Y11

DDR4A_DQ[58]

Data [58]

1.2-V POD

PIN_W10

DDR4A_DQ[59]

Data [59]

1.2-V POD

PIN_Y13

DDR4A_DQ[60]

Data [60]

1.2-V POD

PIN_Y8

DDR4A_DQ[61]

Data [61]

1.2-V POD

PIN_Y10

DDR4A_DQ[62]

Data [62]

1.2-V POD

PIN_W11

DDR4A_DQ[63]

Data [63]

1.2-V POD

PIN_V1

DDR4A_DQ[64]

Data [64]

1.2-V POD

PIN_Y1

DDR4A_DQ[65]

Data [65]

1.2-V POD

PIN_W3

DDR4A_DQ[66]

Data [66]

1.2-V POD

PIN_W1

DDR4A_DQ[67]

Data [67]

1.2-V POD

PIN_Y3

DDR4A_DQ[68]

Data [68]

1.2-V POD

PIN_W4

DDR4A_DQ[69]

Data [69]

1.2-V POD

PIN_U1

DDR4A_DQ[70]

Data [70]

1.2-V POD

PIN_U2

DDR4A_DQ[71]

Data [71]

1.2-V POD

Page 43

HAN Pilot Platform

Hardware Manual

42

www.terasic.com

July 5, 2019

PIN_AD9

DDR4A_DBI_n[0]

Data Bus Inversion [0]

1.2-V POD

PIN_AJ5

DDR4A_DBI_n[1]

Data Bus Inversion [1]

1.2-V POD

PIN_AK2

DDR4A_DBI_n[2]

Data Bus Inversion [2]

1.2-V POD

PIN_AG2

DDR4A_DBI_n[3]

Data Bus Inversion [3]

1.2-V POD

PIN_L2

DDR4A_DBI_n[4]

Data Bus Inversion [4]

1.2-V POD

PIN_L3

DDR4A_DBI_n[5]

Data Bus Inversion [5]

1.2-V POD

PIN_U4

DDR4A_DBI_n[6]

Data Bus Inversion [6]

1.2-V POD

PIN_V8

DDR4A_DBI_n[7]

Data Bus Inversion [7]

1.2-V POD

PIN_V4

DDR4A_DBI_n[8]

Data Bus Inversion [8]

1.2-V POD

PIN_AE1

DDR4A_CS_n

Chip Select

SSTL-12

PIN_AE3

DDR4A_RESET_n

Chip Reset

1.2 V

PIN_AC3

DDR4A_ODT

On Die Termination

SSTL-12

PIN_AC6

DDR4A_PAR

Command and Address Parity

Input

SSTL-12

PIN_AC12

DDR4A_ALERT_n

Register ALERT_n output

SSTL-12

PIN_AD1

DDR4A_ACT_n

Activation Command Input

SSTL-12

PIN_T5

DDR4A_EVENT_n

Chip Temperature Event

1.2 V

PIN_AD5

DDR4A_AC_R[0]

Reserved for

QDRII+/RLDRAM3

SSTL-12

PIN_Y6

DDR4A_AC_R[1]

Reserved for

QDRII+/RLDRAM3

SSTL-12

PIN_AC4

DDR4A_C[0]

Reserved for

QDRII+/RLDRAM3

SSTL-12

PIN_AB2

DDR4A_C[1]

Reserved for

QDRII+/RLDRAM3

SSTL-12

PIN_AA8

DDR4A_RZQ

External reference ball for

output drive calibration

1.2 V

The DDR4 SDRAM SO-DIMM socket can support many kinds of memory devices, such as

standard DDR4 SO-DIMM with ECC up to 8GB at 1067MHz, Terasic QDRII+ module, as shown

in Figure 4-17, Figure 4-18.

Page 44

HAN Pilot Platform

Hardware Manual

43

www.terasic.com

July 5, 2019

Figure 4-17 Standard DDR4 SO-DIMM with ECC

Figure 4-18 Terasic QDRII+ module with DDR4 SO-DIMM interface

44..7

7

HHDDMMII TTrraannssmmiitttteerr aanndd RReecceeiivveerr

The HAN Pilot Platform board features HDMI transmitter and receiver.

For HDMI transmitter, as shown in Figure 4-19. The board features a Transition Minimized

Differential Signal (TMDS) retimer IC (TI:SN75DP159). Users can implement Intel or third-party

IP in FPGA; HDMI video or audio data is encoded to TMDS signal and output from FPGA

transceiver. The signals transmit to the retimer IC and display on HDMI monitor through HDMI

connector.

For HDMI Receiver, it features a Redriver IC (DIDOES: PI3HDX1204B1). It transmits the input

TMDS signal into FPGA, and decoded to image video data by Intel or third-party IP, then will be

processed next step. Table 4-15 lists the HDMI Transmitter and Receiver pin assignments, signal

names and functions.

Page 45

HAN Pilot Platform

Hardware Manual

44

www.terasic.com

July 5, 2019

Figure 4-19 The HDMI transceiver interface of the HAN Pilot Platform

Table 4-15 HDMI TX and RX port Pin Assignments, Signal Names and Functions

Signal Name

FPGA Pin

Number

Description

I/O Standard

HDMI_REFCLK_p

V31

HDMI reference clock from

external PLL

LVDS

HDMI_TX_CLK_p

V39

TX TMDS clock channel

HSSI Differential I/O

HDMI_TX_D_p[0]

U37

TX TMDS data channel 0

HSSI Differential I/O

HDMI_TX_D_p[1]

T39

TX TMDS data channel 1

HSSI Differential I/O

HDMI_TX_D_p[2]

R37

TX TMDS data channel 2

HSSI Differential I/O

HDMI_TX_SCL

A25

I2C clock of the TX re-timer IC

and DCC

1.8V

HDMI_TX_SDA

AB25

I2C data of the TX re-timer IC

and DCC

1.8V

HDMI_HPD

AF28

TX Hot Plug Detect

1.8V

HDMI_TX_CEC

AK26

HDMI TX Consumer

Electronics Control

1.8V

HDMI_RX_CLK_p

Y31

RX TMDS clock channel

HSSI Differential I/O

HDMI_RX_D_p[0]

Y35

RX TMDS data channel 0

HSSI Differential I/O

Page 46

HAN Pilot Platform

Hardware Manual

45

www.terasic.com

July 5, 2019

HDMI_RX_D_p[1]

W37

RX TMDS data channel 1

HSSI Differential I/O

HDMI_RX_D_p[2]

W33

RX TMDS data channel 2

HSSI Differential I/O

HDMI_RX_SCL

V7

I2C clock of the RX re-driver IC

1.2 V

HDMI_RX_SDA

T2

I2C clock of the RX re-driver IC

1.2 V

HDMI_HPD_RX

AG27

RX Hot Plug Detect

1.8V

HDMI_RX_5V_N

B26

Detect if the TX terminal has 5V

output

1.8V

HDMI_RX_CEC

AP29

HDMI RX Consumer

Electronics Control

1.8V

DDCSCL_RX

AN27

HDMI DDC(Display Data

Channel) I2C clock

1.8V

DDCSDA_RX

AJ26

HDMI DDC(Display Data

Channel) I2C data

1.8V

44..8

8

GGiiggaabbiitt EEtthheerrnneett

The development board supports one RJ45 10/100/1000 base-T Ethernet using Marvell 88E1111.

SGMII AC coupling interface is used between PHY and FPGA transceiver. The device is an

auto-negotiating Ethernet PHY with an SGMII interface to the FPGA. The Arria 10 SoC FPGA can

communicate with the LVDS interfaces at up to 1.6 Gbps, which is faster than 1.25 Gbps for SGMII.

The MAC function must be provided in the FPGA for typical networking applications. The Marvell

88E1111 PHY uses 2.5-V and 1.1-V power rails and requires a 25MHz reference clock driven from

a dedicated oscillator. It interfaces to an RJ-45 with internal magnetics for driving copper lines with

Ethernet traffic. Figure 4-20 shows the SGMII interface between the FPGA and Marvell 88E1111

PHY. Table 4-16 lists the Ethernet PHY interface pin assignments.

Figure 4-20 SGMII Interface between FPGA and Marvell 88E1111 PHY

Table 4-16 Ethernet PHY Pin Assignments, Signal Names and Functions

Signal Name

FPGA Pin Number

Description

I/O Standard

ETH_TX_p

PIN_AP19

SGMII TX data

LVDS

ETH_RX_p

PIN_AM20

SGMII RX data

LVDS

ETH_INT_n

PIN_AU19

Management bus interrupt

1.8V

Page 47

HAN Pilot Platform

Hardware Manual

46

www.terasic.com

July 5, 2019

ETH_MDC

PIN_AT19

Management bus control

1.8V

ETH_MDIO

PIN_AJ20

Management bus data

1.8V

ETH_RST_n

PIN_AK20

Device reset

1.8V

44..9

9

FFMMCC CCoonnnneeccttoorr

The FPGA Mezzanine Card (FMC) interface provides a mechanism to extend the peripheral-set of

an FPGA host board by means of add-on daughter cards, which can address today’s high-speed

signaling requirements as well as low-speed device interface support. The FMC interfaces support

JTAG, clock outputs and inputs, high-speed serial I/O (transceivers), and single-ended or differential

signaling.

There is one FMC connector on the HAN Pilot Platform board, it is a High Pin Count (HPC) size of

connector, The HPC connector on HAN Pilot Platform board can provides 172 user-define,

single-ended signals (include clock signals) and 10 serial transceiver pairs. Figure 4-21 is the FMC

connector on HAN Pilot Platform board. Table 4-17 lists the FMC connector pin assignments,

signal names and functions

Figure 4-21 FMC connector on HAN Pilot Platform board

Table 4-17 FMC Connector Pin Assignments, Signal Names and Functions

Signal Name

FPGA Pin Number

Description

I/O Standard

FMC_CLK2_BIDIR_p

PIN_AW18

FMC bidirection Clock

signal

1.8 V

FMC_CLK2_BIDIR_n

PIN_AV17

FMC bidirection Clock

signal

1.8 V

FMC_CLK3_BIDIR_p

PIN_C1

FMC bidirection Clock

signal

1.8 V

FMC_CLK3_BIDIR_n

PIN_D1

FMC bidirection Clock

signal

1.8 V

FMC_CLK_M2C_p[0]

PIN_K5

Clock input 0

1.8 V

Page 48

HAN Pilot Platform

Hardware Manual

47

www.terasic.com

July 5, 2019

FMC_CLK_M2C_p[1]

PIN_AW14

Clock input 1

1.8 V

FMC_CLK_M2C_n[0]

PIN_L5

Clock input 0

1.8 V

FMC_CLK_M2C_n[1]

PIN_AW15

Clock input 1

1.8 V

FMC_HA_p[0]

PIN_K12

FMC data bus

1.8 V

FMC_HA_p[1]

PIN_M12

FMC data bus

1.8 V

FMC_HA_p[2]

PIN_D10

FMC data bus

1.8 V

FMC_HA_p[3]

PIN_E12

FMC data bus

1.8 V

FMC_HA_p[4]

PIN_H13

FMC data bus

1.8 V

FMC_HA_p[5]

PIN_J11

FMC data bus

1.8 V

FMC_HA_p[6]

PIN_N13

FMC data bus

1.8 V

FMC_HA_p[7]

PIN_L13

FMC data bus

1.8 V

FMC_HA_p[8]

PIN_J14

FMC data bus

1.8 V

FMC_HA_p[9]

PIN_F13

FMC data bus

1.8 V

FMC_HA_p[10]

PIN_D13

FMC data bus

1.8 V

FMC_HA_p[11]

PIN_G14

FMC data bus

1.8 V

FMC_HA_p[12]

PIN_A10

FMC data bus

1.8 V

FMC_HA_p[13]

PIN_G12

FMC data bus

1.8 V

FMC_HA_p[14]

PIN_A12

FMC data bus

1.8 V

FMC_HA_p[15]

PIN_A7

FMC data bus

1.8 V

FMC_HA_p[16]

PIN_A9

FMC data bus

1.8 V

FMC_HA_p[17]

PIN_C12

FMC data bus

1.8 V

FMC_HA_p[18]

PIN_B11

FMC data bus

1.8 V

FMC_HA_p[19]

PIN_M7

FMC data bus

1.8 V

FMC_HA_p[20]

PIN_F10

FMC data bus

1.8 V

FMC_HA_p[21]

PIN_C9

FMC data bus

1.8 V

FMC_HA_p[22]

PIN_C8

FMC data bus

1.8 V

FMC_HA_p[23]

PIN_G11

FMC data bus

1.8 V

FMC_HA_n[0]

PIN_L12

FMC data bus

1.8 V

FMC_HA_n[1]

PIN_N12

FMC data bus

1.8 V

FMC_HA_n[2]

PIN_E10

FMC data bus

1.8 V

FMC_HA_n[3]

PIN_F12

FMC data bus

1.8 V

FMC_HA_n[4]

PIN_J13

FMC data bus

1.8 V

FMC_HA_n[5]

PIN_K11

FMC data bus

1.8 V

Page 49

HAN Pilot Platform

Hardware Manual

48

www.terasic.com

July 5, 2019

FMC_HA_n[6]

PIN_P13

FMC data bus

1.8 V

FMC_HA_n[7]

PIN_L14

FMC data bus

1.8 V

FMC_HA_n[8]

PIN_K13

FMC data bus

1.8 V

FMC_HA_n[9]

PIN_F14

FMC data bus

1.8 V

FMC_HA_n[10]

PIN_E13

FMC data bus

1.8 V

FMC_HA_n[11]

PIN_H14

FMC data bus

1.8 V

FMC_HA_n[12]

PIN_B10

FMC data bus

1.8 V

FMC_HA_n[13]

PIN_H12

FMC data bus

1.8 V

FMC_HA_n[14]

PIN_B12

FMC data bus

1.8 V

FMC_HA_n[15]

PIN_A8

FMC data bus

1.8 V

FMC_HA_n[16]

PIN_B9

FMC data bus

1.8 V

FMC_HA_n[17]

PIN_C13

FMC data bus

1.8 V

FMC_HA_n[18]

PIN_C11

FMC data bus

1.8 V

FMC_HA_n[19]

PIN_N7

FMC data bus

1.8 V

FMC_HA_n[20]

PIN_G10

FMC data bus

1.8 V

FMC_HA_n[21]

PIN_D9

FMC data bus

1.8 V

FMC_HA_n[22]

PIN_D8

FMC data bus

1.8 V

FMC_HA_n[23]

PIN_H11

FMC data bus

1.8 V

FMC_HB_p[0]

PIN_E1

FMC data bus

1.8 V

FMC_HB_p[1]

PIN_G4

FMC data bus

1.8 V

FMC_HB_p[2]

PIN_N8

FMC data bus

1.8 V

FMC_HB_p[3]

PIN_J4

FMC data bus

1.8 V

FMC_HB_p[4]

PIN_H2

FMC data bus

1.8 V

FMC_HB_p[5]

PIN_G5

FMC data bus

1.8 V

FMC_HB_p[6]

PIN_D3

FMC data bus

1.8 V

FMC_HB_p[7]

PIN_A2

FMC data bus

1.8 V

FMC_HB_p[8]

PIN_B1

FMC data bus

1.8 V

FMC_HB_p[9]

PIN_AT13

FMC data bus

1.8 V

FMC_HB_p[10]

PIN_AM17

FMC data bus

1.8 V

FMC_HB_p[11]

PIN_AJ16

FMC data bus

1.8 V

FMC_HB_p[12]

PIN_AW13

FMC data bus

1.8 V

FMC_HB_p[13]

PIN_AV14

FMC data bus

1.8 V

FMC_HB_p[14]

PIN_AP14

FMC data bus

1.8 V

Page 50

HAN Pilot Platform

Hardware Manual

49

www.terasic.com

July 5, 2019

FMC_HB_p[15]

PIN_AK16

FMC data bus

1.8 V

FMC_HB_p[16]

PIN_AU16

FMC data bus

1.8 V

FMC_HB_p[17]

PIN_AT17

FMC data bus

1.8 V

FMC_HB_p[18]

PIN_AM15

FMC data bus

1.8 V

FMC_HB_p[19]

PIN_AR15

FMC data bus

1.8 V

FMC_HB_p[20]

PIN_AP16

FMC data bus

1.8 V

FMC_HB_p[21]

PIN_AV18

FMC data bus

1.8 V

FMC_HB_n[0]

PIN_E2

FMC data bus

1.8 V

FMC_HB_n[1]

PIN_H4

FMC data bus

1.8 V

FMC_HB_n[2]

PIN_P8

FMC data bus

1.8 V

FMC_HB_n[3]

PIN_J5

FMC data bus

1.8 V

FMC_HB_n[4]

PIN_H3

FMC data bus

1.8 V

FMC_HB_n[5]

PIN_H6

FMC data bus

1.8 V

FMC_HB_n[6]

PIN_E3

FMC data bus

1.8 V

FMC_HB_n[7]

PIN_B2

FMC data bus

1.8 V

FMC_HB_n[8]

PIN_C2

FMC data bus

1.8 V

FMC_HB_n[9]

PIN_AT14

FMC data bus

1.8 V

FMC_HB_n[10]

PIN_AL17

FMC data bus

1.8 V

FMC_HB_n[11]

PIN_AH16

FMC data bus

1.8 V

FMC_HB_n[12]

PIN_AV13

FMC data bus

1.8 V

FMC_HB_n[13]

PIN_AU14

FMC data bus

1.8 V

FMC_HB_n[14]

PIN_AP15

FMC data bus

1.8 V

FMC_HB_n[15]

PIN_AK17

FMC data bus

1.8 V

FMC_HB_n[16]

PIN_AU17

FMC data bus

1.8 V

FMC_HB_n[17]

PIN_AT18

FMC data bus

1.8 V

FMC_HB_n[18]

PIN_AM16

FMC data bus

1.8 V

FMC_HB_n[19]

PIN_AR16