Page 1

Altera DE3 Board

Page 2

Altera DE3 Board

ii

CONTENTS

Chapter 1 Overview ........................................................................................................................... 1

1.1 Introduction .......................................................................................................................... 1

1.2 Layout and Components ...................................................................................................... 1

1.3 Block Diagram of the DE3 Board ........................................................................................ 4

Chapter 2 Using the DE3 Board ....................................................................................................... 8

2.1 Configuring the FPGA and Serial Configuration Device .................................................... 8

2.2 JTAG Chain ........................................................................................................................ 10

2.3 Using the User I/O Interface .............................................................................................. 13

2.4 I/O Groups and V

CCIO

Control Circuit ............................................................................... 14

2.5 Using the HSTC Connectors .............................................................................................. 17

2.6 Connecting HSTC/HSMC Daughter Boards to DE3 HSTC connectors ........................... 20

2.7 Using the GPIO Expansion Headers .................................................................................. 20

2.8 Using the DDR2 SO-DIMM .............................................................................................. 21

2.9 Using the USB OTG .......................................................................................................... 22

2.10 Using the SD Card ............................................................................................................. 23

2.11 LED Indicators ................................................................................................................... 24

2.12 Clock Circuitry ................................................................................................................... 24

2.13 Using the Temperature Sensor ........................................................................................... 27

Chapter 3 Control Panel .................................................................................................................. 28

3.1 Control Panel Setup ........................................................................................................... 28

3.2 Controlling the LEDs and 7-Segment Displays ................................................................. 31

3.3 SWITCH/BUTTON ........................................................................................................... 33

3.4 Memory Controller ............................................................................................................ 33

3.5 USB2.0 OTG ...................................................................................................................... 35

3.6 SD CARD .......................................................................................................................... 36

3.7 Temperature Monitor ......................................................................................................... 37

3.8 I/O Group ........................................................................................................................... 38

3.9 Overall Structure of the DE3 Control Panel ...................................................................... 40

Chapter 4 DE3 System Builder ....................................................................................................... 41

4.1 Introduction ........................................................................................................................ 41

4.2 General Design Flow ......................................................................................................... 41

4.3 Using DE3 System Builder ................................................................................................ 43

4.4 Creating My First DE3 Project .......................................................................................... 49

4.5 Connect TERASIC Daughter Boards to a DE3 Board ...................................................... 50

4.6 Connect Multiple DE3 Boards ........................................................................................... 53

4.7 Connect a Custom-Made Daughter Board to the DE3 Board ............................................ 56

Page 3

Altera DE3 Board

iii

Chapter 5 Examples of Advanced Demonstration ........................................................................ 58

5.1 USB Host ........................................................................................................................... 58

5.2 USB Device........................................................................................................................ 65

5.3 SD Card .............................................................................................................................. 68

5.4 DDR2 SDRAM .................................................................................................................. 73

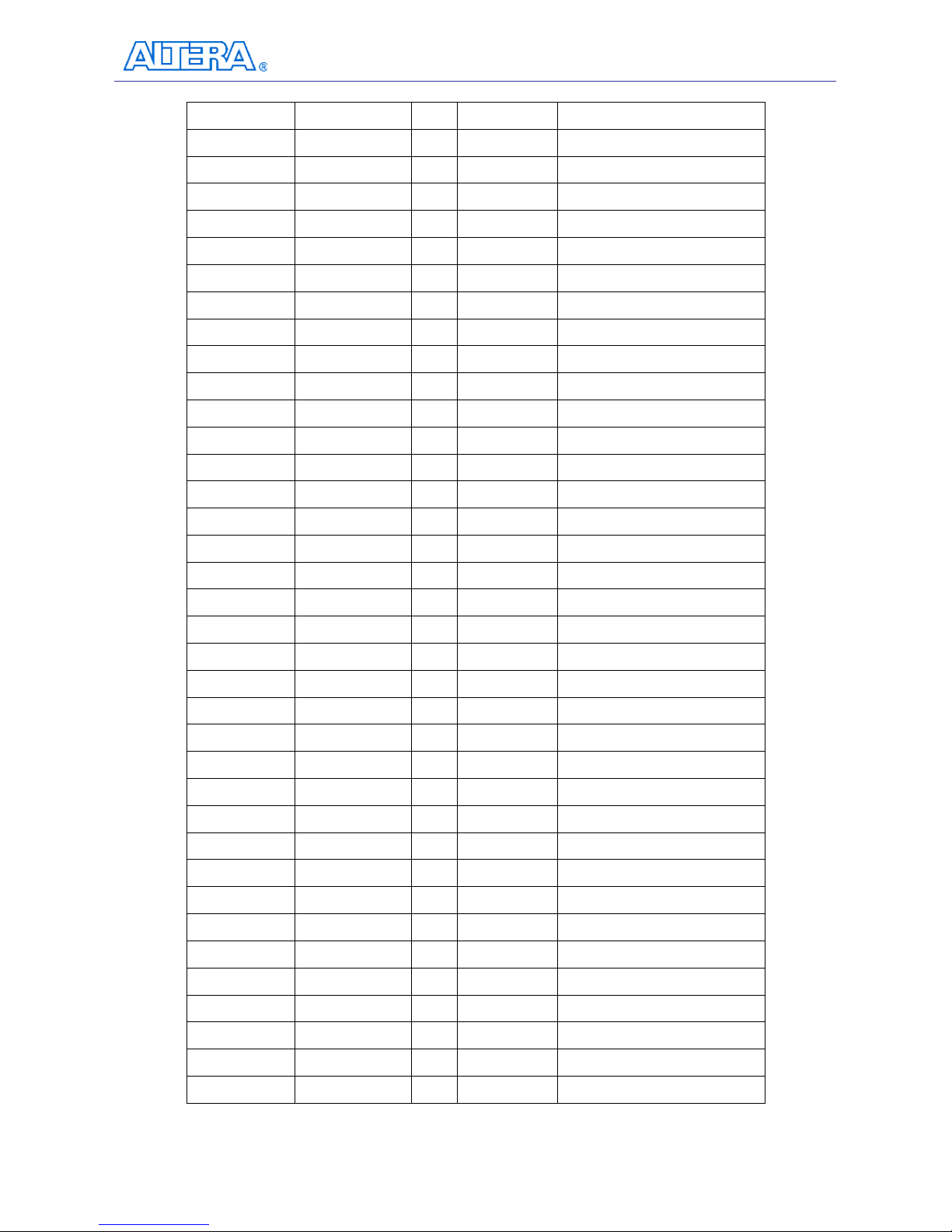

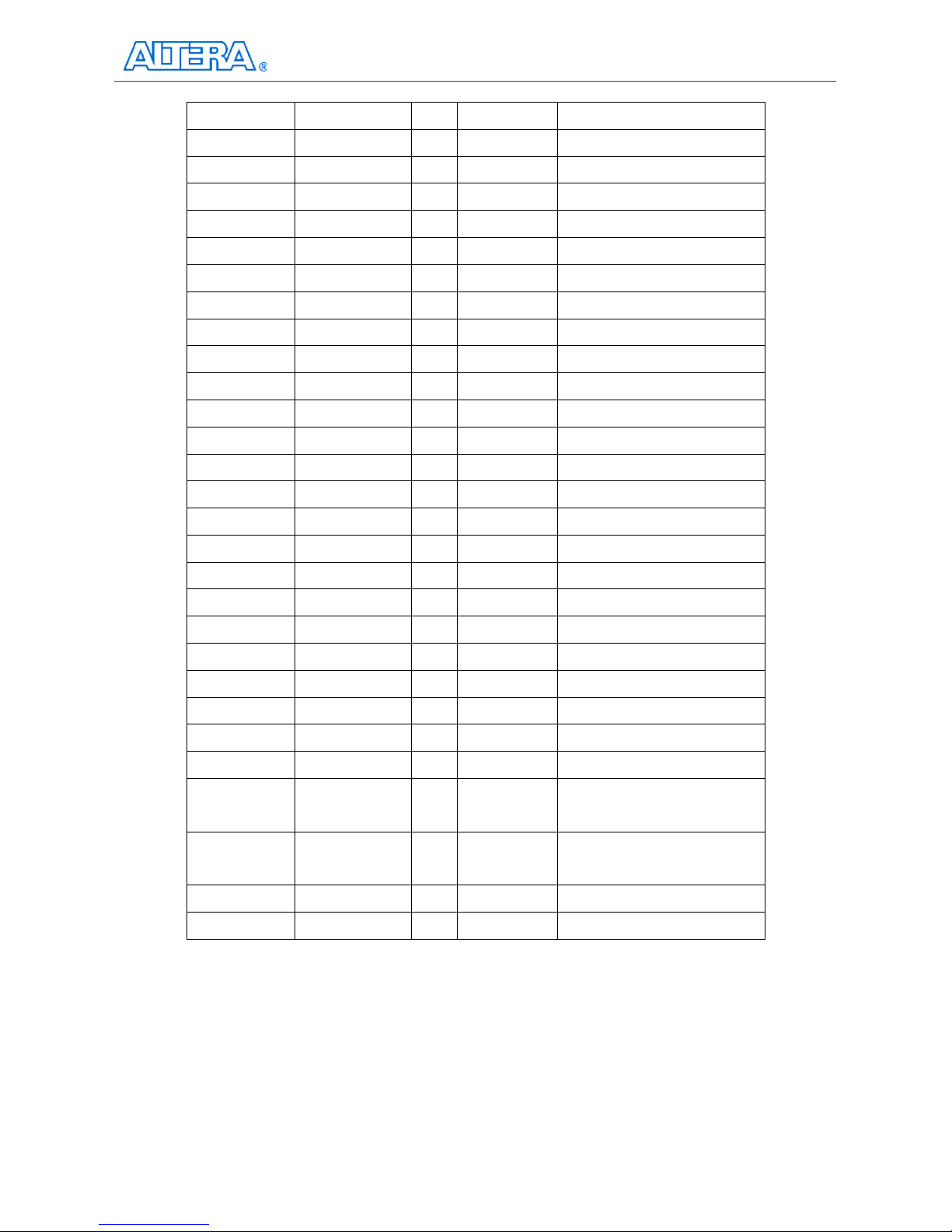

Appendix A Pin connections between components and FPGA on the DE3 board ..................... 80

Appendix B Pin Compatible List for HSTC and HSMC Connector .......................................... 98

Appendix C Programming the Serial Configuration Device ..................................................... 102

Appendix D DE3_HSTC Utility .................................................................................................... 108

Appendix E LVDS Termination Resistors ................................................................................... 112

Additional Information.................................................................................................................. 114

Getting Help ................................................................................................................................. 114

Revision History .......................................................................................................................... 114

Page 4

DE3 User Manual

1

Chapter 1

Overview

1

This chapter presents the features and design characteristics of the DE3 board.

1.1 Introduction

The DE3 board has plenty of features that allow users to implement a wide range of designed

circuits. The Stratix® III device is capable of dealing with resource-consuming projects and

complex algorithm verification; the HSTC interface is equipped for high-speed inter-connection and

configurable I/O standards. The DDR2 SO-DIMM socket puts the experience of faster memory

access into practice, while the SD card socket provides the realization of data storage extension.

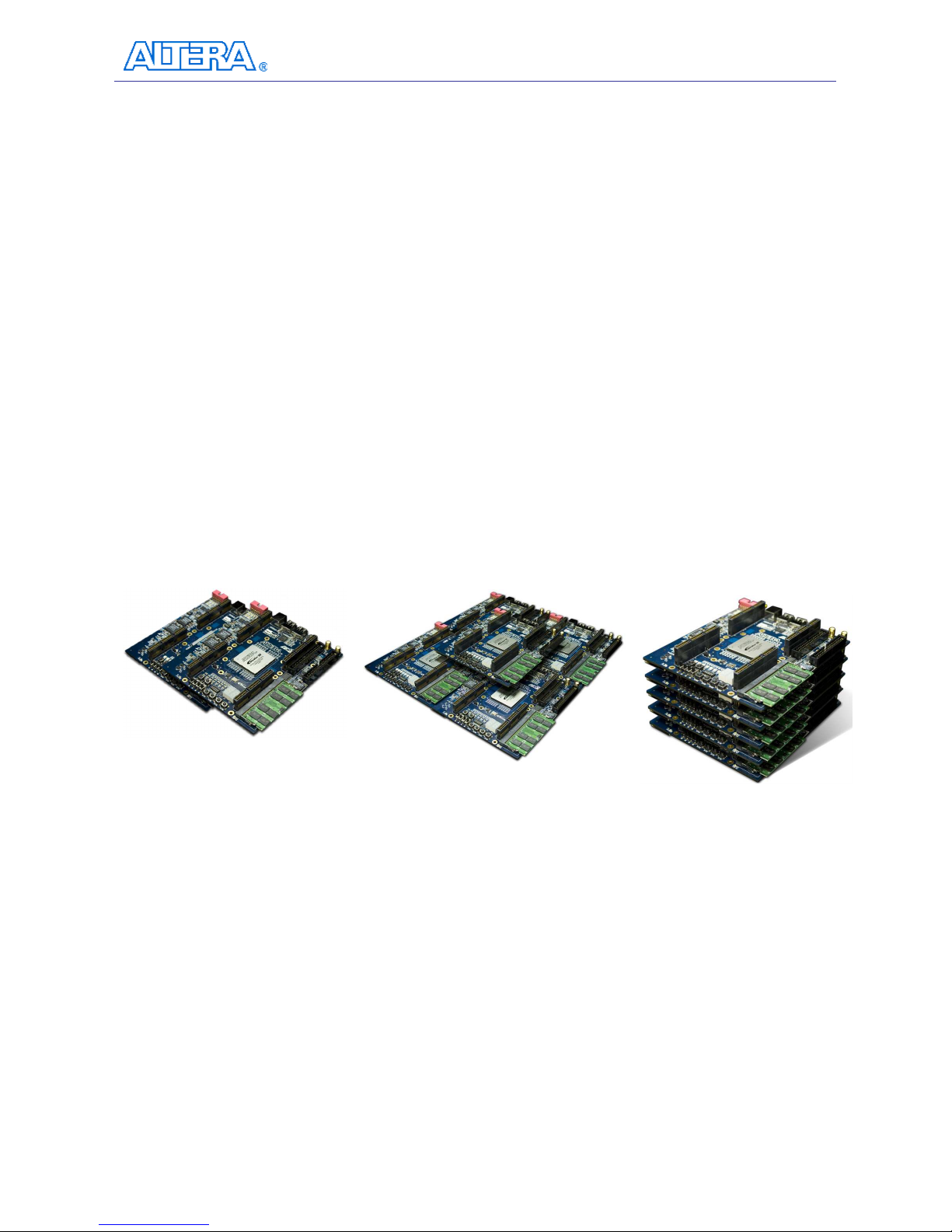

In addition, the DE3 board has an innovative stackable mechanism which allows users to assemble

DE3 boards into a powerful system as shown in Figure 1.1. The DE3 can also connect with multiple

daughter boards designed by Terasic in stock.

Figure 1.1 The stackable mechanism of the DE3 board

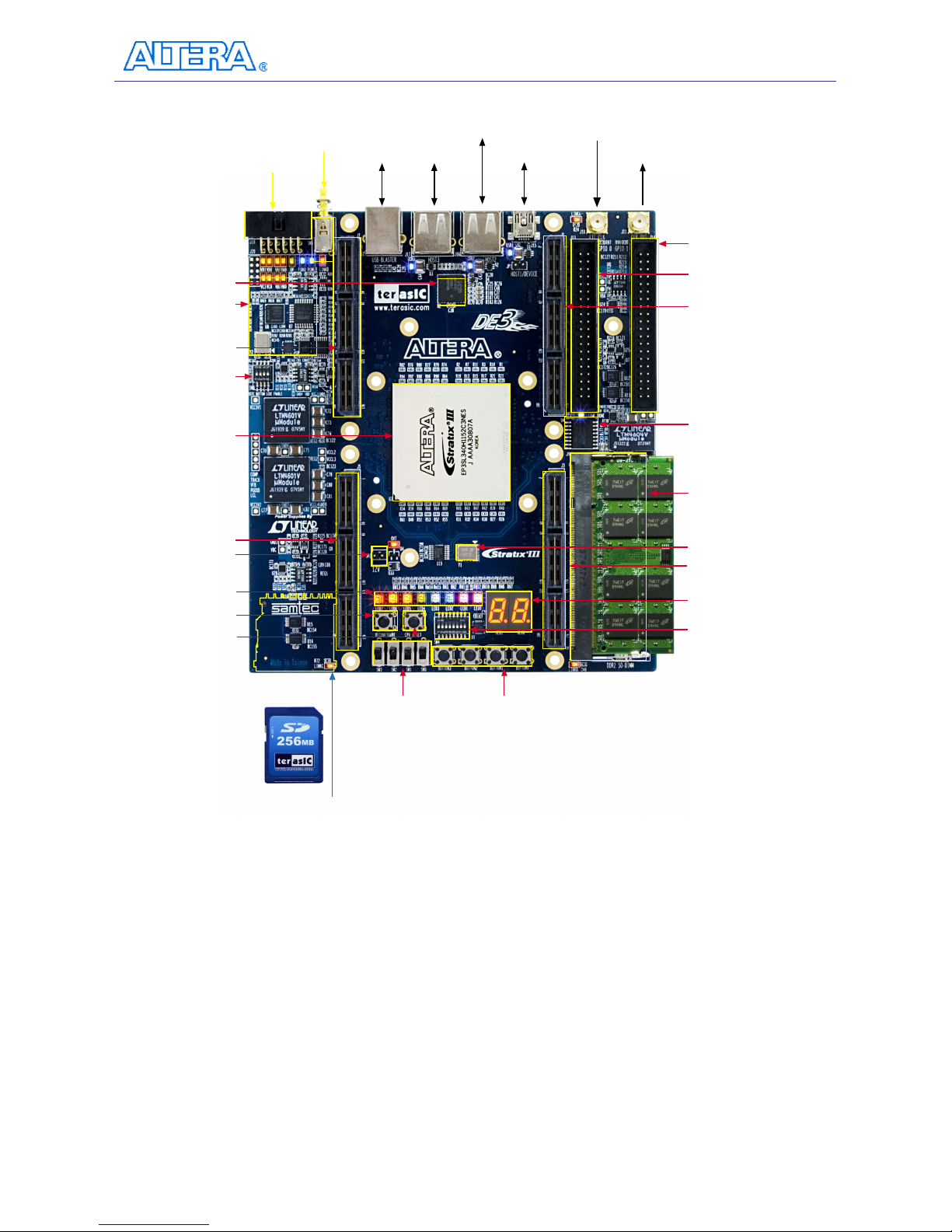

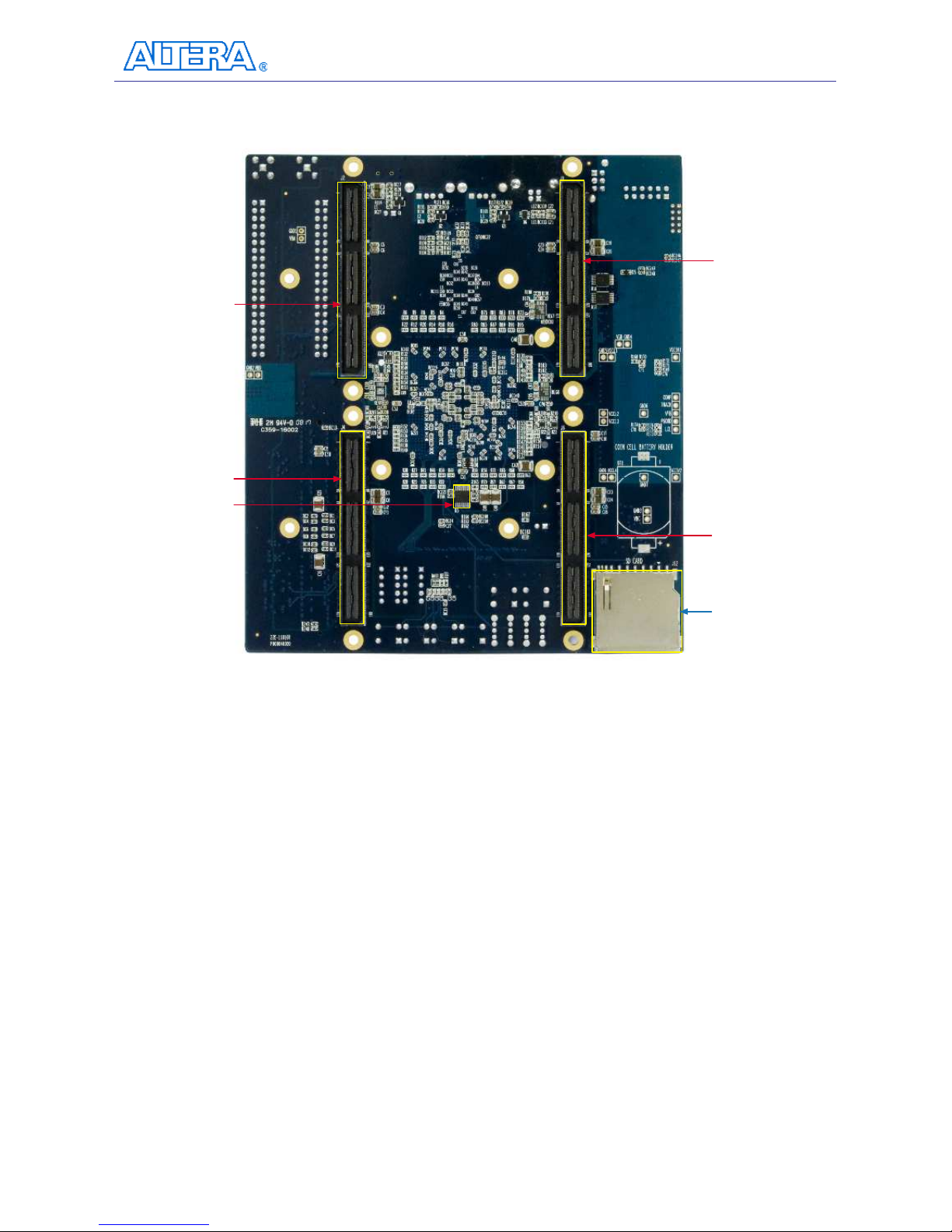

1.2 Layout and Components

Figure 1.2 and Figure 1.3 is the top and bottom view of the DE3 board. It depicts the layout of the

board and indicates the location of the connectors and key components. Users can refer to this

figure for relative location when the connectors and key components are introduced in the following

chapters.

Page 5

DE3 User Manual

2

50MHz Oscillator

Expansion Header 2

SMA External Clock In

DDR2 SO-DIMM Socket

4 Slide Switches

7-Segment Displays

Altera USB Blaster

Controller Chipset

Altera EPCS128 / EPCS64

Configuration Device

USB Host/Device

Controller

HSTC Bottom Side

Enable

8 RGB LEDs

Expansion Header 1

4 Push-Button Switches

USB Blaster

Power ON/OFF Switch

Power Supply

Connector

USB Device

SD Card Slot

USB Device

USB Host/Device SMA PLL Clock Out

Altera Stratix III

3SL340 (DE3-340)

or

3SL260 (DE3-260)

or

3SL150 (DE3-150)

Reconfigure Switch

CPU RESET Switch

8-Position Dip Switch

HSTC Connector C

HSTC Connector D

HSTC Connector B

HSTC Connector A

+12V Fan Connector

Figure 1.2 The DE3 board (Top view)

Page 6

DE3 User Manual

3

Temperature Sensor

HSTC connector B

HSTC connector A

HSTC connector C

SD Card Slot

HSTC connector D

Figure 1.3. The DE3 board (Bottom view)

The following hardware is implemented on the DE3 board:

• Altera Stratix® III FPGA device (3SL340/3SE260/3SL150)

• FPGA configuration interface:

Built-in USB Blaster circuit for programming and user API control

Altera Serial Configuration device – EPCS128/EPCS64

• Expansion Interface:

8 HSTC connectors

Two 40-pin Expansion Headers

• Memory Interface:

DDR2 SO-DIMM socket

SD Card socket

Page 7

DE3 User Manual

4

• User I/O Interface:

4 push-button switches

4 slide switches

1 eight position DIP switch

2 seven-segment displays

8 RGB LEDs

• Clock system

One 50MHz oscillator

2 SMA connectors for external clock input and PLL clock output

• Other interface

1 USB Host/Slave controller(1 three-ports USB Host/Device controller)

1 temperature sensor chip for FPGA temperature measurement

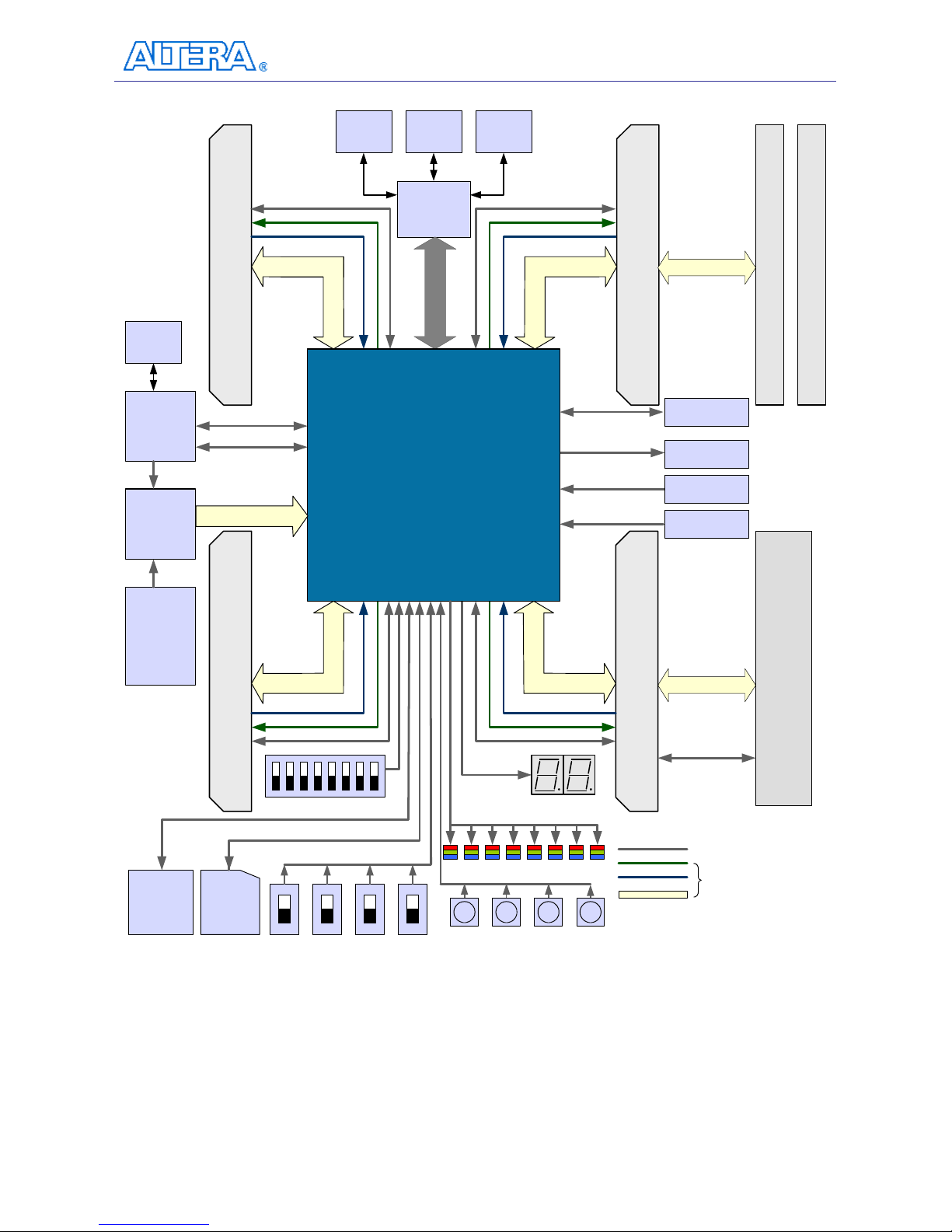

1.3 Block Diagram of the DE3 Board

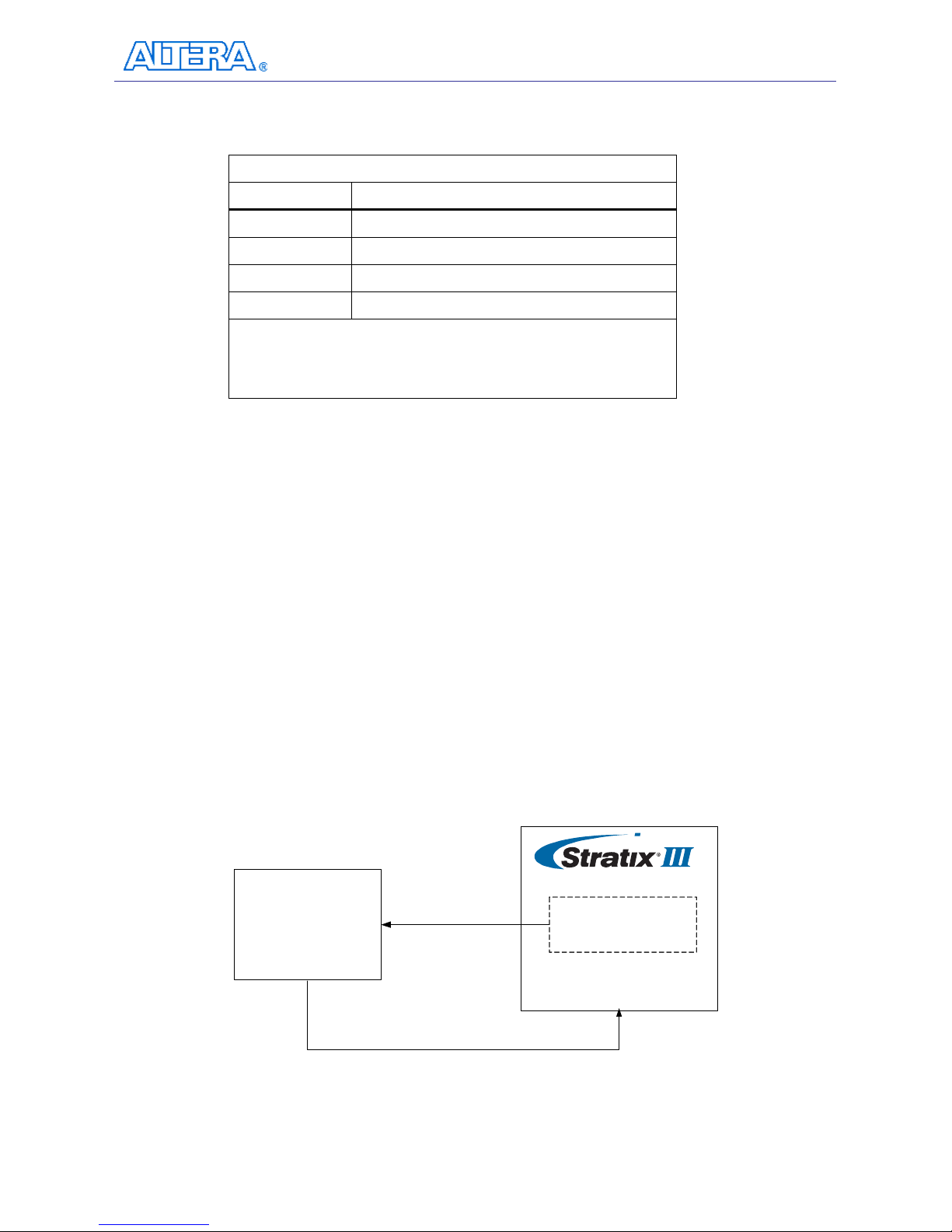

Figure 1.4 shows the block diagram of the DE3 board. To provide maximum flexibility for the users,

all key components are connected with the Stratix III FPGA device. Thus, users can configure the

FPGA to implement any system design.

Page 8

DE3 User Manual

5

Power

1.1V

3.3V

5.0V

12V

GPIO 0

EPCS128

HOST

CON

x120

USB

Hi-Speed

OTG

x60

HSTC C

HSTC B

HSTC A

HSTC D

DDR2 SO-DIMM

x120 x120

x120

Clock IN x5

Clock OUT x5

Clock IN x5

Clock OUT x5

Clock IN x5

Clock OUT x5

1.5V

1.8V

2.5V

3.3V

VCCIO(BA,BB,BC,BD)

PLL_OUT

CLOCK_IN

Clock IN x5

Clock OUT x5

HOST

CON

DEVICE

CON

GPIO 1

x80

PLL OUT

CLOCK IN

50 MHz

OSC

OSC x6

EPM240

JTAG x4

USB

CON

7-Seg x 16

DIP Switch x 8

I2C x2

I2C x2

I2C x2

I2C x2

JVC x4

Select and

Power ON

I2C x2

Stratix III

EP3SL150F1152/

EP3SL340F1152/

EP3SE260F1152

Adjustable Voltage Signal

3.3V

Bank I/O Voltage

3.3V Signal

SD Card

Socket

Button Switch x4

Color LED x 24

Slider Switch x4

SD Card x 4

x120

Temperature

Sensor

Temp. Sensor x 6

Figure 1.4 Block diagram of the DE3 board

Page 9

DE3 User Manual

6

Below is more detailed information regarding the blocks in

Figure 1.4:

Stratix III FPGA

•

EP3SL340

- 338,000 logic elements (LEs)

- 18,381K Total Memory Kbits

- 526 18x18-bit Multipliers blocks

- 12 phase-locked-loops (PLLs)

-

•

EP3SE260

- 254,400 logic elements (LEs)

- 16,282K Total Memory Kbits

- 768 18x18-bit Multipliers blocks

- 12 phase-locked-loops (PLLs)

•

EP3SL150

- 142,000 logic elements (LEs)

- 6,390K Total Memory Kbits

- 384 18x18-bit Multipliers blocks

- 8 phase-locked-loops (PLLs)

Serial Configuration device and USB Blaster circuit

• Altera’s EPCS128/EPCS64 Serial Configuration device

• On-board USB Blaster for programming and user API control

• Support JTAG mode

DDR2 SO-DIMM socket

• Up to 4GB capacity

• Share the same I/O bus with HSTC connector B

SD card socket

• Provides SPI and 1-bit SD mode for SD Card access

Page 10

DE3 User Manual

7

Push-button switches

• 6 push-button switches

- 1 CPU Reset

- 1 FPGA Reconfigure

- 4 user-defined inputs

• Debounced by a Schmitt trigger circuit

• Normally high; generates one active-low pulse when the switch is pressed

Slide switches

• 4 slide switches for user-defined inputs

• When a switch is set to the DOWN or UP position (i.e., close to or away from the edge of

the DE3 board), it causes logic 0 or 1, respectively.

Clock inputs

• 50MHz oscillator

• 1 SMA connector for PLL clock output

• 1 SMA connector for external clock input

USB Host/Slave controller

• Complies fully with Universal Serial Bus Specification Rev. 2.0

• Support data transfer at high-speed, full-speed, and low-speed

• Support both USB host and device

• Three USB ports (one type mini-AB for host/device and two type A for host)

• Support Nios II with the Terasic driver

• Support Programmed I/O (PIO) and Direct Memory Access (DMA)

Eight 180-pin High Speed Terasic Connectors (HSTC) expansion headers

• 4 male and 4 female connectors are on the top and the bottom of DE3 board, respectively.

• 240 LVDS pairs of user-defined IO pins

• Configurable I/O voltage for 3.3V, 2.5V, 1.8V, and 1.5V

Two 40-pin expansion headers

• 72 FPGA I/O pins, as well as 8 power and ground lines, are brought out to two 40-pin

expansion connectors

• 40-pin header is designed to accept a standard 40-pin ribbon cable used for IDE hard drives

• Share the same I/O pins with HSTC connector A

Page 11

DE3 User Manual

8

Chapter 2

Using the DE3 Board

2

This chapter gives instructions for using the DE3 board and its components.

It is strongly recommended that users should read the Getting Started with the Altera DE3 board.pdf

before using the DE3 board. The document is located in the DE3_usermanual folder on the DE3

System CD. The contents of the document includes following:

1. Purpose of the DE3 Board

2. Scope of the DE3 Board and Supporting Material

3. Installing the Altera Design Software

4. Obtain a License File from Altera’s website

5. Setup the License File for Terasic Power Controller IP.

6. Install the USB Blaster Driver

7. Power up the DE3 Board

8. Programming the FPGA Device on the DE3 Board

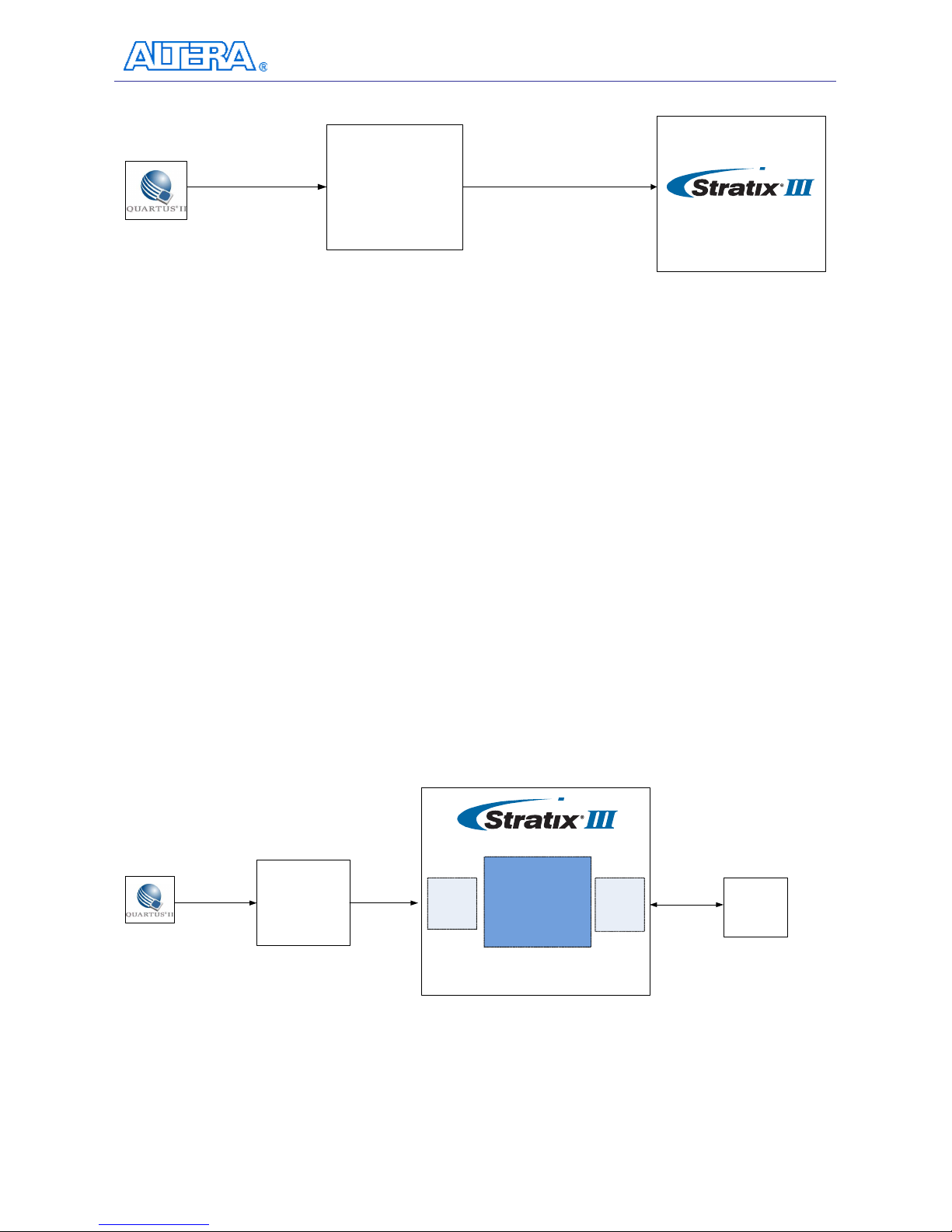

2.1 Configuring the FPGA and Serial Configuration Device

Programming the FPGA device:

The DE3 board has a built-in USB Blaster circuit, which allows users to program the FPGA

device using USB cable and Quartus II programmer in JTAG mode. Current configuration will

be lost when the power is turned off.

To download a configuration bit stream into the Stratix III FPGA, perform the following steps:

• Make sure that power is provided to the DE3 board

• Connect the USB cable supplied to the USB Blaster port of the DE3 board (see Figure 2.1)

• The FPGA can now be programmed in the Quartus II Programmer by selecting a

configuration bit stream file with the .sof filename extension.

Please refer to Getting Started with the Altera DE3 board.pdf for more detailed procedure of

FPGA programming.

Page 12

DE3 User Manual

9

Quartus II

Programmer

USB Blaster

Circuit

JTAG Config Signals

JTAGUART

Figure 2.1 The JTAG configuration scheme

Programming the serial configuration device :

The DE3 board contains a serial configuration device (U4) that stores configuration data for

the Stratix III FPGA. This configuration data is automatically loaded from the serial

configuration device chip into the FPGA when the board is powered up.

Since the Active Serial programming interface is not supported on the DE3 board, users will

need to use a Serial Flash Loader (SFL) function to program the serial configuration device via

the JTAG interface. The FPGA-based SFL is a soft intellectual property (IP) core within the

FPGA that bridges the JTAG and flash interfaces. The SFL mega-function is available from

Quartus II software. Figure 2.2 shows the programming method when adopting a SFL solution.

Please refer to Appendix C Programming the Serial Configuration device for the basic

programming instruction on the serial configuration device. More detailed information on the

SFL mega-function can be found in Altera Application Note 370: Using the Serial Flash

Loader With the Quartus II Software.

Quartus II

Programmer

USB Blaster

Circuit

Serial Configuration Device

JTAG

EPCS

128

SFL Image

to bridge

The

JTAG and ASMI

JTAG

ASMI

Figure 2.2. Programming a serial configuration device with the SFL solution

Page 13

DE3 User Manual

10

2.2 JTAG Chain

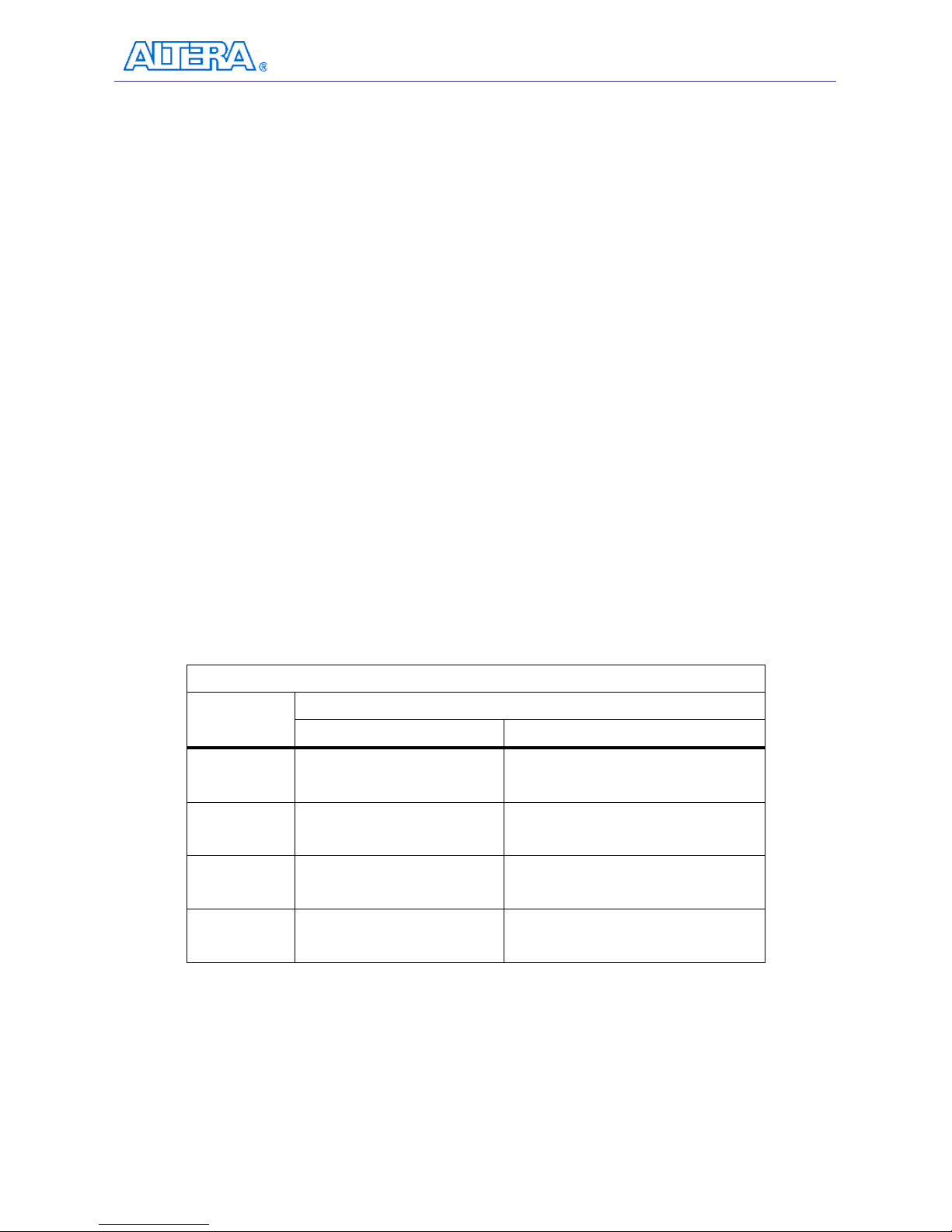

This section describes how to setup the JTAG chain on DE3 board.

If the DE3 board is used without any board connected and all the positions in SW6 are switched to

OFF (i.e., down position), the JTAG-interface signals of all HSTC connectors are bypassed, as

shown in Figure 2.3.

When the top HSTC connector is not connected with any daughter board, the JTGA interface is

bypassed. If a daughter board is connected to the top HSTC connector, the JTAG interface will be

enabled automatically. Figure 2.4 shows the JTAG chain with a daughter board connected to the

DE3 board via top HSTC connector A. Note that if the daughter board does not use the JTAG

interface, the TDI and TOD pins on the daughter board must be shorted for the JTAG signals to pass

through.

A four position DIP switch (SW6) on DE3 board is used to control the JTAG interface signals of

bottom HSTC connectors. Table 2-1 indicates the detailed configurations of SW6. When the bottom

connector is connected with other DE3 board or an daughter board, users need to configure the

SW6 to connect the JTAG chain to other board accordingly. Figure 2.5 shows there are two DE3

boards stacked, and the JTAG chain is established through HSTA connector A, as shown in Figure

2.6.

Table 2-1. DIP switch (SW6) setting for JTAG interface on bottom HSTC connectors

Position

Switch Setting

Turn OFF (lower position) Turn ON (upper position)

1

Bypass the JTAG interface on

the Bottom HSTC connector A(J2)

Enable the JTAG interface for

Bottom HSTC connector A(J2)

2

Bypass the JTAG interface on

the Bottom HSTC connector B(J4)

Enable the JTAG interface for

Bottom HSTC connector B(J4)

3

Bypass the JTAG interface on

the Bottom HSTC connector C(J6)

Enable the JTAG interface for

Bottom HSTC connector C(J6)

4

Bypass the JTAG interface on

the Bottom HSTC connector D(J8)

Enable the JTAG interface for

Bottom HSTC connector D(J8)

Page 14

DE3 User Manual

11

TDI TDO

TDO

TDI

USB Blaster

Circuit

USB

Cable

Host

PC

Statix III FPGA

DE3 Board

OFF

OFF

OFF

OFF

SW6

HSTC Connector A

Bypassed

HSTC Connector B

Bypassed

HSTC Connector C

Bypassed

HSTC Connector D

Bypassed

2

3

4

1

Figure 2.3. JTAG chain for a standalone DE3 board

TDOTDI

TDI TDO

HSTC Connector

A Top

TDI TDO

TDO

TDI

USB

Blaster

Circuit

USB

Cable

Host

PC

Stratix III FPGA

Daughter

Board

DE3 Board

OFF

OFF

OFF

OFF

SW6

Figure 2.4. JTAG chain for a daughter board connected with DE3 board via top HSTC connector A

Page 15

DE3 User Manual

12

Figure 2.5. The two DE3 boards stacked and the JTAG path is established through HSTC connector

A.

TDO TDI

HSTC Connector A

Bottom

TDI TDO

TDO

TDI

USB

Blaster

Circuit

USB

Cable

Host

PC

TDOTDI

HSTC Connector A

Top

TDI TDO

TDO

TDI

USB

Blaster

Circuit

SW6

1

2

3

4

ON

OFF

DE3 Board 1

DE3 Board 2

OFF

OFF

Stratix III FPGA

Stratix III FPGA

SW6

1

2

3

4

OFF

OFF

OFF

OFF

Figure 2.6. JTAG chain for two stacked DE3 boards

Page 16

DE3 User Manual

13

2.3 Using the User I/O Interface

Push-Button Switches:

The DE3 board provides four user-defined, one CPU reset, and one Reconfigure push-button

switches. The Reconfigure push-button is used to force a re-boot of the FPGA from the serial

configuration device.

The CPU reset push-button is an input to the Stratix III device. It is intended to be the master

reset signal for the FPGA designs loaded into the Stratix III device. The CPU reset push

-button is connected to the DEV_CLRn pin on the FPGA. The DEV_CLRn setting is a pin

option in the Quartus II software that users must enable to function the CPU reset as

DEV_CLRn instead of a standard I/O.

Each of these switches is de-bounced using a Schmitt Trigger circuit, as indicated in Figure

2.7. Each push-button provides a high logic level (3.3 volts) or a low logic level (0 volts)

when it is not pressed or pressed, respectively. Table A-1 shows the connections between the

push-buttons and the FPGA.

Push

PushPush

Push----button depressed

button depressedbutton depressed

button depressed

Before

BeforeBefore

Before

Debouncing

DebouncingDebouncing

Debouncing

Schmitt Triger

Schmitt TrigerSchmitt Triger

Schmitt Triger

Debounced

DebouncedDebounced

Debounced

Push

PushPush

Push----button released

button releasedbutton released

button released

Figure 2.7. Switch debouncing

Slide Switches and DIP Switch

There are also four slide switches and one 8-position DIP switch on the DE3 board. Each

switch is connected directly to a pin of the Stratix III FPGA. When a slide switch is in the

DOWN position (i.e., closest to the edge of the board) or the UP position, it provides a low

logic level (0 volts) or a high logic level (3.3 volts) to the FPGA, respectively. For 8-position

DIP switch, when a switch is in the DOWN position (closest to the edge of the board) or the

UP position, it provides a high logic level (3.3 volts) or a low logic level (0 volts) to the FPGA.

The connections between the slide switches and the FPGA are shown in Table A-2, whereas

Table A-3 shows the connections between the 8-position DIP switch and the FPGA.

RGB LEDs

There are 8 RGB user-controllable LEDs on the DE3 board. Each LED has red, green, and

Page 17

DE3 User Manual

14

blue color, driven directly by the Stratix III FPGA; The LED is turned on or off when the

associated pins are driven to a low or high logic level, respectively. A list of the pin names on

the FPGA that are connected to the RGB LEDs is given in

Table A-4.

7-Segment Displays

The DE3 board has two 7-segment displays. As indicated in the schematic in Figure 2.8, the

seven segments are connected to pins of the Stratix III FPGA. Applying a low or high logic

level to a segment to light it up or turns it off.

Each segment in a display is identified by an index listed from 0 to 6 with the positions given

in Figure 2.9. In addition, the decimal point is identified as DP. Table A-5 shows the mapping

of the FPGA pin assignments to the 7-segment displays.

3

7

9

8

5

10

4

2

HEX1_D0

M1

L1

L2

V4

P3

N4

Y11

W12

Y5

Y6

V3

HEX1

HEX0

HEX1_D1

HEX1_D2

HEX1_D3

HEX1_D4

HEX1_D5

HEX1_D6

HEX1_DP

HEX0_D0

HEX0_D1

HEX0_D2

HEX0_D3

HEX0_D4

HEX0_D5

HEX0_D6

HEX6_DP

N3

N1

W7

W8

W10

3

7

9

8

5

10

4

2

Figure 2.8. Connection between 7-segment displays and Stratix III FPGA

0

3

1

24

5

6

DP

Figure 2.9. Position and index of each segment in a 7-segment display

2.4 I/O Groups and V

CCIO

Control Circuit

Most of the user-defined I/O pins on Stratix III device are used for connectors. They are divided

Page 18

DE3 User Manual

15

into four I/O groups, named A, B, C and D.

Table 2-2 shows the relation between I/O groups and

connectors.

Table 2-2 The relation between I/O groups and connectors

I/O Group Connectors

A HSTC connector A, GPIO expansion headers (1)

B HSTC connector B, DDR2 SO-DIMM socket (2)

C HSTC connector C

D HSTC connector D

Note:

(1): HSTC connector A and GPIO expansion headers share the same I/O pins.

(2): HSTC connector B and DDR2 SO-DIMM socket share the same I/O pins.

Besides, the V

CCIO

level for these I/O groups of the FPGA can be configured, and many I/O

standards are supported. The I/O standard of each I/O group on DE3 board has to be set through a

software utility named “DE3 System Builder”. Such tool is intended to generate a top level

Quartus II project, which includes the power controller IP.

After the FPGA is programmed, the power controller IP will control the V

CCIO

control circuit to

provide desired V

CCIO

and V

CCPD

level to the FPGA, according to I/O standard selected by users as

indicated in Figure 2.10.With this feature, users can not only confirm if the V

CCIO

level meets the

design requirement, but also reduce the chance of the DE3 board and its daughter cards being

damaged.

Please refer to Stratix III handbook chapter 7. Stratix III Device I/O Features for more information

about the I/O standard and voltage levels of the Stratix III device. There will be more instructions

for DE3 System Builder in Chapter 4.

V

CCIO

Selection

Power Control

IP

V

CCIO

to I/O bank

V

CCIO

Voltage-Level

Control Circuit

Figure 2.10. The architecture of Power Control IP and V

CCIO

control circuit

Page 19

DE3 User Manual

16

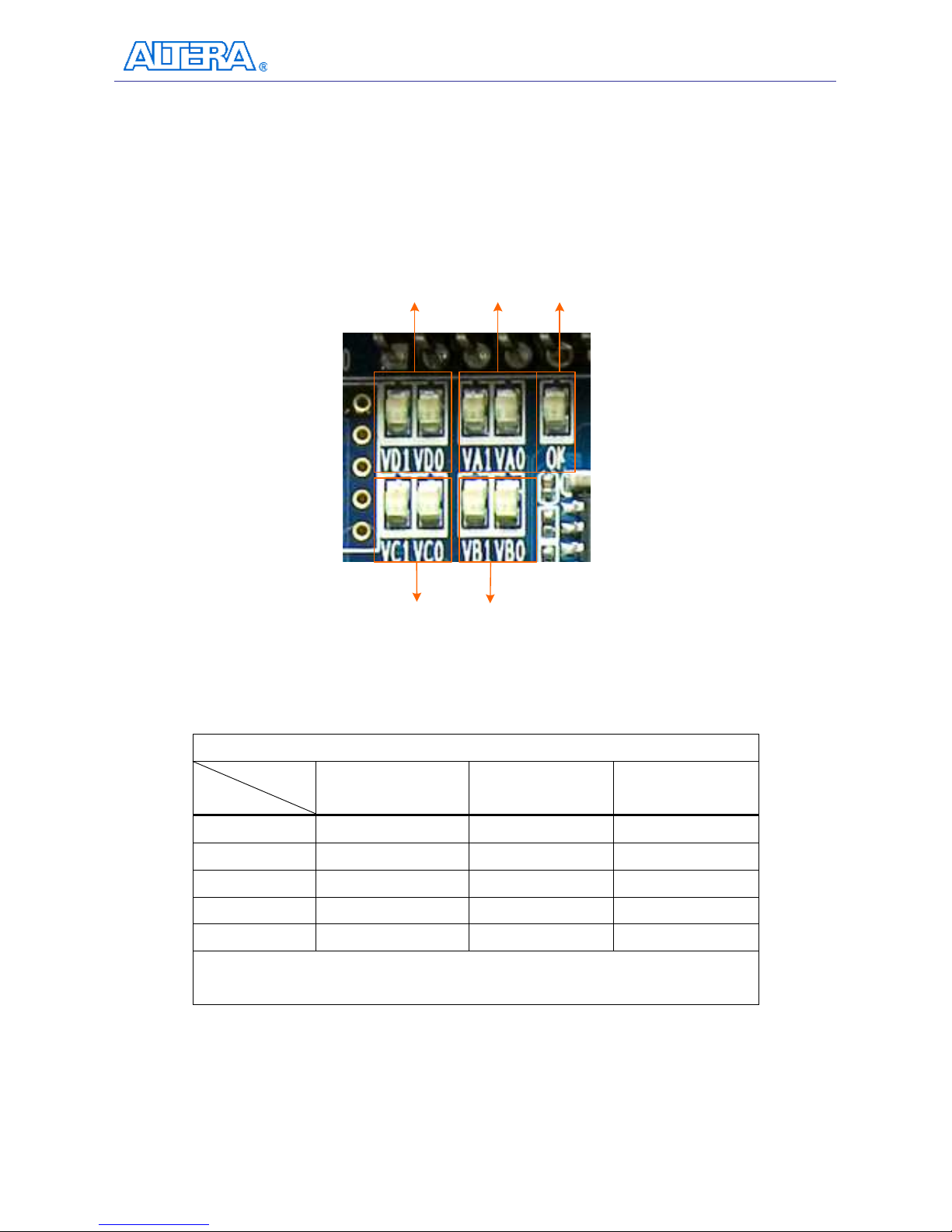

Finally, there are LEDs located at the left-top corner of the DE3 board to indicate the V

CCIO

voltage

level of each I/O group, as shown in Figure 2.11. For example, the LED VA1 and VA2 will be

turned on and off, respectively, when the V

CCIO

of I/O Group A is set to 2.5V. Please refer to Table

2-3 for the status of the LED indicator.

For I/O

Group A

For I/O

Group D

For I/O

Group C

For I/O

Group B

Power

ON/OFF

Indicator

Figure 2.11. The Voltage-Level Indicator for the I/O Groups

Table 2-3 The LEDs indicates the V

CCIO

voltage level of each IO Group.

LED

V

CCIO

Vx1(1) Vx0(1) OK

3.3V Light ON Light ON Light ON

2.5V Light ON Light OFF Light ON

1.8V Light OFF Light ON Light ON

1.5V Light OFF Light OFF Light ON

0V Light OFF Light OFF Light OFF

Note:

(1): Vx1 can be VA1, VB2, VC3, and VD1; Vx0 can be VA0, VB0, VC0, and VD0

Page 20

DE3 User Manual

17

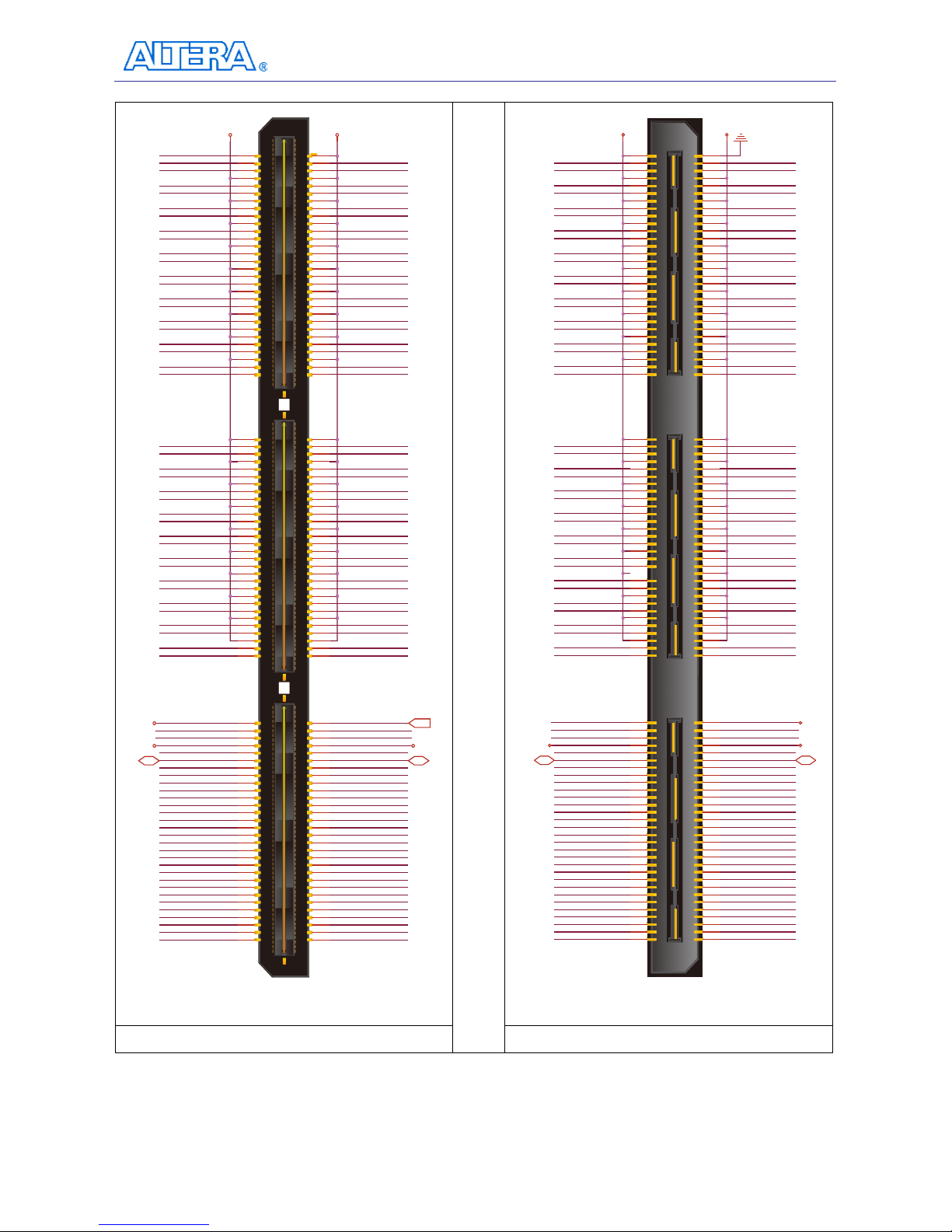

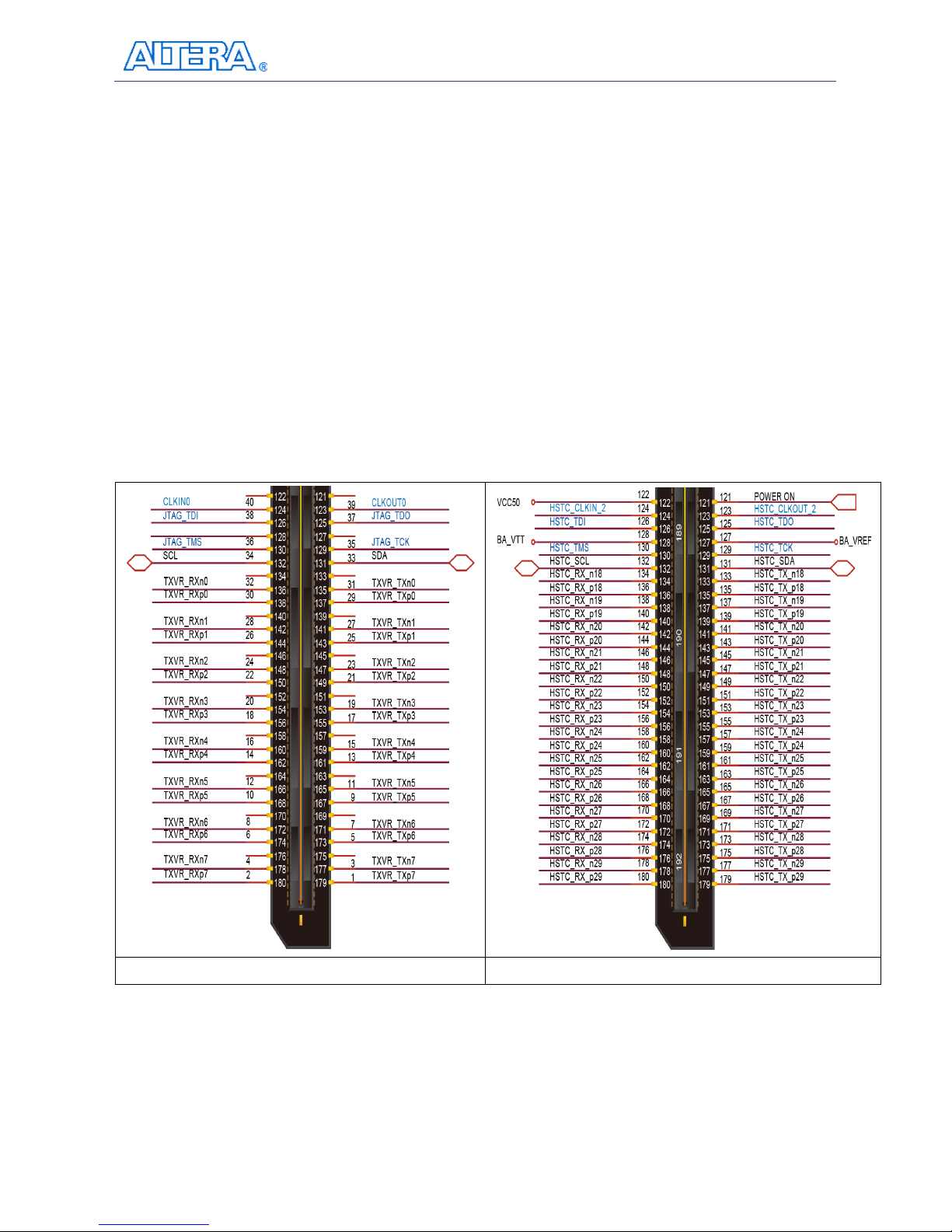

2.5 Using the HSTC Connectors

The High Speed Terasic Connector (HSTC) is a high speed expansion interface defined by Terasic

Technologies. The DE3 board is equipped with 8 HSTC connectors (J1 ~ J8), which can be used to

connect the Stratix III FPGA with daughter boards or the other DE3 boards. The detailed

specifications of the HSTC connector are described below:

4 HSTC Connector Groups:

The eight HSTC connectors on the DE3 board are divided into 4 groups: HSTC A, HSTC B,

HSTC C, and HSTC D. Each group has a male and female HSTC connector on the top and

bottom side of the DE3 board, respectively. In addition, both the male and female HSTC

connector shares the same I/O pins except JTAG and I2C interface.

I/O Distribution:

Each HSTC connector has 120 single-ended I/O (60 pair differential channels), 10

single-ended IO with 5 each for clock input and output (2 differential clock input and output

channel), JTAG and I2C bus. In addition, there are three banks on a HSTC connector. The I/O

pins used in differential transceiver channels on bank 1 support true LVDS inout. On bank 2

and 3, the I/O pins used in differential transmitter channels support emulated LVDS via a

termination resistor, and the differential receiver channels support true LVDS, as shown in.

Figure 2.12. In addition, there is a software utility named “DE3_HSTC” which can perform

the connection test between the I/O pins of the HSTC connector and Stratix III FPGA. The

detailed information about this utility can be found in Appendix D : DE3_HSTC Utility.

Configurable I/O Standards:

The I/O pins of the HSTC connector support many I/O standards with different voltage level,

as the V

CCIO

supplied to FPGA bank I/O is configurable. Users can choose the I/O standard of

HSTC connector in the software utility “DE3 System Builder”.

Compatible with HSMC Connector :

The HSTC connector is not only designed to be backward-compatible with the HSMC

products, but also provides more I/O pins for further connection. The pin assignments of bank

1 and 2 are exactly the same. The only difference between the HSMC and HSTC connector is

the pin assignments for bank 3. For HSTC connector, all the I/O pins on the bank 3 are well

defined. Figure 2.13 shows the I/O distribution of the bank3 for the HSTC and HSMC

connector. Table B-1 shows the pin compatible list for HSTC and HSMC connector.

Page 21

DE3 User Manual

18

VCC50

BA_VREF

HSTC_CLKIN_n 0

GND

HSTC_CLKIN_p 0

HSTC_RX_n0

HSTC_RX_p0

HSTC_RX_n1

HSTC_RX_p1

HSTC_RX_n2

HSTC_RX_p2

HSTC_RX_n3

HSTC_RX_p3

HSTC_RX_n4

HSTC_RX_p4

HSTC_RX_n5

HSTC_RX_p5

HSTC_RX_n6

HSTC_RX_p6

HSTC_RX_n7

HSTC_RX_p7

HSTC_RX_n8

HSTC_RX_p8

HSTC_CLKIN_n 1

HSTC_CLKIN_p 1

HSTC_RX_n9

HSTC_RX_p9

HSTC_RX_n10

HSTC_RX_p10

HSTC_RX_n11

HSTC_RX_p11

HSTC_RX_n12

HSTC_RX_p12

HSTC_RX_n13

HSTC_RX_p13

HSTC_RX_n14

HSTC_RX_p14

HSTC_RX_n15

HSTC_RX_p15

HSTC_RX_n16

HSTC_RX_p16

HSTC_RX_n17

HSTC_RX_p17

HSTC_CLKIN_ 2

HSTC_TDI

HSTC_TMS

HSTC_SCL

HSTC_RX_n18

HSTC_RX_p18

HSTC_RX_n19

HSTC_RX_p19

HSTC_RX_n20

HSTC_RX_p20

HSTC_RX_n21

HSTC_RX_p21

HSTC_RX_n22

HSTC_RX_p22

HSTC_RX_n23

HSTC_RX_p23

HSTC_RX_n24

HSTC_RX_p24

HSTC_RX_n25

HSTC_RX_p25

HSTC_RX_n26

HSTC_RX_p26

HSTC_RX_n27

HSTC_RX_p27

HSTC_RX_n28

HSTC_RX_p28

HSTC_RX_n29

HSTC_RX_p29

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

64

66

70

72

62

68

76

78

74

82

84

80

88

90

86

94

96

92

100

102

98

106

108

104

112

114

110

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

116

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

64

66

70

72

62

68

76

78

74

82

84

80

88

90

86

94

96

92

100

102

98

106

108

104

112

114

110

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

116

1

3

5

7

9

11

13

15

17

18

21

23

25

27

39

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

63

65

69

71

61

67

75

77

73

81

83

79

87

89

85

93

95

91

99

101

97

105

107

103

111

113

109

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

115

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

63

65

69

71

61

67

75

77

73

81

83

79

87

89

85

93

95

91

99

101

97

105

107

103

111

113

109

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

115

VCC3312V

J

2

HSTC Connector A-Top (Male)

BA_VTT

HSTC_CLKOUT_n0

HSTC_CLKOUT_p0

HSTC_TX_n0

HSTC_TX_p0

HSTC_TX_n1

HSTC_TX_p1

HSTC_TX_n2

HSTC_TX_p2

HSTC_TX_n3

HSTC_TX_p3

HSTC_TX_n4

HSTC_TX_p4

HSTC_TX_n5

HSTC_TX_p5

HSTC_TX_n6

HSTC_TX_p6

HSTC_TX_n7

HSTC_TX_p7

HSTC_TX_n8

HSTC_TX_p8

HSTC_CLKOUT_n1

HSTC_CLKOUT_p1

HSTC_TX_n9

HSTC_TX_p9

HSTC_TX_n10

HSTC_TX_p10

HSTC_TX_n11

HSTC_TX_p11

HSTC_TX_n12

HSTC_TX_p12

HSTC_TX_n13

HSTC_TX_p13

HSTC_TX_n14

HSTC_TX_p14

HSTC_TX_n15

HSTC_TX_p15

HSTC_TX_n16

HSTC_TX_p16

HSTC_TX_n17

HSTC_TX_p17

HSTC_CLKOUT_2

POWER ON

HSTC_TDO

HSTC_TCK

HSTC_SDA

HSTC_TX_n18

HSTC_TX_p18

HSTC_TX_n19

HSTC_TX_p19

HSTC_TX_n20

HSTC_TX_p20

HSTC_TX_n21

HSTC_TX_p21

HSTC_TX_n22

HSTC_TX_p22

HSTC_TX_n23

HSTC_TX_p23

HSTC_TX_n24

HSTC_TX_p24

HSTC_TX_n25

HSTC_TX_p25

HSTC_TX_n26

HSTC_TX_p26

HSTC_TX_n27

HSTC_TX_p27

HSTC_TX_n28

HSTC_TX_p28

HSTC_TX_n29

HSTC_TX_p29

Bank

1

2

2

4

4 HSTCA_CL KIN_n0

HSTCA_CL KIN_p0

HSTCA_RX_n0

HSTCA_RX_p0

HSTCA_RX_n1

HSTCA_RX_p1

HSTCA_RX_n2

HSTCA_RX_p2

HSTCA_RX_n3

HSTCA_RX_p3

HSTCA_RX_n4

HSTCA_RX_p4

HSTCA_RX_n5

HSTCA_RX_p5

HSTCA_RX_n6

HSTCA_RX_p6

HSTCA_RX_n7

HSTCA_RX_p7

HSTCA_RX_n8

HSTCA_RX_p8

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

34

34

36

36

38

38

40

40

42

42

44

44

46

46

48

48

50

50

52

52

54

54

56

56

58

58

60

60

HSTCA_CLKIN_n1

64

64

HSTCA_CLKIN_p1

66

66

HSTCA_RX_n9

70

70

HSTCA_RX_p9

72

72

62

62

68

68

HSTCA_RX_n1 0

76

76

HSTCA_RX_p1 0

78

78

74

74

HSTCA_RX_n1 1

82

82

HSTCA_RX_p1 1

84

84

80

80

HSTCA_RX_n1 2

88

88

HSTCA_RX_p1 2

90

90

86

86

HSTCA_RX_n1 3

94

94

HSTCA_RX_p1 3

96

96

92

92

HSTCA_RX_n1 4

100

100

HSTCA_RX_p1 4

102

102

98

98

HSTCA_RX_n1 5

106

106

HSTCA_RX_p1 5

108

108

104

104

HSTCA_RX_n1 6

112

112

HSTCA_RX_p1 6

114

114

110

110

HSTCA_RX_n1 7

118

118

HSTCA_RX_p1 7

120

120

122

122

HSTCA_CLKIN_2

VCC50

BA_VTT

124

124

124

HSTCA_TDI

HSTCA_TMS

126

126

128

128

130

130

HSTCA_SCL

132

132

HSTCA_RX_n1 8

134

134

HSTCA_RX_p1 8

136

136

HSTCA_RX_n1 9

138

138

HSTCA_RX_p1 9

140

140

HSTCA_RX_n2 0

142

142

HSTCA_RX_p2 0

144

144

HSTCA_RX_n2 1

146

146

HSTCA_RX_p2 1

148

148

HSTCA_RX_n2 2

150

150

HSTCA_RX_p2 2

152

152

HSTCA_RX_n2 3

154

154

HSTCA_RX_p2 3

156

156

HSTCA_RX_n2 4

158

158

HSTCA_RX_p2 4

160

160

HSTCA_RX_n2 5

162

162

HSTCA_RX_p2 5

164

164

HSTCA_RX_n2 6

166

166

HSTCA_RX_p2 6

168

168

HSTCA_RX_n2 7

170

170

HSTCA_RX_p2 7

172

172

HSTCA_RX_n2 8

174

174

HSTCA_RX_p2 8

176

176

HSTCA_RX_n2 9

178

178

HSTCA_RX_p2 9

180

180

116

116

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

63

65

69

71

61

67

75

77

73

81

83

79

87

89

85

93

95

91

99

101

97

105

107

103

111

113

109

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

115

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

63

65

69

71

61

67

75

77

73

81

83

79

87

89

85

93

95

91

99

101

97

105

107

103

111

113

109

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

115

HSTCA_CLKOUT_n0

VCC33 12V

J1

HSTC Connector A-Bottom (Female)

HSTCA_CLKOUT_p0

HSTCA_TX_n0

HSTCA_TX_p0

HSTCA_TX_n1

HSTCA_TX_p1

HSTCA_TX_n2

HSTCA_TX_p2

HSTCA_TX_n3

HSTCA_TX_p3

HSTCA_TX_n4

HSTCA_TX_p4

HSTCA_TX_n5

HSTCA_TX_p5

HSTCA_TX_n6

HSTCA_TX_p6

HSTCA_TX_n7

HSTCA_TX_p7

HSTCA_TX_n8

HSTCA_TX_p8

HSTCA_CLKOUT_n1

HSTCA_CLKOUT_p1

HSTCA_TX_n9

HSTCA_TX_p9

HSTCA_TX_n10

HSTCA_TX_p10

HSTCA_TX_n11

HSTCA_TX_p11

HSTCA_TX_n12

HSTCA_TX_p12

HSTCA_TX_n13

HSTCA_TX_p13

HSTCA_TX_n14

HSTCA_TX_p14

HSTCA_TX_n15

HSTCA_TX_p15

HSTCA_TX_n16

HSTCA_TX_p16

HSTCA_TX_n17

HSTCA_TX_p17

HSTCA_CLKOUT_2

POWER ON

BA_VREF

HSTCA_TDO

HSTCA_TCK

HSTCA_SDA

HSTCA_TX_n18

HSTCA_TX_p18

HSTCA_TX_n19

HSTCA_TX_p19

HSTCA_TX_n20

HSTCA_TX_p20

HSTCA_TX_n21

HSTCA_TX_p21

HSTCA_TX_n22

HSTCA_TX_p22

HSTCA_TX_n23

HSTCA_TX_p23

HSTCA_TX_n24

HSTCA_TX_p24

HSTCA_TX_n25

HSTCA_TX_p25

HSTCA_TX_n26

HSTCA_TX_p26

HSTCA_TX_n27

HSTCA_TX_p27

HSTCA_TX_n28

HSTCA_TX_p28

HSTCA_TX_n29

HSTCA_TX_p29

Bank

2

Bank

3

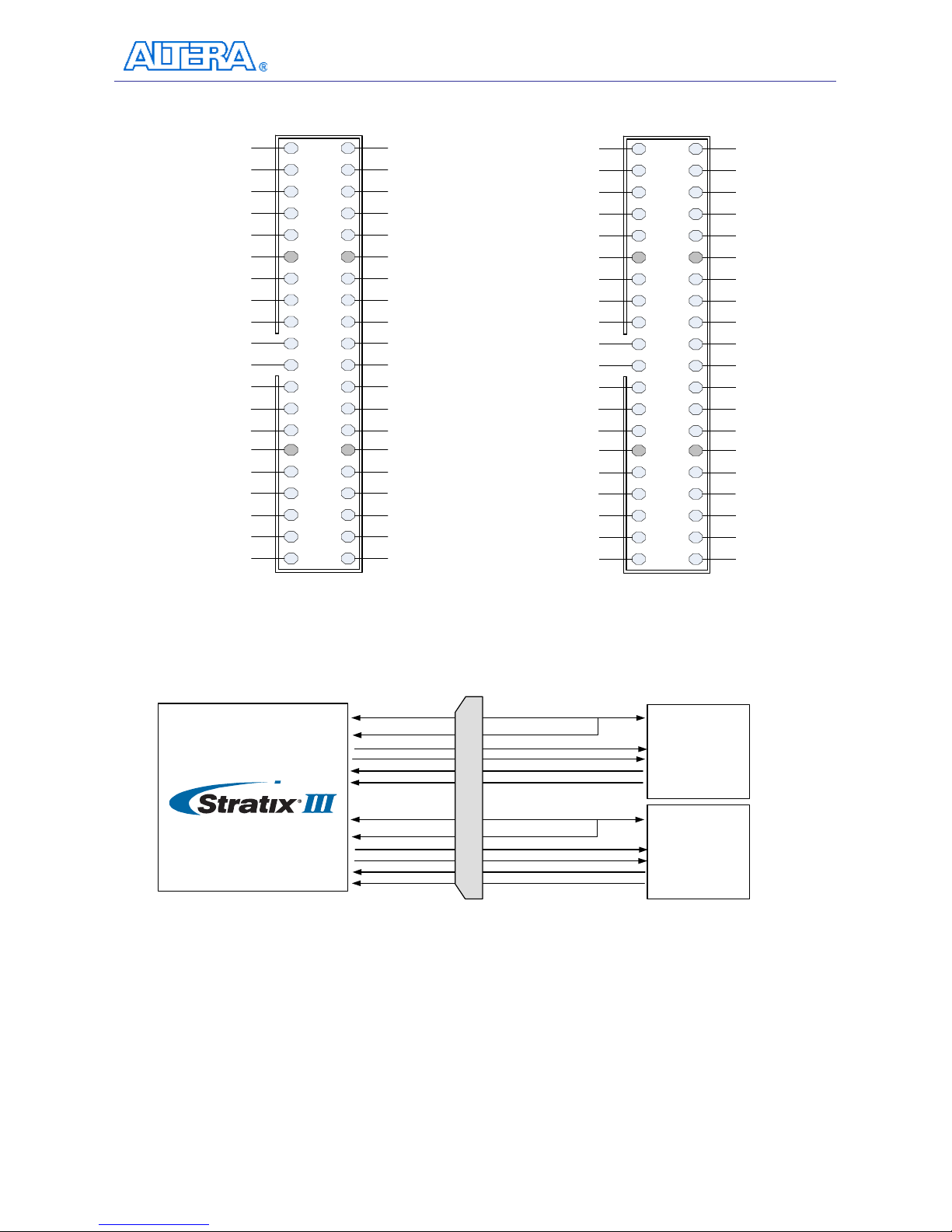

Male HSTC connector Female HSTC connector

Figure 2.12. The male and female HSTC connectors

Page 22

DE3 User Manual

19

Share the same I/O pins with other connectors:

The HSTC connector group HSTCA (J1, J2) and HSTCB (J3, J4) share the same I/O pins with

the GPIO expansion headers (J13, J14) and DDR2 SO-DIMM socket (J9), respectively. Hence

none of the combinations above is allowed to be used at the same time.

Power Supply:

The HSTC connector provides 12, 5, and 3.3 volt for power supply purpose. There are also two

power input pin named B<HSTC Group>_VTT and B<HSTC Group>_VREF, which are

connected to the input reference voltage(V

REF

) and termination voltage pin (VTT) of the Stratix

III FPGA, respectively.

Finally, Table A-6 to Table A-11 shows the connections between the HSTC connectors and the

FPGA.

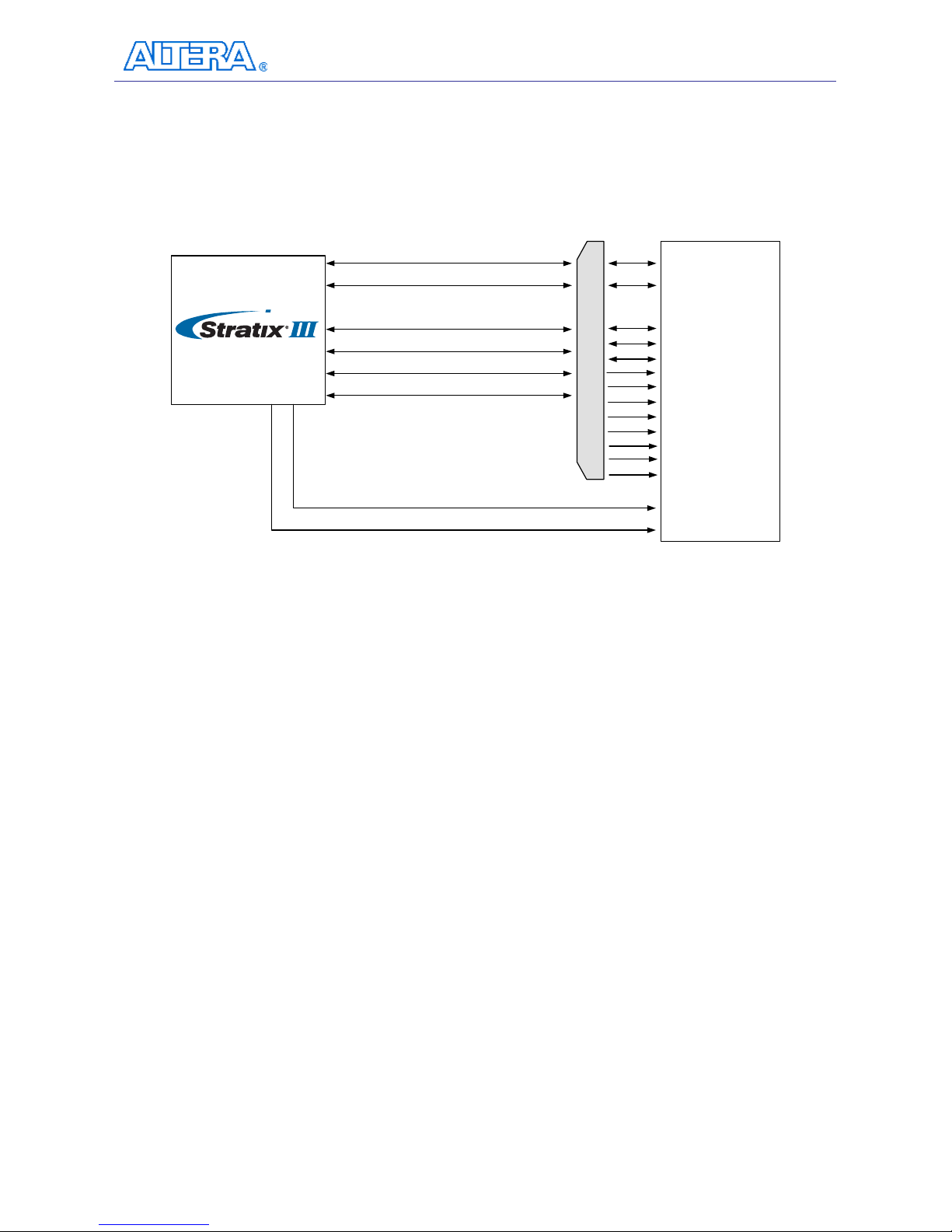

HSMC HSTC

Figure 2.13. The difference between the HSMC and HSTC connectors

Page 23

DE3 User Manual

20

2.6 Connecting HSTC/HSMC Daughter Boards to DE3 HSTC

connectors

It is important when the HSTC/HSMC daughter boards are connected to the DE3 HSTC connector

is to ensure the I/O pins are properly matched between the daughter board and the DE3 connector in

particular the 12V, 5V, and 3.3V power pins. If there are mismatch in pins between the two

connectors, not only would it cause damage to the daughter board but more importantly the FPGA

itself. Please note daughter boards can only be connected to the TOP HSTC connector of the DE3

board, therefore the bottom HSTC connector are only used to establish connection for stacking

purposes.

2.7 Using the GPIO Expansion Headers

The DE3 Board provides two 40-pin expansion headers as shown in Figure 2.14. Each header has

36 pins connected to the Stratix III FPGA, and the two headers share the same I/O pins with HSTC

connector A. The other 4 pins provide DC +5V (VCC5), DC +3.3V (VCC33), and two GND pins.

Among these 36 I/O pins, there are 4 pins connected to the PLL clock input and output pins of the

FPGA.

The I/O pins on the expansion headers have a great flexibility in selecting the I/O standards. The

voltage level of the V

CCIO

can be configured as 3.3V, 2.5V, 1.8V, or 1.5V.

Finally, Figure 2.15 shows the connections between the GPIO expansion headers and Stratix III.

The pin assignments are given in Table A-12 and Table A-13.

Page 24

DE3 User Manual

21

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

GPIO0_CLKINn0

GPIO0_CLKINp0

GPIO0_D2

GPIO0_D4

GPIO0_D6

5V

GPIO0_D8

GPIO0_D10

GPIO0_D12

GPIO0_CLKOUTn0

GPIO0_CLKOUTp0

GPIO0_D16

GPIO0_D18

GPIO0_D20

3.3V

GPIO0_D22

GPIO0_D24

GPIO0_D26

GPIO0_D28

GPIO0_D30

GPIO0_D0

GPIO0_D1

GPIO0_D3

GPIO0_D5

GPIO0_D7

GND

GPIO0_D9

GPIO0_D11

GPIO0_D13

GPIO0_D14

GPIO0_D15

GPIO0_D17

GPIO0_D19

GPIO0_D21

GND

GPIO0_D23

GPIO0_D25

GPIO0_D27

GPIO0_D29

GPIO0_D31

J13

GPIO 0

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

GPIO1_CLKINn1

GPIO1_CLKINp1

GPIO1_D2

GPIO1_D4

GPIO1_D6

5V

GPIO1_D8

GPIO1_D10

GPIO1_D12

GPIO1_CLKOUTn1

GPIO1_CLKOUTp1

GPIO1_D16

GPIO1_D18

GPIO1_D20

3.3V

GPIO1_D22

GPIO1_D24

GPIO1_D26

GPIO1_D28

GPIO1_D30

GPIO1_D0

GPIO1_D1

GPIO1_D3

GPIO1_D5

GPIO1_D7

GND

GPIO1_D9

GPIO1_D11

GPIO1_D13

GPIO1_D14

GPIO1_D15

GPIO1_D17

GPIO1_D19

GPIO1_D21

GND

GPIO1_D23

GPIO1_D25

GPIO1_D27

GPIO1_D29

GPIO1_D31

J14

GPIO 1

Figure 2.14. Pin distribution of the GPIO expansion headers

1

3

19

AD19

AE32

AE31

AE18

GPIO 0

GPIO 1

CLKOUTn0

CLKOUTp0

CLKINn0

CLKINp0

AE19

AD18

AP19

AN19

21

CLKOUTn1

CLKOUTp1

CLKINn1

CLKINp1

1

3

19

21

GPIO0_D [ 0 .. 31 ]

RX_n [ 0 .. 15 ]

RX_p [ 0 .. 15 ]

TX_n [ 0 .. 15 ]

TX_p [ 0 .. 15 ]

GPIO1_D [ 0 .. 31 ]

HSTC A

See Table A-12,13

CLKOUTn0

CLKOUTp0

CLKINn0

CLKINp0

CLKOUTn1

CLKOUTp1

CLKINn1

CLKINp1

See Table A-12,13

See Table A-12,13

See Table A-12,13

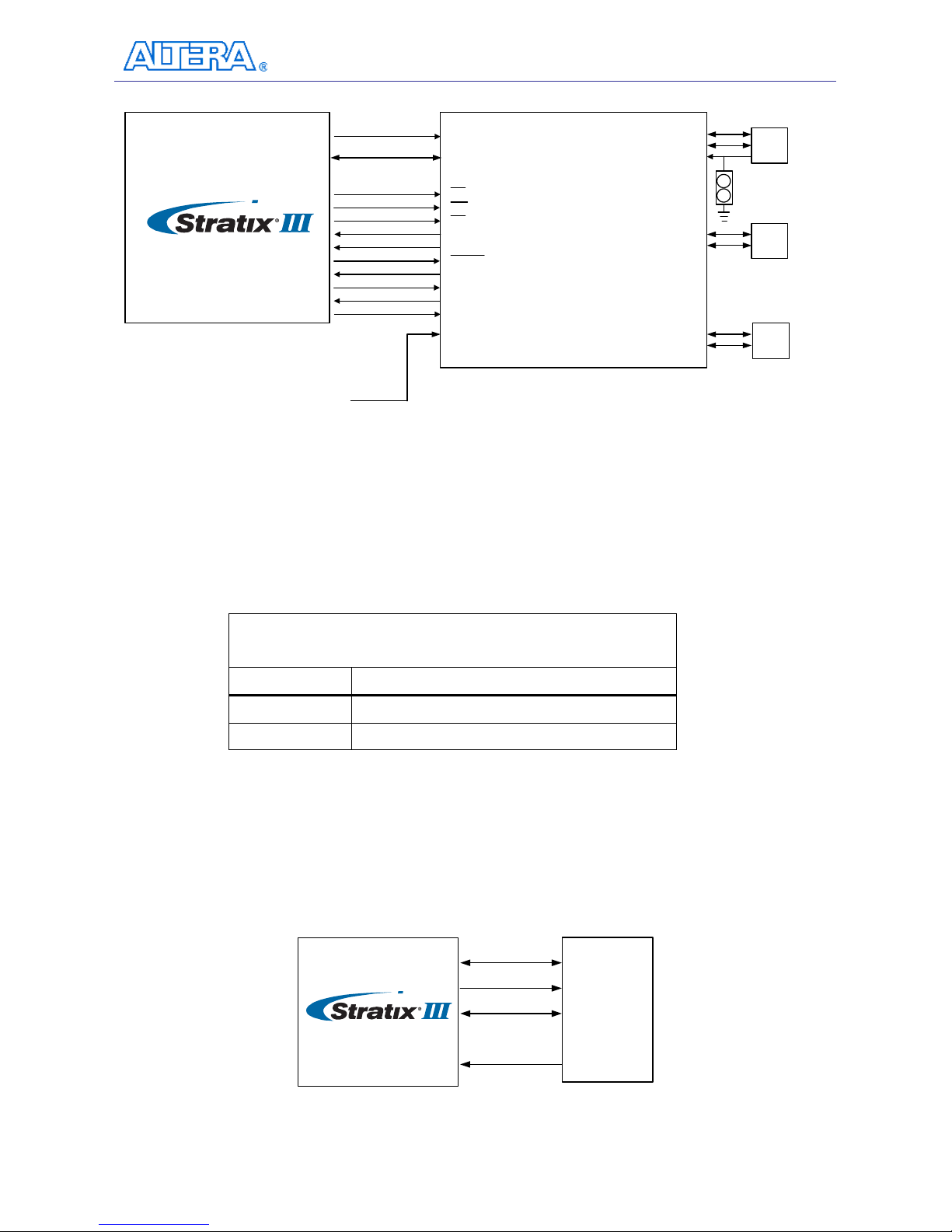

Figure 2.15. Connections between the GPIO expansion headers and Stratix III

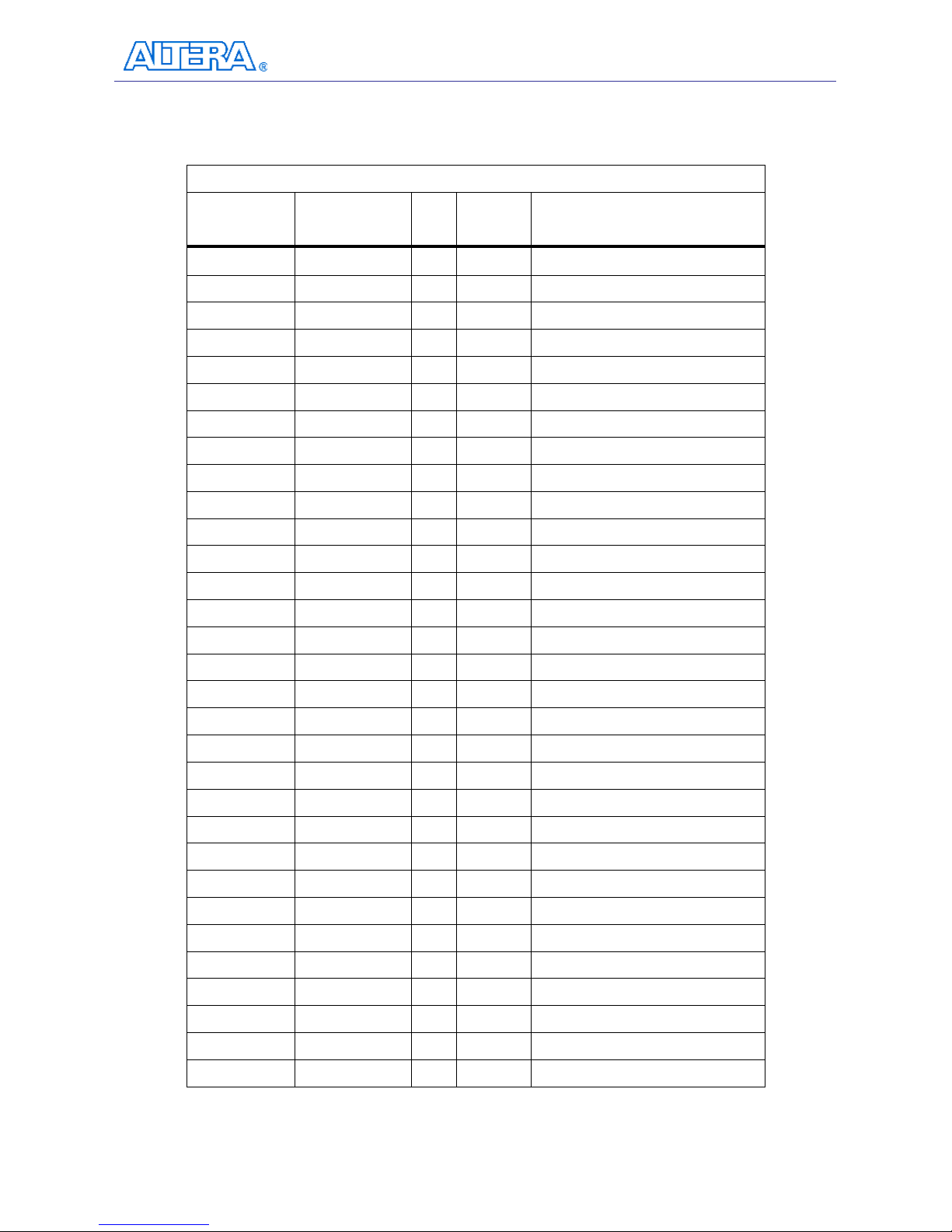

2.8 Using the DDR2 SO-DIMM

The DE3 board provides a 200-pin DDR2 SO-DIMM socket. The maximum capacity supported is

4GB. The DDR2 SO-DIMM shares the same I/O pins with the HSTC connector B, except the

Page 25

DE3 User Manual

22

command input signals DDR2_CS_N[1..0] and presence-detect address input signals

DDR2_SA[1..0]. Users should never use the DDR2 SO-DIMM socket and the HSTC connector B at

the same time.

Figure 2.16 shows the connections between the DDR2 SO-DIMM socket and Stratix

III device. The pin assignments are listed in Table A-14.

T8

T9

DDR2_DQ [ 0..63 ]

HSTCB_SCL

HSTCB_SDA

HSTCB_RX_n [ 0 .. 29 ]

HSTCB_RX_p [ 0 .. 29 ]

HSTCB_TX_n [ 0 .. 29 ]

HSTCB_TX_p [ 0 .. 29 ]

DDR2_DQS_p [ 0..7 ]

DDR2_DQS_n [ 0..7 ]

DDR2_A [ 0..15 ]

DDR2_DM [ 0..7 ]

DDR2_CLK_p [ 0..1 ]

DDR2_CLK_n [ 0..1 ]

DDR2_BA [ 0..2 ]

DDR2_ODT [ 0..1 ]

DDR2_CKE [ 0..1 ]

DDR2_CS_n [ 0..1 ]

DDR2_SCL

DDR2_SDA

HSTC B

DDR2_CS_n [ 0..1 ]

DDR2_SA [ 0..1 ]

Figure 2.16. Connections between the DDR2 and Stratix III FPGA

2.9 Using the USB OTG

The DE3 board provides both USB host and device interfaces using the Philips ISP1761ET

single-chip USB controller. The host and device controllers are compliant with the Universal Serial

Bus Specification Rev. 2.0, supporting data transfer at high-speed (480 Mbit/s), full-speed (12

Mbit/s) and low-speed (1.5 Mbit/s). Figure 2.17 shows the connection between the USB OTG and

Stratix III device. The port 1 can be configured as a downstream port, or an upstream port or OTG

port. If the port 1 is configured as an OTG port, users can use JP1 to specify host or peripheral role,

as listed in Table 2-4. The pin assignments for the associated interface are listed in Table A-15.

Page 26

DE3 User Manual

23

NXP

ISP1761ET

DM1

DP1

USB_ID

DM2

DM3

DP2

DP3

miniAB

TYPE A

JP1 Close = Host

JP1 Open = Device

Host

TYPE A

Host

A[ 1..17]

D[ 0..31]

CS

WR

RD

RESET

HC_IRQ

DC_IRQ

HC_DREQ

HC_DACK

DC_DREQ

DC_DACK

CLKIN

P28

N29

N30

P29

R27

T23

R28

R25

R26

R24

See Table A-15

12MHz

See Table A-15

Figure 2.17. Connections between the USB OTG and Stratix III device

Detailed information of the ISP1761ET device can be found in its datasheet and programming guide;

both documents are available from the manufacturer’s web site, or in the Datasheet/USB folder of

the DE3 System CD. Two complete examples for host and device applications each, can be found

in Sections 5.1and 5.2. These demonstrations provide software drivers for the Nios II processor.

Table 2-4 The default host or peripheral setting for port 1 (J15) of the

ISP1761ET

JP1 setting Connectors

Open Port1 set to peripheral

Close Port 1 set to host

2.10 Using the SD Card

The DE3 board has a SD card socket and can be accessed as optional external memory in both SPI

and 1-bit SD mode. Table A-16 shows the pinout of the SD card socket with Stratix III FPGA.

5

R10

SD Card

SD_CMD

P8

N5

P7

2

7

11

SD_CLK

SD_WPn

SD_DAT 0

Page 27

DE3 User Manual

24

Figure 2.18. Connections between the SD card and Stratix III

2.11 LED Indicators

The DE3 board includes some LEDs to indicate the specified hardware status. The relationship of

LED names and their associated functions are list in Table 2-5.

Table 2-5 Description for LED indicator

LED Name Descriptions

POWER Light on when Power switch(SW5) is turned on

CONF_DONE

Light on when the configuration data is received by Stratix

III FPGA without error ad initialization cycle starts.

LOAD Light on when USB blaster circuit transmits or receives data

LINKA

Light on when HSTC connector A top (J1) is connected with

an extended board

LINKB

Light on when HSTC connector B top (J3) is connected with

an extended board

LINKC

Light on when HSTC connector C top (J5) is connected with

an extended board

LINKD

Light on when HSTC connector D top (J7) is connected with

an extended board

OVT

Light on when the temperature value of the FPGA is higher

than the threshold value setting in the temperature sensor.

USB3,

USB2,

USB1

Power LED indicators for USB port3 (J17), port2 (J16), and

port1 (J1). Each LED will be on as soon as the port power of

the respective port is enabled by software, for example,

after loading drivers

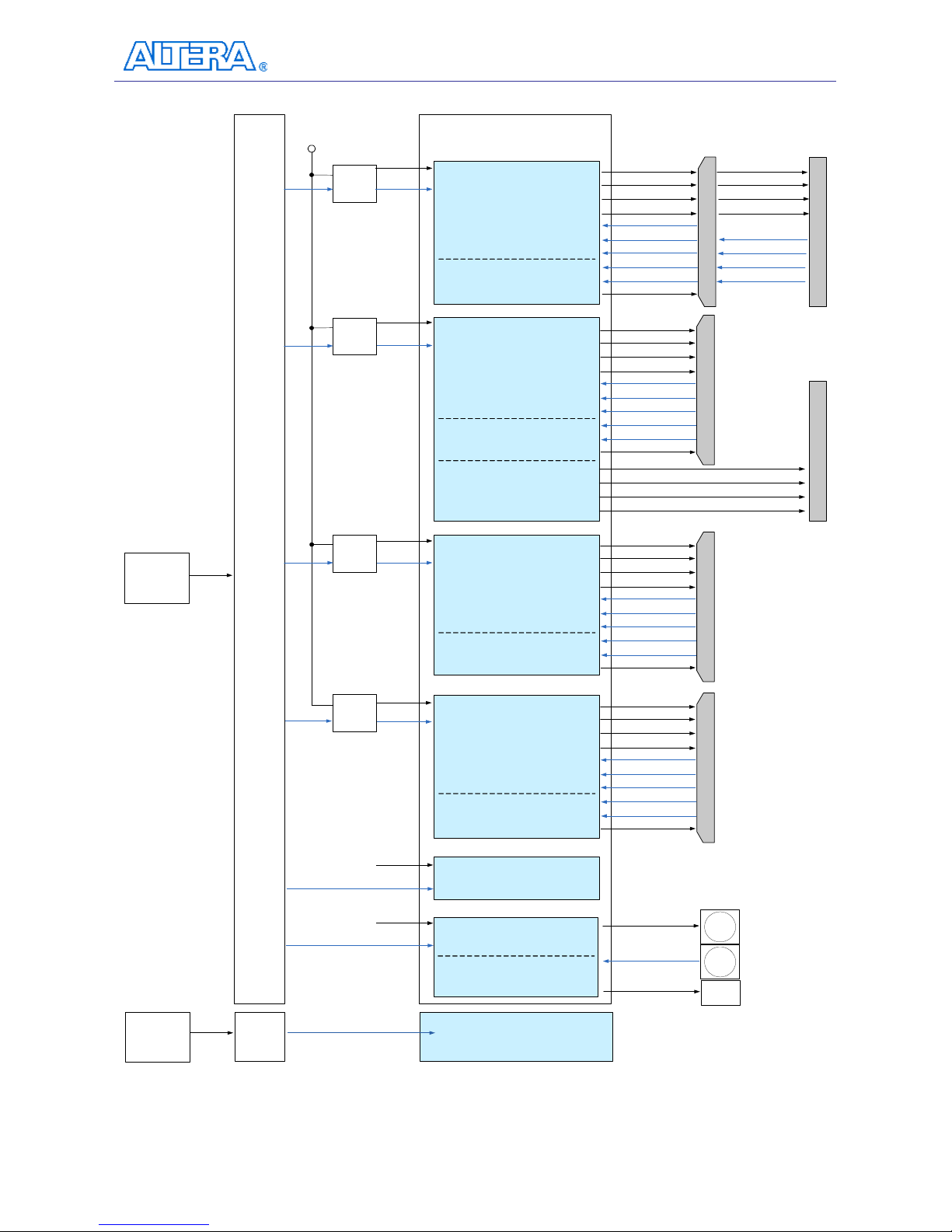

2.12 Clock Circuitry

Clock inputs:

The clock input source of Stratix III FPGA comes from the clock buffer, HSTC connectors, GPIO

expansion headers, and SMA connector as indicated in Figure 2.19. Three of five clock inputs are

connected to the dedicated high speed clock input pins of the FPGA, which allows users to use any

of these clocks as a source clock for the PLL circuit.

Note: The 3 clock inputs connected to the dedicated inputs of the FPGA are (CLKIN_2, CLKIN_n1,

and CLKIN_p1 respectively).

Clock outputs:

Page 28

DE3 User Manual

25

The clock output of Stratix III FPGA includes HSTC connectors, GPIO expansion headers, SMA

connector, and SD card socket as shown in

Figure 2.19.

The associated pin assignments for clock buffer and SMA connectors to FPGA I/O pins are shown

in Table A-17.

Page 29

DE3 User Manual

26

50MHz

Oscillator

Adjustable

+3.3V

Level

Shift

Adjustable

Adjustable

Adjustable

+3.3V

+3.3V

50MHz

50MHz

VCCIO

CLK4p

50MHz

50MHz

50MHz

USB

Blaster

Circuit

12MHz

USB 2.0 OTG

CLK4n

HSTC A

CLKIN2

CLK5n

CLKIN_n1

CLK5p

CLKIN_p1

CLKIN_n1

CLKIN_p1

GPIO

CLKOUT_n1

CLKOUT_p1

PLL_B1_CLKOUT4

Bank 3C

Bank 2A

CLKIN_n0

CLKIN_p0

CLKIN_n0

CLKIN_p0

CLKOUT2

DIFFIO_RX_L34n

DIFFIO_RX_L34p

DIFFIO_TX_L33p

VCCIO

CLK6p

CLK6n

CLK7n

CLK7p

PLL_B2_CLKOUT4

Bank 4C

Bank 5A

DIFFIO_RX_R11n

DIFFIO_RX_R11p

DIFFIO_TX_R12p

DDR2

Bank 4A

DIFFIO_RX_B47n

DIFFOUT_B94n

VCCIO

CLK12p

CLK12n

CLK13n

CLK13p

PLL_T2_CLKOUT4

Bank 7C

Bank 6A

DIFFIO_RX_R34n

DIFFIO_RX_R34p

DIFFIO_TX_R33p

VCCIO

CLK14p

CLK14n

CLK15n

CLK15p

PLL_T1_CLKOUT4

Bank 8C

Bank 1A

DIFFIO_RX_L11n

DIFFIO_RX_L11p

DIFFIO_TX_L12p

Level

Shift

Level

Shift

Level

Shift

VCCIO

Bank 1C

CLK1p

VCCIO

Bank 5C

Bank 6C

CLK8p

CLK10p

EXT_CLK

SMA

CLK_OUT

PLL_R3_FB_CLKOUT0p

SMA

24MHz

Oscillator

High

Speed

Clock

Buffer

PLL_T1_CLKOUT3

PLL_T1_CLKOUT0n

PLL_T1_CLKOUT0p

PLL_T2_CLKOUT3

PLL_T2_CLKOUT0n

PLL_T2_CLKOUT0p

PLL_B2_CLKOUT3

PLL_B2_CLKOUT0n

PLL_B2_CLKOUT0p

PLL_B1_CLKOUT3

PLL_B1_CLKOUT0n

PLL_B1_CLKOUT0p

CLKOUT_n0

CLKOUT_p0

CLKOUT_n1

CLKOUT_p1

CLKOUT_n0

CLKOUT_p0

HSTC B

CLKIN2

CLKIN_n1

CLKIN_p1

CLKOUT_n1

CLKOUT_p1

CLKIN_n0

CLKIN_p0

CLKOUT2

CLKOUT_n0

CLKOUT_p0

DIFFIO_RX_B47p

DIFFOUT_B94p

DDR2_CLKn0

DDR2_CLKp1

DDR2_CLKn1

DDR2_CLKp1

HSTC C

CLKIN2

CLKIN_n1

CLKIN_p1

CLKOUT_n1

CLKOUT_p1

CLKIN_n0

CLKIN_p0

CLKOUT2

CLKOUT_n0

CLKOUT_p0

HSTC D

CLKIN2

CLKIN_n1

CLKIN_p1

CLKOUT_n1

CLKOUT_p1

CLKIN_n0

CLKIN_p0

CLKOUT2

CLKOUT_n0

CLKOUT_p0

50MHz

SD

card

SD_CLK

DIFFIO_TX_R31p

OSC_BA

OSC_BB

OSC_BC

OSC_BD

OSC1_50

OSC2_50

Stratix III

Figure 2.19. Clock connections of the DE3

Page 30

DE3 User Manual

27

2.13 Using the Temperature Sensor

The DE3 board is equipped with a temperature sensor MAX1619, which provides temperature

sensing and over-temperature alert. These functions are achieved by connecting the temperature

sensor to the internal temperature sensing diode of the Stratix III device. The temperature status and

alarm threshold registers of the temperature sensor can be programmed by a two-wire SMBus,

which is connected to the Stratix III FPGA as shown in Figure 2.20. In addition, the 7-bit POR slave

address for this sensor is set to ‘0011000’.

There is an option of connecting a 2-pin +12V fan to JP2 for cooling purpose. The pin near the

HSTC connector C is for +12V, the other one is used for GND. When the temperature of the FPGA

device is over the threshold value set by users, the fan will be turned on. The pin assignments for

the associated interface are listed in Table A-18.

Finally, the detailed information of the temperature sensor device can be found in its datasheet,

which is available from the manufacturer’s web site, or in the Datasheet/Temperature_Sensor folder

of the DE3 System CD.

TEMP_CLK

TEMP_DATA

TEMP_INTn

TEMP_OVERn

Temperature

Sensor

TEMPDIODEp

TEMPDIODEn

DXP

DXN

ALERT

OVERT

SMBDATA

SMBCLK

Figure 2.20. Connections between the temperature sensor and Stratix III device

Page 31

DE3 User Manual

28

Chapter 3

Control Panel

3

The DE3 board comes with a PC-based Control Panel that allows users to access various

components onboard. The host computer communicates with the board via USB port. The tool can

be used to verify the functionality of components.

This chapter presents some basic functions of the Control Panel, illustrates its structure in block

diagram form, and finally describes its capabilities.

3.1 Control Panel Setup

The Control Panel software utility is located in the directory “/Tools/DE3_control_panel” in the

DE3 System CD. To execute the program, simply copy the whole folder to your host computer and

launch the control panel by double clicking the “DE3_Control_Panel.exe”.

The DE3_Control_Panel.exe will auto-detect the FPGA and download the control codes, the .sof

and .elf file, to the Stratix III device through USB-Blaster port.

To activate the Control Panel, perform the following steps:

1. Make sure Quartus II and NIOS II are installed successfully on your PC.

2. Connect the supplied USB cable to the USB Blaster port and the supplied power cord to

J18. Turn the power switch ON as shown in Figure 3.1.

3. Start the executable DE3_control_panel.exe on the host computer. Figure 3.2 will appear

and the Control Panel starts to auto-detect the FPGA and download the .sof and .elf files.

4. After the configuration file is programmed to the DE3 board, the FPGA device information

will be displayed on the window.

5. Note the Control Panel will occupy the USB port, users will not be able to download any

configuration file into the FPGA before you exit the Control Panel program.

6. The Control Panel is now ready, as shown in Figure 3.3

Page 32

DE3 User Manual

29

Figure 3.1. Setup of USB-Blaster cable and power cord

Figure 3.2. Download .sof and .elf files to the DE3 board

Page 33

DE3 User Manual

30

Figure 3.3. DE3 Control Panel is ready

If the connection between DE3 board and USB-Blaster is not established, or the DE3 board is not

powered on before running the DE3_control_panel.exe, the Control Panel will fail to detect the

FPGA and a warning message window will pop up as shown in Figure 3.4.

Figure 3.4. The DE3 Control Panel fails to download .sof file

Page 34

DE3 User Manual

31

The concept of the DE3 Control Panel is illustrated in

Figure 3.5.The “Control Codes” which

performs the control functions is implemented in the FPGA board. It communicates with the

Control Panel window, which is active on the host computer, via the USB Blaster link. The

graphical users interface is used to issue commands to the control codes. It handles all requests and

performs data transfer between the computer and the DE3 board.

EPCS

128

Control

Codes

IO BANK POWER

Power Off / Write / Read

Figure 3.5. The DE3 Control Panel concept

The DE3 Control Panel can be used to light up LEDs, change the values displayed on 7-segment

displays, monitoring buttons/switches status, read/write the serial configuration devices (EPCS128),

access DDR2 SO-DIMM memory, read the information of SD Card, and setup the V

CCIO

level of

the I/O Groups.

3.2 Controlling the LEDs and 7-Segment Displays

One of the functions of the Control Panel is to set up the status of the LEDs and 7-segment displays.

The tab-window shown in Figure 3.6 indicates where you can directly turn all the LEDs on or off

individually by selecting them and clicking “Light All” or “Unlight All”.

Page 35

DE3 User Manual

32

Figure 3.6. Controlling LEDs

Figure 3.7 shows the interface of the 7-SEG and how to select desired patterns. The status of the

7-SEG patterns will be updated immediately.

Figure 3.7. Controlling 7-SEG display

Page 36

DE3 User Manual

33

3.3 SWITCH/BUTTON

Choose the Button tab as shown in Figure 3.8. This function is designed to monitor status of

switches and buttons from a graphic interface in real-time. It can be used to verify the functionality

of switches and buttons.

Figure 3.8. Monitoring Switches and Buttons

3.4 Memory Controller

The Control Panel can be used to write/read data to/from the DDR2 SO-DIMM memory on the DE3

board. We will describe how the DDR2 SO-DIMM is accessed. Click on the Memory tab to reach

the tab-window shown in Figure 3.9.

A 16-bit string can be written into the DDR2 SO-DIMM memory by three steps, namely specifying

the address of the desired location, entering the data to be written, and pressing the Write button.

Contents of the location can be read by pressing the Read button. Figure 3.10 depicts the result of

writing the hexadecimal value 7EFF to location 0x100, followed by reading the same location.

The Sequential Write function of the Control Panel is used to write the contents of a file to the serial

configuration device, as described below:

1. Specify the starting address in the Address box.

Page 37

DE3 User Manual

34

2. Specify the number of bytes to be written in the Length box. If the entire file is to be

loaded, a check mark can be placed in the File Length box instead of giving the number of

bytes.

3. To initiate the writing of data, click on the Write a File to Memory button.

4. When the Control Panel responds with the standard Windows dialog box asking for the

source file, specify the desired file in the usual manner.

The Sequential Read function is used to read the contents of the serial configuration device and

place them into a file as follows:

1. Specify the starting address in the Address box.

2. Specify the number of bytes to be copied into a file in the Length box. If the entire

contents of the serial configuration device are to be copied, then place a check mark in the

Entire Memory box.

3. Press Load Memory Content to a File button.

4. When the Control Panel responds with the standard Windows dialog box ask for the

destination file, users can specify the desired file in the usual manner.

Figure 3.9. Access DDR2 SO-DIMM memory

Page 38

DE3 User Manual

35

Figure 3.10. Writing the hexadecimal value 7EFF to location 0x100

3.5 USB2.0 OTG

Choose the USB tab to reach the window in Figure 3.11. The function is designed to monitor the

status of USB Hub in real-time.

Plug a USB device to any USB port of FPGA board, and both the device type and speed will be

displayed on the control window. Figure 3.11 shows a low-speed HID USB Mouse is plugged into

port 3.

Page 39

DE3 User Manual

36

Figure 3.11. Monitoring status of USB ports

3.6 SD CARD

Choose the SD-CARD tab to the window shown in Figure 3.12. The function is designed to read

the identification and specification of SD Card. Single-bit SD-MODE is used to access the SD Card.

This function can be used to verify the functionality of SD-CARD interface.

To gather the information, simply insert a SD Card to the FPGA board and press the Read button.

The SD-CARD identification and specification will be displayed on the control window

Page 40

DE3 User Manual

37

Figure 3.12. Reading the SD Card Identification and Specification

3.7 Temperature Monitor

Choose the Temperature tab to reach the window shown in Figure 3.13. The function is designed

to control temperature sensor through Control Panel. The temperatures of Stratix III and DE3 board

are shown on the right-hand side of the Control Panel.

When the temperature of Stratix III exceeds the Maximum setting of Over Temperature or Alert, a

warning message will be shown on the Control Panel. Click “Read” button to get current settings

for Over temperature and Alert. Users can enter the maximum and minimum temperatures for Over

temperature or Alert as required. Click the “Write” button to update the values entered.

Page 41

DE3 User Manual

38

Figure 3.13. Accessing the Temperature Sensor through Control Panel

3.8 I/O Group

Choose the I/O Group tab to reach the window shown in Figure 3.14. The function is designed to

read/write and control the V

CCIO

level of all I/O Groups of the DE3 board.

Click the “Read” button to enter the window shown in Figure 3.15. Current V

CCIO

level of all I/O

Groups will be displayed.

Page 42

DE3 User Manual

39

Figure 3.14. Accessing the power status of all I/O Groups

Figure 3.15. Reading the V

CCIO

level of all I/O Groups

Page 43

DE3 User Manual

40

3.9 Overall Structure of the DE3 Control Panel

The DE3 Control Panel communicates with control codes, which are instantiated in the Stratix III

FPGA..

To run the Control Panel, users must set it up first, as explained in Section 3.1. Figure 3.16 depicts

the structure of the Control Panel. Each input/output device is controlled by the NIOS II Processor

instantiated in the FPGA chip. The communication with the PC is done via the USB Blaster link.

The NIOS II interprets the commands sent from the PC and performs the appropriate actions.

Figure 3.16. The block diagram of the DE3 control panel

Page 44

DE3 User Manual

41

Chapter 4

DE3 System Builder

4

This chapter describes how to create a custom design project on the DE3 board by using DE3

System Builder.

4.1 Introduction

The DE3 System Builder is designed to assist users to create a Quartus II project for DE3 board

within minutes. The generated Quartus II project files include:

Quartus II Project File (.qpf)

Quartus II Setting File (.qsf)

Top-Level Deign File (.v)

Synopsis Design Constraints file (.sdc)

Encrypted Power Configuration Controller (.v)

Pin Assignment Document (.htm)

The DE3 System Builder not only can generate the files above, but also can provide error-checking

rules to prevent users from making the following common mistakes:

1. Board damaged for wrong pin/bank voltage assignment.

2. Board malfunction caused by wrong device connections or missing pin counts for

connected ends.

3. Performance dropped because of improper pin assignments.

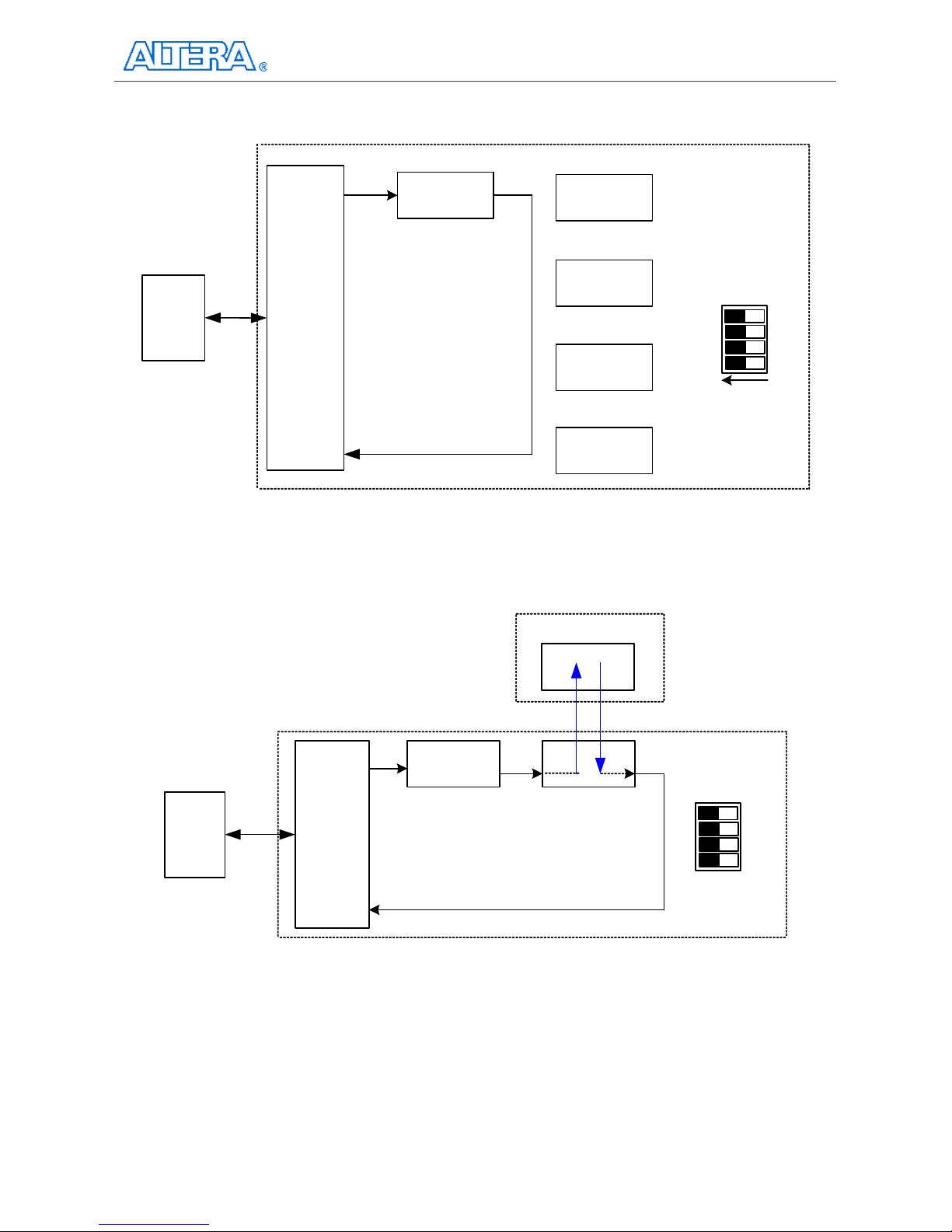

4.2 General Design Flow

This section will introduce the general design flow to build a project for the DE3 board via the DE3

System Builder. The general design flow is illustrated in the Figure 4.1.

First of all, users should launch DE3 System Builder and create a new project according to the

requirement. When users complete the settings, the DE3 System Builder will generate three major

files, which include top-level deign file (.v), encrypted power configuration controller (.v), and

Quartus II setting file (.qsf).

Page 45

DE3 User Manual

42

The top-level deign file contains top-level verilog wrapper for users to add their own design/logic.

The encrypted power configuration controller file contains encrypted core which is generated by

user’s selection on I/O Group voltage. The Quartus II setting file contains information such as

FPGA device type, top-level pin assignment, and I/O standard for each user-defined I/O pin.

Next, users must be aware that they can never modify encrypted power configuration controller file.

User’s own design should be included within top-level deign file.

Finally, Quartus II programmer must be used to download SOF file to DE3 board using JTAG

interface.

Start

Launch

DE3 System Builder

Create New

DE3 System Builder

Project

.QPF

.QSF

.V

.HTML

.SDC

Generate

Quartuss II Project

and Document

Launch Quartus II and

Open Project

Add User Design/

Logic

Compile to generate

.SOF

Configure FPGA

End

Figure 4.1. The general design flow of building a design

for the DE3 board via the DE3 System Builder

Page 46

DE3 User Manual

43

4.3 Using DE3 System Builder

This section provides the detail procedures on how to use the DE3 System Builder.

Install and active the DE3 System Builder

The DE3 System Builder is located in the directory: "Tools\DE3_System_Builder" in

the DE3 System CD. Users can copy the whole folder to a host computer without

installing the utility. Before using the DE3 System Builder, perform the following steps:

Make sure the license file of the “Encrypted Power Configuration Controller

IP” is set in the Quartus II software. (Please refer to the section Add the License

File for Terasic Power Controller IP in the document named “Getting start with

Altera DE3 board” for more information on how to import a license file.)

Execute DE3_System_Builder.exe on the host computer. The DE3 System Builder

user-interface will appear, as shown in Figure 4.2.

Figure 4.2. The DE3 System Builder window

Add Board

On the left-hand side of the DE3 System Builder, there are many boards’ icons in the

Board Selection field. If users select a DE3 board and click Add button, a DE3

Configuration window will pop up. After the setting is completed, a DE3 board will be

added to the System Configuration field.

Page 47

DE3 User Manual

44

If users select any of the daughter boards in the Board Selection field, a window will

pop up and allow users to change the name of the daughter board. Click OK to add the

daughter board to System Configuration Filed.

DE3 Configuration

When users add a DE3 board, a DE3 Configuration window will pop up as shown in

Figure 4.3. This window allows users to configure many features for the DE3 board as

described below:

Figure 4.3. The DE3 Configuration window

Board Name: The board name will be set as the Quartus II project name when it is

created by DE3 System Builder.

FPGA Type: The FPGA device on DE3 board may be EP3SL150 or EP3SH340.

Users need to select the FPGA device and speed grade accordingly.

User I/O Components: Users can enable or disable the User I/O Component from

this field. If the User I/O component is enabled, the DE3 System Builder will

generate the port name, port connection rules (input/output) and the pin

assignments for the User I/O component on the Quartus II top-level file.

Page 48

DE3 User Manual

45

IO Group: There are four I/O Groups in the DE3 Configuration window. The

HSTC connector A, B, C, and D correspond to I/O Groups A, B, C, and D on DE3

board, respectively. Disabled I/O Groups will not be listed in the Quartus II

top-level file. There are three options for each I/O Group as listed below:

i. Type: Users can select a connector type for I/O Group A and B., as

the HSTC connector A and B share the same I/O bus with the GPIO

expansion headers and DDRII SO-DIMM socket.

ii. I/O standard: Users can select the I/O standard for the I/O Group.

iii. Name: Users can change the name of a connector.

I/O GROUP Voltage-level Indicator: This function will indicate the V

CCIO

level

for current I/O standard setting of the four I/O Croups. The status is same as the

LEDs on the DE3 board. Please refer to Section 2.4 for details.

Connection Between Two Connectors

When users add a DE3 board and daughter board in the System configuration field, it is

necessary to establish the connection in between. The port name, port connection rules

(input/output) and the pin assignment of the connector in the top-level file will be fully

compatible with this daughter board. The detailed steps for the connection setup are

shown below:

Establish and remove a connection between two connectors:

i. Move the mouse cursor to the upper connector as shown in Figure 4.4.

Figure 4.4. Step 1 of establishing a connection.

ii. Hold the left button of the mouse and Drag the mouse cursor to the

lower connector as shown in Figure 4.5.

Page 49

DE3 User Manual

46

Figure 4.5. Step 2 of establishing a connection

iii. Release the left mouse button and a green connection line will be

drawn between two connectors as shown in Figure 4.6.

Figure 4.6. Step 3 of establishing a connection

iv. Redo the steps i to iii will remove an established connection as shown

in Figure 4.7.

Figure 4.7. The step for removing a connection between two connectors

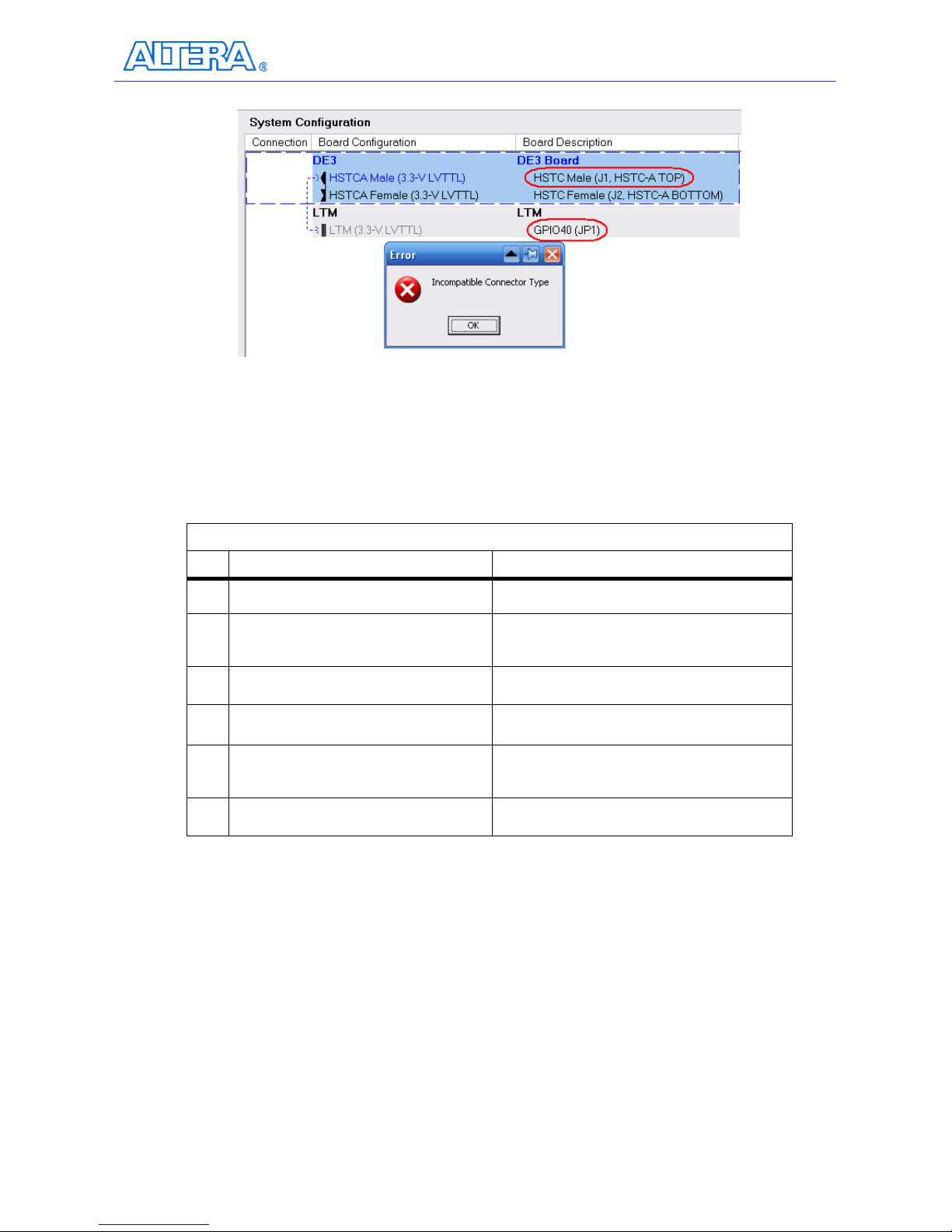

Warning message of an incorrect connection

If users try to establish a connection between two different types and I/O standard

of connectors, a warning message box will pop up as shown in Figure 4.8.

Page 50

DE3 User Manual

47

Figure 4.8. The error message box of an incorrect connection

Project Generation

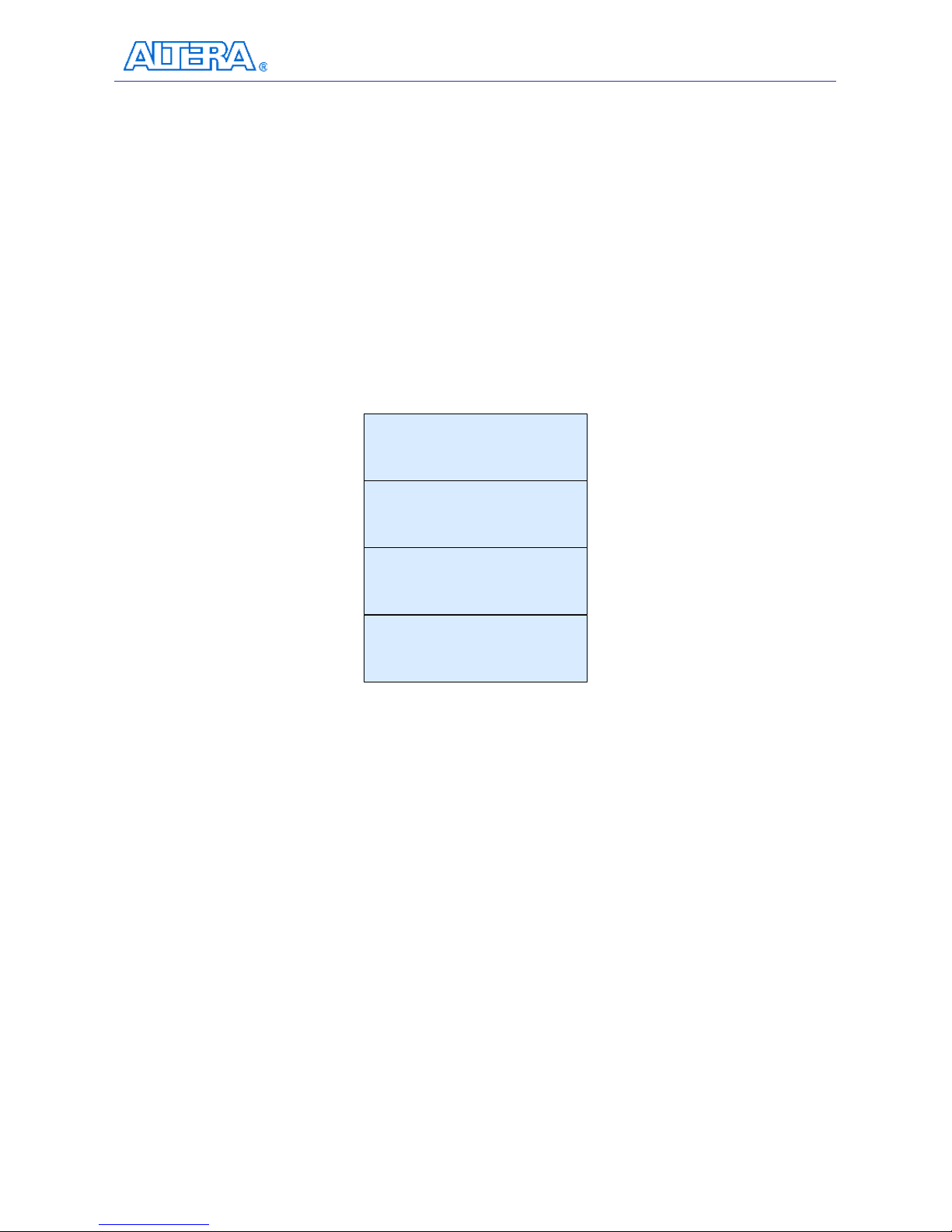

When users press the Generate button, the DE3 System Builder will generate the

corresponding Quartus II files and documents as listed in the Table 4-1:

Table 4-1. The files generated by DE3 System Builder

No.

Filename Description

1 <Board name>.v Top level verilog file for Quartus II

2 IOV_<IO Group voltage level>.v

Encrypted Power Configuration

Controller IP

3 <Board name>.qpf Quartus II Project File

4 <Board name>.qsf Quartus II Setting File

5 <Board name>.sdc Synopsis Design Constraints file for

Quartus II

6 <Board name>.htm Pin Assignment Document

Users can use Quartus II software to add custom logic into the project and compile the

project to generate the SRAM Object File (.sof).

In addition, the Encrypted Power Configuration Controller IP is used to control the

V

CCIO

level of the I/O Groups. This IP file is included in the Quartus II top-level file as

listed in below:

Page 51

DE3 User Manual

48

//=================================================

// IO Group Voltage Configuration (Do not modify it)

//=================================================