Page 1

1

Page 2

CONTENTS

CHAPTER 1 INTRODUCTION ................................................................................................................................. 3

PACKAGE CONTENTS ................................................................................................................................................. 3

1.1

1.2

CYCLONE V GX STARTER KIT SYSTEM CD .............................................................................................................. 4

1.3

LA YOUT A ND COMPONENTS ...................................................................................................................................... 4

1.4

BLOCK DIAGRAM OF THE CYCLONE V GX STARTER KIT BOARD .............................................................................. 8

1.5

GETTING HELP .......................................................................................................................................................... 8

CHAPTER 2 CONTROL PANEL ............................................................................................................................... 9

CONTROL PANEL SETUP ............................................................................................................................................ 9

2.1

2.2

CONTROLLING THE LEDS, 7-SEGMENT DISPLAYS ................................................................................................... 12

2.3

SWITCHES AND PUSH-BUTTONS .............................................................................................................................. 14

2.4

SRAM/LPDDR2 CONTROLLER AND PROGRAMMER ............................................................................................... 15

2.5

SD CARD ................................................................................................................................................................ 17

2.6

ADC ....................................................................................................................................................................... 17

2.7

UART-USB COMMUNICATION ................................................................................................................................ 18

2.8

HDMI-TX .............................................................................................................................................................. 19

2.9

HSMC .................................................................................................................................................................... 20

2.10

OVERALL STRUCTURE OF THE C5G CONTROL PANEL ........................................................................................... 21

CHAPTER 3 USING THE STARTER KIT .............................................................................................................. 23

CONFIGURATION, STAT US AND SETUP ..................................................................................................................... 23

3.1

3.2

GENERAL USER INPUT/OUTPUT .............................................................................................................................. 27

3.3

CLOCK CIRCUIT ...................................................................................................................................................... 33

3.4

RS-232 SERIAL PORT TO USB INTERFACE ............................................................................................................... 35

3.5

SRAM : STAT IC RANDOM ACCESS MEMORY .......................................................................................................... 36

3.6

LPDDR2 MEMORY ................................................................................................................................................. 37

3.7

MICRO SD-CARD .................................................................................................................................................... 40

3.8

HDMI TX INTERFACE ............................................................................................................................................. 42

3.9

AUDIO INTERFACE ................................................................................................................................................... 43

3.10

HSMC : HIGH-SPEED MEZZANINE CARD ............................................................................................................. 44

3.11

USING THE 2X20 GPIO EXPANSION HEADER ........................................................................................................ 49

CHAPTER 4 SYSTEM BUILDE R ........................................................................................................................... 56

INTRODUCTION ....................................................................................................................................................... 56

4.1

4.2

GENERAL DESIGN FLOW ......................................................................................................................................... 56

4.3

USING C5G SYSTEM BUILDER ................................................................................................................................ 57

1

Page 3

CHAPTER 5 RTL BASED EXAMPLE CODES ...................................................................................................... 64

FACTORY CONFIGURATION ...................................................................................................................................... 64

5.1

5.2

LPDDR2 SDRAM RTL TEST ................................................................................................................................. 65

CHAPTER 6 NIOS-II BASED EXAMPLE CODES ............................................................................................... 68

SRAM .................................................................................................................................................................... 68

6.1

6.2

UART TO USB CONTROL LED ................................................................................................................................. 71

6.3

HDMI TX ............................................................................................................................................................... 75

6.4

TRANSCEIVER HSMC LOOPBACK TEST .................................................................................................................. 83

6.5

AUDIO RECORDING AND PLAYING ........................................................................................................................... 84

6.6

MICRO SD CARD FILE SYSTEM READ ...................................................................................................................... 87

6.7

SD CARD MUSIC PLAYER DEMONSTRATION ............................................................................................................. 91

2

Page 4

Chapter 1

Introduction

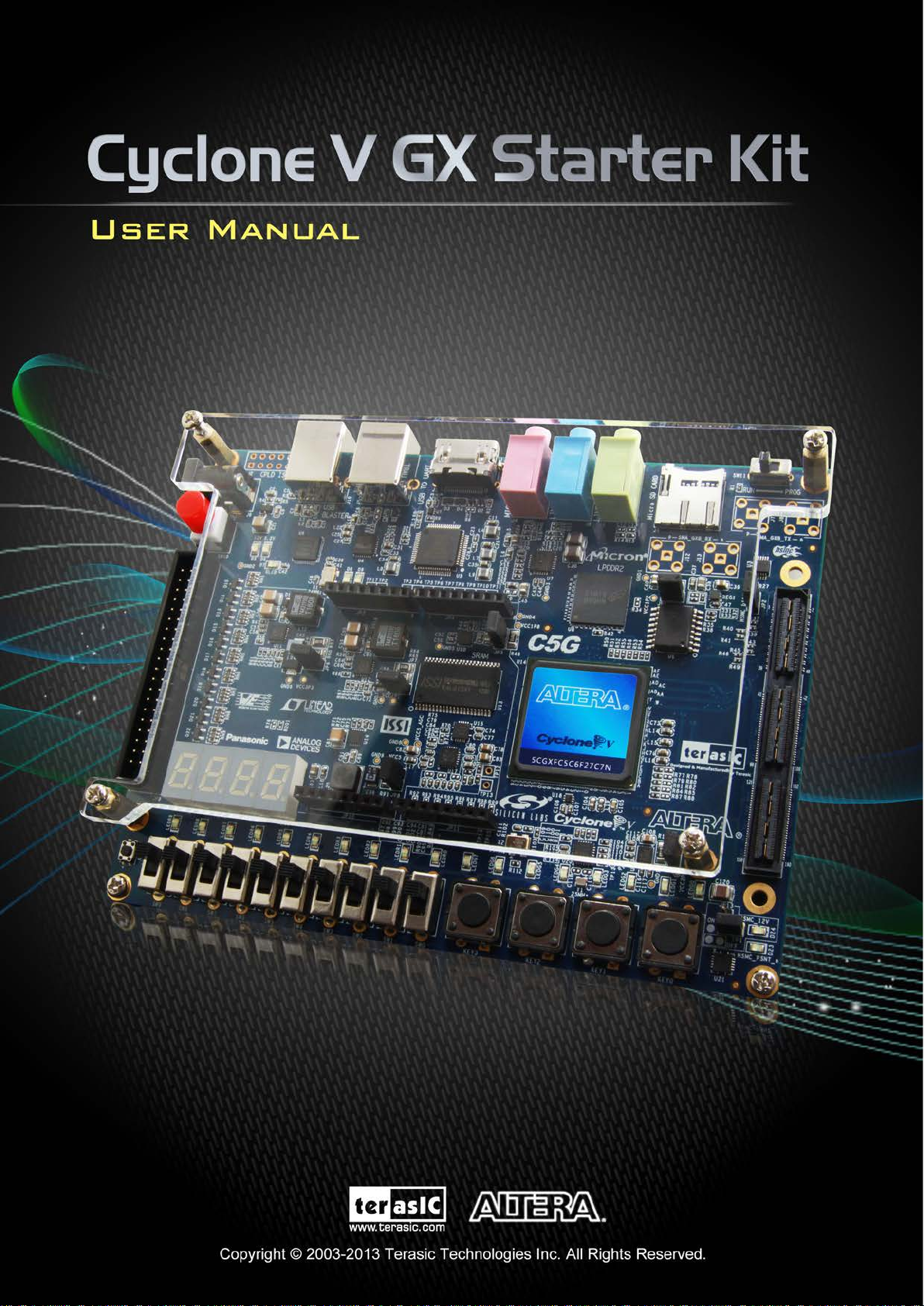

The Cyclone V GX Starter Kit p resents a robust hardware design platform built around the Altera

Cyclone V GX FPGA, which is optimized for the lowest cost and power requirement for transceiver

applications with industry-leading programmable logic for ultimate design flexibility. With Cyclone

V FPGAs, you can get the power, cost, and performance levels you need for high-volume

applications including protocol bridging, motor control drives, broadcast video converter and

capture cards, and handheld devices. The Cyclone V GX Starter Kit development board includes

hardware such as Arduino Header, on-board USB Bl aster, audio and video capabilities and much

more. In addition, an on -board HSMC connector with high-speed transceivers all ows for an even

greater array of hardw are setups. By leveraging all of these capabilities, the Cyclone V GX Starter

Kit is the perfect solution for showcasing, evaluating, and prototyping the true potential of the

Altera Cyclone V GX FPGA.

The Cyclone V GX Start er Kit contains all components needed to use the board in conjunction with

a computer that runs the Microsoft Windows XP or later.

11..11.. PPaacckkaaggee CCoonntteennttss

Figure 1-1 shows a photograph of the Cyclone V GX Starter Kit package.

Figure 1-1 The Cyclone V GX Starter Kit package contents

3

Page 5

The Cyclone V GX Starter Kit package includes:

• The Cyclone V GX Starter Kit board

• Cyclone V GX Starter Kit Quick Start Guide

• 12V DC Power Supply

• Type A Male to Type B Male USB Cable

• System CD

11..22.. CCyycclloonnee VV GGXX SSttaarrtteerr KKiitt SSyysstteemm CCDD

The Cyclone V GX Start Kit System CD contains the documentation and supporting materials,

including the User Manual, Control Panel, System Builder, referen ce des i g ns an d d evi c e d at ash eets .

User can download this System CD from the web (http://c5g.terasic.com).

11..33.. LLaayyoouutt aanndd CCoommppoonneennttss

This chapter presents the features and design characteristics of the board.

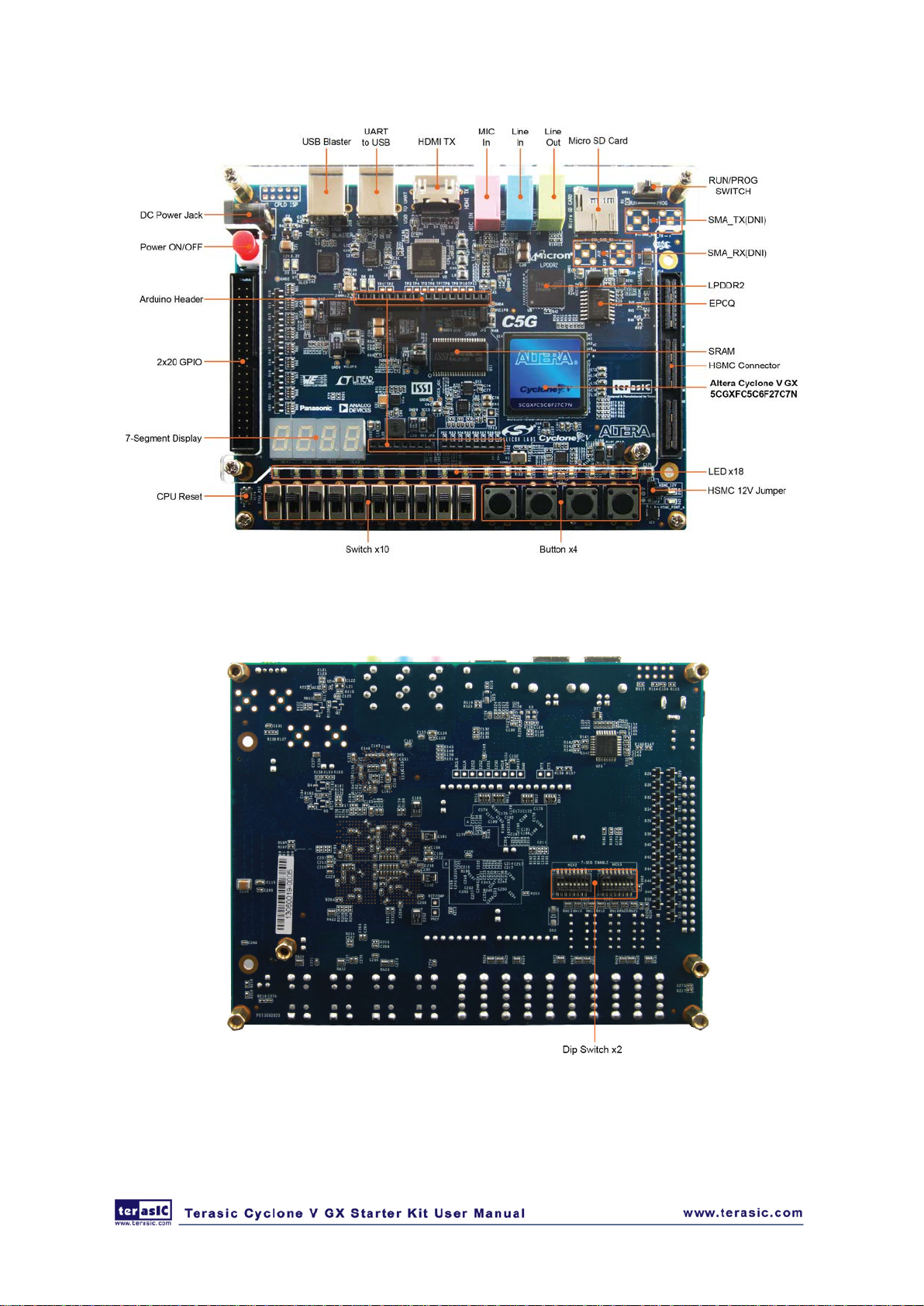

A photograph of the board is shown in Fig u re 1-2 and Fig u re 1-3. It depicts the layout of the board

and indicates the location of the connectors and key components.

This chapter presents the features and design characteristics of the board

4

Page 6

Figure 1-2 Development Board (top view)

Figure 1-3 Development Board (bottom view)

5

Page 7

The board has man y features t hat allow users to i mplement a wi de range o f designed cir cuits, fro m

simple circuits to various multimedia projects.

The following hardware is provided on the board:

FFPPGGAA DDeevviiccee

• Cyclone V GX 5CGXFC5C6F27C7N Device

• 77K Programmable Logic Elements

• 4884 Kbits embedded memory

• Six Fractional PLLs

• Two Hard Memory Controllers

• Six 3.125G Transceivers

CCoonnffiigguurraattiioonn aanndd DDeebbuug

• Quad Serial Configuration device – EPCQ256 on FPGA

• On-Board USB Blaster (Normal type B USB connector)

MMeemmoorryy DDeevviiccee

• LPDDR2 x32 bits data bus

• SRAM x16 bits data bus

g

CCoommmmuunniiccaattiioonn

• UART to USB

CCoonnnneeccttoorrss

• HSMC x 1, including 4-lanes 3.125G transceiver,

• 2x20 GPIO Header

• Arduino header, including analog pins.

• SMA pads, unpopulated.

DDiissppllaayy

• HDMI TX, compatible with DVI v1.0 and HDCP v1.4

6

Page 8

AAuuddiioo

• 24-bit CODEC, Line-in, line-out, and microphone-in jacks

SSwwiittcchheess,, BBuuttttoonnss aanndd LLEEDDss

• 18 LEDs

• 10 Slide Switches

• 4 Debounced Push Buttons

• 1 CPU reset Push Buttons

PPoowweerr

• 12V DC input

7

Page 9

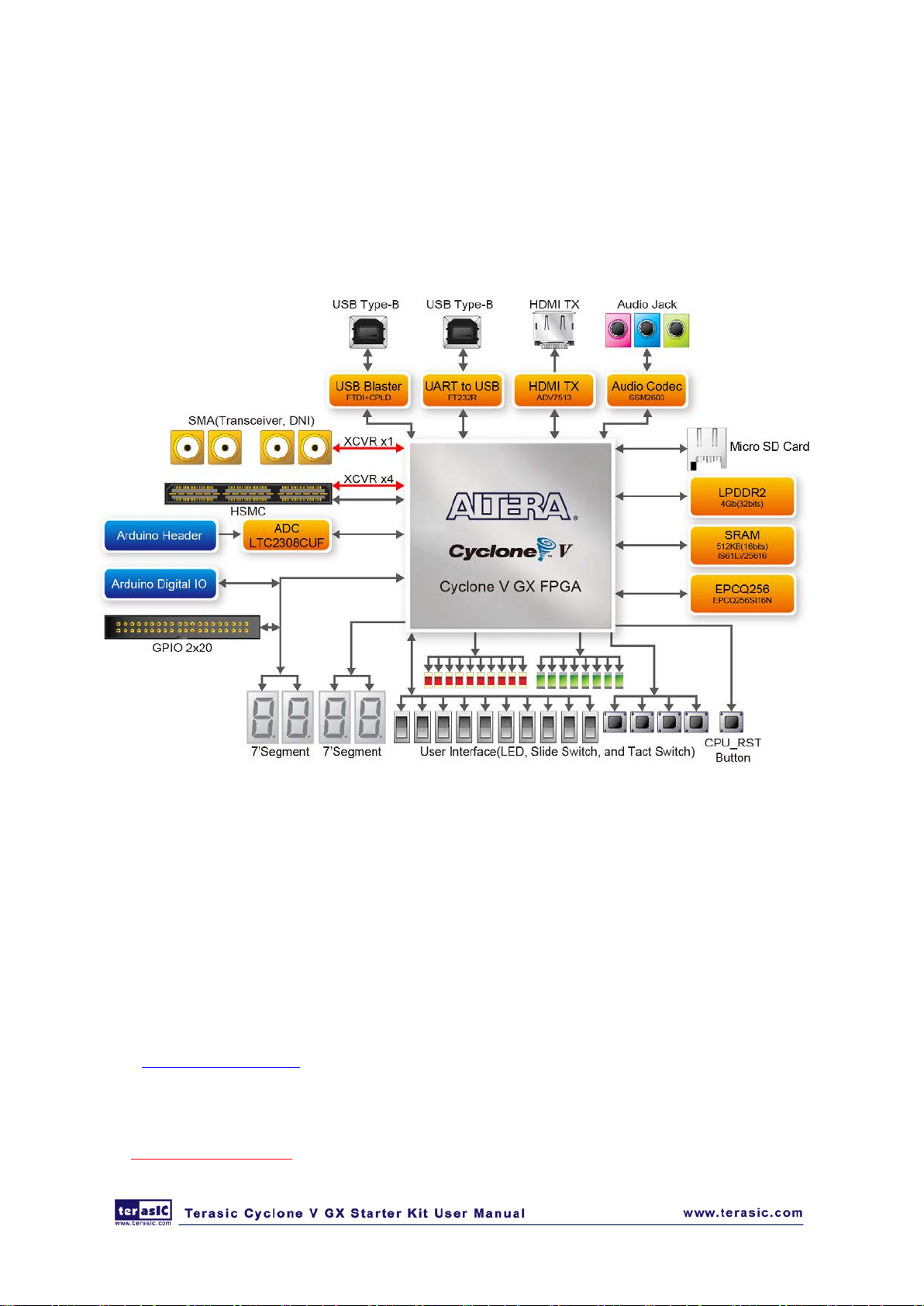

11..44.. BBlloocckk DDiiaaggrraamm ooff tthhee CCyycclloonnee VV GGXX SSttaarrtteerr KKiitt BBooaarrdd

Figure 1-4 gives the block diagram of the board. To provide maximum flexibility for the user, all

connections are made through the Cyclone V GX FPGA device. Thus, the user can configure the

FPGA to implement any system design.

Figure 1-4 Board Block Diagram

11..55.. GGeettttiinngg HHeellpp

Here are the addresses where you can get help if you encounter any problem:

• Terasic Technologies

Taiwan/ 9F, No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, Taiwan 300-70

Email: support@terasic.com

Tel.: +886-3-5750-880

Web: http://c5g.terasic.com

8

Page 10

Chapter 2

Control Panel

The Cyclone V GX Start board comes with a Control Panel program that allows users to access

various components on the board from a host computer. The host computer communicates with the

board through a USB connection. The program can be used to verify the functionality of

components on the board or be used as a debug tool while developing RTL code.

This chapter first presents some basic functions of the Control Panel, then describes its structur e in

the block diagram form, and finally describes its capabilities.

22..11

CCoonnttrrooll PPaanneell SSeettuup

The Control Panel Software Utility is located in the directory “Tools/ ControlPanel” on the Cyclone

V GX Starter Kit System CD. It's free of installation, just copy the whole folder to your host

computer and launch the control panel by executing the “C5G_ControlPanel.exe”.

p

Specific control circuits should be downloaded to your FPGA board before the control panel can

request it to perform required tasks. The program will call Quartus II tools to download the control

circuit to the FPGA board through the USB-Blaster[USB-0] connection.

To activate the Control Panel, perform the following steps:

1. Make sure Quartus II 13.0 or a later version is installed successfully on your PC.

2. Set the RUN/PROG switch to the RUN position.

3. Connect the supplied USB cable to the USB Blaster port, connect the 12V power supply, and

turn the power switch ON.

4. Start the executable C5G_ControlPanel.exe on the host computer. The Control Panel user

interface shown in Figure 2-1 will appear.

5. The C5G_ControlPanel.sof bit stream is loaded automatically as soon as the

C5G_ControlPanel.exe is launched.

6. In case of a disconnetion, click on CONNECT where the .sof will be re-loaded onto the board.

9

Page 11

Please note that the Control Panel will occupy the USB port until you close that port; you cannot use Quartus II

to download a configuration file into the FPGA until the USB port is closed.

7. The Control Panel is now ready for use; experience it by setting the ON/OFF status for some

LEDs and observing the result on the C5G board.

Figure 2-1 The C5G Control Panel

10

Page 12

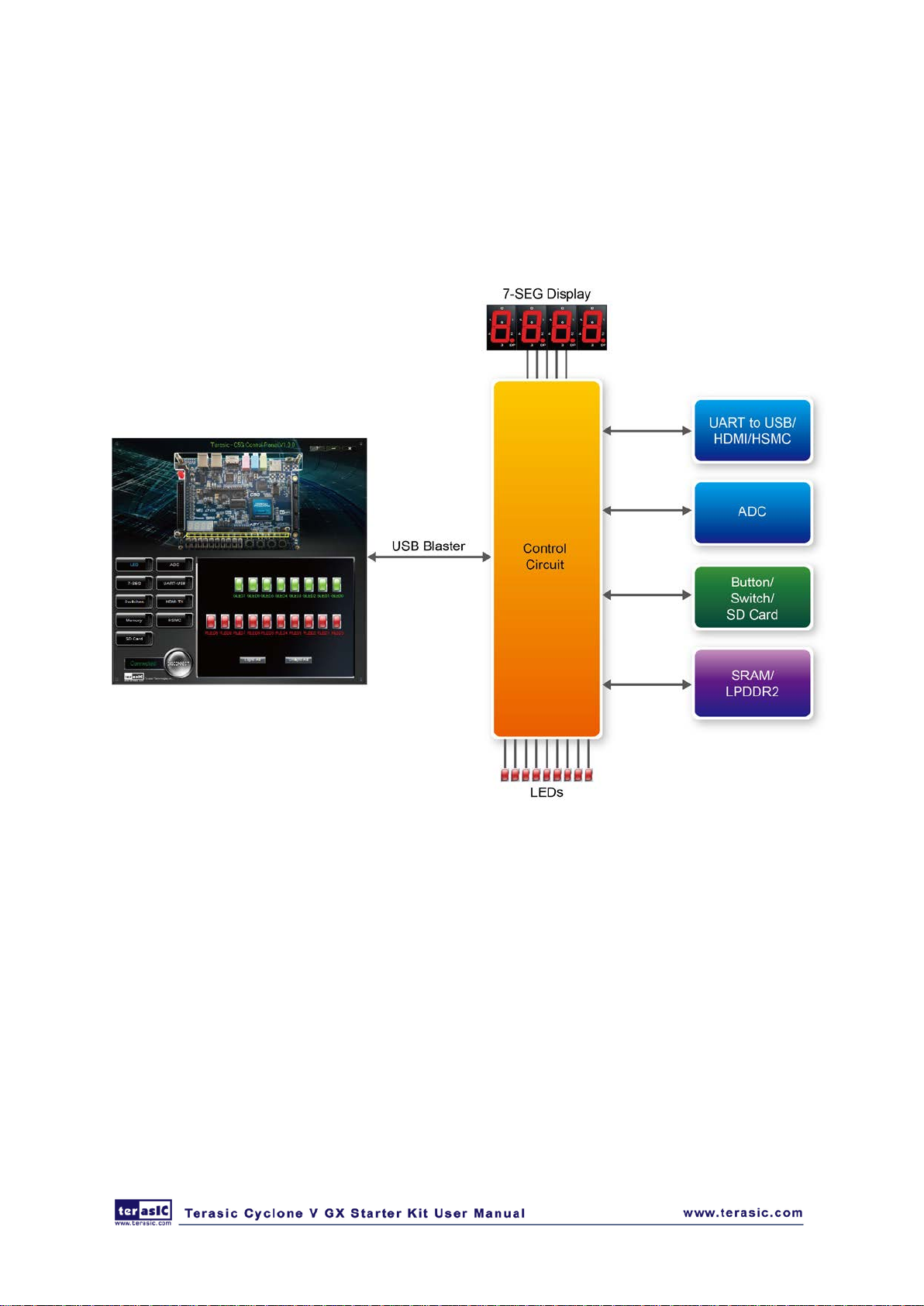

The concept of the C5G Control Panel is illustrated in Figure 2-2. The “Control Circuit” that

performs the control functions is implemented in the FPGA board. It communicates with the

Control Panel window, which is active on the host computer, via the USB Blaster link. The

graphical interfac e is used to send commands to the control circuit. It handles all the requests and

performs data transfers between the computer and the Cyclone V Starter Kit board.

Figure 2-2 The C5G Control Panel concept

The C5G Control Panel can be used to light up LEDs, change the values displayed on 7-segment,

monitor buttons/switches status, read/write the SRAM and LPDDR2 Memory, output HDMI-TX

color pattern to VGA monitor, verify functionality of HSMC connector I/Os, communicate with PC

via UART to USB interface, read SD Card specification information. The feature of reading/writing

a word or an entire file from/to the Memory allows the user to develop multimedia applications

(Flash Audio Player, Flash Picture Viewer) without worrying about how to build a Memory

Programmer.

11

Page 13

22..22

CCoonnttrroolllliinngg tthhee LLEEDDss,, 77--sseeggmmeenntt DDiissppllaayys

A simple function of the Control Panel is to allow setting the values displayed on LEDs, 7-segment

displays.

Choosing the LED tab leads to the window in Figu re 2-3. Here, you can directly turn the LE Ds on

or off individually or by clicking “Light All” or “Unlight All”.

s

Figure 2-3 Controlling LEDs

12

Page 14

Choosing the 7-SEG t ab leads to the window shown in Fi gure 2-4. From the window, directly use

the left-ri ght arrows to control the 7-SEG patterns on the Cyclone V GX Starter board which are

updated immediately. Note that the dots of the 7-SEGs are not enabled on Cyclone V GX Starter

Board.

Figure 2-4 Controlling 7-SEG display

The ability to set arbitrary values into simple display devices is not needed in typical design

activities. However, it gives users a simple mechanism for verifying that these devices are

functioning correctly in case a malfunction is suspected. Thus, it can be used for troubleshooting

purposes.

13

Page 15

22..33

SSwwiittcchheess aanndd PPuusshh--bbuuttttoonns

Choosing the Switches tab leads to the window in Fig ure 2-5. The function is designed to monitor

the status of slide switches and push-buttons in real time and show the status in a graphical user

interface. It can be used to verify the functionality of the slide switches and push-buttons.

s

Figure 2-5 Monitoring switches and butto n s

The ability to check the status of push-button and slide switch is not needed in typical design

activities. However, it provides users a simple mechanism to verify if th e buttons and switches are

functioning correctly. Thus, it can be used for troubleshooting purposes.

14

Page 16

22..44

SSRRAAMM//LLPPDDDDRR22 CCoonnttrroolllleerr aanndd PPrrooggrraammmmeer

The Control Panel can be used to write/read data to/from the SRAM and LPDDR2 chips on the

Cyclone V GX Starter b oard. As an example, we will describe ho w the LPDDR2 may be accessed ;

the same approach is us ed to access t he SRAM. Cli ck on the Memor y tab and select “LPDDR2” t o

reach the window in Figure 2-6.

r

Figure 2-6 Access ing the LPDDR2

A 16-bit word can be written into the LPDDR2 by entering the address of the desired location,

specifying the data to be written, and pressing the Write button. Contents of the location can be read

by pressing the Read button. Fig ure 2 -6 depicts the result of writing the hexadecimal value 06CA

into offset address 200, followed by reading the same location.

The Sequential Write function of the Control Panel is used to write the contents of a file into the

LPDDR SDRAM as follows:

1. Specify the starting address in the Address box.

15

Page 17

2. Specify the number of bytes to be written in the Length box. If the entire file is to be loaded,

then a checkmark may be placed in the File Length box instead of giving the number of bytes.

3. To initiate the writing process, click on the Write a File to Memory button.

4. When the Control Panel responds with the standard Windows dialog box asking for the source

file, specify the desired file in the usual manner.

The Control Panel also supports loading files with a .hex extension. Files with a .hex extension are

ASCII text files that specify memory values using ASCII characters to represent hexadecimal

values. For example, a file containing the line

0123456789ABCDEF

defines eight 8-bit values: 01, 23, 45, 67, 89, AB, CD, EF. These values will be loaded

consecutively into the memory.

The Sequential Read function is used to read the contents of the LPDDR2 and fill them into a file as

follows:

1. Specify the starting address in the Address box.

2. Specify the number of bytes to be copied into the file in the Length box. If the entire contents

of the LPDDR2 are to be copied (which involves all 512 Mbytes), then place a checkmark in

the Entire Memory box.

3. Press Load Memory Content to a File button.

4. When the Control Panel responds with the standard Windows dialog box asking for the

destination file, specify the desired file in the usual manner.

Users can use the similar way to access the SRAM.

16

Page 18

22..55

SSDD CCaarrd

The function is designed to read the identification and specification information of the SD Card.

The 4-bit SD MODE is used to access the SD Card. This function can be used to verify the

functionality of the SD Card Interface. Fo llow the steps below to perform the SD Card exercise:

1. Choosing the SD Card tab leads to the window in Figure 2-7.

2. Insert an SD Card to the Cyclone V GX Starter board, and then press the Read button to read

the SD Card. The SD Card’s identification, specification, and file format information will be

displayed in the control window.

d

Figure 2-7 Reading the SD Card Identifica tion and Specification

22..66

From the Control Panel, users are able to view the eight-channel 12-bit analog-to-digital converter

reading. The values shown are the ADC register outputs from all of the eight separate channels. The

C

AADDC

17

Page 19

voltage shown is the voltage reading from the separate pins on the extension header. Figure 2-8

shows the ADC readings when the ADC tab is chosen.

Figure 2-8 Reading of eight channel ADC

22..77

UUAARRTT--UUSSBB CCoommmmuunniiccaattiioon

The Control Panel allows users to verify the operation of the UART to USB serial communication

interface on the Cyclone V GX Starter Board. The setup is established by connecting a USB cable

from the PC to the USB port where the Control Panel communicates to the terminal emulator

software on the PC, or vice versa. The Receive terminal window on the Co ntrol Panel monitors the

serial communication status. Follow the steps below to initiate the UART communication:

1. Choosing the UART-USB tab leads to the window in Figure 2-9.

2. Plug in an USB cable from PC USB port to the USB to UART port on Cyclone V GX Starter

board.

3. The UART settings are provided below in case a connection from the PC is used:

n

18

Page 20

• Baud Rate: 115200

• Parity Check Bit: None

• Data Bits: 8

• Stop Bits: 1

• Flow Control (CTS/RTS): OFF

4. To begin the communication, enter specific letters followed by clicking Send. During the

communication process, observe the status of the Receive terminal window to verify its

operation.

Figure 2-9 UART to USB Serial Communication

22..88

HHDDMMII--TTX

C5G Control Panel provides video pattern function that allows users to output color pattern to

HDMI interfaced LCD monitor using the Cyclone V GX Starter board. Follow the steps below to

generate the video pattern function:

Note, do not install HSMC loopback board while using HDMI-TX function because the loopback

board will inference the I2C bus of HDMI.

Choosing the Video tab leads to the window in Figure 2-10.

X

19

Page 21

Plug a HDMI cable to HDMI connector of the Cyclone V GX Starter board and LCD monitor.

The LCD monitor will display the same color pattern on the control panel window.

Click the drop down menu shown in Figure 2-10 where you can output the selected color

individually.

Figure 2-10 Controlling VGA display

22..99

HHSSMMC

Select the HSMC tab to reach the window shown in Figure 2-11. This function is designed to verify

the functionality of the signals located on the HSMC connector. Before running the HSMC

loopback verification test, follow the instruction noted under the Loopback Installation section and

click on Verify. Please note to turn off the Cyclone V GX Starter board before the HSMC loopback

adapter is installed to prevent any damage to the board.

The HSMC loopback adapter is not provided in the kit package but can be purchased through the

website below: (http://hsmc_loopback.terasic.com)

C

20

Page 22

Figure 2-11 HSMC loopback verification test performed under Control Panel

22..1100

The C5G Control Panel is based on a Nios II Qsys system instantiated in the Cyclone V GX FPGA

with software running on the on-chip memory. The software part is implemented in C code; the

hardware part is implemented in Verilog HDL code with Qsys builder. The source code is not

available on the C5G System CD.

To run the Control Panel, users should make the configuration according to Section 3.1. Figure

2-12 depicts the structure of the Control Panel. Each input/output device is controlled by the Nios II

Processor instantiated in the FPGA chip. The communication with the PC is done via the USB

Blaster link. The Nios II interprets the commands sent from the PC and performs the corresponding

actions.

OOvveerraallll SSttrruuccttuurree ooff tthhee CC55GG CCoonnttrrooll PPaanneel

l

21

Page 23

Figure 2-12 The block diagram of the C5G control panel

22

Page 24

Chapter 3

Using the Starter Kit

In this chapter we introduce the important components on the Cyclone V GX Starter Kit.

33..11 CCoonnffiigguurraattiioonn,, SSttaattuuss aanndd SSeettuupp

The procedure of downloading a circuit from a host computer to the Cyclone V GX Starter Kit

board is described in the tutorial Quartus II Introduction. This tutorial can be found under the

\tutorials folder on the Cyclone V GX Starter Kit System CD. You are encouraged to read the

tutorial first, and treat the information below as a short reference.

The Cyclone V GX Starter Ki t board contains a serial configuration device that stores configuration

data for the Cyclone V GX FPGA. This configuration data is automatically loaded from the

configuration devi ce into th e FPGA when powered on. Using the Quartus II software, it is possible

to reconfigure the FPGA at any time, and it is also possible to change the non-volatile data that is

stored in the serial configuration device. Both types of programming methods are described below.

1. JTAG programming: In this method of programming, named after the IEEE standards Joint

Test Action Group, the configuration bit stream is downloaded directly into the Cyclone GX

FPGA. The FPGA will retain this configuration as long as power is applied to the board; the

configuration information will be lost when the power is turned off.

2. AS programming: In this method, called Active Serial programming, the configuration bit

stream is downloaded into the Altera EPCQ256 serial configuration device. It provides

non-volatile storage of the bit stream, so that the information is retained even when the power

supply to the Cyclone V GX Starter Kit board is turned off. When the board’s power is turned

on, the configuration data in the EPCQ256 device is automatically loaded into the Cyclone V

GX FPGA.

JTAG Chain on Cyclone V GX Starter Kit board

To use JTAG interface for configuring FPGA device, the JTAG chain on Cyclone V GX Starter Kit

must form a closed loop that allows Quartus II programmer to detect FPGA device. Figure 3-1

illustrates the JTAG chain on Cyclone V GX Starter Kit board. Shorting pin1 and pin2 on JP2 can

23

Page 25

disable the JTAG signals on HSMC connector that will form a closed JTAG loop chain on Cyclone

V GX Starter Kit board (See Figure 3 -2). Thus, only the on-board FPGA device (Cyclone V GX)

will be detected by the Quartus II programmer. If users want to include another FPGA device or

interface containing FPGA device in the chain via HSMC connector, remove JP2 Jumper (open pin1

and pin2 on JP2) to enable the JTAG signal ports on the HSMC connector.

Figure 3-1 The JTAG chain on Cyclone V GX Starter K it board

Figure 3-2 The JTAG chain configuration header

The sections below describe the steps to perform both JTAG and AS programming. For both

methods the Cyclone V GX Starter Kit board is connected to a host computer via a USB cable.

Using this connection, the board will be identified by the host computer as an Altera USB Blaster

device.

24

Page 26

Configuring the FPGA in JTAG Mode

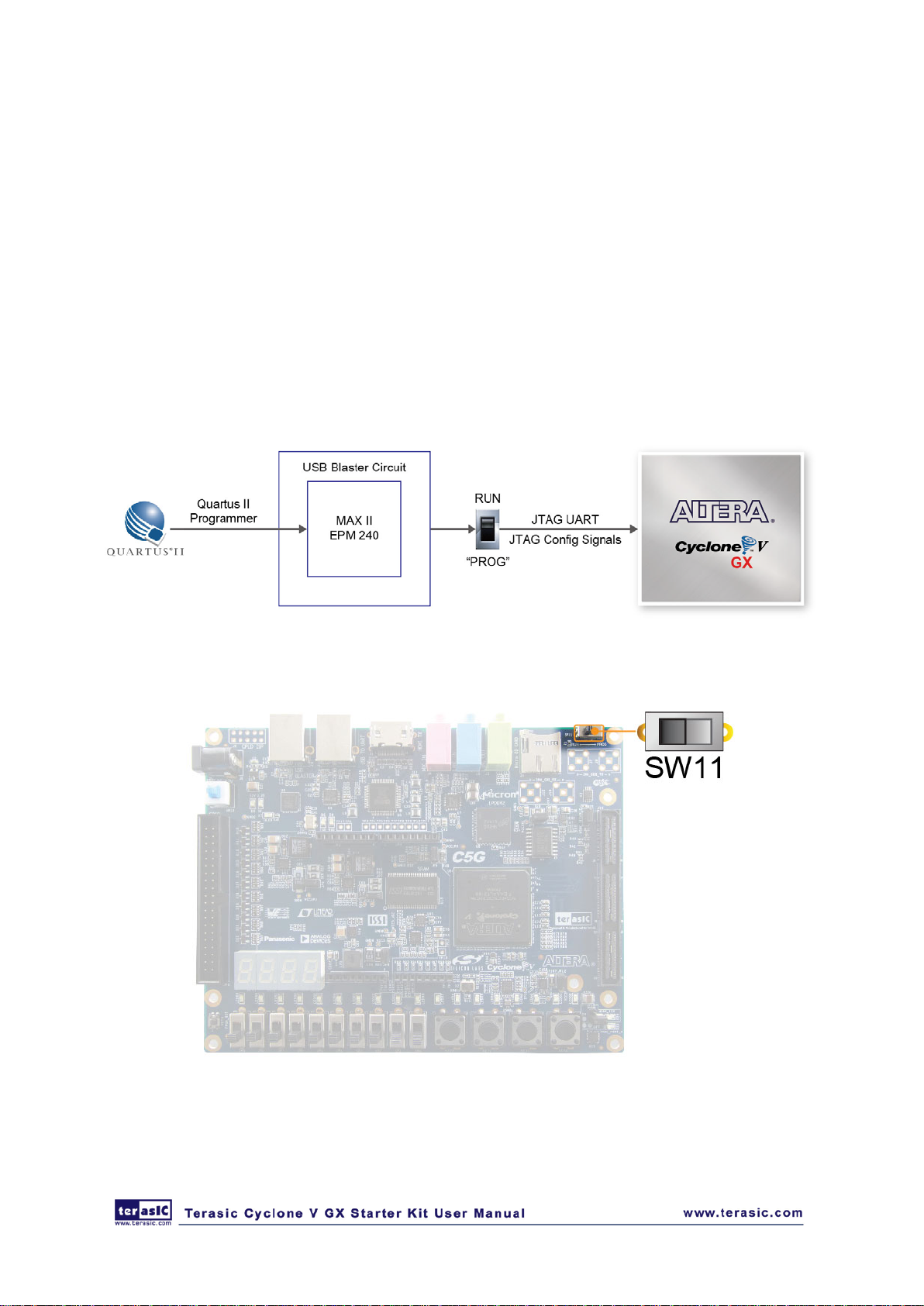

Fig ure 3-3 illustrates the JTAG configuration setup. To download a configuration bit stream into

the Cyclone V GX FPGA, you need to perform the following steps:

• Ensure that power is applied to the Cyclone V GX Starter Kit board

• Configure the JTAG programming circuit by setting the RUN/PROG slide switch (SW11) to the

RUN position (See Figure 3-4)

• Connect the supplied USB cable to the USB Blaster port on the Cyclone V GX Starter Kit board

(See Figure 1-2)

• The FPGA can now be programmed by using the Quartus II Programmer to select a

configuration bit stream file with the .sof filename extension

Figure 3-3 The JTAG configuration scheme

Figure 3-4 The RUN/PROG switch (SW11) is set in JTAG mode

25

Page 27

Board

Reference

LED Name

Description

D5 12

Illuminates when 12

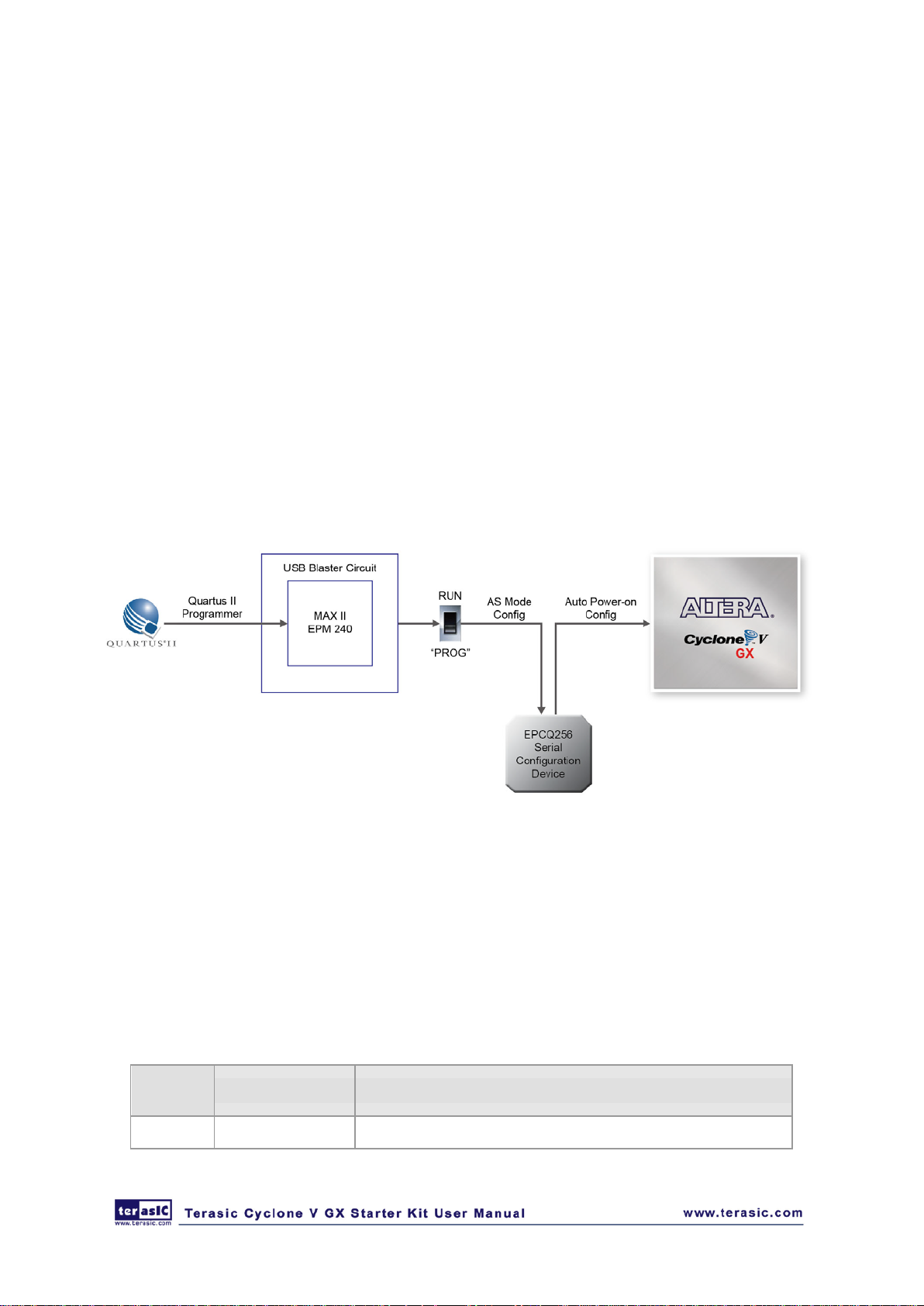

Configuring the EPCQ256 in AS Mode

Fig ure 3-5 illustrates the AS configuration setup. To download a configuration bit stream into the

EPCQ256 serial configuration device, you need to perform the following steps:

• Ensure that power is applied to the Cyclone V GX Starter Kit board.

• Connect the supplied USB cable to the USB Blaster port on the Cyclone V GX Starter Kit board

• Configure the JTAG programming circuit by setting the RUN/PROG slide switch (SW11) to the

PROG position.

• The EPCQ256 chip can now be programmed by using the Quartus II Programmer to select a

configuration bit stream file with the .pof filename extension.

• Once the programming operation is finished, set the RUN/PROG slide switch back to the RUN

position and then reset the board by turning the power switch off and back on; this action causes

the new configuration data in the EPCQ256 device to be loaded into the FPGA chip.

Figure 3-5 The AS configuration scheme

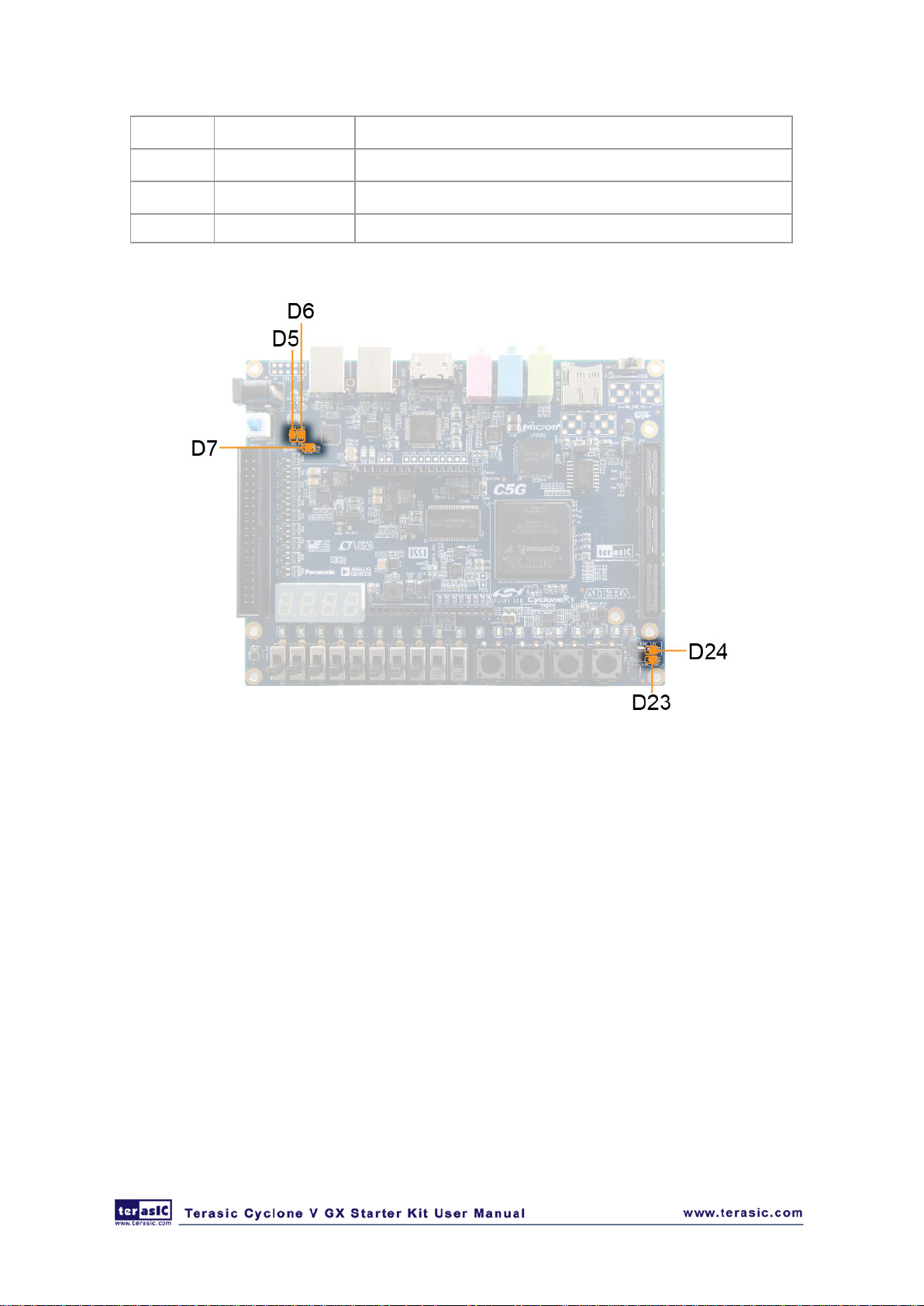

Status LED

• The FPGA development board includes board-specific status LEDs to indicate board status.

Please refer to Table 3-1 for the description of the LED indicator. Please refer to Figure 3-6 for

detailed LED location.

Table 3-1 Status LED

-V Power

-V power is active.

26

Page 28

D6 3.3

Illuminates when 3.3

D

HSMC_12

Illuminates when

D

HSMC_PSNT_n

Illuminates

D7 ULED

Illuminates when the

-V Power

-V power is active.

24

23

-V Power

HSMC 12-V power is active.

when HSMC Daughter Card is present

on-board USB-Blaster is working

Figure 3-6 Status L ED position

33..22 GGeenneerraall UUsseerr IInnppuutt//OOuuttppuutt

This section describes the user I/O interface to the FPGA.

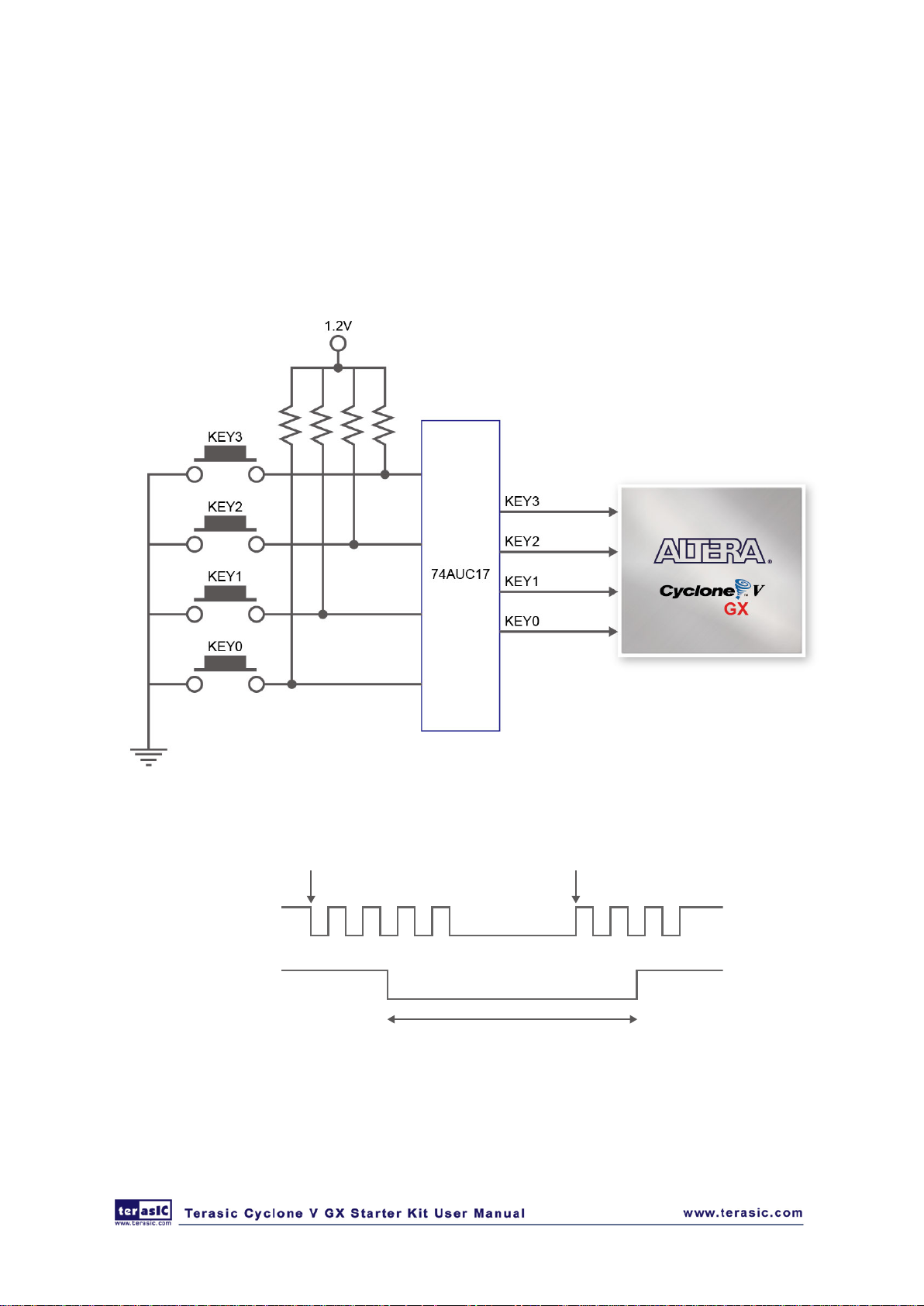

User Defined Push-buttons

The board includes four user defined push-buttons that allow users to interact with the Cyclone V

GX device as shown in Figu re 3-7. E ach of these switches is debounced using a Schmitt Trigger

circuit, as indicated in Fi gu re 3 -8. The four outputs called KEY0, KEY1, KEY2, and KEY3 of the

Schmitt Trigger devices are connected directly to the Cyclone V GX FPGA. Each push-button

switch provides a high logic level when it is not pressed, and provides a low logic level when

27

Page 29

Pushbutton releasedPushbutton depressed

Before

Debouncing

Schmitt Trigger

Debounced

depressed. Since the push-button switches are debounced, they are appropriate for using as clocks

or reset inputs in a circuit.

Ta b l e 3 -2 lists the board referenc es, signal names, and their corresponding Cyclone V GX device

pin numbers.

Figure 3-7 Connections between the push-button and Cyclone V GX FPGA

Figure 3-8 Switch debouncing

28

Page 30

Board

Reference

Schematic

Signal Name

Description

I/O

Standard

Cyclone

Pin Number

KEY0

KEY0

High Logic Level when

not

The four push buttons (KEY0,

KEY1, KEY2, and KEY3) go through the

1.2-V

PIN_P11

KEY1

KEY1

1.2-V

PIN_P12

KEY2

KEY2

1.2-V

PIN_Y15

KEN3

KEN3

1.2-V

PIN_Y16

High Logic Level when

not

pressed.

Table 3-2 Push-button Pin Assignments, Schematic Signal Names, and Functions

KEY4 CPU_RESET_n

pressed.

the button is

debounce circuit.

the button is

3.3-V PIN_AB24

V GX

User-Defined Slide Switch

There are ten slide switches connected to FPGA on the board (See Fig ure 3-9). These s witches ar e

not debounced, and are assumed for use as level-sensitive data inputs to a circuit. Each switch is

connected directly to a pin on the Cyclone V GX FPGA. When the switch is in the DOWN position

(closest to the edge of the board), it provides a low logic level to the FPGA, and when the switch is

in the UP position it provides a high logic level.

Table 3-3 lists the signal names and their corresponding Cyclone V GX device pin numbers.

Figure 3-9 Connections between the slide switches and Cyclone V GX FPGA

29

Page 31

Reference

Signal Name

Standard

Cyclone

Pin Number

SW0

SW0

Slide Switch[0]

1.2-V

PIN_AC9

SW1

SW1

Slide Switch[1]

1.2-V

PIN_AE10

SW2

SW2

Slide Switch[2]

1.2-V

PIN_AD13

SW3

SW3

Slide Switch[3]

1.2-V

PIN_AC8

SW4

SW4

Slide Switch[4]

1.2-V

PIN_W11

SW5

SW5

Slide Switch[5]

1.2-V

PIN_AB10

SW6

SW6

Slide Switch[6]

1.2-V

PIN_V10

SW7

SW7

Slide Switch[7]

1.2-V

PIN_AC10

SW8

SW8

Slide Switch[8]

1.2-V

PIN_Y11

SW9

SW9

Slide Switch[9]

1.2-V

PIN_AE19

Table 3-3 Slide Switch Pin Assignments, Schematic Signal Names, and Functions

Board

Schematic

Description

I/O

V GX

User-Defined LEDs

There are also ei ghte en user-controllable LEDs co nnected t o FP GA on the board. Ten red LEDs are

situated above the ten slide switches, and eight green LEDs are found above the push-button

switches. Each LED is driven directly by a pin on the Cyclone V GX FPGA; driving its associated

pin to a high logic level turns the LED on, and dri ving the pin low turns it off. Fi gu re 3 -10 shows

the connections between LEDs and Cyclone V GX FPGA.

Figure 3-10 Connections between the LEDs and Cyclone V GX FPGA

Table 3-4 lists the signal names and their corresponding Cyclone V GX device pin numbers.

30

Page 32

Reference

Signal Name

Standard

V GX

Pin Number

LEDR0

LEDR0

2.5-V

PIN_F7

LEDR1

LEDR1

2.5-V

PIN_F6

LEDR2

LEDR2

2.5-V

PIN_G6

LEDR3

LEDR3

2.5-V

PIN_G7

LEDR4

LEDR4

2.5-V

PIN_J8

LEDR5

LEDR5

2.5-V

PIN_J7

LEDR6

LEDR6

2.5-V

PIN_K10

LEDR7

LEDR7

2.5-V

PIN_K8

LEDR8

LEDR8

2.5-V

PIN_H7

LEDR9

LEDR9

2.5-V

PIN_J10

LEDG0

LEDG0

2.5-V

PIN_L7

LEDG1

LEDG1

2.5-V

PIN_K6

LEDG2

LEDG2

2.5-V

PIN_D8

LEDG3

LEDG3

2.5-V

PIN_E9

LEDG4

LEDG4

2.5-V

PIN_A5

LEDG5

LEDG5

2.5-V

PIN_B6

LEDG6

LEDG6

2.5-V

PIN_H8

LEDG7

LEDG7

2.5-V

PIN_H9

Table 3-4 User LEDs Pin Assignments, Schematic Signal Names, and Functions

Board

Schematic

Description

Driving a logic 1 on the I/O port turns the LED

ON.

Driving a logic 0 on the I/O port turns the LED

OFF.

I/O

Cyclone

User-Defined 7-Segment Displays

The FPGA board has four 7-segment displays. As indicated in the schematic in Fig ure 3-11, the

seven segments (common anode) are connected to pins on Cyclone V GX FPGA. Applying a low

logic level to a segment will light it up and applying a high logic level turns it off.

Please note that two 7-segment displays, HEX2 and HEX3, share bus with the GPIO. When using

HEX2 and HEX3, you need to switch the Dip Switch S1/S2 which is located on the back of the

board to the "ON" position before FPGA can control corresponding 7-segment displays.

Each segment in a display is identified by an index listed from 0 to 6 with the positions given in

Figure 3-12. In addition, the decimal has no function at all. Table 3-5 shows the mapping of the

FPGA pin assignments to the 7-segment displays.

31

Page 33

Name

Cyclone V GX

Seven Segment Digit 0[0]

PIN_V19

Figure 3-11 Connection between 7-segment displays and Cyclone V GX FPGA

Table 3-5 User 7-segment display Pin Assignments, Schematic Signal Names, and Functions

Figure 3-12 Connections between the 7-segment display HEX0 and Cyclone V GX FPGA

Board

Reference

HEX0 HEX0_D0

Schematic

Signal

Description

32

I/O

Standard

2.5-V

Pin Number

Page 34

Seven Segment Digit 0[1]

PIN_V18

HEX0

HEX0_D2

Seven Segment Digit 0[2]

2.5-V

PIN_V17

Seven Segment Digit 0[3]

PIN_W18

Seven Segment Digit 0[4]

PIN_Y20

Seven Segment Digit 0[5]

PIN_Y19

Seven Segment Digit 0[6]

PIN_Y18

HEX1

HEX0_D0

Seven Segment Digit 1[0]

2.5-V

PIN_AA18

Seven Segment Digit 1[1]

PIN_AD26

HEX1

HEX0_D2

Seven Segment Digit 1[2]

2.5-V

PIN_AB19

Seven Segment Digit 1[3]

PIN_AE26

Seven Segment Digit 1[4]

PIN_AE25

HEX1

HEX0_D5

Seven Segment Digit 1[5]

2.5-V

PIN_AC19

Seven Segment Digit 1[6]

PIN_AF24

Seven Segment Digit 2[0], Share GPIO22

PIN_AD7

Seven Segment Digit 2[1] , Share GPIO23

PIN_AD6

Seven Segment Digit 2[2] , Share GPIO24

PIN_U20

HEX2

HEX0_D3

Seven Segment Digit 2[3] , Share GPIO25

3.3-V

PIN_V22

Seven Segment Digit 2[4] , Share GPIO26

PIN_V20

Seven Segment Digit 2[5] , Share GPIO27

PIN_W21

Seven Segment Digit 2[6] , Share GPIO28

PIN_W20

Seven Segment Digit 3[0] , Share GPIO29

PIN_Y24

HEX3

HEX0_D1

Seven Segment Digit 3[1] , Share GPIO30

3.3-V

PIN_Y23

Seven Segment Digit 3[2] , Share GPIO31

PIN_AA23

HEX3

HEX0_D3

Seven Segment Digit 3[3] , Share GPIO32

3.3-V

PIN_AA22

Seven Segment Digit 3[4] , Share GPIO33

PIN_AC24

Seven Segment Digit 3[5] , Share GPIO34

PIN_AC23

HEX3

HEX0_D6

Seven Segment Digit 3[6] , Share GPIO35

3.3-V

PIN_AC22

HEX0 HEX0_D1

2.5-V

HEX0 HEX0_D3

HEX0 HEX0_D4

HEX0 HEX0_D5

HEX0 HEX0_D6

HEX1 HEX0_D1

HEX1 HEX0_D3

HEX1 HEX0_D4

HEX1 HEX0_D6

HEX2 HEX0_D0

HEX2 HEX0_D1

HEX2 HEX0_D2

HEX2 HEX0_D4

HEX2 HEX0_D5

HEX2 HEX0_D6

HEX3 HEX0_D0

2.5-V

2.5-V

2.5-V

2.5-V

2.5-V

2.5-V

2.5-V

2.5-V

3.3-V

3.3-V

3.3-V

3.3-V

3.3-V

3.3-V

3.3-V

HEX3 HEX0_D2

HEX3 HEX0_D4

HEX3 HEX0_D5

3.3-V

3.3-V

3.3-V

33..33 CClloocckk CCiirrccuuiitt

The development board includes one 50MHz and one programmable Clock Generator. Figure 3-13 shows the

default frequencies of on-board external clocks going to the Cyclone V GX FPGA.

33

Page 35

Signal Name

Frequency

Pin Number

X2

CLOCK_50_B3B

50.0 MHz

1.2-V

PIN_T13

U20

CLOCK_125_p

125.0 MHz

LVDS

PIN_U12

U20

CLOCK_125_n

125.0 MHz

LVDS

PIN_V12

CLOCK_50_B5B

50.0 MHz

3.3-V

PIN_R20

CLOCK_50_B6A

50.0 MHz

3.3-V

PIN_N20

U20

CLOCK_50_B7A

50.0 MHz

2.5-V

PIN_H12

U20

CLOCK_50_B3A

50.0 MHz

2.5-V

PIN_M10

U20

REFCLK_p0

125.0 MHz

1.5-V PCML

PIN_V6

U20

REFCLK_n0

125.0 MHz

1.5-V PCML

PIN_W6

U20

REFCLK_p1

156.25 MHz

1.5-V PCML

PIN_N7

U20

REFCLK_n1

156.25 MHz

1.5-V PCML

PIN_P6

Figure 3-13 Clock circuit of the FPGA Board

The programming Clock Generator is a highly flexible and configurable clock generator/buffer. The

is to provide special and high quality clock signals for high-speed transceiver s. The clock gene rator

is controlled by the FPGA through the I2C serial interface. The user can modify the frequency

between 0.16 MHz to 200 MHz.

Table 3-6 lists the clock source, signal names, default frequency and their corresponding Cyclone V

GX device pin numbers. Ta ble 3-7 lists the programmable Clock Generator control pins, signal

names, I/O standard and their corresponding Cyclone V GX device pin numbers.

Table 3-6 Clock Source, Signal Name, Default Frequency, Pin Assignments and Functions

Source

Schematic

X2

Default

I/O Standard

Cyclone V GX

Application

34

Page 36

Oscillator

Signal Name

Pin Number

Signal Name

Stratix V GX Pin

Number

UART_TX

Transmit Asynchronous Data Output

PIN_L9

UART_RX

Receiving Asynchronous Data Input

PIN_M9

Table 3-7 Programmable oscillator control pin, Signal Name, I/O standard, Pin Assignme nts

and Descriptions

Programmable

U20 (Si5338)

Schematic

I/O Standard

I2C_SCL 2.5-V PIN_B7

I2C_SDA 2.5-V PIN_G11

Cyclone V GX

Description

I2C bus, direct

connected with Si5338

33..44 RRSS--223322 SSeerriiaall PPoorrtt ttoo UUSSBB iinntteerrffaaccee

The RS-232 is designed to perform communication between board and PC, allowing a transmission

speed of up to 3Mbps. This interface wouldn’t support HW flow control signals. The physical

interface is done using UART-US B on-board bridge from a FT232R chip and connects to the host

using a USB Type-B connector. For detailed information on how to use the transceiver, please refer

to the datasheet, which is available on the manufacturer ’s website, or under the Datasheets\FT232

folder on the Kit System CD. Figure 3-14 shows the related schematics, and Ta bl e 3-8 lists the

RS-232 pin assignments, signal names and functions. Table 3-9 lists the RS-232 status LEDs.

Figure 3-14 Connections between the Cyclone V GX FPGA and FT232R Chip

Table 3-8 RS-232 Pin Assignments, Schematic Signal Names, and Functions

Schematic

Description I/O Standard

2.5-V

35

Page 37

Board Reference

LED Name

Description

Signal Name

Pin Number

SRAM_A0

Address bus

3.3-V

PIN_B25

SRAM_A1

Address bus

3.3-V

PIN_B26

SRAM_A2

Address bus

3.3-V

PIN_H19

SRAM_A3

Address bus

3.3-V

PIN_H20

SRAM_A4

Address bus

3.3-V

PIN_D25

Table 3-9 RS-232 Status LED

D8 TX LED Illuminates when RS-232 transmit is active.

D9 RX LED Illuminates when RS-232 receiving is active.

33..55 SSRRAAMM :: SSttaattiicc RRaannddoomm AAcccceessss MMeemmoorryy

The IS61LV25616AL SRAM (Static Random Access Memory) device is featured on the

development board. For detailed information on how to use the SRAM, please refer to th e dat ash e et,

which is available o n the manuf acturer ’s website, or under the Datasheets\SRAM folder on the Kit

System CD. Figure 3-15 shows the related schematics and Table 3-10 lists the SRAM pin

assignments, signal names relative to the Cyclone V GX device.

Figure 3-15 Connections between the Cyclone V GX FPGA and SRAM Chip

Table 3-10 SRAM Pin Assignments, Schematic Signal Names, and Functions

Schematic

Description I/O Standard

36

Cyclone V GX

Page 38

SRAM_A5

Address bus

3.3-V

PIN_C25

SRAM_A6

Address bus

3.3-V

PIN_J20

SRAM_A7

Address bus

3.3-V

PIN_J21

SRAM_A8

Address bus

3.3-V

PIN_D22

SRAM_A9

Address bus

3.3-V

PIN_E23

SRAM_A10

Address bus

3.3-V

PIN_G20

SRAM_A11

Address bus

3.3-V

PIN_F21

SRAM_A12

Address bus

3.3-V

PIN_E21

SRAM_A13

Address bus

3.3-V

PIN_F22

SRAM_A14

Address bus

3.3-V

PIN_J25

SRAM_A15

Address bus

3.3-V

PIN_J26

SRAM_A16

Address bus

3.3-V

PIN_N24

SRAM_A17

Address bus

3.3-V

PIN_M24

SRAM_D0

Data bus

3.3-V

PIN_E24

SRAM_D1

Data bus

3.3-V

PIN_E25

SRAM_D2

Data bus

3.3-V

PIN_K24

SRAM_D3

Data bus

3.3-V

PIN_K23

SRAM_D4

Data bus

3.3-V

PIN_F24

SRAM_D5

Data bus

3.3-V

PIN_G24

SRAM_D6

Data bus

3.3-V

PIN_L23

SRAM_D7

Data bus

3.3-V

PIN_L24

SRAM_D8

Data bus

3.3-V

PIN_H23

SRAM_D9

Data bus

3.3-V

PIN_H24

SRAM_D10

Data bus

3.3-V

PIN_H22

SRAM_D11

Data bus

3.3-V

PIN_J23

SRAM_D12

Data bus

3.3-V

PIN_F23

SRAM_D13

Data bus

3.3-V

PIN_G22

SRAM_D14

Data bus

3.3-V

PIN_L22

SRAM_D15

Data bus

3.3-V

PIN_K21

SRAM_CE_n

Chip Enable, active Low

3.3-V

PIN_N23

SRAM_OE_n

Output Enable, active Low

3.3-V

PIN_M22

SRAM_WE_n

Write Enable, active Low

3.3-V

PIN_G25

SRAM_LB_n

Lower-Byte Control, D0~D7, active Low

3.3-V

PIN_H25

SRAM_UB_n

Upper-Byte Control, D8~D15, active Low

3.3-V

PIN_M25

33..66 LLPPDDDDRR22 MMeemmoorryy

The development board has one 4Gb Mobile Low-Power DDR2 SDRAM (LPDDR2) which is a high-speed

CMOS, dynamic random-access memory containing 4,294,967,296-bits shown in

For detailed information on how to use the LPDDR2, please refer to the datasheet, which is

Figure 3-16.

37

Page 39

Signal Name

Pin Number

DDR2LP_CA0

Command/address bus

1.2-V HSUL

PIN_AE6

DDR2LP_CA1

Command/address bus

1.2-V HSUL

PIN_AF6

DDR2LP_CA2

Command/address bus

1.2-V HSUL

PIN_AF7

DDR2LP_CA3

Command/address bus

1.2-V HSUL

PIN_AF8

DDR2LP_CA4

Command/address bus

1.2-V HSUL

PIN_U10

available on the manufacturer’s website, or under the Datasheets\LPDDR2 folder on the Kit System

CD. Fig ure 3 -17 shows the rel ated schematics and Ta b l e 3 -11 lists the LPDDR2 pin assignments,

signal names, and functions.

Figure 3-16 Connections between the Cyclone V GX FPGA and LPDDR2 Chip

Table 3-11 LPDDR2 Memory Pin Assignments, Schematic Signal Names, and Functions

Schematic

Figure 3-17 LPDDR2 and Cyclone V GX FPGA

Cyclone V GX

Description I/O Standard

38

Page 40

DDR2LP_CA5

Command/address bus

1.2-V HSUL

PIN_U11

DDR2LP_CA6

Command/address bus

1.2-V HSUL

PIN_AE9

DDR2LP_CA7

Command/address bus

1.2-V HSUL

PIN_AF9

DDR2LP_CA8

Command/address bus

1.2-V HSUL

PIN_AB12

DDR2LP_CA9

Command/address bus

1.2-V HSUL

PIN_AB11

DDR2LP_DQ0

Data bus

1.2-V HSUL

PIN_AA14

DDR2LP_DQ1

Data bus

1.2-V HSUL

PIN_Y14

DDR2LP_DQ2

Data bus

1.2-V HSUL

PIN_AD11

DDR2LP_DQ3

Data bus

1.2-V HSUL

PIN_AD12

DDR2LP_DQ4

Data bus

1.2-V HSUL

PIN_Y13

DDR2LP_DQ5

Data bus

1.2-V HSUL

PIN_W12

DDR2LP_DQ6

Data bus

1.2-V HSUL

PIN_AD10

DDR2LP_DQ7

Data bus

1.2-V HSUL

PIN_AF12

DDR2LP_DQ8

Data bus

1.2-V HSUL

PIN_AC15

DDR2LP_DQ9

Data bus

1.2-V HSUL

PIN_AB15

DDR2LP_DQ10

Data bus

1.2-V HSUL

PIN_AC14

DDR2LP_DQ11

Data bus

1.2-V HSUL

PIN_AF13

DDR2LP_DQ12

Data bus

1.2-V HSUL

PIN_AB16

DDR2LP_DQ13

Data bus

1.2-V HSUL

PIN_AA16

DDR2LP_DQ14

Data bus

1.2-V HSUL

PIN_AE14

DDR2LP_DQ15

Data bus

1.2-V HSUL

PIN_AF18

DDR2LP_DQ16

Data bus

1.2-V HSUL

PIN_AD16

DDR2LP_DQ17

Data bus

1.2-V HSUL

PIN_AD17

DDR2LP_DQ18

Data bus

1.2-V HSUL

PIN_AC18

DDR2LP_DQ19

Data bus

1.2-V HSUL

PIN_AF19

DDR2LP_DQ20

Data bus

1.2-V HSUL

PIN_AC17

DDR2LP_DQ21

Data bus

1.2-V HSUL

PIN_AB17

DDR2LP_DQ22

Data bus

1.2-V HSUL

PIN_AF21

DDR2LP_DQ23

Data bus

1.2-V HSUL

PIN_AE21

DDR2LP_DQ24

Data bus

1.2-V HSUL

PIN_AE15

DDR2LP_DQ25

Data bus

1.2-V HSUL

PIN_AE16

DDR2LP_DQ26

Data bus

1.2-V HSUL

PIN_AC20

DDR2LP_DQ27

Data bus

1.2-V HSUL

PIN_AD21

DDR2LP_DQ28

Data bus

1.2-V HSUL

PIN_AF16

DDR2LP_DQ29

Data bus

1.2-V HSUL

PIN_AF17

DDR2LP_DQ30

Data bus

1.2-V HSUL

PIN_AD23

DDR2LP_DQ31

Data bus

1.2-V HSUL

PIN_AF23

DDR2LP_DQS_p0

Data Strobe positive

Differential 1.2-V HSUL

PIN_V13

DDR2LP_DQS_p1

Data Strobe positive

Differential 1.2-V HSUL

PIN_U14

DDR2LP_DQS_p2

Data Strobe positive

Differential 1.2-V HSUL

PIN_V15

DDR2LP_DQS_p3

Data Strobe positive

Differential 1.2-V HSUL

PIN_W16

DDR2LP_DQS_n0

Data Strobe negative

Differential 1.2-V HSUL

PIN_W13

DDR2LP_DQS_n1

Data Strobe negative

Differential 1.2-V HSUL

PIN_V14

DDR2LP_DQS_n2

Data Strobe negative

Differential 1.2-V HSUL

PIN_W15

DDR2LP_DQS_n3

Data Strobe negative

Differential 1.2-V HSUL

PIN_W17

39

Page 41

DDR2LP_DM0

Data Write Mask (byte enables)

1.2-V HSUL

PIN_AF11

DDR2LP_DM1

Data Write Mask (byte enables)

1.2-V HSUL

PIN_AE18

DDR2LP_DM2

Data Write Mask (byte enables)

1.2-V HSUL

PIN_AE20

DDR2LP_DM3

Data Write Mask (byte enables)

1.2-V HSUL

PIN_AE24

DDR2LP_CK_p

Differential Output Clock (positive)

Differential 1.2-V HSUL

PIN_N10

DDR2LP_CK_n

Differential Output Clock (negative)

Differential 1.2-V HSUL

PIN_P10

DDR2LP_CKE0

Clock Enable 0

1.2-V HSUL

PIN_AF14

DDR2LP_CKE1

Clock Enable 1 (Not use)

1.2-V HSUL

PIN_AE13

DDR2LP_CS_n0

Chip Select 0

1.2-V HSUL

PIN_R11

DDR2LP_CS_n1

Chip Select 1 (Not use)

1.2-V HSUL

PIN_T11

External resistance (240Ω ±1%)

DDR2LP_OCT_RZQ

ZQ calibration.

1.2-V HSUL PIN_AE11

33..77 MMiiccrroo SSDD--CCaarrdd

The development board supports Micro SD card interface u sing x4 data lines. F igure 3-18 shows

the related signals connections between the SD Card and Cyclone V G X FPGA and Fig ure 3-19

shows micro SD card plug-in position.

Finally, Table 3-12 lists all the associated pins

Figure 3-18 Connection between the SD Card Socket and Cyclone V GX FPGA

40

Page 42

Signal Name

Pin Number

SD_CLK

Serial Clock

3.3-V

PIN_AB6

SD_CMD

Command, Response

3.3-V

PIN_W8

SD_DAT0

Serial Data 0

3.3-V

PIN_U7

SD_DAT1

Serial Data 1

3.3-V

PIN_T7

SD_DAT2

Serial Data 2

3.3-V

PIN_V8

SD_DAT3

Serial Data 3

3.3-V

PIN_T8

Figure 3-19 Micro SD Card

Table 3-12 SD Card Pin Assignments, Schematic Signal Names, and Functions

Schematic

Description I/O Standard

41

Cyclone V GX

Page 43

Signal Name

Pin Number

HDMI_TX_D0

Video Data bus

3.3-V

PIN_V23

HDMI_TX_D1

Video Data bus

3.3-V

PIN_AA26

HDMI_TX_D2

Video Data bus

3.3-V

PIN_W25

HDMI_TX_D3

Video Data bus

3.3-V

PIN_W26

HDMI_TX_D4

Video Data bus

3.3-V

PIN_V24

HDMI_TX_D5

Video Data bus

3.3-V

PIN_V25

HDMI_TX_D6

Video Data bus

3.3-V

PIN_U24

HDMI_TX_D7

Video Data bus

3.3-V

PIN_T23

HDMI_TX_D8

Video Data bus

3.3-V

PIN_T24

HDMI_TX_D9

Video Data bus

3.3-V

PIN_T26

HDMI_TX_D10

Video Data bus

3.3-V

PIN_R23

HDMI_TX_D11

Video Data bus

3.3-V

PIN_R25

HDMI_TX_D12

Video Data bus

3.3-V

PIN_P22

HDMI_TX_D13

Video Data bus

3.3-V

PIN_P23

33..88 HHDDMMII TTXX IInntteerrffaaccee

The development board provides High Performance HDMI Transmitter via the Analog Devices

ADV7513 which incorporates HDMI v1.4 features, including 3D video support, and 165 MHz

supports all video formats up to 1080p and UXGA. The ADV7513 is controlled via a serial I2C bus

interface, which is connected to pins on the Cyclone V GX FPGA. A schematic diagram of the

audio circuitry is shown in F ig ure 3 -20. Detailed information on using the ADV7513 HDMI TX is

available on the manu facturer’s website, or under the Datasheets\HDMI folder on the Kit System

CD.

Ta b le 3 -13 lists the HDMI Interface pin assignments and si gnal names relat ive to the Cyclone V

GX device.

Figure 3-20 Connections between the Cyclone V GX FPGA and HDMI Transmitter Chip

Table 3-13 HDMI Pin Assignments, Schematic Signal Names, and Functions

Schematic

Description I/O Standard

Cyclone V GX

42

Page 44

HDMI_TX_D14

Video Data bus

3.3-V

PIN_N25

HDMI_TX_D15

Video Data bus

3.3-V

PIN_P26

HDMI_TX_D16

Video Data bus

3.3-V

PIN_P21

HDMI_TX_D17

Video Data bus

3.3-V

PIN_R24

HDMI_TX_D18

Video Data bus

3.3-V

PIN_R26

HDMI_TX_D19

Video Data bus

3.3-V

PIN_AB26

HDMI_TX_D20

Video Data bus

3.3-V

PIN_AA24

HDMI_TX_D21

Video Data bus

3.3-V

PIN_AB25

HDMI_TX_D22

Video Data bus

3.3-V

PIN_AC25

HDMI_TX_D23

Video Data bus

3.3-V

PIN_AD25

HDMI_TX_CLK

Video Clock

3.3-V

PIN_AJ28

HDMI_TX_DE

Data Enable Signal for Digital Video.

3.3-V

PIN_Y26

HDMI_TX_HS

Vertical Synchronization

3.3-V

PIN_U26

HDMI_TX_VS

Horizontal Synchronization

3.3-V

PIN_U25

HDMI_TX_INT

Interrupt Signal

1.2-V

PIN_T12

I2C_SCL

I2C Clock

2.5-V

PIN_B7

I2C_SDA

I2C Data

2.5-V

PIN_G11

33..99 AAuuddiioo IInntteerrffaaccee

The board provides high-quality 24-bit audio via the Analog Devices SSM2603 audio CODEC

(Encoder/Decoder). This chip supports microphone-in, line-in, and line-out ports, with a sample rate

adjustable from 8 kHz to 96 kHz. The SSM2603 is controlled via a serial I2C bus interface, which

is connected to pins on the Cyclone V GX FPGA. A schematic diagram of the audio circuitry is

shown in Figure 3-21. Detailed information on using the SSM2603 codec is available in its

datasheet, which can be found on the manufacturer’s website, or under the Datasheets\Audio

CODEC folder on the Kit System CD

Ta b le 3 -14 lists the Audio Codec pin assignments and signal names relative to the Cyclone V GX

device.

43

Page 45

Signal Name

Pin Number

AUD_ADCLRCK

Audio CODEC ADC LR Clock

2.5-V

PIN_C7

AUD_ADCDAT

Audio CODEC ADC Data

2.5-V

PIN_D7

AUD_DACLRCK

Audio CODEC DAC LR Clock

2.5-V

PIN_G10

AUD_DACDAT

Audio CODEC DAC Data

2.5-V

PIN_H10

AUD_XCK

Audio CODEC Chip Clock

2.5-V

PIN_D6

AUD_BCLK

Audio CODEC Bit-Stream Clock

2.5-V

PIN_E6

I2C_SCL

I2C Clock

2.5-V

PIN_B7

I2C_SDA

I2C Data

2.5-V

PIN_G11

Figure 3-21 Connections between FPGA and Audio CODEC

Table 3-14 Audio CODEC Pin Assignments, Schematic Signal Names, and Functions

Schematic

Description I/O Standard

Cyclone V GX

33..1100 HHSSMMCC :: HHiigghh--SSppeeeedd MMeezzzzaanniinnee CCaarrdd

The FPGA development board contains one HSMC connector. The HSMC connector provides a

mechanism to extend the peripheral-set of an FPGA host board by means of add-on c ards, which

can address today’s high speed signaling requirement as well as low-speed device interf ace suppo rt.

The HSMC interfaces support JTAG, clock outputs and inputs, high-speed serial I/O (trans ceivers),

and single-ended or differential signaling.

The HSMC interfa ce co nn ected to the Cyclone V GX device is a female HSM C conn ector having a

total of 172pins, including 121 signal pins (120 signal pins +1 PSNTn pin) , 39 power pins, and 12

ground pins. The HSMC connector is based on the SAMTEC 0.5 mm pitch, surfac e-mount QSH

family of high-speed, board-to-board connectors. The Cyclone V GX device provides +12 V DC

and +3.3 V DC power to the mezzanine card through the HSMC connector. Table 3-15 indicates the

44

Page 46

Function

Jump Position

Jump Position (J13)

LED Indicator (D24)

maximum power consumption for the HSMC connector.

Note that the +12V DC power rail goes through a jumper (See Figu re 3-22). The function of the

jumper is to avoid cases when users no longer use the 12V power, and the power goes directly to

HSMC daughter boards and thus leads to burning the FPGA I/Os.

This jumper can be found bottom-right corner near the HSMC connector. The factory default setting

is "OFF", meaning the 12V power won't be available to the daughter boards. When users need to

connect the daughter boards, they need to switch the jumper to "ON" position. Please see Table

3-15 for setting details.

Figure 3-22 HSMC 12V Power Jump and Cyclone V GX FPGA (default OFF)

Table 3-15 HSMC 12V Power Jump Setting Indicators

HSMC 12V OFF J13.2 – TP1

HSMC 12V ON J13.1 – J13.2

45

Page 47

Supplied Voltage

Max. Current Limit

12V

1A

3.3V

1.5A

Signal Name

Pin Number

HSMC_CLKIN0

Dedicated clock input

2.5-V

PIN_N9

differential clock input

HSMC_CLKIN_n2

LVDS RX or CMOS I/O or

2.5-V or LVDS

PIN_K9

There are three banks in this connector. Fi gure 3 -23 shows t he bank arrangement of signals with

respect to the SAMTEC connector. Ta b l e 3 -16 lists the mapping of the FPGA pin assignments to

the HSMC connectors.

Figure 3-23 HSMC Signal Bank Diagram

Table 3-16 Power Supply of the HSMC

Table 3-17 Pin Assignments for HSMC connector

Schematic

Description I/O Standard

HSMC_CLKIN_n1 LVDS RX or CMOS I/O or

46

Cyclone V GX

2.5-V or LVDS

PIN_G14

Page 48

differential clock input

differential clock input

differential clock input

HSMC_CLKOUT0

Dedicated clock output

2.5-V

PIN_A7

differential clock input/output

differential clock input/output

differential clock input/output

differential clock input/output

HSMC_D0

LVDS TX or CMOS I/O

2.5-V

PIN_D11

HSMC_D1

LVDS RX or CMOS I/O

2.5-V

PIN_H14

HSMC_D2

LVDS TX or CMOS I/O

2.5-V

PIN_D12

HSMC_D3

LVDS RX or CMOS I/O

2.5-V

PIN_H13

I2C_SCL

I2C Clock

2.5-V

PIN_B7

I2C_SDA

I2C Data

2.5-V

PIN_G11

HSMC_GXB_RX_p0

Transceiver RX bit 0

1.5-V PCML

PIN_AD2

HSMC_GXB_RX_p1

Transceiver RX bit 1

1.5-V PCML

PIN_AB2

HSMC_GXB_RX_p2

Transceiver RX bit 2

1.5-V PCML

PIN_Y2

HSMC_GXB_RX_p3

Transceiver RX bit 3

1.5-V PCML

PIN_V2

HSMC_GXB_TX_p0

Transceiver TX bit 0

1.5-V PCML

PIN_AE4

HSMC_GXB_TX_p1

Transceiver TX bit 1

1.5-V PCML

PIN_AC4

HSMC_GXB_TX_p2

Transceiver TX bit 2

1.5-V PCML

PIN_AA4

HSMC_GXB_TX_p3

Transceiver TX bit 3

1.5-V PCML

PIN_W4

HSMC_GXB_RX_n0

Transceiver RX bit 0

1.5-V PCML

PIN_AD1

HSMC_GXB_RX_n1

Transceiver RX bit 1

1.5-V PCML

PIN_AB1

HSMC_GXB_RX_n2

Transceiver RX bit 2

1.5-V PCML

PIN_Y1

HSMC_GXB_RX_n3

Transceiver RX bit 3

1.5-V PCML

PIN_V1

HSMC_GXB_TX_n0

Transceiver TX bit 0

1.5-V PCML

PIN_AE3

HSMC_GXB_TX_n1

Transceiver TX bit 1

1.5-V PCML

PIN_AC3

HSMC_GXB_TX_n2

Transceiver TX bit 2

1.5-V PCML

PIN_AA3

HSMC_GXB_TX_n3

Transceiver TX bit 3

1.5-V PCML

PIN_W3

HSMC_RX _n0

LVDS RX bit 0n or CMOS I/O

LVDS or 2.5-V

PIN_M12

HSMC_RX _n1

LVDS RX bit 1n or CMOS I/O

LVDS or 2.5-V

PIN_L11

HSMC_RX _n2

LVDS RX bit 2n or CMOS I/O

LVDS or 2.5-V

PIN_H17

HSMC_RX _n3

LVDS RX bit 3n or CMOS I/O

LVDS or 2.5-V

PIN_K11

HSMC_RX _n4

LVDS RX bit 4n or CMOS I/O

LVDS or 2.5-V

PIN_J16

HSMC_RX _n5

LVDS RX bit 5n or CMOS I/O

LVDS or 2.5-V

PIN_J11

HSMC_RX _n6

LVDS RX bit 6n or CMOS I/O

LVDS or 2.5-V

PIN_G17

HSMC_RX _n7

LVDS RX bit 7n or CMOS I/O

LVDS or 2.5-V

PIN_F12

HSMC_RX _n8

LVDS RX bit 8n or CMOS I/O

LVDS or 2.5-V

PIN_F18

HSMC_CLKIN_p1 LVDS RX or CMOS I/O or

HSMC_CLKIN_p2 LVDS RX or CMOS I/O or

HSMC_CLKOUT_n1 LVDS TX or CMOS I/O or

HSMC_CLKOUT_n2 LVDS TX or CMOS I/O or

HSMC_CLKOUT_p1 LVDS TX or CMOS I/O or

HSMC_CLKOUT_p2 LVDS TX or CMOS I/O or

2.5-V or LVDS

2.5-V or LVDS

2.5-V or LVDS

2.5-V or LVDS

2.5-V or LVDS

2.5-V or LVDS

PIN_G15

PIN_L8

PIN_A18

PIN_A16

PIN_A19

PIN_A17

47

Page 49

HSMC_RX _n9

LVDS RX bit 9n or CMOS I/O

LVDS or 2.5-V

PIN_E15

HSMC_RX _n10

LVDS RX bit 10n or CMOS I/O

LVDS or 2.5-V

PIN_D13

HSMC_RX _n11

LVDS RX bit 11n or CMOS I/O

LVDS or 2.5-V

PIN_D15

HSMC_RX _n12

LVDS RX bit 12n or CMOS I/O

LVDS or 2.5-V

PIN_D16

HSMC_RX _n13

LVDS RX bit 13n or CMOS I/O

LVDS or 2.5-V

PIN_D17

HSMC_RX _n14

LVDS RX bit 14n or CMOS I/O

LVDS or 2.5-V

PIN_E19

HSMC_RX _n15

LVDS RX bit 15n or CMOS I/O

LVDS or 2.5-V

PIN_D20

HSMC_RX _n16

LVDS RX bit 16n or CMOS I/O

LVDS or 2.5-V

PIN_A24

HSMC_RX _p0

LVDS RX bit 0 or CMOS I/O

LVDS or 2.5-V

PIN_N12

HSMC_RX _p1

LVDS RX bit 1 or CMOS I/O

LVDS or 2.5-V

PIN_M11

HSMC_RX _p2

LVDS RX bit 2 or CMOS I/O

LVDS or 2.5-V

PIN_H18

HSMC_RX _p3

LVDS RX bit 3 or CMOS I/O

LVDS or 2.5-V

PIN_L12

HSMC_RX _p4

LVDS RX bit 4 or CMOS I/O

LVDS or 2.5-V

PIN_H15

HSMC_RX _p5

LVDS RX bit 5 or CMOS I/O

LVDS or 2.5-V

PIN_J12

HSMC_RX _p6

LVDS RX bit 6 or CMOS I/O

LVDS or 2.5-V

PIN_G16

HSMC_RX _p7

LVDS RX bit 7 or CMOS I/O

LVDS or 2.5-V

PIN_G12

HSMC_RX _p8

LVDS RX bit 8 or CMOS I/O

LVDS or 2.5-V

PIN_E18

HSMC_RX _p9

LVDS RX bit 9 or CMOS I/O

LVDS or 2.5-V

PIN_F16

HSMC_RX _p10

LVDS RX bit 10 or CMOS I/O

LVDS or 2.5-V

PIN_E13

HSMC_RX _p11

LVDS RX bit 11 or CMOS I/O

LVDS or 2.5-V

PIN_C14

HSMC_RX _p12

LVDS RX bit 12 or CMOS I/O

LVDS or 2.5-V

PIN_E16

HSMC_RX _p13

LVDS RX bit 13 or CMOS I/O

LVDS or 2.5-V

PIN_D18

HSMC_RX _p14

LVDS RX bit 14 or CMOS I/O

LVDS or 2.5-V

PIN_E20

HSMC_RX _p15

LVDS RX bit 15 or CMOS I/O

LVDS or 2.5-V

PIN_D21

HSMC_RX _p16

LVDS RX bit 16 or CMOS I/O

LVDS or 2.5-V

PIN_B24

HSMC_TX _n0

LVDS TX bit 0n or CMOS I/O

LVDS or 2.5-V

PIN_E11

HSMC_TX _n1

LVDS TX bit 1n or CMOS I/O

LVDS or 2.5-V

PIN_B9

HSMC_TX _n2

LVDS TX bit 2n or CMOS I/O

LVDS or 2.5-V

PIN_C10

HSMC_TX _n3

LVDS TX bit 3n or CMOS I/O

LVDS or 2.5-V

PIN_B11

HSMC_TX _n4

LVDS TX bit 4n or CMOS I/O

LVDS or 2.5-V

PIN_A11

HSMC_TX _n5

LVDS TX bit 5n or CMOS I/O

LVDS or 2.5-V

PIN_B19

HSMC_TX _n6

LVDS TX bit 6n or CMOS I/O

LVDS or 2.5-V

PIN_C15

HSMC_TX _n7

LVDS TX bit 7n or CMOS I/O

LVDS or 2.5-V

PIN_A21

HSMC_TX _n8

LVDS TX bit 8n or CMOS I/O

LVDS or 2.5-V

PIN_C12

HSMC_TX _n9

LVDS TX bit 9n or CMOS I/O

LVDS or 2.5-V

PIN_A9

HSMC_TX _n10

LVDS TX bit 10n or CMOS I/O

LVDS or 2.5-V

PIN_A13

HSMC_TX _n11

LVDS TX bit 11n or CMOS I/O

LVDS or 2.5-V

PIN_C22

HSMC_TX _n12

LVDS TX bit 12n or CMOS I/O

LVDS or 2.5-V

PIN_B14

HSMC_TX _n13

LVDS TX bit 13n or CMOS I/O

LVDS or 2.5-V

PIN_A22

HSMC_TX _n14

LVDS TX bit 14n or CMOS I/O

LVDS or 2.5-V

PIN_B17

HSMC_TX _n15

LVDS TX bit 15n or CMOS I/O

LVDS or 2.5-V

PIN_C18

HSMC_TX _n16

LVDS TX bit 16n or CMOS I/O

LVDS or 2.5-V

PIN_B20

HSMC_TX _p0

LVDS TX bit 0 or CMOS I/O

LVDS or 2.5-V

PIN_E10

HSMC_TX _p1

LVDS TX bit 1 or CMOS I/O

LVDS or 2.5-V

PIN_C9

HSMC_TX _p2

LVDS TX bit 2 or CMOS I/O

LVDS or 2.5-V

PIN_D10

48

Page 50

HSMC_TX _p3

LVDS TX bit 3 or CMOS I/O

LVDS or 2.5-V

PIN_A12

HSMC_TX _p4

LVDS TX bit 4 or CMOS I/O

LVDS or 2.5-V

PIN_B10

HSMC_TX _p5

LVDS TX bit 5 or CMOS I/O

LVDS or 2.5-V

PIN_C20

HSMC_TX _p6

LVDS TX bit 6 or CMOS I/O

LVDS or 2.5-V

PIN_B15

HSMC_TX _p7

LVDS TX bit 7 or CMOS I/O

LVDS or 2.5-V

PIN_B22

HSMC_TX _p8

LVDS TX bit 8 or CMOS I/O

LVDS or 2.5-V

PIN_C13

HSMC_TX _p9

LVDS TX bit 9 or CMOS I/O

LVDS or 2.5-V

PIN_A8

HSMC_TX _p10

LVDS TX bit 10 or CMOS I/O

LVDS or 2.5-V

PIN_B12

HSMC_TX _p11

LVDS TX bit 11 or CMOS I/O

LVDS or 2.5-V

PIN_C23

HSMC_TX _p12

LVDS TX bit 12 or CMOS I/O

LVDS or 2.5-V

PIN_A14

HSMC_TX _p13

LVDS TX bit 13 or CMOS I/O

LVDS or 2.5-V

PIN_A23

HSMC_TX _p14

LVDS TX bit 14 or CMOS I/O

LVDS or 2.5-V

PIN_C17

HSMC_TX _p15

LVDS TX bit 15 or CMOS I/O

LVDS or 2.5-V

PIN_C19

HSMC_TX _p16

LVDS TX bit 16 or CMOS I/O

LVDS or 2.5-V

PIN_B21

33..1111 UUssiinngg tthhee 22xx2200 GGPPIIOO EExxppaannssiioonn HHeeaaddeerr

The board provides one 40-pin expansion header (GPIO) and one Arduino Uno R2 expansion

header. These two kinds of expansion headers share parts of the IO. In addition, GPIO share I/O

with 7-Segment Display. Please refer to Figure 3-24. for detailed connections and block diagrams.

Figure 3-24 Connections between FPGA / GPIO / Arduino and 7-Segment display (share bus)

Now we introduce the 40-pin expansion header (GPIO) and Arduino Uno R2 expansion header.

40-pin Expansion Header

49

Page 51

Supplied Voltage

Max. Current Limit

5V

1A

3.3V

1.5A

The 40-pin head er connects directly to 36 pins of the Cyclone V GX FPGA, and also provides DC

+5V (VCC5), DC +3.3V (VCC3P3), and two GND pins. Figure 3-25 shows the I/O distribution of

the GPIO connector. The maximum power consumption of the daughter card that connects to GPIO

port is shown in Tab l e 3 -18. Ta bl e 3-19 shows all the pin assignments of the GPIO connector and

Share pin.

Figure 3-25 GPIO Pin Arrangeme nt

Table 3-18 Power Supply of the Expansion Header

50

Page 52

Signal Name

Signal Name

Pin Number

GPIO0

GPIO DATA[0] , Dedicated Clock Input

3.3-V

PIN_T21

GPIO1 GPIO DATA[1]

3.3-V

PIN_D26

GPIO2

GPIO DATA[2] , Dedicated Clock Input

3.3-V

PIN_K25

GPIO3

Arduino_IO0

GPIO DATA[3] , Arduino IO0

3.3-V

PIN_E26

GPIO4

Arduino_IO1

GPIO DATA[4] , Arduino IO1

3.3-V

PIN_K26

GPIO5

Arduino_IO2

GPIO DATA[5] , Arduino IO2

3.3-V

PIN_M26

GPIO6

Arduino_IO3

GPIO DATA[6] , Arduino IO3

3.3-V

PIN_M21

GPIO7

Arduino_IO4

GPIO DATA[7] , Arduino IO4

3.3-V

PIN_P20

GPIO8

Arduino_IO5

GPIO DATA[8] , Arduino IO5

3.3-V

PIN_T22

GPIO9

Arduino_IO6

GPIO DATA[9] , Arduino IO6

3.3-V

PIN_T19

GPIO10

Arduino_IO7

GPIO DATA[10] , Arduino IO7

3.3-V

PIN_U19

Each pin on the expansion headers is connected to two diodes and a resistor that provides protection

against high and low voltages. Fig ure 3-26 shows the protection circuitr y for only one of the pin on

the header, but this circuitry is applied for all 36 data pins.

Figure 3-26 Connections between the GPIO connector and Cyclone V GX FPGA

Table 3-19 Pin Assignments for 40-pin Expansion Header connector and share bus signal.

Schematic

Share Bus

Description I/O Standard

Cyclone V GX

51

Page 53

GPIO11

Arduino_IO8

GPIO DATA[11] , Arduino IO8

3.3-V

PIN_U22

GPIO12

Arduino_IO9

GPIO DATA[12] , Arduino IO9

3.3-V

PIN_P8

GPIO13

Arduino_IO10

GPIO DATA[13] , Arduino IO10

3.3-V

PIN_R8

GPIO14

Arduino_IO11

GPIO DATA[14] , Arduino IO11

3.3-V

PIN_R9

GPIO15

Arduino_IO12

GPIO DATA[15] , Arduino IO12

3.3-V

PIN_R10

PLL Clock output

GPIO17 GPIO DATA[17]

3.3-V

PIN_Y9

GPIO18

GPIO DATA[18] , PLL Clock output

3.3-V

PIN_G26

GPIO19 GPIO DATA[19]

3.3-V

PIN_Y8

GPIO20 GPIO DATA[20]

3.3-V

PIN_AA7

GPIO21 GPIO DATA[21]

3.3-V

PIN_AA6

GPIO22

HEX2_D0

GPIO DATA[22]

3.3-V

PIN_AD7

GPIO23

HEX2_D1

GPIO DATA[23]

3.3-V

PIN_AD6

GPIO24

HEX2_D2

GPIO DATA[24]

3.3-V

PIN_U20

GPIO25

HEX2_D3

GPIO DATA[25]

3.3-V

PIN_V22

GPIO26

HEX2_D4

GPIO DATA[26]

3.3-V

PIN_V20

GPIO27

HEX2_D5

GPIO DATA[27]

3.3-V

PIN_W21

GPIO28

HEX2_D6

GPIO DATA[28]

3.3-V

PIN_W20

GPIO29

HEX3_D0

GPIO DATA[29]

3.3-V

PIN_Y24

GPIO30

HEX3_D1

GPIO DATA[30]

3.3-V

PIN_Y23

GPIO31

HEX3_D2

GPIO DATA[31]

3.3-V

PIN_AA23

GPIO32

HEX3_D3

GPIO DATA[32]

3.3-V

PIN_AA22

GPIO33

HEX3_D4

GPIO DATA[33]

3.3-V

PIN_AC24

GPIO34

HEX3_D5

GPIO DATA[34]

3.3-V

PIN_AC23

GPIO35

HEX3_D6

GPIO DATA[35]

3.3-V

PIN_AC22

GPIO16 Arduino_IO13

GPIO DATA[16] , Arduino IO13,

3.3-V PIN_F26

Arduino Uno Expansion Header

The board provides Arduino Uno revision 2 compatibility expansion header which comes with four

independent headers. The headers connect serial resistor 47 ohm to 15 pins (14pins GPIO and 1pin

Reset) of the Cyclone V GX FPGA, 8-pins Analog input connects to ADC, and also provides DC

+12V (VCC12), DC +5V (VCC5), DC +3.3V (VCC3P3), and three GND pins.

Please refer to Figure 3-27. for detailed pin-out information. The red font in Fig ure 3 -28 represents

the signal name (shared bus) connected to FPGA.

52

Page 54

Signal Name

Pin Number

Arduino_IO0

Arduino IO0

3.3-V

PIN_E26

Arduino_IO1

Arduino IO1

3.3-V

PIN_K26

Arduino_IO2

Arduino IO2

3.3-V

PIN_M26

Arduino_IO3

Arduino IO3

3.3-V

PIN_M21

Arduino_IO4

Arduino IO4

3.3-V

PIN_P20

Arduino_IO5

Arduino IO5

3.3-V

PIN_T22

Arduino_IO6

Arduino IO6

3.3-V

PIN_T19

Arduino_IO7

Arduino IO7

3.3-V

PIN_U19

Arduino_IO8

Arduino IO8

3.3-V

PIN_U22

Arduino_IO9

Arduino IO9

3.3-V

PIN_P8

Arduino_IO10

Arduino IO10

3.3-V

PIN_R8

Arduino_IO11

Arduino IO11

3.3-V

PIN_R9

Arduino_IO12

Arduino IO12

3.3-V

PIN_R10

Arduino_IO13

Arduino IO13

3.3-V

PIN_F26

Arduino_Reset_n

Reset signal, low active.

3.3-V

PIN_AB24

Figure 3-27 Arduino Pin Arrangement and Connections.

Ta b l e 3 -20 lists the all the pin assignments of the Arduino Uno connecto r (digital), signal names

relative to the Cyclone V GX device.

Table 3-20 Pin Assignments for Arduino Uno Expansion Header connector

Schematic

Description I/O Standard

Cyclone V GX

53

Page 55

Besides 14 pins for digitial GPIO, there are also 8 analog inputs on the Arduino Uno Expansion

Header. Consequently, we use ADC LTC2308 from Linear Technology on the board for possible

future analog-to-digital applications.

The LTC2308 is a low noise, 500ksps, 8-channel, 12-bit ADC with an SPI/MICROWIRE

compatible serial interface. This ADC includes an internal reference and a fully differential

sample-and-hold circuit to reduce common mode noi se. The internal conversion clock allows the

external serial output data clock (SCK) to operate at any frequency up to 40MHz.

The LTC2308 is controlled via a serial SPI bus interface, which is connected to pins on the Cyclone

V GX FPGA. A schematic diagram of the ADC circuitry is shown in Figure 3-28. Detailed

information for using the LTC2308 is available in its datasheet, which can be found on the

manufacturer’s website, or under the Datasheets\ADC folder on the Kit System CD

Table 3-21 lists the ADC SPI Interface pin assignments, signal names relative to the Cyclone V GX

device.

Figure 3-28 A rd uino Analog input (ADC) Pin Arrangement and Connections

54

Page 56

Schematic

Signal Name

Description

I/O Standard

Cyclone

Pin Number

ADC_CONVST

Conversion Start

1.2-V

PIN_AB22

ADC_SCK

Serial Data Clock

1.2-V

PIN_AA21

ADC_SDI

Serial Data Input (FPGA to ADC)

1.2-V

PIN_Y10

ADC_SDO

Serial Data Out (ADC to FPGA)

1.2-V

PIN_W10

Table 3-21 ADC SPI Interface Pin Assignments, Schematic Signal Names, and Functions

V GX

55

Page 57

Chapter 4

System Builder

This chapter describes how users can create a custom design project on the board by using the

Software Tool of Cyclone V GX Starter Kit – C5G System Builder.

44..11 IInnttrroodduuccttiioonn

The C5G System Builder is a Windows-based software util ity, designed to assi st users to create a