TEMIC TEA1007 Datasheet

Adronic Components GmbH

Simple Phase Control Circuit

Description

Integrated circuit, TEA1007, is designed as a general

phase control circuit in bipolar technology. It has an

internal supply voltage limitation. With typical 150 mA

ignition pulse, it is possible to determine the phase-shift

Features

D

Current consumption v 2.5 mA

D

Ignition pulse typ. 150 mA

D

Voltage and current synchronization

TEA1007

of the ignition point by comparing the mains sync. ramp

voltage with a preset required value. It generates a single

ignition pulse per half wave; therefore, it is suitable for

capacitive and inductive loads in low cost applications.

D

Internal supply voltage control

Package: DIP8

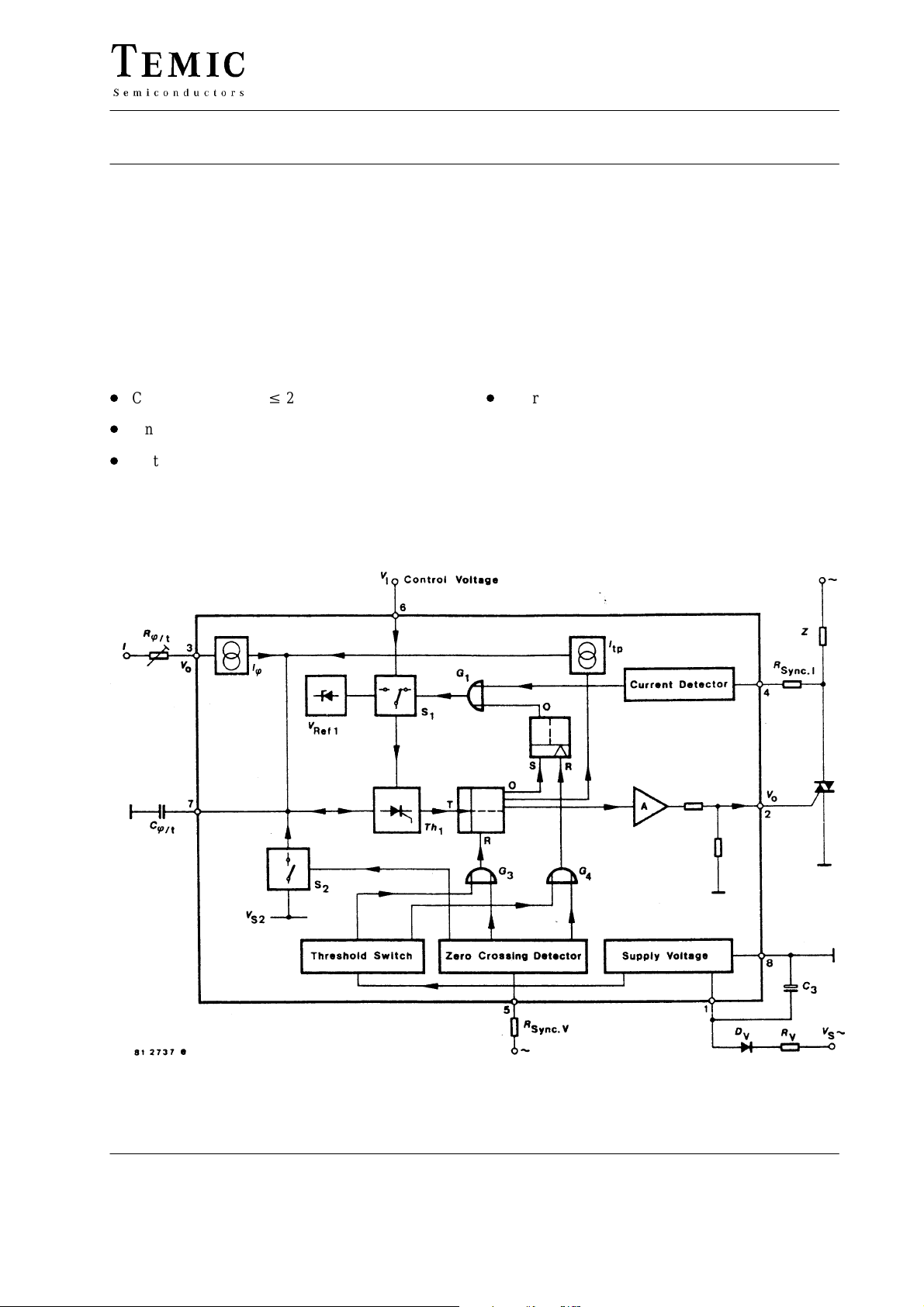

Block Diagram

R = series resistance

v

TELEFUNKEN Semiconductors

Rev . A1, 28-May-96

Figure 1. Block diagram with typical circuitry

1 (8)

Adronic Components GmbH

TEA1007

General Description

The phase-shift of the ignition point is determined in the

usual manner by comparison between a mains

synchronized ramp voltage and a predetermined required

value. The capacitor C

reference point Pin 8 is discharged at the zero transition

of the mains voltage via the V

switch S

. After the end of the zero transition pulse, C

2

is charged from the constant current source Iö, whose

value is adjusted externally with R

unavoidable tolerance of C

When the potential at Pin 7 reaches the nominal value

predetermined at Pin 6, the thyristor Th

functions as a comparator, ignites and sets the following

clock flip-flop. The output of the clock flip-flop releases

the output amplifier, connects a second constant current

source to the capacitor C

voltage switch S

voltage V

The capacitor C

+ Itp until it reaches the internal reference voltage

I

ö

. The length of this Phase 2 corresponds to the width

V

Ref

via an RS flip-flop and the OR gate G1.

Ref1

ö

of the output pulse t

the value V

, thyristor Th1ignites again and resets the

Ref

clock flip-flop to its initial state. The output pulse is thus

terminated and the constant source I

However, the RS flip-flop holds the switch S

internal reference voltage remains connected to Th

is greater than the maximum permissible control

V

Ref

voltage at Pin 6, this prevents more than one ignition

pulse from being generated in each half-cycle of the

mains voltage. This is particularly important because the

energy contents of the output pulse is of the same order

as the internal requirements of the circuit for each

half-wave.

between Pin 7 and the common

/t

ö

detector, gate G2and

o

at Pin 3 due to the

ö

(Phase 1).

/t

ö

, which also

1

, and switches the reference

/t

ö

to an internally generated threshold

1

is charged in this second phase by

/t

. When the capacitor voltage reaches

p

is switched off.

tp

so that the

1

. As

1

ö

/t

95 11358

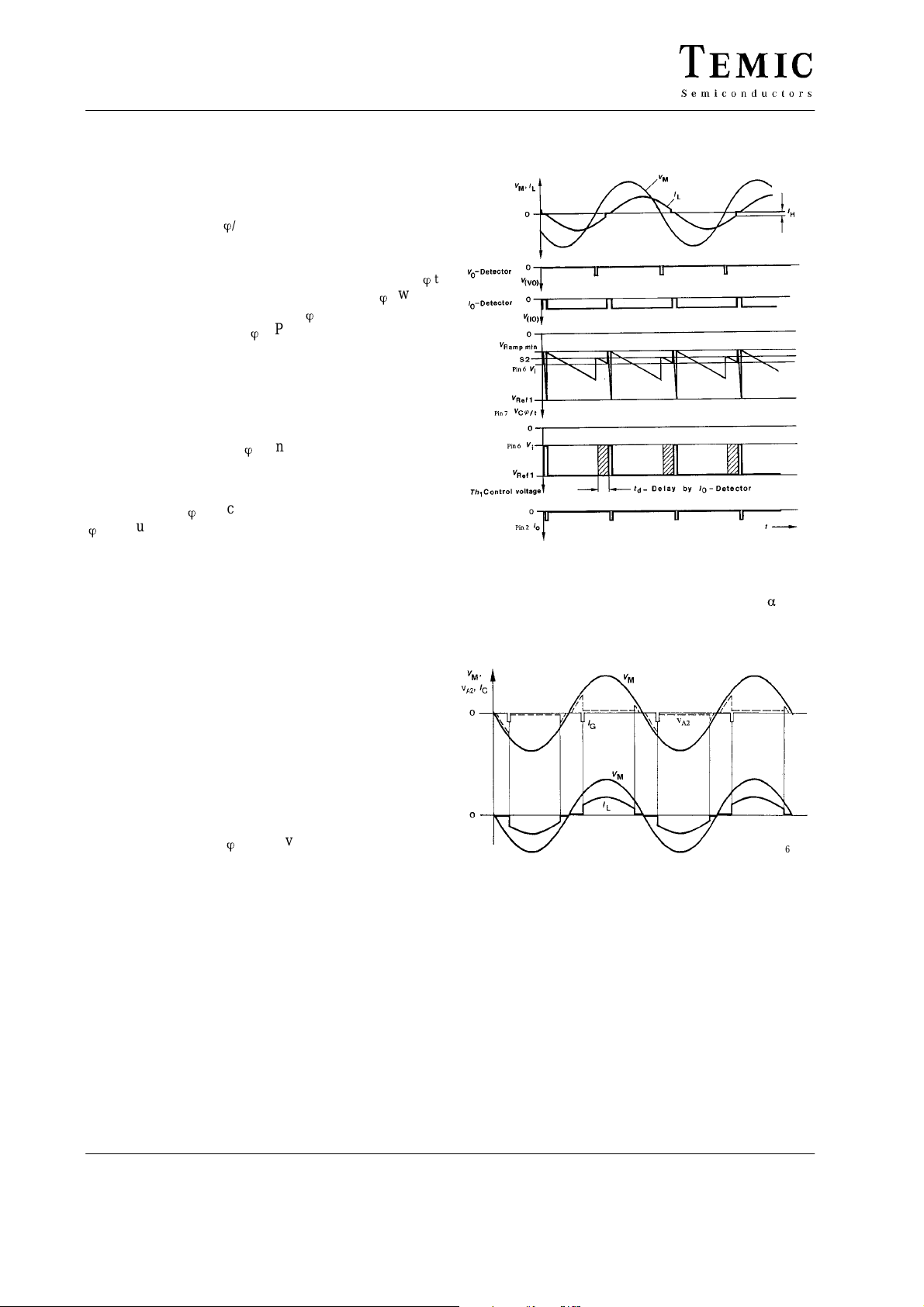

Figure 2. Functional diagram for inductive load of

a

max

In the following zero transition of the mains voltage, the

zero transition detector (Input Pin 5) resets the RS

flip-flop, discharges C

again via S2, and also insures

/t

ö

that the clock flip-flop is in the reset condition. A further

part of the basic function is the current detector with its

input at Pin 4. When controlling inductive loads, the load

current lags behind the mains voltage which means that

the circuit could generate an ignition pulse during the

period in which current is still flowing with a polarity

opposite to that of the mains voltage if the current were

not taken into account (see figure 2).

This, in turn, would lead, to so-called “gaps” in the load

current as the next ignition pulse is generated in the subsequent half-cycle.

2 (8)

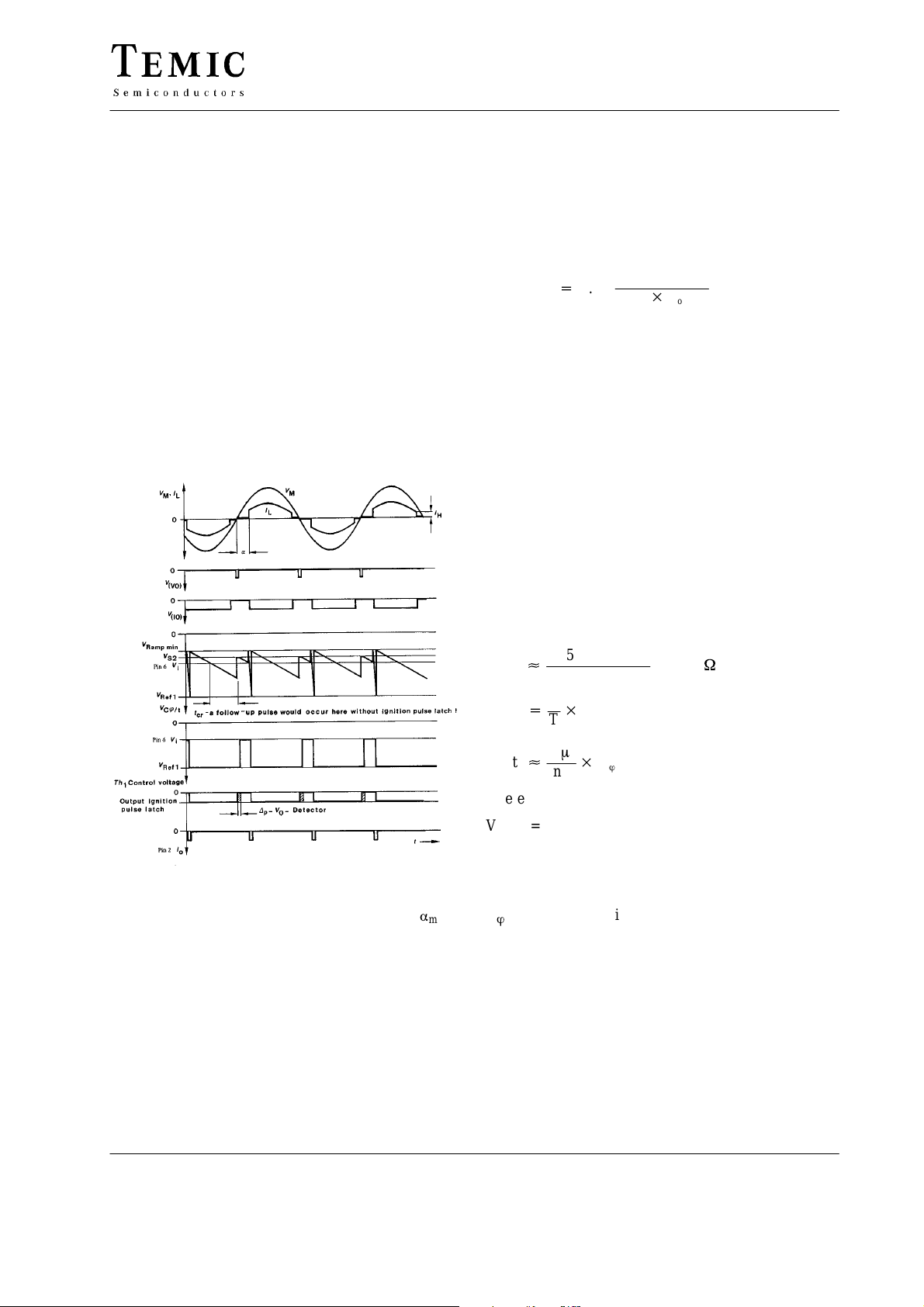

Figure 3. Triac voltages + currents at resistive load

V

= Zero cross voltage

o

= Zero cross current

I

O

= Mains voltage

V

M

= Load current

I

L

= Gate current

I

G

V

= Triac voltage at anode HI

HI

TELEFUNKEN Semiconductors

Rev . A1, 28-May-96

95 11360

Adronic Components GmbH

TEA1007

In indication as to whether load current is flowing or not

is provided by the triac itself. When the triac is ignited,

the voltage at electrode H

drops from the instantaneous

1

value of the mains voltage to approximately 1.5 V, the

value of the forward voltage of the triac. When the load

current drops below the hold current of the triac towards

the end of the half-cycle, V

again returns to the instan-

H1

taneous value of the mains voltage. The current detector

with its input at Pin 4 now controls this triac voltage and

blocks the pulse generator via G

and S1by increasing the

1

reference voltage as long as the triac is conducting. As, in

the case of a resistive load, the triac may be extinguished

shortly before the zero transition of the mains voltage –

when the load current drops below the hold current – the

RS flip-flop must prevent any possible second ignition

pulse from being generated.

Additional Function

An internal supply voltage control circuit insures that

output pulses can be generated only when the supply

voltage required for operation of all logic functions is

available.

Series resistance R

+

R

1max

I

= IS + IP + Ix whereas

tot

I

= Total current consumption

tot

I

= Current requirement of the lC

S

I

= A verage current requirement of the triggering pulses

P

I

= Current requirement of other peripheral components

x

can be calculated approx. as follows:

1

V

–V

0.85

Mmin

2 I

Smax

tot

Determination of Gate Series

Resistance, Firing Current and Pulse

Width

95 11359

Figure 4. Functional diagram for resistive load and

Firing current requirement depends upon the triac used

which can be regulated with series resistance as given

below:

R

Gmax

[

+

I

P

tP[

12.5 V – V

I

G

T

8ms

nF

I

t

Gmax

p

C

Gmax

– 110

W

ö

whereas:

V

=Triac’s gate voltage

G

=Triac’s gate current

I

G

=Gate current requirement – average

I

P

T =Period duration of mains frequency

=(firing) pulse width

t

p

=Ramp capacitor

a

min

C

ö

TELEFUNKEN Semiconductors

Rev . A1, 28-May-96

3 (8)

Loading...

Loading...