Page 1

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Page 2

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 2 of 76

Mod. 0805 2011-07 Rev.2

APPLICABILITY TABLE

PRODUCT

GL865-DUAL V3

Page 3

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 3 of 76

Mod. 0805 2011-07 Rev.2

SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

Notice

While reasonable efforts have been made to assure the accuracy of this document, Telit

assumes no liability resulting from any inaccuracies or omissions in this document, or from

use of the information obtained herein. The information in this document has been carefully

checked and is believed to be entirely reliable. However, no responsibility is assumed for

inaccuracies or omissions. Telit reserves the right to make changes to any products described

herein and reserves the right to revise this document and to make changes from time to time

in content hereof with no obligation to notify any person of revisions or changes. Telit does

not assume any liability arising out of the application or use of any product, software, or

circuit described herein; neither does it convey license under its patent rights or the rights of

others.

It is possible that this publication may contain references to, or information about Telit

products (machines and programs), programming, or services that are not announced in your

country. Such references or information must not be construed to mean that Telit intends to

announce such Telit products, programming, or services in your country.

Copyrights

This instruction manual and the Telit products described in this instruction manual may be,

include or describe copyrighted Telit material, such as computer programs stored in

semiconductor memories or other media. Laws in the Italy and other countries preserve for

Telit and its licensors certain exclusive rights for copyrighted material, including the

exclusive right to copy, reproduce in any form, distribute and make derivative works of the

copyrighted material. Accordingly, any copyrighted material of Telit and its licensors

contained herein or in the Telit products described in this instruction manual may not be

copied, reproduced, distributed, merged or modified in any manner without the express

written permission of Telit. Furthermore, the purchase of Telit products shall not be deemed

to grant either directly or by implication, estoppel, or otherwise, any license under the

copyrights, patents or patent applications of Telit, as arises by operation of law in the sale of a

product.

Computer Software Copyrights

The Telit and 3rd Party supplied Software (SW) products described in this instruction manual

may include copyrighted Telit and other 3rd Party supplied computer programs stored in

semiconductor memories or other media. Laws in the Italy and other countries preserve for

Telit and other 3rd Party supplied SW certain exclusive rights for copyrighted computer

programs, including the exclusive right to copy or reproduce in any form the copyrighted

computer program. Accordingly, any copyrighted Telit or other 3rd Party supplied SW

computer programs contained in the Telit products described in this instruction manual may

not be copied (reverse engineered) or reproduced in any manner without the express written

permission of Telit or the 3rd Party SW supplier. Furthermore, the purchase of Telit products

shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any

license under the copyrights, patents or patent applications of Telit or other 3rd Party supplied

SW, except for the normal non-exclusive, royalty free license to use that arises by operation

of law in the sale of a product.

Page 4

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 4 of 76

Mod. 0805 2011-07 Rev.2

Usage and Disclosure Restrictions

License Agreements

The software described in this document is the property of Telit and its licensors. It is

furnished by express license agreement only and may be used only in accordance with the

terms of such an agreement.

Copyrighted Materials

Software and documentation are copyrighted materials. Making unauthorized copies is

prohibited by law. No part of the software or documentation may be reproduced, transmitted,

transcribed, stored in a retrieval system, or translated into any language or computer language,

in any form or by any means, without prior written permission of Telit

High Risk Materials

Components, units, or third-party products used in the product described herein are NOT

fault-tolerant and are NOT designed, manufactured, or intended for use as on-line control

equipment in the following hazardous environments requiring fail-safe controls: the operation

of Nuclear Facilities, Aircraft Navigation or Aircraft Communication Systems, Air Traffic

Control, Life Support, or Weapons Systems (High Risk Activities"). Telit and its supplier(s)

specifically disclaim any expressed or implied warranty of fitness for such High Risk

Activities.

Trademarks

TELIT and the Stylized T Logo are registered in Trademark Office. All other product or

service names are the property of their respective owners.

Copyright © Telit Communications S.p.A.

Page 5

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 5 of 76

Mod. 0805 2011-07 Rev.2

Contents

1. Introduction

............................................................................................................ 9

1.1. Scope ............................................................................................................................. 9

1.2. Audience ........................................................................................................................ 9

1.3. Contact Information, Support .......................................................................................... 9

1.4. Document Organization ................................................................................................ 10

1.5. Text Conventions ......................................................................................................... 11

1.6. Related Documents ....................................................................................................... 11

2. Overview

............................................................................................................... 12

3. GL865-DUAL V3 Mechanical Dimensions

................................................................ 13

4. GL865-DUAL V3 module connections

...................................................................... 14

4.1. PIN-OUT ..................................................................................................................... 14

4.2. Pin Layout ................................................................................................................... 17

5. Hardware Commands

............................................................................................. 18

5.1. Auto-Turning ON the GL865-DUAL V3 ....................................................................... 18

5.2. Turning OFF the GL865-DUAL V3 .............................................................................. 20

5.3. Resetting the GL865-DUAL V3 .................................................................................... 22

5.3.1. Hardware Unconditional restart ......................................................................................... 22

6. Power Supply

........................................................................................................ 24

6.1. Power Supply Requirements ......................................................................................... 24

6.2. Power Consumption ..................................................................................................... 25

6.3. General Design Rules ................................................................................................... 26

6.3.1. Electrical Design Guidelines ............................................................................................. 26

6.3.2. Thermal Design Guidelines ............................................................................................... 29

6.3.3. Power Supply PCB layout Guidelines ................................................................................ 30

7. Antenna

................................................................................................................ 31

7.1. GSM Antenna Requirements ......................................................................................... 31

7.1.1. GL865-DUAL V3 Antenna – PCB line Guidelines ............................................................. 31

7.2. PCB Design Guidelines ................................................................................................ 33

Page 6

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 6 of 76

Mod. 0805 2011-07 Rev.2

7.2.1. Transmission line design ................................................................................................... 33

7.2.2. Transmission line measurements ....................................................................................... 34

7.3. GSM Antenna - Installation Guidelines.......................................................................... 36

8. Logic level specifications

......................................................................................... 37

8.1. Reset signal .................................................................................................................. 38

9. Serial Ports

............................................................................................................ 39

9.1. MODEM SERIAL PORT ............................................................................................. 39

9.2. RS232 level translation ................................................................................................. 41

10. Audio Section Overview

....................................................................................... 43

10.1. MIC connection ........................................................................................................ 43

10.2. LINE-IN connection .................................................................................................. 44

10.3. EAR connection ........................................................................................................ 46

10.4. Electrical Characteristics ........................................................................................... 48

10.4.1. Input Lines ....................................................................................................................... 48

10.4.2. Output Lines .................................................................................................................... 49

11. General Purpose I/O

............................................................................................ 50

11.1. GPIO Logic levels ..................................................................................................... 51

11.2. Using a GPIO Pad as INPUT ..................................................................................... 52

11.3. Using a GPIO Pad as OUTPUT ................................................................................. 52

11.4. Using the RF Transmission Control GPIO4 ................................................................ 52

11.5. Using the RFTXMON Output GPIO5 ........................................................................ 52

11.6. Using the Alarm Output GPIO6 ................................................................................. 53

11.7. Using the Buzzer Output GPIO7 ................................................................................ 53

11.8. Magnetic Buzzer Concepts ........................................................................................ 54

11.8.1. Short Description .............................................................................................................. 54

11.8.2. Frequency Behavior .......................................................................................................... 55

11.8.3. Power Supply Influence .................................................................................................... 55

11.8.4. Working Current Influence ................................................................................................ 55

11.9. STAT LED Indication of network service availability ................................................. 56

11.10. SIMIN detect function ............................................................................................... 57

Page 7

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 7 of 76

Mod. 0805 2011-07 Rev.2

11.11. RTC Bypass out ........................................................................................................ 57

11.12. SIM Holder Implementation ...................................................................................... 57

12. DAC and ADC section

......................................................................................... 58

12.1. DAC Converter ......................................................................................................... 58

12.1.1. Description ...................................................................................................................... 58

12.1.2. Enabling DAC .................................................................................................................. 59

12.1.3. Low Pass Filter Example ................................................................................................... 59

12.2. ADC Converter ......................................................................................................... 60

12.2.1. Description ...................................................................................................................... 60

12.2.2. Using ADC Converter....................................................................................................... 60

13. Mounting the GL865-DUAL V3 on your Board

...................................................... 61

13.1. General ..................................................................................................................... 61

13.2. Module finishing & dimensions ................................................................................. 61

13.3. Recommended foot print for the application ............................................................... 62

13.4. Stencil ...................................................................................................................... 62

13.5. PCB pad design ........................................................................................................ 63

13.6. Recommendations for PCB pad dimensions (mm): ..................................................... 63

13.7. Solder paste .............................................................................................................. 65

13.8. GL865-DUAL V3 Solder reflow ................................................................................ 65

13.9. Debug of the GL865-DUAL V3 in production ............................................................ 66

14. Packing system

................................................................................................... 67

14.1. Packing on tray ......................................................................................................... 67

14.2. Packing on reel ......................................................................................................... 69

14.2.1. Carrier tape detail ............................................................................................................. 70

14.2.2. Carrier tape detail ............................................................................................................. 70

14.3. Moisture sensibility ................................................................................................... 71

15. Conformity Assessment Issues

.............................................................................. 72

16. Safety Recommendations

..................................................................................... 75

17. Document History

............................................................................................... 76

Page 8

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 8 of 76

Mod. 0805 2011-07 Rev.2

Page 9

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 9 of 76

Mod. 0805 2011-07 Rev.2

1. Introduction

1.1. Scope

The aim of this document is the description of some hardware solutions useful for developing

a product with the Telit GL865-DUAL V3 module.

1.2. Audience

This document is intended for Telit customers, who are integrators, about to implement their

applications using our GL865-DUAL V3 modules.

1.3. Contact Information, Support

For general contact, technical support, to report documentation errors and to order manuals,

contact Telit Technical Support Center (TTSC) at:

TS-EMEA@telit.com

TS-NORTHAMERICA@telit.com

TS-LATINAMERICA@telit.com

TS-APAC@telit.com

Alternatively, use:

http://www.telit.com/en/products/technical-support-center/contact.php

For detailed information about where you can buy the Telit modules or for recommendations

on accessories and components visit:

http://www.telit.com

To register for product news and announcements or for product questions contact Telit

Technical Support Center (TTSC).

Our aim is to make this guide as helpful as possible. Keep us informed of your comments and

suggestions for improvements.

Telit appreciates feedback from the users of our information.

Page 10

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 10 of 76

Mod. 0805 2011-07 Rev.2

1.4. Document Organization

This document contains the following chapters:

Chapter 1: “Introduction” provides a scope for this document, target audience, contact and support

information, and text conventions.

Chapter 2: “Overview” provides an overview of the document.

Chapter 3: “GL865-DUAL V3 Mechanical Dimensions”

Chapter 4: “GL865-DUAL V3 Module Connections” deals with the pin out configuration and layout.

Chapter 5: “Hardware Commands” How to operate on the module via hardware.

Chapter 6: “Power supply” Power supply requirements and general design rules.

Chapter 7: “Antenna” The antenna connection and board layout design are the most important parts in

the full product design.

Chapter 8: “Logic Level specifications” Specific values adopted in the implementation of logic levels

for this module.

Chapter 9: “Serial ports” The serial port on the Telit GL865-DUAL V3 is the core of the interface

between the module and OEM hardware

Chapter 10: “Audio Section overview” Refers to the audio blocks of the Base Band Chip of the GL865DUAL V3 Telit Modules.

Chapter 11: “General Purpose I/O” How the general purpose I/O pads can be configured.

Chapter 12 “DAC and ADC Section” Deals with these two kind of converters.

Chapter 13: “Mounting the GL865-DUAL V3 on the application board” Recommendations and

specifics on how to mount the module on the user’s board.

Chapter 14: “Packaging system” Recommendations and specifics on how the system is packaged.

Chapter 15: “Conformity Assessment Issues”

Chapter 16: “Safety Recommendations”

Chapter 17: “Document History” Holds all document changes

Page 11

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 11 of 76

Mod. 0805 2011-07 Rev.2

1.5. Text Conventions

Danger – This information MUST be followed or catastrophic equipment failure or bodily

injury may occur.

Caution or Warning – Alerts the user to important points about integrating the module, if

these points are not followed, the module and end user equipment may fail or malfunction.

Tip or Information – Provides advice and suggestions that may be useful when

integrating the module.

All dates are in ISO 8601 format, i.e. YYYY-MM-DD.

1.6. Related Documents

• Telit's GSM/GPRS Family Software User Guide, 1vv0300784

• Audio settings application note , 80000NT10007a

• Digital Voice Interface Application Note, 80000NT10004a

• GL865-DUAL V3 Product description, 80400ST10120a

• SIM Holder Design Guides, 80000NT10001a

• AT Commands Reference Guide, 80000ST10025a

• Telit EVK2 User Guide, 1vv0300704

Page 12

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 12 of 76

Mod. 0805 2011-07 Rev.2

2. Overview

The aim of this document is the description of some hardware solutions useful for developing

a product with the Telit GL865-DUAL V3 module.

In this document all the basic functions of a mobile phone will be taken into account; for each

one of them a proper hardware solution will be suggested and eventually the wrong solutions

and common errors to be avoided will be evidenced. Obviously this document cannot

embrace all hardware solutions and products that may be designed. Avoiding the wrong

solutions shall be considered as mandatory. While the suggested hardware configurations

shall not be considered mandatory, the information given shall be used as a guide and a

starting point for properly developing your product with the Telit GL865-DUAL V3 module.

For further hardware details that may not be explained in this document refer to the Telit

GL865-DUAL V3 Product Description document where all the hardware information is

reported.

NOTICE:

The integration of the GSM/GPRS GL865-DUAL V3 cellular module within user application

shall be done according to the design rules described in this manual.

The information presented in this document is believed to be accurate and reliable. However,

no responsibility is assumed by Telit Communications S.p.A. for its use, nor any infringement

of patents or other rights of third parties which may result from its use. No license is granted

by implication or otherwise under any patent rights of Telit Communications S.p.A. other

than for circuitry embodied in Telit products. This document is subject to change without

notice.

Page 13

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 13 of 76

Mod. 0805 2011-07 Rev.2

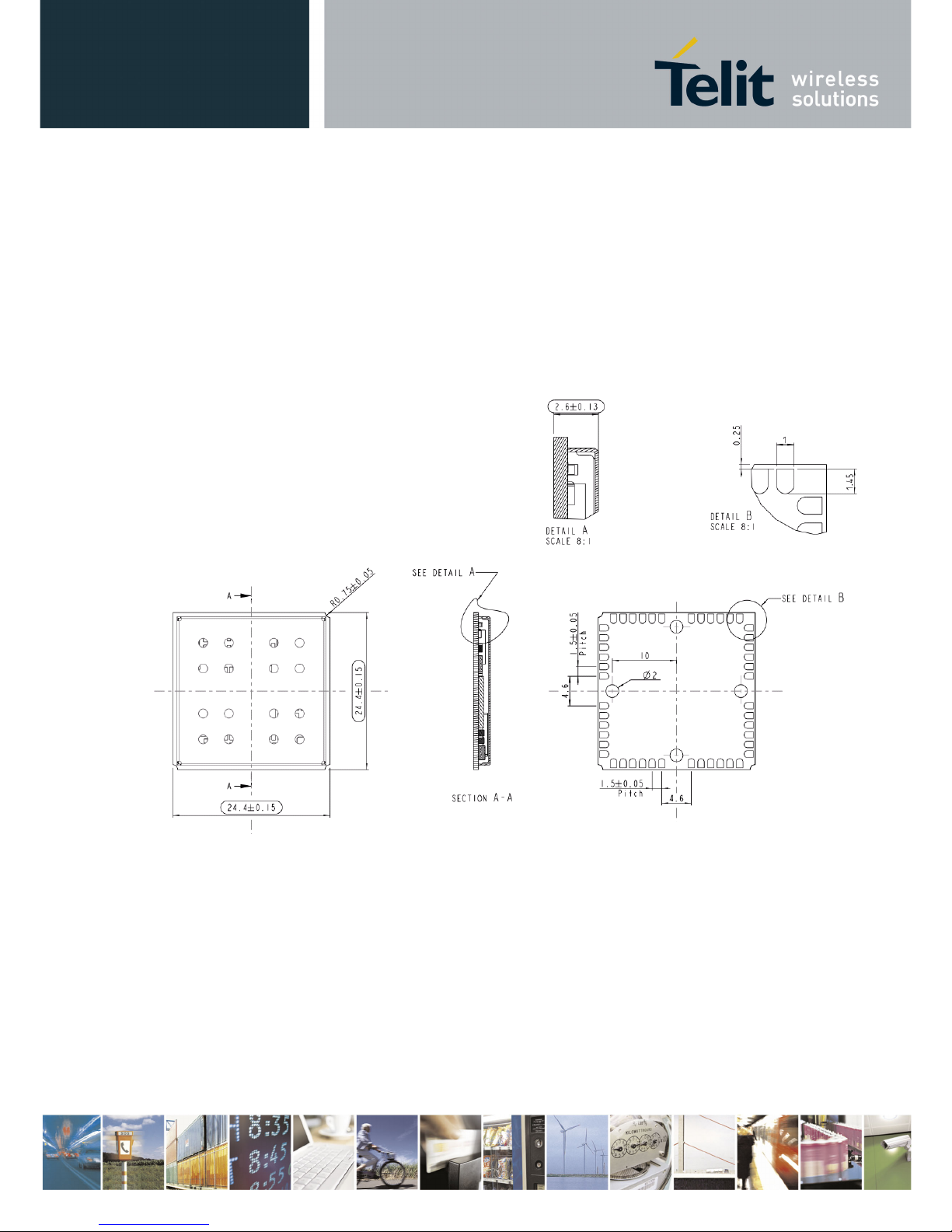

3. GL865-DUAL V3 Mechanical Dimensions

The GL865-DUAL V3 overall dimensions are:

• Length: 24.4 mm

• Width: 24.4 mm

• Thickness: 2.6 mm

• Weight 2.8 g

Page 14

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 14 of 76

Mod. 0805 2011-07 Rev.2

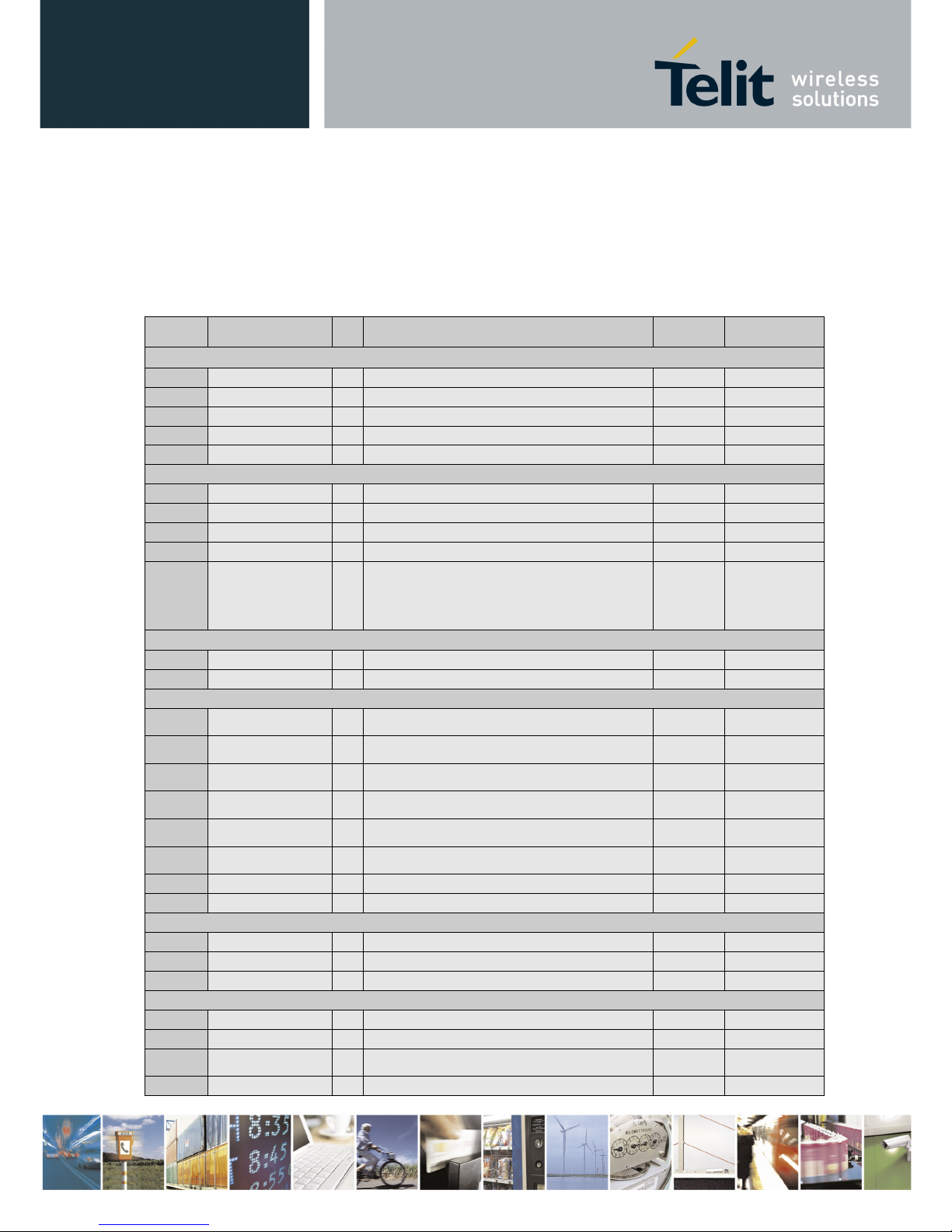

4. GL865-DUAL V3 module connections

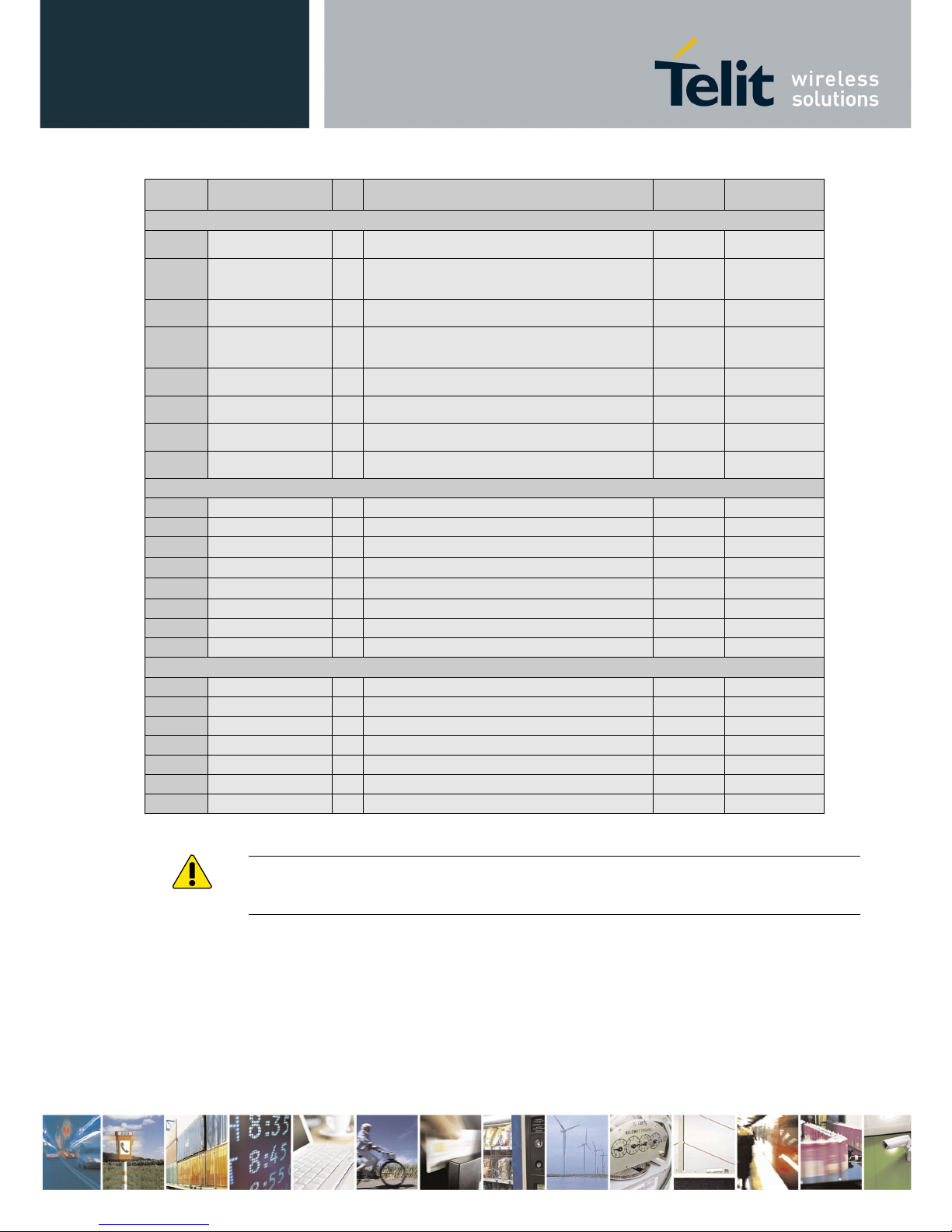

4.1. PIN-OUT

Pad Signal I/O Function Note Type

Audio

20

EAR- AO Earphone signal output, phase - Audio

21

EAR+ AO Earphone signal output, phase + Audio

22

MIC- AI Mic. signal input; phase- Audio

24

MIC+ AI Mic. signal input; phase+ Audio

23

AGND - Analog Ground -

SIM card interface

9

SIMVCC - External SIM signal – Power supply for the SIM 1,8 / 3V

10

SIMRST O External SIM signal – Reset 1,8 / 3V

11

SIMC LK O External SIM signal – Clock

1,8 / 3V

12

SIMIO I/O External SIM signal – Data I/O 4.7k Pull up 1,8 / 3V

X

All GPI0

can be

program

med

SIMIN I Presence SIM input CMOS 1.8V

Trace

44

RXD_AUX I Auxiliary UART (RX Data)

CMOS 1.8V

45

TXD_AUX O Auxiliary UART (TX Data) CMOS 1.8V

Prog. / Data + HW Flow Control

1

C109/DCD/GPO O

Output for Data carrier detect signal (DCD) to DTE

/ GP output

CMOS 1.8V

2

C125/RING/GPO O

Output for Ring indicator signal (RI) to DTE

/ GP output

CMOS 1.8V

3

C107/DSR/GPO O

Output for Data set ready signal (DSR) to DTE

/ GP output

CMOS 1.8V

4

C108/DTR/GPI I

Input for Data terminal ready signal (DTR) from DTE

/ GP input

CMOS 1.8V

5

C105/RTS/GPI I

Input for Request to send signal (RTS) from DTE

/ GP input

CMOS 1.8V

6

C106/CTS/GPO O

Output for Clear to send signal (CTS) to DTE

/ GP output

CMOS 1.8V

7

C103/TXD I Serial data input (TXD) from DTE CMOS 1.8V

8

C104/RXD O Serial data output to DTE CMOS 1.8V

DAC and ADC

13

ADC_IN1 AI Analog/Digital converter input A/D

14

ADC_IN2

AI

Analog/Digital converter input

A/D

15

DAC_OUT AO Digital/Analog converter output D/A

Miscellaneous Functions

30

VRTC AO VRTC Backup Power

47

RESET* I Reset input CMOS 1.8V

43

V_AUX / PWRMON O

1.8V stabilized output Imax=100mA

/ Power ON monitor

Power Out 1.8V

34

Antenna I/O Antenna pad – 50 Ω RF

Page 15

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 15 of 76

Mod. 0805 2011-07 Rev.2

Pad Signal I/O Function Note Type

GPIO

42

GPIO_01 / DVI_WA0 I/O

GPIO01 Configurable GPIO

/ Digital Audio Interface (WA0)

CMOS 1.8V

41

GPIO_02 / JDR /

DVI_RX

I/O

GPIO02 I/O pin

/ Jammer Detect Report

/ Digital Audio Interface (RX)

CMOS 1.8V

40

GPIO_03 / DVI_TX I/O

GPIO03 GPIO I/O pin

/ Digital Audio Interface (TX)

CMOS 1.8V

39

GPIO_04 / TX Disable

/ DVI_CLK

I/O

GPIO04 Configurable GPIO

/ TX Disable input

/ Digital Audio Interface (CLK)

CMOS 1.8V

29

GPIO_05 / RFTXMON I/O

GPIO05 Configurable GPIO

/ Transmitter ON monitor

CMOS 1.8V

28

GPIO_06 / ALARM I/O

GPIO06 Configurable GPIO

/ ALARM

CMOS 1.8V

27

GPIO_07 / BUZZER I/O

GPIO07 Configurable GPIO

/ Buzzer

CMOS 1.8V

26

GPIO_08 / STAT_LED I/O

GPIO08 Configurable GPIO

/ Digital Audio Interface (CLK)

CMOS 1.8V

Power Supply

38

VBATT - Main power supply (Baseband) Power

37

VBATT_PA - Main power supply (Radio PA) Power

23

AGND - AF Signal Ground (see audio section) AF Signal

32

GND - Ground Power

33

GND - Ground Power

35

GND

-

Ground

Power

36

GND - Ground Power

46

GND - Ground Power

RESERVED

48

-

16

-

17

-

18

-

19

-

25

-

31

-

WARNING:

Reserved pins must not be connected.

Page 16

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 16 of 76

Mod. 0805 2011-07 Rev.2

NOTE:

If not used, almost all pins should be left disconnected. The only exceptions are the following

pins:

Pin

signal

38, 37

VBATT & VBATT_PA

32, 33, 35, 36, 46

GND

23

AGND

7

TXD

8

RXD

5

RTS

43

V_AUX / PWRMON

47

RESET*

45

TXD_AUX

44

RXD_AUX

Page 17

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 17 of 76

Mod. 0805 2011-07 Rev.2

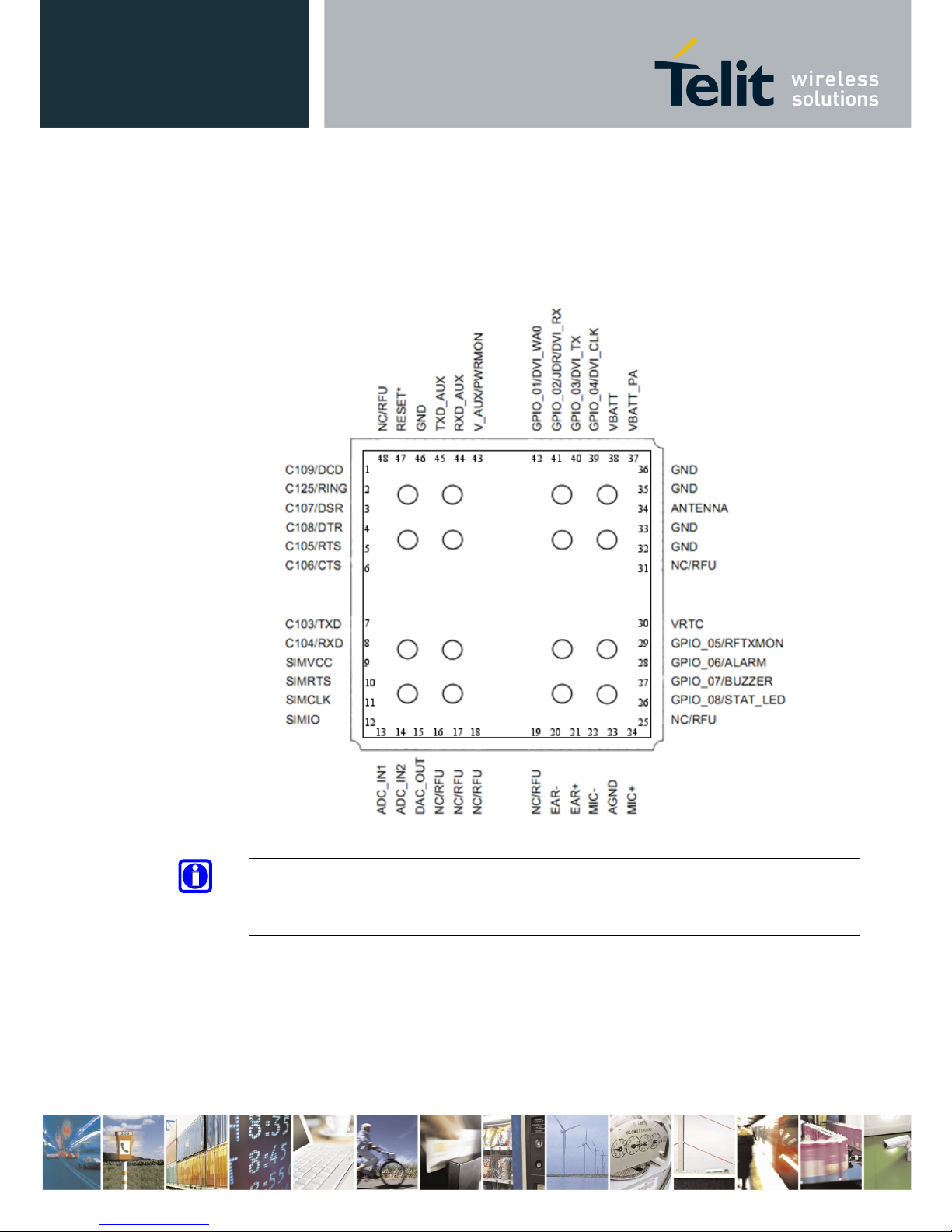

4.2. Pin Layout

TOP VIEW

NOTE:

The pins defined as NC/RFU shall be considered RESERVED and must not be connected to

any pin in the application.

Page 18

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 18 of 76

Mod. 0805 2011-07 Rev.2

5. Hardware Commands

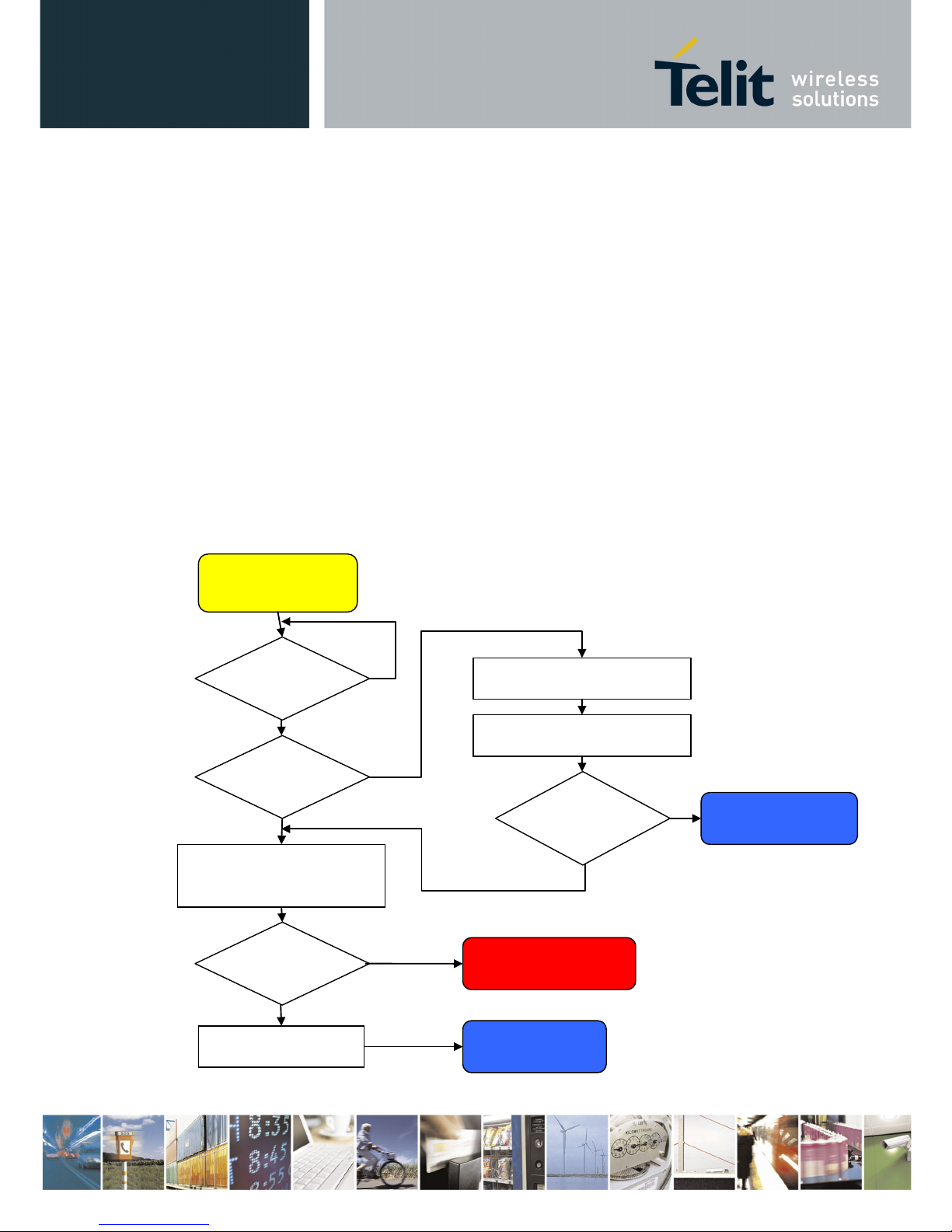

5.1. Auto-Turning ON the GL865-DUAL V3

To Auto-turn on the GL865-DUAL V3, the power supply must be applied on the power pins

VBATT and VBATT_PA, after 1000 m-seconds, the V_AUX / PWRMON pin will be at the

high logic level and the module can be considered fully operating.

When the power supply voltage is between 3.22V and 3.4V, after 5000 m-seconds, the

V_AUX / PWRMON pin will be at the high logic level and the module can be considered

fully operating.

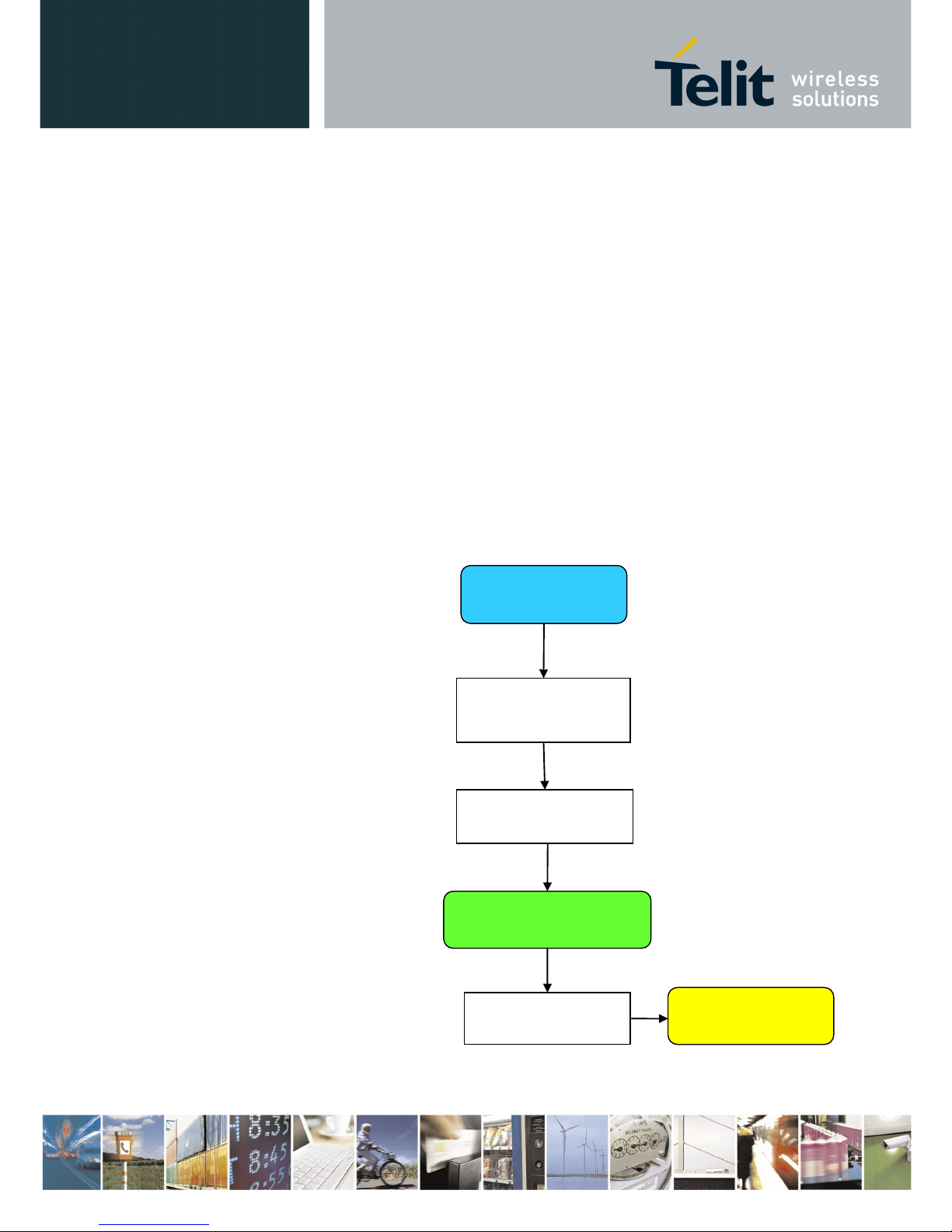

The following flow chart shows the proper turn on procedure:

Modem ON Proc.

PWR supply = ON?

Y

Delay 1s - 5s for Low

Voltage Operating

Y

Modem Reset Proc.

AT init sequence.

N

Start AT

CMD.

N

PWMON = ON?

Y

PWMON = ON?

Delay 300mS

Enter AT<CR>

AT answer in

1second ?

N Y N

Delay 1s

Page 19

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 19 of 76

Mod. 0805 2011-07 Rev.2

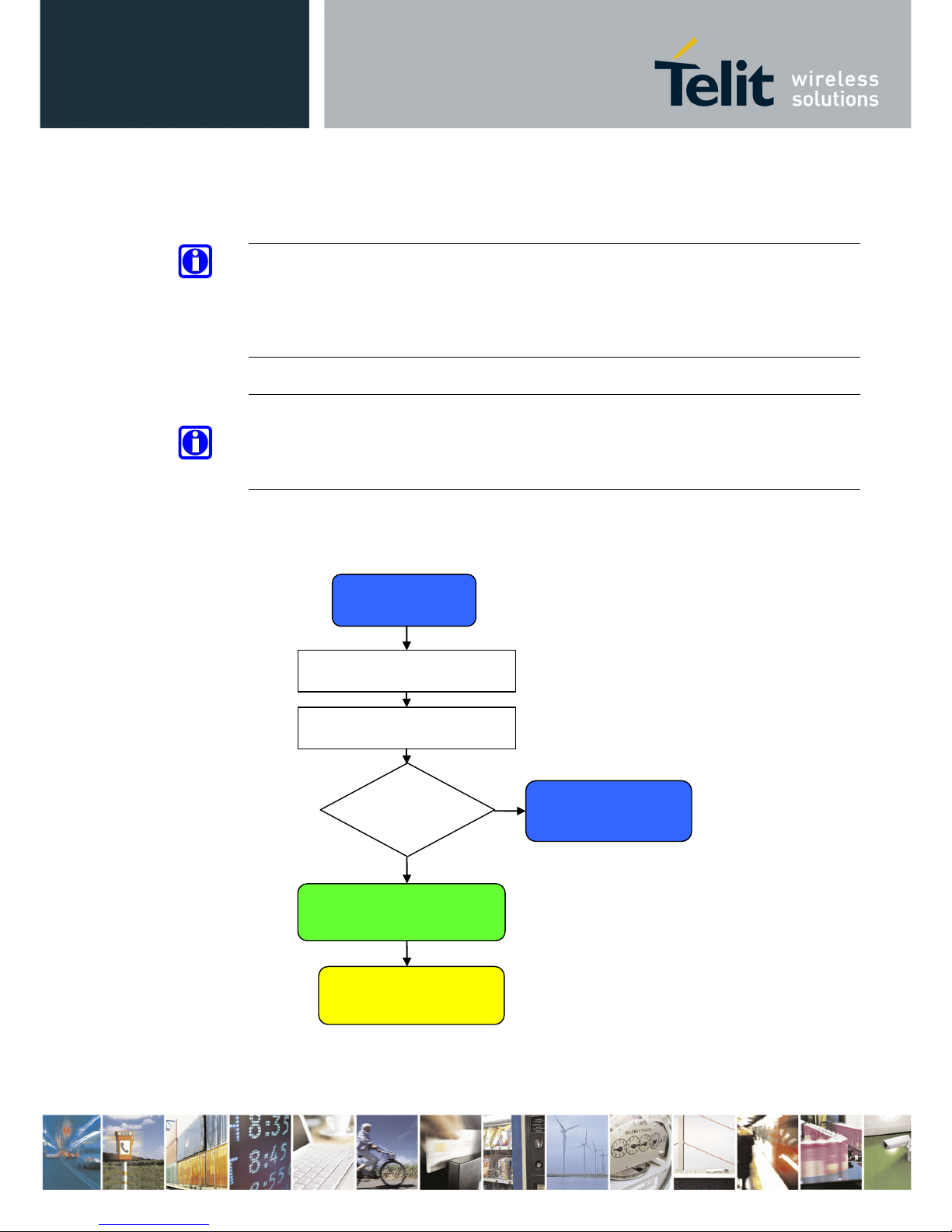

NOTE:

The power supply must be applied either at the same time on pins VBATT and VBATT_PA,

or first applied on VBATT_PA and then on VBATT. The opposite sequence shall be avoided.

The reverse procedure applies for powering down the module: first disconnect VBATT, then

VBATT_PA, or both at once.

NOTE:

In order to prevent a back powering effect it is recommended to avoid having any HIGH logic

level signal applied to the digital pins of the GL865-DUAL V3 when the module is powered

OFF or during an ON/OFF transition.

A flow chart showing the AT commands managing procedure is displayed below:

Modem ON Proc.

Disconnect PWR

supply

AT init sequence.

Delay 300mS

Enter AT<CR>

AT answer in

1second?

Y

N

Start AT CMD.

Page 20

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 20 of 76

Mod. 0805 2011-07 Rev.2

5.2. Turning OFF the GL865-DUAL V3

Turning off of the device can be done in two ways:

• General turn OFF

• Processor turn OFF

General turn OFF – disconnect the power supply from the both power pins VBATT and

VBATT_PA at the same time. In this case all parts of the module are in OFF condition, no

power consumption is present.

Processor turn OFF – disconnect the power supply only from the power pin VBATT, the

power pin VBATT_PA can be connected to power supply, in this case a low, about 30uA,

power consumption is present

Before either of both OFF procedures is applied, the AT#SYSHALT AT command must be

sent (see AT Commands Reference Guide, 80000ST10025a), after the OK response message,

wait for 10 seconds, then the module can be consider fully not operating and at this moment is

possible disconnect the Power Supply.

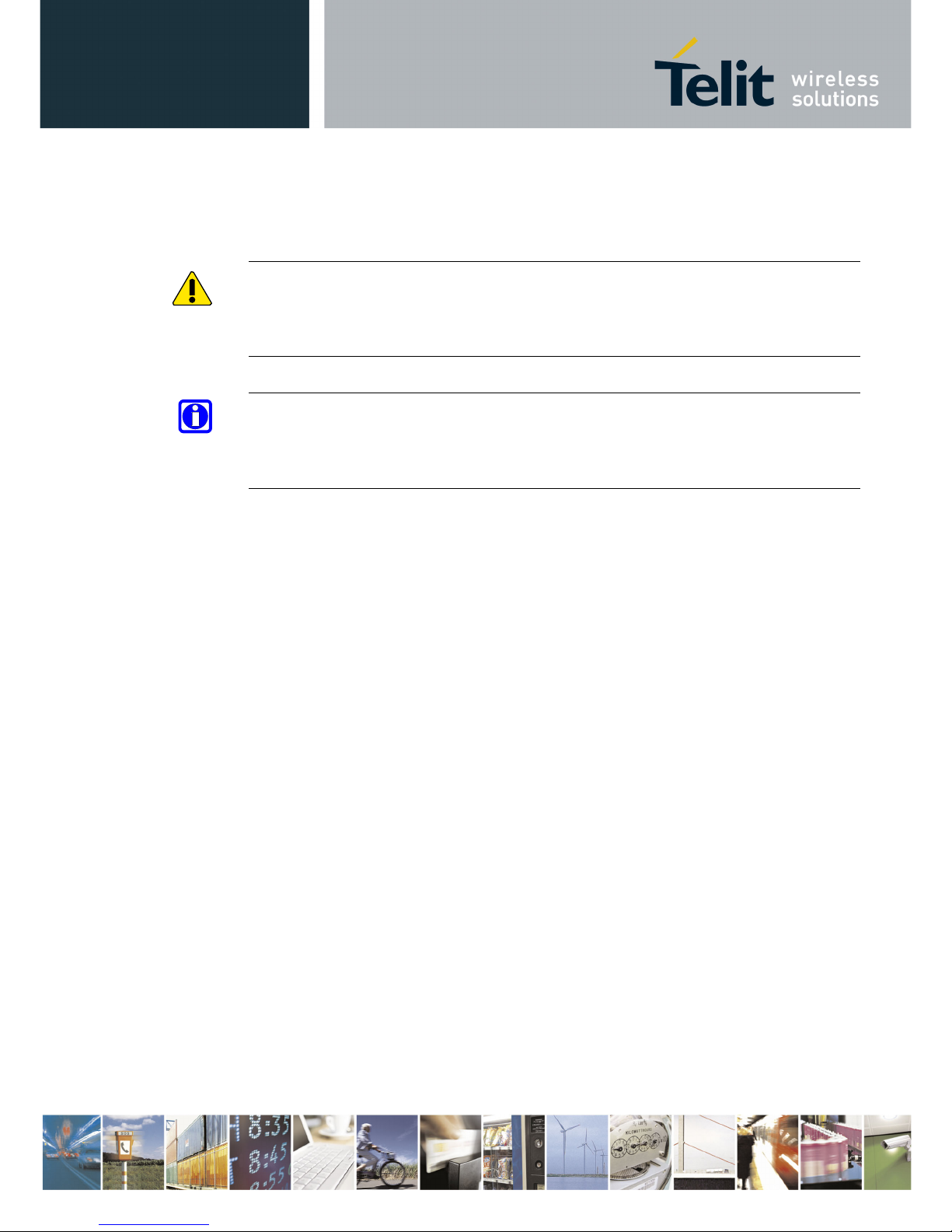

The following flow chart shows the proper turnoff procedure:

Modem OFF

Proc.

AT#SYSHALT

Disconnect PWR

supply

10s timeout

Modem ON Proc.

Delay 1.5s

Page 21

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 21 of 76

Mod. 0805 2011-07 Rev.2

WARNING:

POWERMON can be used to monitor only the power on but it cannot be used to monitor the

power off because it remains high. Instead AT#SYSHALT works in the same way as previous

GL865-DUAL V2.

NOTE:

In order to prevent a back powering effect it is recommended to avoid having any HIGH logic

level signal applied to the digital pins of the GL865-DUAL V3 when the module is powered

off or during an ON/OFF transition.

Page 22

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 22 of 76

Mod. 0805 2011-07 Rev.2

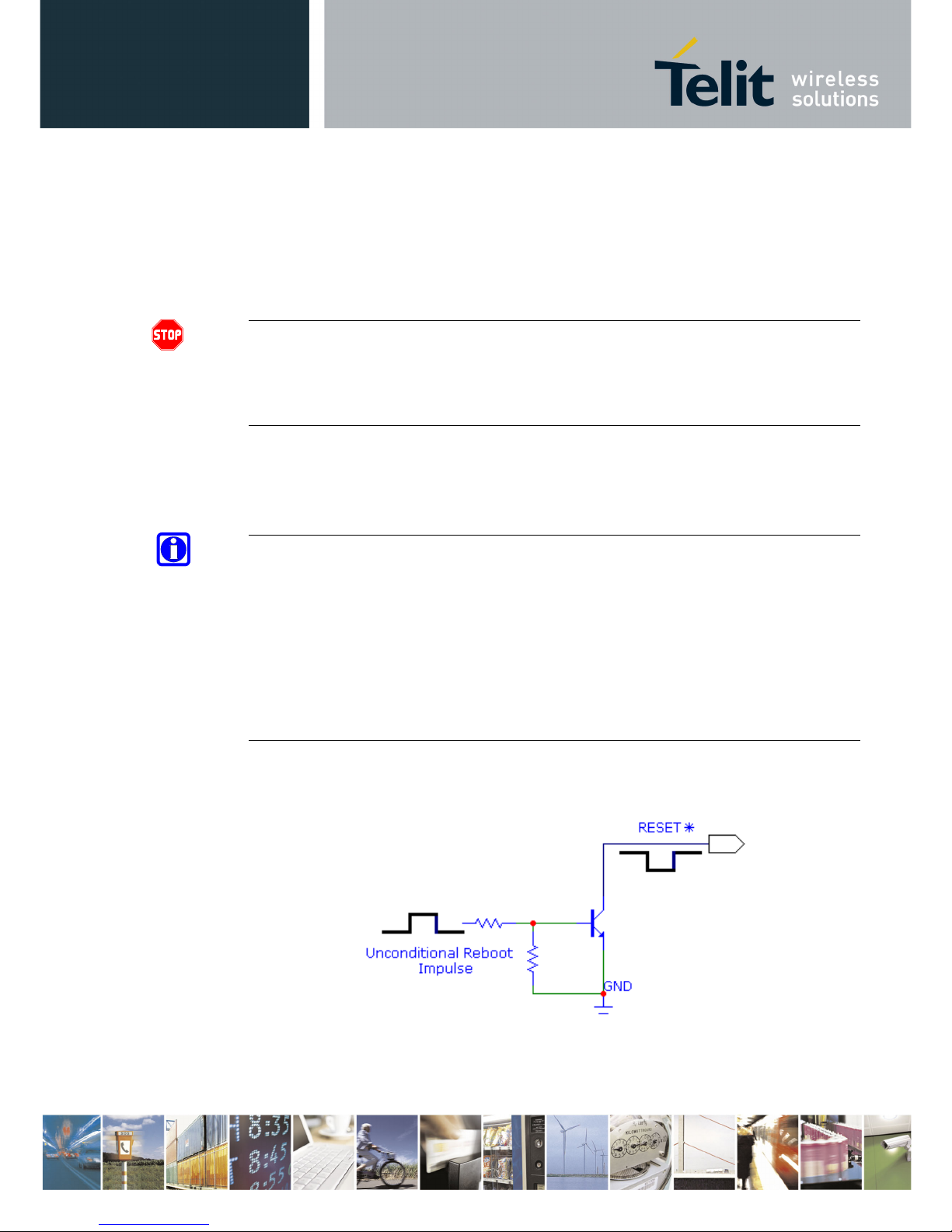

5.3. Resetting the GL865-DUAL V3

5.3.1. Hardware Unconditional restart

WARNING:

The hardware unconditional Restart must not be used during normal operation of the device

since it does not detach the device from the network. It shall be kept as an emergency exit

procedure to be done in the rare case that the device gets stuck waiting for some network or

SIM responses.

To unconditionally reboot the GL865-DUAL V3, the pad RESET* must be tied low for at

least 200 milliseconds and then released.

The maximum current that can be drained from the ON* pad is 0,15 mA.

NOTE:

Do not use any pull up resistor on the RESET* line nor any totem pole digital output. Using

pull up resistor may bring to latch up problems on the GL865-DUAL V3 power regulator and

improper functioning of the module. The line RESET* must be connected only in open

collector configuration; the transistor must be connected as close as possible to the RESET*

pin.

TIP:

The unconditional hardware restart must always be implemented on the boards and the

software must use it as an emergency exit procedure.

A simple circuit to do it is:

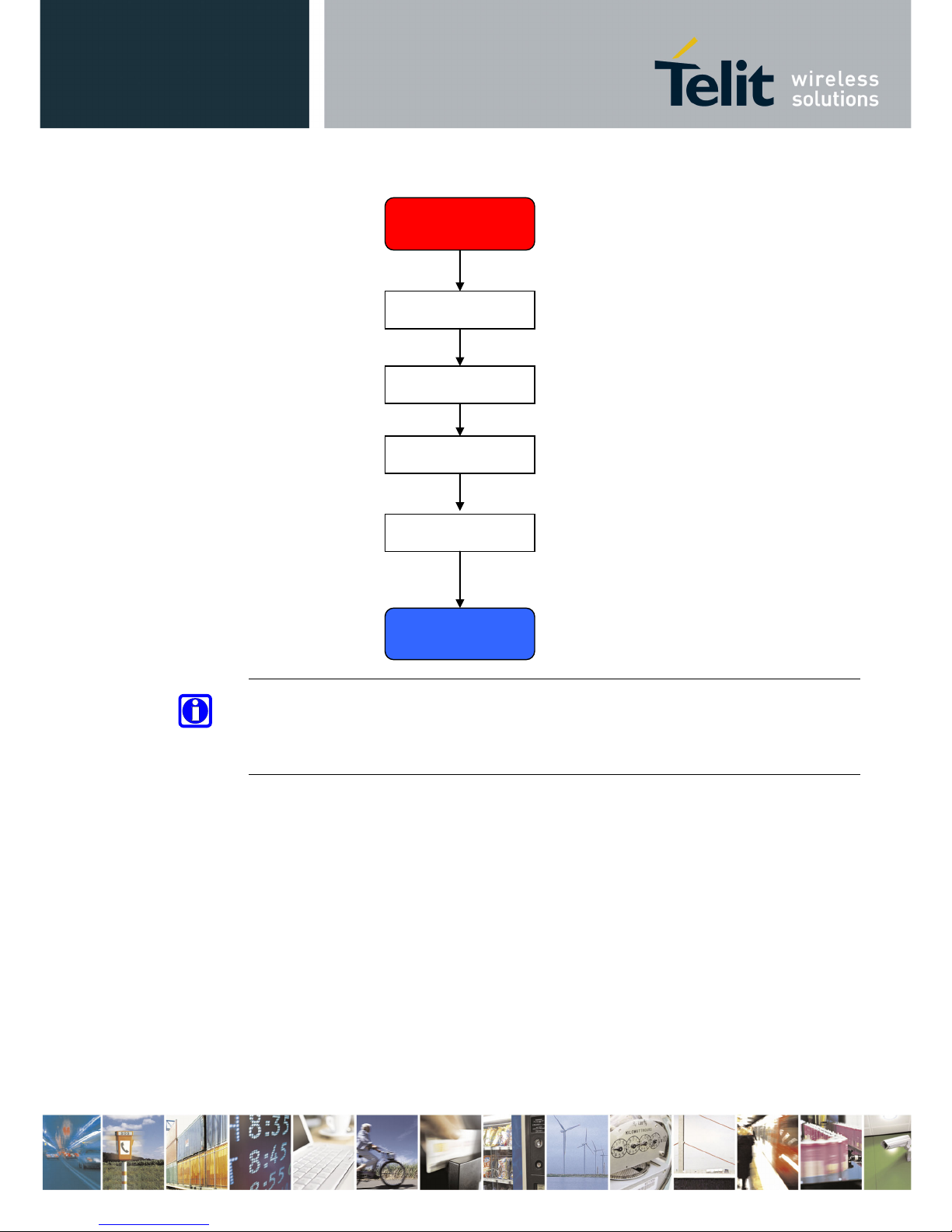

In the following flow chart is detailed the proper restart procedure:

Page 23

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 23 of 76

Mod. 0805 2011-07 Rev.2

NOTE:

In order to prevent a back powering effect it is recommended to avoid having any HIGH logic

level signal applied to the digital pins of the GL865-DUAL V3 when the module is powered

OFF or during an ON/OFF transition.

Modem Reset

Proc.

Reset = LOW

Delay 200ms

Reset = HIGH

Delay 1s

Start AT CMD.

Page 24

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 24 of 76

Mod. 0805 2011-07 Rev.2

6. Power Supply

The power supply circuitry and board layout are a very important part in the full product

design and they strongly reflect on the product overall performance, hence read the

requirements carefully and the guidelines that will follow for a proper design.

6.1. Power Supply Requirements

The external power supply must be connected to VBATT & VBATT_PA signals and must

fulfill the following requirements:

POWER SUPPLY

Nominal Supply Voltage

3.8 V

Normal Operating Voltage Range

3.40 V÷ 4.20 V

Extended Operating Voltage Range

3.10 V÷ 4.50 V

NOTE:

The Operating Voltage Range MUST never be exceeded; care must be taken when designing

the application’s power supply section to avoid having an excessive voltage drop.

If the voltage drop is exceeding the limits it could cause a Power Off of the module.

The Power supply must be higher than 3.22 V to power on the module.

NOTE:

Overshoot voltage (regarding MAX Extended Operating Voltage) and drop in voltage

(regarding MIN Extended Operating Voltage) MUST never be exceeded;

The “Extended Operating Voltage Range” can be used only with complete assumption and

application of the HW User guide suggestions.

NOTE:

When the power supply voltage is between 3.22V and 3.4V, after 5000 m-seconds, the

V_AUX / PWRMON pin will be at the high logic level and the module can be consider fully

operating. See Par. 5.1

.

Page 25

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 25 of 76

Mod. 0805 2011-07 Rev.2

6.2. Power Consumption

The GL865-DUAL V3 power consumptions are:

GL865-DUAL V3

Mode

Average

(mA)

Mode description

SWITCHED OFF

Module power supplied only on VBATT_PA pin, the VBATT pin

is not power supplied.

Switched Off

Typical 2uA

max 20uA

Switched Off with

AT#SYSHALT

<500uA

Module power supplied on VBATT_PA pin and VBATT pin, the

command AT#SYSHALT is applied.

IDLE mode

AT+CFUN=1

10

Normal mode: full functionality of the module

AT+CFUN=4

10

Disabled TX and RX; module is not registered on the network

AT+CFUN=0 or =5

2

Paging Multiframe 2

1.7

Paging Multiframe 3

1,5

Paging Multiframe 4

0,9

Paging Multiframe 9

CSD TX and RX mode

GSM VOICE CALL

GSM900 CSD PL5

200

DCS1800 CSD PL0

150

GPRS (class 1) 1TX + 1RX

GPRS Sending data mode

GSM900 PL5

200

DCS1800 PL0

140

GPRS (class 10) 2TX + 3RX

GPRS Sending data mode

GSM900 PL5

330

DCS1800 PL0

250

The GSM system is made in a way that the RF transmission is not continuous, but it is packed

into bursts at a base frequency of approx. 217 Hz, and the relative current peaks can be as

high as about 2A. Therefore the power supply has to be designed to withstand these current

peaks without big voltage drops; this means that both the electrical design and the board

layout must be designed for this current flow.

If the layout of the PCB is not well designed a strong noise floor is generated on the ground

and the supply; this will reflect on all the audio paths producing an audible annoying noise at

approx. 217 Hz; if the voltage drop during the peak current absorption is too much, then the

device may even shutdown as a consequence of the supply voltage drop.

NOTE:

The electrical design for the Power supply should be made ensuring it will be capable of a

peak current output of at least 2 A.

Page 26

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 26 of 76

Mod. 0805 2011-07 Rev.2

6.3. General Design Rules

The principal guidelines for the Power Supply Design embrace three different design steps:

• the electrical design

• the thermal design

• the PCB layout.

6.3.1. Electrical Design Guidelines

The electrical design of the power supply depends strongly on the power source from which

this power is drained. We will distinguish them into three categories:

• +5V input (typically PC internal regulator output)

• +12V input (typically automotive)

• Battery

6.3.1.1. + 5V input Source Power Supply Design Guidelines

• The desired output for the power supply is 3.8V, hence there's not a big difference

between the input source and the desired output and a linear regulator can be used. A

switching power supply will not be suited because of the low drop out requirements.

• When using a linear regulator, a proper heat sink shall be provided in order to dissipate

the power generated.

• A Bypass low ESR capacitor of adequate capacity must be provided in order to cut the

current absorption peaks close to the GL865-DUAL V3, a 100μF tantalum capacitor is

usually suited.

• Make sure the low ESR capacitor on the power supply output (usually a tantalum one)

is rated at least 10V.

• A protection diode should be inserted close to the power input, in order to save the

GL865-DUAL V3 from power polarity inversion.

An example of linear regulator with 5V input is:

Page 27

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 27 of 76

Mod. 0805 2011-07 Rev.2

6.3.1.2. + 12V input Source Power Supply Design Guidelines

• The desired output for the power supply is 3.8V, hence due to the big difference

between the input source and the desired output, a linear regulator is not suited and

shall not be used. A switching power supply will be preferable because of its better

efficiency especially with the 2A peak current load represented by the GL865-DUAL

V3.

• When using a switching regulator, a 500kHz or more switching frequency regulator is

preferable because of its smaller inductor size and its faster transient response. This

allows the regulator to respond quickly to the current peaks absorption.

• In any case the frequency and Switching design selection is related to the application

to be developed due to the fact the switching frequency could also generate EMC

interferences.

• For car PB battery the input voltage can rise up to 15,8V and this should be kept in

mind when choosing components: all components in the power supply must withstand

this voltage.

• A Bypass low ESR capacitor of adequate capacity must be provided in order to cut the

current absorption peaks, a 100μF tantalum capacitor is usually suited.

• Make sure the low ESR capacitor on the power supply output (usually a tantalum one)

is rated at least 10V.

• For Car applications a spike protection diode should be inserted close to the power

input, in order to clean the supply from spikes.

• A protection diode should be inserted close to the power input, in order to save the

GL865-DUAL V3 from power polarity inversion. This can be the same diode as for

spike protection.

An example of switching regulator with 12V input is in the below schematic:

Page 28

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 28 of 76

Mod. 0805 2011-07 Rev.2

6.3.1.3. Battery Source Power Supply Design Guidelines

• The desired nominal output for the power supply is 3.8V and the maximum voltage

allowed is 4.2V, hence a single 3.7V Li-Ion cell battery type is suited for supplying the

power to the Telit GL865-DUAL V3 module.

WARNING:

The three cells Ni/Cd or Ni/MH 3.6 V Nom. battery types or 4V PB types MUST NOT BE

USED DIRECTLY since their maximum voltage can rise over the absolute maximum voltage

for the GL865-DUAL V3 and damage it.

NOTE:

DON'T USE any Ni-Cd, Ni-MH, and Pb battery types directly connected with GL865-DUAL

V3. Their use can lead to overvoltage on the GL865-DUAL V3 and damage it. USE ONLY

Li-Ion battery types.

• A Bypass low ESR capacitor of adequate capacity must be provided in order to cut the

current absorption peaks, a 100μF tantalum capacitor is usually suited.

• Make sure the low ESR capacitor (usually a tantalum one) is rated at least 10V.

• A protection diode should be inserted close to the power input, in order to save the

GL865-DUAL V3 from power polarity inversion. Otherwise the battery connector

should be done in a way to avoid polarity inversions when connecting the battery.

• The battery capacity must be at least 500mAh in order to withstand the current peaks

of 2A; the suggested capacity is from 500mAh to 1000mAh.

Page 29

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 29 of 76

Mod. 0805 2011-07 Rev.2

6.3.2. Thermal Design Guidelines

The thermal design for the power supply heat sink should be done with the following

specifications:

See Par. 6.2 Power Consumption

NOTE:

The average consumption during transmissions depends on the power level at which the

device is requested to transmit by the network. The average current consumption hence varies

significantly.

Considering the very low current during idle, especially if Power Saving function is enabled,

it is possible to consider from the thermal point of view that the device absorbs current

significantly only during calls.

For the heat generated by the GL865-DUAL V3, you can consider it to be during

transmission 1W max during CSD/VOICE calls and 2W max during class10 GPRS upload.

This generated heat will be mostly conducted to the ground plane under the GL865-DUAL

V3; you must ensure that your application can dissipate it.

Page 30

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 30 of 76

Mod. 0805 2011-07 Rev.2

6.3.3. Power Supply PCB layout Guidelines

As seen on the electrical design guidelines the power supply shall have a low ESR capacitor

on the output to cut the current peaks and a protection diode on the input to protect the supply

from spikes and polarity inversion. The placement of these components is crucial for the

correct working of the circuitry. A misplaced component can be useless or can even decrease

the power supply performance.

• The Bypass low ESR capacitor must be placed close to the Telit GL865-DUAL V3

power input pads or in the case the power supply is a switching type it can be placed

close to the inductor to cut the ripple provided the PCB trace from the capacitor to the

GL865-DUAL V3 is wide enough to ensure a dropless connection even during the 2A

current peaks.

• The protection diode must be placed close to the input connector where the power

source is drained.

• The PCB traces from the input connector to the power regulator IC must be wide

enough to ensure no voltage drops occur when the 2A current peaks are absorbed.

Note that this is not made in order to save power loss but especially to avoid the

voltage drops on the power line at the current peaks frequency of approx. 217 Hz that

will reflect on all the components connected to that supply, introducing the noise floor

at the burst base frequency. For this reason while a voltage drop of 300-400 mV may

be acceptable from the power loss point of view, the same voltage drop may not be

acceptable from the noise point of view. If your application doesn't have audio

interface but only uses the data feature of the Telit GL865-DUAL V3, then this noise

is not so disturbing and power supply layout design can be more forgiving.

• The PCB traces to the GL865-DUAL V3 and the Bypass capacitor must be wide

enough to ensure no significant voltage drops occur when the 2A current peaks are

absorbed. This is for the same reason as previous point. Try to keep this trace as short

as possible.

• The PCB traces connecting the Switching output to the inductor and the switching

diode must be kept as short as possible by placing the inductor and the diode very

close to the power switching IC (only for switching power supply). This is done in

order to reduce the radiated field (noise) at the switching frequency (100-500 kHz

usually).

• The use of a good common ground plane is suggested.

• The placement of the power supply on the board should be done in such a way to

guarantee that the high current return paths in the ground plane are not overlapped to

any noise sensitive circuitry as the microphone amplifier/buffer or earphone amplifier.

• The power supply input cables should be kept separate from noise sensitive lines such

as microphone/earphone cables.

Page 31

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 31 of 76

Mod. 0805 2011-07 Rev.2

7. Antenna

The antenna connection and board layout design are the most important aspect in the full

product design as they strongly affect the product overall performance, hence read carefully

and follow the requirements and the guidelines for a proper design.

7.1. GSM Antenna Requirements

As suggested on the Product Description the antenna and antenna transmission line on PCB

for a Telit GL865-DUAL V3 device shall fulfill the following requirements:

ANTENNA REQUIREMENTS

Frequency range

880-960 MHz GSM900 band

1710-1885MHz MHz DCS1800 band

Gain

1.4dBi @ GSM900 and 3dBi @ DCS1800

Impedance

50 Ohm

Input power

> 2 W

VSWR absolute max

≤ 10:1 (limit to avoid permanent damage)

VSWR recommended

≤ 2:1 (limit to fulfill all regulatory requirements)

7.1.1. GL865-DUAL V3 Antenna – PCB line Guidelines

When using the Telit GL865-DUAL V3 module, since there's no antenna connector on the

module, the antenna must be connected to the GL865-DUAL V3 through the PCB with the

antenna pad (pin 34).

In the case that the antenna is not directly developed on the same PCB, hence directly

connected at the antenna pad of the GL865-DUAL V3, then a PCB line is needed in order to

connect with it or with its connector.

Page 32

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 32 of 76

Mod. 0805 2011-07 Rev.2

This transmission line shall fulfill the following requirements:

ANTENNA LINE ON PCB REQUIREMENTS

Impedance

50 ohm

Max Attenuation

0,3 dB

No coupling with other signals allowed

Cold End (Ground Plane) of antenna shall be equipotential to the

GL865-DUAL V3 ground pins

This transmission line should be designed according to the following guidelines:

• Ensure that the antenna line impedance is 50 ohm;

• Keep the antenna line on the PCB as short as possible, since the antenna line loss

shall be less than 0,3 dB;

• Antenna line must have uniform characteristics, constant cross section, avoid

meanders and abrupt curves;

• Keep, if possible, one layer of the PCB used only for the Ground plane;

• Surround (on the sides, over and under) the antenna line on PCB with Ground, avoid

having other signal tracks facing directly the antenna line track;

• The ground around the antenna line on PCB has to be strictly connected to the

Ground Plane by placing vias every 2mm at least;

• Place EM noisy devices as far as possible from GL865-DUAL V3 antenna line;

• Keep the antenna line far away from the GL865-DUAL V3 power supply lines;

• If you have EM noisy devices around the PCB hosting the GL865-DUAL V3, such as

fast switching ICs, take care of the shielding of the antenna line by burying it inside

the layers of PCB and surround it with Ground planes, or shield it with a metal frame

cover.

• If you don't have EM noisy devices around the PCB of GL865-DUAL V3, by using a

micro strip on the superficial copper layer for the antenna line, the line attenuation

will be lower than a buried one;

Page 33

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 33 of 76

Mod. 0805 2011-07 Rev.2

7.2. PCB Design Guidelines

This section explains the suggested design for the transmission line on the customer’s

application board.

7.2.1. Transmission line design

During the design of the GL865-DUAL V3 interface board, the placement of components has

been chosen properly, in order to keep the line length as short as possible, thus leading to

lowest power losses possible. A Grounded Coplanar Waveguide (G-CPW) line has been

chosen, since this kind of transmission line ensures good impedance control and can be

implemented in an outer PCB layer as needed in this case. A SMA female connector has been

used to feed the line.

The interface board is realized on a FR4, 4-layers PCB. Substrate material is characterized by

relative permittivity ε

r

= 4.6 ± 0.4 @ 1 GHz, TanD= 0.019 ÷ 0.026 @ 1 GHz.

A characteristic impedance of nearly 50 Ω is achieved using trace width = 1.1 mm, clearance

from coplanar ground plane = 0.3 mm each side. The line uses reference ground plane on

layer 3, while copper is removed from layer 2 underneath the line. Height of trace above

ground plane is 1.335 mm. Calculated characteristic impedance is 51.6 Ω, estimated line loss

is less than 0.1 dB. The line geometry is shown below:

Page 34

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 34 of 76

Mod. 0805 2011-07 Rev.2

7.2.2. Transmission line measurements

HP8753E VNA (Full-2-port calibration) has been used in this measurement session. A

calibrated coaxial cable has been soldered at the pad corresponding to GL865-DUAL V3 RF

output; a SMA connector has been soldered to the board in order to characterize the losses of

the transmission line including the connector itself. During Return Loss / impedance

measurements, the transmission line has been terminated to 50 Ω load.

Return Loss plot of line under test is shown below:

Page 35

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 35 of 76

Mod. 0805 2011-07 Rev.2

Line input impedance (in Smith Chart format, once the line has been terminated to 50 Ω load)

is shown in the following figure:

Insertion Loss of G-CPW line plus SMA connector is shown below:

Page 36

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 36 of 76

Mod. 0805 2011-07 Rev.2

7.3. GSM Antenna - Installation Guidelines

• Install the antenna in a place covered by the GSM signal.

• Antenna shall not be installed inside metal cases

• Antenna shall be installed also according to antenna manufacturer instructions.

• Installation should also take in account the R&TTE requirements described in the

“Conformity Assessment Issues” chapter

Page 37

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 37 of 76

Mod. 0805 2011-07 Rev.2

8. Logic level specifications

Where not specifically stated, all the interface circuits work at 1.8V CMOS logic levels. The

following table shows the logic level specifications used in the GL865-DUAL V3 interface

circuits:

Absolute Maximum Ratings -Not Functional

Parameter

Min

Max

Input level on any digital pin

(CMOS 1.8) when on

-0.3V

+2.1V

Operating Range - Interface levels (1.8V CMOS)

Level

Min

Max

Input high level

1.3V

1.9V

Input low level

0V

0.35V

Output high level

1.6V

1.9V

Output low level

0V

0.2V

Current characteristics

Level

Typical

Output Current

1mA

Input Current

1uA

Page 38

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 38 of 76

Mod. 0805 2011-07 Rev.2

8.1. Reset signal

Signal

Function

I/O

pin

RESET*

Phone reset

I

47

RESET* is used to reset the GL865-DUAL V3. Whenever this signal is pulled low, the

GL865-DUAL V3 is reset. When the device is reset it stops any operation. After the release of

the reset GL865-DUAL V3 is unconditionally shut down, without doing any detach operation

from the network where it is registered. This behavior is not a proper shut down because any

GSM device is requested to issue a detach request on turn off. For this reason the Reset signal

must not be used to normally shutting down the device, but only as an emergency exit in the

rare case the device remains stuck waiting for some network response.

The RESET* is internally controlled on start-up to achieve a proper power-on reset sequence,

so there's no need to control this pin on start-up. It may only be used to reset a device already

on that is not responding to any command.

NOTE:

Do not use this signal to power OFF the GL865-DUAL V3. Use the ON/OFF procedure to

perform this function.

Reset Signal Operating levels:

Signal

Min

Max

RESET* Input high

1.8V(NOTE1)

2.1V

RESET* Input low

0V

0.2V

(NOTE1) this signal is internally pulled up so the pin can be left floating if not used.

If unused, this signal may be left unconnected. If used, then it must always be connected with

an open collector transistor, to permit to the internal circuitry the power on reset and under

voltage lockout functions.

Page 39

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 39 of 76

Mod. 0805 2011-07 Rev.2

9. Serial Ports

The serial port on the GL865-DUAL V3 is the core of the interface between the module and

OEM hardware.

2 serial ports are available on the module:

• MODEM SERIAL PORT 1 (Main, ASC0)

• MODEM SERIAL PORT 2 (Auxiliary, ASC1)

9.1. MODEM SERIAL PORT

Several configurations can be designed for the serial port on the OEM hardware, but the most

common are:

• RS232 PC com port

• microcontroller UART

@ 1.8V (Universal Asynchronous Receive Transmit)

• microcontroller UART

@ 3V or other voltages different from 1.8V

• microcontroller UART

@ 5V or other voltages different from 1.8V

Depending from the type of serial port on the OEM hardware a level translator circuit may be

needed to make the system work. The only configuration that doesn't need a level translation

is the 1.8V UART.

The serial port on the GL865-DUAL V3 is a +1.8V UART with all the 8 RS232 signals. It

differs from the PC-RS232 in the signal polarity (RS232 is reversed) and levels. The levels

for the GL865-DUAL V3 UART are the CMOS levels:

Absolute Maximum Ratings -Not Functional

Parameter

Min

Max

Input level on any digital

pad when on

-0.3V

+2.1V

Input voltage on analog

pads when on

-0.3V

+2.1V

Operating Range - Interface levels (1.8V CMOS)

Level

Min

Max

Input high level V

IH

1.5V

1.9V

Input low level VIL

0V

0.35V

Output high level VOH

1.6V

1.9V

Output low level VOL

0V

0.2V

Page 40

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 40 of 76

Mod. 0805 2011-07 Rev.2

The signals of the GL865-DUAL V3 serial port are:

RS232 Pin

Number

Signal

GL865-DUAL V3

Pad Number

Name

Usage

1 DCD - dcd_uart 1 Data Carrier Detect

Output from the GL865-DUAL V3 that

indicates the carrier presence

2 RXD - tx_uart 8 Transmit line *see Note

Output transmit line of GL865-DUAL

V3 UART

3 TXD - rx_uart 7 Receive line *see Note

Input receive of the GL865-DUAL V3

UART

4 DTR - dtr_uart 4 Data Terminal Ready

Input to the GL865-DUAL V3 that

controls the DTE READY condition

5

GND

32, 33, 35, 36, 46

Ground

Ground

6 DSR - dsr_uart 3 Data Set Ready

Output from the GL865-DUAL V3 that

indicates the module is ready

7 RTS -rts_uart 5 Request to Send

Input to the GL865-DUAL V3 that

controls the Hardware flow control

8 CTS - cts_uart 6 Clear to Send

Output from the GL865-DUAL V3 that

controls the Hardware flow control

9 RI - ri_uart 2 Ring Indicator

Output from the GL865-DUAL V3 that

indicates the incoming call condition

NOTE:

According to V.24, RX/TX signal names are referred to the application side, therefore on the

GL865-DUAL V3 side these signal are on the opposite direction: TXD on the application side

will be connected to the receive line (here named TXD/ rx_uart ) of the GL865-DUAL V3

serial port and vice versa for RX.

NOTE:

For a minimum implementation, only the TXD and RXD lines can be connected, the other

lines can be left open provided a software flow control is implemented.

NOTE:

In order to avoid a back powering effect it is recommended to avoid having any HIGH logic

level signal applied to the digital pins of the GL865-DUAL V3 when the module is powered

off or during an ON/OFF transition.

Page 41

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 41 of 76

Mod. 0805 2011-07 Rev.2

9.2. RS232 level translation

In order to interface the GL865-DUAL V3 with a PC com port or a RS232 (EIA/TIA-232)

application a level translator is required. This level translator must:

• invert the electrical signal in both directions;

• change the level from 0/1.8V to +15/-15V

Actually, the RS232 UART 16450, 16550, 16650 & 16750 chipsets accept signals with lower

levels on the RS232 side (EIA/TIA-562), allowing a lower voltage-multiplying ratio on the

level translator. Note that the negative signal voltage must be less than 0V and hence some

sort of level translation is always required.

The simplest way to translate the levels and invert the signal is by using a single chip level

translator. There are a multitude of them, differing in the number of drivers and receivers and

in the levels (be sure to get a true RS232 level translator not a RS485 or other standards).

By convention the driver is the level translator from the 0-1.8V UART to the RS232 level.

The receiver is the translator from the RS232 level to 0-1.8V UART.

In order to translate the whole set of control lines of the UART you will need:

• 5 drivers

• 3 receivers

NOTE:

The digital input lines working at 1.8V CMOS have an absolute maximum input voltage of

2.1V; therefore the level translator IC shall not be powered by the +3.8V supply of the

module. Instead, it must be powered from a +1.8V (dedicated) power supply.

Page 42

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 42 of 76

Mod. 0805 2011-07 Rev.2

An example of RS232 level adaptation circuitry could be done using a MAXIM transceiver

(MAX218).

In this case the chipset is capable to translate directly from 0/1.8V to the RS232 levels

(Example done on 4 signals only).

The RS232 serial port lines are usually connected to a DB9 connector with the following

layout:

Page 43

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 43 of 76

Mod. 0805 2011-07 Rev.2

10. Audio Section Overview

The Base Band Chip of the GL865-DUAL V3 provides one input for audio to be transmitted

(Uplink) that can be connected directly to a microphone or an audio source.

The bias for the microphone is already provided by the product; so the connection can be

done in both following ways:

10.1. MIC connection

The first connection (referred to as single ended) is preferable, since the residual Vmic noise

is fed into the input as common mode and therefore rejected, while the ground noise is

blocked by the high impedance of the microphone (electret mike is a current signal source). In

this situation we have to recall that the microphone is a sound to current transducer, so the

resistor turns the current into voltage and acts as a voltage source; finally the resistor feeds the

input in balanced way even if the configuration, from a microphone point of view, seems to

be un-balanced.

If a "balanced way" is anyway desired, much more care has to be taken to Vmic noise and

ground noise; also the 33pF-100Ohm-33pF RF-filter has to be doubled (one each wire).

1u

220n

220n

1K

2.2K

1u

÷10u

MODULE

-

+

INPUT

ADC

Vmic

MIC/AF_IN+

MIC/AF_IN-

AGND

Integral Ground Plane

Page 44

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 44 of 76

Mod. 0805 2011-07 Rev.2

TIP: Since the J-FET transistor inside the microphone acts as RF-detector-amplifier, ask

vendor for a microphone with anti-EMI capacitor (usually a 33pF or a 10pF capacitor placed

across the output terminals inside the case).

10.2. LINE-IN connection

1u

220n

220n

1K

1K

1u

1u

AF_IN+

MIC/AF_IN+

MIC/AF_IN-

AGND

MODULE

- + INPUT

ADC

Vmic

AF_IN-

1u

220n

220n

1K

1K

MIC/AF_IN+

MIC/AF_IN-

AGND

MODULE

-

+

INPUT

ADC

Vmic

Wire Or Ground Plane

Page 45

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 45 of 76

Mod. 0805 2011-07 Rev.2

If the audio source is not a mike but a different device, the following connections can be done.

Place a 1Kohm resistor to ground on the negative input, in order to get balanced the input;

than connect the source via 1uF capacitor, so the DC current is blocked.

Since the input is differential, the common mode voltage noise between the two (different)

grounds is rejected, provided that both AF_IN+ & AF_IN- are connected directly onto the

source.

1u

220n

220n

1K

1K

1u

1u

AF_IN+

MIC/AF_IN+

MIC/AF_IN-

AGND

MODULE

- + INPUT

ADC

Vmic

Remote_GND

Page 46

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 46 of 76

Mod. 0805 2011-07 Rev.2

10.3. EAR connection

The audio output of the GL865-DUAL V3 is balanced, this is helpful to double the level and

to reject common mode (click and pop are common mode and therefore rejected); furthermore

the output stage is class-D, so it can manage directly a loudspeaker with electrical impedance

of at least 8Ohm. This stage is powered by switching from Vbatt to gnd at a frequency

ranging from 0.6 to 2MHz, so it has a good efficiency and thus a big power budget 0.7W;

being a class-D architecture, please use some caution (see the NOTE below).

NOTE:

When the loudspeaker is connected with a long cable, an L-C filter is recommended.

When the EAR+/- are feeding some electronic circuitry, an R-C filter is recommended.

TIP: in order to get the maximum audio level at a given output voltage level (dBspl/Vrms),

the following breaking through procedure can be used. Have the loudspeaker as close as you

can to the listener (this simplify also the echo cancelling); choose the loudspeaker with the

higher sensitivity (dBspl per W); choose loudspeakers with the impedance close to the limit

(ex: 16 or 8 Ohm), in order to feed more power inside the transducer (it increases the W/Vrms

ratio). If this were not enough, an external amplifier should be used.

WARNING:

The audio output hardware of the GL865-DUAL V3 is based on a Class-D amplifier so any

singled-end output configuration MUST NOT BE USED, otherwise the presence of GSM

buzzing and low level audio performance will result.

EAR+

EAR-

TELIT MODULE

- + OUTPUT

DAC

Page 47

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 47 of 76

Mod. 0805 2011-07 Rev.2

L-C filtering for LOW impedance load.

R-C filtering for HIGH impedance load.

EAR+

EAR-

TELIT MODULE

- + OUTPUT

DAC

GND

EAR+

EAR-

TELIT MODULE

-

+

OUTPUT

DAC

GND

HiZ CIRCUITRY

Page 48

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 48 of 76

Mod. 0805 2011-07 Rev.2

10.4. Electrical Characteristics

10.4.1. Input Lines

Microphone/Line-in path

Line Type Differential

Coupling capacitor ≥ 100nF

Differential input resistance 50kΩ

Levels

To have 0 dBfs @1KHz

(*)

Differential input voltage

MIC Gain = 0dB 290mVrms

MIC Gain = +6dB 145mVrms

MIC Gain = +12dB 72mVrms

MIC Gain = +18dB 36mVrms

MIC Gain = +24dB 18mVrms

MIC Gain = +30dB 9mVrms

MIC Gain = +36dB 4.5mVrms

MIC Gain = +42dB 2.25mVrms

(*) 0 dBfs in the network are +3.14 dBm0

TIP: The Electret microphone is internally amplified by a J-Fet transistor, thus the sound

is carried out as saturation drain current; this means that the Norton equivalence has to be

considered. The signal is converted to voltage on the 2.2KOhm resistance, from there on

circuitry has to be routed in order to not pick up common mode noise; beware of the return

path (ground).

Page 49

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 49 of 76

Mod. 0805 2011-07 Rev.2

10.4.2. Output Lines

EAR/Line-out Output

Differential line coupling

Direct connection (VDC=1.7÷2.1V)

output load resistance

≥ 8 Ω

signal bandwidth

250÷3400Hz

(@ -3dB with default filter)

max. differential output voltage

1120 mVpp @3.14dBm0 (*)

differential output voltage

550mV

rms

@0dBm0 (*)

volume increment 2dB per step

volume steps 0..10

(*) in default condition: Output Volume = +20dB, Output Attenuation = 0dB

TIP: We suggest driving the load differentially; this kills all the common mode noises

(click and pop, for example), the output swing will double (+6dB) and the big output

coupling capacitor will be avoided.

In order to get the maximum power output from the device, the resistance of the tracks has

to be negligible in comparison to the load.

Page 50

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 50 of 76

Mod. 0805 2011-07 Rev.2

11. General Purpose I/O

The general purpose I/O pads can be configured to act in three different ways:

• input

• output

• alternate function (internally controlled)

Input pads can be read; they report the digital value (high or low) present on the pad at the

read time .

Output pads can only be written or queried and set the value of the pad output.

An alternate function pad is internally controlled by the GL865-DUAL V3 firmware and acts

depending on the function implemented.

For Logic levels please refer to chapter 8.

The following table shows the available GPIO on the GL865-DUAL V3.

Pin

Signal

I/O

Function

Type

Input /

output

current

Default

State

ON_OFF

state

State

during

Reset

Note

42 GPIO_01 I/O Configurable GPIO

CMOS

1.8V

1uA/1mA INPUT 0 0

Alternate function

DVI_WA0

41 GPIO_02 I/O Configurable GPIO

CMOS

1.8V

1uA/1mA INPUT 0 0

Alternate function

JDR and DVI_RX

40 GPIO_03 I/O Configurable GPIO

CMOS

1.8V

1uA/1mA INPUT 0 0

Alternate function

DVI_TX

39 GPIO_04 I/O Configurable GPIO

CMOS

1.8V

1uA/1mA INPUT 0 0

Alternate function

TX Disable and

DVI_TX

29 GPIO_05 I/O Configurable GPIO

CMOS

1.8V

1uA/1mA INPUT 0 0

Alternate function

RFTXMON

28 GPIO_06 I/O Configurable GPIO

CMOS

1.8V

1uA/1mA INPUT 0 0

Alternate function

ALARM

27 GPIO_07 I/O Configurable GPIO

CMOS

1.8V

1uA/1mA INPUT 0 0

Alternate function

BUZZER

26 GPIO_08 I/O Configurable GPIO

CMOS

1.8V

1uA/1mA INPUT 0 0

Alternate function

STAT_LED

WARNING:

During power up the GPIOs may be subject to transient glitches.

Page 51

GL865-DUAL V3 Hardware User Guide

1vv0301018 Rev.5 – 2013-08-05

Reproduction forbidden without written authorization from Telit Communications S.p.A. - All Rights Reserved. Page 51 of 76

Mod. 0805 2011-07 Rev.2

Also the UART‘s control flow pins can be usable as GPI/O.

Pin

Signal

I/O

Function

Type

Input /

output

current

Default

State

ON_OFF

state

State

during

Reset