INVERTING VOL T AGE DOUBLER

EVALUATION

KIT

AVAILABLE

FEATURES

1

TC682

2

GENERAL DESCRIPTION

■ 99.9% Voltage Conversion Efficiency

■ 92% Power Conversion Efficiency

■ Wide Input Voltage Range ...............+2.4V to +5.5V

■ Only 3 External Capacitors Required

■ 185µA Supply Current

■ Space-Saving 8-Pin SOIC and 8-Pin Plastic DIP

Packages

APPLICATIONS

■ – 10V from +5V Logic Supply

■ – 6V from a Single 3V Lithium Cell

■ Portable Handheld Instruments

■ Cellular Phones

■ LCD Display Bias Generator

■ Panel Meters

■ Operational Amplifier Power Supplies

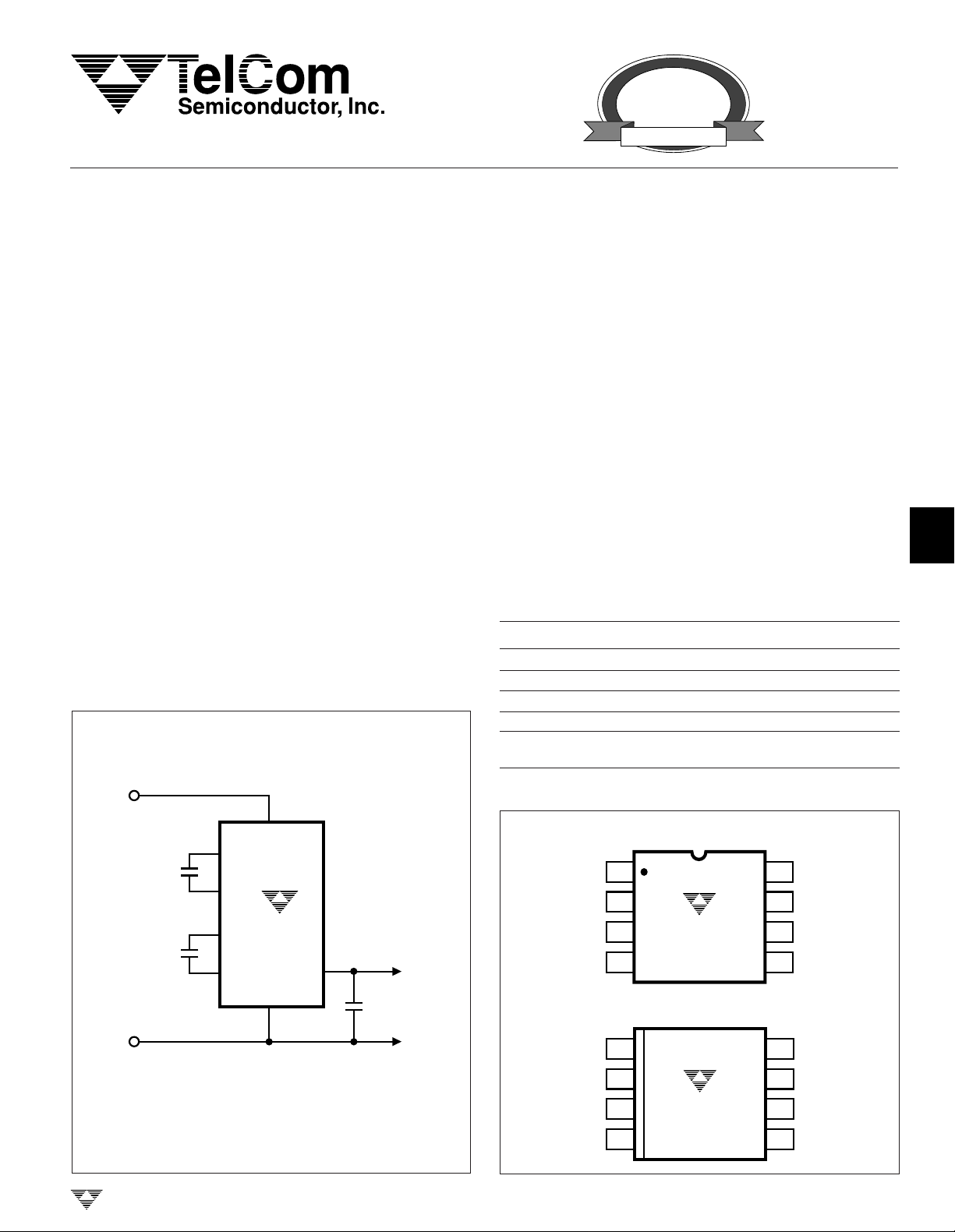

TYPICAL OPERATING CIRCUIT

+2.4V < VIN < +5.5V

V

IN

The TC682 is a CMOS charge pump converter that

provides an inverted doubled output from a single positive

supply. An on-board 12kHz (typical) oscillator provides the

clock and only 3 external capacitors are required for full

circuit implementation.

Low output source impedance (typically 140Ω), provides output current up to 10mA. The TC682 features low

quiescent current and high efficiency, making it the ideal

choice for a wide variety of applications that require a

negative voltage derived from a single positive supply (for

example: generation of – 6V from a 3V lithium cell or – 10V

generated from a +5V logic supply).

The minimum external parts count and small physical

size of the TC682 make it useful in many medium-current,

dual voltage analog power supplies.

ORDERING INFORMATION

Part No. Package Temp. Range

T

C682COA 8-Pin SOIC 0°C to +70°C

TC682CPA 8-Pin Plastic DIP 0°C to +70°C

T

C682EOA 8-Pin SOIC – 40°C to +85°C

TC682EPA 8-Pin Plastic DIP – 40°C to +85°C

TC7660EV Evaluation Kit for

Charge Pump Family

PIN CONFIGURATIONS

3

4

5

GND

TELCOM SEMICONDUCTOR, INC.

V

IN

+

+

C

1

–

+

C

2

–

C

1

–

C

1

TC682

+

C

2

–

2

GND

V

OUT

C

All Caps = 3.3µF

V = – (2 x V )

OUT

C

OUT

+

V

IN

OUT

V

V

C

1

C

2

C

2

OUT

C

C

C

OUT

–

+

–

–

1

+

2

–

2

8-Pin DIP

6

18

27

36

45

18

27

36

45

TC682CPA

TC682EPA

8-Pin SOIC

TC682COA

TC682EOA

NC

+

C

1

V

IN

GND

NC

C

1

V

IN

GND

7

+

8

TC682-2 8/21/96

4-21

V

GND

GND

C

2

+

C

2

–

R

L

C

1

+

C

1

C

2

C

1

–

IN

V

IN

V

OUT

C

All Caps = 3.3µF

OUT

TC682

(+5V)

V

OUT

–

–

6

7

1

2

3

5

4

–

+

+

–

+

TC682

INVERTING VOL T AGE DOUBLER

ABSOLUTE MAXIMUM RATINGS*

VIN.......................................................................... +5.8V

VIN dV/dT ............................................................. 1V/µsec

V

......................................................................– 11.6V

OUT

V

Short-Circuit Duration ............................Continuous

OUT

*This is a stress rating only and functional operation of the device at these

or any other conditions above those indicated in the operational sections of

the specifications is not implied. Exposure to Absolute Maximum Rating

Conditions for extended periods may affect device reliability.

Power Dissipation (TA ≤ 70°C)

Plastic DIP

...........................................................

730mW

SOIC...............................................................470mW

Storage Temperature Range ................– 65°C to +150°C

Lead Temperature (Soldering, 10 sec) .................+300°C

ELECTRICAL CHARACTERISTICS: Over Operating Temperature Range, V

= +5V, test circuit Figure 1,

IN

unless otherwise indicated.

Symbol Parameter Test Conditions Min Typ Max Unit

V

IN

I

IN

R

OUT

F

OSC

P

EFF

V

OUT EFF

TelCom Semiconductor reserves the right to make changes in the circuitry or specifications detailed in this manual at any time without notice. Minimums

and maximums are guaranteed. All other specifications are intended as guidelines only. TelCom Semiconductor assumes no responsibility for the use

of any circuits described herein and makes no representations that they are free from patent infringement.

Supply Voltage Range RL = 2kΩ 2.4 — 5.5 V

Supply Current RL = ∞, TA = 25°C — 185 300 µA

RL = ∞ — — 400

V

Source Resistance I

OUT

Source Resistance I

–

= 10mA, TA = 25°C — 140 180 Ω

L

–

= 10mA — — 230

L

–

I

= 5mA, VIN = 2.8V — 170 320

L

Oscillator Frequency — 12 — kHz

Power Efficiency RL = 2kΩ, TA = 25°C9092—%

Voltage Conversion Efficiency V

, RL = ∞ 99 99.9 — %

OUT

PIN DESCRIPTION

Pin No.

8-Pin DIP/SOIC Symbol Description

–

Input. Capacitor C1 negative

1

terminal.

+

Input. Capacitor C2 positive

2

terminal.

–

Input. Capacitor C2 negative

2

terminal

OUT

Output. Negative output voltage

(– 2VIN)

Input. Power supply voltage.

IN

+

Input. Capacitor C1 positive

1

terminal

4-22

1C

2C

3C

4V

5 GND Input. Device ground.

6V

7C

8 N/C No Connection

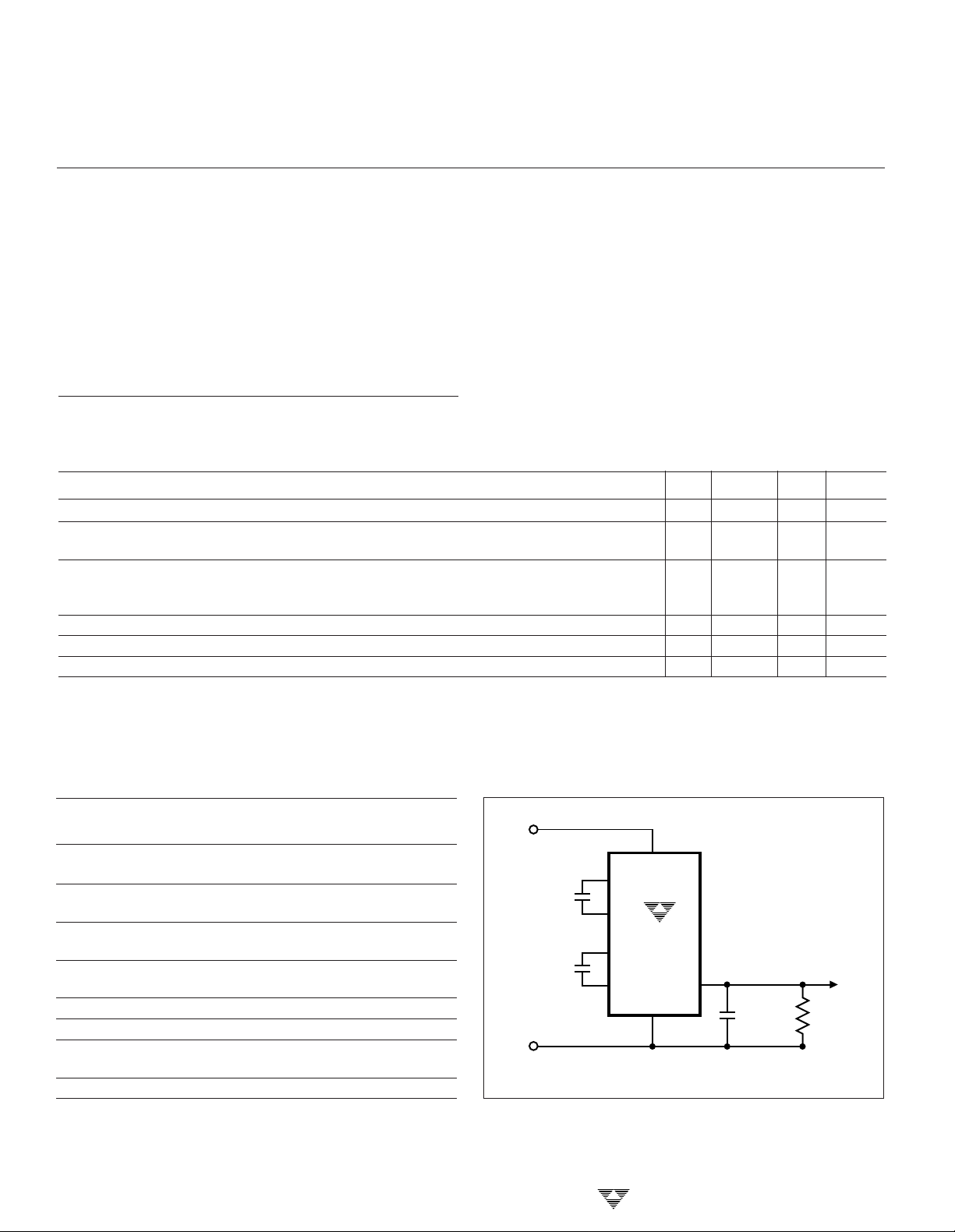

Figure 1. TC682 Test Circuit

TELCOM SEMICONDUCTOR, INC.

C

1

+

C

1

C

2

C

3

C

2

+

V

IN

V

IN

V

OUT

GND

GND

TC682

22µF

22µF

22µF

7

6

54

3

2

1

V

OUT

C

2

–

C

1

–

–

–

INVERTING VOL T AGE DOUBLER

1

TC682

DETAILED DESCRIPTION

Phase 1

VSS charge storage – before this phase of the clock

cycle, capacitor C1 is already charged to +5V. C

switched to ground and the charge in C

. Since C

+

is at +5V, the voltage potential across capacitor

2

–

is transferred to C

1

C2 is now –10V.

V

= +5V

IN

SW1

+

C

1

–

SW2

–5V

Figure 2. Charge Pump – Phase 1

SW3

+

C

2

–

SW4

–

C

3

+

+

is then

1

V

OUT

Phase 2

VSS transfer – phase two of the clock connects the

negative terminal of C2 to the negative side of reservoir

capacitor C3 and the positive terminal of C2 to ground,

transferring the generated – 10V to C3. Simultaneously, the

positive side of capacitor C1 is switched to +5V and the

negative side is connected to ground. C2 is then switched to

VCC and GND and Phase 1 begins again.

+5V

EFFICIENCY CONSIDERATIONS

Theoretically a charge pump voltage multiplier can

approach 100% efficiency under the following conditions:

• The charge pump switches have virtually no offset

and are extremely low on resistance.

–

2

• Minimal power is consumed by the drive circuitry

• The impedances of the reservoir and pump capacitors are negligible.

For the TC682, efficiency is as shown below:

Voltage Efficiency = V

V

Power Loss = I

There will be a substantial voltage difference between

–

V

OUT

and 2 V

if the impedances of the pump capacitors

IN

/ (– 2VIN)

OUT

= – 2VIN + V

OUT

V

DROP

(V

OUT

= (I

DROP

OUT

)

) (R

DROP

OUT

)

C1 and C2 are high with respect to their respective output

loads.

Larger values of reservoir capacitor C3 will reduce

output ripple. Larger values of both pump and reservoir

capacitors improve the efficiency. See "Capacitor Selection" in Applications section.

APPLICATIONS

Negative Doubling Converter

The most common application of the TC682 is as a

charge pump voltage converter which provides a negative

output of two times a positive input voltage (Figure 4).

2

3

4

5

SW1 SW3

6

V

+

C

–

Figure 3. Charge Pump – Phase 2

MAXIMUM OPERATING LIMITS

The TC682 has on-chip zener diodes that clamp V

approximately 5.8V, and V

maximum supply voltage or excessive current will be shunted

by these diodes, potentially damaging the chip. The TC682

will operate over the entire operating temperature range with

an input voltage of 2V to 5.5V.

TELCOM SEMICONDUCTOR, INC.

+

C

1

SW4SW2

2

–

–10V

–

to – 11.6V. Never exceed the

OUT

OUT

–

C

3

+

7

to

IN

Figure 4. Inverting Voltage Doubler

4-23

8

TC682

INVERTING VOL T AGE DOUBLER

Capacitor Selection

The output resistance of the TC682 is determined, in

part, by the ESR of the capacitors used. An expression for

R

is derived as shown below:

OUT

R

= 2(R

OUT

+2(

+1/(f

+ESR

Assuming all switch resistances are approximately

equal...

R

= 16R

OUT

+1/(f

R

is typically 140Ω at +25°C with VIN = +5V and

OUT

3.3µF low ESR capacitors. The fixed term (16RSW) is about

80-90Ω. It can be seen easily that increasing or decreasing

values of C1 and C2 will affect efficiency by changing R

However, be careful about ESR. This term can quickly

become dominant with large electrolytic capacitors. Table 1

shows R

OUT

ESR). C1 must be rated at 6VDC or greater while C2 and C3

must be rated at 12VDC or greater.

Output voltage ripple is affected by C3. Typically the

larger the value of C3 the less the ripple for a given load

current. The formula for

V

RIPPLE

For a 10µF (0.5Ω ESR) capacitor for C3, f

and I

= 10mA the peak-to-peak ripple voltage at the

OUT

output will be less then 60mV. In most applications (I

= 10mA) a 10-20µF capacitor and 1-5µF pump capacitors

will suffice. Table 2 shows V

(assume 1Ω ESR).

SW1

R

SW1

PUMP

SW

PUMP

+ R

+ R

C3

+ 4ESR

ESR

SW2 +

ESR

SW2 +

x C1) +1/(f

+ 4ESR

C1

x C1) +1/(f

+ R

C1

C1

PUMP

PUMP

SW3

+ R

x C2)

x C2)

+ R

SW3

C2

SW4

+ R

SW4

+ ESR

+ ESRC2)

+ ESRC2)

C3

OUT

for various values of C1 and C2 (assume 0.5Ω

is given below:

)

OUT

= 10kHz

PUMP

OUT

for different values of C3

= {1/[2(f

P-P VRIPPLE

x C3)] + 2(ESRC3)} (I

PUMP

RIPPLE

Table 2. V

C3 (µF) V

Peak- to-Peak vs. C3 (I

RIPPLE

RIPPLE

0.50 1020

1.00 520

3.30 172

5.00 120

10.00 70

22.00 43

100.00 25

OUT

(mV)

Paralleling Devices

Paralleling multiple TC682s reduces the output resistance of the converter. The effective output resistance is the

output resistance of a single device divided by the number

of devices. As illustrated in Figure 5, each requires separate

.

pump capacitors C1 and C2, but all can share a single

reservoir capacitor.

–5V Regulated Supply From A Single 3V Battery

Figure 6 shows a – 5V power supply using one 3V

battery. The TC682 provides – 6V at V

lated to – 5V by the negative LDO. The input to the TC682

can vary from 3V to 5.5V without affecting regulation appreciably. A TC54 device is connected to the battery to detect

undervoltage. This unit is set to detect at 2.7V. With higher

input voltage, more current can be drawn from the outputs

of the TC682. With 5V at VIN, 10mA can be drawn from the

regulated output. Assuming 150Ω source resistance for the

<

converter, with I

–

= 10mA, the charge pump will droop 1.5V.

L

–

, which is regu-

OUT

= 10mA)

Table 1. R

C1, C2 (µF) R

4-24

vs. C1, C2

OUT

OUT

0.05 4085

0.10 2084

0.47 510

1.00 285

3.30 145

5.00 125

10.00 105

22.00 94

100.00 87

(Ω)

TELCOM SEMICONDUCTOR, INC.

INVERTING VOL T AGE DOUBLER

V

IN

1

TC682

2

GND

10µF

+

3V

–

10µF

10µF

+

–

+

–

10µF

C

C

C

C

+

1

–

1

+

2

–

2

V

IN

TC682

GND

+

10µF

–

–

V

OUT

10µF

+

–

V

IN

+

C

1

–

C

1

TC682

+

C

2

–

C

2

GND

–

V

OUT

–

–

22µF

C

OUT

+

NEGATIVE

SUPPLY

3

4

Figure 5. Paralleling TC682 for Lower Output Source Resistance

5

V

+

1

–

1

+

–

2

IN

TC682

GND

+

V

SS

–

V

OUT

–

22µF

+

–

C

OUT

V

IN

NEGATIVE LDO

REGULATOR

V

OUT

1µF

–

GROUND

6

–5 SUPPLY

+

–

+

C

C

C

2

–

C

Figure 6. Negative Supply Derived from 3V Battery

TELCOM SEMICONDUCTOR, INC.

TC54VC2702Exx

V

IN

V

V

SS

OUT

7

LOW BATTERY

8

4-25

TC682

INVERTING VOL T AGE DOUBLER

TYPICAL CHARACTERISTICS (F

Output Resistance vs. V

240

220

200

180

160

140

OUTPUT RESISTANCE (Ω)

120

12 3

Supply Current vs. V

300

NO LOAD

250

200

150

VIN (V)

4

IN

= 12kHz)

OSC

IN

C1– C3 = 3.3µF

5 0 510156

(V)

OUT

V

–10.0

–10.5

120

–7.5

–8.0

–8.5

–9.0

–9.5

200

180

160

140

V

vs. Load Current

OUT

V

= 5V

IN

LOAD CURRENT (mA)

Output Source Resistance vs. Temperature

V

= 5V

IN

I

= 10mA

OUT

100

SUPPLY CURRENT (µA)

50

12 3

4

VIN (V)

200

V

150

100

50

OUTPUT RIPPLE (mV PK-PK)

0

0

56

Output Ripple vs. Output Current

= 5V

IN

C3 =10µF

C3 =100µF

5

OUTPUT CURRENT (mA)

10

100

OUTPUT SOURCE RESISTANCE (Ω)

80

–50 0 50 100

TEMPERATURE (°C)

15

20

4-26

TELCOM SEMICONDUCTOR, INC.

Loading...

Loading...