Page 1

Instruction Manual

TMSSC1

604-Pin Socket Hardware Support

071-1138-00

Warning

The servicing instructions are for use by qualified

personnel only. To avoid personal injury, do not

perform any servicing unless you are qualified to

do so. Refer to all safety summaries prior to

performing service.

www.tektronix.com

Page 2

Copyright © Tektronix, Inc. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes

that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077

TEKTRONIX and TEK are registered tradem arks of Tektronix, Inc.

Page 3

HARDWARE WARRANTY

Tektronix warrants that the products that it m anufactures and sells will be free from defects in materials and

workmanship for a period of one (1) year from the date of shipment. If a product proves defect ive during this

warranty period, Tektronix, at its option, ei ther will repa ir the defective product wit hout charge for parts and labor,

or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration

of the warranty period and make suitable arrangements for the performance of service. Customer shall be

responsible for packaging and shipping the defective product to the service center designated by Tektronix, with

shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a

location within the country in which the Tektronix service center is located. Customer shall be responsible for

paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defe ct, fail ure or damage caused by improper use or improper or inadequate

maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage

resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product;

b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any

damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been

modified or integrated with other products when the effect of such modification or integration increases the time

or difficulty of servicing the product.

THIS W ARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS

OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF

MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX’

RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND

EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY.

TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL,

INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR

THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Page 4

Page 5

Table of Contents

Getting Started

General Safety Summary vii...................................

Service Safety Summary ix....................................

Preface xi...................................................

Manual Conventions xi..............................................

Contacting Tektronix xii..............................................

Support Package Description 1--1.......................................

Logic Analyzer Software Compatibility 1--1...............................

Logic Analyzer Configuration 1--2......................................

Options and Accessories 1--3...........................................

Probe Adapter Review 1--3............................................

Configuring the Probe Adapter 1--4......................................

Connecting the Logic Analyzer to a Target System 1--5......................

Connect the P6860 Probes to the Preprocessor Unit 1--13..................

Applying Power 1--15..............................................

Removing Power 1--15.............................................

Verifying Probe Operation 1--15........................................

Storage 1--16........................................................

Care and Maintenance 1--17.............................................

Shipping the Probe Adapter 1--18........................................

Operating Basics

Specifications

Reference

Maintenance

Setting Up the Software 2--1.....................................

Installing the Software 2--1............................................

Custom Clocking 2--2................................................

Channel Group Definitions 2--3........................................

Channel Assignments 2--3.............................................

Circuit Description 3--1...............................................

Loading Diagrams 3--3................................................

Specification Tables 3--5..............................................

Channel Assignment Tables 4--1.................................

Channel Group Definition Tables 4--27............................

Fuses 5--1..........................................................

Removal and Installation Procedures 5--3.........................

Removing and Installing the Cables 5--3..................................

Reinstalling the Cables 5--9............................................

TMSSC1 604 Pin Socket Hardware Support

i

Page 6

Table of Contents

Replaceable Parts List

Index

Removing and Installing a Fan 5--15......................................

Parts Ordering Information 6--1.........................................

Using the Replaceable Parts List 6--2.....................................

ii

TMSSC1 604 Pin Socket Hardware Support

Page 7

List of Figures

Table of Contents

Figure 1--1: Configuration of the master and slave modules 1--2.......

Figure 1--2: Jumper locations on the preprocessor unit 1--4...........

Figure 1--3: Module configuration for the master and slave modules 1--5

Figure 1--4: Remove the heat sink retention mechanism from

the target system 1--7.......................................

Figure 1--5: Connect the microprocessor 1--8.......................

Figure 1--6: Connect the probe head to the 604 Pin Socket 1--9........

Figure 1--7: Engage the ZIF lever 1--10.............................

Figure 1--8: Connect the heat sink and probe head to the

target system 1--11..........................................

Figure 1--9: Remove the microprocessor from the probe head 1--12.....

Figure 1--10: Connect the probes 1--13.............................

Figure 1--11: Module configuration of the master and slave modules 1--14

Figure 1--12: Place the probe head in a static shielding bag 1--19.......

Figure 1--13: Place the end caps on the preprocessor 1--19.............

Figure 1--14: Place the probe head into the square cutout 1--20.........

Figure 2--1: State Speed menu 2--2...............................

Figure 3--1: Electrical load model for typical signals 3--3.............

Figure 3--2: Pin header electrical load model for typical signals 3--4...

Figure 3--3: LIF electrical load model for typical signals 3--4.........

Figure 3--4: Mated Samtec model 3--4.............................

Figure 3--5: BCLK Receiver 3--4.................................

Figure 3--6: Dimensions of the TMSSC1 604 Pin Socket probe head 3--8

Figure 3--7: Dimensions of the preprocessor unit 3--9................

Figure 4--1: Configuration for master and slave modules 4--1.........

Figure 5--1: Remove AC power cord 5--4..........................

Figure 5--2: Remove the attaching screws 5--4......................

Figure 5--3: Remove the fan plug 5--5.............................

Figure 5--4: Remove the LED cable 5--5...........................

Figure 5--5: Remove power supply cables 5--6......................

Figure 5--6: Remove the power supply dual plug 5--6................

Figure 5--7: Remove the power supply shield 5--7...................

Figure 5--8: Remove the logic board from the chassis 5--7............

Figure 5--9: Remove the cables from the back of the logic board 5--8...

TMSSC1 604 Pin Socket Hardware Support

iii

Page 8

Table of Contents

Figure 5--10: Power switch location 5--9...........................

Figure 5--11: Remove the attaching screws 5--10.....................

Figure 5--12: Attach the cables to the logic board 5--10................

Figure 5--13: Place logic board in the chassis 5--11...................

Figure 5--14: Attach the logic board to the chassis 5--11...............

Figure 5--15: Attach the power supply shield 5--12...................

Figure 5--16: Attach fan plug 5--12................................

Figure 5--17: Attach the LED cable to the Logic board 5--13...........

Figure 5--18: Attach the power supply cables 5--13...................

Figure 5--19: Attach the power supply dual plug 5--14................

Figure 5--20: Attach the bottom cover 5--14.........................

Figure 5--21: Power switch and AC power cord locations 5--15.........

Figure 5--22: Remove the bottom cover 5--16........................

Figure 5--23: Remove the bottom cover 5--16........................

Figure 5--24: Remove the pin connectors 5--17.......................

Figure 5--25: Back of the preprocessor unit 5--18....................

Figure 5--26: Location of fan plug 5--19............................

Figure 6--1: Probe adapter exploded view 6--6......................

Figure 6--2: Preprocessor unit exploded view 6--8...................

iv

TMSSC1 604 Pin Socket Hardware Support

Page 9

List of Tables

Table of Contents

Table 1--1: Frequency select jumpers 1--4.........................

Table 3--1: Electrical specifications for the target system 3--5........

Table 3--2: Electrical specifications for the AC input to the

preprocessor unit 3--6......................................

Table 3--3: BCLK timing and electrical specifications 3--6..........

Table 3--4: Environmental specifications 3--6......................

Table 3--5: Certifications and compliances 3--7.....................

Table 4--1: Clock channel assignments 4--1........................

Table 4--2: Qual channel assignments 4--3.........................

Table 4--3: Master Address Module 32-channel assignments 4--3......

Table 4--4: Master Control Module 32-channel assignments 4--5......

Table 4--5: Master Data Module 32-channel assignments 4--6.........

Table 4--6: Master Extend Module 32-channel assignments 4--7.......

Table 4--7: Slave Address Module 32-channel assignments 4--8.......

Table 4--8: Slave Control Module 32-channel assignments 4--10........

Table 4--9: Slave Data Module 32-channel assignments 4--11..........

Table 4--10: Slave Extend Module 32-channel assignments 4--12.......

Table 4--11: Slave2 Address Module 32-channel assignments 4--13.....

Table 4--12: Slave2 Control Module 32-channel assignments 4--15......

Table 4--13: Slave2 Data Module 32-channel assignments 4--16........

Table 4--14: Slave2 Extend Module 32-channel assignments 4--17......

Table 4--15: Slave3 Address Module 32-channel assignments 4--18.....

Table 4--16: Slave3 Data Module 32-channel assignments 4--20........

Table 4--17: Slave3 Control Module 32-channel assignments 4--21......

Table 4--18: Slave3 Extend Module 32-channel assignments 4--22......

Table 4--19: A[35:32] channel group definitions 4--25................

Table 4--20: A[31:00] channel group definitions 4--25................

Table 4--21: Ab[35:32] channel group definitions 4--27...............

Table 4--22: Ab[31:00] channel group definitions 4--27...............

Table 4--23: AddrParity channel group definitions 4--28..............

Table 4--24: Request channel group definitions 4--28.................

Table 4--25: Response channel group definitions 4--29................

Table 4--26: Data channel group definitions 4--30....................

Table 4--27: D0[63:32] and D0[31:00] channel group definitions 4--34...

Table 4--28: DataInvert channel group definitions 4--38..............

Table 4--29: DataParity channel group definitions 4--38..............

TMSSC1 604 Pin Socket Hardware Support

v

Page 10

Table of Contents

Table 4--30: Execution channel group definitions 4--39...............

Table 4--31: Error channel group definitions 4--39...................

Table 4--32: Compatible channel group definitions 4--39..............

Table 4--33: Diagnostic channel group definitions 4--40...............

Table 4--34: Misc channel group definitions 4--40....................

Table 4--35: D[63:48] channel group definitions 4--41................

Table 4--36: D[47:32] channel group definitions 4--41................

Table 4--37: D[15:00] channel group definitions 4--42................

vi

TMSSC1 604 Pin Socket Hardware Support

Page 11

General Safety Summary

Review the following safety precautions to avoid injury and prevent damage to

this product or any products connected to it. To avoid potential hazards, use this

product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read

the General Safety Summary in other system manuals for warnings and cautions

related to operating the system.

ToAvoidFireor

Personal Injury

Use Proper Power Cord. Use only the power cord specified for this product and

certified for the country of use.

Connect and Disconnect Properly. Do not connect or disconnect probes or test

leads while they are connected to a voltage source.

Ground the Product. This product is grounded through the grounding conductor

of the power cord. To avoid electric shock, the grounding conductor must be

connected to earth ground. Before making connections to the input or output

terminals of the product, ensure that the product is properly grounded.

Observe All Terminal Ratings. To avoid fire or shock hazard, observe all ratings

and markings on the product. Consult the product manual for further ratings

information before making connections to the product.

Connect the ground lead of the probe to earth ground only.

Do Not Operate Without Covers. Do not operate this product with covers or panels

removed.

Use Proper Fuse. Use only the fuse type and rating specified for this product.

Avoid Exposed Circuitry. Do not touch exposed connections and components

when power is present.

Do Not Operate With Suspected Failures. If you suspect there is damage to this

product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

Keep Product Surfaces Clean and Dry.

Provide Proper Ventilation. Refer to the manual’s installation instructions for

details on installing the product so it has proper ventilation.

TMSSC1 604 Pin Socket Hardware Support

vii

Page 12

General Safety Summary

Symbols and Terms

Terms in this Manual. These terms may appear in this manual:

WARNING. Warning statements identify conditions or practices that could result

in injury or loss of life.

CAUTION. Caution statements identify conditions or practices that could result in

damage to this product or other property.

Terms on the Product. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the

marking.

WARNING indicates an injury hazard not immediately accessible as you read the

marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

CAUTION

Refer to Manual

WARNING

High Voltage

Protective Ground

(Earth) Terminal

viii

TMSSC1 604 Pin Socket Hardware Support

Page 13

Service Safety Summary

Only qualified personnel should perform service procedures. Read this Service

Safety Summary and the General Safety Summary before performing any service

procedures.

Do Not Service Alone. Do not perform internal service or adjustments of this

product unless another person capable of rendering first aid and resuscitation is

present.

Disconnect Power. To avoid electric shock, switch off the instrument power, then

disconnect the power cord from the mains power.

Use Care When Servicing With Power On. Dangerous voltages or currents may

exist in this product. Disconnect power, remove battery (if applicable), and

disconnect test leads before removing protective panels, soldering, or replacing

components.

To avoid electric shock, do not touch exposed connections.

TMSSC1 604 Pin Socket Hardware Support

ix

Page 14

Service Safety Summary

TMSSC1 604 Pin Socket Hardware Support

x

Page 15

Preface

Manual Conventions

This instruction manual contains specific information about the

TMSSC1 604 Pin Socket microprocessor support package and is part of a set of

information on how to operate this product on compatible Tektronix logic

analyzers.

If you are familiar with operating microprocessor support packages on the logic

analyzer for which the TMSSC1 604 Pin Socket support was purchased, all you

need is this instruction manual to set up and run the support package.

If you are not familiar with operating microprocessor support packages, you need

to supplement this instruction manual with information on basic operations from

the Tektronix logic analyzer online help to set up and run the support package.

This manual uses the following conventions:

H A pound sign (#) following a signal name indicates an active low signal.

H The phrase “information on basic operations” refers to basic information in

the logic analyzer online help.

H The terms “Master” and “Slave” refer to modules that are located in

numbered slots (see Figure 1--1 on page 1--2).

TMSSC1 604 Pin Socket Hardware Support xi

Page 16

Preface

Contacting Tektronix

Phone 1-800-833-9200*

Address Tektronix, Inc.

Department or name (if known)

14200 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

USA

Web site www.tektronix.com

Sales support 1-800-833-9200, select option 1*

Service support 1-800-833-9200, select option 2*

Technical support Email: techsupport@tektronix.com

1-800-833-9200, select option 3*

6:00 a.m. -- 5:00 p.m. Pacific time

* This phone number is toll free in North America. After office hours, please leave a

voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the

Tektronix web site for a list of offices.

xii

TMSSC1 604 Pin Socket Hardware Support

Page 17

Getting Started

Page 18

Page 19

Getting Started

This section contains information about the TMSSC1 604 Pin Socket hardware

support product and connecting the logic analyzer to the target system.

Support Package Description

The probe adapter is an interposer design that allows the logic analyzer to acquire

data from a microprocessor in the operating environment with little effect on the

target system. To accomplish this the probe adapter is connected to the target

system, and then the microprocessor connects to the probe adapter. Signals from

the microprocessor based system flow through the probe adapter and the probe

cables and to the logic analyzer.

The TMSSC1 604 Pin Socket Hardware support product includes the following:

H PUB32G8 timing and limited state software

H TMSSC1 604 Pin Socket probe adapter

NOTE. This probe adapter is also compatible with the TMS117 IA32G8 software

support product that provides timing and disassembly analysis capabilities,

synchronous transactions, and instruction decoding. This software support

product is available only to customers with a valid, restricted, secret nondisclosure agreement (RS-NDA) with Intel.

Contact your Tektronix representative if you would like to acquire this software.

Logic Analyzer Software Compatibility

The software label on the disc states that version 4.2 SP1 of the logic analyzer

software is compatible with the TMSSC1 604 Pin Socket product.

TMSSC1 604 Pin Socket Hardware Support 1--1

Page 20

Getting Started

Logic Analyzer Configuration

The logic analyzer configuration require a minimum of four, 136 channel,

235 MHz merged modules and a minimum of sixteen P6860 Probes.

The modules must be configured and merged as shown in Figure 1--1 on

page 1--2. The memory depth is chosen automatically based on the shallowest

memory depth of the modules.

Labeling Probes

S

L

A

V

E

4

Figure 1--1: Configuration of the master and slave modules

The term master module refers to the middle module of a 5-wide module merge.

The term slave module refers to the modules directly to the left or right of the

master module of a 4 or 5-wide module merge. Figure 1--1 shows the configuration for a 4 or 5-wide module merge.

The probe adapter relies on the default channel mapping and labeling scheme for

the probes. Apply labels using the instructions described in P6860 High Density

Logic Analyzer Probe Label Instructions manual, Tektronix 071-1123-XX. This

manual can be accessed from the Tektronix.com web site or from the logic

analyzer online help.

S

L

A

V

E

2

M

A

S

T

E

R

S

L

A

V

E

1

S

L

A

V

E

3

1--2

P6860 Probes

You can use a TLA7AX 235 MHz logic analyzer module and the P6860 probes

to connect to the TMSSC1 604 Pin Socket probe adapter.

Refer to the P6810, P6860, and P6880 Logic Analyzer Probes Instruction

manual, Tektronix 071-1059-XX, for more information. You can access this

manual from the Tektronix.com web site. You can also find information about

these probes in the logic analyzer online help.

TMSSC1 604 Pin Socket Hardware Support

Page 21

Options and Accessories

Optional and standard accessories are listed in the Replaceable Parts List on page on

page 6--4

Probe Adapter Review

Review the information on basic operations of microprocessor support packages

that is included with each logic analyzer product. Each logic analyzer includes

information that describes how to perform tasks common to support packages on

that platform. This information can be in the form of the logic analyzer online

help, an installation manual, or a user manual.

Also, review electrical, environmental, and mechanical specifications in the

Specifications section on page 3--1 as they pertain to the target system, as well as

the following descriptions of other TMSSC1 604 Pin Socket hardware product

information.

Getting Started

System Clock Rate

Acquisition before Reset

BCLK

Data Bus

Address Bus

Disabling the Cache

The TMSSC1 604 Pin Socket hardware support can acquire data from the

604 Pin Socket microprocessor operating at BCLK speeds of up to 167 MHz.

The clock rate is not guaranteed for prototype shipment of the product.

Contact the Tektronix sales representative for current information on the fastest

devices supported.

The data acquired by the logic analyzer will be inaccurate, if this data is acquired

just before a power on Reset signal is observed by the target system.

Refer to the BCLK specifications and restrictions listed in Table 3--3 on

page 3--6, in the Specifications chapter.

The TMSSC1 604 Pin Socket probe adapter supports only a quad-pumped data

bus.

The TMSSC1 604 Pin Socket probe adapter supports only a double-pumped

address bus.

The cache bus is not monitored; therefore, the cache must be disabled. Disabling

the cache makes all instruction prefetches visible on the bus so that they are

acquired and displayed and correctly disassembled.

TMSSC1 604 Pin Socket Hardware Support

1--3

Page 22

Getting Started

Configuring the Probe Adapter

You can configure the probe adapter by using the jumper information in

Table 1--1. Figure 1--2 shows the location of all jumpers.

HALF Vtt

HALF Vtt Jumper

Frequency

Select Jumper

Frequency select

J10, J11, J12

Figure 1--2: Jumper locations on the preprocessor unit

Place the jumper in the pin 1--2 position to reference the following signals to 1/2

Vtt:

A20M#, INIT#, IGNNE#, LINT1, LINT0, SLP#, SMI#, STPCLK#

Place the jumper in the pin 2--3 position to reference the preceding signals to

GTLREF. Refer to your chipset for more information.

For the Frequency Select Jumper settings, see Table 1--1 for the appropriate

operating frequency.

Table 1--1: Frequency select jumpers

Frequency S1 (J10) S2 (J11) S3 (J12)

140 -- 230 MHz 1--2 1--2 1--2

70 -- 140 MHz 2--3 2--3 1--2

1--4

TMSSC1 604 Pin Socket Hardware Support

Page 23

Table 1--1: Frequency select jumpers (Cont.)

Frequency S3 (J12)S2 (J11)S1 (J10)

30 -- 70 MHz 1--2 2--3 1--2

20 -- 30 MHz 1--2 2--3 2--3

Connecting the Logic Analyzer to a Target System

CAUTION. To prevent static damage to the microprocessor, the probe adapter, the

probes, and the module, you must handle components only in a static-free

environment.

Always wear a grounding wrist strap, heel strap, or similar device while

handling the microprocessor and probe adapter.

Before you connect the probe adapter to the target system, connect the P6860

probes to the logic annalyzer modules. For reference, Figure 1 --3 shows the

module configuration for the Master and Slave modules.

Getting Started

S

L

A

V

E

4

Figure 1--3: Module configuration for the master and slave modules

The target system must allow clearance for the probe adapter. Refer to the

dimensions on page 3--9 for the required clearances.

S

L

A

V

E

2

M

A

S

T

E

R

S

L

A

V

E

1

S

L

A

V

E

3

TMSSC1 604 Pin Socket Hardware Support

1--5

Page 24

Getting Started

WARNING. To prevent harm to yourself or damage to the preprocessor unit, do

not open the preprocessor unit, except to remove the probe adapter cables or

exchange a fan. There are no operator serviceable parts inside the preprocessor

unit. Refer servicing of internal parts in the preprocessor unit to Tektronix

authorized personnel only. External parts may be replaced by qualified service

personnel.

Tools Required

The following are the required tools:

H Flat-bladed screwdriver (0.1 inch tip width) to remove the heat sink retention

module

H POZIDRIV (PZ0) screwdriver to attach probe head to target system.

Optional Tools. A torque wrench helps to ensure reliable connections by meeting

the nominal torque values listed in these instructions.

CAUTION. To prevent static damage to the microprocessor, the probe adapter, the

probes, and the module, handle components only in a static-free environment.

Always wear a grounding wrist strap, heel strap, or similar device while

handling the microprocessor and probe adapter.

Read the following general instructions before removing parts.

NOTE. For storage and shipping, retain the cardboard cartons and packing

material that is shipped with the probe adapter.

1--6

Use the following steps to connect the logic analyzer to the target system:

1. Power off the target system. It is not necessary to power off the logic

analyzer.

2. Power off any probe adapters that may be attached to your target system.

3. To discharge any static electricity, touch the ground connector located on the

logic analyzer.

4. On the target system, remove the heat sink from the microprocessor and set

the heat sink aside.

5. Disengage the ZIF socket on the target system.

6. Remove the microprocessor from the target system by following the removal

procedure from the microprocessor vendor.

TMSSC1 604 Pin Socket Hardware Support

Page 25

Getting Started

7. Remove the heat sink retention mechanism from the target system by

removing the center post from each rivet (see Figure 1 --4).

Center post

Heat sink

retention

mechanism

Target

system

Figure 1--4: Remove the heat sink retention mechanism from the target system

CAUTION. To prevent damage to the probe head and pins, always handle the

probe head carefully and use care to properly align the probe head pins to the

ZIF socket on the target system. Also, reinstall the pin protector to the bottom of

the probe head when the probe head is not in use.

8. Remove the tape and the pin protector board from the bottom of the probe

head.

TMSSC1 604 Pin Socket Hardware Support

1--7

Page 26

Getting Started

9. Connect the microprocessor to the probe head using the clear plastic

alignment guide shown in Figure 1--5. Align the microprocessor pin A1

indicator with the socket pin A1 indicator, and press the microprocessor into

place as shown in Figure 1--5.

Metal bracket

(do not remove)

Probe head

Microprocessor

Clear plastic

Pin A1

alignment guide

Figure 1--5: Connect the microprocessor

NOTE. To maintain stability on the probe head, do not remove the metal brackets.

1--8

TMSSC1 604 Pin Socket Hardware Support

Page 27

Getting Started

10. Connect the probe head to the target system. You must visually verify proper

pin alignment between the probe head pins and the socket on the target

system.

Probe head

White base

bracket

Open the

lever

604 Pin socket

Pin A1

Target System with

bottom backing plate

Figure 1--6: Connect the probe head to the 604 Pin Socket

TMSSC1 604 Pin Socket Hardware Support

1--9

Page 28

Getting Started

11. Activate the ZIF socket on the target system.

Push lever

down

Figure 1--7: Engage the ZIF lever

1--10

TMSSC1 604 Pin Socket Hardware Support

Page 29

Getting Started

12. Slide the air-cooled heat sink on top of the microprocessor as shown in

Figure 1--8.

You may need to use thermal grease for better contact between the heat sink

and the microprocessor. For thermal requirements, refer to the microproces-

sor vendor information.

13. Thread the supplied standoffs onto the four screws

14. Slide each screw and standoff assembly through the heat-sink base and attach

to the pem nut on the bottom of the target system. Torque the screws to

8 in-lbs (see Figure 1--8).

Screws with

standoffs (4)

heat sink

Figure 1--8: Connect the heat sink and probe head to the target system

15. Connect the fan connector to the target system.

TMSSC1 604 Pin Socket Hardware Support

Target System

1--11

Page 30

Getting Started

Removing the Probe Head

from the Target System

To remove the probe head from the target system, follow these steps:

1. Power off the target system and the preprocessor unit. It is not necessary to

power off the logic analyzer.

2. Disconnect the fan plug from the target system.

3. Remove the four screws and standoffs from the probe adapter and target

system (see Figure 1--8 on page 1--11).

4. Remove the heat sink from the microprocessor (see Figure 1 --8 on

page 1--11).

5. Disengage the ZIF socket on the target system.

6. Disconnect the probe head from the 604 Pin Socket on the target system.

7. Install the pin-protector cover to the bottom of the probe head pins.

8. Using a flat-bladed screwdriver, remove the microprocessor from the probe head

by gently prying up all four corners of the microprocessor (see Figure 1--9).

Twist the microprocessor off the

extraction fixture on all four side.

1--12

Figure 1--9: Remove the microprocessor from the probe head

9. Disconnect the preprocessor unit from the Tektronix logic analyzer.

10. Store the probe adapter.

TMSSC1 604 Pin Socket Hardware Support

Page 31

Getting Started

Connect the P6860 Probes

to the Preprocessor Unit

You can configure the P6860 Probes for timing or disassembly software

functions. For reference, Figure 1--10 shows the P6860 connectors and the

preprocessor unit.

NOTE. For more detailed information on how to attach a P6860 probe to your

connector, refer to the logic analyzer online help or the P6860 probe manual

listed on page 1--2. Then connect the probes for the minimum configuration for

disassembly and timing or only timing support, as described on page 1--14.

Figure 1--10: Connect the probes

TMSSC1 604 Pin Socket Hardware Support

1--13

Page 32

Getting Started

Figure 1--11 shows the configuration for the Master and Slave modules.

S

L

A

V

E

4

Figure 1--11: Module configuration of the master and slave modules

Following is the minimum configuration for timing support.

1. Match the A, D, C, and E probes from the Master module with the corre-

sponding M_ D3/D2 and A3/A2, M_D1/D and A1/A0, M_C1/C0 and C3/C2,

and M_E3/E2 and E1/E probe connector labels on the preprocessor unit.

Align the pin 1 indicator on the probe label with the Pin 1 indicator of the

connector on the preprocessor unit. Connect the probes.

2. Repeat step 1 to make probe connections between Slave1 through Slave3 and

the preprocessor unit.

S

L

A

V

E

2

M

A

S

T

E

R

S

L

A

V

E

1

S

L

A

V

E

3

1--14

Applying Power

CAUTION. To prevent damage to the probe and preprocessor unit, you must

always position the probes perpendicular to the foot print on the PCB. Incorrect

handling of the P6860 probe while connecting to or disconnecting from the

preprocessor unit can damage the probe.

To apply power to the probe adapter and target system, follow these steps:

WARNING. To prevent personal injury or damage to the preprocessor unit, there

are no operator serviceable parts inside the cover of the preprocessor unit. Refer

servicing of parts in the preprocessor unit to Tektronix authorized personnel only.

1. Check that the power switch on the preprocessor unit is in the off position. If

power off, the zero (0) is visible on the power switch.

2. Plug the AC power cord into the IEC connector on the back of the preproces -

sor unit.

TMSSC1 604 Pin Socket Hardware Support

Page 33

Getting Started

3. Plug the AC power cord into an electrical outlet that you know is working

properly.

4. Power on the preprocessor unit. A green, power on LED lights on the front

of the preprocessor unit, indicating that the probe adapter is active.

5. Power on the target system.

Removing Power

To remove power from the target system and the probe adapter, follow these

steps:

1. Power off the target system.

2. Power off the probe adapter at the back of the preprocessor unit.

Verifying Probe Operation

If you have trouble using the probe adapter to acquire data from the target

system, use the following check list to ensure that the probe adapter and

probe-head cables are working correctly.

WARNING. To prevent harm to yourself or damage to the preprocessor unit, do

not open the preprocessor unit, except to verify probe head cable connections.

There are no operator serviceable parts inside the preprocessor unit. Refer

servicing of internal parts in the preprocessor unit to Tektronix authorized

personnel only. External parts may be replaced by qualified service personnel.

1. Check that power is supplied to the preprocessor unit by observing the green

LED on the front of the case. If the LED is not lighted:

H Check that the power switch on the back of the preprocessor unit is

powered on. If powered off, a zero (0) is visible on the switch.

H Check that the AC power cord is plugged into an electrical outlet that

you know is working properly.

H Check if the fans in preprocessor unit are rotating.

H If the LED is still not lighted, call a Tektronix application engineer.

2. Check that signals are passing through the probe connectors by using the

following procedure:

a. Go to the setup menu and select “show activity”.

TMSSC1 604 Pin Socket Hardware Support

1--15

Page 34

Getting Started

Storage

b. Visually verify from the display that signals are transitioning on each

probe connector and that the activity is on all used channels that are not

demux destinations.

c. If the channels never transition:Check the probe connections on top of

the preprocessor unit. Refer to the P6860 instruction manual (see page

1--2) for more information about connecting the P6860 probes.

If the preceding bulleted items did not correct the problem, replace the

existing probe with a new probe.

d. If the signals are still not transitioning, disconnect the probe from the

socket in the preprocessor unit. Then plug that probe into a socket that is

transitioning signals.

The storage instructions describe short- and long-term storage of the probe head,

cables, and preprocessor unit.

Short-Term Storage

Long-Term Storage

CAUTION. To prevent damage to the sensitive probe-head cables, dress the cables

to not pinch or contact any sharp objects. When you fold the cables use a

minimum radius of 0.25 (0.64 cm) at the fold.

For short-term storage follow these steps:

1. Power off the probe adapter. You can leave the logic analyzer powdered on.

2. Disconnect the probe head from the target system (See page 1--12).

3. Wrap pink (antistatic) bubble wrap around the probe head, and store the

probe head with the preprocessor unit.

For long-term storage use the existing cardboard carton and packaging, and

follow these steps:

1. Power off the probe adapter. You can leave the logic analyzer powdered on.

2. Disconnect the preprocessor unit from the logic analyzer by removing the

P6860 probes from the top of the preprocessor unit.

3. Unplug the AC power cord from the IEC connector on the back of the

preprocessor unit.

1--16

4. Disconnect the probe head from the target system (see page 1--12).

TMSSC1 604 Pin Socket Hardware Support

Page 35

Getting Started

5. Place the foam end caps on both sides of the preprocessor unit. The

depression on the foam end caps are in the up position.

6. Place the preprocessor unit inside the cardboard carton.

7. Place the pink-foam panel on top of the end caps.

8. Place the probe head in the center cutout of the pink-foam panel.

CAUTION. To prevent damage to the sensitive probe head cables, dress the cables

so they are not pinched or contacting any sharp objects. When you fold the

cables use a minimum of 0.25 (0.64 cm) radius at the fold.

9. Place other accessories in the appropriate cutouts.

10. Place the cardboard accessory tray containing the P6860 probes on top of the

pink-foam panel. Close the carton.

Care and Maintenance

External Cleaning Only

Before cleaning this product, read the following information.

CAUTION. Static discharge can damage the microprocessor, the probe adapter,

the probes, and the module. To prevent static damage, you must handle components only in a static-free environment.

The probe adapter, consisting of the probe head and preprocessor unit, does not

require scheduled or periodic maintenance. However, to keep good electrical

contact and efficient heat dissipation, keep the probe adapter free of dirt, dust,

and contaminants. When not in use, store the probe adapter in the original

shipping bags and cardboard carton (see Storage on page 1--16).

Clean dirt and dust with a soft bristle brush. For more extensive cleaning, use

only a damp cloth moistened with deionized water; do not use any other chemical

cleaning agents.

WARNING. To prevent harm to yourself or damage to the preprocessor unit, do

not open the preprocessor unit for cleaning. There are no operator serviceable

parts inside the preprocessor unit. Refer servicing of internal parts in the

preprocessor unit to Tektronix authorized personnel only. External parts may be

replaced by qualified service personnel.

TMSSC1 604 Pin Socket Hardware Support

1--17

Page 36

Getting Started

Shipping the Probe Adapter

To commercially transport the TMSSC1 604 Pin Socket probe adapter, package

as follows:

1. Use the existing cardboard shipping carton and cushioning material.

If the existing shipping carton is not available, use a double-walled,

corrugated cardboard shipping carton that allows a 3 inch (7.62 cm)

minimum on all sides of the product.

2. If you are shipping the probe adapter to a Tektronix service center for

Warranty service, attach a tag to the probe adapter showing the following:

H Owner’s name and address

H Name of a person who can be contacted

H Probe adapter type and serial number

H Description of the problem

3. Using nonstatic generating tape, tape the pin-protector board to the bottom of

the pin header.

4. Place the probe head in a static shielding bag, close with nonstatic generating

tape, and then lay the probe head on top of the preprocessor unit (see Figure

1--12 on page 1--19).

NOTE. DO NOT place the probe head in the large static shielding bag with the

processor unit.

1--18

TMSSC1 604 Pin Socket Hardware Support

Page 37

Figure 1--12: Place the probe head in a static shielding bag

Getting Started

5. Place the preprocessor unit inside a static shielding bag.

6. Place the foam end caps on both sides of the preprocessor unit and the

preprocessor unit inside the cardboard carton (see Figure 1--13).

Figure 1--13: Place the end caps on the preprocessor

TMSSC1 604 Pin Socket Hardware Support

1--19

Page 38

Getting Started

7. Place the pink-foam panel on top of the end caps (see Figure 1--14).

8. Place the probe head in the center cutout of the pink-foam panel.

CAUTION. To prevent damage to the sensitive probe head cables, you must dress

the cables so they are not pinched or contacting any sharp objects. When you

fold the cables use a minimum of 0.25 (0.64 cm / 0.25 inch) radius at the fold.

1--20

Figure 1--14: Place the probe head into the square cutout

9. Place other accessories in the appropriate cutouts.

10. Lay the pink foam spacer panel on top of the probe head.

11. If you are also returning the probe cables, place the cardboard accessory tray

containing the P6860 probes on top of the pink foam panel.

12. Close and tape the cardboard carton.

TMSSC1 604 Pin Socket Hardware Support

Page 39

Operating Basics

Page 40

Page 41

Setting Up the Software

The following information is covered in this section:

H Acquiring data

H Changing how data is displayed

Information on general tasks and functions for the logic analyzer is described in

the logic analyzer online help.

Before you acquire and display data, you need to load the software and specify

the setup as described in this section. The TMSSC1 604 Pin Socket microprocessor software provides default values for the setup, but you can change them as

needed.

You need to purchase the TMS117 IA32G8 software support product from your

Tektronix sales representative if you are interested in disassembling data.

Installing the Software

NOTE. Before you install any software, it is recommended you verify that the

microprocessor support software is compatible with the logic analyzer software.

To install the TMSSC1 604 Pin Socket software on your Tektronix logic

analyzer, follow these steps:

1. Insert the floppy disk in the disk drive.

2. Click the Windows Start button, point to Settings, and click Control Panel.

3. In the Control Panel window, double-click Add/Remove Programs.

4. Follow the instructions on the screen for installing the software from the

floppy disk.

To remove or uninstall software, follow the above instructions except select

Uninstall. You must close all windows before you uninstall any software.

The TMSSC1 604 Pin Socket software installs the IA32G8_T setup file. This

setup file has custom clocking options.

TMSSC1 604 Pin Socket Hardware Support

2--1

Page 42

Setting Up the Support

Custom Clocking

The TMSSC1 604 Pin Socket software installs the PUB32G8 setup file. This

setup provides timing and state support only for the 604 Pin Socket microprocessor. This setup file offers different state speeds and custom clocking options. All

channels are displayed as active high.

Options

A special custom clocking program is loaded into the module every time you

load the setup file from the TMSSC1 604 Pin Socket support software.

You can change the custom clocking or state speed options by clicking the

“More...” button in the PUB32G8 setup window.

State Speed. Select the nearest state speed to your BClock frequency in the

Custom Options window (see Figure 2--1).

Figure 2--1: State Speed menu

2--2 TMSSC1 604 Pin Socket Hardware Support

Page 43

Channel Group Definitions

The TMSSC1 604 Pin Socket software automatically defines channel groups for

the following installed IA32G8_T software setup. Following is a list all the

channel group definition tables. The channel group definition tables are located

in the Reference section beginning on page 4--25.

The channel groups are listed below:

Address1 ASTB1

Address0 ASTB

Data3 DSTB3

Data2 DSTB2

Data1 DSTB1

Data DSTB0

DataInvert DataStrobe

DataParity DataCtrl

Arbitrate Request

Execution Error

Address AddrStrobe

AddrParity Snoop

Response Compatible

Diagnostic Misc

VID

Setting Up the Support

Channel Assignments

Channel assignments tables and the corresponding support signals are located in

the Reference section beginning on page 4--1.

TMSSC1 604 Pin Socket Hardware Support

2--3

Page 44

Setting Up the Support

2--4

TMSSC1 604 Pin Socket Hardware Support

Page 45

Specifications

Page 46

Page 47

Specifications

Circuit Description

This section contains specifications for the TMSSC1 604 Pin Socket hardware

support.

The TMSSC1 604 Pin Socket probe adapter hardware uses a custom ASIC to

preprocess all signals on the IA32G8 microprocessor before the signals are

captured by the logic analyzer. The custom ASIC performs the following

functions:

H Latches signals within a narrow valid window

H Demultiplexes double-pumped, source-synchronous signals

H Deterministically synchronizes source-synchronous signals to BCLK

Latched Operation

The ASIC latches all signals on the IA32G8 microprocessor. The latched signals

are processed in the ASIC according to their type. Following is a description of

each type:

4x Quad-Pumped Signals. These signals include D[63:00]# and DP[3:0]#. The

ASIC latches these signals using their dedicated strobes, STBP[3:0] and

STBN[3:0], and then performs four-way demultiplexing on these signals. The

ASIC also inverts the appropriate signals when the DBI[3:0] signals are active.

2x Double-Pumped Signals. These signals include A[53:03]# and AP[1:0]#. The

module latches these signals using their dedicated strobes, ASTB[1:0], and then

performs two-way demultiplexing on these signals.

1x Common-Clock Signals. These signals include all of the remaining front-side

bus signals. The module latches these signals using the rising edge of BCLK.

TMSSC1 604 Pin Socket Hardware Support

3--1

Page 48

Specifications

Derived Signals

Signal Probing

Bus Tracking Logic

The TMSSC1 604 Pin Socket probe adapter hardware derives several custom

signals from the front-side bus signals captured by the ASIC. These signals are

used by the logic analyzer support software to provide clocking, transaction

phase linking, and disassembly. Following is a description of these custom

signals:

PHASE_D. This signal can be used by the logic analyzer to store only bus cycles

that contain active information. The PHASE_D signal is asserted when any of the

following signals are asserted: ADS#, DRDY#, INIT#, RESET#, RS[2:0]#, and

SNOOP_D.

TRACK_ERR_D. This signal is asserted whenever the request or snoop counters

exceed their maximum or a minimum value. This signal is also asserted when

ADS# has been observed active for two clock cycles in a row.

The 604 Pin Socket probe adapter uses passive series isolation to acquire data.

The 604 Pin Socket probe adapter uses a bus tracking PAL to aid the disassembly

software in linking various bus phases.

Common Clock

The IA32G8 software allows disassembly from a data bus operating at the

common clock rate specified in Table 3--1. The setup and hold sample points are

set to default timing numbers based on FSB specifications.

3--2 TMSSC1 604 Pin Socket Hardware Support

Page 49

Loading Diagrams

Specifications

BGA604 Socket microprocessor

Signal 1

Nocona processor

Signal 2

60 Ω

~6350 mils

926 ps

300 Ω

R5

300 Ω

R5

C7

0.5 pF

C8

0.5 pF

75 Ω

~48’’

5.97 ns

C5

0.5 pF

60 Ω

~6350 mils

926 ps

Mated

samtec

R2

270 Ω

BGA604 Socket

In 1

In 2

R2

270 Ω

C6

0.5 pF

LIF socket

VSS

~628 mils

C3

0.5 pF

C10

0.5 pF

Out 1

Out 2

60 Ω

80 ps

C4

0.5 pF

75 Ω

~1350 mils

197 ps

C1

0.5 pF

60 Ω

~628 mils

80 ps

75 Ω

R4

C2

0.5 pF

BGA604 Pin header

In 1

In 2

Receiver

Out 1

Pin header

Out 2

VSS

75 Ω

~48’’

5.97 ns

Mated

samtec

Figure 3--1: Electrical load model for typical signals

TMSSC1 604 Pin Socket Hardware Support

C10

0.5 pF

75 Ω

~1350 mils

197 ps

Receiver

75 Ω

R4

3--3

Page 50

Specifications

TF2_1

K12= 0.082

L1=1.685 n

Signal in 1

Signal in 2

Vss

L2=1.685 n

+

+

C2

0.44 p

C1

0.44 p

+

Signal out 1

Signal out 2

C3

0.44 p

Vss

Figure 3--2: Pin header electrical load model for typical signals

TF2_1

K12= 0.318

L1=5.20 n

L2=5.20 n

Signal in 1

Signal in 2

Vss

+

C1

0.66 p

+

C2

1.3 p

+

Signal out 1

Signal out 2

C3

1.3 p

Vss

Figure 3--3: LIF electrical load model for typical signals

C3

0.7 p

L1

3.2 n

Signal Out 2

C2

0.5 p

Signal in 1

R1

10 m

C4

0.5 p

Figure 3--4: Mated Samtec model

750 Ω

Signal in 1

1.5 nH

750 Ω

1.5 nH

1.5 pF

0.1 Ω

750 Ω

Figure 3--5: BCLK Receiver

3--4

TMSSC1 604 Pin Socket Hardware Support

Page 51

Specification Tables

Specifications

These specifications are for a probe adapter connected between a compatible

Tektronix logic analyzer and a target system. Signal voltage swing in your target

system must be at least 300 mV

around the GTL+ reference voltage.

p-p

NOTE. The functionality and specifications are not guaranteed for the prototype

product.

Table 3--1 lists the electrical requirements of the target system. Table 3--2 lists the

electrical requirements for the power supply that provides power to the 604 Pin

Socket probe adapter. Table 3--3 lists the BCLK timing and electrical specifications. Table 3--4 lists the environmental specifications.

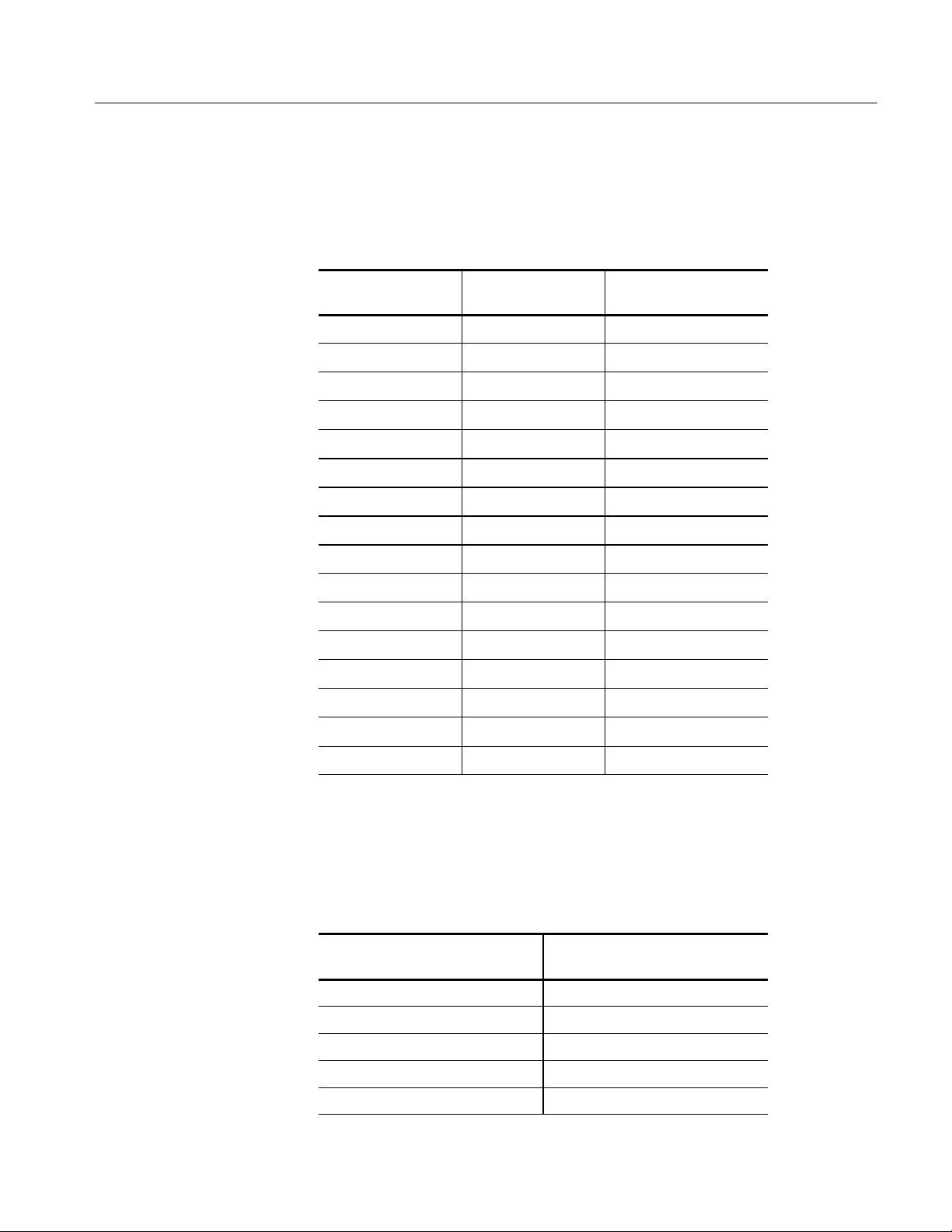

Table 3--1: Electrical specifications for the target system

Characteristics Requirements

DC power requirements

Voltage, V

Current, V

Common clock rate Maximum 167 MHz

Common clock capture

Window 725 ps

T

su

T

hd

2x Source Synchronous capture

Window 725 ps

T

su

T

hd

4x Source Synchronous capture

Window 500 ps

T

su

T

hd

cc

REF

1.05 V ᐔ5%

I maximum <2 mA, I typical <1 mA

975 ps

--250 ps

375 ps

350 ps

200 ps

300 ps

TMSSC1 604 Pin Socket Hardware Support

3--5

Page 52

Specifications

Table 3--2: Electrical specifications for the AC input to the preprocessor unit

Characteristic Description

Input Voltage rating 100 -- 240 VAC CAT II

Input Frequency Rating 50 -- 60 Hz

Input Current Rating 6.0 A maximum

Table 3--3: BCLK timing and electrical specifications

Characteristics Minimum Maximum Units Notes

Vin(lo) min -- V

Vin(hi) max V

+125 mV -- V

REF

Duty Cycle 45 55 %

t

lh

t

hl

-- 1.25 ns Monotonically increasing

-- 1.25 ns Monotonically decreasing

--125 mV V

REF

Table 3--4: Environmental specifications

Characteristic

Temperature

Maximum operating +50 °C (+122 °F)

Minimum operating 0 °C (+32 °F)

Nonoperating -- 5 5 °Cto+75°C(--67°F to +167 °F)

Humidity 10 to 95% relative humidity, noncondensing

Altitude

Operating 3 km (10,000 ft) maximum

Nonoperating 15 km (50,000 ft) maximum

Electrostatic immunity The probe adapter is static sensitive

Required airflow clearances

for the preprocessor unit

Sides 5.08 cm (2 in)

Back 7.62 cm (3 in)

1

Designed to meet Tektronix standard 062-2847-00 class 5.

2

Not to exceed microprocessor thermal considerations. Customer supplied cooling

might be required across the CPU.

1

Description

2

3--6

TMSSC1 604 Pin Socket Hardware Support

Page 53

Table 3--5: Certifications and compliances

g

gyp

Category Standards or description

Specifications

EC Declaration of Conformity -EMC

EC Declaration of Conformity -Low Voltage

U.S. Nationally Recognized

Testing Laboratory Listing

Canadian Certification CAN/CSA C22.2 No. 1010.1 Safety requirements for electrical equipment for measurement,

Additional Compliance ANSI/ISA S82.01:1994 Safety standard for electrical and electronic test, measuring,

Installation (Overvoltage)

Category Descriptions

Pollution Degree Descriptions A measure of the contaminates that could occur in the environment around and within a product.

Equipment Type Test and measuring

Safety Class Class 1 (as defined in IEC 61010-1, Annex H) -- grounded product

Pollution Degree Descriptions Pollution Degree 2 (as defined in IEC 61010-1). Note: Rated for indoor use only.

Meets intent of Directive 89/336/EEC for Electromagnetic Compatibility. Compliance was

demonstrated to the following specifications as listed in the Official Journal of the European

Communities:

EN 61000--3--2 AC power line harmonic emissions

Compliance was demonstrated to the following specification as listed in the Official Journal of the

European Communities:

Low Voltage Directive 73/23/EEC, amended by 93/68/EEC

EN 61010-1/A2:1995 Safety requirements for electrical equipment for measurement

control and laboratory use.

UL3111-1 Standard for electrical measuring and test equipment.

control, and laboratory use.

controlling, and related equipment.

IEC61010-1/A2:1995 Safety requirements for electrical equipment for measurement,

control, and laboratory use.

Terminals on this product may have different installation (overvoltage) category designations. The

installation categories are:

CAT III Distribution-level mains (usually permanently connected). Equipment at this level is

typically in a fixed industrial location.

CAT II Local-level mains (wall sockets). Equipment at this level includes appliances, portable

tools, and similar products. Equipment is usually cord-connected.

CAT I Secondary (signal level) or battery operated circuits of electronic equipment.

Typically the internal environment inside a product is considered to be the same as the external.

Products should be used only in the environment for which they are rated.

Pollution Degree 2 Normally only dry, nonconductive pollution occurs. Occasionally a

temporary conductivity that is caused by condensation must be

expected. This location is a typical office/home environment.

Temporary condensation occurs only when the product is out of

service.

TMSSC1 604 Pin Socket Hardware Support

3--7

Page 54

Specifications

92.71 mm

(3.650 in)

Dimensions

78.74 mm

(3.100 in)

56.49 mm

(2.224 in)

38.10 mm

(1.500 in)

Figure 3--6 shows the dimensions of the TMSSC1 604 Pin Socket probe head.

88.90 mm

(3.500 in)

81.28 mm

(3.200 in)

Figure 3--6: Dimensions of the TMSSC1 604 Pin Socket probe head

3--8

TMSSC1 604 Pin Socket Hardware Support

Page 55

Specifications

Figure 3--7 shows the dimensions of the preprocessor unit.

CAUTION. T o prevent damage to the circuitry in the preprocessor unit, you must

observe the required clearances in T able 3--4 on page 3--6 (clearances are not shown

in Figure 3--7).

474.32 mm

(18.674 in)

425.45 mm

(16.750 in)

420.37 mm

(16.550 in)

139.70 mm

(5.500 in)

Figure 3--7: Dimensions of the preprocessor unit

160.27 mm

(6.310 in)

TMSSC1 604 Pin Socket Hardware Support

3--9

Page 56

Specifications

3--10

TMSSC1 604 Pin Socket Hardware Support

Page 57

Reference

Page 58

Page 59

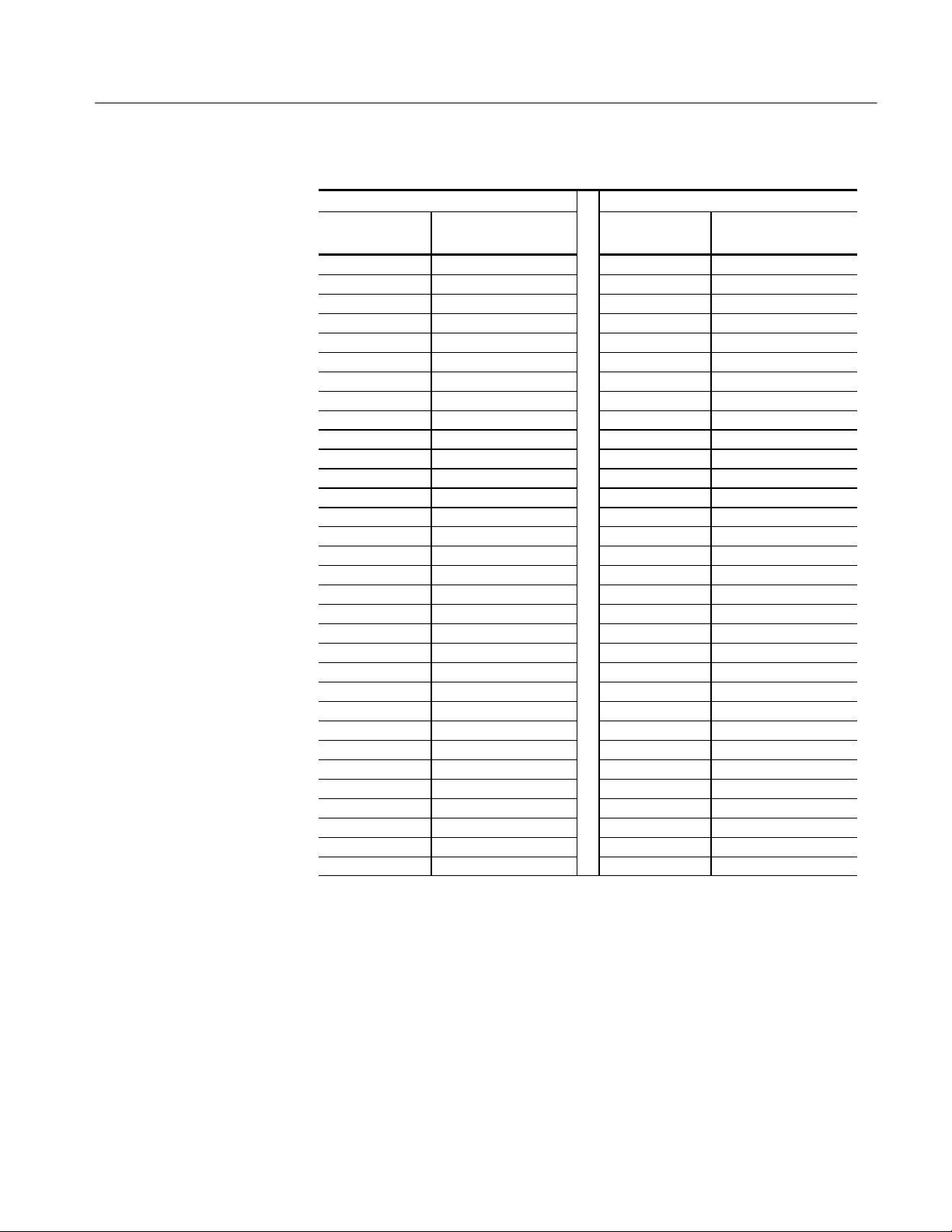

Channel Assignment Tables

This section contains the following Channel Group Assignments.

Channel assignment tables use the following conventions:

H A pound sign (#) following a signal name indicates an active low signal.

H All signals are required by the support unless indicated otherwise.

H Channels are shown starting with the most significant bit (MSB) descending

to the least significant bit (LSB).

H An @ sign indicates that this signal is derived on the probe adapter.

H The term master module refers to the middle module of a 5-wide module

merge. The term slave module refers to the modules directly to the right of

the master module of a 4 or 5-wide module merge. F igure 4--1 shows the

configuration for 4 and 5-wide merged modules.

Clock Channel

Assignments

S

L

A

V

E

4

Figure 4- 1: Configuration for master and slave modules

Tables 4--1 lists the clock channel assignments and the corresponding support

signal.

Table 4- 1: Clock channel assignments

Logic analyzer

acquisition channel

M_Clock:3 Data DBI1_T

M_Clock:2 Qual PHASE_D

S

L

A

V

E

2

M

A

S

T

E

R

Clock, Qual,

or Data

S

L

A

V

E

1

S

L

A

V

E

3

PUB32G8

support signal name

TMSSC1 604 Pin Socket Hardware Support

4- 1

Page 60

Reference: Channel Assignment Tables

Table 4- 1: Clock channel assignments (cont.)

Logic analyzer

acquisition channel

M_Clock:1 Unused Unused

M_Clock:0 Clock BCLK

S_Clock:3 Clock ADSTB1

S_Clock:2 Data ADS_LL

S_Clock:1 Data DRDY

S_Clock:0 Clock ADSTB0

S2_Clock:3 Data D2_D27

S2_Clock:2 Data D1_DBI0

S2_Clock:1 Data D0_DBI0

S2_Clock:0 Data D2_D10

S3_Clock:3 Data D2_D33

S3_Clock:2 Data D1_DBI3

S3_Clock:1 Data D0_DBI3

S3_Clock:0 Data D2_D57

Clock, Qual,

or Data

PUB32G8

support signal name

4- 2

TMSSC1 604 Pin Socket Hardware Support

Page 61

Reference: Channel Assignment Tables

Qual Channel

Assignments

Tables 4--2 lists the Qual channel assignments and the corresponding support

signal.

Table 4- 2: Qual channel assignments

Logic analyzer

acquisition channel

Clock, Qual,

or Data

PUB32G8

support signal name

M_Qual:3 Data D49_T

M_Qual:2 Data DBI2_T

M_Qual:1 Data DPSLP

M_Qual:0 Data D03_T

S_Qual:3 Unused Unused

S_Qual:2 Unused Unused

S_Qual:1 Data STPCLK

S_Qual:0 Data ADS

S2_Qual:3 Data D3_DBI1

S2_Qual:2 Data D1_DBI1

S2_Qual:1 Data D0_DBI1

S2_Qual:0 Data D3_DBI0

S3_Qual:3 Data D3_DBI2

S3_Qual:2 Data D1_DBI2

S3_Qual:1 Data D0_DBI2

S3_Qual:0 Data D3_DBI3

Table 4--3 lists the channel assignments for the Address group and the corresponding support signal.

Table 4- 3: Master Address Module 32-channel

assignments

Logic analyzer

acquisition channel

M_A3:7 Unused

M_A3:6 Unused

M_A3:5 Unused

M_A3:4 Unused

PUB32G8

support signal name

M_A3:3 Unused

TMSSC1 604 Pin Socket Hardware Support

4- 3

Page 62

Reference: Channel Assignment Tables

Table 4- 3: Master Address Module 32-channel

assignments (Cont.)

Logic analyzer

acquisition channel

M_A3:2 Unused

M_A3:1 Unused

M_A3:0 Unused

M_A2:7 Unused

M_A2:6 Unused

M_A2:5 Unused

M_A2:4 Unused

M_A2:3 Unused

M_A2:2 Unused

M_A2:1 Unused

M_A2:0 Unused

M_A1:7 Unused

M_A1:6 Unused

M_A1:5 BINIT

M_A1:4 Unused

PUB32G8

support signal name

M_A1:3 Unused

M_A1:2 Unused

M_A1:1 VID2

M_A1:0 VID5

M_A0:7 INIT

M_A0:6 BR1

M_A0:5 FSBSEL0

M_A0:4 VID0

M_A0:3 FSBSEL1

M_A0:2 VID1

M_A0:1 VID3

M_A0:0 VID4

4- 4

TMSSC1 604 Pin Socket Hardware Support

Page 63

Reference: Channel Assignment Tables

Table 4--4 lists the channel assignments for the Control group and the corresponding support signal.

Table 4- 4: Master Control Module 32-channel assignments

Logic analyzer

acquisition channel

M_C3:7 D23_T

M_C3:6 D21_T

M_C3:5 D22_T

M_C3:4 D19_T

M_C3:3 D17_T

M_C3:2 D26_T

M_C3:1 D25_T

M_C3:0 D20_T

M_C2:7 D31_T

M_C2:6 D29_T

M_C2:5 D30_T

M_C2:4 D18_T

M_C2:3 D16_T

M_C2:2 D24_T

M_C2:1 D27_T

PUB32G8 support

signal name

M_C2:0 D28_T

M_C1:7 STBN0

M_C1:6 STBP0

M_C1:5 DP0

M_C1:4 DP1

M_C1:3 STBP1

M_C1:2 STBN1

M_C1:1 STBP3

M_C1:0 STBN3

M_C0:7 RESET

M_C0:6 SLP

M_C0:5 Unused

M_C0:4 Unused

M_C0:3 DP3

TMSSC1 604 Pin Socket Hardware Support

4- 5

Page 64

Reference: Channel Assignment Tables

Table 4- 4: Master Control Module 32-channel assignments (Cont.)

Logic analyzer

acquisition channel

M_C0:2 DP2

M_C0:1 STBN2

M_C0:0 STBP2

PUB32G8 support

signal name

Table 4--5 lists the channel assignments for the Data group and the corresponding

support signal.

Table 4- 5: Master Data Module 32-channel assignments

Logic analyzer

acquisition channel

M_D3:7 D02_T

M_D3:6 D09_T

M_D3:5 D06_T

M_D3:4 D00_T

M_D3:3 D01_T

PUB32G8 support

signal name

M_D3:2 D12_T

M_D3:1 D08_T

M_D3:0 D07_T

M_D2:7 D04_T

M_D2:6 D05_T

M_D2:5 D15_T

M_D2:4 D13_T

M_D2:3 D11_T

M_D2:2 D10_T

M_D2:1 D14_T

M_D2:0 DBI0_T

M_D1:7 Unused

M_D1:6 Unused

M_D1:5 Unused

M_D1:4 Unused

M_D1:3 Unused

4- 6

TMSSC1 604 Pin Socket Hardware Support

Page 65

Reference: Channel Assignment Tables

Table 4- 5: Master Data Module 32-channel assignments (Cont.)

Logic analyzer

acquisition channel

M_D1:2 Unused

M_D1:1 Unused

M_D1:0 Unused

M_D0:7 Unused

M_D0:6 Unused

M_D0:5 Unused

M_D0:4 Unused

M_D0:3 Unused

M_D0:2 Unused

M_D0:1 Unused

M_D0:0 Unused

PUB32G8 support

signal name

Table 4--6 lists the channel assignments for the Extend group and the corresponding support signal.

Table 4- 6: Master Extend Module 32-channel assignments

Logic analyzer

acquisition channel

M_E3:7 D55_T

M_E3:6 D48_T

M_E3:5 D54_T

M_E3:4 D58_T

M_E3:3 D63_T

M_E3:2 D59_T

M_E3:1 D56_T

M_E3:0 D61_T

M_E2:7 D50_T

M_E2:6 D53_T

M_E2:5 D52_T

M_E2:4 D60_T

M_E2:3 D62_T

PUB32G8 support

signal name

TMSSC1 604 Pin Socket Hardware Support

4- 7

Page 66

Reference: Channel Assignment Tables

Table 4- 6: Master Extend Module 32-channel assignments (Cont.)

Logic analyzer

acquisition channel

M_E2:2 D51_T

M_E2:1 D57_T

M_E2:0 DBI3_T

M_E1:7 D44_T

M_E1:6 D38_T

M_E1:5 D32_T

M_E1:4 D35_T

M_E1:3 D36_T

M_E1:2 D42_T

M_E1:1 D33_T

M_E1:0 D34_T

M_E0:7 D45_T

M_E0:6 D37_T

M_E0:5 D39_T

M_E0:4 D41_T

PUB32G8 support

signal name

M_E0:3 D43_T

M_E0:2 D47_T

M_E0:1 D40_T

M_E0:0 D46_T

Table 4--7 lists the channel assignments for the Slave Address group and the

corresponding support signal.

Table 4- 7: Slave Address Module 32-channel assignments

Logic analyzer

acquisition channel

S_A3:7 A15

S_A3:6 A14

S_A3:5 A11

S_A3:4 A07

S_A3:3 REQa2

PUB32G8 support

signal name

4- 8

TMSSC1 604 Pin Socket Hardware Support

Page 67

Reference: Channel Assignment Tables

Table 4- 7: Slave Address Module 32-channel assignments (Cont.)

Logic analyzer

acquisition channel

S_A3:2 BR0

S_A3:1 A09

S_A3:0 A03

S_A2:7 A04

S_A2:6 REQa3

S_A2:5 HITM

S_A2:4 BPRI

S_A2:3 IGNNE

S_A2:2 A20M

S_A2:1 Unused

S_A2:0 Unused

S_A1:7 BNR

S_A1:6 HIT

S_A1:5 LOCK

S_A1:4 DBSY

PUB32G8 support

signal name

S_A1:3 A12

S_A1:2 A16

S_A1:1 A10

S_A1:0 A08

S_A0:7 A05

S_A0:6 REQa1

S_A0:5 RS1

S_A0:4 RS2

S_A0:3 A13

S_A0:2 A06

S_A0:1 REQa0

S_A0:0 REQa4

TMSSC1 604 Pin Socket Hardware Support

4- 9

Page 68

Reference: Channel Assignment Tables

Table 4--8 lists the channel assignments for the Slave Control group and the

corresponding support signal.

Table 4- 8: Slave Control Module 32-channel assignments

Logic analyzer

acquisition channel

S_C3:7 A28

S_C3:6 A17

S_C3:5 A30

S_C3:4 A25

S_C3:3 A32

S_C3:2 A31

S_C3:1 A34

S_C3:0 A29

S_C2:7 A26

S_C2:6 A33

S_C2:5 A21

S_C2:4 A27

S_C2:3 A23

S_C2:2 A22

S_C2:1 Unused

PUB32G8 support

signal name

4- 10

S_C2:0 Unused

S_C1:7 A28b

S_C1:6 A17b

S_C1:5 A30b

S_C1:4 A25b

S_C1:3 A32b

S_C1:2 A31b

S_C1:1 A34b

S_C1:0 A29b

S_C0:7 A26b

S_C0:6 A33b

S_C0:5 A21b

S_C0:4 A27b

S_C0:3 A23b

TMSSC1 604 Pin Socket Hardware Support

Page 69

Reference: Channel Assignment Tables

Table 4- 8: Slave Control Module 32-channel assignments (Cont.)

Logic analyzer

acquisition channel

S_C0:2 A22b

S_C0:1 Unused

S_C0:0 Unused

PUB32G8 support

signal name

Table 4--9 lists the channel assignments for the Slave Data group and the

corresponding support signal.

Table 4- 9: Slave Data Module 32-channel assignments

Logic analyzer

acquisition channel

S_D3:7 A15b

S_D3:6 A14b

S_D3:5 A11b

S_D3:4 A07b

S_D3:3 REQb2

PUB32G8 support

signal name

S_D3:2 THERMTRIP

S_D3:1 A09b

S_D3:0 A03b

S_D2:7 A04b

S_D2:6 REQb3

S_D2:5 FERR

S_D2:4 TRDY

S_D2:3 SMI

S_D2:2 RS0

S_D2:1 Unused

S_D2:0 Unused

S_D1:7 LINT1

S_D1:6 LINT0

S_D1:5 FORCEPR

S_D1:4 DEFER

S_D1:3 A12b

TMSSC1 604 Pin Socket Hardware Support

4- 11

Page 70

Reference: Channel Assignment Tables

Table 4- 9: Slave Data Module 32-channel assignments (Cont.)

Logic analyzer

acquisition channel

S_D1:2 A15b

S_D1:1 A10b

S_D1:0 A08b

S_D0:7 A05b

S_D0:6 REQb1

S_D0:5 PROCHOT

S_D0:4 PSMI

S_D0:3 A13b

S_D0:2 A06b

S_D0:1 REQb0

S_D0:0 REQb4

PUB32G8 support

signal name

Table 4--10 lists the channel assignments for the Slave Extend group and the

corresponding support signal.

Table 4- 10: Slave Extend Module 32-channel assignments

Logic analyzer

acquisition channel

S_E3:7 Unused

S_E3:6 IERR

S_E3:5 AP0

S_E3:4 RSP

S_E3:3 A35

S_E3:2 Unused

S_E3:1 Unused

S_E3:0 Unused

S_E2:7 Unused

S_E2:6 Unused

S_E2:5 Unused

S_E2:4 Unused

S_E2:3 A20

PUB32G8 support

signal name

4- 12

TMSSC1 604 Pin Socket Hardware Support

Page 71

Reference: Channel Assignment Tables

Table 4- 10: Slave Extend Module 32-channel assignments (Cont.)

Logic analyzer

acquisition channel

S_E2:2 A18

S_E2:1 A24

S_E2:0 A19

S_E1:7 MCERR

S_E1:6 Unused

S_E1:5 Unused

S_E1:4 Unused

S_E1:3 A35b

S_E1:2 AP1

S_E1:1 BPM4

S_E1:0 BPM5

S_E0:7 BPM2

S_E0:6 BPM3

S_E0:5 BPM0

S_E0:4 BPM1

PUB32G8 support

signal name

S_E0:3 A20b

S_E0:2 A18b

S_E0:1 A24b

S_E0:0 A19b

Table 4--11 lists the channel assignments for the Slave2 Address group and the

corresponding support signal.

Table 4- 11: Slave2 Address Module 32-channel

assignments

Logic analyzer

acquisition channel

S2_A3:7 D2_D05

S2_A3:6 D2_D13

S2_A3:5 D2_D04

S2_A3:4 D2_D11

PUB32G8 support

signal name

TMSSC1 604 Pin Socket Hardware Support

4- 13

Page 72

Reference: Channel Assignment Tables

Table 4- 11: Slave2 Address Module 32-channel

assignments (Cont.)

Logic analyzer

acquisition channel

S2_A3:3 D2_D14

S2_A3:2 D2_D15

S2_A3:1 D2_D12

S2_A3:0 D2_D07

S2_A2:7 D2_D00

S2_A2:6 D2_D08

S2_A2:5 D2_D01

S2_A2:4 D2_D09

S2_A2:3 D2_D02

S2_A2:2 D2_D03

S2_A2:1 D2_DBI0

S2_A2:0 D2_D06

S2_A1:7 D0_D03

S2_A1:6 D0_D06

S2_A1:5 D0_D01

PUB32G8 support

signal name

S2_A1:4 D0_D02

S2_A1:3 D0_D09

S2_A1:2 D0_D08

S2_A1:1 D0_D12

S2_A1:0 D0_D00

S2_A0:7 D0_D07

S2_A0:6 D0_D15

S2_A0:5 D0_D04

S2_A0:4 D0_D14

S2_A0:3 D0_D11

S2_A0:2 D0_D13

S2_A0:1 D0_D05

S2_A0:0 D0_D10

4- 14

TMSSC1 604 Pin Socket Hardware Support

Page 73

Reference: Channel Assignment Tables

Table 4--12 lists the channel assignments for the Slave2 Control group and the

corresponding support signal.

Table 4- 12: Slave2 Control Module 32-channel

assignments

Logic analyzer

acquisition channel

S2_C3:7 D2_D28

S2_C3:6 D2_D24

S2_C3:5 D2_D18

S2_C3:4 D2_D16

S2_C3:3 D2_D31

S2_C3:2 D2_D30

S2_C3:1 D2_D20

S2_C3:0 D2_D29

S2_C2:7 D2_D26

S2_C2:6 D2_D25

S2_C2:5 D2_D17

S2_C2:4 D2_D23

S2_C2:3 D2_D22

S2_C2:2 D2_D21

S2_C2:1 D2_DBI1

PUB32G8 support

signal name

S2_C2:0 D2_D19

S2_C1:7 D0_D21

S2_C1:6 D0_D19

S2_C1:5 D0_D17

S2_C1:4 D0_D22

S2_C1:3 D0_D23

S2_C1:2 D0_D25

S2_C1:1 D0_D20

S2_C1:0 D0_D26

S2_C0:7 D0_D29

S2_C0:6 D0_D30

S2_C0:5 D0_D18

S2_C0:4 D0_D31

TMSSC1 604 Pin Socket Hardware Support

4- 15

Page 74

Reference: Channel Assignment Tables

Table 4- 12: Slave2 Control Module 32-channel

assignments (Cont.)

Logic analyzer

acquisition channel

S2_C0:3 D0_D16

S2_C0:2 D0_D24

S2_C0:1 D0_D28

S2_C0:0 D0_D27

PUB32G8 support

signal name

Table 4--13 lists the channel assignments for the Slave2 Data group and the

corresponding support signal.

Table 4- 13: Slave2 Data Module 32-channel assignments

Logic analyzer

acquisition channel

S2_D3:7 D3_D03

S2_D3:6 D3_D09

S2_D3:5 D3_D02

S2_D3:4 D3_D00

PUB32G8 support

signal name

S2_D3:3 D3_D05

S2_D3:2 D3_D12

S2_D3:1 D3_D08

S2_D3:0 D3_D07

S2_D2:7 D3_D01

S2_D2:6 D3_D04

S2_D2:5 D3_D11

S2_D2:4 D3_D06

S2_D2:3 D3_D15

S2_D2:2 D3_D14

S2_D2:1 D3_D13

S2_D2:0 D3_D10

S2_D1:7 D1_D03

S2_D1:6 D1_D02

S2_D1:5 D1_D06

4- 16

TMSSC1 604 Pin Socket Hardware Support

Page 75

Reference: Channel Assignment Tables

Table 4- 13: Slave2 Data Module 32-channel assignments (Cont.)

Logic analyzer

acquisition channel

S2_D1:4 D1_D09

S2_D1:3 D1_D00

S2_D1:2 D1_D12

S2_D1:1 D1_D07

S2_D1:0 D1_D08

S2_D0:7 D1_D01

S2_D0:6 D1_D04

S2_D0:5 D1_D15

S2_D0:4 D1_D11

S2_D0:3 D1_D05

S2_D0:2 D1_D14

S2_D0:1 D1_D10

S2_D0:0 D1_D13

PUB32G8 support

signal name

Table 4--14 lists the channel assignments for the Slave2 Extend group and the

corresponding support signal.

Table 4- 14: Slave2 Extend Module 32-channel

assignments

Logic analyzer

acquisition channel

S2_E3:7 D3_D19

S2_E3:6 D3_D21

S2_E3:5 D3_D23

S2_E3:4 D3_D20

S2_E3:3 D3_D22

S2_E3:2 D3_D25

S2_E3:1 D3_D26

S2_E3:0 D3_D31

S2_E2:7 D3_D17

S2_E2:6 D3_D27

S2_E2:5 D3_D29

PUB32G8 support

signal name

TMSSC1 604 Pin Socket Hardware Support

4- 17

Page 76

Reference: Channel Assignment Tables

Table 4- 14: Slave2 Extend Module 32-channel

assignments (Cont.)

Logic analyzer

acquisition channel

S2_E2:4 D3_D16