Page 1

Service Manual

TLA7PG2

Pattern Generator and Probes

071-0714-01

This document applies to firmware version 1.00

and above.

Warning

The servicing instructions are for use by qualified

personnel only. To avoid personal injury, do not

perform any servicing unless you are qualified to

do so. Refer to all safety summaries prior to

performing service.

www.tektronix.com

Page 2

Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and

are protected by United States copyright laws and international treaty provi sions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the

Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of t he

Commercial Computer Software -- Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information i n this publication supercedes

that in all previously published material. Specifications and price change privi leges reserved.

Tektronix, Inc., 14200 SW Karl Braun Drive, Beaverton, OR 97077

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

Page 3

WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of one (1) year from

the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will

repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective

product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the

warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging

and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix

shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix

service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges

for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance

and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts

by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from

improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with

other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY

OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY

IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

TEKTRONIX’ RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND

EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX

AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR

CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS

ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Page 4

Page 5

Table of Contents

Specifications

Operating Information

General Safety Summary xi...................................

Service Safety Summary xiii....................................

Preface xv...................................................

Manual Structure xv................................................

Manual Conventions xvi..............................................

Related Manuals xvi.................................................

Contacting Tektronix xvii.............................................

Introduction xix..............................................

Strategy for Servicing xix.............................................

Tektronix Service Offerings xx........................................

Product Description 1--1..............................................

Pattern Generator Module Characteristics 1--2.............................

Probe Characteristics 1--6.............................................

Pattern Generator Module Timing Diagrams 1--25...........................

P6470 and P6471 Probe Environmental Characteristics 1--27..................

Certifications 1--28...................................................

Installation 2--1.....................................................

Operating Environment 2--2...........................................

Applying and Interrupting Power 2--2....................................

Diagnostics 2--3.....................................................

Menus 2--5.........................................................

Online Help 2--5.....................................................

Setups 2--6.........................................................

P6475 Power On/Off Procedure 2--8.....................................

Merging Pattern Generator Modules 2--10.................................

Importing and Exporting Data 2--10......................................

Pattern Editing 2 --11..................................................

Theory of Operation

Module Overview 3--1................................................

Probe Overview 3--4.................................................

Performance Verification

Verification Summary 4--1.............................................

Equipment Required 4--5..............................................

P6475 Variable Probe Test Record 4--6...................................

Setup Procedures 4--7................................................

Functional Verification Procedures 4--13...........................

TLA7PG2 Functional Verification Procedures 4--14.........................

TLA7PG2 Pattern Generator Module Service Manual

i

Page 6

Table of Contents

Adjustment Procedures

Maintenance

P6470 Functional Verification Procedures 4--40.............................

P6471 Functional Verification Procedures 4--51.............................

P6472 Functional Verification Procedures 4--58.............................

P6473 Functional Verification Procedures 4--66.............................

P6474 Functional Verification Procedures 4--76.............................

P6475 Functional Verification Procedures 4--87.............................

Performance V erification Procedures 4--104.........................

TLA7PG2 Maximum Operating Frequency 4--105............................

P6475 Delay Accuracy Check 4--111......................................

Preparation 6--1.....................................................

Preventing ESD 6--1.................................................

Inspection and Cleaning 6--2...........................................

Removal and Installation Procedures 6--5.........................

Preparation 6--5.....................................................

Removal Procedures for the Pattern Generator 6--7.........................

Installation Procedures for Pattern Generator 6--12..........................

Removal Procedures for Standard Probes 6--13.............................

Removal Procedures for P6475 Variable Probe 6--19.........................

Troubleshooting 6--25...........................................

LEDs 6--25..........................................................

Troubleshooting Procedures 6--25........................................

Diagnostics 6--27.....................................................

Restoring and Reinstalling Software 6--29..........................

Restoring Software 6--29...............................................

Reinstalling Pattern Generator Application Software 6--30....................

Uninstalling Pattern Generator Application Software 6--30....................

Updating Module Firmware 6--31........................................

Repackaging 6--35..............................................

Repackaging Instructions 6--35..........................................

Options and Accessories

Pattern Generator Options 7--1.........................................

P6475 Options 7--1..................................................

Pattern Generator and Probe Optional Accessories 7--2......................

Pattern Generator Standard Accessories 7--2..............................

Probe Options 7--2...................................................

Probe Standard Accessories 7--2........................................

Replaceable Electrical Parts

Diagrams

Replaceable Mechanical Parts

Parts Ordering Information 10--1.........................................

Using the Replaceable Parts List 10--2....................................

ii

TLA7PG2 Pattern Generator Module Service Manual

Page 7

List of Figures

Table of Contents

Figure 1--1: Clock and strobe timing diagram 1--25..................

Figure 1--2: P6470, P6472, P6473, and P6474 inhibit

timing diagram 1--25............................................

Figure 1--3: P6470, P6472, P6473, and P6474 external

event for inhibit timing diagram 1--26.............................

Figure 1--4: External event for jump timing diagram 1--26............

Figure 1--5: External event for half channel advance

timing diagram 1--26............................................

Figure 1--6: External event for full channel advance

timing diagram 1--27............................................

Figure 1--7: External event for delay to data output for

advance diagram 1--27..........................................

Figure 4--1: Termination Board 4--12..............................

Figure 4--2: External Clock Input connections using a

P6470, P6471, P6472, P6473, or P6474 4--15........................

Figure 4--3: External Clock Input connections using a P6475 4--16.....

Figure 4--4: Internal Clock Frequency connections using

a P6470, P6471, P6472, P6473, or P6474 4--19.......................

Figure 4--5: Internal Clock Frequency connection using

a P6475 4--20..................................................

Figure 4--6: Merge operation connections using P6470,

P6471, P6472, P6473, or P6474 probes 4--24........................

Figure 4--7: Merge operation connections using P6475 probe 4--25.....

Figure 4--8: Merged and unmerged modules in the

Merge Modules window 4--27....................................

Figure 4--9: Timing Chart 4--28...................................

Figure 4--10: TLA7PG2 Deskew function connections

using a P6470, P6471, P6472. P6473, or P6474 4--29..................

Figure 4--11: TLA7PG2 Deskew function connections

using a P6475 probe 4--30........................................

Figure 4--12: TLA7PG2 Inhibit function (by data) connections

using a P6470, P6473, or P6474 probe 4--33.........................

Figure 4--13: TLA7PG2 Inhibit function (by data) connections

using a P6475 probe 4--33........................................

TLA7PG2 Pattern Generator Module Service Manual

iii

Page 8

Table of Contents

Figure 4--14: Inhibit function (by Event) connections

using a P6470, P6473, or P6474 4--36..............................

Figure 4--15: Inhibit function (by Event) connections

using a P6475 4--37.............................................

Figure 4--16: Internal Clock Frequency connections 4--41.............

Figure 4--17: Sequence and Data Output connections 4--44............

Figure 4--18: P6470 Sequence and Data sample waveforms 4--46.......

Figure 4--19: P6470 Sequence and Data strobed

sample waveforms 4--47.........................................

Figure 4--20: Inhibit function connections 4--48.....................

Figure 4--21: Internal Clock Frequency connections 4--51.............

Figure 4--22: Sequence and Data Output connections 4--54............

Figure 4--23: P6471 Sequence and Data sample waveforms 4--56.......

Figure 4--24: P6471 Sequence and Data strobed

sample waveforms 4--57.........................................

Figure 4--25: Internal Clock Frequency connections 4--59.............

Figure 4--26: Sequence and Data Output connections 4--62............

Figure 4--27: P6472 Sequence and Data sample waveforms 4--64.......

Figure 4--28: P6472 Sequence and Data strobed

sample waveforms 4--65.........................................

Figure 4--29: Internal Clock Frequency connections 4--66.............

Figure 4--30: Sequence and Data Output connections 4--69............

Figure 4--31: P6473 Sequence and Data sample waveforms 4--71.......

Figure 4--32: P6473 Sequence and Data strobed

sample waveforms 4--72.........................................

Figure 4--33: Inhibit function connections 4--74.....................

Figure 4--34: Internal Clock Frequency connections 4--77.............

Figure 4--35: Sequence and Data Output connections 4--80............

Figure 4--36: P6474 Sequence and Data sample waveforms 4--82.......

Figure 4--37: P6474 Sequence and Data strobed

sample waveforms 4--83.........................................

Figure 4--38: Inhibit function connections 4--85.....................

Figure 4--39: Internal Clock Frequency connections 4--88.............

Figure 4--40: Sequence and Data Output connections 4--90............

Figure 4--41: P6475 Sequence and Data sample waveforms 4--92.......

Figure 4--42: P6475 Sequence and Data strobed

sample waveforms 4--93.........................................

Figure 4--43: Inhibit function connections 4--94.....................

iv

TLA7PG2 Pattern Generator Module Service Manual

Page 9

Table of Contents

Figure 4--44: P6475 Data Output and CH6 Output

Mode connections 4--97..........................................

Figure 4--45: NRZ data format 4--99...............................

Figure 4--46: RZ data format 4--99................................

Figure 4--47: R1 data format 4--100.................................

Figure 4--48: OR logic 4--101......................................

Figure 4--49: AND logic 4--101.....................................

Figure 4--50: CH6 AND (NOT CH7) 4--102..........................

Figure 4--51: CH6 OR (NOT CH7 ) 4--103...........................

Figure 4--52: Maximum Operating Frequency Connections

using P6470, P6471, P6472, P6473, or P6474 (Example) 4--106..........

Figure 4--53: Maximum Operating Frequency Connections

using a P6475 probe 4--107........................................

Figure 4--54: Timing chart for the Maximum Operating

Frequency check 4--109..........................................

Figure 4--55: Delay Accuracy connections 4--111......................

Figure 6--1: Right cover 6--7.....................................

Figure 6--2: A50 PG board 6--8..................................

Figure 6--3: J1960 cable housing latch 6--9.........................

Figure 6--4: A20 and A50 fuse locations 6--10........................

Figure 6--5: Ejector assembly 6-- 11................................

Figure 6--6: Cushioning pad 6 --12.................................

Figure 6--7: Removing the standard probe cover 6--13................

Figure 6--8: P6470 series termination resistors 6--14..................

Figure 6--9: P6474 series termination resistors 6--15..................

Figure 6--10: P6472 PECL and LVPECL jumper position 6--15........

Figure 6--11: Fuse location for the P6470 and P6471 6--16.............

Figure 6--12: Removing the standard probe fan 6--18.................

Figure 6--13: Removing the P6475 cover 6--19.......................

Figure 6--14: Removing the P6475 fans 6--20........................

Figure 6--15: Disconnect power supply cables 6--21..................

Figure 6-- 16: Remove the power supply board 6--22..................

Figure 6--17: Troubleshooting procedure 6--26......................

Figure 6--18: Flash programming pins 6--31........................

TLA7PG2 Pattern Generator Module Service Manual

v

Page 10

Table of Contents

Figure 9--1: Function block diagram for the TLA7PG2

Pattern Generator 9--2.........................................

Figure 9--2: Function block diagram for P6470, P6471,

P6472, P6473, and P6474 probes 9--3.............................

Figure 9--3: Function block diagram for P6475 Probe 9--4............

Figure 9--4: Cable diagram for the TLA7PG2

pattern generator 9--5..........................................

Figure 9--5: Cable diagram for the P6475 probe 9--6................

Figure 10--1: TLA7PG2 chassis 10--6..............................

Figure 10--2: TLA7PG2 cables and fuses 10--8......................

Figure 10--3: P6470 probe chassis 10--10............................

Figure 10--4: P6471 probe chassis 10--12............................

Figure 10--5: P6472, P6473, and P6474 probe chassis 10--14............

Figure 10--6: P6475 variable probe chassis 10--16.....................

Figure 10--7: Cables for standard probes 10--17......................

Figure 10--8: Cables for P6475 variable probe 10--18..................

vi

TLA7PG2 Pattern Generator Module Service Manual

Page 11

List of Tables

Table of Contents

T able 1--1: PG module electrical characteristics,

operational mode 1--2.........................................

T able 1--2: PG module electrical characteristics,

output pattern 1-- 2............................................

T able 1--3: PG module, internal clock 1--3........................

Table 1--4: PG module, external clock input 1-- 3...................

T able 1--5: PG module, event processing 1--3......................

Table 1--6: PG module, intermodule interactions 1--4...............

T able 1--7: PG module, merged PG modules 1--4..................

Table 1--8: PG module, mechanical 1--4...........................

Table 1--9: P6470 TTL/CMOS probe 1-- 6.........................

Table 1--10: P6471 ECL probe 1--9..............................

Table 1--11: P6472 PECL/LVPECL probe 1--11.....................

Table 1--12: P6473 LVDS probe 1--12..............................

Table 1--13: P6474 LVCMOS probe 1--15..........................

Table 1--14: P6475 Variable probe 1--18...........................

Table 1--15: Power Supply (P6475 only) 1--23.......................

T able 1--16: Atmospherics 1--23..................................

Table 1--17: Dynamics characteristics (P6470, P6471,

P6472, P6473, and P6474) 1--23..................................

Table 1--18: Dynamics characteristics (P6475) 1--24..................

Table 1--19: Probe cables 1--24...................................

Table1--20:Twistedleadset 1--24...............................

Table 1--21: Certifications and compliances for P6475 1--25...........

Table 1--22: P6470 TTL/CMOS probe and P6471 ECL probe 1--27....

Table 1--23: Certifications and compliances 1--28....................

T able 4--1: Pattern generator module verification procedures 4--2.....

Table 4--2: Test equipment 4-- 5..................................

Table 4--3: Front panel indicators 4--8............................

Table 4--4: Extended Diagnostic test Items and

faulty component 4--10.........................................

T a b l e 4 -- 5 : D e l a y 4 -- 1 1 2..........................................

Table 6--1: Tools required for part removal 6--6....................

Table 6--2: P6470 series termination resistors 6--14..................

TLA7PG2 Pattern Generator Module Service Manual

vii

Page 12

Table of Contents

Table 6--3: P6472, P6473, P6474, and P6475 fuse descriptions 6--16....

Table 6--4: P6470 and P6471 fuse descriptions 6--17.................

T a b l e 6 -- 5 : L E D s 6 -- 2 5..........................................

Table 6--6: Restoring software 6--29..............................

Table 7--1: Optional accessories 7--2..............................

T able 7--2: Pattern generator standard accessories 7--2..............

T able 7--3: Probe standard accessories 7--3........................

viii

TLA7PG2 Pattern Generator Module Service Manual

Page 13

General Safety Summary

Review the following safety precautions to avoid injury and prevent damage to

this product or any products connected to it. To avoid potential hazards, use this

product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read

the General Safety Summary in other system manuals for warnings and cautions

related to operating the system.

ToAvoidFireor

Personal Injury

Use Proper Power Cord. Use only the power cord specified for this product and

certified for the country of use.

Ground the Product. These products (P6470, P6471, P6472, P6473, and P6474)

are indirectly grounded through the grounding conductor of the mainframe

power cord. The P6475 is directly grounded through the grounding conductor of

the probe power cord. To avoid electric shock, the grounding conductor must be

connected to earth ground. Before making connections to the input or output

terminals of the product, ensure that the product is properly grounded.

Observe All Terminal Ratings. To avoid fire or shock hazard, observe all ratings

and markings on the product. Consult the product manual for further ratings

information before making connections to the product.

Do Not Operate Without Covers. Do not operate this product with covers or panels

removed.

Use Proper Fuse. Use only the fuse type and rating specified for this product.

Avoid Exposed Circuitry. Do not touch exposed connections and components

when power is present.

Do Not Operate With Suspected Failures. If you suspect there is damage to this

product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

Keep Product Surfaces Clean and Dry.

Provide Proper Ventilation. Refer to the manual’s installation instructions for

details on installing the product so it has proper ventilation.

TLA7PG2 Pattern Generator Module Service Manual

ix

Page 14

General Safety Summary

Symbols and Terms

Terms in this Manual. These terms may appear in this manual:

WARNING. Warning statements identify conditions or practices that could result

in injury or loss of life.

CAUTION. Caution statements identify conditions or practices that could result in

damage to this product or other property.

Terms on the Product. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the

marking.

WARNING indicates an injury hazard not immediately accessible as you read the

marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

CAUTION

Refer to Manual

Protective Ground

(Earth) Terminal

x

TLA7PG2 Pattern Generator Module Service Manual

Page 15

Service Safety Summary

Only qualified personnel should perform service procedures. Read this Service

Safety Summary and the General Safety Summary before performing any service

procedures.

Do Not Service Alone. Do not perform internal service or adjustments of this

product unless another person capable of rendering first aid and resuscitation is

present.

Disconnect Power. To avoid electric shock, switch off the instrument power, then

disconnect the power cord from the mains power.

Use Care When Servicing With Power On. Dangerous voltages or currents may

exist in this product. Disconnect power, remove battery (if applicable), and

disconnect test leads before removing protective panels, soldering, or replacing

components.

To avoid electric shock, do not touch exposed connections.

TLA7PG2 Pattern Generator Module Service Manual

xi

Page 16

Service Safety Summary

xii

TLA7PG2 Pattern Generator Module Service Manual

Page 17

Preface

Manual Structure

This is the service manual for the TLA7PG2 Pattern Generator. The manual

contains information needed to service the pattern generator to the module level.

The following lists contains a brief description of each manual section.

H The Specifications contains a description and a list of the characteristics of

the pattern generator and pattern generator probes.

H The Operating Information includes general information and operating

instructions at the level needed to safely power on and service the pattern

generator.

H The Theory of Operation contains circuit descriptions that support general

service to the module level.

H The Performance Verification contains procedures to verify the functional

operation of the pattern generator and modules as well as procedures to

verify the performance to advertised specifications.

H The Adjustment Procedures normally lists procedures to adjust the instru-

ment to meet advertised specifications. At this printing, there are no

adjustment procedures required for the pattern generator module.

H The Maintenance contains information and procedures for performing

preventive and corrective maintenance of the pattern generator module.

These instructions include cleaning and fault isolation to the module.

H The Options contains information about options and accessories that are

available for the instrument.

H The Replaceable Electrical Parts contains a statement referring you to the

Mechanical Parts List, where both electrical and mechanical parts are listed.

H The Diagrams contains block diagrams and cabling diagrams that are useful

in isolating failed components.

H The Replaceable Mechanical Parts includes a table of all replaceable parts,

their descriptions, and their Tektronix part numbers.

TLA7PG2 Pattern Generator Module Service Manual

xiii

Page 18

Preface

Manual Conventions

This manual uses certain conventions that you should become familiar with

before doing service.

Some sections of the manual contain procedures for you to perform. To keep

these instructions clear and consistent, this manual uses the following conventions:

H Names of front-panel controls and menus appear in the same case (initial

capitals, all uppercase, and so on.) in the manual as they appear on the

TLA7PG2 Pattern Generator front panel and menus.

H Instruction steps are numbered, unless there is only one step.

H An arrow placed after a menu title directs you to access the indicated

submenu. For example, System → System Configuration is directing you to

select the System menu and then select the submenu named System

Configuration.

Related Manuals

Other documentation for the TLA7PG2 Pattern Generator include:

H The Tektronix Logic Analyzer Family User Manual contains specifications

and information on how to use the TLA7PG2 Pattern Generator.

H A series of probe manuals that provide information for using the probes the

the TLA7PG2 Pattern Generator.

xiv

TLA7PG2 Pattern Generator Module Service Manual

Page 19

Contacting Tektronix

Preface

Phone 1-800-833-9200*

Address Tektronix, Inc.

Department or name (if known)

14200 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

USA

Web site www.tektronix.com

Sales support 1-800-833-9200, select option 1*

Service support 1-800-833-9200, select option 2*

Technical support Email: techsupport@tektronix.com

1-800-833-9200, select option 3*

1-503-627-2400

6:00 a.m. -- 5:00 p.m. Pacific time

* This phone number is toll free in North America. After office hours, please leave a

voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the

Tektronix web site for a list of offices.

TLA7PG2 Pattern Generator Module Service Manual

xv

Page 20

Preface

xvi

TLA7PG2 Pattern Generator Module Service Manual

Page 21

Introduction

Strategy for Servicing

This manual contains information needed to service the TLA7PG2 Pattern

Generator, as well as general information critical to safe and effective servicing.

To prevent personal injury or damage to the pattern generator, consider the

following before attempting service:

H The procedures in this manual should be performed only by a qualified

service person.

H Read the General Safety Summary and the Service Safety Summary, near the

beginning of this manual.

H Read Preparation for Use in the Operating Instructions section.

To isolate a failure to a module, use the fault isolation procedures found in

Troubleshooting in the Maintenance chapter of this manual. To move and replace

any failed module, follow the instructions in Removal and Installation Proce-

dures,alsopartoftheMaintenance chapter of this manual. After isolating a

faulty module, replace it with a fully-tested module obtained from the factory.

The Replaceable Mechanical Parts section contains part number and ordering

information for all replaceable modules.

TLA7PG2 Pattern Generator Module Service Manual

xvii

Page 22

Introduction

Tektronix Service Offerings

Tektronix provides service to cover repair under warranty as well as other

services that may provide a cost-effective answer to your service needs.

Whether providing warranty repair service or any of the other services listed

below, Tektronix service technicians are well equipped to service the TLA7PG2

Pattern Generator. Tektronix technicians train on Tektronix products; they have

access to the latest information on improvements to the TLA7PG2 Pattern

Generator as well as the latest new options.

Warranty Repair Service

Self Service

Tektronix warrants this product for one year from the date of purchase. (The

warranty is listed in the front of this manual.) Tektronix technicians provide

warranty service at most Tektronix service locations worldwide. The Tektronix

product catalog lists all service locations worldwide.

Tektronix supports repair to the module level by providing Module Exchange.

Module Exchange. This service reduces down-time for repair by allowing you to

exchange most modules for remanufactured ones. Tektronix ships an updated

tested exchange module from the Beaverton, Oregon service center, typically

within 24 hours. Each module comes with a 90-day service warranty.

xviii

TLA7PG2 Pattern Generator Module Service Manual

Page 23

Specifications

Product Description

This chapter provides a high-level description of the TLA7PG2 Pattern

Generator module and the associated pattern generator probes. It also lists the

specifications for the modules and probes.

The TLA7PG2 Pattern Generator is a 64-channel, programmable pattern

generator module with sequential control that plugs into the TLA700 series

mainframes, and is intended for use as an integral component of the Tektronix

Logic Analyzer Family series of products.

The pattern generator module provides multichannel signals for use in applications, such as simulation of missing system elements, erroneous signals for stress

testing, or extended analysis for simulating a device under test.

You can put circuits in a desired state and operate the pattern generator at full

speed or single step it through a series of states. The TLA7PG2 Pattern

Generator can also generate infrequently encountered test conditions to test a

hardware design or software program for robustness.

The TLA7PG2 Pattern Generator supports the following probes:

H P6470 TTL/CMOS

H P6471 ECL

H P6472 PECL/LVPECL

H P6473 LVDS

H P6474 LVCMOS

H P6475 Variable

You can have up to four probes on each pattern generator.

Following are some of the key features of the TLA7PG2 Pattern Generator:

H Provides up to 64 channels

H Offers a Jump If condition for all data blocks (maximum of 4000) up to

clock rates of 268 MHz

The TLA7PG2 Pattern Generator can fully test circuits at real clock speeds,

without having to use improvised setups.

TLA7PG2 Pattern Generator Module Service Manual

1- 1

Page 24

Specifications

Pattern Generator Module Characteristics

All specifications are guaranteed unless noted Typical. Typical characteristics

describe typical or average performance and provide useful reference information.

Specifications that are marked with the n symbol are checked directly (or

indirectly) in the Performance Verifications chapter of this manual.

The specifications apply to all versions of the pattern generator unless otherwise

noted.

The performance limits in this specification are valid with these conditions:

H The modules must be installed in a Tektronix Logic Analyzer Mainframe.

H The module must have had at least a 30 minute warm-up period.

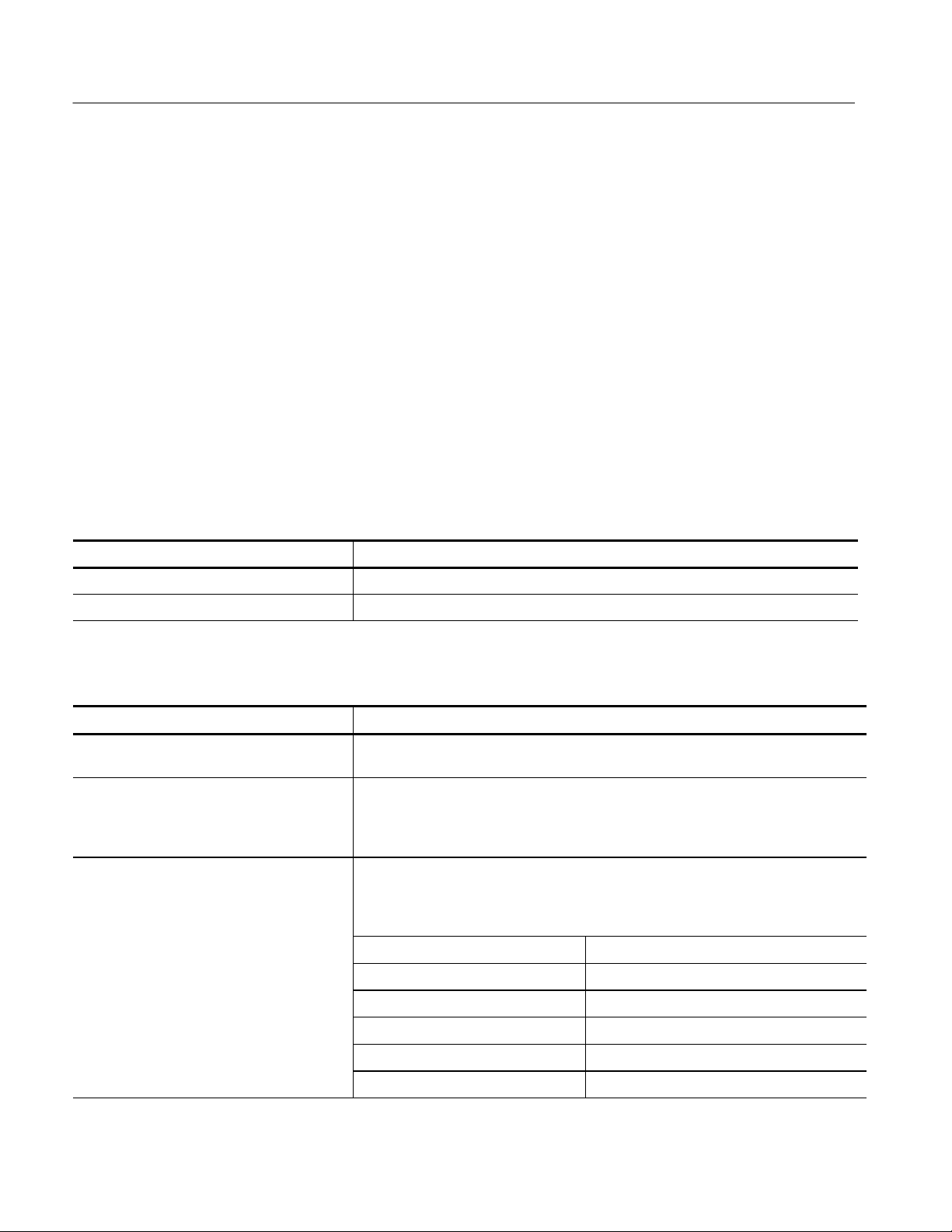

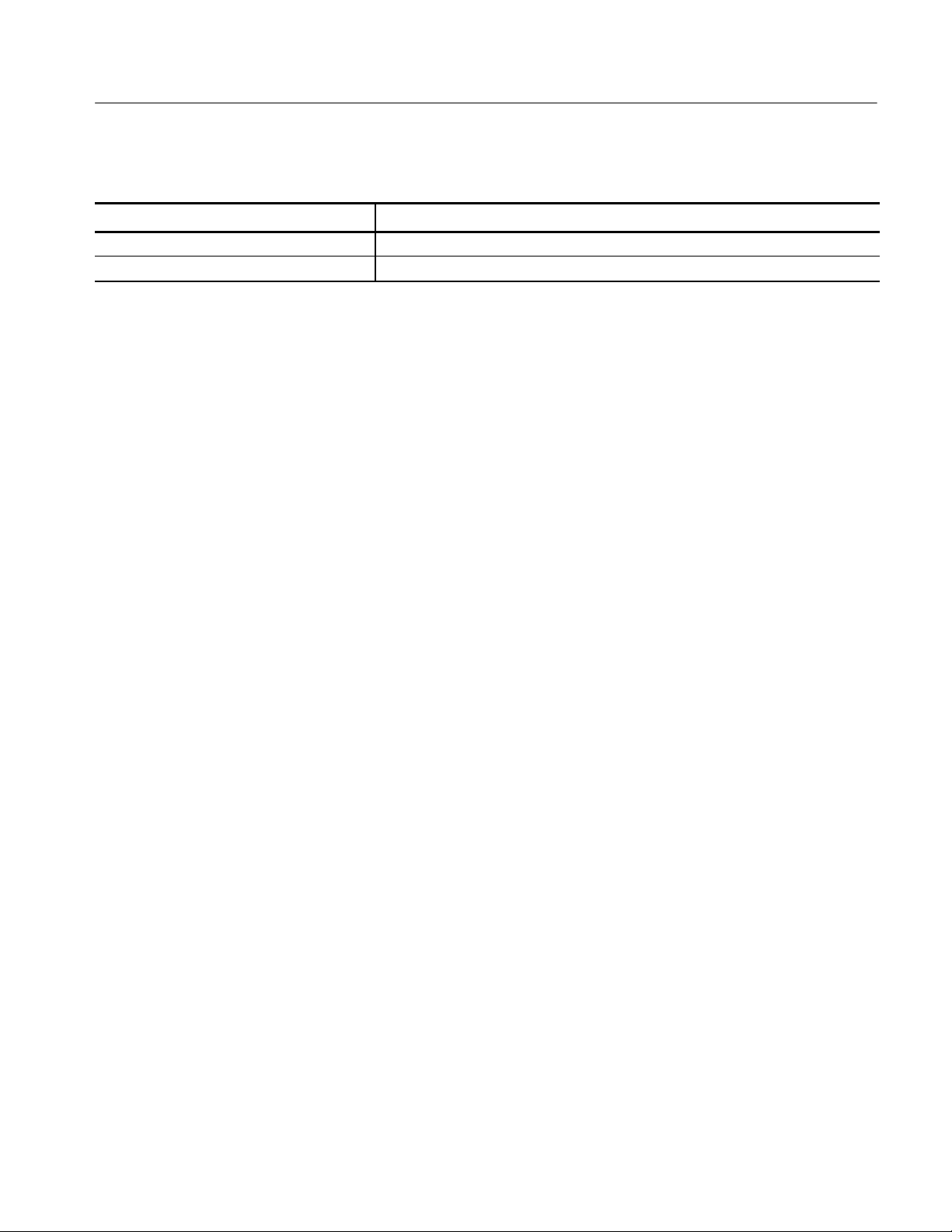

Table 1- 1: PG module electrical characteristics, operational mode

Characteristic Description

Normal Pattern data output is synchronized by the internal/external clock input

Step Pattern data output is synchronized by the software command

Table 1- 2: PG module electrical characteristics, output pattern

Characteristic Description

n Maximum Operating Clock Frequency 134 MHz in Full Channel Mode

268 MHz in Half Channel Mode

Pattern length 40 to 262,140 (218-- 4) in Full Channel Mode (standard)

80 to 524,280 (2

40 to 1,048,572 (2

80 to 2,097,144 (2

Number of channels 64 channels in Full Channel Mode

32 channels in Half Channel Mode

The pattern memory for the following data channel will be shared with strobe

control/internal inhibit control

Probe D data output channel Control

D0:0 STRB0

D0:1 STRB1

19

-- 8) in Half Channel Mode (standard)

20

-- 4) in Full Channel Mode (option 1M or PowerFlex upgrade)

21

-- 8) in Half Channel Mode (option1M or PowerFlex upgrade)

1- 2

D0:2 STRB2

D0:3 STRB3

D0:4 Inhibit probe A

TLA7PG2 Pattern Generator Module Service Manual

Page 25

Table 1- 2: PG module electrical characteristics, output pattern (Cont.)

Characteristic Description

D0:5 Inhibit probe B

D0:6 Inhibit probe C

D0:7 Inhibit probe D

Sequences Maximum 4,000

Number of Blocks Maximum 4,000

Number of Sub-Sequences Maximum 50

Sub-Sequences Maximum 256 steps

Repeat Count 1 to 65,536 or infinite

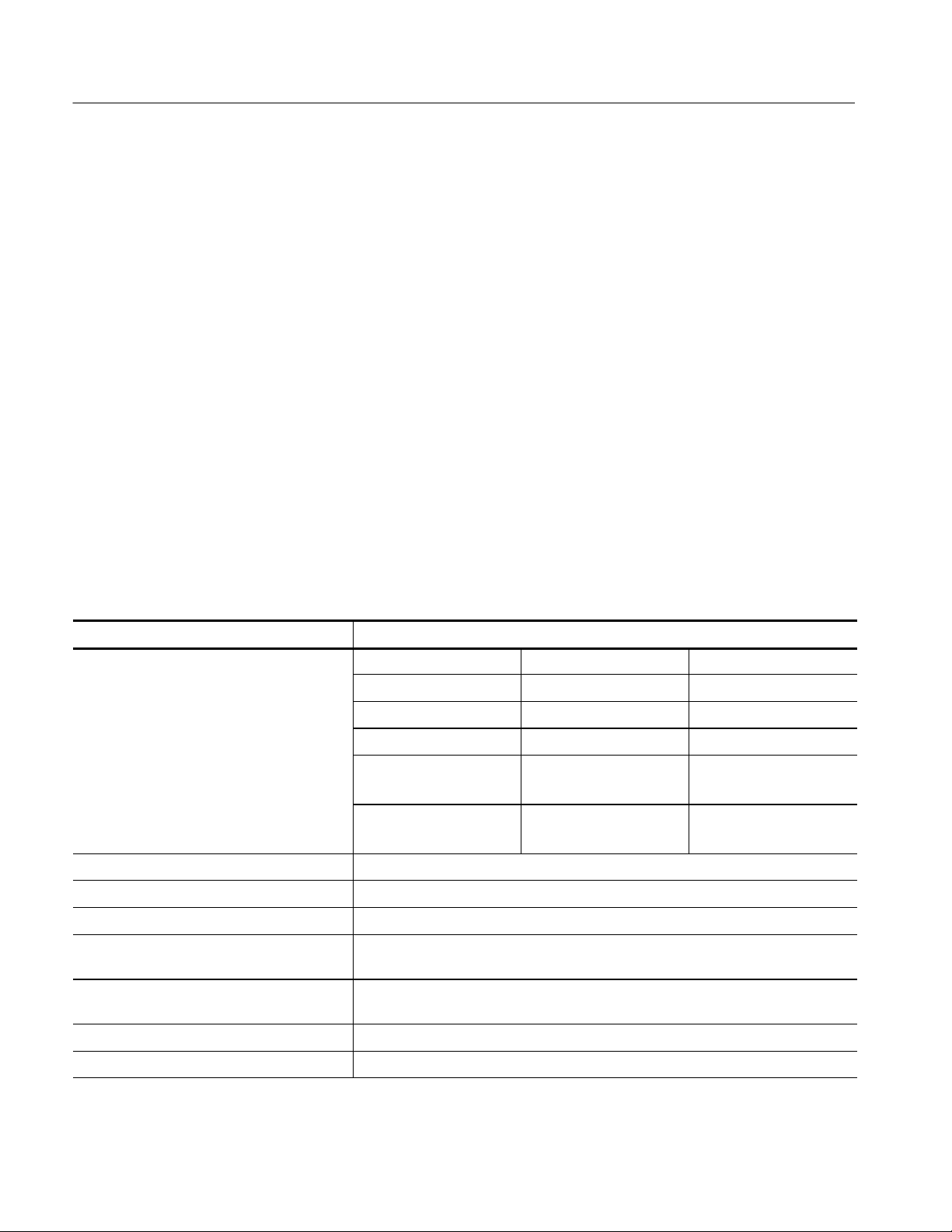

Table 1- 3: PG module, internal clock

Specifications

Characteristic Description

Clock Period 2.0000000 s to 7.4626865 ns in Full Channel Mode

1.0000000 s to 3.7313432 ns in Half Channel Mode

Period Resolution 8 digits

Table 1- 4: PG module, external clock input

Characteristic Description

Clock Rate DC to 134 MHz in Full Channel Mode

DC to 268 MHz in Half Channel Mode

Polarity Normal or Invert

Threshold

Range --2.56 V to +2.54 V

Resolution 20 mV

Input Impedance 1kΩ terminated to GND

Sensitivity 500 mV

p-p

Table 1- 5: PG module, event processing

Characteristic Description

Event Action Advance, Jump and Inhibit

Number of Event Inputs 8 External Event Inputs (2 per each probe)

TLA7PG2 Pattern Generator Module Service Manual

1- 3

Page 26

Specifications

Table 1- 5: PG module, event processing (Cont.)

Characteristic Description

Number of Event Definitions 8

(A maximum of 256 event input patterns can be OR’d to define an event)

Event Mode

for Advance Edge or Level

for Jump Edge or Level

Event Filter None or 50 ns

Table 1- 6: PG module, intermodule interactions

Characteristic Description

Signal Input Input from backplane

Selectable from Signal 1, 2, 3, and 4

Used to define the Event

Signal Output Output to backplane

Selectable from Signal 1, 2, 3, and 4

Specified as High or Low in each Sequence line

Table 1- 7: PG module, merged PG modules

Characteristic Description

Number of modules that can be merged

together

External Event Input for merged module For Jump and Advance, only the External Event Input of the leftmost module is used;

5

for Inhibit, each module uses its own External Event Input as a source

Table 1- 8: PG module, mechanical

Characteristic Description

Slot width Requires 2 mainframe slots

Weight

(Typical)

Overall dimensions (excluding connectors)

Height 10.32 in (262 mm)

Width 2.39 in (61 mm)

2.5kg(5lbs4oz)

1- 4

TLA7PG2 Pattern Generator Module Service Manual

Page 27

Table 1- 8: PG module, mechanical (Cont.)

Characteristic Description

Depth 14.7 in (373 mm)

Mainframe interlock 1.4 ECI keying is implemented

Specifications

TLA7PG2 Pattern Generator Module Service Manual

1- 5

Page 28

Specifications

loa

d:10k

Ω+1

5pf,sampl

att

8

Probe Characteristics

Table 1- 9: P6470 TTL/CMOS probe

All specifications are guaranteed unless noted Typical. Typical characteristics

describe typical or average performance and provide useful reference information.

Specifications that are marked with the n symbol are checked directly (or

indirectly) in the Performance Verifications chapter of this manual.

The specifications apply to all versions of the pattern generator probes unless

otherwise noted.

The performance limits in this specification are valid with these conditions:

H The probes must be installed in a TLA7PG2 Pattern Generator.

H The probes must have had at least a 30 minute warm-up period.

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +5 V

Series Termination Resistor: 75 Ω

Load: 510 Ω +50pF

Characteristic

Maximum Clock Frequency

(with series termination resistor: 75 Ω)

Maximum Clock Frequency

(with series termination resistor: 75 Ω,

eoutputp

bit counter)

Typical

Output Level (VCC) 2.0Vto5.5V,25mVstep,into1MΩ

Maximum Resistive Load 220 Ω

Maximum Capacitive Load 50 pF

Output Type 74LVC541A for Data Output

Series Termination Resistor 75 Ω standard. 43, 100 and 150 Ω as optional accessories

ern:

Description

Output Level (Vcc) Full Channel mode Half Channel mode

Vcc ≤ 3.3 V

3.3 V < Vcc ≤5V 62.5 MHz 125 MHz

Vcc > 5 V 52.5 MHz 105 MHz

Output Level (Vcc) Full Channel mode Half Channel mode

Vcc ≤5.5 V

74LVC244A for Clock/Strobe Output

(18 pin DIP socket)

134 MHz 268 MHz

134 MHz 268 MHz

Supported Channel Mode Half and Full

Number of External Inhibit Inputs 1

1- 6

TLA7PG2 Pattern Generator Module Service Manual

Page 29

Table 1- 9: P6470 TTL/CMOS probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +5 V

Series Termination Resistor: 75 Ω

Load: 510 Ω +50pF

Characteristic Description

Rise/Fall Time

(20% to 80%

load: 1 MΩ +< 1 pF)

Typical

Clock/Strobe Output

Rise 640 ps

Fall 1.1 ns

Data Output

Rise 680 ps

Fall 2.9 ns

Specifications

Rise/Fall Time

(20% to 80%

load: 510 Ω +51pF)

Typical

Data Output Skew

Typical

Data Output to Strobe Output Delay

Typical

Data Output to Clock Output Delay

Typical

External Clock Input to Clock Output Delay

Typical

External Inhibit Input to Output Enable Delay

Typical

External Inhibit Input to Output Disable Delay

Typical

Probe D Data Output to Output Enable Delay

(for Internal Inhibit) Typical

Clock/Strobe Output

Rise 6.5 ns

Fall 6.3 ns

Data Output

Rise 5.2 ns

Fall 4.5 ns

< 570 ps between all data output pins of all modules in the mainframe after

intermodule skew is adjusted manually

< 480 ps between all data output pins of all probes of single module

< 440 ps between all data output pins of single probe

+ 1.7 ns when strobe delay set to zero. (Td3 in Figure 1--1 on page 1--25)

+2.4 ns (Td2 in Figure 1--1 on page 1--25)

61 ns (Td1 in Figure 1--1 on page 1--25)

34 ns for Data Output (Td4 in Figure 1--2 on page 1--25)

86 ns for Data Output (Td5 in Figure 1--2 on page 1--25)

7 ns for Data Output (Td4 in Figure 1--2 on page 1--25)

Probe D Data Output to Output Disable Delay

(for Internal Inhibit) Typical

External Event Input to Clock Output Setup

(for inhibit)

(event-filter: off) Typical

External Event Input and Inhibit Input

Input Type

Minimum Pulse Width

8 ns for Data Output (Td5 in Figure 1--2 on page 1--25)

Full channel mode: 1.5 clocks + 240 ns (Td6 in Figure 1--3 on page 1--25)

Half channel mode: 2 clocks + 240 ns

74LVC14A, Positive True, 1 kΩ to GND

200 ns (event filter: off)

TLA7PG2 Pattern Generator Module Service Manual

1- 7

Page 30

Specifications

Table 1- 9: P6470 TTL/CMOS probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +5 V

Series Termination Resistor: 75 Ω

Load: 510 Ω +50pF

Characteristic Description

External Event Input Delay to Data Output for

Advance

External Event Input

Number of Inputs

Setup Time of Event Typical

Input for Event Jump

230 ns to 330 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 1--7 on page 1--27)

(CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock

period when the External Clock is used.)

2

Half Channel Mode

54 to 61 clocks + 240 ns before the next block

Full Channel Mode

27.5 to 31 clocks + 240 ns before the next block

(Td9 in Figure 1--4 on page 1--26)

Setup Time of Event Input for Event Advance

Typical

Mainframe External Signal Input to PG Probe

data output

for Advance

via Signal 1, 2 Typical

via Signal 3, 4 Typical

for Inhibit

via Signal 1, 2 Typical

via Signal 3, 4 Typical

PG Probe Clock Output to Mainframe External

Signal Output

via Signal 1, 2 Typical

via Signal 3, 4 Typical

Number of Data Outputs 16 in Full Channel Mode

In Half Channel Mode, 240 ns before the rising edge of 5th clock output pulse from

the last of the previous block (Td10 in Figure 1--5 on page 1--26)

In Full Channel Mode, 240 ns before the rising edge of 3rd clock output pulse from the

last of the previous block (Td11 in Figure 1--6 on page 1--27)

200 ns to 300 ns + 1.5 to 2.5 CLK2

230 ns to 330 ns + 1.5 to 2.5 CLK2

(CLK2 is from 2.5 ns to 5 ns when the Internal Clock is used. It is the same as one

clock period when the External Clock is used)

100 ns to 200 ns + 2 to 3 CLK (Half Channel Mode)

100 ns to 200 ns + 1.5 to 2.5 CLK (Full Channel Mode)

130 ns to 230 ns+ 2 to 3 CLK (Half Channel Mode)

130 ns to 230 ns + 1.5 to 2.5 CLK (Full Channel Mode)

18 ns -- 5 CLK (Half Channel Mode)

18 ns -- 3 CLK (Full Channel Mode)

29 ns -- 5 CLK (Half Channel Mode)

29 ns -- 3 CLK (Full Channel Mode)

8 in Half Channel Mode

Number of Clock Outputs 1

Number of Strobe Outputs 1

Number of External Event Inputs 2

1- 8

(Only one Clock Output or Strobe Output can be enabled at one time per probe)

TLA7PG2 Pattern Generator Module Service Manual

Page 31

Table 1- 9: P6470 TTL/CMOS probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +5 V

Series Termination Resistor: 75 Ω

Load: 510 Ω +50pF

Characteristic Description

Clock Output Polarity Positive

Strobe Type RZ only

Table 1- 10: P6471 ECL probe

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted:

Load: 51 Ω terminated to --2 V

Specifications

Characteristic

Maximum Clock Frequency 134 MHz in Full Channel mode

Output Level ECL

Output Type 100E151 for data output

Supported Channel Mode Half and Full

Rise/Fall Time

(20% to 80%) Typical

Data Output Skew Typical < 255 ps between all data output pins of all modules in the mainframe after

Description

268 MHz in Half Channel mode

100EL16 for strobe output

100EL04 for clock output

outputs are unterminated

Clock Output

Rise 320 ps

Fall 330 ps

Data Output

Rise 1,200 ps

Fall 710 ps

Strobe Output

Rise 290 ps

Fall 270 ps

intermodule skew is adjusted manually

< 240 ps between all data output pins of all probes of single module

< 210 ps between all data output pins of a single probe

Data Output to Strobe Output Delay

Typical

Data Output to Clock Output Delay

Typical

External Clock Input to Clock Output Delay

Typical

+2.94 ns when strobe delay set to zero (Td3 in Figure 1--1 on page 1--25)

+780 ps (Td2 in Figure 1--1 on page 1--25)

50 ns (Td1 in Figure 1--1 on page 1--25)

TLA7PG2 Pattern Generator Module Service Manual

1- 9

Page 32

Specifications

Table 1- 10: P6471 ECL probe (Cont.)

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted:

Load: 51 Ω terminated to --2 V

Characteristic Description

External Event Input Delay to Data Output for

Advance

External Event Input

Input Level

Input Type

Minimum Pulse Width

External Event Input

Number of Inputs

Setup Time of Event

Input for Event Jump

Typical

170 ns to 270 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 1--7 on page 1--27)

(CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock

period when the External Clock is used.)

ECL

10H116with75kΩ to --2 V

150 ns (Event filter: off)

2

Half Channel Mode, 54 to 61 clocks + 180 ns before the next block

Full Channel Mode, 27.5 to 31 clocks + 180 ns before the next block (Td9 in

Figure 1--4 on page 1--26)

Setup Time of Event

Input for Event Advance

Typical

Mainframe External Signal Input to PG Probe

data output

for Advance

via Signal 1, 2 Typical

via Signal 3, 4 Typical

PG Probe Clock Output to Mainframe External

Signal Output

via Signal 1, 2 Typical

via Signal 3, 4 Typical

Number of Data Outputs 16 in Full Channel Mode

Number of Clock Outputs 1

Number of Strobe Outputs 1

Half Channel Mode:

80 ns before the rising edge of 5th clock output pulse from the last of the

previous block (Td10 in Figure 1--5 on page 1--26)

Full Channel Mode

80 ns before the rising edge of 3rd clock output pulse from the last of the

previous block (Td11 in Figure 1--6 on page 1--27)

200 ns to 300 ns + 1.5 to 2.5 CLK2

230 ns to 330 ns + 1.5 to 2.5 CLK2

(CLK2 from 2.5 ns to 5 ns when Internal Clock is used. It is same as one clock period

when External Clock is used.)

28 ns -- 5 CLK (Half Channel Mode)

28 ns -- 3 CLK (Full Channel Mode)

38 ns -- 5 CLK (Half Channel Mode)

38 ns -- 3 CLK (Full Channel Mode)

8 in Half Channel Mode

(Only one Clock Output or one Strobe Output can be enabled at one time per probe)

Number of External Event Inputs 2

Clock Output Polarity Positive

Strobe Type RZ only

1- 10

TLA7PG2 Pattern Generator Module Service Manual

Page 33

Table 1- 11: P6472 PECL/LVPECL probe

q

y

All timing values are specified with a load condition of 1 M Ω + ≤ 1 pF with PECL mode.

Specifications

Characteristic

Maximum Clock Frequency Full Channel Mode Half Channel Mode

Number of Data Outputs 8 Full Channel

Number of Clock Outputs 1 differential

Number of Strobe Outputs 1 differential

Number of External Event Inputs 2

Clock Output Polarity Positive

Strobe Type RZ (return to zero) only

Strobe Delay Zero or Trailing Edge

Output Level PECL, LVPECL (selectable by moving a jumper in the probe)

Output Type 100EL90 (all outputs are terminated)

Supported Channel Mode Half and Full

Rise/Fall Time (20% to 80%) Rise 430 ps

Data Output Skew < 385 ps between all data output pins of all modules in the mainframe after

Description

134 MHz 268 MHz

8 Half Channel

(Only one Clock Output or one Strobe Output can be enabled at one time per probe)

Fall 970 ps

intermodule skew is adjusted manually

< 370 ps between all data output pins of all probes of single module

< 340 ps between all data output pins of a single probe

Data Output to Strobe Output Delay + 2.93 ns when strobe delay is set to zero (See Td3 in Figure 1--1 on page 1--25)

Data Output to Clock Output Delay + 1.12 ns (Td2 in Figure 1--1 on page 1--25)

External Clock Input to Clock Output Delay 50 ns (See Td1 in Figure 1 --1 on page 1--25)

External Event Input Delay to Data Output for

Advance

External Event Input

Input Level

Input Type

Minimum Pulse Width (event filter: off)

170 ns to 270 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 1--7 on page 1--27)

(CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock

period when the External Clock is used.)

PECL, LVPECL (selectable by moving a jumper in the probe)

100EL91, unterminated

150 ns

TLA7PG2 Pattern Generator Module Service Manual

1- 11

Page 34

Specifications

Usingsignal1or2

q

y

Table 1- 11: P6472 PECL/LVPECL probe (Cont.)

All timing values are specified with a load condition of 1 M Ω + ≤ 1 pF with PECL mode.

Characteristic Description

External Event Input

Setup Time of Event Input for Event

Jump

Setup Time of Event Input for Event Advance Half Channel Mode: 180 ns before the rising edge of the 5th clock output pulse from

Mainframe External Signal Input to PG Probe

Data Output

For Advance:

Using signal 3 or 4

PG Probe Clock Output to Mainframe External

Signal Output

Using signal 1 or 2

Half Channel Mode: 54 to 61 Clocks + 180 ns before the next block

Full Channel Mode: 27.5 to 31 Clocks + 180 ns before the next block

(see Td9 in Figure 1--4 on page 1--26)

the last of the previous block (See Td10 in Figure 1--5 on page 1--26)

Full Channel Mode: 180 ns before the rising edge of the 3rd clock output pulse from

the last of the previous block (see Td11 in Figure 1--6 on page 1--27)

200 ns to 300 ns + 1.5 to 2.5 CLK2

230 ns to 330 ns + 1.5 to 2.5 CLK2

(CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock

period when the External Clock is used.)

31 ns --5 CLK (Half Channel Mode)

31 ns --3 CLK (Full Channel Mode)

Using signal 3 or 4

40 ns --5 CLK (Half Channel Mode)

40 ns --3 CLK (Full Channel Mode)

Table 1- 12: P6473 LVDS probe

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted:

Load: 100 Ω +<1pF

Characteristic

Maximum Clock Frequency Full Channel Mode Half Channel Mode

Number of Data Outputs 16 Full Channel

1- 12

Description

134 MHz 268 MHz

8 Half Channel

TLA7PG2 Pattern Generator Module Service Manual

Page 35

Specifications

Table 1- 12: P6473 LVDS probe (Cont.)

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted:

Load: 100 Ω +<1pF

Characteristic Description

Number of Clock Outputs 1 (Only one Clock Output or One Strobe Output can be enabled at one time per

probe.)

Number of Strobe Outputs 1 (Only one Clock Output or One Strobe Output can be enabled at one time per

probe.)

Number of External Event Inputs 1

Number of External Inhibit Inputs 1

Clock Output Polarity Positive

Strobe Type RZ (return to zero) only

Strobe Delay Zero or Trailing Edge

Maximum Capacitive Load 10 pF

Output Type LVDS (TIA/EIA--644 compatible)

Supported Channel Mode Half and Full

Rise/Fall Time

Rise: 910 ps

(20% to 80%)

Data Output Skew < 365 ps between all data output pins of all modules in the mainframe after

Data Output to Strobe Output Delay --280 ns when strobe delay is set to zero (See Td3 in Figure 1--1 on page 1--25)

Data Output to Clock Output Delay 1.2 ns (Td2 in Figure 1--1 on page 1--25)

External Clock Input to Clock Output Delay 55 ns (See Td1 in Figure 1 --1 on page 1--25 )

External Inhibit Input to Output Enable Delay 9 ns for Data Output (See Td4 in Figure 1--2 on page 1--25)

External Inhibit Input to Output Disable Delay 12 ns for Data Output (See Td5 in Figure 1--2 on page 1--25)

Probe D Data Output to Output Enable Delay

(for Internal Inhibit)

Probe D Data Output to Output Disable Delay

(for Internal Inhibit)

External Event Input to Clock Output Setup

(for inhibit) event-filter: off

External Event Input Delay to Data Output for

Advance

Fall: 750 ps

intermodule skew is adjusted manually

< 350 ps between all data output pins of all probes of single module

< 320 ps between all data output pins of a single probe

2 ns for Data Output (See Td4 in Figure 1--2 on page 1--25)

5 ns for Data Output (See Td5 in Figure 1--2 on page 1--25)

Full Channel mode: 1.5 Clocks + 180 ns

Half Channel mode: 2 Clocks + 180 ns

(See Td6 in Figure 1--3 on page 1--26)

170 ns to 270 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 1--7 on page 1--27)

(CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock

period when the External Clock is used.)

TLA7PG2 Pattern Generator Module Service Manual

1- 13

Page 36

Specifications

Table 1- 12: P6473 LVDS probe (Cont.)

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted:

Load: 100 Ω +<1pF

Characteristic Description

External Event Input and Inhibit Input

Input Type

Minimum Pulse Width (event filter: off)

External Event Input Setup Time of Event

Input for Event Jump

External Event Input Setup Time for Event

Advance

Mainframe External Signal Input to PG Probe

Data Output

For Advance:

Using signal 1 or 2

Using signal 3 or 4

For Inhibit:

LVDS (TIA/EIA--644 compatible), positive true

150 ns

Half Channel Mode: 54 to 61 Clocks + 180 ns before the next block

Full Channel Mode: 27.5 to 31 Clocks + 180 ns before the next block

(See Td9 in Figure 1--4 on page 1--26)

Half Channel Mode: 180 ns before the rising edge of the 5th clock output pulse from

the last of the previous block (See Td10 in Figure 1--5 on page 1--26)

Full Channel Mode: 180 ns before the rising edge of the 3rd clock output pulse from

the last of the previous block (See Td11 in Figure 1--6 on page 1--27)

200 ns to 300 ns + 1.5 to 2.5 CLK2

230 ns to 330 ns + 1.5 to 2.5 CLK2

(CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock

period when the External Clock is used.)

Using signal 1 or 2

Using signal 3 or 4

PG Probe Clock Output to Mainframe External

Signal Output

Using signal 1 or 2

Using signal 3 or 4

1- 14

100 ns to 200 ns + 2 to 3 CLK (Half Channel Mode)

100 ns to 200 ns +1.5 to 2.5 CLK (Full Channel Mode)

130 ns 230 ns + 2 to 3 CLK (Half Channel Mode)

130 ns to 230 ns + 1.5 to 2.5 CLK (Full Channel Mode)

26 ns --5 CLK (Half Channel Mode)

26 ns --3 CLK (Full Channel Mode)

35 ns --5 CLK (Half Channel Mode)

35 ns --3 CLK (Full Channel Mode)

TLA7PG2 Pattern Generator Module Service Manual

Page 37

Table 1- 13: P6474 LVCMOS probe

q

y

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +3.3 V

Series Termination Resistor: 75 Ω

Load: 510 Ω+20pF

Specifications

Characteristic

Maximum Clock Frequency Full Channel Mode Half Channel Mode

Number of Data Outputs 16 Full Channel

Number of Clock Outputs 1 (Only one Clock Output or One Strobe Output can be enabled at one time per

Number of Strobe Outputs 1 (Only one Clock Output or One Strobe Output can be enabled at one time per

Number of External Event Inputs 2

Number of External Inhibit Inputs 1

Clock Output Polarity Positive

Strobe Type RZ (return to zero) only

Strobe Delay Zero or Trailing Edge

Output Level (Vcc) 1.2Vto3.3V,25mVstep,into1MΩ

Maximum Resistive Load 510 Ω

Maximum Capacitive Load 20 pF

Output Type 74AVC16244

Series Termination Resistor 75 Ω standard. 43, 100 and 150 Ω as optional accessories

Supported Channel Mode Half and Full

Rise/Fall Time

Description

134 MHz 268 MHz

8 Half Channel

probe.)

probe.)

(18 pin DIP socket)

Rise 1200 ps

(20 % to 80 %, load: 1M Ω+< 1pF)

Rise/Fall Time

(20 % to 80 %, load: 510 Ω+50 pF)

Data Output Skew < 590 ps between all data output pins of all modules in the mainframe after

Data Output to Strobe Output Delay 460 ps when strobe delay is set to zero (See Td3 in Figure 1--1 on page 1--25)

Data Output to Clock Output Delay 1.84 ns (Td2 in Figure 1--1 on page 1--25)

External Clock Input to Clock Output Delay 55 ns (See Td1 in Figure 1 --1 on page 1--25)

TLA7PG2 Pattern Generator Module Service Manual

Fall 610 ps

Rise 3.4 ns

Fall 3.2 ns

intermodule skew is adjusted manually

< 500 ps between all data output pins of all probes of single module

< 460 ps between all data output pins of a single probe

1- 15

Page 38

Specifications

Table 1- 13: P6474 LVCMOS probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +3.3 V

Series Termination Resistor: 75 Ω

Load: 510 Ω+20pF

Characteristic Description

External Inhibit Input to Output Enable Delay 36 ns for Data Output (See Td4 in Figure 1--2 on page 1--25)

External Inhibit Input to Output Disable Delay 18 ns for Data Output (See Td5 in Figure 1--2 on page 1--25)

Probe D Data Output to Output Enable Delay

(for Internal Inhibit)

Probe D Data Output to Output Disable Delay

(for Internal Inhibit)

External Event Input to Clock Output Setup

(for inhibit) event-filter: off

6 ns for Data Output (See Td4 in Figure 1--2 on page 1--25)

7 ns for Data Output (See Td5 in Figure 1--2 on page 1--25)

Full Channel mode: 1.5 Clocks + 180 ns

Half Channel mode: 2 Clocks + 180 ns

External Event Input Delay to Data Output for

Advance

External Event Input and Inhibit Input

Input Type

Minimum Pulse Width

External Event Input

Setup Time of Event

Input for Event Jump

External Event Input Setup Time for Event

Advance

(See Td6 in Figure 1--3 on page 1--26)

170 ns to 270 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 1--7 on page 1--27)

(CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock

period when the External Clock is used.)

74AVC16244, Positive True, 1 k Ω to GND

The V

150 ns (event filter: off)

Half Channel Mode: 54 to 61 Clocks + 180 ns before the next block

Full Channel Mode: 27.5 to 31 Clocks + 180 ns before the next block

(See Td9 in Figure 1--4 on page 1--26)

Half Channel Mode: 180 ns before the rising edge of the 5th clock output pulse from

the last of the previous block (See Td10 in Figure 1--5 o n page 1--26)

Full Channel Mode: 180 ns before the rising edge of the 3rd clock output pulse from

the last of the previous block (See Td11 in Figure 1--6 on page 1--27)

of the input receiver is variable and the same as the Vccof the output driver.

cc

1- 16

TLA7PG2 Pattern Generator Module Service Manual

Page 39

Table 1- 13: P6474 LVCMOS probe (Cont.)

(CLK

(CLK2isfrom

2.5nsto5nswhentheInternalClockisuse

d.Itisthesameason

e

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +3.3 V

Series Termination Resistor: 75 Ω

Load: 510 Ω+20pF

Characteristic Description

Mainframe External Signal Input to PG Probe

Data Output

For Advance:

Specifications

Using signal 1 or 2

Using signal 3 or 4

For Inhibit:

Using signal 1 or 2

Using signal 3 or 4

PG Probe Clock Output to Mainframe External

Signal Output

Using signal 1 or 2

Using signal 3 or 4

200 ns to 300 ns + 1 to 2 CLK2

230 ns to 330 ns + 1 to 2 CLK2

2isfrom 2.5 ns to 5 nswhen the InternalClockisused.Itisthesameas one

clock period when the External Clock is used.)

100 ns to 200 ns + 2 to 3 CLK (Half Channel Mode)

100 ns to 200 ns + 1.5 to 2.5 CLK (Full Channel Mode)

130 ns to 230 ns + 2 to 3 CLK (Half Channel Mode)

130 ns to 230 ns + 1.5 to 2.5 CLK (Full Channel Mode)

25 ns --5 CLK (Half Channel Mode)

25 ns --3 CLK (Full Channel Mode)

34 ns --5 CLK (Half Channel Mode)

34 ns --3 CLK (Full Channel Mode)

TLA7PG2 Pattern Generator Module Service Manual

1- 17

Page 40

Specifications

V

p

,

Vol

--3Vto+

6.7

5,10mVste

p,into1MΩ

V

V

V

Table 1- 14: P6475 Variable probe

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: Voh +2 V, Vol 0 V

Slew Rate: 2.5 V/ns

Delay Range: 0

Delay Time: 0 ns

Load: 50 Ω

Characteristic

Description

Maximum Clock Frequency

Delay Range: 0

Delay ≤ 10 ns

Delay Range: 0

Delay ≥ 10 ns

Delay Range: 1,2,3 30 MHz 30 MHz

Number of Data Outputs 8 (CH0 to CH7)

Number of Clock Outputs 1

Number of Strobe Outputs 0

Number of External Event Inputs 2

Number of External Inhibit Inputs 1

Clock Output Polarity Positive or Negative

Data Format CH0 to CH5: NRZ

CH6 and CH7: NRZ, R1 or RZ (independent)

Output Impedance 50 Ω

Output Level

ol -- 3Vto +6.75,10 mVste

Full CH Mode Half CH Mode

134 MHz 268 MHz

134 MHz 268 MHz

into1MΩ

Voh

oltage Swing

Control

--2.75Vto+7V,10mVstep,into1MΩ

250 m

p-p

CH0 to CH5: Common

CH6, CH7, CLK: Independent

Accuracy

± 3% of value ± 0.1 V

Output Current

Sink

Source

<--30 mA

<+30 mA

Supported Channel Mode Half and Full

1- 18

to 9

p-p

TLA7PG2 Pattern Generator Module Service Manual

Page 41

Specifications

Table 1- 14: P6475 Variable probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: Voh +2 V, Vol 0 V

Slew Rate: 2.5 V/ns

Delay Range: 0

Delay Time: 0 ns

Load: 50 Ω

Characteristic Description

Delay Channel CH6 and CH7 (Independent)

Delay Time Delay Range Minimum Delay Maximum Delay

0 0 ns 20 ns

1 15ns 30ns

2 25ns 40ns

3 35ns 50ns

With reference to CH0, CH6, CH7 independent.

Delay Resolution 10 ps

Delay Accuracy ±(3%ofDelayTime)± 0.8 ns (to CH0)

(For delay range of 1, 2, and 3 this is only for rising edge. The falling edge will be

delayed approximately 4 ns from the setting value.)

CH6 Output Mode The following five modes are available:

Normal

CH6 or CH7

CH6 and CH7

CH6 or (not CH7)

CH6 and (not CH7)

Slew Rate Control 0.5 V/ns to 2.5 V/ns, 100 mV step

Rise/Fall Time

20 % to 80 % at maximum slew rate,

load: 1 M Ω +<10pF

Rise/Fall Time

Rise 550 ps

Fall 640 ps

Rise 430 ps

20 % to 80 % at maximum slew rate,

load: 50 Ω

Fall 510 ps

TLA7PG2 Pattern Generator Module Service Manual

1- 19

Page 42

Specifications

Table 1- 14: P6475 Variable probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: Voh +2 V, Vol 0 V

Slew Rate: 2.5 V/ns

Delay Range: 0

Delay Time: 0 ns

Load: 50 Ω

Characteristic Description

Data Output Skew < 295 ps between all data output pins of all modules in the mainframe after

intermodule skew is adjusted manually

< 280 ps between all data output pins of all probes of single module

< 250 ps between all data output pins of a single probe

Data Output to Clock Output Delay 940 ps (See Td2 in Figure 1--1 on page 1--25)

External Clock Input to Clock Output Delay 62 ns (See Td1 in Figure 1 --1 on page 1--25)

External Inhibit Input to Output Enable Delay 30 ns for Data Output (See Td4 in Figure 1--2 on page 1--25)

External Inhibit Input to Output Disable Delay 28 ns for Data Output (See Td5 in Figure 1--1 on page)

Probe D Data Output to Output Enable Delay

--100 ps for Data Output (See Td4 in Figure 1--2 on page 1--25)

(for Internal Inhibit)

Probe D Data Output to Output Disable Delay

(for Internal Inhibit)

External Event Input to Clock Output Setup

(for inhibit) event-filter: off

External Event Input Delay to Data Output for

Advance

External Event Input and Inhibit Input

Polarity

Impedance

Threshold:

Level

Resolution

Minimum Pulse Width

--4.4 ns for Data Output (See Td5 in Figure 1--2 on page 1--25)

Full Channel mode: 1.5 Clocks +180 ns

Half Channel mode: 2 Clocks + 180 ns

(See Td6 in Figure 1--3 on page 1--26)

170 ns to 270 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 1--7 on page 1--27)

(CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock

period when the External Clock is used.)

Positive True

1kΩ to GND

--2.5 V to +2.5 V Event and Inhibit are independent

20 mV

150 ns (event filter: off)

1- 20

TLA7PG2 Pattern Generator Module Service Manual

Page 43

Table 1- 14: P6475 Variable probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: Voh +2 V, Vol 0 V

Slew Rate: 2.5 V/ns

Delay Range: 0

Delay Time: 0 ns

Load: 50 Ω

Characteristic Description

External Event Input

Specifications

Setup Time of Event

Input for Event Jump

Setup Time of Event Input for Event Advance Half Channel Mode: 180 ns before the rising edge of the 5th clock output pulse from

Half Channel Mode: 54 to 61 Clocks + 180 ns before the next block

Full Channel Mode: 27.5 to 31 Clocks + 180 ns before the next block

(See Td9 in Figure 1--4 on page 1--26)

the last of the previous block (See Td10 in Figure 1--5 on page 1--26 )

Full Channel Mode: 180 ns before the rising edge of the 3rd clock output pulse from

the last of the previous block (See Td11 in Figure 1--6 on page 1--27)

TLA7PG2 Pattern Generator Module Service Manual

1- 21

Page 44

Specifications

Usingsignal1or2

100to200ns+2to3CLK(HalfChannelMode)

Table 1- 14: P6475 Variable probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: Voh +2 V, Vol 0 V

Slew Rate: 2.5 V/ns

Delay Range: 0

Delay Time: 0 ns

Load: 50 Ω

Characteristic Description

Mainframe External Signal Input to PG Probe

Data Output

For Advance:

Using signal 1 or 2

Using signal 3 or 4

For Inhibit: (Output Enable)

Using signal 3 or 4

For Inhibit: (Output Disable)

Using signal 1 or 2

Using signal 3 or 4

PG Probe Clock Output to Mainframe External

Signal Output Delay

Using signal 1 or 2

200 to 300 ns + 1.5 to 2.5 CLK2

230 to 330 ns + 1.5 to 2.5 CLK2

(CLK2 is from 2.5 ns to 5 ns when the Internal Clock is used. It is the same as one

clock period when the External Clock is used.)

100 to 200 ns +1.5 to 2.5 CLK (Full Channel Mode)

130 to 230 ns + 2 to 3 CLK (Half Channel Mode)

130 to 230 ns + 1.5 to 2.5 CLK (Full Channel Mode)

100 to 200 ns + 2 to 3 CLK (Half Channel Mode)

100 to 200 ns +1.5 to 2.5 CLK (Full Channel Mode)

130 to 230 ns + 2 to 3 CLK (Half Channel Mode)

130 to 230 ns + 1.5 to 2.5 CLK (Full Channel Mode)

19 ns --5 CLK (Half Channel Mode)

19 ns --3 CLK (Full Channel Mode)

Using signal 3 or 4

1- 22

28 ns --5 CLK (Half Channel Mode)

28 ns --3 CLK (Full Channel Mode)

TLA7PG2 Pattern Generator Module Service Manual

Page 45

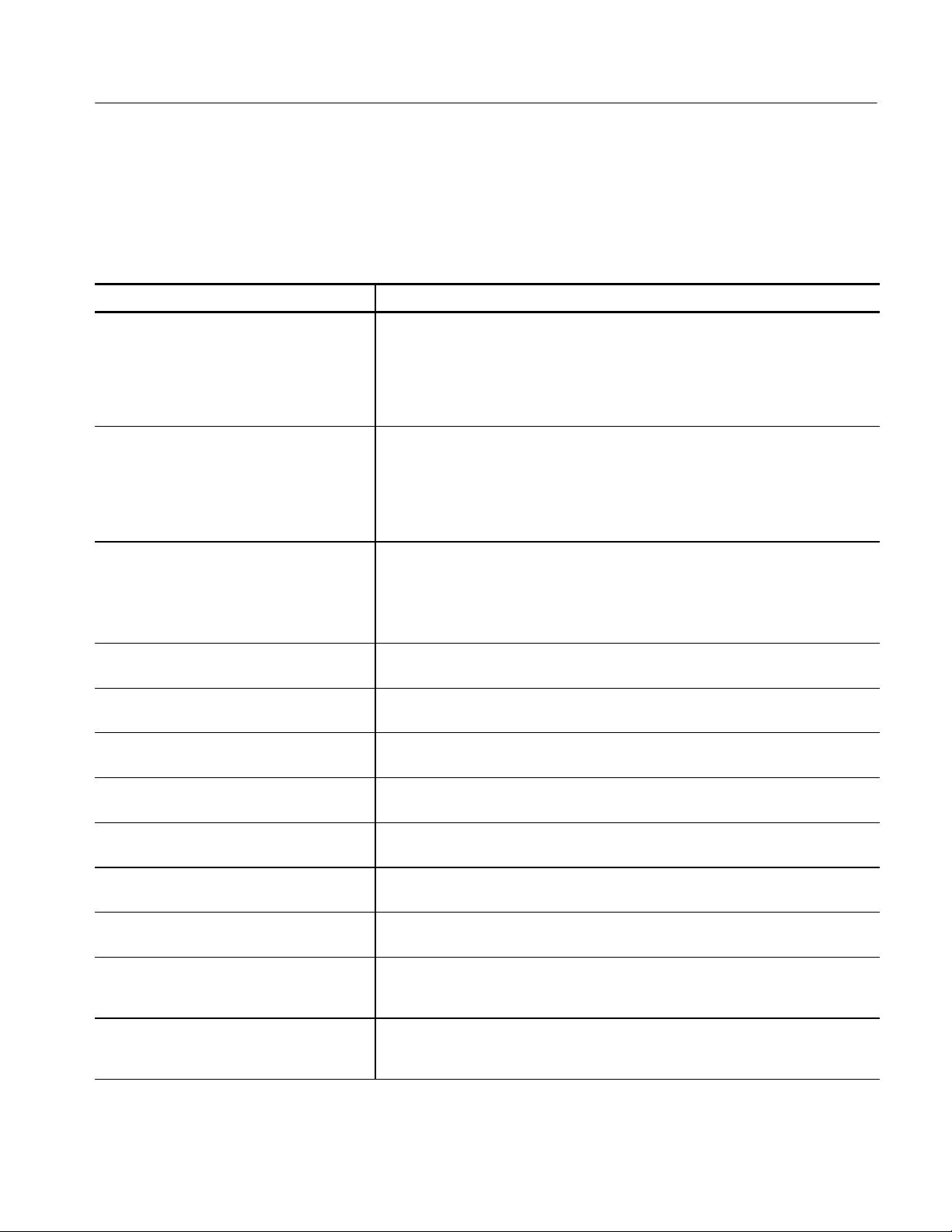

Table 1- 15: Power Supply (P6475 only)

Characteristic Description

AC Line Power

Voltage rating 100 -- 240 V AC

Voltage range 90 -- 250 V AC

Frequency range 50 to 60 Hz

Maximum power 35 W

Maximum current 2A

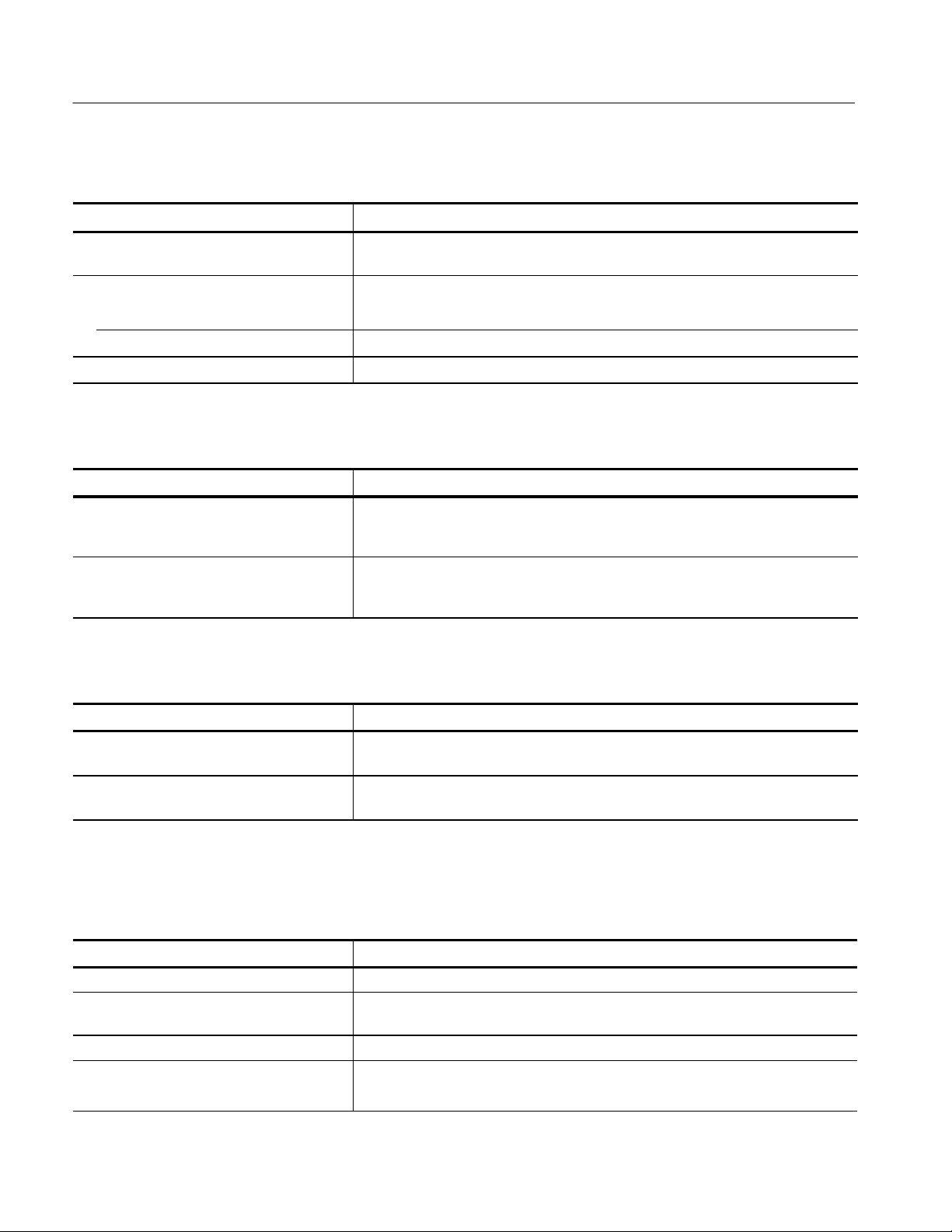

Table 1- 16: Atmospherics

Characteristic Description

Temperature

Operating: +0°Cto+50°C

Specifications

Nonoperating: --20°Cto+60°C

Relative Humidity

Operating: 20% to 80% (No condensation)

Maximum wet-bulb temperature 29.4°C

Nonoperating: 5% to 90% (No condensation)

Maximum wet-bulb temperature 40.0°C

Altitude

Operating: Up to 4.5 km (15,000 ft)

Maximum operating temperature decreases 1°C

Nonoperating: Up to 15 km (50,000 ft)

Table 1- 17: Dynamics characteristics (P6470, P6471, P6472, P6473, and P6474)

Characteristic Description

Vibration

Operating: 3.038 m/s2(0.31 G

Nonoperating: 24.108 m/s2(2.46 G

, 5 Hz to 500 Hz

rms)

),5Hzto500Hz

rms

TLA7PG2 Pattern Generator Module Service Manual

1- 23

Page 46

Specifications

Table 1- 17: Dynamics characteristics (P6470, P6471, P6472, P6473, and P6474) ( Cont.)

Characteristic Description

Shock

Nonoperating: 294 m/s2(30G), half-sine, 11 ms duration,

3 shocks per axis in each direction (18 shocks total)

Table 1- 18: Dynamics characteristics (P6475)

Characteristic Description

Vibration

Operating: 3.038 m/s2(0.31 G

Nonoperating: 24.108 m/s2(2.46 G

Shock (P6475 only)

Nonoperating: 588 m/s2(60G), half-sine, 11 ms duration,

3 shocks per axis in each direction (18 shocks total)

, 5 Hz to 500 Hz

rms)

),5Hzto500Hz

rms

Table 1- 19: Probe cables

Characteristic Description

Dimensions

Length

Length 3.3 m (10.83 ft) Time alignment cable

1.5 m (5 ft) Standard probe cable

Table 1- 20: Twisted lead set

Characteristic Description

Dimensions

Length

25.4 cm (10 in)

1- 24

TLA7PG2 Pattern Generator Module Service Manual

Page 47

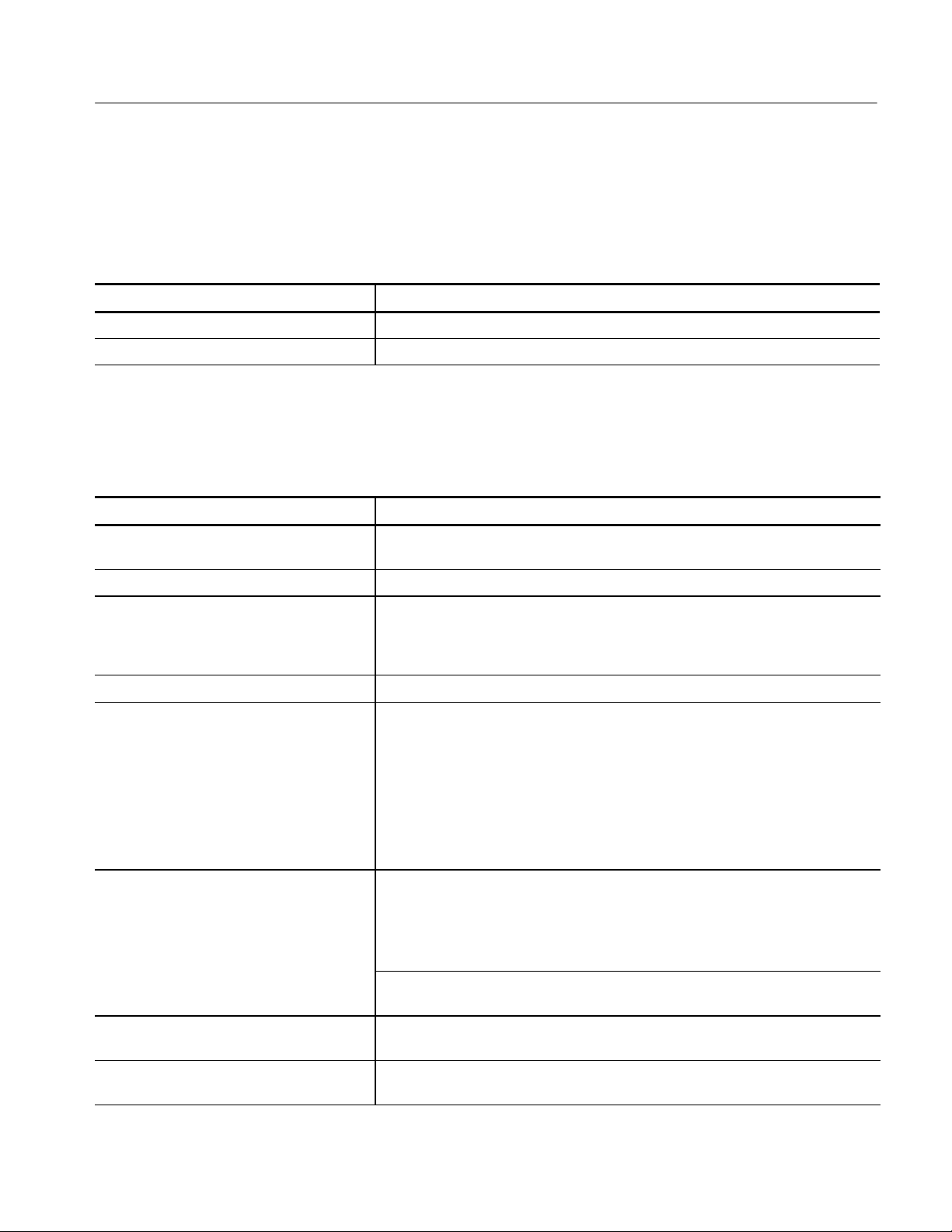

Table 1- 21: Certifications and compliances for P6475

Category Standards or description

Safety

Third party certification UL 3111-1

CSA C22.2 No.1010.1

Self-Declaration EN61010-1 with second amendment

Pattern Generator Module Timing Diagrams

Figures 1--1 through 1--6 show the pattern generator timing diagrams. The

diagrams apply to all probes unless otherwise stated.

External clock Input

Specifications

Td1

Clock Output

Td2

Data Output

Td3

Strobe Output

(strobe delay = zero)

Figure 1- 1: Clock and strobe timing diagram

Inhibit Input or

Probe D data Output

Td4

Data Output

Td5

10%

Figure 1- 2: P6470, P6472, P6473, and P6474 inhibit timing diagram

TLA7PG2 Pattern Generator Module Service Manual

90%

1- 25

Page 48

Specifications

Event

Input

Td6

Clock

Output

Data

Output

Td6

Figure 1- 3: P6470, P6472, P6473, and P6474 external event for inhibit timing

diagram

Event Input

Td9

Data Output Current Block Jump Target Block

Figure 1- 4: External event for jump t iming diagram

1- 26

Event

Input

Td10

Clock

Output

End of previous block

Figure 1- 5: External event for half channel advance timing diagram

TLA7PG2 Pattern Generator Module Service Manual

Block Output

after the event

Page 49

Event

Input

Td11

Clock

Output

End of previous block Block Output

Figure 1- 6: External event for full channel advance t iming diagram

Event

Input

Td12

Clock

Output

Specifications

after the event

Figure 1- 7: External event for delay to data output for advance diagram

P6470 and P6471 Probe Environmental Characteristics

Table 1- 22: P6470 TTL/CMOS probe and P6471 ECL probe

Characteristic Description

Vibration

Operating: 0.31 G

Nonoperating: 2.46 G

Shock

Nonoperating: 294 m/s2(30G), half-sine, 11 ms duration,

3 shocks per axis in each direction (18 shocks total)

, 5 to 500 Hz

rms

, 5 Hz to 500 Hz

rms

Block Output

after the event

TLA7PG2 Pattern Generator Module Service Manual

1- 27

Page 50

Specifications

Certifications

Table 1- 23: Certifications and compliances

Category Standards or description

EC Declaration of Conformity -EMC

Australia/New Zealand

Declaration of Conformity -EMC

General EMC To ensure compliance with EMC requirements, only high quality shielded cables having a reliable,

Meets intent of Directive 89/336/EEC, amended by 93/68/EEC for Electromagnetic Compatibility

when configured with sampling head modules designed for use with this instrument as identified in

this manual. Compliance was demonstrated to the following specifications as listed in the Official

Journal of the European Union:

EN 61326 EMC Requirements for Electrical Equipment for Measurement,

Control and Laboratory use.

Class A Radiated and Conducted Emissions

IEC 61000-4-2 Performance Criterion B

IEC 61000-4-3 Performance Criterion A

IEC 61000-4-4 Performance Criterion B

IEC 61000-4-5 Performance Criterion B

IEC 61000-4-6 Performance Criterion A