Page 1

ffitonix

COMMITTED

TO EXCELLENCE

WARNING

THE FOLLOWING

SERVICING

INSTRUCTIONS

ARE FOR

USE

BY

QUALIFIED

PERSONNEL

ONLY.

TO AVOID PERSONAL INJURY,

DO NOT

PERFORM ANY

SERVICING OTHER

THAN

THAT

CONTAINED

IN

OPERATING

INSTRUCTIONS

UNLESS

YOU ARE

QUALIFIED

TO DO

SO.

PLEASE

CHECK FOR

CHANGE INFORMATION

AT THE REAR

OF THIS MANUAL.

7603/R7603

Tektronix,

Inc.

P.O.

Box

500

Beaverlon,

Oregon 97077

070-1

429-00.

Product

Grouo 42

oscrLLoscoPE

SERVICE

INSTRUCTION

MANUAL

First

Printing

JUN 1972

Revised

DEC

1984

Serial Number

Page 2

Copyright ' 1972

Tektronix,

Inc.

Ail

rights

reserved.

Contents

of this

publication

may not

be

reproduced

in

any

form

without

the written

permission

of Tektronix.

Inc.

Products

of

Tektronix,

Inc.

and its

subsidiaries

are

covered

by U.S.

and

foreign

patents

and/or

pending

patents.

TEKTRONIX,

TEK,

SCOPE-MOB|LE.

ano

are

registered

trademarks

of Tektronix,

Inc.

TELEQUtpMENT

is a registered

trademark

of

Tektronix

U.K. Limited.

Printed

in

U.S.A.

Specification

and

price

change

priviteges

are reserved.

INSTRUMENT

SERIAL

NUMBERS

Each instrument

has

a serial number

on a

paiel

insert,

tag,

or

stamped

on the chassis.

The

first

number

or letter

designates the

country

of manufacture.

The

last

five

digits

of

the serial number

are

assigned

sequentially

and

are

unique to

each instrument.

Those

manufactured

in

the

United States have

six unique

digits.

The

country

of

manufacture

is identified

as

follows:

8000000

Tektronix,

Inc.,

Beaverton,

Oregon,

USA

100000

Tektronix

Guernsey,

Ltd.,

Channel

lslands

200000

Tektronix

United Kingdom,

Ltd.,

London

300000

Sony/Tektronix,

Japan

700000

Tektronix

Holland,

NV,

Heerenveen.

The Netherlands

Page 3

SECTION 1

SECTION

2

SECTION

3

OPERATING I NSTRUCTIONS

Prel

iminary Information

Display Definitions

Plug-in

Units

Controls and Connectors

Operating Checkout

Simplified

Operating

Instructions

General Operating

Information

SPECIF ICATION

Vertical Deflection

System

Triggering

Horizontal

Deflection

System

Cal i

brator

External

Z Axis

Input

Outputs

Character

Generator

Display

(CRT)

and

Options

Power

Source

Signals

Out

Environmental

Physical

Standard

Accessories

7600-Series

System

Specifications

CALIBRATION

Test Equi

pment

Required

Calibration

Procedure

Power

Supply

Display

and Z-Axis

Vertical

Deflection

System

Triggering

System

Horizontal

Deflection

System

Cal i brator

Signals

In

& Out

Readout

Operation

Readout

Gate Trig'd Operation

TABLE

OF

CONTENTS

Page

1-1

1-2

t-J

1-3

1-?

1-7

1-9

2-1

2-2

22

23

23

z-+

z-4

2-5

25

z-6

2-6

2-6

7603/R7603

Service

SECTION 4

CIRCU IT DESCR

IPTION

Block Diagram

Circuit

Operation

Logic Fundementals

Main Interface

Logic Circuit

Trigger

Selector

Vertical

Interface

Vertical Amplifier

Horizontal Amplifier

Calibrator

and Front Panel

Switching

CRT Circuit

Low-Voltage

Power

Supply

Signal

Out

Board

Readout

System

SECTION 5 MAINTENANCE

Preventive

Maintenance

Troubleshoo

ting

Location

of

Circuit Boards

Electrode

Configuration for

Semiconductors

Corrective

Maintenance

SECTION 6 RACKMOUNTING

Instrument

Dimensions

Rack Dimensions

Slide-Out Tracks

Mounting Procedure

SECTION

7

ELECTRICAL

PARTS

LIST

SECTION

8 DIAGRAMS

and

CIRCUtT

BOARD

ILLUSTRATIONS

SECTION

9

IV]ECHAN

ICAL PARTS

LIST

CHANGE INFORIMATION

Page

4-1

A1

a-l

z+-J

4-6

4-6

4-16

4',ts

4-20

4-21

4-23

4-24

4-27

4-31

4-31

c-l

5-2

5-4,5-5

5-7

5-1 0

o-l

b-l

o-l

61

31

3-4

3-5

J-O

39

J-tt

313

J-tc

J- to

317

3-18

REV JUN 1981

Page 4

7603/R7603

SAFETY SUMMARY

The

general

safety

information

contained

in this

summary

is for servicing

personnel.

Specific

warnings

and cautions will

be

found throughout the

manual where they apply, but

may not

appear

in

this summary.

TERMS

IN THIS MANUAL

CAUTION statements

identify conditions or

practices

that

could

result in

damage

to the equipment

or other

property.

WARNING statements

identify

conditions

or

practices

that could

result in

personal

injury

or

loss

of

life.

AS MARKED ON EQUIPMENT

CAUTION

indicates

a

personal

injury hazard not immediately

accessible as one

reads the marking,

or a

hazard

to

property

including the equipment

itself.

DANGER

indicates

a

personal

injury hazard immediately

accessible as one

reads the marking.

SYMBOLS

IN THIS MANUAL

€\

(ry

Static-Sensitive

Devices

,\

A

This

symbol

indicates

where

applicable cautionary or other

information is to be found.

AS MARKED ON EQUIPMENT

+

DANGER-HIgh

vortage.

Protective

ground

(earth)

terminal.

ATTENTION-refer

to manual.

WARNINGS

POWER SOURCE

This

product

is intended to

operate

from

a

power

source

that will not apply

mare

than

250 volts rms

between the supply

conductors or between either

supply conductor and

ground.

A

protective

ground

connection by

way

of

the

grounding

conduc-

tor in the

oower

cord is essential

for

safe

operation.

USE THE PROPER

POWER CORD

Use only

the

power

cord and connector

specified

for

your

product.

Use

only a

power

cord that

is in

good

condition.

GROUNDING

THE PRODUCT

This

product

is

grounded

through the

grounding

conductor of

the

power

cord.

To avoid electrical shock,

plug

the

power

cord

into a

properly

wired receptacle before

making

connections

to the

product

input

or output terminals.

A

protective

ground

connectron by

way

of

the

grounding

conductor

in the

power

cord is essential

for

safe operation.

A

\:-/

A

tl

REV DEC

1983

Page 5

7603/R7603

DANGER ARISING FROM LOSS

OF GROUND

.

Upon

loss

of

the

protective-ground

connection,

all accessible conductive

parts

(including

knobs

and controls that may

appear

I

to

Oe

insulating),

can

render

an electric shock.

USE THE PROPER FUSE

To avoid hazard, use

only

the fuse

specified

in

the

parts

list for

your

product,

and

which is

identical in type, voltage

rating,

and

current rating.

DO NOT OPERATE IN EXPLOSIVE

ATMOSPHERES

To

avoid explosion,

do

not

operate this

product

in an

atmosphere of explosive

gases

unless it

has

been specifically

certified for

such ooeration.

DO NOT

SERVICE

ALONE

Do

not

perform

internal

service or adjustment

of

this

product

unless

another

person

capable

of

rendering

first

aid and

resuscitation is

oresent.

USE CARE WHEN SERVICING WITH POWER

ON

Dangerous voltages

exist

at several

points

in

this

product.

To

avoid

personal

injury,

do not touch

exposed

connections

and

components

while

power

is

on.

Disconnect

power

before removing

protective panels,

soldering, or

replacing

components.

SILICONE

GREASE

HANDLING

Handle silicone

grease

with

care.

Avoid

getting

the silicone

grease

in

your

eyes. Wash hands

thoroughly

after

using silicone

grease.

il|

ADD

DEC 1983

Page 6

?

l:

*

#

I

t

I

I

A

t;

,?g

S:ffi

s

ate"":

'|

r

l:,1

'iti'.

s

,g'

i$iiil

':&

\,-Tv

*€-*

7603

Features

The

TEKTRoNIx

7603

oscilloscope

is a

solid

state,

light

weight

instrument

designed

for

general-purpose

measuring

applications.

This instrument

has

three

plug-in

compartments

that

accept

TEKTRONIX

7-series

plug-in

units

to form

a

complete

measurement

system.

The nrvo

plug-in

compartments

on the

left

are

connected

to

the

vertical

deflection

system.

The right

plug-in

compartment

is connected

to

the horizontal

deflection

system.

Electronic

switching

between

the

vertical

plug-in

compartments

allows

a multi-trace

vertical

display.

The flexibility

of

this

plug-in

feature

and

the

variety

of

plug-in

units

available

allow this

system

to

be

used for

many

measurement

applications.

ln

addition,

the

instrument

contains

a

readout

system

to

provide

a CRT

display

of alphanumeric

information

from

the

plug-in

units.

Data

such

asdeflection

factor,

sweep

rate,

etc.

can be

encoded

and displayed

on the

CRT.

This

instrument

features

a large-screen,

8 X

10 division

display;

each

division

equals

1.22

centimeters.

The

CRT

provides

small

spot

size

and fast

writing

speed.

Regulated

DC

power

supplies

assure

that

performance

is

not

affected

by

variations

in

line

voltage

and frequency,

or by

changes

in

the load

due

to

the

varying

power

requirements

of

the

plug-in

units. Maximum

power

consumption

is

about

170 watts

(60

hertz,

115_volt

line).

I

If.'"".'"'.'''"''".''.''';r'r':":':':

:r':':',ii!d-rc

:

*?*

-

-

-

-!-

t

rilj

h,;;.;,r'

_#,

*

,r

.,,.

1S,",

rSi&

*

llttt

t*,* ::r'1,*,,a

l?:,1*

t$s*

&

&

iv

REV

AUG

1983

Page 7

OPERATING

INSTRUCTIONS

General

To

effectively

use the 7603,

the

operation

and

capabilities

of the

instrument

must

be known.

This

section

describes

the

operation of the front-

and rear-panel

controls

and connectors

and

gives

simplified

and

general

operating

information.

PRELIM

INARY IN FORMATION

Operating

Voltage

WA RI'TG

This instrument

is

designed for

operation from

a

power

source with

its neutral

at or

near earth

(ground

)

potential

with

a separate

safety-earth

conductor.

lt is not intended

for

operation

from

two

phases

of a multi-phase

system,

or across

the legs

of a

si ng le-ph

ase, th ree-w

i re system.

The 7603

can be

operated

from either

a 110-volt

or

a

.

220-volt

nominal line-voltage

source. ln

addition.

three

)

operating ranges

can

be

selected

within

each nominal

line

voltage

source. The

voltage-selector

jumper

on the Rectifier

board

(see

Fig.

1-1)

allows selection

of

the

operating

voltage. To

convert

the

instrument

from

one regulating

range

to

another, first disconnect

the instrument

from

the

power

source. Then,

slide out

the

power

unit as

described

in

the Maintenance

section. Remove

the

voltage-selector

jumper

and re-install it

on the

set of

pins

which represent

the desired regulating

range.

Select

a

range

which is

centered

about the

average

line

voltage

to which the

instrument

is

to be

connected

(see

Table 1

-

1 ) .

TABLE

1-1

Regulating

Range

and Fuse Data

Pins

Regulating

Range

Selected 110-volts

nominal

220-volts

nominal

LOW

90 to 110

volts

180 to 220

volts

MED

gg

to 121 volts

198

to 242 volts

Hl

108

to 132 volts

218

to

262

volts

Line Fuse 3.2

A

slow-blow

1.6 A

slow-blow

To

convert

from 11O-volts

to 220-volts

nominal

line

I

voltage,

or vice versa, remove

the voltage-selector

jumper

z

and

replace

it

with the spare

jumper (stored

on

pins

adjacent

to

voltage

selector

area). The

jumpers

are color-

REV

NOV

1981

I

Section 1

-7

603l R7

603

Service

Fig.

1-1.

Locations of voltage-selector

jumper,

spare

jumper,

and

ALT

FUSE

in

power

unit

(7603

strown).

coded

to indicate the nominal

voltage

for

which

they are

intended;

brown for 110-volt

nominal

operation

and

red

for

220.uolt

nominal

operation.

Change

the line fuse

to

provide

protection

for the

selected nominal

line voltage.

Use the

fuse located in

the ALT FUSE

holder

on the Rectifier

board

(see

Fig. 1-1)

or see Table

1-1 for value.

Also,

change

the line-cord

plug

to

match

the

power-source

receptacle

or

use

a suitable

adapter.

Power

Cord

Conductor

ldentif

ication

Conductor

Ungrounded

(Line)

Grounded

(Neutral

)

Grounding

(Earthing)

Color

Alternate

Color

Green-Yellow

Green-Yellow

The 7603 is

designed

to be used

with a three-wire

AC

power

system. lf

a

three-

to two-wire

adapter is

used to

connect

this instrument

to a two-wire

AC

power

svstem,

be

sure

to connect

the

ground

lead

of

the adapter to

earth

(ground).

Failure

to complete

the

ground

system may

allow

the

chassis

of this

instrument

to be elevated

above

qround

potential

and

pose

a shock hazard.

Operating

Temperature

The

7603

can be

operated

where

the

ambient

air

temperature is

between

0"C

and

+50oC.

This

instrument

Brown

Bl

ue

Black

White

Page 8

Operating

I nstructions-7603/R7603

Service

can be stored

in

ambient

temperatures between

-55"C

and

+75oC.

After

storage at

temperatures beyond the

operating

limits,

allow

the chassis

temperature to come within the

operating

limits before

power

is

applied.

The 7603

is

cooled

by convection

air

flow

through the

instrument. Components which

require the most cooling

are

mounted

externally

on a heat radiator at the rear.

Adequate

clearance

must be

provided

on all sides to allow

heat to be

dissipated

from the

instrument.

Do not block or

restrict the air flow through the

holes in the cabinet

or

the

heat radiator on the

rear. Maintain the clearance

provided

bv the feet

on

the bottom and allow about two

inches

clearance

on the

top, sides, and rear

(more

if

possible).

The R7603 is cooled

by

air drawn

in through the

air

filter

on

the rear

panel

and

blown

out

through

the

holes on

the right side.

Adequate clearance must be

provided

at

these

locations. Allow at

least

one and one-half

inches

clearance

behind

the air

filter and at least one

inch

on the

right

side.

A thermal cutout

in

this

instrument

provides

thermal

protection

and

interrupts the

power

to

the instrument if

the

internal

temperature

exceeds a safe

operating

level.

Power

is

automatically restored when the

temperature

returns to a safe

level.

Operation

in conf ined

areas or

in

close

proximity

to heat-producing instruments may cause

the thermal cutout to open

more

frequently.

Operating

Position

A bale-type stand

is mounted

on the

bottom

of

this

instrument.

This

stand

permits

the 7603 to be tilted up

about

i0o for

more convenient

viewing.

Rackmounting

Instructions

and

dimensional

drawings for rackmounting

the R7603

are

located in Section

6 of the service manual.

DISPLAY DEFINITIONS

General

The following definitions describe the types

of displays

which

can be

obtained

with a 7603

Oscilloscope svstem

with real-time

amplif

iers,

time-base units,

or

combinations

of these. Use of special

purpose plug-in

units may result in

different

types of displays, which are defined in the

instruction

manuals for these special units. The following

termlnology

will

be used throughout

this

manua,.

1-2

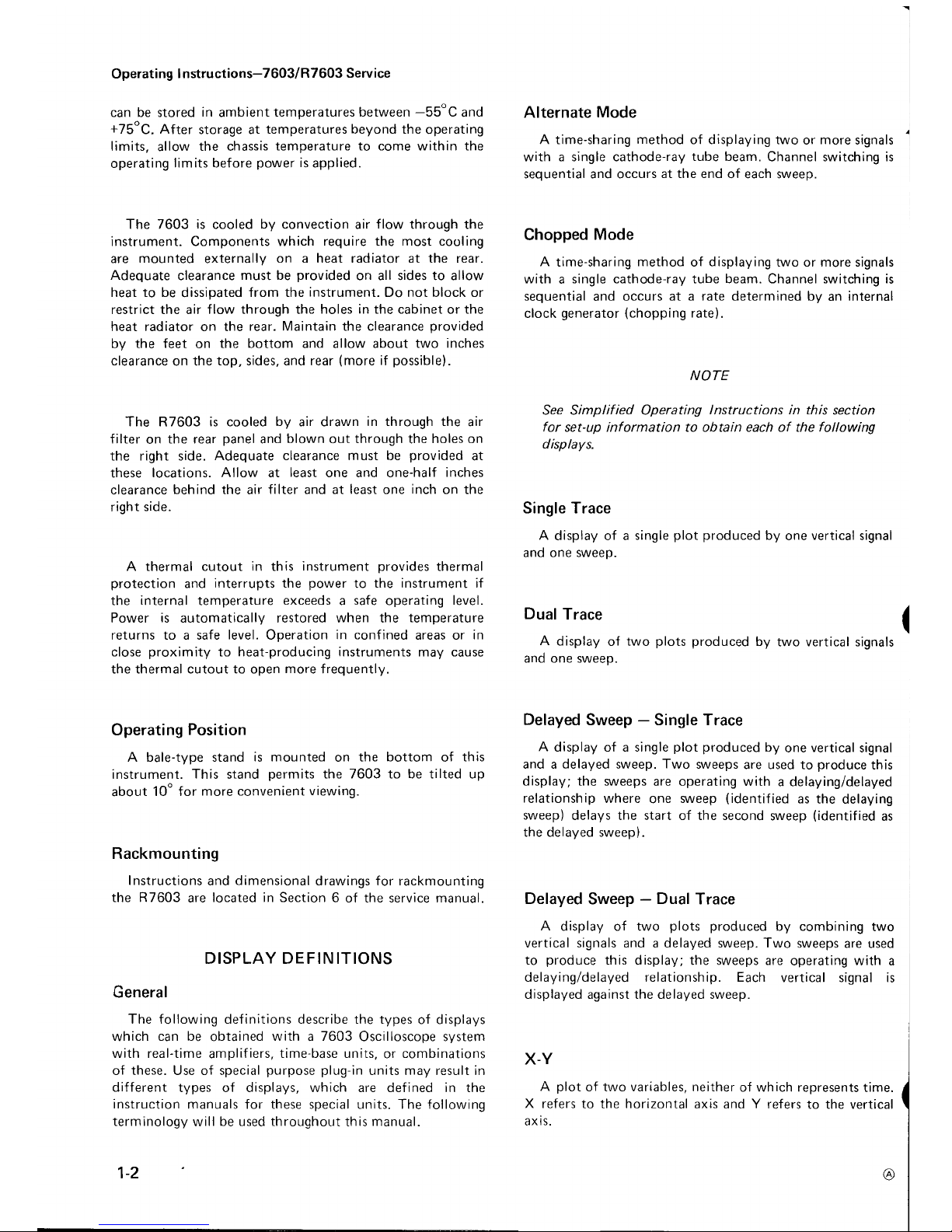

Alternate

Mode

A time-sharing

method

of displaying two

or

more

signals

with a single cathode-ray

tube beam.

Channel switching is

sequential and occurs

at the end

of each sweep.

Chopped

Mode

A

time-sharing

method

of

displaying

two or more signals

with a single cathode-ray tube beam. Channel switching is

sequential

and occurs

at a rate determined by

an

internal

clock

generator

(chopping

rate).

NOTE

See Simplified Operating

lnstructions in this

section

for

set-up information to obtain each of the following

displays.

Single Trace

A

display of a

single

plot produced

by

one

vertical

signal

ano one sweep.

Dual

Trace

A

display

of two

plots

produced

by

two vertical signals

and one sweep.

Delayed Sweep - Single Trace

A

display of a single

plot

produced

by

one

vertical

signal

and a delayed sweep.

Two

sweeps

are used to

produce

this

display; the sweeps

are operating with

a delaying/delayed

relationship

where

one

sweep

(identified

as

the delaying

sweep)

delays the start of the second

sweep

(identified

as

the delayed sweep).

Delayed

Sweep

-

Dual

Trace

A

display of two

plots produced

by combining

two

vertical signals and a delayed sweep. Two

sweeps are used

to

produce

this

display; the sweeps are

operating with a

delaying/delayed relationsh ip. Each

vertical signal is

displayed against the delayed sweep.

X.Y

A

plot

of two variables, neither

of which represents

time.

X

refers to the horizontal

axis and Y refers

to the vertical

ax

is.

@

Page 9

PLUG.IN

UNITS

lGeneral

The 7603

is

designed to accept up to three TEKTRONIX

7-series

plug-in

units.

This

plug-in

feature

allows a variety

of

display combinations

and also allows selection

of band-

width, sensitivity, display mode,

etc. to

meet

the measure-

ment requirements. In

addition, it

allows the oscilloscope

system to be

expanded to meet f uture measurement

requirements.

The

overall

capabilities

of the

resultant

system are

in

large

part

determined by the

characteristics

of

the

plug-in

selected. For complete information

on

plug-ins

available for

use with this

instrument,

see the current

Tektronix,

I nc. catalog.

Plug-ln

Installation

To install

a

plug-in

unit into

one of the

plug-in

compartments, align the slots

in

the top and bottom

of

the

plug-in

with the

associated

guide

rails in

the

plug-in

compartment. Push the

plug-in

unit

firmly into

the

plug-in

compartment until

it locks into

place.

To remove

a

plug-in,

pull

the release latch

on

the

plug-in

unit to disengage it

and

pull

the unit

out of

the

plug-in

compartment. Plug-in

units

can

be removed

or

installed

without turninq

off

the

instrument

power.

It

is

not necessary that

all of the

plug-in

compartments

be filled to operate the

instrument;

the

only

plug-in

units

needed

are those required for the measurement

to

be made.

lHowever,

at environmental extremes,

excess

radiation may

l

'

be radiated into

or out of this

instrument

through the

open

plug-in

compartments. Blank

plug-in panels

are

available

from Tektronix, lnc.

to cover the unused

compartment;

order

TEKTRON lX Part No. 016-0155-00.

When

the

7603 is calibrated in

accordance with the

calibration

procedure given

in

this

instruction

manual, the

vertical and

horizontal

gain

are standardized. This

allows

calibrated

plug-in

units to

be

changed from one

plug-in

compartment

to another without

recalibration. However,

the basic calibration of the individual

plug-in

units should

be checked when

they are

installed in

this system

to

verifv

their

measurement

accuracy. See the operating instructions

section

of the

plug-in

unit instruction manual for verifi-

cation

orocedure.

Special

purpose plug-in

units may have

specific restric-

tions regarding

the

plug-in

compartments in

which

they can

be

installed.

This information

will be

given

in

the instruc-

tion manual

for these

plug-in

units.

NOTE

Later

production

of

rackmount

oscilloscopes

are

pro-

vided

with

support

posts

between the individual

plug-

in

compartments. A

post

or

posts

must

be

removed

if

I

a

multiwidth

plug-in

is to be installed. To remove a

/

post,

unfasten

the screws that secure it at

the top and

bottom

of the

plug-in

housing.

REV

C.

MAY 1978

Operating I nstructions-7603/R7603

Service

CONTROLS

AND

CONNECTORS

The major

controls

for

operation

of the 7603

are located

on the f ront

oanel of the instrument.

F igs.

1-2

and 1-3

provide

a

brief

description

of each

control

ano connector.

More

detailed operating information

is

given

under

General

Operating I nformation.

OPERATING

CHECKOUT

General

The following

Operating Checkout

provides

a

means

of

verifying

instrument

operation

and basic

calibration with-

out

removing

the covers or making

internal

adjustments.

Since

it

demonstrates

the use

of all

controls and connec-

tors,

it

can

also be

used

to

provide

basic

training

on the

operation of

this instrument. lf

re-calibration

of

the 7603

appears to be necessary,

see

the Calibration

procedure

in

Section 3 of this manual.

lf re-calibration

of a

plug-in

unit

is indicated,

see

the

instruction manual

for

the appropriate

plug-in

unit.

Set-Up Information

1. Set

the front-panel controls

as follows:

INTENSITY

FOCUS

BEAM FINDER

GRATICULE ILLUM

VERT MODE

TR IG

SOU RCE

POWER

Cou nterclockwise

M id

ra nge

Pressed in

As

desired

LEFT

VERT

MODE

Pushed

in

2. Connect

the

7603

to a

power

source

which meets

the

voltage

and

frequency

requirements

of this

instrument.

The

applied voltage should

be

near

the center

of

the voltage

range marked

on

the rear

panel

(see

Operating Voltage in

this section for information

on converting

this

instrument

from

one operating voltage to

another).

3. Install TEKTRONIX

7A-series

amplifier

units into

both

the left

and

right

vertical

plug-in

compartments.

Install

a

7B-series

time-base

unit

into

the horizontal

compartment.

4.

Pull

the

POWER

switch

to turn

the instrument

on.

Allow

several minutes

warmup

before

proceeding.

5"

Set both vertical

units for

a def lection

factor

of two

volts/division

and center the vertical

position

controls.

Set

both

vertical

units for AC

input

coupling.

6. Set

the time-base unit

for

a sweep rate

of one

millisecond/division

in

the

auto,

internal

trigger mode.

1-3

Page 10

FUNCTIONS

OF

CONTROLS AND CONNECTORS

Operating

Instructions-7603/R7603

Service

Front

Panel

1.

INTENS|TY-Controls brightness of the display. Control

is

inoperative when

horizontal compartment is vacant.

2. READOUT-Turns

on the

readout display

and controls

the

readout intensity,

3. FOCUS-Provides

adjustment

for

optimum display definition.

4. GRATICULE

ILLUM-Controls

graticule

illumination.

5. BEAM

FINDER-When

pressed.

the scan

is limited

to

within

the

graticule

area.

6. TRIG SOURCE-Selects

source of

internal trigger signal

for

the

time base

plug-in

in the horizontal compartment.

LEFT: The

trigger signal

is

obtained

from the

plug-in

unit in

the left vertical compartment

only.

VERT MODE: Trigger signal automatically

follows

the vertical

display

except in CHOP and ADD; then

the trigger

signal

is the

algebraic sum of the

signals

from

the

left

and

right

vertical

compartments.

RIGHT: The trigger signal

is

obtained

from

the

plug-in

unit in

the

right

vertical compartment

only.

7. POWER-

Switch: Controls

power

to the

instrument.

Light: lndicates

that the

power

saritch is on

and that the

instrument is

connected to a line

voltage

source.

8.

CALIBBATOB-Calibrator outpur

pin

jacks (4V,0.4V,40

mV,

groundl.

Positivegoing

pulse

or DC voltage

selected by

changing internal

jumper.

Repetition rate

is

approximately

one

kilohertz.

9. VERT MODE-Selects vertical mode

of operation.

LEFT:

Signals

from

plug-in

unit in left

vertical

compartment

are displayed.

ALT: Signals

from

plug-in

units

in

both

the

left

and

right

vertical

compartments

are displayed

(dual

tracel.

Display

slrvitched between

vertical

plug-in

units

after each

sareep.

ADD:

Signals

from

plug-in

units in

both the left

and

right

vertical

compartments are

algebraically added

and the

sum

is

displayed on the

CRT.

CHOP: Signals

from

plug-in

units in

both

the

left

and right

vertical

compartments

are displayed

(dual

tracel, The display is

switched between vertical

plug-in

units

at approximately

one

megahertz

rate.

RIGHT:

Signals

from

plug-in

unit in right

vertical compart-

ment is displayed.

10. Camera Power

{Not

Labeledl-Three-pin

connector on

CRT

bezel

provides power

output

(+15

Vl. Receives remote

single

sweep

reset

signal

from

compatible

camera systems,

and a

ground pin

connection.

',:l*,ll!l

lra.a,rr'

.t

d;

r,

dhi

*&5i

#

I

.l*

I

ll

*-

L".

Ytn \

\

lv

'

:i.

,

liii

a 1t]1:

I

ia*;,

.

:,:9;

2:9?'

@

#w

ffI;_r

"frii$,

;i-?r

1;,'"m

K

"**

'M

,rr&t

il g .sf

[t*e

Et!t

jl

Rlr

q

* ..i.::,.

1-4

Fig, 1-2, Front-panel controls and connectors.

Page 11

Operating I nstructions-7603/R7603 Service

aaaaaaaaaaaaaaaaaaaaaaaaaa

aa

aaaaaaaaaaaaataaa

aa aaaaaaataaataaaaa

aarr!.i!.aaaaaaaaaaaaaaaaa

m

wans

{uar}

a

1.9-{tls

IMrxJ

:

I

usr

" a

AI fl6Y, i0 Xr

r:::l

J 2A

StoW

rOo

lrmV

mt6t

55i$oy00T17601l

=ll6a$0w200,?48vnAncr

ntM0il

tMSt

li

t7613l82l

qLrtBiarl

IU6l

rrySt0t

?3?t

Wil:

t$ s3 R rs€r

r!

s

trt z AIts r{

ilSVMtX:5t0n

f:i

lil

i",,,,

,l

&w

!$rMl

*m

ffir

g*w

strsry

W$ira

&#'

wryw

*#:r.

f1

8d'

t

*gw-*q

ffiM

C@&m @Wt

ffi1il

Es"1*d*ffit

6tH#s*84 @#4Sl

**{}il

*-{eq rull

-,*q{ffiqtr

*"u*r

a

t#cl#!i'

m!

E€c{r"EI

If**lt

!:tnlf-4r

;5 {,P*'{

s. &{

ryl&ri#.@

*elE&F€#d$

ry'

is;

-

*w*

$-ft6r

T

's{t

' .

qtes.q

-

"4S

'-Y

*ttl

*-.v m

tu,Eil +il

st l"

d r*s453t

.4i''g!

s

+![

t*D t,

.,f

ei&gn

16

w

fi sd

tfl !]*-+l

-ry

.{.*

q

,

S{{n

lse:s*ffi

ryqigs. sM4*€e3K

Y'!&&

!n

.i.- - :

.

D0ltltf

5L[NA1

or-F'ASl5'iru

r.",,.,,,..,_

I

1!

s ,N5:qUM-Nr

<

Cn\NrClt0

I

*" "'

. I tu:

r=J

r

,ii

.:;,itiis I

.

ou'

lrxsrft

frr0ilrNLv

5J

r0

d00

i/

I

"..!,

,0..,

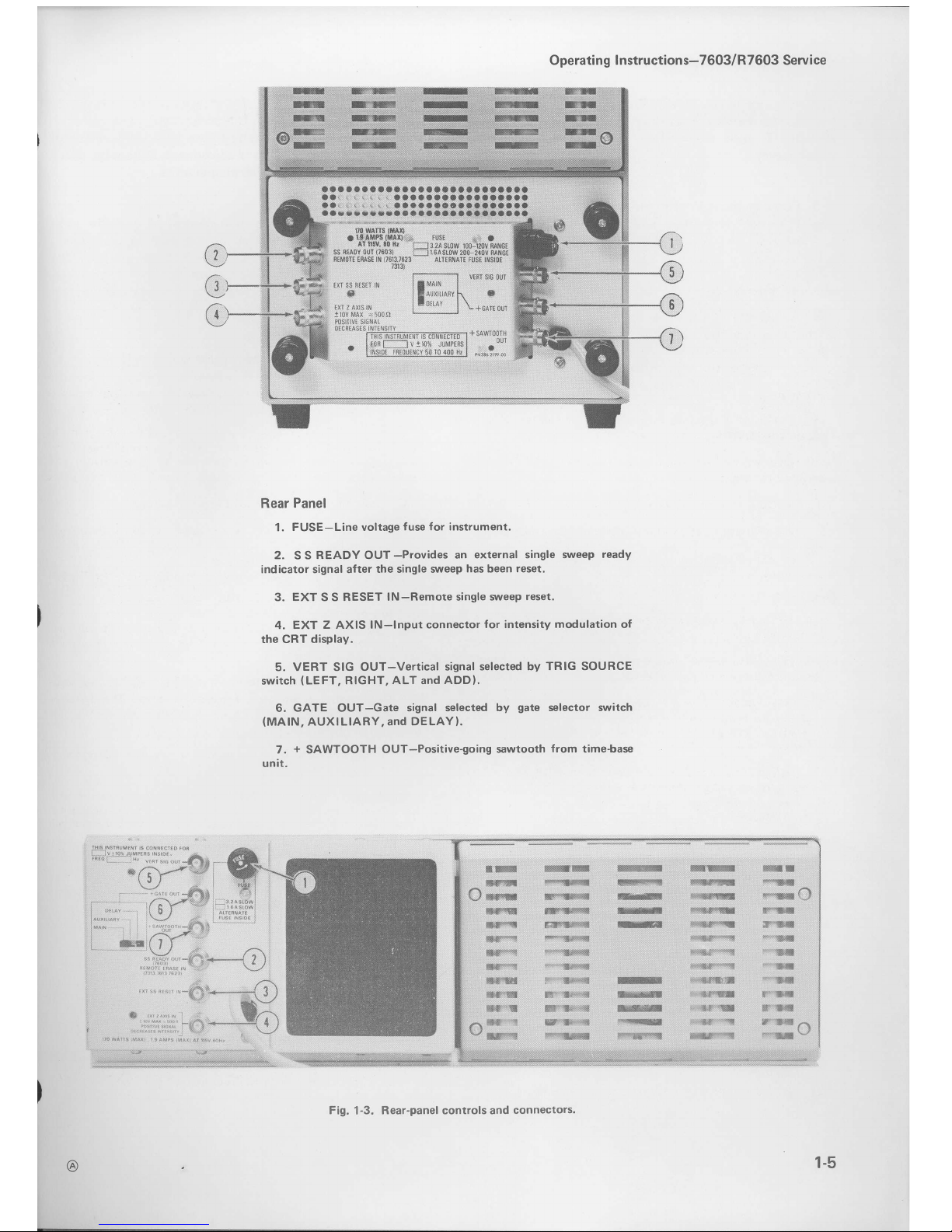

Rear

Panel

1.

FUSE-Line voltage

fuse

for

instrument.

2. SS

READY OUT-Provides

an external single

sweep ready

indicator signal

after the single s,veep

has been reset.

3.

EXT

S S

RESET

lN-Remote single wveep

reset.

4.

EXT Z AXIS

lN-lnput connector

for intensity modulation of

the cRT display.

5. VERT SIG

OUT-Vertical

signal selected by

TRIG SOURCE

switch

(LEFT.

RIGHT,

ALT and ADDI.

6.

GATE OUT-Gate

signal selected by

gate

selector switch

(MAlN,

AUXILIARY, and

DELAYI.

7. + SAWTOOTH

OUT-Positive-going

sawtooth

from time-base

unit.

@

Fig, 1-3, Rear-panel controls and

connectors.

1-5

Page 12

Operating

I nstructions-7603/R7603

Service

7.

Advance

the

INTENSITY

control

until the

trace is

at

the

desired

viewing

level

(near

midrange).

Advance

the

R EADOUT

until the

readout

display

is

at the

desired

viewing

level.

8.

Connect

the 4

V calibrator

pin-jack

to

the input

of

the left

vertical

unit

with a BNC

to

pin-jack

cable

(supplied

accessory).

Display

Focus

9. Adlust

the FOCUS

control

for

a sharp,

well-defined

display

over the

entire trace

length.

lf

a

properly

focused

display

cannot

be

obtained with

the

FOCUS

control.

the

internal

Astigmatism

adjustment

must

be

re-set;

see the

Calibration

section

of this manual.

Trace

Alignment

10. Disconnect

the input

signal

and

position

the

trace

with

the left vertical

unit

position

control

so it

coincides

with

the center

horizontal

line

of the

graticule.

lf

the trace

is

not

parallel

to the center

horizontal

line

of the

graticule,

see Trace

Rotation

adjustment

procedure

in

Calibration

section.

Graticule I

llum ination

11. Rotate

the

GRAT ILLUM

control

throughout

its

range

and notice

that

the illumination

of the

graticule

lines

increases

as the control is

turned

clockwise

(most

obvious

with

tinted f ilter

installed).

Set the

control

so

the

qraticule

lines

are illuminated

as desired.

Vertical

Deflection

System

12.

Connect

the 4

V calibrator

signal

to

the

input

connector

of the left

vertical

unit with

the BNC

to

pin-iack

cable.

Set both

vertical

units for

a deflection

factor

of

one

volt/division.

The

display

amplitude

should

be

four

divisions.

Note

the exact

display

amplitude

for step

15.

13. Notice

that the

position

control

of

onlV the left

vertical

unit has

an effect

on the

position

of the

display.

Position

the

display to

the upper

half

of the

graticule.

14.

Press

the RIGHT

button

of

the VERT

MODE

switch.

Remove

the

calibrator

signal

from

the left

vertical

and connect

it

to

the right

vertical.

The

display

amplitude

should

be

four

divisions

within 0.12

division.

Note

the

exact

display

amplitude

for

the next

step.

i5. A

correct

display in both

steps

12

and 14

indicates

that

the 7603

Vertical

Deflection

System

and

the vertical

1-6

plug-in

units

are calibrated.

lf

the

displays

noted

previously

are both

outside

the

given

tolerance

in

the

same

direction

(i.e.,

high

or

low),

the Vertical

Gain

or 4 Volts

calibrator

adlustment

probably

needs

re-adjustment.

Otherwise.

check

the

calibration

of the vertical

plug-in

units.

16. Notice

that the

position

control

of

only

the right

vertical

unit

has

an effect

on

the

position

of the

display.

Position

the

display

to the lower

half

of

the

graticule.

Set

both

vertical

units

for

a

deflection

factor

of

two

volts/

division.

Connect

calibrator

signal

to

both

vertical

units

bv

using

a

dual

input

coupler.

17. Press

the ALT

button

of the

VERT

MODE

switch.

Notice

that

two traces

are

displayed

on the

CRT.

The

top

trace is

produced

by the

left

vertical

unit

and the bottom

trace is

produced

by

the right

vertical

unit.

Set

the sweep

rate

to 50

milliseconds/division.

Notice

that

the

display

alternates

between

the left

and

right

vertical

units

after

each sweep.

Turn

the sweep

rate switch

throughout

its

range.

Notice

that

the

display

alternates

between

vertical

units

at all sweep

rates.

18.

Press

the CHOP

button

of the VERT

MODE

switch.

Turn

the

sweep

rate

throughout

its

range.

Notice

that

a

dual-trace

display is

presented

at all

sweep

rates,

but

unlike

ALT

both

vertical

units

are displayed

on each sweep

in

a

time-sharing

manner.

Return

the sweep

rate

to 0.5

m il I isecond/d

ivision.

19.

Press

the ADD

button

of the VERT

MODE

switch.

The

display

should

be

four divisions

in

amplitude.

Notice

that the

position

control

of either

vertical

unit moves

the

display.

Return

the

VERT MODE

switch

to LEFT.

Triggering

20.

Center

the

display

on the

CBT

with

the left

vertical

unit

position

control.

Disconnect

the

input

signal

from

the

right

vertical

unit input

connector.

Sequentially

press

all of

the

VERT MODE

switch

buttons.

Notice

that

a stable

display

is

obtained in

all

positions

of the

VERT

MODE

switch

(straight

line in R IGHT

position).

21. Press

the LEFT

button

of

the TRIG

SOURCE

switch.

Again,

sequentially

press

all

of the

VERT MODE

buttons.

Notice

that

the

display is

again

stable in

all

positions,

as

in

the

previous

step.

22.

Press

the RIGHT

button

of the TRIG

SOURCE

switch. Sequentially press

all of the

VERT

MODE

buttons

and notice

that a stable

display

cannot

be

obtained

in

any

position.

This is

because

there is no

input

signal connected

@

Page 13

to

the right vertical

unit. Return the

TRIG

SOURCE switch

to VERT

MODE.

Remove calibrator signal from

left

vertical unit and

connect it to right

vertical

unit.

Repeat

steps

20

ro

22. The trigger signal will come

from

right

vertical.

When the LEFT button

is

pressed

of

the TRIG

SOURCE switch

the displav

is not stable because there is

no input signal

connected to

the left vertical. Return the

TRIG SOURCE switch

to VERT

MODE.

Horizontal

Def lection

System

23. Position the start of

the sweep to the

left

graticule

line with the

time-base unit

position

control.

24. Connect a

10X

probe

to the

input

of the right

vertical

unit. Set the right

vertical unit for a deflection

factor of

10 volts/division and

set the VERT MODE switch

to

RIGHT. Set the time-base

unit for a sweep rate of five

m illiseconds/d iv

ision.

25. Connect the

probe

tip to a

line-voltage source. The

display should show

three complete cycles over the 10

divisions within

0.3 division. A correct display

indicates

that the

7603

Horizontal Deflection System

and

the

time-base

plug-in

unit are

correctly calibrated.

lf

the display

is

outside the

given

tolerance, either the

7603

or the

time-base

unit needs to be recalibrated.

Refer to the

Calibration

section of this manual. and to the time-base

unit manual for adjustment

procedure.

NOTE

This step

is based on an

accurate 60-Hertz line

frequency.

For other line

frequencies,

this

procedure

will need to be changed accordingly.

26. Disconnect

the

probe

from

the

line-voltage

source

and the

right

vertical

unit

and

connect the

probe

to the

left

vertical

unit.

Set the VERT

MODE

switch

to

LEFT

and set

the time-base

unit for

a sweep

rate

of 0.5

millisecond/

division.

Beam

Finder

27. Set the deflection factor of the

left vertical

unit to

0.1 volt/division.

Notice that a square-wave

display

is not

visible. since

the deflection exceeds the scan area of the

CRT.

28. Press and

hold the BEAM FINDER switch. Notice

that the

display

is

returned to the viewing area

in

compressed form.

Increase the vertical

and

horizontal

def lection factors until the displav

is

reduced to about two

divisions vertically and

horizontally

(when

the horizontal

unit is

operated

in

the time-base

mode, change

only the

REV B SEP 1979

Operating I nstructions-7603/R7603

Service

def lection factor

of

the vertical

unit).

Adjust

the

position

controls

of the displayed

vertical

unit

and the time-base

unit to center the compressed display

about the center lines

of

the

graticule.

Release

the

BEAM FINDER

switch. Notice

that the display remains within the viewing

area.

Z-Axis lnput

29. lf

an external signal

is

available

(five

volts

peak-to-

peak

minimum at two

megahertz

or

less), the

function

of

the

EXT Z AXIS input can be

demonstrated. Connect

the

external

signal to both

the

input

of the right vertical

unit

and the EXf Z

AXIS

connector with two BNC

cables

and a

BNC T

connector. Set the

VERT l\4ODE

switch to RIGHT

and

set the vertical unit for

a deflection factor

of two

volts/division. Set

the

time-base

unit for a sweeD

rate which

displays several cycles

of

the signal. Adjust

the

amplitude of

the signal

generator

until intensity modulation

is visible

on

the display.

The

positive peaks

of

the

waveform should be

blanked

out and the

negative

peaks

intensified. Notice

that

the setting of the INTENSITY control

determines the

amount of

intensity modulation

that is visible.

30. Disconnect

the signal

f rom

the EXT Z AX lS

connector, but

leave it connected

to the

right vertical

unit

input.

Check

that

peak-to-peak

amplitude

of the displayed

signal

is

four

divisions

maximum.

31.

This completes

the Operating

Checkout

procedure

for the 7603. Instrument

operations not

explained

here,

or

operations which

need further

explanation

are

discussed

under

General Operating Information.

SIMPLI F I

ED

OPERATING INSTRUCTIONS

The

following information

is

provided

to aid in

quickly

obtaining the correct

setting for

the 7603

controls

to

present

a

display. The

operator

should be familiar

with

the

complete

function and

operation

of this

instrument

as

described

elsewhere

in

this section

before

using

this

procedure.

For

detailed

operating information

for

the

plug-in

units, see

the

instruction

manuals

for the

applicable

u n

its.

Single-Trace Display

The

following

procedure

will

provide

a display

of

a

single-trace

vertical unit

against

one time-base

unit. For

simplicity

of explanation,

the vertical

unit is installed

in

the

left

vertical

compartment. The

right vertical

compartment

can be used if

the

procedure

is

changed

accordingly.

1.

Install

a

7A-series

com

partment.

unit in

the left

1-7

Page 14

Operating

I nstruction

s-7603/R7603

Service

2.

Press

the LEFT

button

of

the VERT

MODE

switch.

3. Install

a

7B-series

time-base

unit

in the

horizontal

com

partment.

4. Press

the VERT MODE

button

of the

TRIG

SOURCE

switch.

5.

Connect

the signal

to the input

connector

of the

vertical

unit.

6. Set

the vertical

unit

for AC input

coupling

and

cal

ibrated

def

lection

factors.

7.

Set

the

time-base

unit

for

auto

mode,

internal

triggering

at a calibrated

sweep rate

of

one millisecond/

d

ivision.

8. Advance

the INTENSITY

control

until

a display

is

visible.

(lf

no display

is visible

with INTENSITy

at

about

midrange,

press

and hold

the BEAM

FINDER

switch

and

adjust

the

vertical

deflection

factor

until

the

display is

reduced

in

size

vertically;

then

center

the

compressed

display with

vertical

and horizontal position

controls;

release

the

BEAM FINDER.)

Adjust

the FOCUS

control

for

a well-def

ined

display.

Adjust

Readout

INTENSITy

for

the

desired

viewing level.

9.

Set the

vertical

deflection

factor

and vertical

position

control

for

a display

which

remains

within

the

qraticule

area vertically.

10. lf

necessary,

set

the time-base

triggering

controls

for

a stable

display.

11.

Adjust

the

time-base

position

control

so

the display

begins

at the left

edge

of the

graticule.

Set

the time-base

sweep

rate

to display

the

desired number

of cyctes.

Dual-Trace

Display

The

following

procedure

will

provide

a display

of two

slngle-trace

vertical

units

against

one time-base

unit.

1 . Install

7A-series

vertical

units in

both

vertical

plug-in

com

partments.

2. Press

the LEFT

button

of the VERT

MODE

switch.

1-8

3. Install

a

7B-series

time-base

unit

in

the horizontal

com

partment.

4.

Press

the VERT

MODE

button

of the TRIG

SOURCE

switch.

5.

Connect

the

signal

to

the input

connectors

of the

vertical

units.

6. Set

the

vertical

units

for AC

input

coupling

and

cal ibrated

def lection

factors.

7.

Set

the

time-base

unit

for

auto

mode,

internal

triggering

at a sweep

rate

of

one millisecond/division.

8. Advance

the INTENSITY

control

until

a display

is

visible.

(lf

no

display

is visible

with lNTENSlry

at

midrange,

press

and hold

BEAM

FINDER

switch

and

adjust

vertical

deflection

factor

until

display

is

reduced

in

size

vertically;

then

center

compressed

display

with

vertical

and

horizontal position

controls;

release

the

BEAM

FINDER

switch.)

Set

the FOCUS

control

for

a

well-defined

display.

9. Set

the left

vertical

unit

def lection

factor

for

a display

about

four

divisions

in

amplitude.

Adjust

the left

vertical

position

control

to move

th is d isplay

to the

top

of the

graticule

area.

10.

Press

the RIGHT

button

of the

VERT

MODE

switch.

1

1.

Set the

R IGHT

vertical

unit

def lection

f actor

for

a

display

about four

divisions in

amplitude

(if

display

cannot

be

located,

use

BEAM FINDER

switch).

position

this

display

to the

bottom

of the

graticule

area

with

the

right

vertical

unit

position

control.

12. Press

the ALT

or CHOP

button

of the

VERT

MODE

switch.

A

dual-trace

d

isplay

of

the

signal

f rom

the left

vertical

and right

vertical

plug-in

units

should

be

presented

on

the CRT.

(For

more information

on choice

of dual-trace

mode,

see Vertical

Mode

in

this

section.)

13. lf

necessary,

adjust the

time-base

triggering

controls

f

or a stable

d isplay.

'l

4.

Adjust

the

time-base

position

control

so

the display

begins

at the left

edge

of the

graticule.

Set

the

time-base

sweep

rate

for

the

desired horizontal

display.

@

Page 15

Delayed

Sweep

-

Single

Trace

)

fne

following

procedure

will

provide

a delayed

sweep

display

of

a single-trace

vertical

unit.

1. Follow

the complete

procedure

given

under

Single-Trace

Displays.

2.

Be

sure the

time-base

unit installed

in

the

horizontal

compartment

is

a dual

time-base

with

delaying/delayed

caoabilities.

3.

Follow

the

procedure

given

in

the instruction

manual

for

the

dual

time-base

unit

to

obtain

a delayed-sweep

display.

Delayed

Sweep

-

Dual

Trace

The

following

procedure

will

provide

a delayed-sweep

display

of two single-trace

vertical

units.

1. Follow

the complete

procedure

given

under Dual-

Trace

Display.

\

j

2.

Be sure

the

time-base

unit installed

in

the horizontal

'

compartment

is

a dual time-base

unit with

delaying/delayed

capab i

I ities.

3.

Follow

the

procedure

given

in

the

instruction

manual

for

the dual

time-base

unit

to obtain

a

delayed-sweep

display.

X-Y

Display

The

following

procedure

will

provide

an

X-y

display

(one

signal versus

another rather

than

against

time).

NOTE

Some 7B-series

time-base

units

have

provisions

for

amplif

ier

operation

in the X-Y

mode;

see X-Y

operation

in

this section for

details

of operation

in

this manner.

'l

. Install

7A-series

amplif ier

units

in

both

the left

vertical

and

the horizontal

compartments.

2.

Press

the

LEFT

button

of

the VERT

MODE

switch.

@

Operating

I nstructions-7603/R7603

Service

3.

Connect

the X-signal

to the

amplifier

unit

in the

horizontal

compartment.

4.

Connect

the Y-signal

to

the

vertical

compartment.

amplif ier

unit in

the left

5. Set

both

amplifier

units

for AC

input

coupling

and

cal ibrated

def

lection

factors.

6. Advance

the INTENSITY

control

until

a

display is

visible.

(lf

no

display is

visible,

press

and hold

BEAM

FINDER

switch

and adjust the

def

lection

factors

of

both

amplifier

units

until

display is

reduced

in

size both

vertically

and horizontally;

then

center

compressed

display

with

the

position

controls;

release

the BEAM

FINDER

switch.)

Adjust

the FOCUS

control

for

a well-defined

d isp lay.

GENERAL

OPERATING

INFORMATION

Intensaty

Control

The

setting

of the INTENSITY

control

mav

affect

the

correct

focus

of the d isplay.

Slight

re-ad

justment

of the

FOCUS

control

may

be necessary,

when

the intensity

level

is

changed.

To

protect

the

CRT

phosphor;

do not

turn

the

INTENSITY

control

higher

than

necessary

to

provide

a

satisfactory

display.

The

light

filters

reduce

the

observed

light

output

from

the

CRT. When

using

these

f ilters,

avoid

advancing

the INTENSITY

control

to

a setting

that may

burn

the

phosphor.

When

the

highest

intensity

display

is

desired,

remove

the

f ilters

and

use

only

the

clear

faceplate

protector (permanently

installed

behind

bezel).

Apparent

trace intensity

can

also be

improved

in

such

cases

bv

reducing

the

ambient

light

level

or using

a viewing

hood.

Also,

be

careful

that the INTENSITY

control

is

not

set

too

high

when

changing

the time-base

unit

sweep

rate

from

a

fast

to

a slow

sweep

rate,

or when

changing

to

the

X-y

mode

of

operation.

The instrument

incorporates protection

circuitry

which

automatically

reduces

the

display intensity

to

a lower

level

when

the

time-base

unit

is

set

to

a slow

sweep

rate. This

reduces

the danger

of

damaging

the

CRT

phosphor

at these

slower

sweep

rates.

Display

Focus

The

FOCUS

control

allows

adjustment

for

best

defini-

tion

of the

CRT

display. The

Readout

intensity

should

be

turned

on, when

adjusting

the

Focus

control.

Slight

re-adjustment

of

this control

may

be

necessarV

as

the

display

conditions

change. lf

a

properly

focused

display

cannot

be

obtained

with the

FOCUS

control,

the internal

Astigmatism

adjustment

must

be

re-set;

see

the Calibration

section

of this manual.

1-9

Page 16

Operating

I nstructions-7603/R7603

Service

Graticule

The graticule

of the 7603 is marked

on the inside

of the

faceplate

of the CRT,

providing

accurate, no-parallax

measurements.

The

graticule

is

divided into

eight vertical

and ten horizontal

divisions. Each

division is

1.22 centi-

meters

square.

In

addition,

each major division

is

divided

into

five minor

divisions.

The

vertical

gain

and

horizontal

timing

of the

plug-in

units

are calibrated

to

the

graticule

so

accurate measurements

can be

made from

the CRT. The

illumination

of the

graticule

lines

can be varied

with

the

GRATICU LE I LLUM

control.

NOTE

Two

types

of crt

graticules

have

been

used in

some

Tektronix

orcillorcopes.

One

graticule

has

0%

and

100o1' risetime

reference

points

that are separated

by

6

vertical

graticule

divisions.

The other

graticule

has

the 0%

and

100% risetime

reference

points

separated

by 5 vertical

divisions.

ln

your

manual,

illustrations

of

the

crt

face or risetime

measurement

instructions

may

not

correspond

with

the

graticule

markings

on

your

oscilloscope.

Fig. 1-4

shows the

graticule

of

the

7603

and def ines

the

various

measurement

lines. The

terminology

defined

here

will be used in

all discussions involving graticule

measure-

ments. Notice

the 0%,

1oyo,goyo

and 100%

markings

on

the

left

side

of the

graticule.

These

markings

are

provided

to

facil itate

risetime measurements.

Light Filter

The

tinted f ilter

provided

with

the 7603 minimizes

light

ref lections from

the face

of the

CRT to improve

contrast

when

viewing

the

display under

high

ambient light

condi-

tions. This

filter should be

removed

for

waveform

photo-

graphs

or when viewing

high writing

rate

displays. To

remove

the filter,

loosen the

two screws

on

the

riqht side

of

Fig,

1-4, Def inition

of

measurement

lines

on 7603

graticule,

1-10

the bezel

and remove

the bezel. Remove

the

tinted

filter;

leave

the clear

plastic

faceplate

protector

installed

and

replace

the bezel. The

faceplate

protector

should

be left in

place

at

all times to

protect

the

CRT faceplate

from

scratch es.

An

optional

mesh filter

is

available

for

use

with

the

7603. This

filter

provides

shielding

against

radiated

EMI

(electro-magnetic

interference)

from

the face

of the

CRT. lt

also serves

as a light

filter

to make

the

trace

more

visible

under high

ambient light

conditions.

The

mesh

f

ilter

f its in

place

of the

plastic

CRT

mask

and

the tinted

filter.

Beam Finder

The BEAM

FINDER

switch

provides

a means

of

locating

a display

which

overscans the viewing

area

either vertically

or

horizontally.

When

the BEAM FINDER

switch is

pressed

and held,

the display is compressed

within

the

graticule

area.

Release

the BEAM FINDER

switch

to return

to

a

normal

display. To

locate

and reposition

an

overscanneo

display,

use the

following

procedure:

1.

Press

and hold the BEAM

FINDER

switch.

2.

Increase

the vertical

and horizontal

deflection

factors

until the vertical

deflection

is reduced

to

about two

divisions

and the horizontal

deflection

is

reduced

to

about

four

divisions

(the

horizontal

deflection

needs

to be

reduced

only

when

in

the X-Y

mode

of operation).

3. Adjust

the vertical

and horizontal

position

controls

to

center

the

display

about the vertical

and horizontal

center

I i nes

of th

e oraticu

le.

4.

Release

the BEAM FINDER

switch;

the

display

should remain

within

the viewino

area.

Readout

Modes

The

characters

of the readout

display

are written

by

the

CRT beam

on

a time-share

basis with

signal

waveforms.

The

Readout

system

operates in

a

free running

mode

to

randomly interrupt

the

waveform

display

to

present

the

readout

characters.

The

readout

system

can

also

operate in

a GATE TRIG'D

mode. No

readout

signal is

produced

until

after

the

sweep has

occurred.

In

this mode

the

sweep

musr

run

to have

the readout

d isplayed.

Display Photography

A

permanent

record

of the CRT

display

can

be

obtained

with

an

oscilloscope

camera system.

The

instruction

manuals

for

the TEKTRONIX

Oscilloscope

Cameras

include

complete instructions

for

obtaining waveform

photographs.

The

following

specif ic information

applies to

the 7603.

(

,0

REV

C

SEP 1979

Page 17

The

CRT bezel

of

the 7603

provides

integral

mounting

for a TEKTRONIX

Oscilloscope

Camera. The

three

pins

;located

on the

left

side

of the CRT bezel

connect

power

to

compatible camera

systems.

lt

also

receives control

signals

from TEKTRONIX

automatic cameras

to

allow camera-

controlled

single-shot

photography

(see

camera

manual for

f urther information).

Vertical Mode

Left and Right Mode.

When

the

LEFT

or

RIGHT

button

of

the

VERT MODE

switch

is

pressed,

only the signal

from

the

plug-in

unit

in

the selected

compartment is

displayed.

Alternate

Mode.

The ALT

position

of the VERT

MODE

switch

produces

a display which

alternates between

the

plug-in

units in

the

left

vertical

and right vertical

compart-

ments

with each sweep

of the CRT. Although

the ALT

mode can be

used

at all sweep rates,

the CHOP mode

provides

a more satisfactory

display

at sweep rates below

about 20 milliseconds/division.

At

these slower

sweep rates,

alternate-mode switching becomes

visually

perceptible.

NOTE

This instrument

will not operate in

the ALT

mode if

the horizontal

plug-in

unit is

not operated in

the

time-base

mode.

The

TRIG SOURCE

switch

allows selection

of the

triggering

for an alternate display. When

this

switch is set

to

the VERT MODE

position,

each sweep is

triggered by

the

signal being

displayed on the

CRT.

This

provides

a stable

display of two unrelated signals,

but

does

not indicate

the

time relationship between

the signals. In

either the LEFT

or

RIGHT

positions

of

the TRIG

SOURCE

switch, the two

signals

are displayed showing

true time

relationship.

However, if

the signals

are

not

time-related, the

display

from the

plug-in

unit

which is

not

providing

a trigger signal

will appear unstable

on

the CRT.

Chopped Mode. The

CHOP

position

of the VERT

MODE

switch

produces

a display which

is

electronically

switched between channels

at a one-megahertz rate. In

general,

the CHOP

mode

provides

the

best

display

at

sweep

rates lower than

about