Page 1

PCIe5.0 (CEM) Receiver Test

Application Help

*P 077170602 *

077-1706-02

Page 2

Page 3

PCIe5.0 (CEM) Receiver Test

Application Help

Register now!

Click the following link to protect your product.

www.tek.com/register

*P 077170602 *

077-1706-02

Page 4

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its subsidiaries or suppliers, and are

protected by national copyright laws and international treaty provisions. Tektronix products are covered by U.S. and foreign patents, issued

and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges

reserved.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

Contacting Tektronix

Tektronix, Inc.

14150 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

USA

For product information, sales, service, and technical support:

• In North America, call 1-800-833-9200.

• Worldwide, visit to www.tek.com find contacts in your area.

Page 5

Table of Contents

Table of Contents

List of Figures..............................................................................................................................................................................12

List of Tables............................................................................................................................................................................... 15

Welcome..................................................................................................................................................................................... 17

Getting help and support.............................................................................................................................................................18

Related documentation........................................................................................................................................................ 18

Technical support................................................................................................................................................................. 18

Conventions......................................................................................................................................................................... 18

Getting started.............................................................................................................................................................................20

Required equipment and accessories..................................................................................................................................20

Installing the software.......................................................................................................................................................... 21

Operating basics......................................................................................................................................................................... 22

Launch the application......................................................................................................................................................... 22

Close the application............................................................................................................................................................22

Launch Real-Time Oscilloscope.......................................................................................................................................... 22

Launch TekRxService.......................................................................................................................................................... 23

Application panels................................................................................................................................................................24

Application panels overview..........................................................................................................................................24

Connections panel........................................................................................................................................................ 25

Settings panel............................................................................................................................................................... 26

Help panel.....................................................................................................................................................................36

Calibrations panel......................................................................................................................................................... 36

Tests panel....................................................................................................................................................................61

Options panel................................................................................................................................................................83

Programmatic interface commands ......................................................................................................................................... 100

PREF:BERT:IP...................................................................................................................................................................100

PREF:RTS:IP.....................................................................................................................................................................100

CONN:BERT .....................................................................................................................................................................100

CONN:RTS........................................................................................................................................................................ 101

SETTINGS:TEKRXSERVICE:ANALYSISTIMEOUT..........................................................................................................101

SETTINGS:SIGTEST:VERSION........................................................................................................................................101

SETTINGS:SOCKETSERVER:IP...................................................................................................................................... 101

SETTINGS:SOCKETSERVER:LISTENINGPORT.............................................................................................................102

SETTINGS:SOCKETSERVER:TIMEOUT......................................................................................................................... 102

SETTINGS:MULTITONESJCAL:ENABLE......................................................................................................................... 102

SETTINGS:MULTITONESJCAL:FREQUENCYCOUNT.................................................................................................... 103

SETTINGS:MULTITONESJCAL:MAXFREQUENCY......................................................................................................... 103

SETTINGS:MULTITONESJCAL:MINFREQUENCY.......................................................................................................... 103

SETTINGS:MULTITONESJCAL:POINTS.......................................................................................................................... 103

SETTINGS:EYE:ACQUISITIONS...................................................................................................................................... 104

SETTINGS:TP1:CH1DEEMBEDFILE................................................................................................................................104

SETTINGS:TP1:CH2DEEMBEDFILE................................................................................................................................104

SETTINGS:TP1:ENABLECH1DEEMBED......................................................................................................................... 105

SETTINGS:TP1:ENABLECH2DEEMBED......................................................................................................................... 105

SETTINGS:TP2:CH1DEEMBEDFILE................................................................................................................................105

PCIe5.0 (CEM) Receiver Test Application Help 5

Page 6

Table of Contents

SETTINGS:TP2:CH2DEEMBEDFILE................................................................................................................................106

SETTINGS:TP2:ENABLECH1DEEMBED......................................................................................................................... 106

SETTINGS:TP2:ENABLECH2DEEMBED......................................................................................................................... 106

SETTINGS:MULTITONESJCAL:DEFAULT........................................................................................................................107

SETTINGS:MULTITONESJCAL:GENERATE....................................................................................................................107

SETTINGS:TP1:CH1:EXTERNALATTEN..........................................................................................................................107

SETTINGS:TP1:CH2:EXTERNALATTEN..........................................................................................................................107

SETTINGS:TP2:CH1:EXTERNALATTEN..........................................................................................................................108

SETTINGS:TP2:CH2:EXTERNALATTEN..........................................................................................................................108

SETTINGS:EYE:ALGO......................................................................................................................................................108

SETTINGS:CTLE:ANALYSISTOOL...................................................................................................................................109

SETTINGS:RESTORE.......................................................................................................................................................109

SETTINGS:RECALL.......................................................................................................................................................... 109

SETTINGS:SAVE...............................................................................................................................................................109

SETTINGS:RECALL:STATUS............................................................................................................................................110

SETTINGS:RESTORE:STATUS........................................................................................................................................ 110

SETTINGS:SAVE:STATUS................................................................................................................................................ 110

TP1CAL:OPEN...................................................................................................................................................................111

TP1CAL:WIZARD:OPEN....................................................................................................................................................111

TP1CAL:WIZARD:CLOSE..................................................................................................................................................111

TP1CAL:DELETE............................................................................................................................................................... 111

TP1CAL:REPORT..............................................................................................................................................................112

TP1CAL:SAVE................................................................................................................................................................... 112

TP1CAL:EQUIP:INIT..........................................................................................................................................................112

TP1CAL:AUTOCAL............................................................................................................................................................112

TP1CAL:AMPLITUDE:RUN............................................................................................................................................... 113

TP1CAL:PRESET:RUN .....................................................................................................................................................113

TP1CAL:RJ:RUN ...............................................................................................................................................................113

TP1CAL:SJ:RUN................................................................................................................................................................114

TP1CAL:MULTITONESJCAL:RUN.................................................................................................................................... 114

TP1CAL:EQUIP:STATUS...................................................................................................................................................114

TP1CAL:AMPLITUDE:STATUS......................................................................................................................................... 114

TP1CAL:PRESET:STATUS................................................................................................................................................ 115

TP1CAL:PWJCAL:DJ.........................................................................................................................................................115

TP1CAL:PWJCAL:MODE.................................................................................................................................................. 115

TP1CAL:PWJCAL:RJ.........................................................................................................................................................116

TP1CAL:PWJCAL:START..................................................................................................................................................116

TP1CAL:PWJCAL:STATUS............................................................................................................................................... 116

TP1CAL:RJ:STATUS..........................................................................................................................................................116

TP1CAL:SJ:STATUS..........................................................................................................................................................117

TP1CAL:MULTITONESJCAL:RUN.................................................................................................................................... 117

TP1CAL:AMPLITUDE:SETTING .......................................................................................................................................117

TP1CAL:RJ:SETTING........................................................................................................................................................118

TP1CAL:SJ:SETTING........................................................................................................................................................118

TP1CAL:SAVE:ID ..............................................................................................................................................................118

TP1CAL:SAVE:GENERATEDBY....................................................................................................................................... 118

TP1CAL:SAVE:COMMENTS............................................................................................................................................. 119

TP1CAL:ACDC:RUN..........................................................................................................................................................119

TP1CAL:ACDC:STATUS....................................................................................................................................................119

6

Page 7

Table of Contents

TP1CAL:ACDC:SETTING..................................................................................................................................................119

TP1CAL:SJ@210MHz:RUN.............................................................................................................................................. 120

TP1CAL:SJ@210MHz:STATUS.........................................................................................................................................120

TP1CAL:IL:MODE..............................................................................................................................................................120

TP1CAL:MANUAL:IL......................................................................................................................................................... 121

TP1CAL:MEASURELOSS:START.....................................................................................................................................121

TP1CAL:IL:SCOPEACQS..................................................................................................................................................121

TP1CAL:IL:AVGS...............................................................................................................................................................122

TP1CAL:MEASURELOSS:STATUS.................................................................................................................................. 122

TP2CAL:OPEN.................................................................................................................................................................. 122

TP2CAL:WIZARD:OPEN................................................................................................................................................... 122

TP2CAL:WIZARD:CLOSE................................................................................................................................................. 123

TP2CAL:DUT:TYPE........................................................................................................................................................... 123

TP2CAL:SELECT:TP1....................................................................................................................................................... 123

TP2CAL:DELETE.............................................................................................................................................................. 123

TP2CAL:REPORT..............................................................................................................................................................124

TP2CAL:SAVE................................................................................................................................................................... 124

TP2CAL:EQUIP:INIT......................................................................................................................................................... 124

TP2CAL:CMI:RUN ............................................................................................................................................................ 125

TP2CAL:ILMEAS:RUN...................................................................................................................................................... 125

TP2CAL:CTLEANDPRESET:RUN.....................................................................................................................................125

TP2CAL:STRESSEDEYE:RUN ........................................................................................................................................ 125

TP2CAL:EQUIP:STATUS...................................................................................................................................................126

TP2CAL:CMI:STATUS....................................................................................................................................................... 126

TP2CAL:ILMEAS:STATUS.................................................................................................................................................126

TP2CAL:CTLEANDPRESET:STATUS...............................................................................................................................127

TP2CAL:STRESSEDEYE:STATUS................................................................................................................................... 127

TP2CAL:DMI:SETTING..................................................................................................................................................... 127

TP2CAL:CMI:SETTING..................................................................................................................................................... 127

TP2CAL:SAVE:ID ..............................................................................................................................................................128

TP2CAL:SAVE:GENERATEDBY....................................................................................................................................... 128

TP2CAL:SAVE:COMMENTS............................................................................................................................................. 128

TP2CAL:SAVE:ISIPAIR......................................................................................................................................................128

TP2CAL:ILMEASFORDMI:RUN........................................................................................................................................ 129

TP2CAL:ILMEASFORDMI:STATUS.................................................................................................................................. 129

TP2CAL:STRESSEDEYE:ACQUISITIONS....................................................................................................................... 129

TP2CAL:DMI:RUN............................................................................................................................................................. 130

TP2CAL:DMI:STATUS....................................................................................................................................................... 130

TP2CAL:CTLEANDPRESET:ACQUISITIONS...................................................................................................................130

TP2CAL:CTLE:ESTIMATOR..............................................................................................................................................130

TP2CAL:SEASIMCTLE:GEN5...........................................................................................................................................131

TP2CAL:STRESSEDEYE:SJ.............................................................................................................................................131

TP2CAL:STRESSEDEYE:DMI.......................................................................................................................................... 131

TP2CAL:STRESSEDEYE:AMPLITUDE............................................................................................................................ 132

TP2CAL:IL:MODE..............................................................................................................................................................132

TP2CAL:MANUAL:IL......................................................................................................................................................... 132

TP2CAL:IL:SCOPEACQS .................................................................................................................................................133

TP2CAL:IL:AVGS...............................................................................................................................................................133

TP2CAL:CTLEANDPRESET:CHKPRESET.......................................................................................................................133

PCIe5.0 (CEM) Receiver Test Application Help 7

Page 8

Table of Contents

TP2CAL:CTLEANDPRESET:CHKCTLE............................................................................................................................133

TP2CAL:STRESSEDEYE:MANUALCALRUN................................................................................................................... 134

TP2CAL:STRESSEDEYE:EXHAUSTIVESWEEP............................................................................................................. 134

TP2CAL:STRESSEDEYE:LINEARSWEEP.......................................................................................................................135

TP2CAL:STRESSEDEYE:EXHAUSTIVE ......................................................................................................................... 135

TP2CAL:STRESSEDEYE:STEPSIZE................................................................................................................................136

TEST:SELECT:TESTDURATION ......................................................................................................................................136

TEST:SELECT:STRESSCONFIGTYPE ............................................................................................................................137

TEST:SELECT:AMP ..........................................................................................................................................................137

TEST:SELECT:DMI ........................................................................................................................................................... 137

TEST:SELECT:CMI............................................................................................................................................................ 138

TEST:SELECT:RJ ............................................................................................................................................................. 138

TEST:SELECT:SJ.............................................................................................................................................................. 138

TEST:SELECT:BER........................................................................................................................................................... 139

TEST:SELECT:ERRORLIMIT.............................................................................................................................................139

LOOPBACK:SELECT:CONFIGURATIONTYPE................................................................................................................ 139

LOOPBACK:SELECT:PRESETSNAME ............................................................................................................................140

LOOPBACK:SELECT:PRESETSPRESHOOT ..................................................................................................................140

LOOPBACK:SELECT:PRESETSDEEMPHASIS............................................................................................................... 140

LOOPBACK:SELECT:BERTCTLEMODE.......................................................................................................................... 140

LOOPBACK:SELECT:BERTCTLETYPE............................................................................................................................141

LOOPBACK:SELECT:BERTCTLEVALUE......................................................................................................................... 141

LOOPBACK:SELECT:AUTOSEARCHMODE....................................................................................................................141

JTOLTEST:OPEN...............................................................................................................................................................142

JTOLTEST:WIZARD:OPEN............................................................................................................................................... 142

JTOLTEST:WIZARD:CLOSE............................................................................................................................................. 142

JTOLTEST:JITTERSTEP:HIGHFREQ............................................................................................................................... 143

JTOLTEST:JITTERSTEP:LOWFREQ................................................................................................................................ 143

JTOLTEST:JITTERSTEP:MIDDLEFREQ...........................................................................................................................143

JTOLTEST:JITTERSTEP:VERYLOWFREQ...................................................................................................................... 143

JTOLTEST:SELECT:TP2FILE ...........................................................................................................................................144

JTOLTEST:SELECT:CUSTOM:MASK............................................................................................................................... 144

JTOLTEST:MIN:FREQ....................................................................................................................................................... 144

JTOLTEST:MAX:FREQ ..................................................................................................................................................... 145

JTOLTEST:FREQ:POINTS................................................................................................................................................ 145

JTOLTEST:FREQ:GENERATE.......................................................................................................................................... 145

JTOLTEST:FREQ:DEFAULT..............................................................................................................................................145

JTOLTEST:SELECT:RELAXATION....................................................................................................................................146

JTOLTEST:SEARCH:ALGO ..............................................................................................................................................146

JTOLTEST:RUN ................................................................................................................................................................ 146

JTOLTEST:SAVE:ID ..........................................................................................................................................................147

JTOLTEST:SAVE:GENERATEDBY....................................................................................................................................147

JTOLTEST:SAVE:COMMENTS ........................................................................................................................................ 147

JTOLTEST:SAVE............................................................................................................................................................... 148

JTOLTEST:RUNSTATUS................................................................................................................................................... 148

JTOLTEST:FREQ ..............................................................................................................................................................148

JTOLTEST:PLOT:POINTS................................................................................................................................................. 148

JTOLTEST:SELECT:SJAMPUNITS................................................................................................................................... 149

JTOLTEST:SELECT:CLOCKTYPE.................................................................................................................................... 149

8

Page 9

Table of Contents

JTOLTEST:PLOT............................................................................................................................................................... 149

JTOLTEST:TABLE..............................................................................................................................................................150

JTOLTEST:SELECT:DUTTYPE......................................................................................................................................... 150

JTOLTEST:BERMEASUREMENT:PATTERN.....................................................................................................................150

JTOLTEST:LINKTRAINING:LOOPBACKMODEGEN5...................................................................................................... 151

JTOLTEST:LINKTRAINING:BERTINITIALPRESET...........................................................................................................151

JTOLTEST:LINKTRAINING:DUTINITIALPRESET.............................................................................................................152

JTOLTEST:LINKTRAINING:DUTTARGETPRESET...........................................................................................................152

JTOLTEST:LINKTRAINING:LANENUMBER......................................................................................................................152

JTOLTEST:LINKTRAINING:LINKNUMBER....................................................................................................................... 153

JTOLTEST:LINKTRAINING:STRESSTYPE.......................................................................................................................153

JTOLTEST:LINKTRAINING:CTLE..................................................................................................................................... 153

JTOLTEST:LINKTRAINING:DUTPOWERONTYPE...........................................................................................................153

JTOLTEST:LINKTRAINING:SCRIPTLOCATION .............................................................................................................. 154

JTOLTEST:LINKTRAINING:DUTPOWERDELAY..............................................................................................................154

JTOLTEST:CLOCK:ARCHITECTURE .............................................................................................................................. 154

JTOLTEST:COMMONCLOCK:SKP:GEN12:INTERVAL.................................................................................................... 155

JTOLTEST:COMMONCLOCK:SKP:GEN345:INTERVAL ................................................................................................. 155

JTOLTEST:FILTER:SKP.................................................................................................................................................... 155

JTOLTEST:INSERT:SKP....................................................................................................................................................156

JTOLTEST:LINKTRAINING:CTLETYPE............................................................................................................................ 156

JTOLTEST:LINKTRAINING:CBBAUTORESET................................................................................................................. 156

JTOLTEST:LINKTRAINING:CBBPOWERCYCLE..............................................................................................................157

JTOLTEST:LINKTRAINING:CBBPOWERRESET..............................................................................................................157

JTOLTEST:LINKTRAINING:CBBWAITINGTIME............................................................................................................... 157

JTOLTEST:LINKTRAINING:POWEROPTIONTYPE..........................................................................................................158

JTOLTEST:LINKTRAINING:ENABLEDUTLOOPBACKAFTERTEST................................................................................ 158

JTOLTEST:LINKTRAINING:USERPATTERNLOCATION.................................................................................................. 158

JTOLTEST:SKP:GEN12:DOUBLESKP..............................................................................................................................159

JTOLTEST:SKP:GEN12:SYMBOLLENGTH...................................................................................................................... 159

JTOLTEST:SKP:GEN345:DOUBLESKP ...........................................................................................................................159

JTOLTEST:SKP:GEN345:SYMBOLLENGTH.................................................................................................................... 160

LEQRXTEST:OPEN ..........................................................................................................................................................160

LEQRXTEST:WIZARD:OPEN ...........................................................................................................................................160

LEQRXTEST:WIZARD:CLOSE .........................................................................................................................................161

LEQRXTEST:DUTTYPE ................................................................................................................................................... 161

LEQRXTEST:CLOCKTYPE .............................................................................................................................................. 161

LEQRXTEST:SHOW:CONNECTIONDIAGRAM ...............................................................................................................162

LEQRXTEST:LINKTRAINING:BERTINITIALPRESET.......................................................................................................162

LEQRXTEST:LINKTRAINING:DUTINITIALPRESET ........................................................................................................162

LEQRXTEST:LINKTRAINING:DUTTARGETPRESET.......................................................................................................162

LEQRXTEST:LINKTRAINING:LINKNUMBER................................................................................................................... 163

LEQRXTEST:LINKTRAINING:LANENUMBER..................................................................................................................163

LEQRXTEST:LINKTRAINING:LOOPBACKMODEGEN5...................................................................................................163

LEQRXTEST:LINKTRAINING:CTLETYPE........................................................................................................................ 164

LEQRXTEST:LINKTRAINING:POWEROPTIONTYPE...................................................................................................... 164

LEQRXTEST:LINKTRAINING:CBBAUTORESET..............................................................................................................164

LEQRXTEST:SSC:STATE..................................................................................................................................................165

LEQRXTEST:LINKTRAINING:AUTOSEARCHANDTUNECDR.........................................................................................165

PCIe5.0 (CEM) Receiver Test Application Help 9

Page 10

Table of Contents

LEQRXTEST:LINKTRAINING:CBBPOWERCYCLE..........................................................................................................165

LEQRXTEST:LINKTRAINING:CBBPOWERRESET..........................................................................................................166

LEQRXTEST:LINKTRAINING:CBBWAITINGTIME............................................................................................................166

LEQRXTEST:LINKTRAINING:ENABLEDUTLOOPBACKAFTERTEST.............................................................................166

LEQRXTEST:CLOCK:ARCHITECTURE............................................................................................................................167

LEQRXTEST:COMMONCLOCK:SKP:GEN12:INTERVAL.................................................................................................167

LEQRXTEST:COMMONCLOCK:SKP:GEN345:INTERVAL...............................................................................................167

LEQRXTEST:FILTER:SKP.................................................................................................................................................168

LEQRXTEST:INSERT:SKP................................................................................................................................................ 168

LEQRXTEST:SKP:GEN12:DOUBLESKP.......................................................................................................................... 168

LEQRXTEST:SKP:GEN12:SYMBOLLENGTH ..................................................................................................................169

LEQRXTEST:SKP:GEN345:DOUBLESKP........................................................................................................................ 169

LEQRXTEST:SKP:GEN345:SYMBOLLENGTH.................................................................................................................169

LEQRXTEST:LINKTRAINING:USERPATTERNLOCATION...............................................................................................170

LEQRXTEST:SSC:STATE..................................................................................................................................................170

LEQRXTEST:LINKTRAINING:AUTOSEARCHANDTUNECDR.........................................................................................170

LEQRXTEST:LINKTRAINING:DUTPOWERONTYPE....................................................................................................... 171

LEQRXTEST:LINKTRAINING:DUTPOWERDELAY.......................................................................................................... 171

LEQRXTEST:LINKTRAINING:SCRIPTLOCATION............................................................................................................171

LEQRXTEST:BERMEASUREMENT:PATTERN.................................................................................................................172

LEQRXTEST:LINKTRAINING:STRESSTYPE................................................................................................................... 172

LEQRXTEST:LINKTRAINING:CTLE..................................................................................................................................173

LEQRXTEST:LINKTRAINING:ENABLEDUTLOOPBACKAFTERTEST.............................................................................173

LEQRXTEST:RUN............................................................................................................................................................. 173

LEQRXTEST:STATUS....................................................................................................................................................... 174

LEQRXTEST:LINKTRAINING:STATUS............................................................................................................................. 174

LEQRXTEST:LINKTRAINING:STOP ................................................................................................................................ 174

LEQRXTEST:TEST:ADDERROR ......................................................................................................................................174

LEQRXTEST:TEST:CURRENTBER.................................................................................................................................. 175

LEQRXTEST:TEST:CURRENTERRORCOUNT................................................................................................................175

LEQRXTEST:TEST:CURRENTTOTALBITS...................................................................................................................... 175

LEQRXTEST:TEST:RESULT............................................................................................................................................. 175

LEQRXTEST:SAVE:ID.......................................................................................................................................................176

LEQRXTEST:SAVE:GENERATEDBY................................................................................................................................176

LEQRXTEST:SAVE:COMMENTS......................................................................................................................................176

LEQRXTEST:SAVE ...........................................................................................................................................................177

LEQTXTEST:OPEN........................................................................................................................................................... 177

LEQTXTEST:WIZARD:OPEN............................................................................................................................................ 177

LEQTXTEST:WIZARD:CLOSE.......................................................................................................................................... 177

LEQTXTEST:SELECT:TP1FILE.........................................................................................................................................178

LEQTXTEST:DUTTYPE ....................................................................................................................................................178

LEQTXTEST:CLOCKTYPE ...............................................................................................................................................178

LEQTXTEST:SELECT:TEST..............................................................................................................................................179

LEQTXTEST:LINKTRAINING:BERTINITIALPRESET....................................................................................................... 179

LEQTXTEST:LINKTRAINING:LINKNUMBER....................................................................................................................179

LEQTXTEST:LINKTRAINING:LANENUMBER.................................................................................................................. 180

LEQTXTEST:LINKTRAINING:DUTPOWERONTYPE........................................................................................................180

LEQTXTEST:LINKTRAINING:DUTPOWERDELAY...........................................................................................................180

LEQTXTEST:LINKTRAINING:SCRIPTLOCATION............................................................................................................181

10

Page 11

Table of Contents

LEQTXTEST:LINKTRAINING:CTLE.................................................................................................................................. 181

LEQTXTEST:STRESSTYPE..............................................................................................................................................181

LEQTXTEST:AMPLITUDE.................................................................................................................................................181

LEQTXTEST:APPLYSOFTEQ........................................................................................................................................... 182

LEQTXTEST:FILTERFILE..................................................................................................................................................182

LEQTXTEST:DUTWFMSCALE..........................................................................................................................................182

LEQTXTEST:LOOPBACKRUN..........................................................................................................................................183

LEQTXTEST:DUTID.......................................................................................................................................................... 183

LEQTXTEST:CLEARALL................................................................................................................................................... 183

LEQTXTEST:RUN .............................................................................................................................................................184

LEQTXTEST:STATUS........................................................................................................................................................184

LEQTXTEST:LINKTRAINING:STATUS..............................................................................................................................184

LEQTXTEST:LINKTRAINING:STOP..................................................................................................................................184

LEQTXTEST:SAVE:ID........................................................................................................................................................185

LEQTXTEST:SAVE:COMMENTS .....................................................................................................................................185

LEQTXTEST:SAVE:GENERATEDBY................................................................................................................................ 185

LEQTXTEST:INITIALPRESET...........................................................................................................................................186

LEQTXTEST:SELECTPRESET ........................................................................................................................................ 186

LEQTXTEST:LINKTRAINING:CBBAUTORESET..............................................................................................................186

LEQTXTEST:LINKTRAINING:CBBPOWERCYCLE.......................................................................................................... 187

LEQTXTEST:LINKTRAINING:CBBPOWERRESET.......................................................................................................... 187

LEQTXTEST:LINKTRAINING:CBBWAITINGTIME............................................................................................................187

LEQTXTEST:LINKTRAINING:POWEROPTIONTYPE.......................................................................................................188

LEQTXTEST:SOFTWAREQTYPE <0/1>...........................................................................................................................188

PCIe5.0 (CEM) Receiver Test Application Help 11

Page 12

List of Figures

List of Figures

Figure 1: TekRxTest - PCIe5.0 CEM application......................................................................................................................... 17

Figure 2: TekRxTest application window..................................................................................................................................... 22

Figure 3: Launch Real-Time Oscilloscope.................................................................................................................................. 23

Figure 4: TekRxService application window................................................................................................................................24

Figure 5: Connections panel....................................................................................................................................................... 25

Figure 6: Settings panel.............................................................................................................................................................. 26

Figure 7: Components: RT Scope...............................................................................................................................................27

Figure 8: Components: TekRxService.........................................................................................................................................28

Figure 9: TP3 Calibration: Attenuator Settings............................................................................................................................29

Figure 10: TP3 Calibration: Calibrations..................................................................................................................................... 30

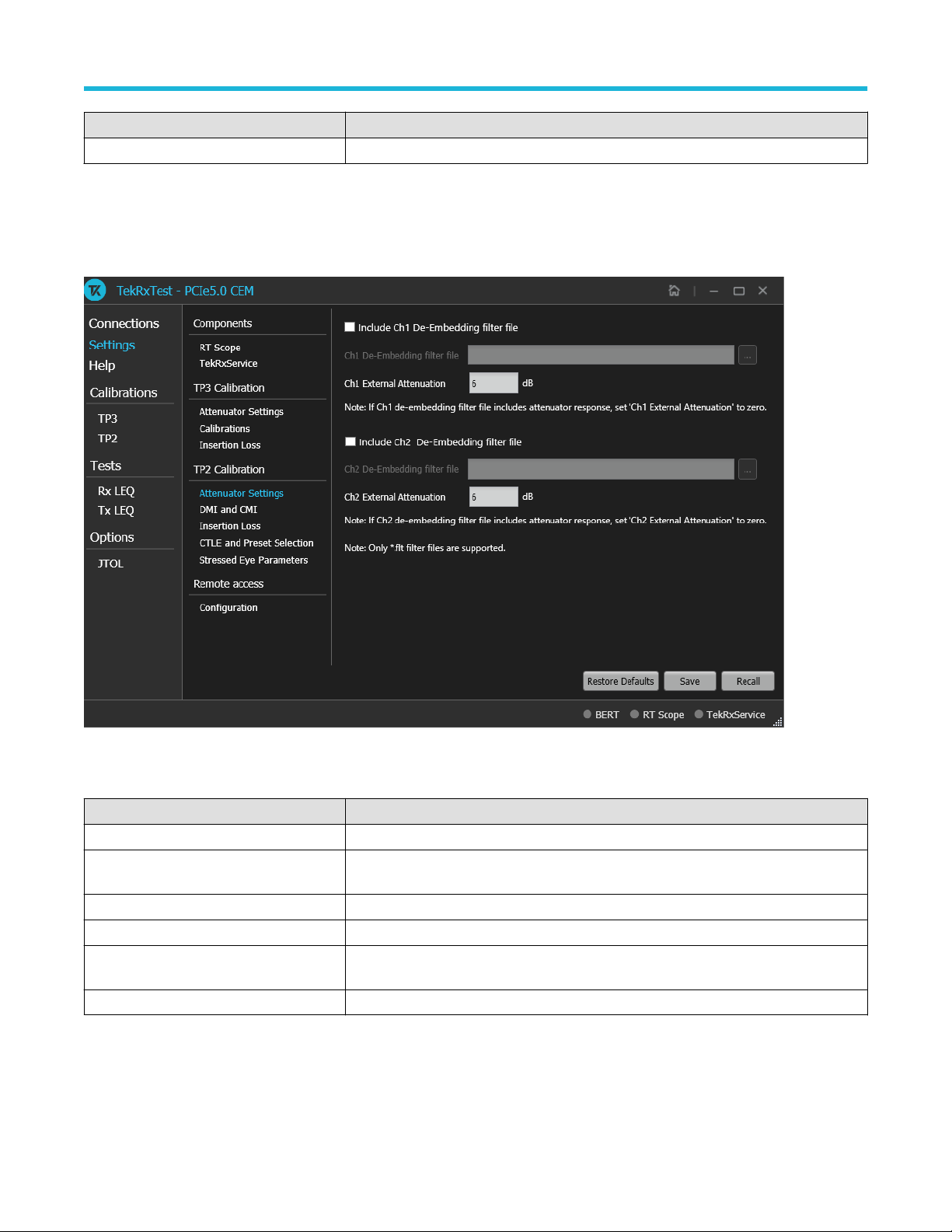

Figure 11: TP2 Calibration: Attenuator Settings..........................................................................................................................31

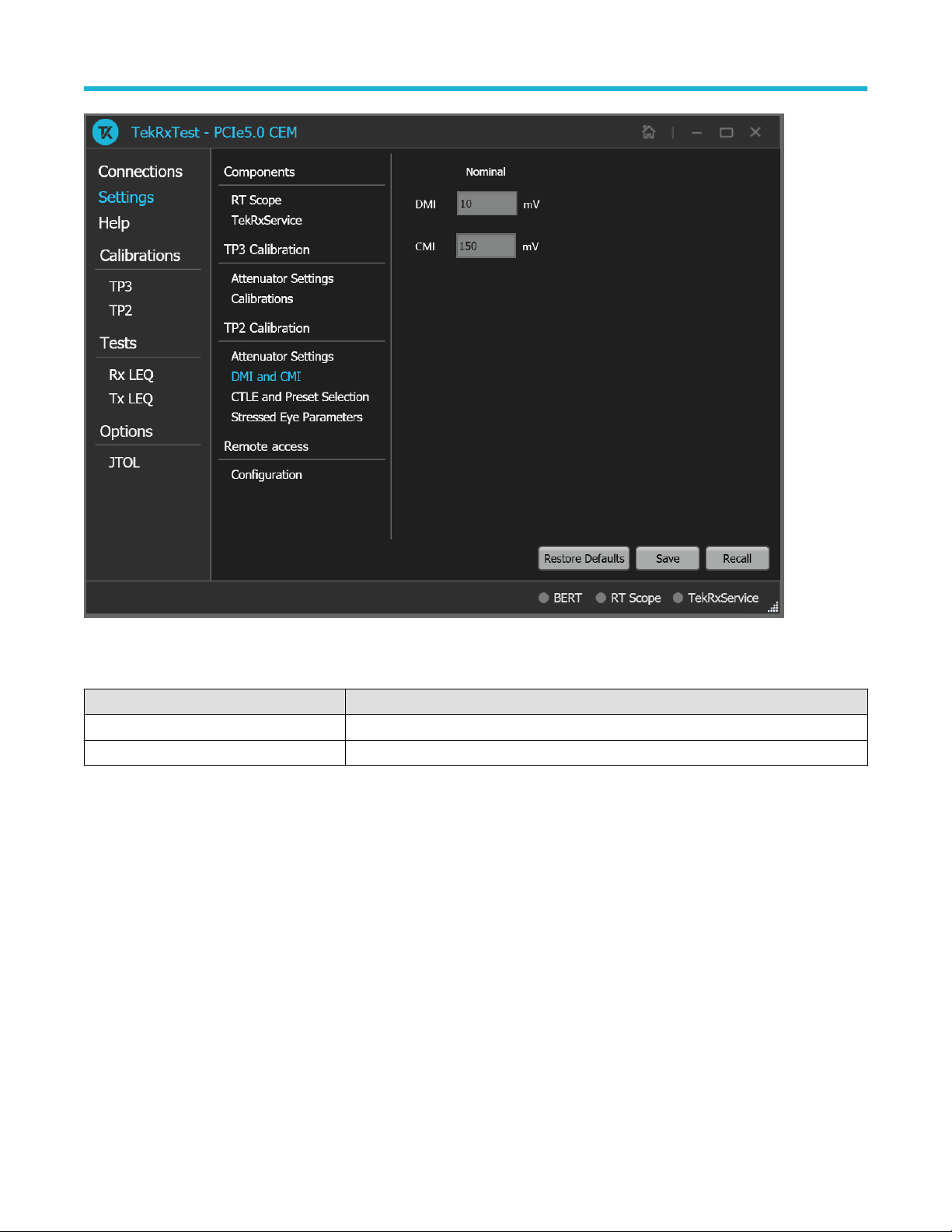

Figure 12: TP2 Calibration: DMI and CMI .................................................................................................................................. 32

Figure 13: TP2 Calibration: CTLE and Preset Selection.............................................................................................................33

Figure 14: TP2 Calibration: Stressed Eye Parameters............................................................................................................... 34

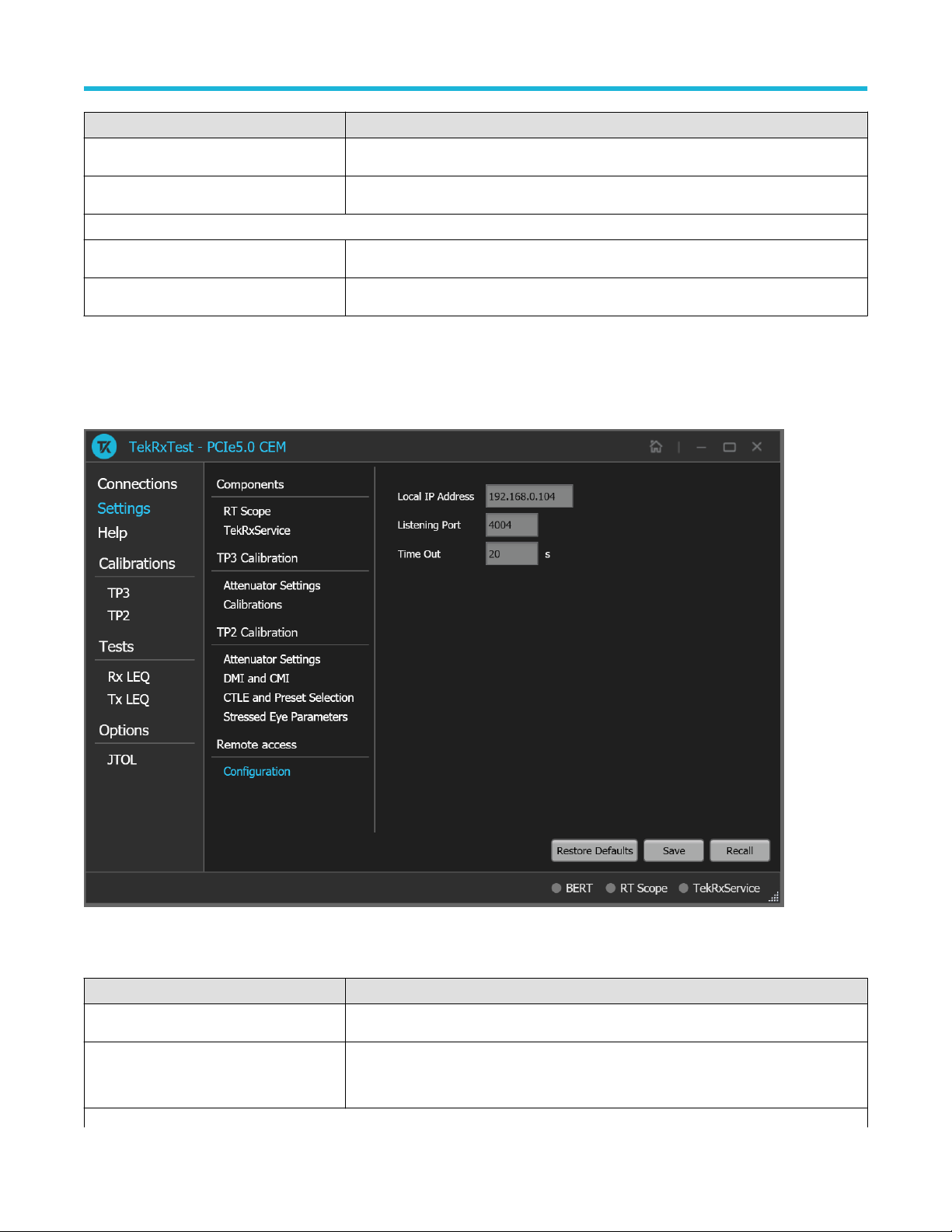

Figure 15: Remote access: Configuration...................................................................................................................................35

Figure 16: TP3 Calibration.......................................................................................................................................................... 37

Figure 17: TP3 Calibration: Connection Diagram....................................................................................................................... 38

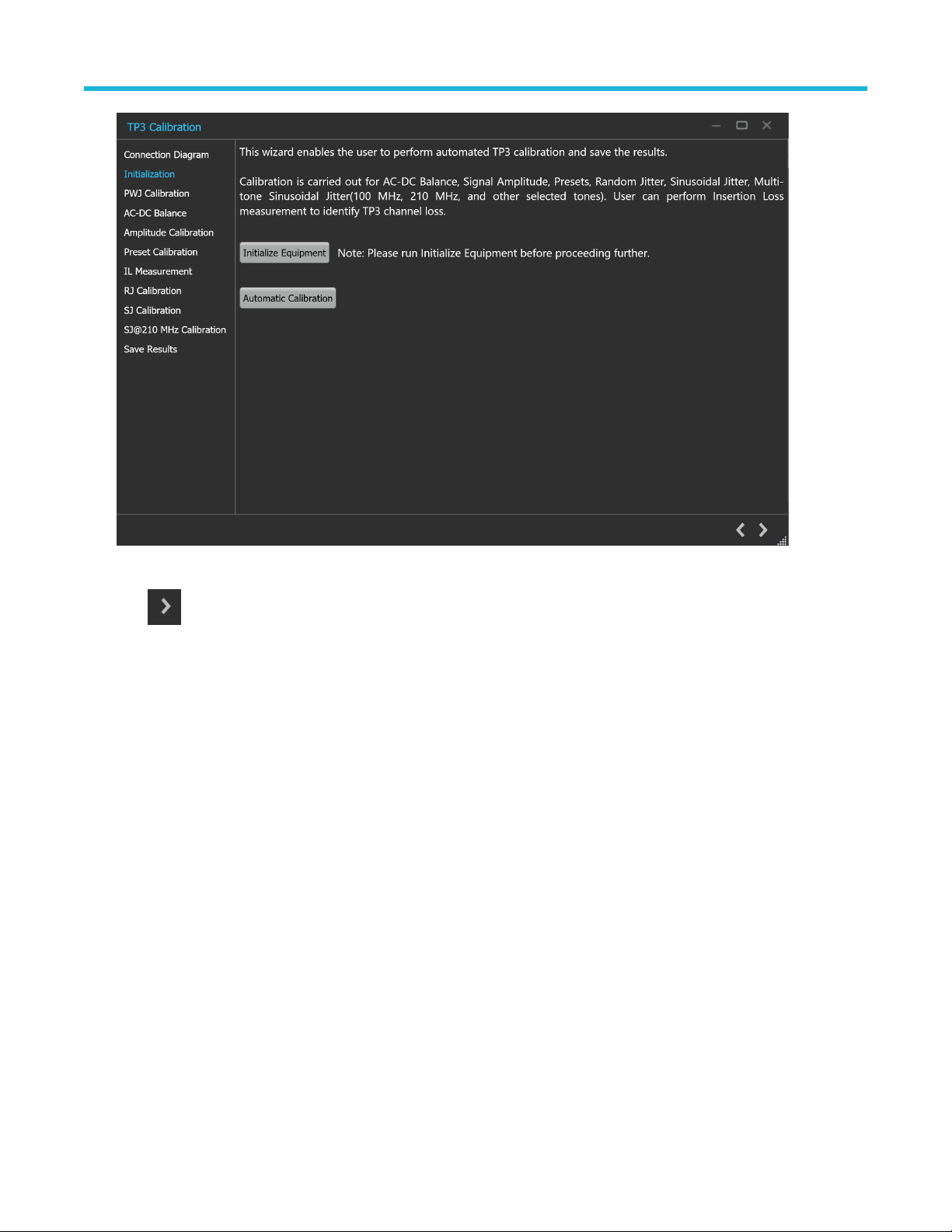

Figure 18: TP3 Calibration: Initialization..................................................................................................................................... 39

Figure 19: TP3 Calibration: PWJ Calibration.............................................................................................................................. 40

Figure 20: TP3 Calibration: AC-DC Balance...............................................................................................................................41

Figure 21: TP3 Calibration: Amplitude Calibration...................................................................................................................... 42

Figure 22: TP3 Calibration: Preset Calibration............................................................................................................................43

Figure 23: TP3 Calibration: IL Measurement.............................................................................................................................. 44

Figure 24: TP3 Calibration: RJ Calibration..................................................................................................................................45

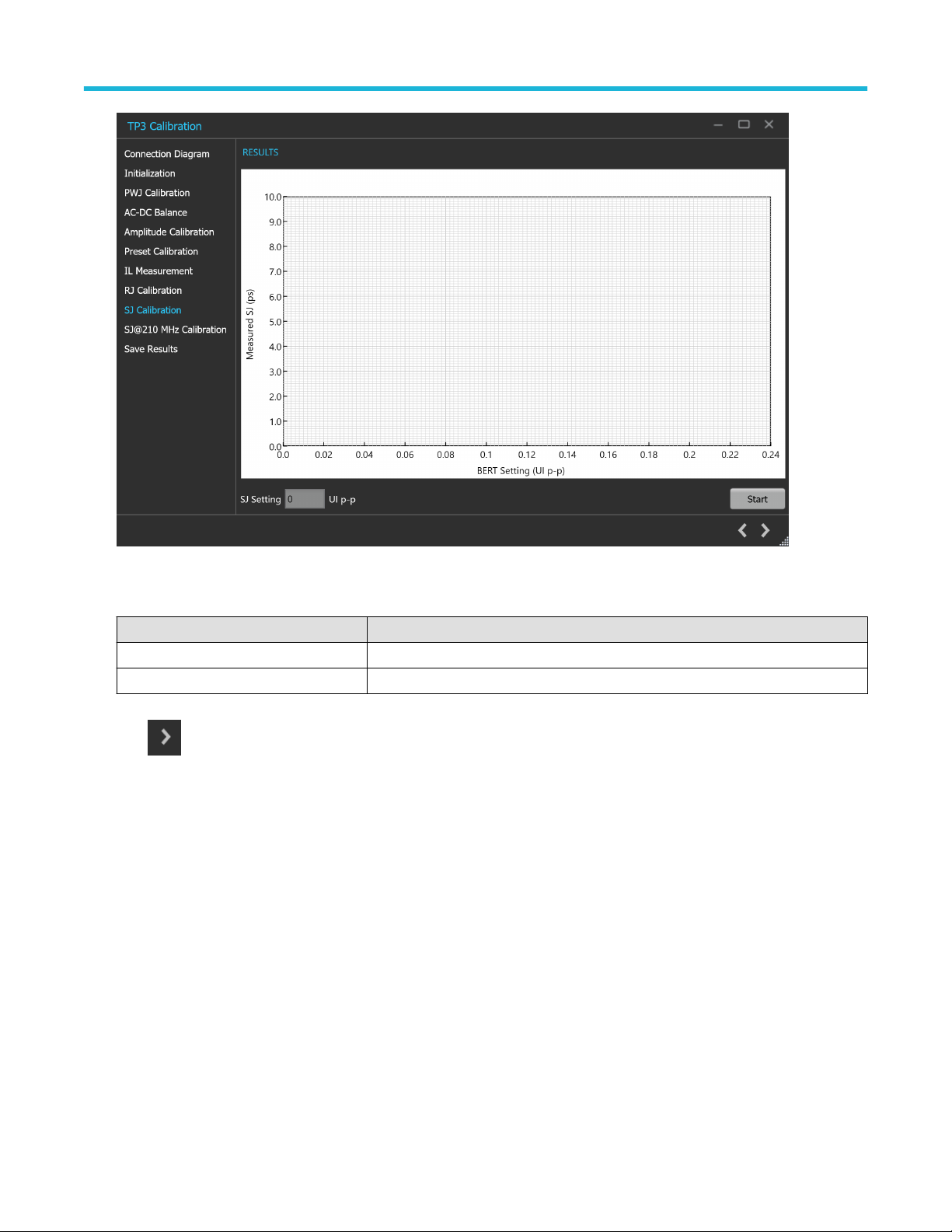

Figure 25: TP3 Calibration: SJ Calibration..................................................................................................................................46

Figure 26: TP3 Calibration: SJ@210 MHz Calibration................................................................................................................47

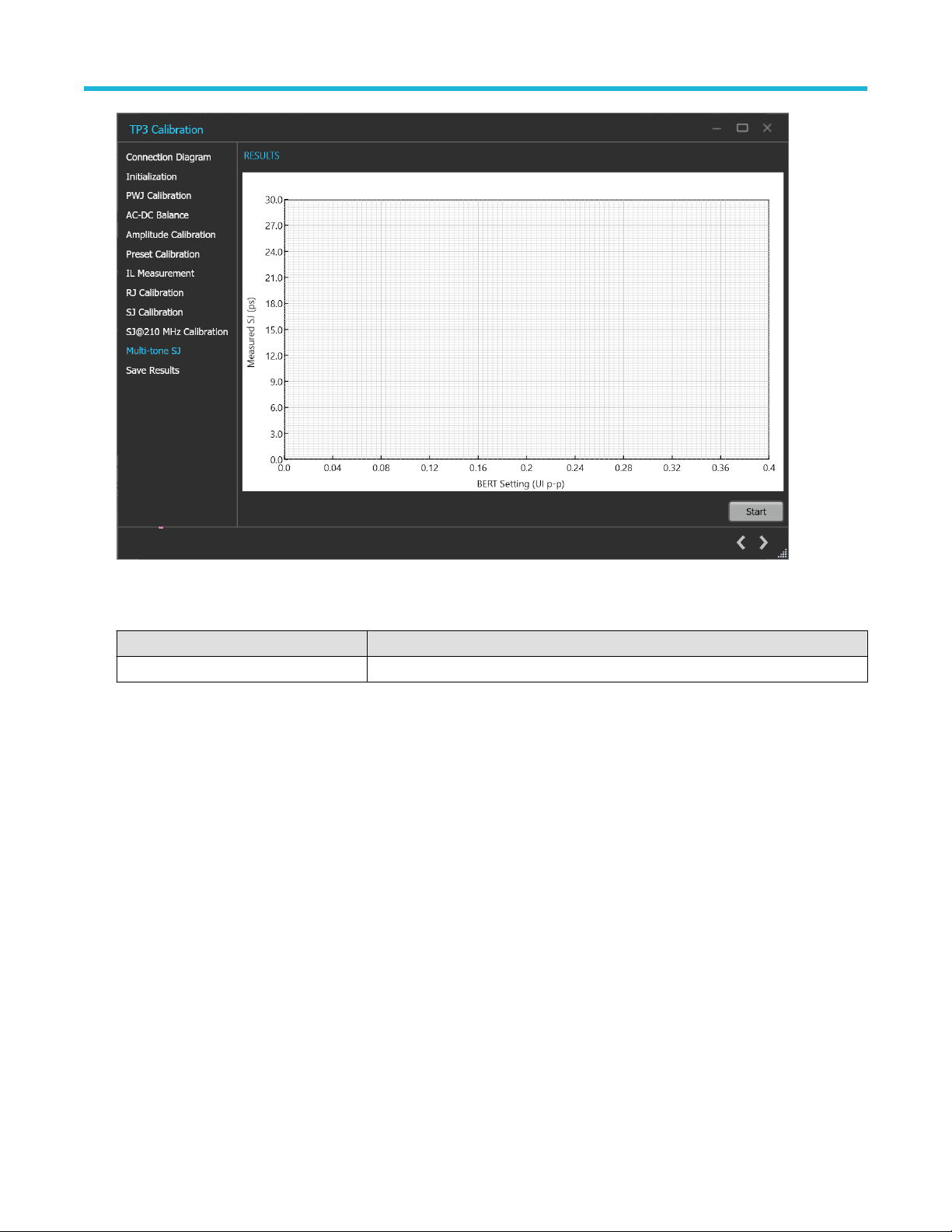

Figure 27: TP3 Calibration: Multi-tone SJ................................................................................................................................... 48

Figure 28: TP3 Calibration: Save Results................................................................................................................................... 49

Figure 29: TP2 Calibration.......................................................................................................................................................... 50

Figure 30: TP2 Calibration: Description...................................................................................................................................... 51

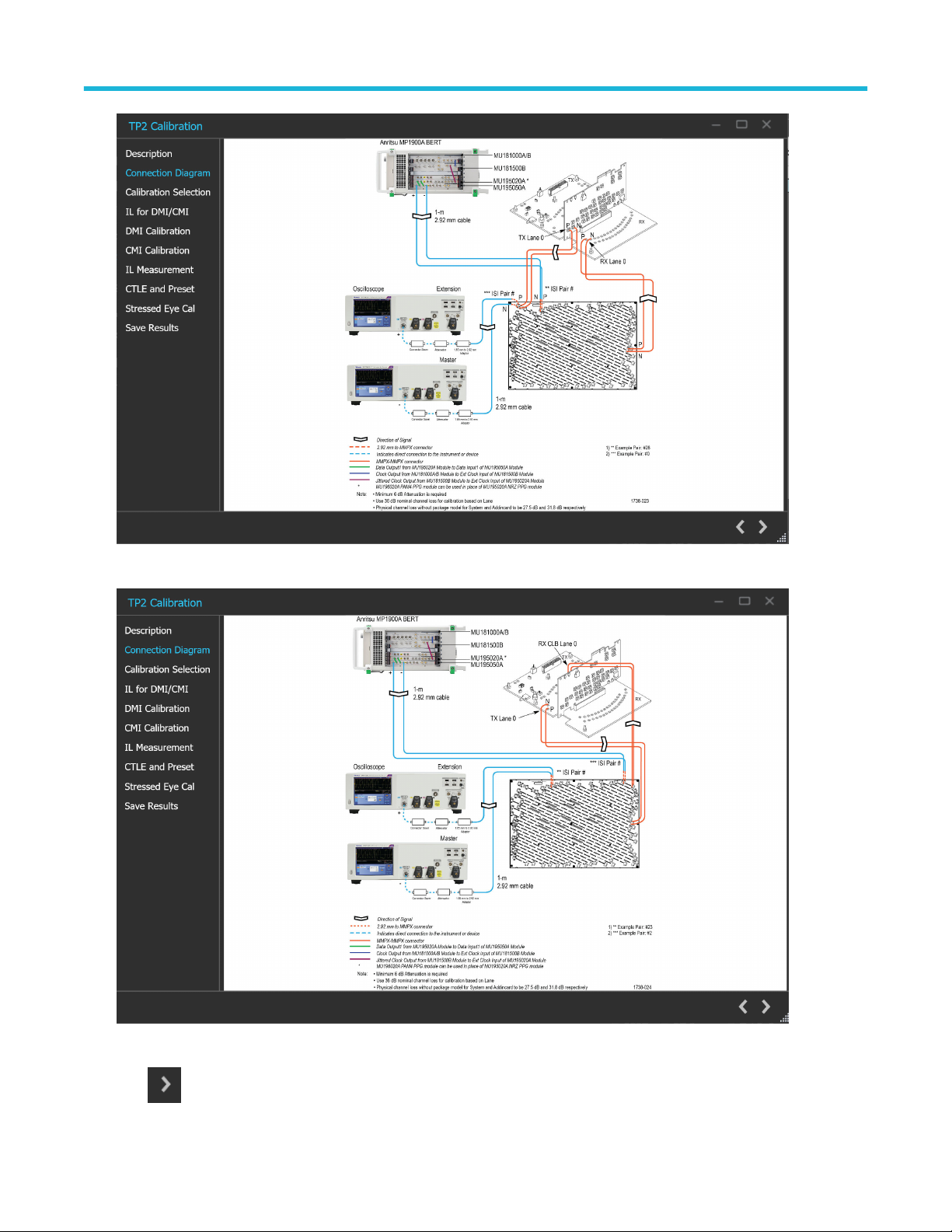

Figure 31: TP2 Calibration: Connection Diagram-AIC ............................................................................................................... 52

Figure 32: TP2 Calibration: Connection Diagram-System ......................................................................................................... 52

12

Page 13

List of Figures

Figure 33: TP2 Calibration: Calibration Selection....................................................................................................................... 53

Figure 34: TP2 Calibration: IL for DMI/CMI.................................................................................................................................54

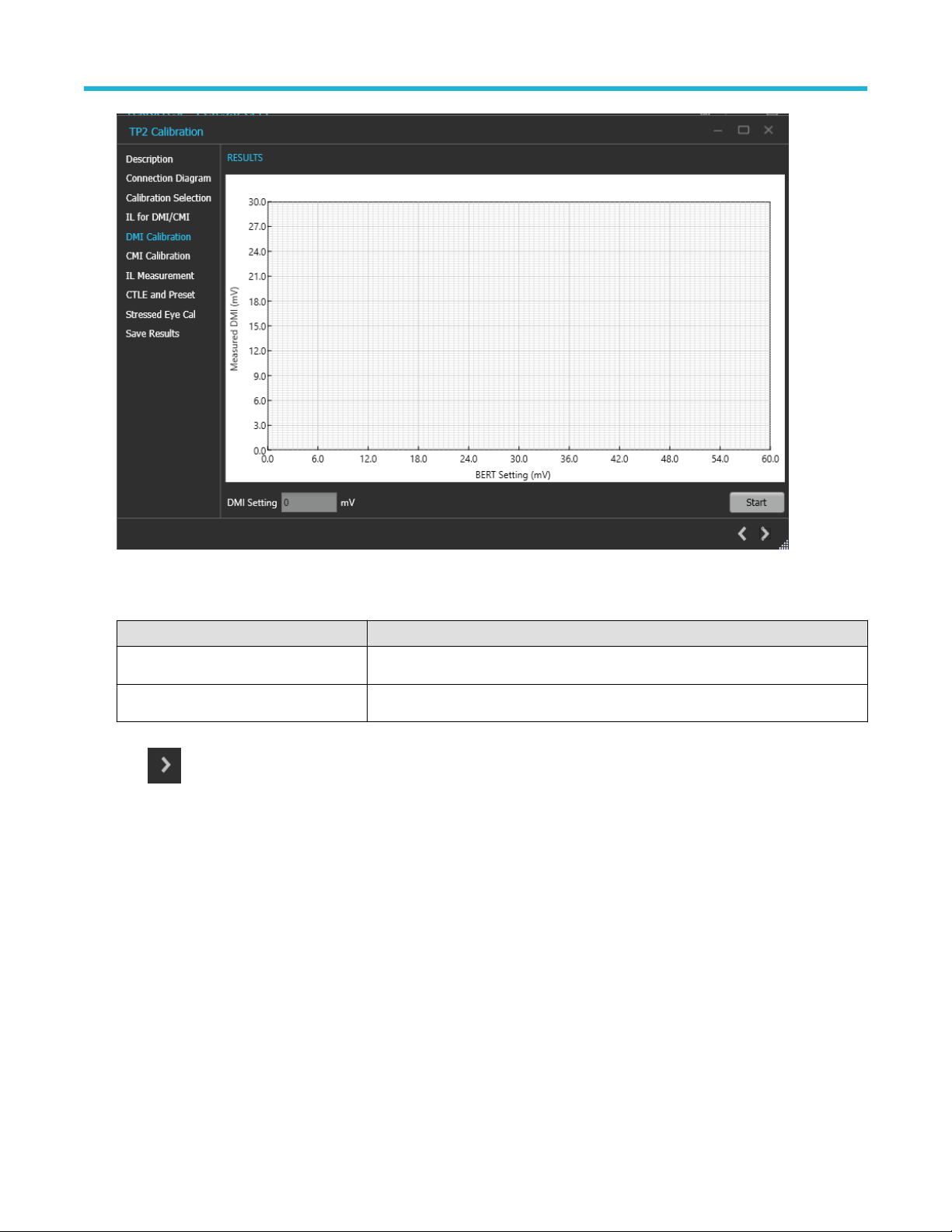

Figure 35: TP2 Calibration: DMI Calibration............................................................................................................................... 55

Figure 36: TP2 Calibration: CMI Calibration............................................................................................................................... 56

Figure 37: TP2 Calibration: IL Measurement.............................................................................................................................. 57

Figure 38: TP2 Calibration: CTLE and Preset ............................................................................................................................58

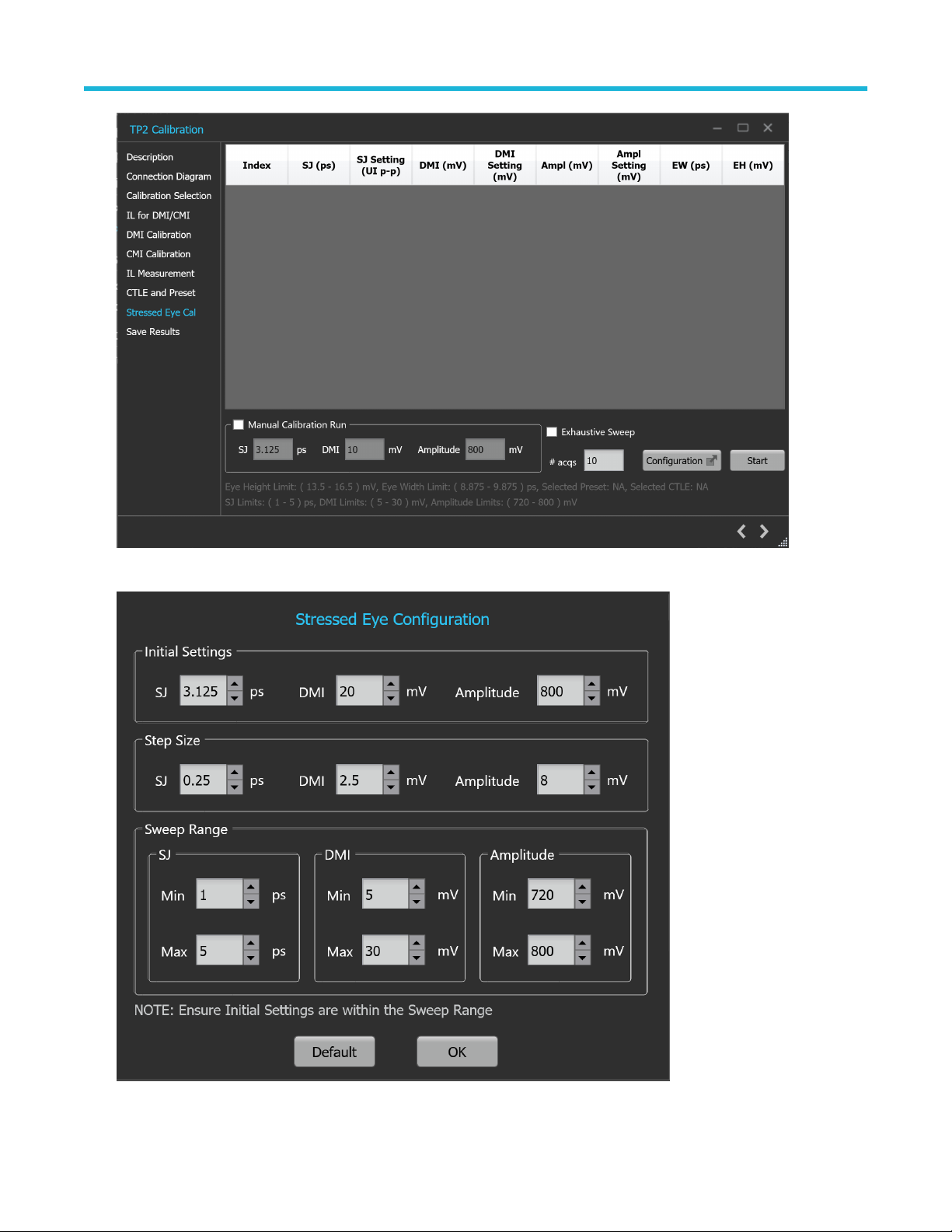

Figure 39: TP2 Calibration: Stressed Eye Cal............................................................................................................................ 59

Figure 40: TP2 Calibration: Stressed Eye Configuration............................................................................................................ 59

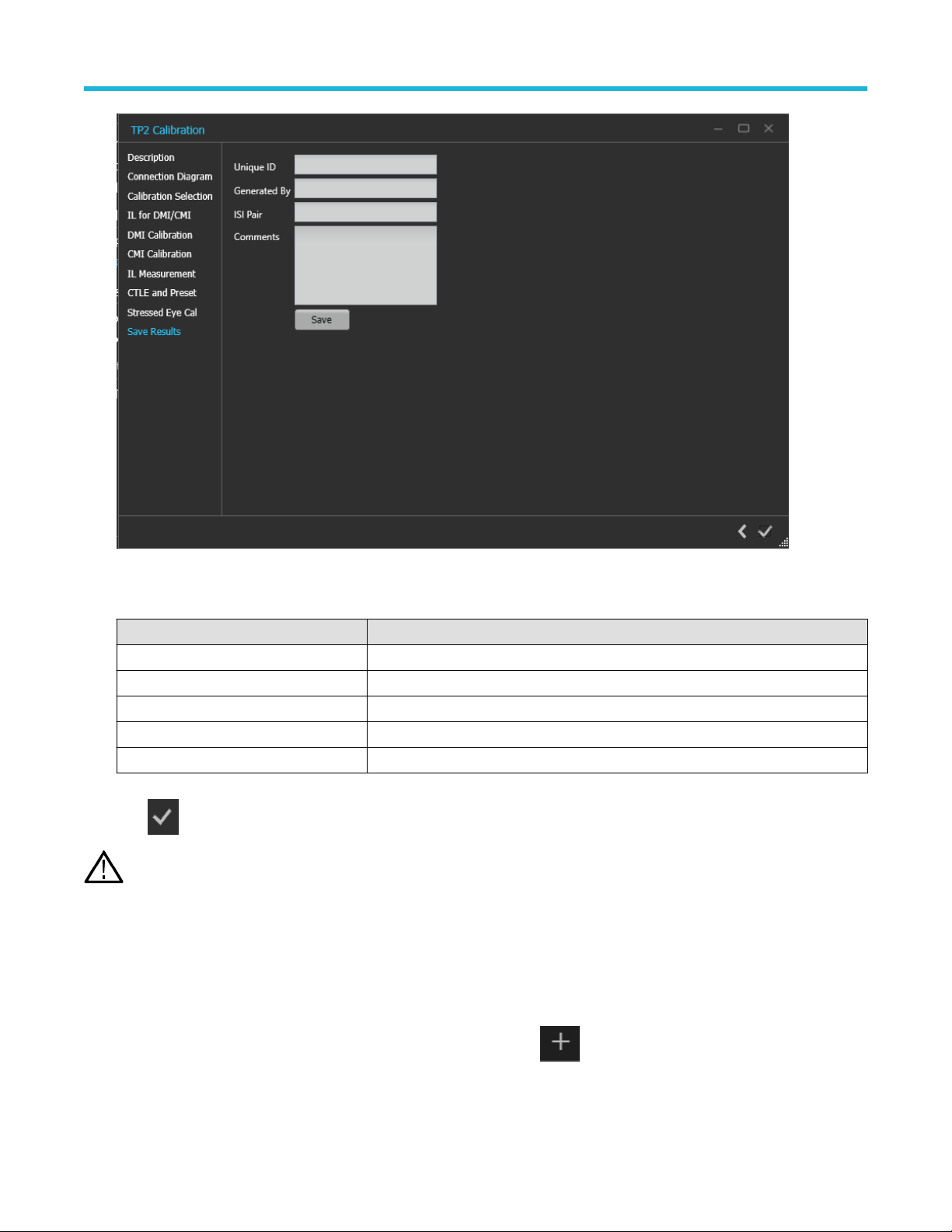

Figure 41: TP2 Calibration: Save Results................................................................................................................................... 61

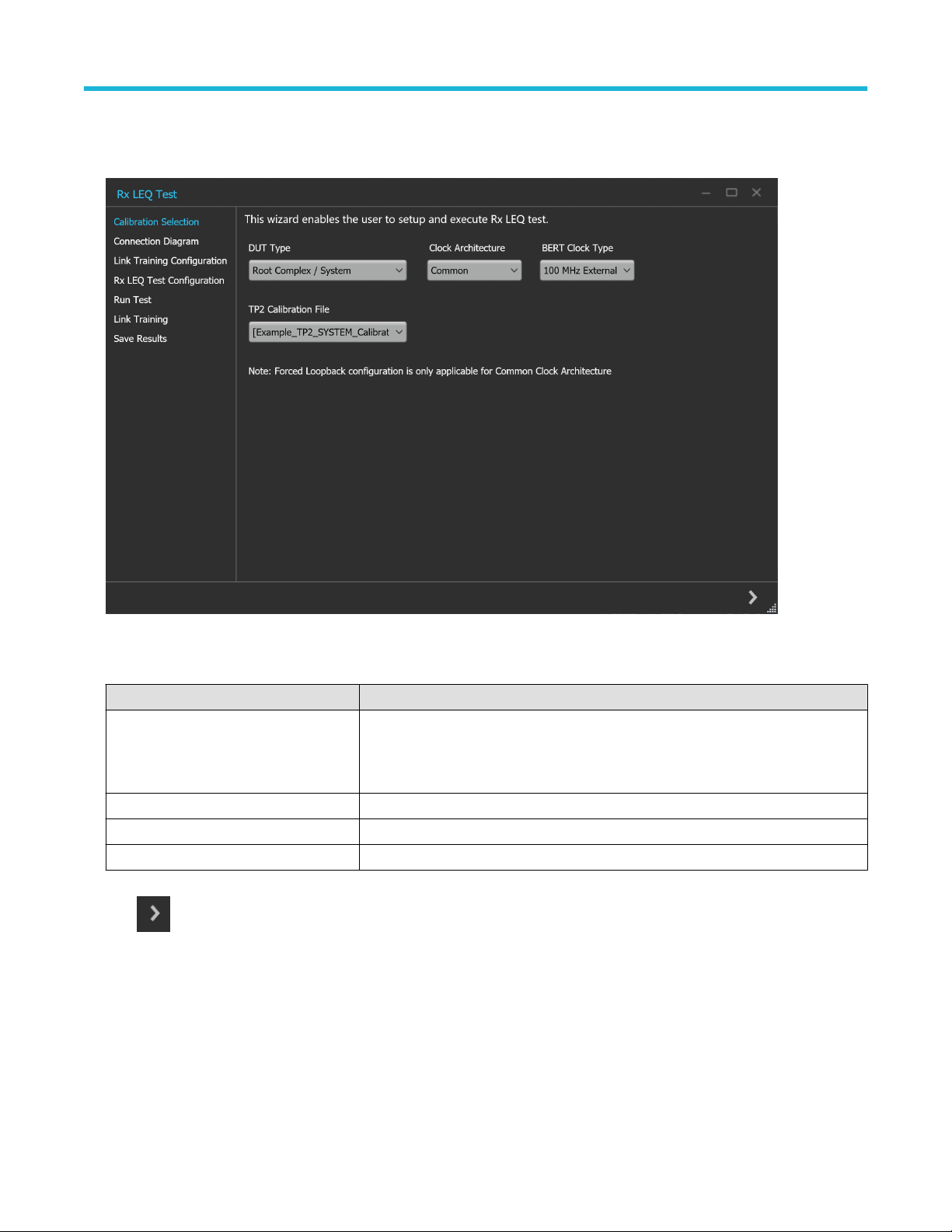

Figure 42: Rx LEQ Test: Calibration Selection............................................................................................................................62

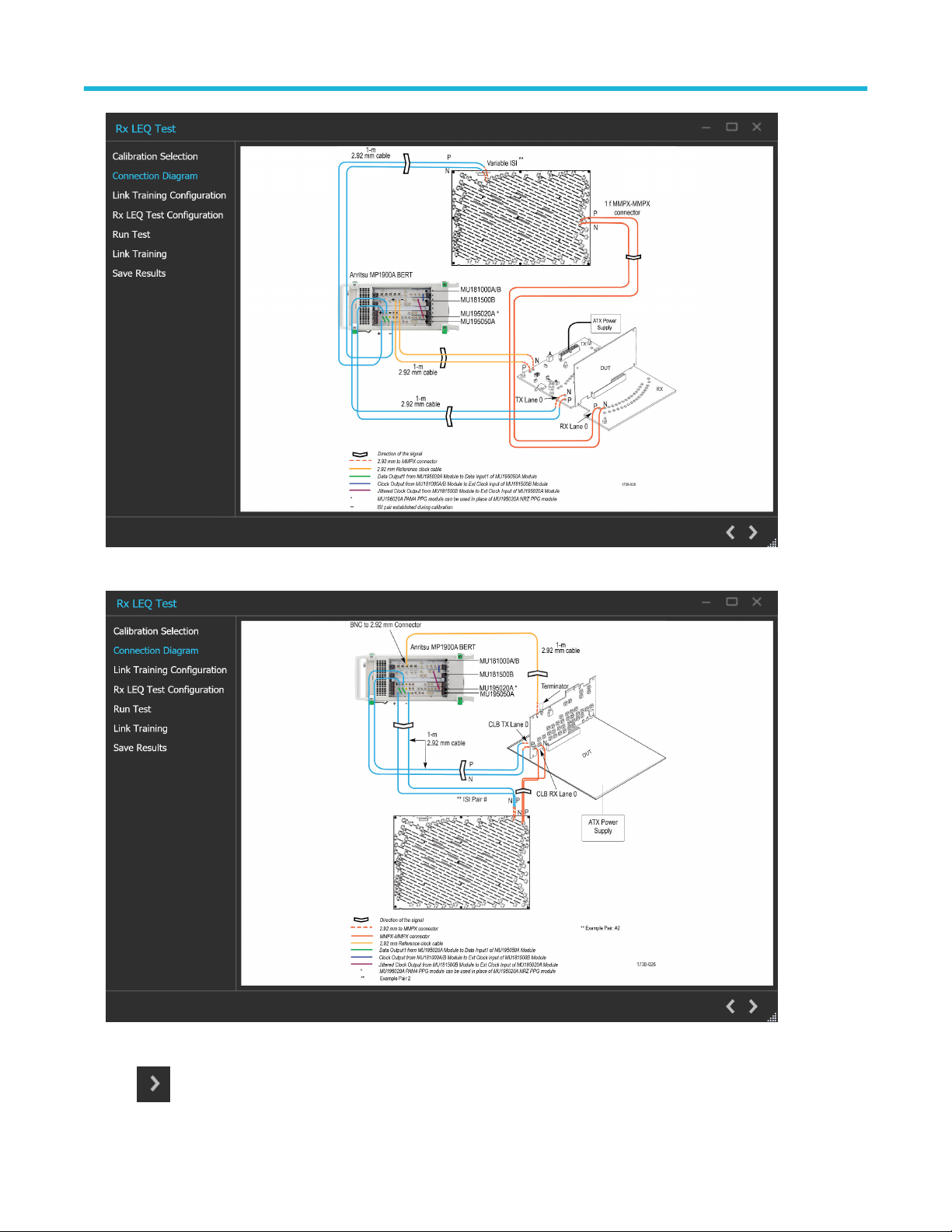

Figure 43: Rx LEQ Test: Connection Diagram(AIC)....................................................................................................................63

Figure 44: Rx LEQ Test: Connection Diagram(System)..............................................................................................................63

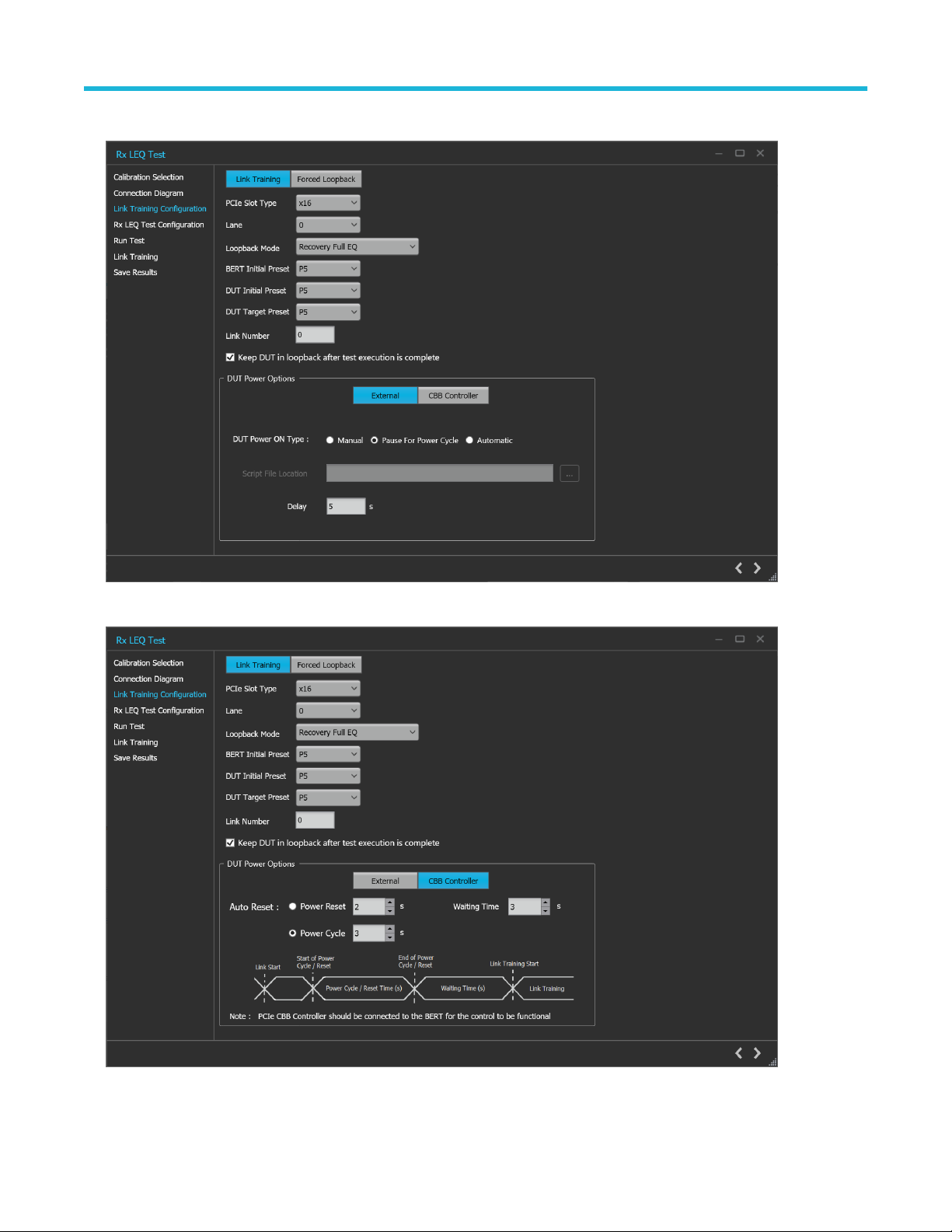

Figure 45: Rx LEQ Test: Link Training Configuration (Link Training-External)............................................................................64

Figure 46: Rx LEQ Test: Link Training Configuration (Link Training-CBB Controller).................................................................64

Figure 47: Rx LEQ Test: Link Training Configuration (Forced Loopback)...................................................................................65

Figure 48: Rx LEQ Test: Rx LEQ Test Configuration (Basic)...................................................................................................... 67

Figure 49: Rx LEQ Test: Rx LEQ Test Configuration (SKP Ordered Set)................................................................................... 67

Figure 50: Rx LEQ Test: Run Test (Basic).................................................................................................................................. 69

Figure 51: Rx LEQ Test: Run Test (Advanced Debug)).............................................................................................................. 70

Figure 52: Rx LEQ Test: Link Training........................................................................................................................................ 73

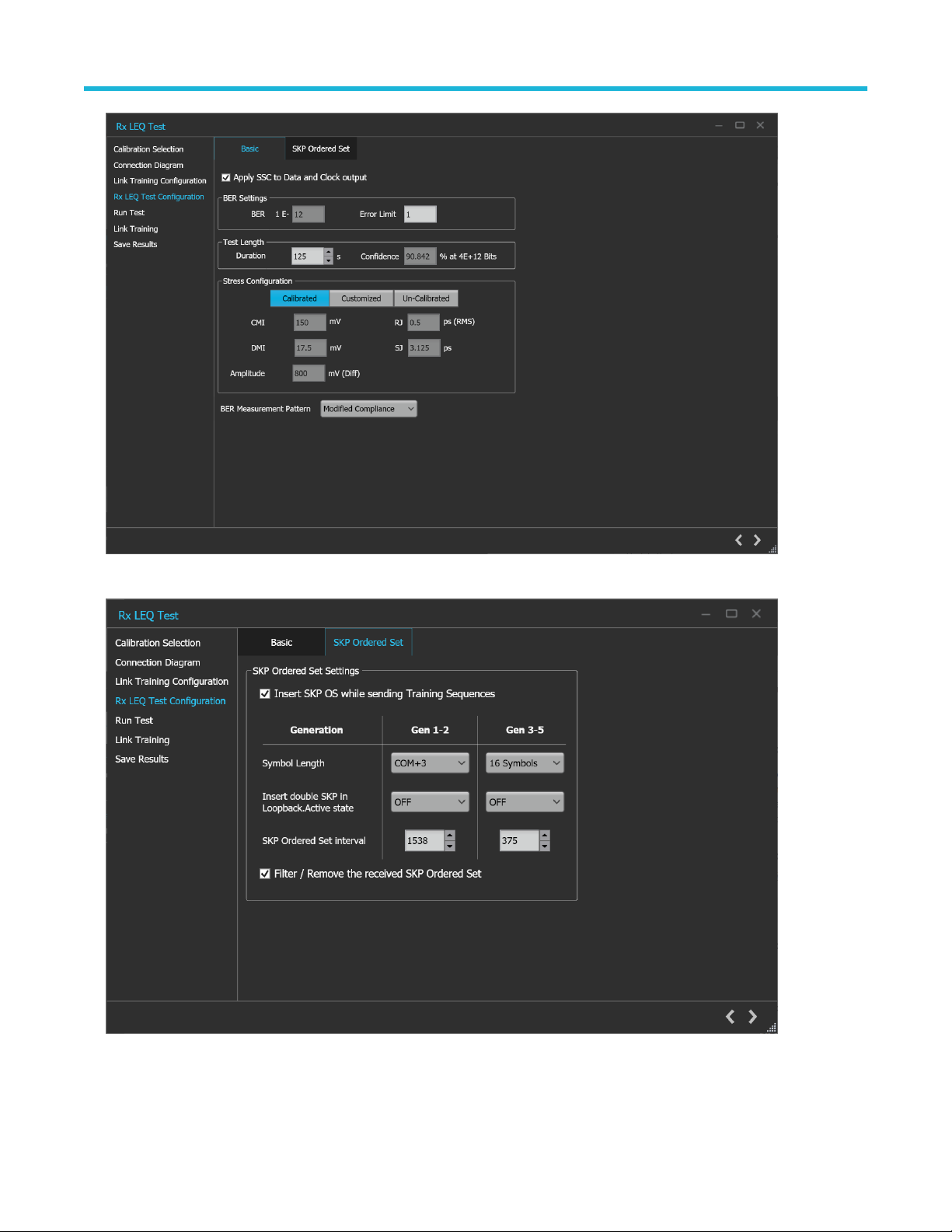

Figure 53: Rx LEQ Test: Save Results........................................................................................................................................74

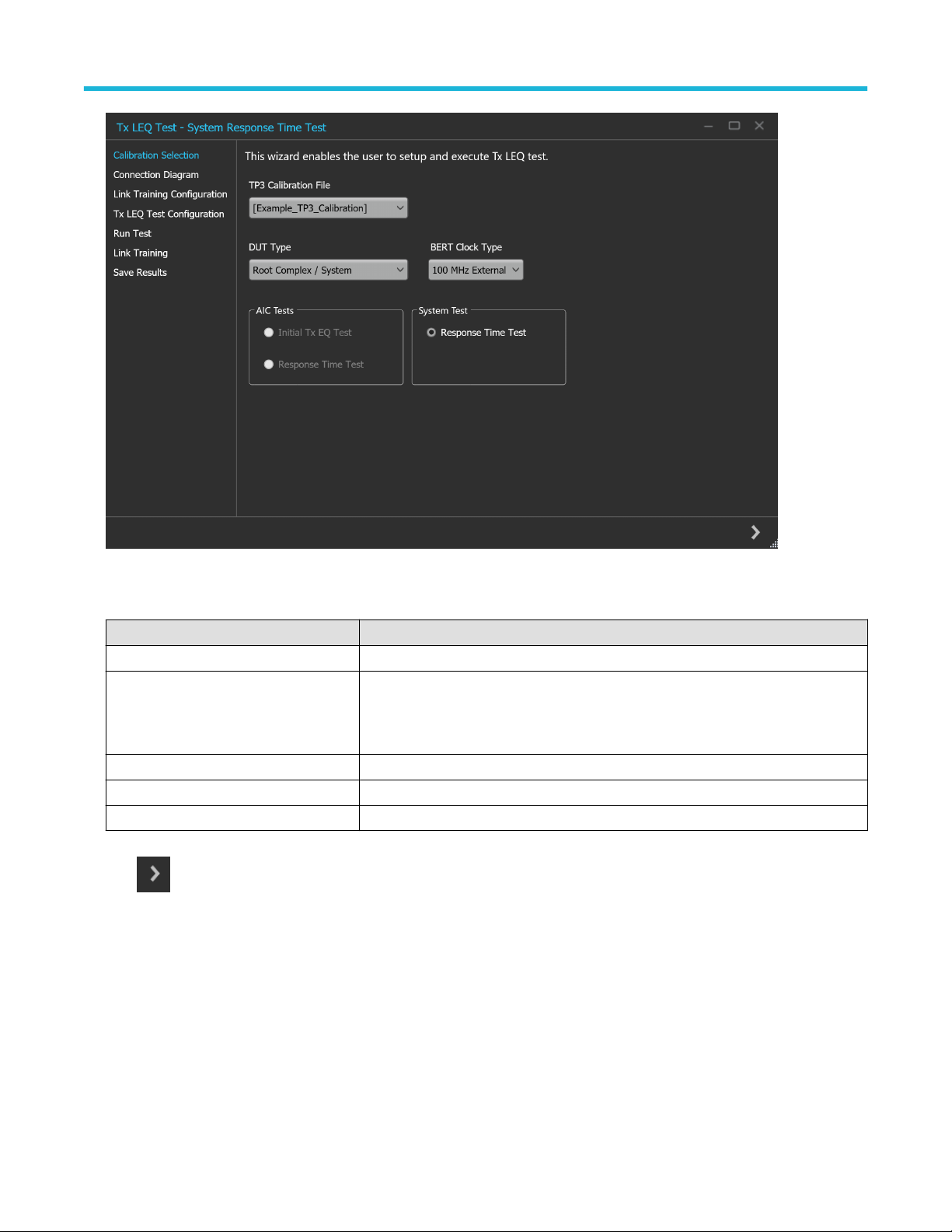

Figure 54: Tx LEQ Test: Calibration Selection............................................................................................................................ 75

Figure 55: Tx LEQ Test: Connection Diagram(AIC).................................................................................................................... 76

Figure 56: Tx LEQ Test: Connection Diagram(System).............................................................................................................. 76

Figure 57: Tx LEQ Test: Link Training Configuration (External)..................................................................................................77

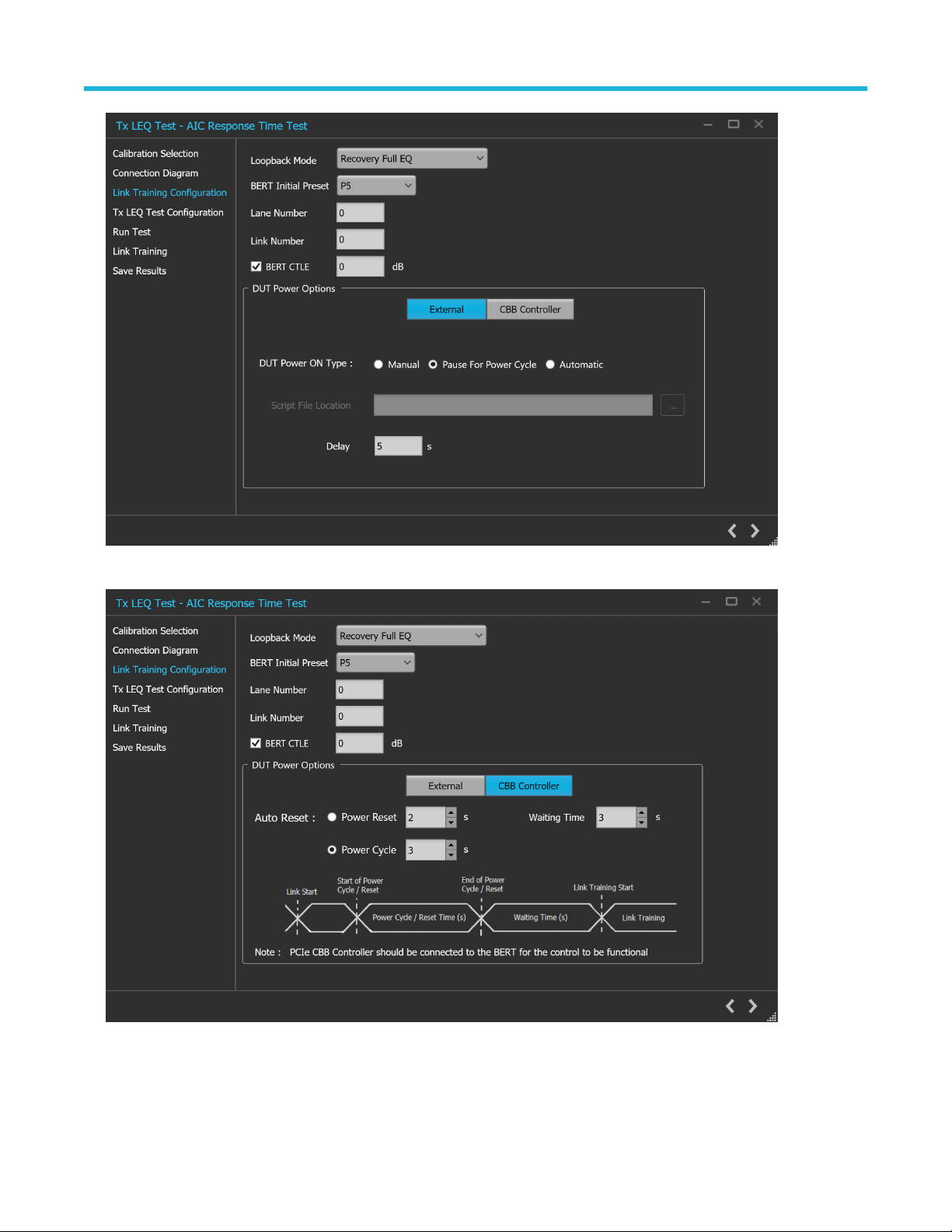

Figure 58: Tx LEQ Test: Link Training Configuration (CBB Controller).......................................................................................77

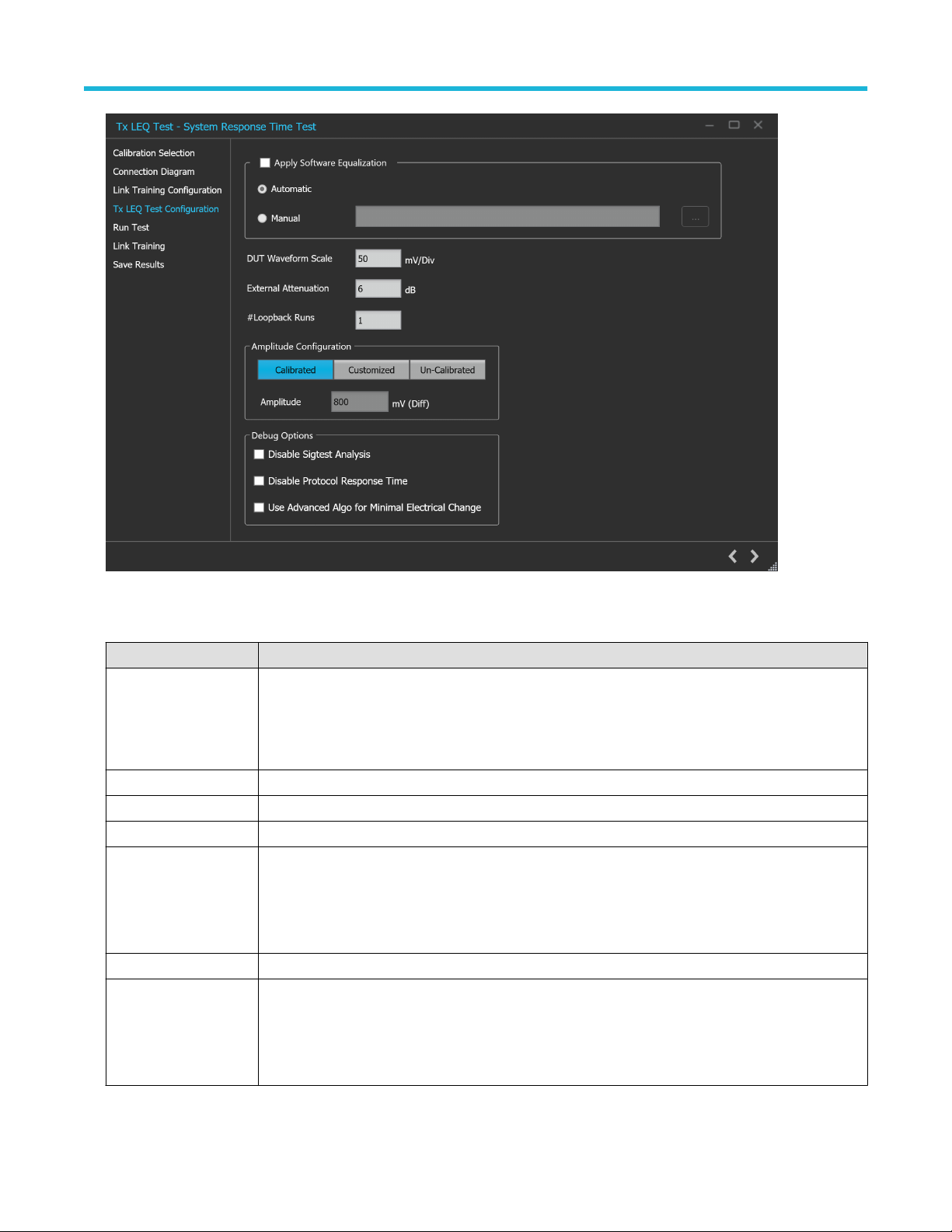

Figure 59: Tx LEQ Test: Tx LEQ Test Configuration................................................................................................................... 79

Figure 60: Tx LEQ Test: Run Test(System Response Time Test)...............................................................................................80

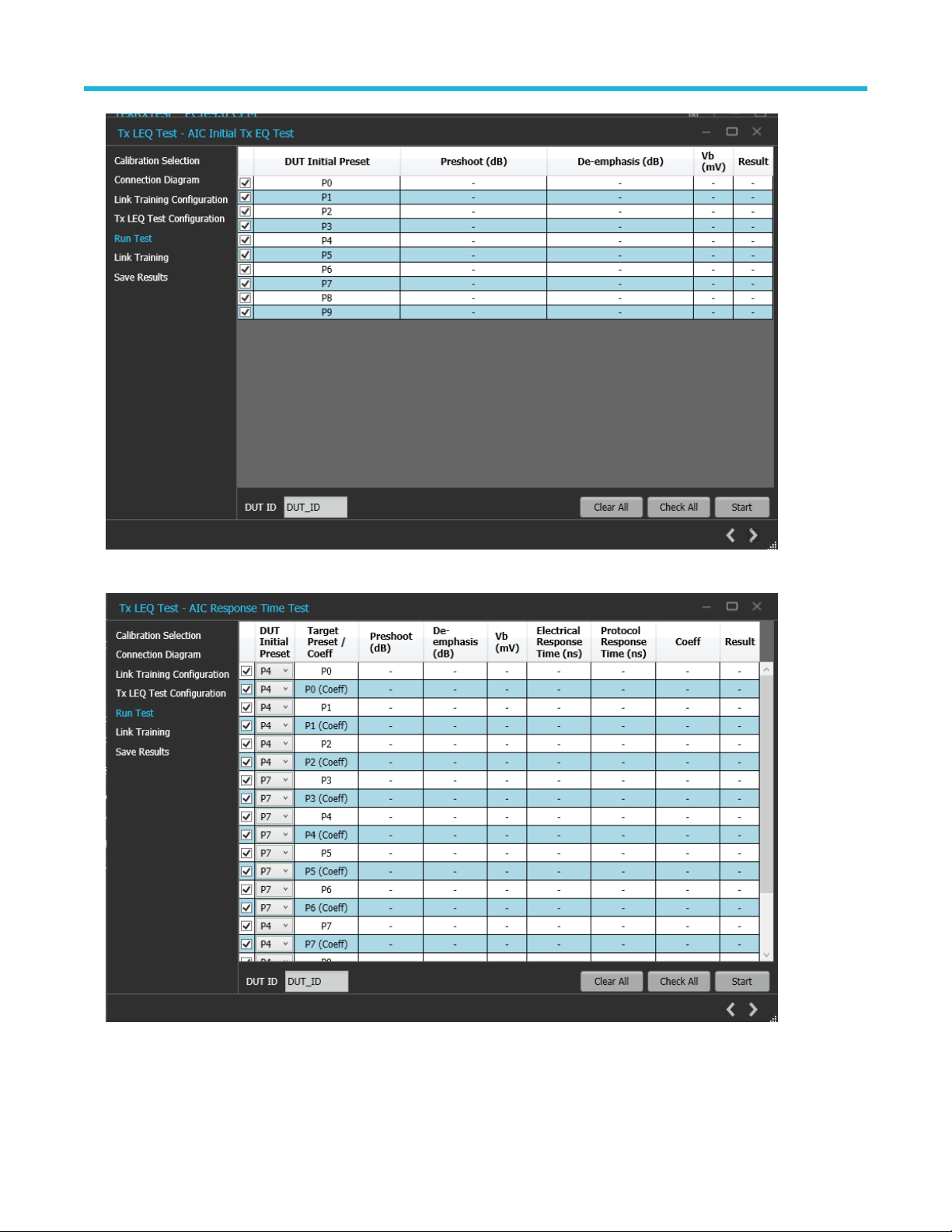

Figure 61: Tx LEQ Test: Run Test(AIC Initial Tx EQ Test).......................................................................................................... 81

Figure 62: Tx LEQ Test: Run Test(AIC Response Time Test).....................................................................................................81

Figure 63: Tx LEQ Test: Link Training.........................................................................................................................................82

Figure 64: Tx LEQ Test: Save Results........................................................................................................................................ 83

Figure 65: JTOL Test...................................................................................................................................................................84

Figure 66: JTOL Test: Calibration Selection................................................................................................................................85

Figure 67: JTOL Test: Connection Diagram(AIC)........................................................................................................................86

PCIe5.0 (CEM) Receiver Test Application Help 13

Page 14

List of Figures

Figure 68: JTOL Test: Connection Diagram(System)..................................................................................................................86

Figure 69: JTOL Test: Link Training Configuration (Link Training-External)................................................................................87

Figure 70: JTOL Test: Link Training Configuration (Link Training-CBB Controller).....................................................................88

Figure 71: JTOL Test: Link Training Configuration (Forced Loopback).......................................................................................89

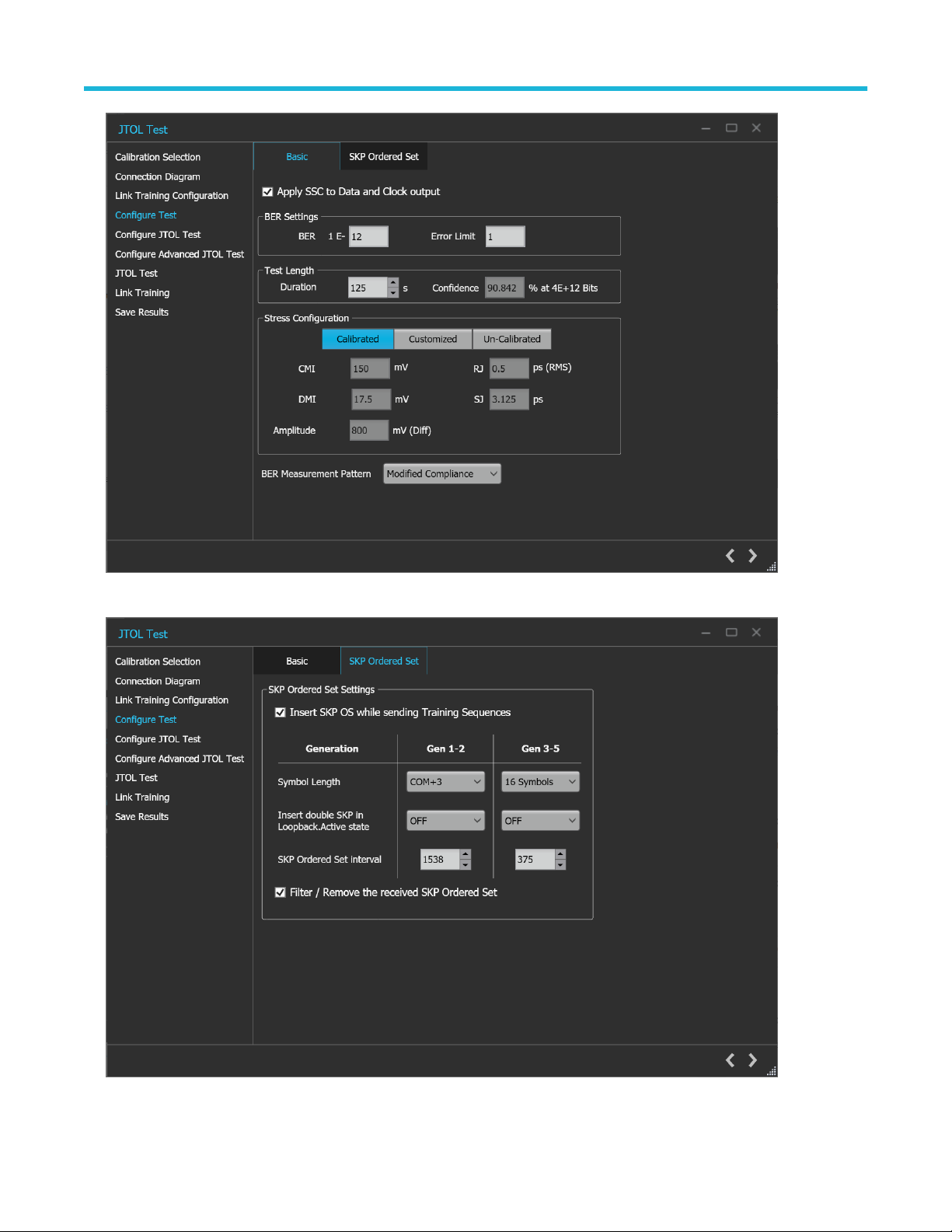

Figure 72: JTOL Test: Configure Test (Basic)............................................................................................................................. 91

Figure 73: JTOL Test: Configure Test (SKP Ordered Set).......................................................................................................... 91

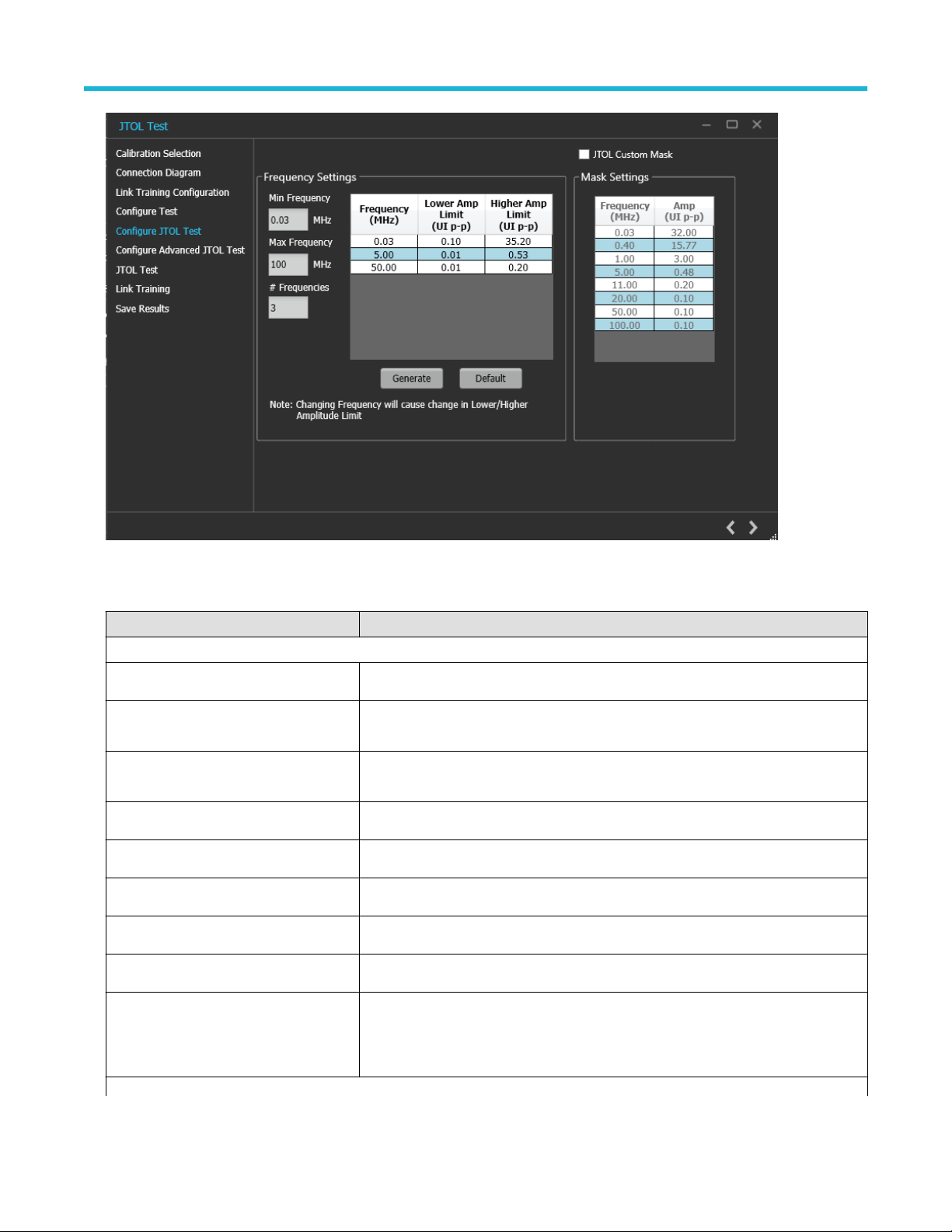

Figure 74: JTOL Test: Configure JTOL Test................................................................................................................................93

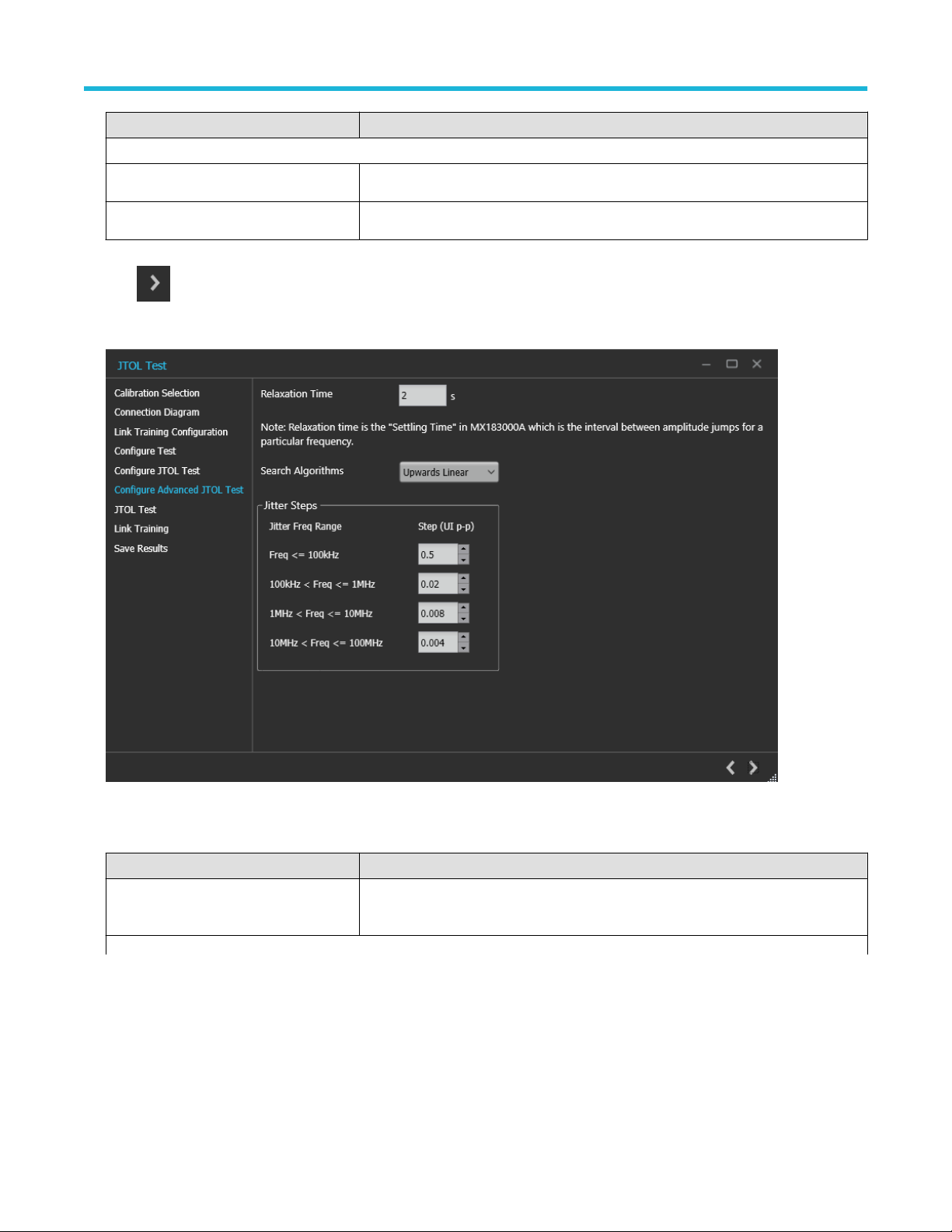

Figure 75: JTOL Test: Configure Advanced JTOL Test...............................................................................................................94

Figure 76: JTOL Test: JTOL Chart.............................................................................................................................................. 96

Figure 77: JTOL Test (Result Table)............................................................................................................................................97

Figure 78: JTOL Test: Link Training............................................................................................................................................ 98

Figure 79: JTOL Test: Save Results............................................................................................................................................99

14

Page 15

List of Tables

List of Tables

Table 1: Product documentation..................................................................................................................................................18

Table 2: Icon descriptions............................................................................................................................................................19

Table 3: Application panels overview.......................................................................................................................................... 24

Table 4: Connections panel.........................................................................................................................................................25

Table 5: Settings panel configurations........................................................................................................................................ 26

Table 6: Components: RT Scope................................................................................................................................................ 27

Table 7: Components: TekRxService.......................................................................................................................................... 28

Table 8: TP3 Calibration: Attenuator Settings............................................................................................................................. 29

Table 9: TP3 Calibration: Calibrations.........................................................................................................................................30

Table 10: PCIe Gen 5 TP2 Calibration: Attenuator Settings....................................................................................................... 31

Table 11: TP2 Calibration: DMI and CMI ....................................................................................................................................32

Table 12: TP2 Calibration: CTLE and Preset Selection.............................................................................................................. 33

Table 13: TP2 Calibration: Stressed Eye Parameters.................................................................................................................34

Table 14: Remote access: Configuration.................................................................................................................................... 35

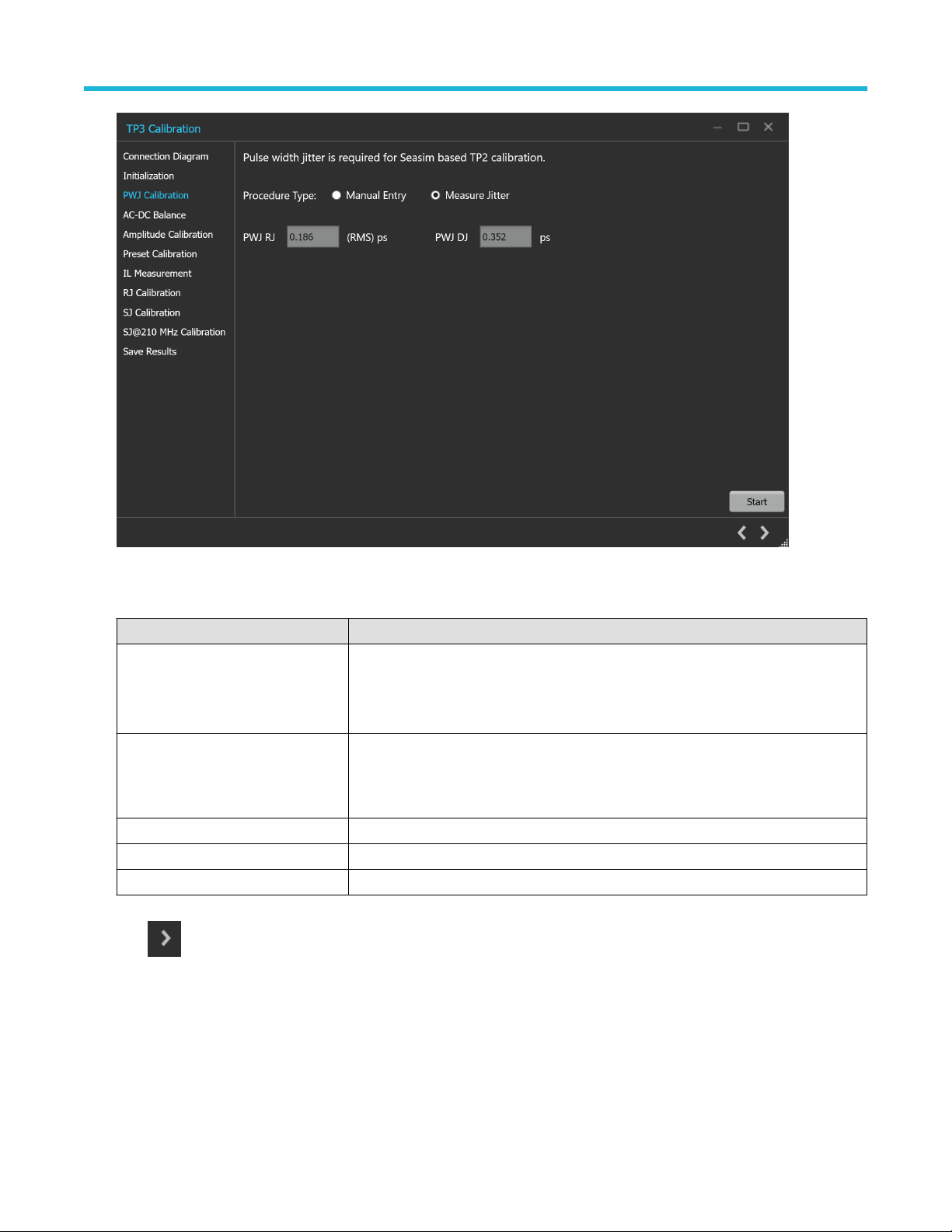

Table 15: TP3 Calibration: PWJ Calibration................................................................................................................................ 40

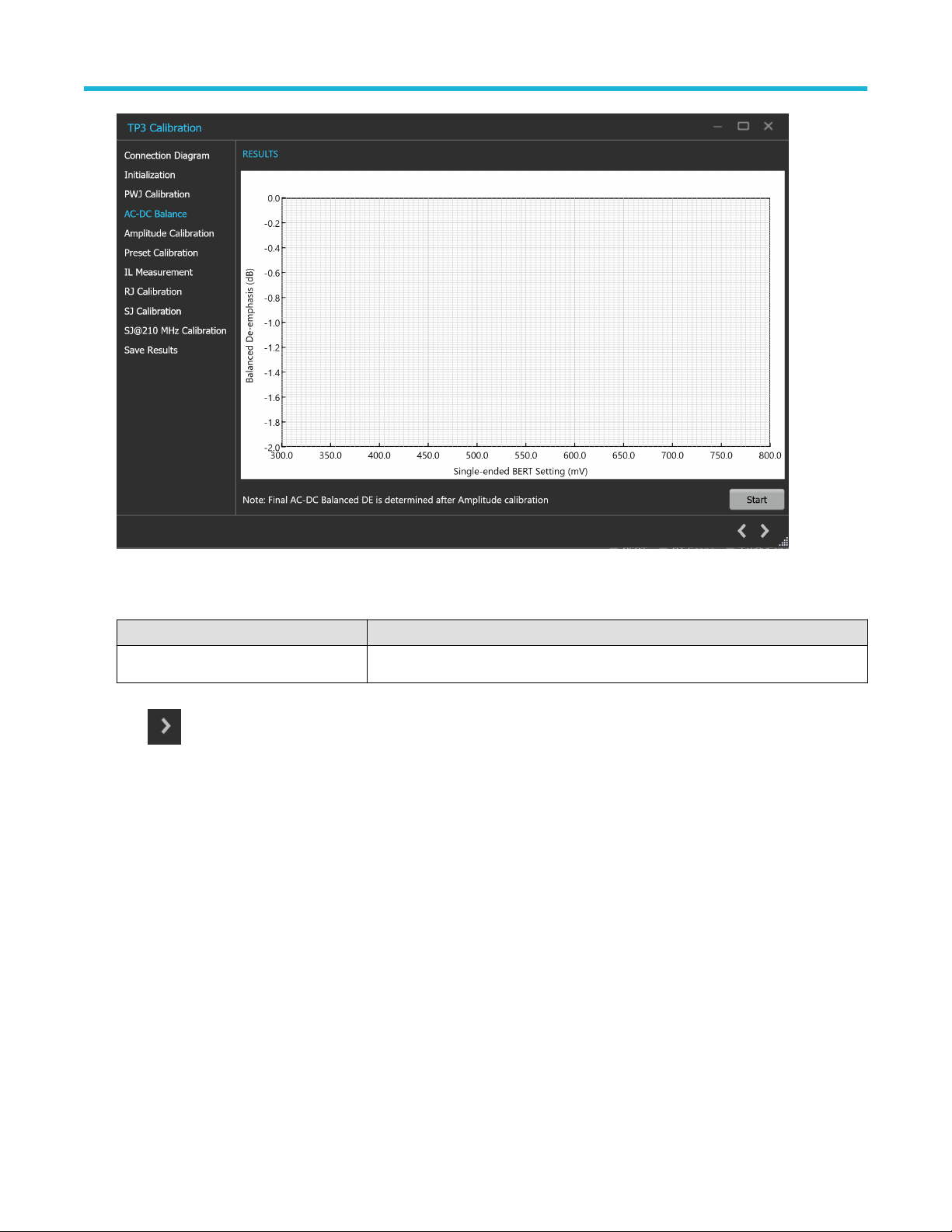

Table 16: TP3 Calibration: AC-DC Balance................................................................................................................................ 41

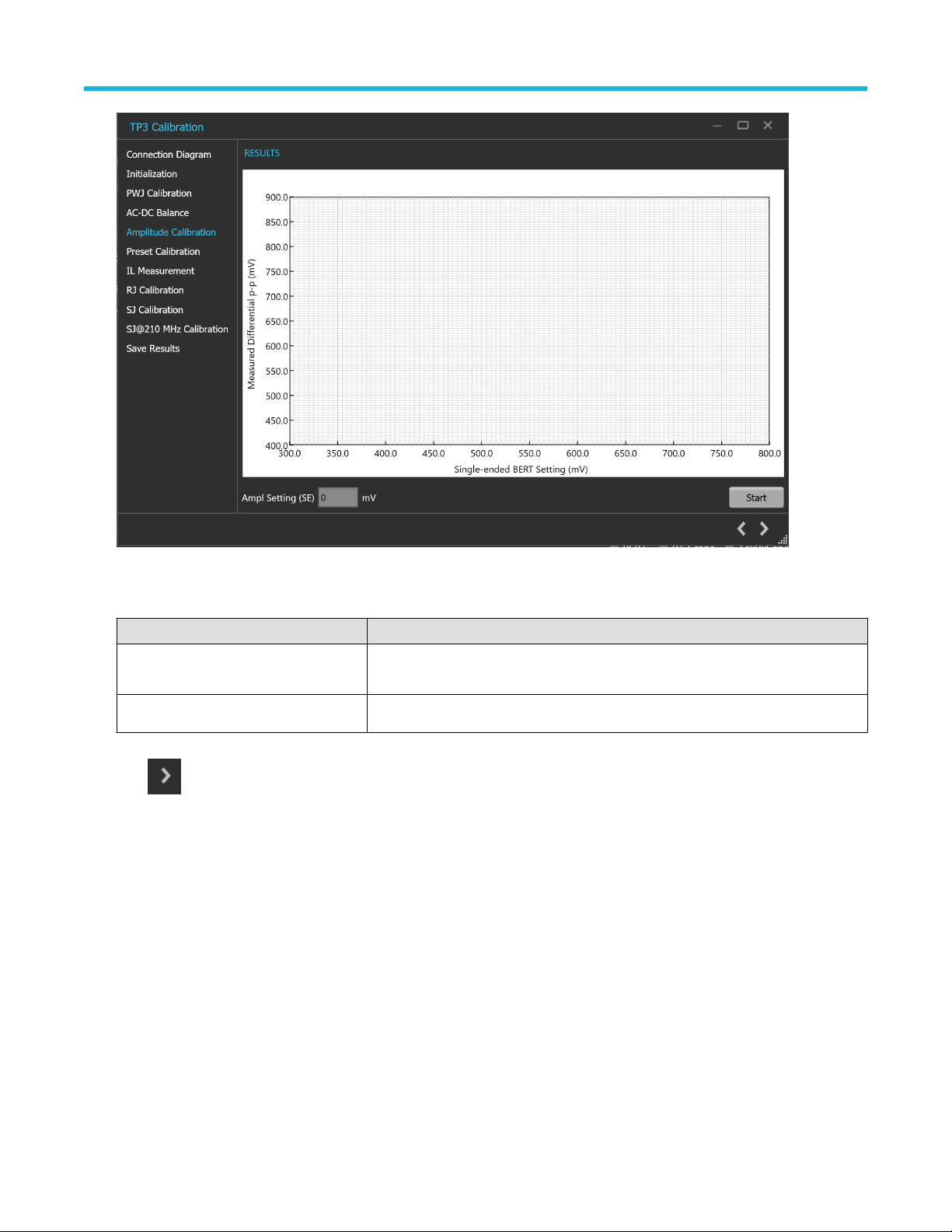

Table 17: TP3 Calibration: Amplitude Calibration........................................................................................................................42

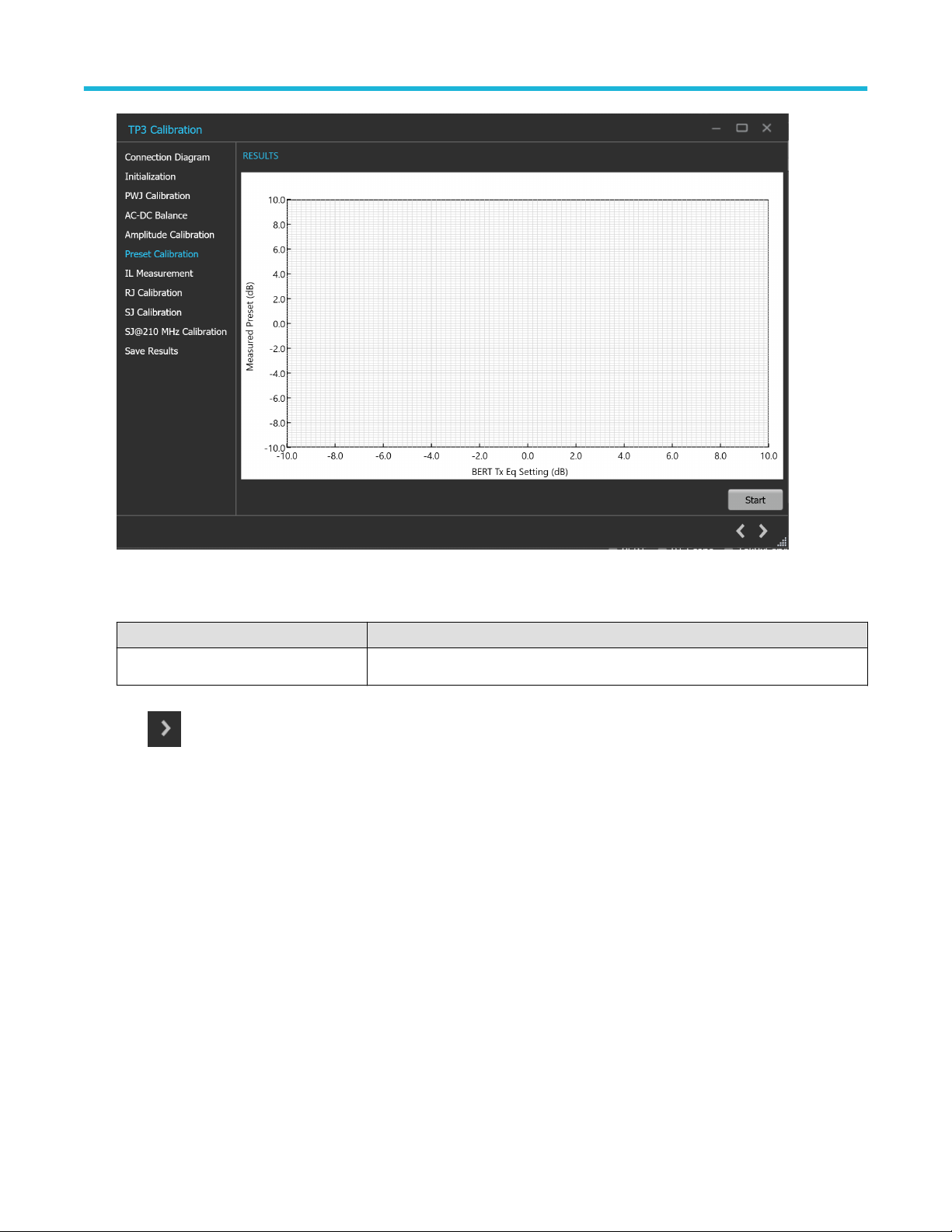

Table 18: TP3 Calibration: Preset Calibration............................................................................................................................. 43

Table 19: TP3 Calibration: IL Measurement................................................................................................................................44

Table 20: TP3 Calibration: RJ Calibration................................................................................................................................... 45

Table 21: TP3 Calibration: SJ Calibration................................................................................................................................... 46

Table 22: TP3 Calibration: SJ@210 MHz Calibration................................................................................................................. 47

Table 23: TP3 Calibration: Multi-tone SJ.....................................................................................................................................48

Table 24: TP3 Calibration: Save Results.....................................................................................................................................49

Table 25: TP2 Calibration: Description........................................................................................................................................51

Table 26: TP2 Calibration: Calibration Selection.........................................................................................................................53

Table 27: TP2 Calibration: IL for DMI/CMI.................................................................................................................................. 54

Table 28: TP2 Calibration: DMI Calibration................................................................................................................................. 55

Table 29: TP2 Calibration: CMI Calibration................................................................................................................................. 56

Table 30: TP2 Calibration: IL Measurement................................................................................................................................57

Table 31: TP2 Calibration: CTLE and Preset ............................................................................................................................. 58

Table 32: TP2 Calibration: Stressed Eye Cal.............................................................................................................................. 60

PCIe5.0 (CEM) Receiver Test Application Help 15

Page 16

List of Tables

Table 33: TP2 Calibration: Save Results.....................................................................................................................................61

Table 34: Rx LEQ Test: Calibration Selection............................................................................................................................. 62

Table 35: Rx LEQ Test: Link Training Configuration for Link Training.........................................................................................65

Table 36: Rx LEQ Test: Link Training Configuration for Forced Loopback..................................................................................66

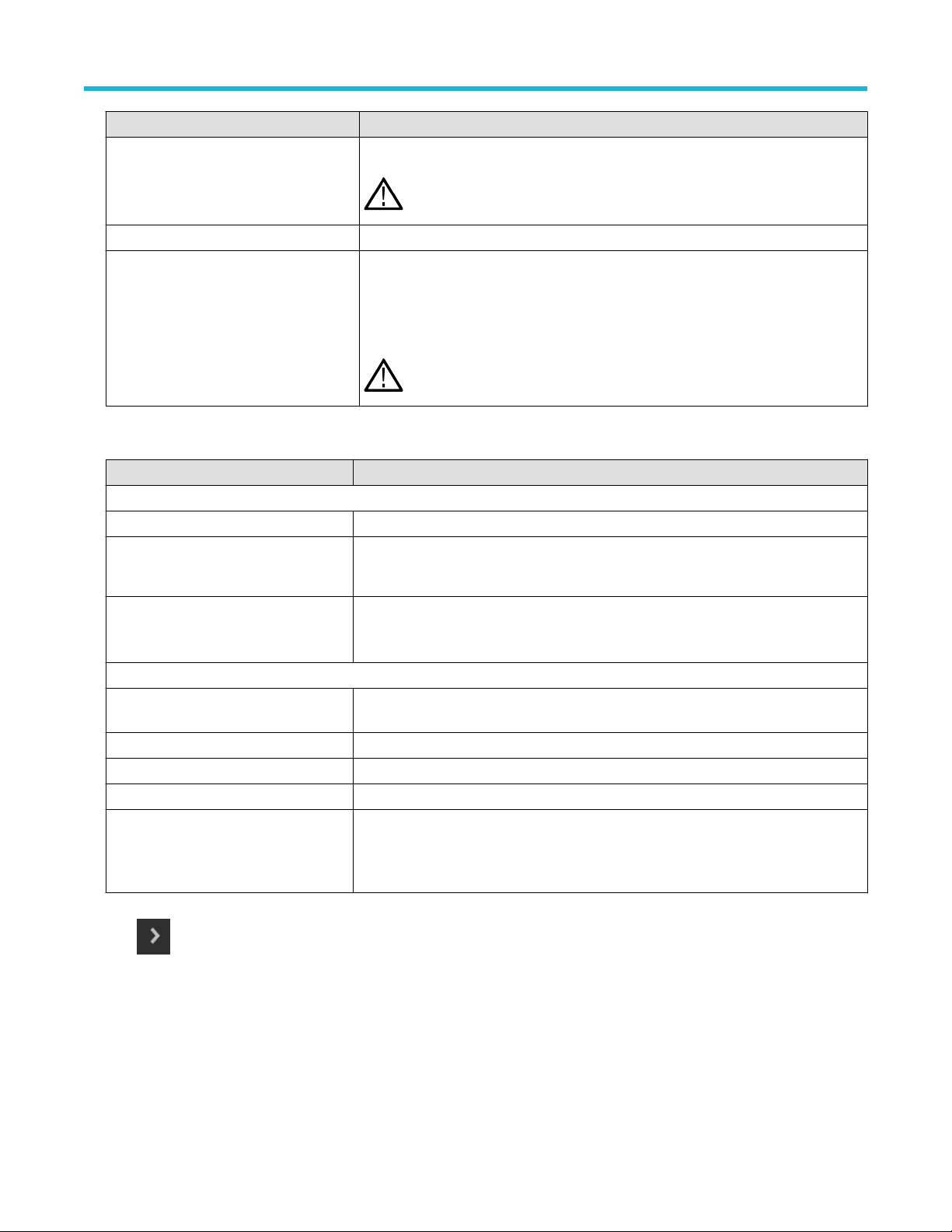

Table 37: Rx LEQ Test: Rx LEQ Test Configuration (Basic)........................................................................................................68

Table 38: Rx LEQ Test: Rx LEQ Test Configuration (SKP Ordered Set).....................................................................................68

Table 39: Rx LEQ Test: Run Test (Basic).................................................................................................................................... 70

Table 40: Rx LEQ Test: Run Test (Advanced Debug)................................................................................................................. 71

Table 41: Rx LEQ Test: Link Training..........................................................................................................................................73

Table 42: Rx LEQ Test: Save Results......................................................................................................................................... 74

Table 43: Tx LEQ Test: Calibration Selection..............................................................................................................................75

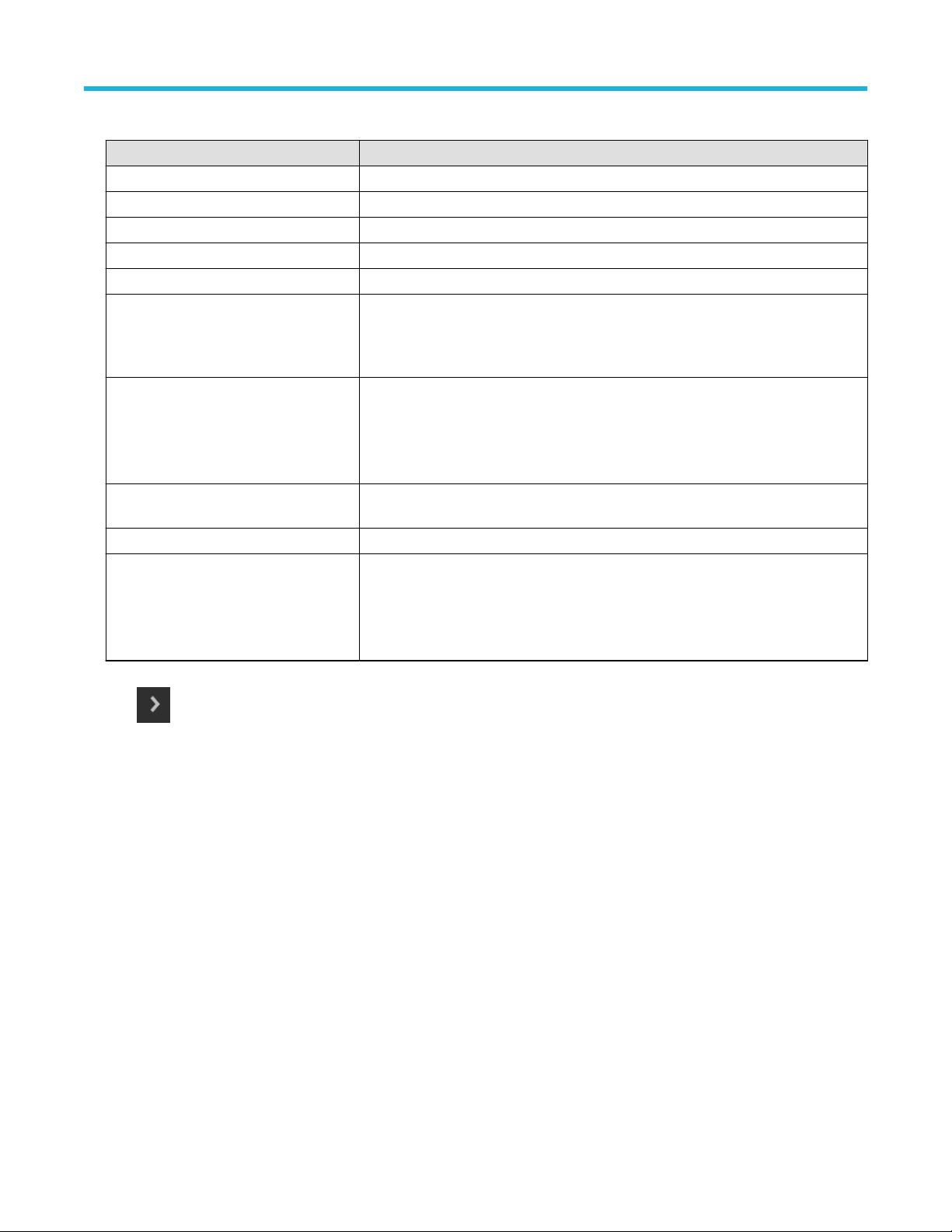

Table 44: Tx LEQ Test: Link Training Configuration....................................................................................................................78

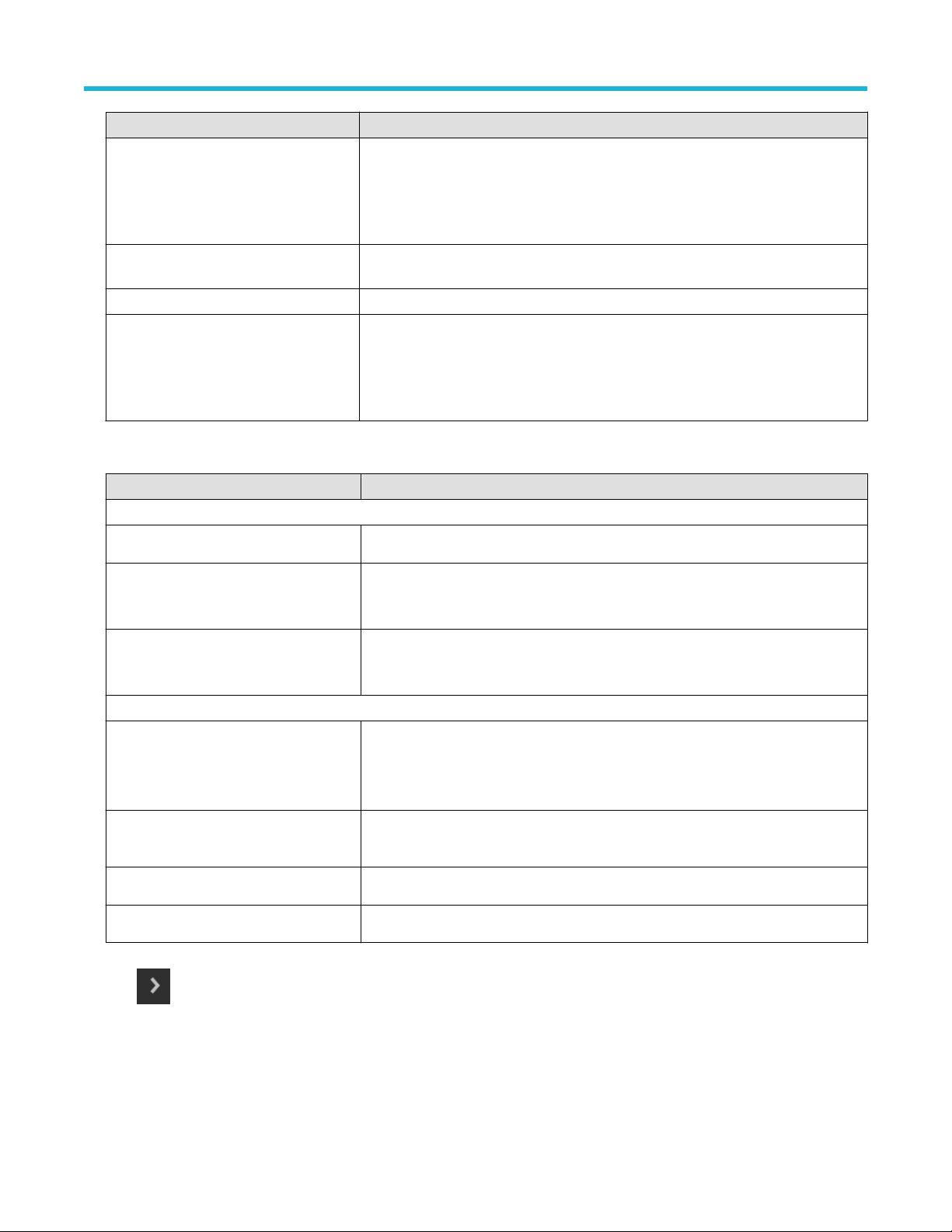

Table 45: Tx LEQ Test: Tx LEQ Test Configuration.....................................................................................................................79

Table 46: Tx LEQ Test: Run Test.................................................................................................................................................82

Table 47: Tx LEQ Test: Save Results..........................................................................................................................................83

Table 48: JTOL Test: Calibration Selection................................................................................................................................. 85

Table 49: JTOL Test: Link Training Configuration for Link Training ............................................................................................89

Table 50: JTOL Test: Link Training Configuration for Forced Loopback..................................................................................... 90

Table 51: JTOL Test: Configure Test (Basic)...............................................................................................................................92

Table 52: JTOL Test: Configure Test (SKP Order Set)................................................................................................................92

Table 53: JTOL Test: Configure JTOL Test................................................................................................................................. 93

Table 54: JTOL Test: Configure Advanced JTOL Test................................................................................................................ 94

Table 55: JTOL Test: JTOL Chart................................................................................................................................................96

Table 56: JTOL Test (Results Table)........................................................................................................................................... 97

Table 57: JTOL Test: Link Training..............................................................................................................................................98

Table 58: JTOL Test: Save Results............................................................................................................................................. 99

16

Page 17

Welcome

Welcome

Welcome to the PCIe5.0 (CEM) TekRxTest application. This application performs the test as per the Gen 5 PHY Test Specification Revision

5.0 Version 1.0 and Base Specification Revision 6.0.1 Version 1.0.

Figure 1: TekRxTest - PCIe5.0 CEM application

Receiver testing is accomplished by connecting the output of BERT PPG (which can produce specific PCIe test patterns) to the input of the

DUT through a specialized set of fixtures and cables. The BERT can be programmed to add different amounts of random jitter, sinusoidal

jitter, differential, Common mode interference along with variable signal amplitude, preshoot, and de-emphasis. Output of the DUT is