Page 1

www.keithley.com

KPXI Simultaneous A/D Module

Reference Manual

KPXI-SDAQ-901-01 Rev. A / January 2007

A GREATER MEASURE OF CONFIDENCE

ECA 42912

Page 2

WARRANTY

Keithley Instruments, Inc. warrants this product to be free from defects in material and workmanship for a period of

1 year from date of shipment.

Keithley Instruments, Inc. warrants the following items for 90 days from the date of shipment: probes, cables,

rechargeable batteries, diskettes, and documentation.

During the warranty period, we will, at our option, either repair or replace any product that proves to be defective.

To exercise this warranty, write or call your local Keithley Instruments representative, or contact

Keithley Instruments headquarters in Cleveland, Ohio. You will be given prompt assistance and return instructions.

Send the product, transportation prepaid, to the indicated service facility. Repairs will be made and the product

returned, transportation prepaid. Repaired or replaced products are warranted for the balance of the original

warranty period, or at least 90 days.

LIMITATION OF WARRANTY

This warranty does not apply to defects resulting from product modification without Keithley Instruments’ express

written consent, or misuse of any product or part. This warranty also does not apply to fuses, software,

non-rechargeable batteries, damage from battery leakage, or problems arising from normal wear or failure to follow

instructions.

THIS WARRANTY IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING ANY

IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR USE. THE REMEDIES

PROVIDED HEREIN ARE BUYER’S SOLE AND EXCLUSIVE REMEDIES.

NEITHER KEITHLEY INSTRUMENTS, INC. NOR ANY OF ITS EMPLOYEES SHALL BE LIABLE FOR ANY

DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OF

ITS INSTRUMENTS AND SOFTWARE EVEN IF KEITHLEY INSTRUMENTS, INC., HAS BEEN ADVISED IN

ADVANCE OF THE POSSIBILITY OF SUCH DAMAGES. SUCH EXCLUDED DAMAGES SHALL INCLUDE, BUT

ARE NOT LIMITED TO: COSTS OF REMOVAL AND INSTALLATION, LOSSES SUSTAINED AS THE RESULT

OF INJURY TO ANY PERSON, OR DAMAGE TO PROPERTY.

A G R E A T E R M E A S U R E O F C O N F I D E N C E

Keithley Instruments, Inc.

Corporate Headquarters • 28775 Aurora Road • Cleveland, Ohio 44139

440-248-0400 • Fax: 440-248-6168 • 1-888-KEITHLEY (534-8453) • www.keithley.com

12/06

Page 3

KPXI

Simultaneous A/D Module

Reference Manual

©2007, Keithley Instruments, Inc.

Document Number:

All rights reserved.

Cleveland, Ohio, U.S.A.

KPXI-SDAQ-901-01 Rev. A / January 2007

Page 4

Manual Print History KPXI Simultaneous A/D Module Reference Manual

Manual Print History

The print history shown below lists the printing dates of all Revisions and Addenda created for this

manual. The Revision Level letter increases alphabetically as the manual undergoes subsequent

updates. Addenda, which are released between Revisions, contain important change information that

the user should incorporate immediately into the manual. Addenda are numbered sequentially. When a

new Revision is created, all Addenda associated with the previous Revision of the manual are

incorporated into the new Revision of the manual. Each new Revision includes a revised copy of this

print history page.

Revision A (Document Number KPXI-SDAQ-901-01) ........................................ January 2007

All Keithley Instruments product names are trademarks or registered trademarks of Keithley Instruments, Inc.

Other brand names are trademarks or registered trademarks of their respective holders.

KPXI-SDAQ-901-01 Rev. A / January 2007

Page 5

The following safety precautions should be observed before using this product and any associated instrumentation. Although

some instruments and accessories would normally be used with non-hazardous voltages, there are situations where hazardous

conditions may be present.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions

required to avoid possible injury. Read and follow all installation, operation, and maintenance information carefully before using

the product. Refer to the manual for complete product specifications.

If the product is used in a manner not specified, the protection provided by the product may be impaired.

The types of product users are:

Responsible body is the individual or group responsible for the use and maintenance of equipment, for ensuring that the

equipment is operated within its specifications and operating limits, and for ensuring that operators are adequately trained.

Operators use the product for its intended function. They must be trained in electrical safety procedures and proper use of the

instrument. They must be protected from electric shock and contact with hazardous live circuits.

Maintenance personnel perform routine procedures on the product to keep it operating properly, for example, setting the line

voltage or replacing consumable materials. Maintenance procedures are described in the manual. The procedures explicitly state

if the operator may perform them. Otherwise, they should be performed only by service personnel.

Safety Precautions

Service personnel are trained to work on live circuits, and perform safe installations and repairs of products. Only properly

trained service personnel may perform installation and service procedures.

Keithley Instruments products are designed for use with electrical signals that are rated Measurement Category I and

Measurement Category II, as described in the International Electrotechnical Commission (IEC) Standard IEC 60664. Most

measurement, control, and data I/O signals are Measurement Category I and must not be directly connected to mains voltage or

to voltage sources with high transient over-voltages. Measurement Category II connections require protection for high transient

over-voltages often associated with local AC mains connections. Assume all measurement, control, and data I/O connections are

for connection to Category I sources unless otherwise marked or described in the Manual.

Exercise extreme caution when a shock hazard is present. Lethal voltage may be present on cable connector jacks or test

fixtures. The American National Standards Institute (ANSI) states that a shock hazard exists when voltage levels greater than

30V RMS, 42.4V peak, or 60VDC are present. A good safety practice is to expect that hazardous voltage is present in any

unknown circuit before measuring.

Operators of this product must be protected from electric shock at all times. The responsible body must ensure that operators

are prevented access and/or insulated from every connection point. In some cases, connections must be exposed to potential

human contact. Product operators in these circumstances must be trained to protect themselves from the risk of electric shock.

If the circuit is capable of operating at or above 1000 volts, no conductive part of the circuit may be exposed.

Do not connect switching cards directly to unlimited power circuits. They are intended to be used with impedance limited sources.

NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to

limit fault current and voltage to the card.

Before operating an instrument, make sure the line cord is connected to a properly grounded power receptacle. Inspect the

connecting cables, test leads, and jumpers for possible wear, cracks, or breaks before each use.

12/06

Page 6

When installing equipment where access to the main power cord is restricted, such as rack mounting, a separate main input

power disconnect device must be provided, in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any other instruments while power is applied to the circuit under

test. ALWAYS remove power from the entire test system and discharge any capacitors before: connecting or disconnecting

cables or jumpers, installing or removing switching cards, or making internal changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground.

Always make measurements with dry hands while standing on a dry, insulated surface capable of withstanding the voltage being

measured.

The instrument and accessories must be used in accordance with its specifications and operating instructions or the safety of the

equipment may be impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating

information, and as shown on the instrument or test fixture panels, or switching card.

When fuses are used in a product, replace with same type and rating for continued protection against fire hazard.

Chassis connections must only be used as shield connections for measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use

of a lid interlock.

If a screw is present, connect it to safety earth ground using the wire recommended in the user documentation.

!

The symbol on an instrument indicates that the user should refer to the operating instructions located in the manual.

The symbol on an instrument shows that it can source or measure 1000 volts or more, including the combined effect of

normal and common mode voltages. Use standard safety precautions to avoid personal contact with these voltages.

The symbol on an instrument shows that the surface may be hot. Avoid personal contact to prevent burns.

The symbol indicates a connection terminal to the equipment frame.

The WARNING heading in a manual explains dangers that might result in personal injury or death. Always read the associated

information very carefully before performing the indicated procedure.

The CAUTION heading in a manual explains hazards that could damage the instrument. Such damage may invalidate the

warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and all test cables.

To maintain protection from electric shock and fire, replacement components in mains circuits, including the power transformer,

test leads, and input jacks, must be purchased from Keithley Instruments. Standard fuses, with applicable national safety

approvals, may be used if the rating and type are the same. Other components that are not safety related may be purchased

from other suppliers as long as they are equivalent to the original component. (Note that selected parts should be purchased only

through Keithley Instruments to maintain accuracy and functionality of the product.) If you are unsure about the applicability of a

replacement component, call a Keithley Instruments office for information.

To clean an instrument, use a damp cloth or mild, water based cleaner. Clean the exterior of the instrument only. Do not apply

cleaner directly to the instrument or allow liquids to enter or spill on the instrument. Products that consist of a circuit board with

no case or chassis (e.g., data acquisition board for installation into a computer) should never require cleaning if handled

according to instructions. If the board becomes contaminated and operation is affected, the board should be returned to the

factory for proper cleaning/servicing.

Page 7

Table of Contents

Section Topic Page

1 Introduction............................................................................................. 1-1

Introduction ................................................................................................. 1-2

Features ............................................................................................... 1-2

Applications.......................................................................................... 1-2

Safety symbols and terms .......................................................................... 1-2

Specifications.............................................................................................. 1-3

Unpacking and inspection........................................................................... 1-3

Inspection for damage.......................................................................... 1-3

Shipment contents ............................................................................... 1-3

Instruction manual................................................................................ 1-3

Repacking for shipment........................................................................ 1-4

Software...................................................................................................... 1-4

Programming library KDAQ-DRVR ...................................................... 1-4

KDAQ-LVIEW LabVIEW® driver .......................................................... 1-4

2 Installation............................................................................................... 2-1

Introduction ................................................................................................. 2-2

Handling precautions .................................................................................. 2-2

Configuration .............................................................................................. 2-2

Plug and Play ....................................................................................... 2-2

Configuration........................................................................................ 2-2

Troubleshooting.................................................................................... 2-2

Installation................................................................................................... 2-3

3 Operation and Connection .................................................................. 3-1

Introduction ................................................................................................. 3-2

Signal connections...................................................................................... 3-2

Connectors pin assignment.................................................................. 3-2

Analog Input Signal Connection........................................................... 3-4

Operation Theory ....................................................................................... 3-6

A/D Conversion .................................................................................... 3-6

D/A Conversion .................................................................................. 3-16

Digital I/O ........................................................................................... 3-22

General Purpose Timer/Counter Operation ....................................... 3-23

Trigger Sources .................................................................................. 3-26

User-controllable Timing Signals........................................................ 3-30

Calibration................................................................................................. 3-34

Loading Calibration Constants ........................................................... 3-34

Auto-calibration .................................................................................. 3-34

Saving Calibration Constants............................................................. 3-35

Appendix Topic Page

A KDAQ-DRVR User’s Guide .................................................................. A-1

Introduction to KDAQ-DRVR ...................................................................... A-2

About the KDAQ-DRVR software......................................................... A-2

KDAQ-DRVR hardware support........................................................... A-2

KDAQ-DRVR language support........................................................... A-2

Fundamentals of building applications with KDAQ-DRVR.......................... A-3

Page 8

Table of Contents KPXI Simultaneous A/D Module Reference Manual

Appendix Topic Page

A KDAQ-DRVR User’s Guide (continued)

Microsoft® Visual Basic (Version 6.0) .................................................. A-3

Using Microsoft Visual Basic.NET ....................................................... A-4

Microsoft Visual C/C++........................................................................ A-4

KDAQ-DRVR utilities for Win32 ................................................................. A-5

KDAQ-DRVR configuration utility (configdrv) ...................................... A-5

KDAQ-DRVR data file converter utility (KiDAQCvt)............................. A-6

KDAQ-DRVR overview .............................................................................. A-6

General configuration function group .................................................. A-7

Analog input function group................................................................. A-7

Analog output function group............................................................. A-10

Digital input function group ................................................................ A-12

Digital output function group .............................................................. A-13

General timer/counter function group ................................................ A-13

DIO function group ............................................................................ A-13

SSI function group ............................................................................. A-14

Calibration function group.................................................................. A-14

KDAQ-DRVR application hints................................................................. A-15

Analog input programming hints ........................................................ A-16

Analog output programming hints ............................................................ A-36

One-shot analog output programming scheme ................................. A-36

Digital input programming hints ......................................................... A-50

Digital output programming hints....................................................... A-51

DAQ event message programming hints........................................... A-52

Continuous data transfer in KDAQ-DRVR ............................................... A-53

Continuous data transfer mechanism................................................ A-53

Double-buffered AI/AO operation ...................................................... A-53

Single-buffered versus double-buffered data transfer ....................... A-54

Pre-trigger mode/middle-trigger data acquisition (AI)........................ A-54

B KDAQ-DRVR Function Reference ..................................................... B-1

Function description................................................................................... B-2

Data types............................................................................................ B-2

Function reference............................................................................... B-2

Status Codes............................................................................................ B-94

AI range codes......................................................................................... B-95

AI data format........................................................................................... B-97

DATA file format ....................................................................................... B-97

Header............................................................................................... B-98

ChannelRange................................................................................... B-99

Data Block ......................................................................................... B-99

C KIDAQ®-LabVIEW Compatible Interface Guide............................. C-1

Introduction to KIDAQ®-LabVIEW ............................................................. C-2

Overview.............................................................................................. C-2

Using KIDAQ LabVIEW VIs in LabVIEW............................................. C-2

KIDAQ LabVIEW Programming........................................................... C-3

Device Driver Handling .............................................................................. C-4

Windows XP/2000 Device Driver......................................................... C-4

Driver Utility ......................................................................................... C-4

KIDAQ Utilities ........................................................................................... C-4

KIDAQ Registry/Configuration utility.................................................... C-4

KIDAQ Device Browser ....................................................................... C-4

KIDAQ LabVIEW VIs Overview.................................................................. C-5

Analog Input VIs .................................................................................. C-6

Analog Output VIs ............................................................................... C-6

Digital I/O VIs....................................................................................... C-7

Timer/Counter VIs................................................................................ C-7

Calibration and Configuration VIs........................................................ C-8

Error Handler VI................................................................................... C-8

ii KPXI-SDAQ-901-01 Rev. A / January 2007

Page 9

KPXI Simultaneous A/D Module Reference Manual Table of Contents

Appendix Topic Page

C KIDAQ®-LabVIEW Compatible Interface Guide (continued)

Distribution of Applications......................................................................... C-8

Windows XP/2000 ............................................................................... C-8

D KIDAQ®-LabVIEW Compatible Function Reference..................... D-1

Introduction ................................................................................................ D-2

Hardware support....................................................................................... D-2

KPXI-DIO series: ................................................................................. D-2

KPXI-DAQ series: ................................................................................ D-2

Digitizer series: .................................................................................... D-2

Analog input VIs......................................................................................... D-3

Easy analog input VIs.......................................................................... D-3

Intermediate analog input VIs.............................................................. D-7

Analog output VIs..................................................................................... D-21

Easy analog output VIs...................................................................... D-21

Intermediate analog output VIs.......................................................... D-24

Advanced analog output VIs.............................................................. D-32

Digital I/O VIs ........................................................................................... D-33

Easy Digital I/O VIs............................................................................ D-33

Intermediate Digital I/O VIs................................................................ D-37

Advanced Digital I/O VIs.................................................................... D-45

Counter VIs .............................................................................................. D-46

Easy Counter VIs .............................................................................. D-46

Intermediate Counter VIs .................................................................. D-50

Advanced Counter VIs ...................................................................... D-63

Calibration and Configuration VIs ............................................................ D-67

Calibration VIs .................................................................................. D-67

Other Calibration and Configuration VIs............................................ D-68

Service VIs ............................................................................................... D-70

Error Codes ............................................................................................. D-71

AI Range Codes ...................................................................................... D-73

AI Data Format ....................................................................................... D-76

Service Form

KPXI-SDAQ-901-01 Rev. A / January 2007 iii

Page 10

Table of Contents KPXI Simultaneous A/D Module Reference Manual

This page left blank intentionally.

iv KPXI-SDAQ-901-01 Rev. A / January 2007

Page 11

List of Figures

Section Figure Title Page

2 Figure 2-1 Typical PXI module installation...................................................... 2-4

Figure 2-2 Device manager (successful installation) ...................................... 2-5

3 Figure 3-1 68-pin VHDCI-type pin assignment ............................................... 3-2

Figure 3-2 Single-ended measurements connections..................................... 3-5

Figure 3-3 Ground-referenced source and differential input ........................... 3-5

Figure 3-4 Floating source and differential input............................................. 3-6

Figure 3-5 Synchronous Digital Inputs Block Diagram.................................... 3-7

Figure 3-6 Synchronous Digital Inputs timing ................................................ 3-7

Figure 3-7 Scan timing .................................................................................. 3-10

Figure 3-8 Pre-trigger (trigger occurs after at least M scans acquired)......... 3-11

Figure 3-9 Pre-trigger scan acquisition ......................................................... 3-12

Figure 3-10 Pre-trigger with M_enable = 0 (Trigger occurs before M scans). 3-12

Figure 3-11 Pre-trigger with M_enable = 1 ..................................................... 3-13

Figure 3-12 Middle trigger with M_enable = 1................................................. 3-13

Figure 3-13 Middle trigger (trigger occurs when a scan is in progress) .......... 3-14

Figure 3-14 Post trigger .................................................................................. 3-14

Figure 3-15 Delay trigger ................................................................................ 3-15

Figure 3-16 Post trigger with re-trigger ........................................................... 3-15

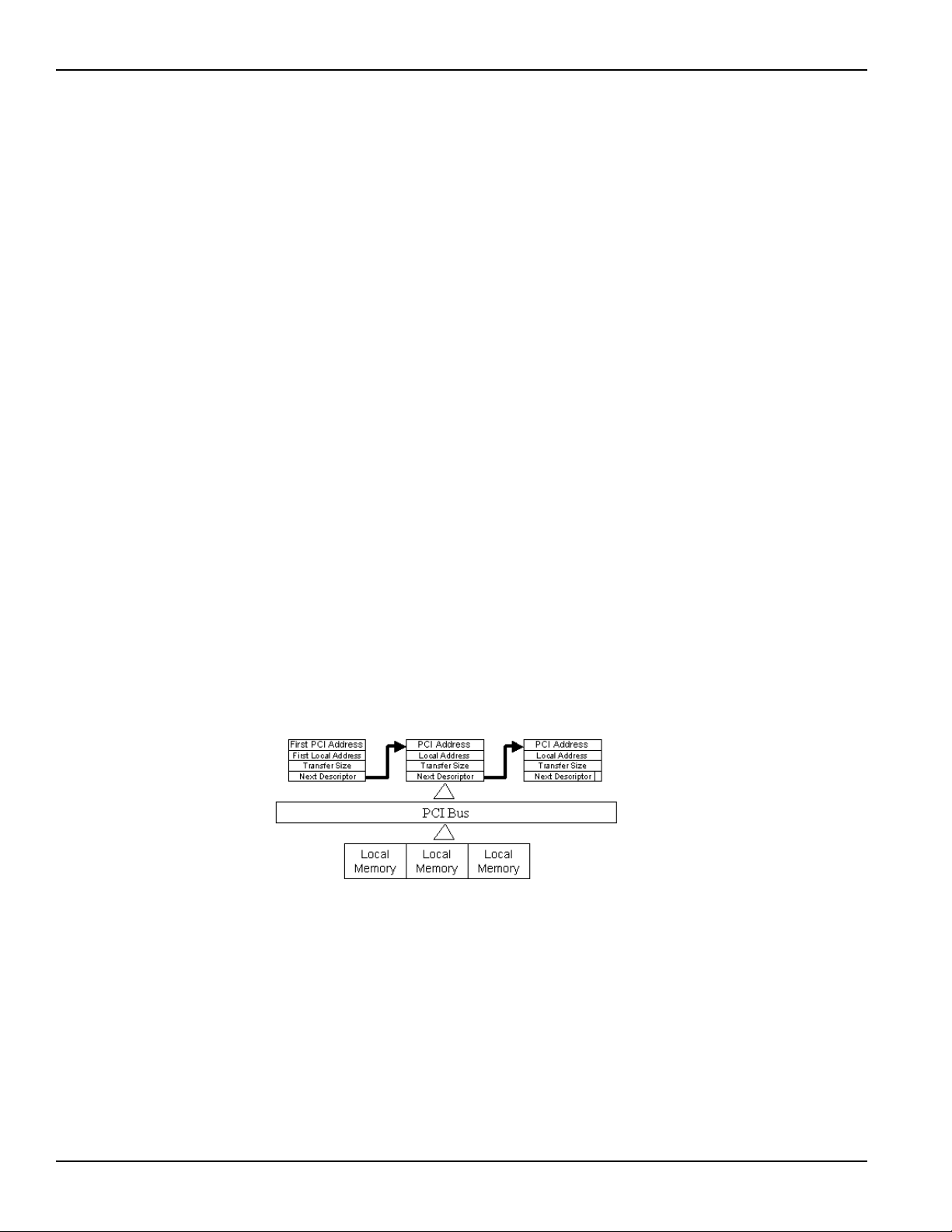

Figure 3-17 Scatter/gather DMA for data transfer........................................... 3-16

Figure 3-18 Typical D/A timing of waveform generation ................................. 3-18

Figure 3-19 Post trigger waveform generation................................................ 3-19

Figure 3-20 Delay trigger waveform generation.............................................. 3-19

Figure 3-21 Re-triggered waveform generation .............................................. 3-20

Figure 3-22 Finite iterative waveform generation............................................ 3-20

Figure 3-23 Infinite iterative waveform generation.......................................... 3-21

Figure 3-24 Stop mode I.................................................................................. 3-22

Figure 3-25 Stop mode II................................................................................. 3-22

Figure 3-26 Stop mode III................................................................................ 3-22

Figure 3-27 Mode 1 Operation ....................................................................... 3-24

Figure 3-28 Mode 2 Operation ....................................................................... 3-24

Figure 3-29 Mode 3 Operation ........................................................................ 3-24

Figure 3-30 Mode 5 operation......................................................................... 3-25

Figure 3-31 Mode 6 operation......................................................................... 3-25

Figure 3-32 Mode 7 operation......................................................................... 3-26

Figure 3-33 Mode 8 operation......................................................................... 3-26

Figure 3-34 Analog trigger block diagram....................................................... 3-27

Figure 3-35 Below-Low analog trigger condition............................................. 3-27

Figure 3-36 Above-High analog trigger condition............................................ 3-28

Figure 3-37 Inside-Region analog trigger condition ........................................ 3-28

Figure 3-38 High-Hysteresis analog trigger condition..................................... 3-29

Figure 3-39 Low-Hysteresis analog trigger condition...................................... 3-29

Figure 3-40 External digital trigger.................................................................. 3-29

Figure 3-41 DAQ signals routing..................................................................... 3-30

Page 12

List of Figures KPXI Simultaneous A/D Module Reference Manual

Appendix Figure Title Page

A Figure A-1 Open Project dialog box................................................................ A-3

Figure A-2 Driver Configuration window ......................................................... A-5

Figure A-3 KDAQ-DRVR application building blocks.................................... A-15

Figure A-4 Typical function flow for all types of KDAQ-DRVR series............ A-16

Figure A-5 Fills channel gain queue first....................................................... A-17

Figure A-6 Synchronous operation ............................................................... A-18

Figure A-7 Non-double buffered asynchronous operation............................ A-19

Figure A-8 Double buffered asynchronous operation ................................... A-20

Figure A-9 All types of KPXI-DRVR series ................................................... A-22

Figure A-10 Fills channel gain queue first....................................................... A-23

Figure A-11 All types of KDAQ-DRVR series ................................................. A-25

Figure A-12 Fills channel gain queue first....................................................... A-26

Figure A-13 All types of KDAQ-DRVR series ................................................. A-27

Figure A-14 Fills channel gain queue first....................................................... A-29

Figure A-15 All types of KDAQ-DRVR series ................................................. A-31

Figure A-16 Fills channel gain queue first....................................................... A-32

Figure A-17 All types of KDAQ-DRVR series ................................................. A-33

Figure A-18 Fills channel gain queue first....................................................... A-35

Figure A-19 One-shot analog output programming ........................................ A-37

Figure A-20 One-shot analog output programming ........................................ A-38

Figure A-21 Non-double-buffered asynchronous continuous

analog output programming ........................................................ A-39

Figure A-22 Non-double-buffered asynchronous continuous

analog output programming ........................................................ A-40

Figure A-23 Double-buffered asynchronous continuous analog

output programming .................................................................... A-41

Figure A-24 Double-buffered asynchronous continuous analog

output programming .................................................................... A-43

Figure A-25 Typical flow of asynchronous analog output operation ............... A-44

Figure A-26 Typical flow of asynchronous analog output operation ............... A-45

Figure A-27 Typical flow of double-buffered asynchronous

analog output operation .............................................................. A-47

Figure A-28 Typical flow of double-buffered asynchronous

analog output operation .............................................................. A-49

Figure A-29 One-shot digital input programming ............................................ A-50

Figure A-30 Typical flow of non-buffered single-point digital

output operation .......................................................................... A-51

Figure A-31 Double buffer mode principle ...................................................... A-53

B Figure B-1 Scan timing example................................................................... B-13

Figure B-2 Scan timing example................................................................... B-15

Figure B-3 Scan timing example................................................................... B-17

Figure B-4 Scan timing example................................................................... B-20

Figure B-5 Scan timing example................................................................... B-22

Figure B-6 Scan timing example................................................................... B-25

Figure B-7 Scan timing example................................................................... B-27

Figure B-8 Scan timing example................................................................... B-30

Figure B-9 DATA file format .......................................................................... B-98

Figure B-10 DAQ File Conversion Utility....................................................... B-100

C Figure C-1 Function Browser Options............................................................. C-2

Figure C-2 Functions palette........................................................................... C-3

Figure C-3 Keithley PXI Devices Explorer ...................................................... C-5

vi KPXI-SDAQ-901-01 Rev. A / January 2007

Page 13

KPXI Simultaneous A/D Module Reference Manual List of Figures

Appendix Figure Title Page

D Figure D-1 Analog input palette ...................................................................... D-3

Figure D-2 Analog output palette .................................................................. D-21

Figure D-3 Digital I/O palette......................................................................... D-33

KPXI-SDAQ-901-01 Rev. A / January 2007 vii

Page 14

List of Figures KPXI Simultaneous A/D Module Reference Manual

This page left blank intentionally.

viii KPXI-SDAQ-901-01 Rev. A / January 2007

Page 15

List of Tables

Section Table Title Page

3 Table 3-1 68-pin VHDCI-type pin descriptions............................................... 3-3

Table 3-2 Legend of SSI signals.................................................................... 3-4

Table 3-4 Unipolar analog input range and output digital code ..................... 3-8

Table 3-5 Bipolar analog input range and output digital code........................ 3-8

Table 3-3 Bipolar analog input range and output digital code........................ 3-8

Table 3-6 Unipolar analog input range and output digital code ..................... 3-9

Table 3-7 Bipolar output code table............................................................. 3-17

Table 3-8 Unipolar output code table........................................................... 3-17

Table 3-9 Analog trigger SRC1 (EXTATRIG) ideal transfer characteristic... 3-27

Table 3-10 Summary of user-controllable timing signals ............................... 3-30

Table 3-11 Auxiliary function input signals..................................................... 3-31

Table 3-12 Summary of SSI timing signals.................................................... 3-33

Appendix Table Title Page

A Table A-2 Initial default AI configuration....................................................... A-18

Table A-1 Initial default channel configuration ............................................. A-18

Table A-3 Initial default channel configuration ............................................. A-38

Table A-4 Initial default DA configuration ..................................................... A-38

B Table B-1 Suggested data types.................................................................... B-2

Table B-2 Example trigger condition selection (KDAQ_AIO_Config)........... B-46

Table B-3 Status codes returned by KDAQ-DRVR ...................................... B-94

Table B-4 Analog input range of digitizers ................................................... B-96

Table B-5 Valid values for each model ......................................................... B-96

Table B-6 AI data format .............................................................................. B-97

Table B-7 Data file header ........................................................................... B-98

Table B-8 Data structure of ChannelRange unit (length: 2 bytes)................ B-99

D Table D-1 KI AI acquire waveform.................................................................. D-3

Table D-2 KI AI acquire waveforms ................................................................ D-4

Table D-3 KI AI sample channel..................................................................... D-6

Table D-4 KI AI sample channels ................................................................... D-6

Table D-5 KI AI clear ...................................................................................... D-7

Table D-6 KI AI config .................................................................................... D-9

Table D-7 2-byte binary array....................................................................... D-12

Table D-8 Scaled and Binary Arrays ............................................................ D-14

Table D-9 Scaled Array ................................................................................ D-16

Table D-10 KI AI single scan .......................................................................... D-17

Table D-11 KI AI start ..................................................................................... D-19

Table D-12 KI AO generate waveform ........................................................... D-22

Table D-13 KI AO generate waveforms.......................................................... D-22

Table D-14 KI AO update channel.................................................................. D-23

Table D-15 KI AO update channels................................................................ D-24

Table D-16 KI AO clear .................................................................................. D-25

Page 16

List of Tables KPXI Simultaneous A/D Module Reference Manual

Appendix Table Title Page

D Table D-17 KI AO Config ............................................................................... D-25

Table D-18 KI AO start................................................................................... D-27

Table D-19 KI AO wait ................................................................................... D-28

Table D-20 KI AO write binary array.............................................................. D-29

Table D-21 KI AO write binary array scaled array ......................................... D-30

Table D-22 KI AO Trigger and Gate Config ................................................... D-32

Table D-23 KI Read from Digital Line ............................................................ D-34

Table D-24 KI Read from Digital Port ............................................................ D-34

Table D-25 KI Write to Digital Line................................................................. D-35

Table D-26 KI Write to Digital Port................................................................. D-36

Table D-27 KI DIO Clear................................................................................ D-37

Table D-28 KI DIO Config .............................................................................. D-38

Table D-29 KI DIO Read................................................................................ D-40

Table D-30 KI DIO Start ................................................................................. D-42

Table D-31 KI DIO Write ................................................................................ D-43

Table D-32 KI DIO Port Config ...................................................................... D-45

Table D-33 KI Count Events or Time ............................................................. D-46

Table D-34 KI Generate Delayed Pulse......................................................... D-47

Table D-35 KI Generate Pulse-Train.............................................................. D-48

Table D-36 KI Measure Pulse-Width or Period.............................................. D-49

Table D-37 KI Continuous Pulse Generator Config....................................... D-50

Table D-38 KI Counter Divider Config ........................................................... D-52

Table D-39 KI Counter Read ......................................................................... D-53

Table D-40 KI Counter Start........................................................................... D-54

Table D-41 KI Counter Stop........................................................................... D-55

Table D-42 KI Delayed Pulse Generator Config............................................ D-56

Table D-43 KI Down Counter or Divider Config ............................................. D-58

Table D-44 KI Event or Time Counter Config ................................................ D-59

Table D-45 KI Pulse-Width or Period Measurement Config .......................... D-61

Table D-46 KI UpDown Counter Config......................................................... D-62

Table D-47 KI ICTR Control........................................................................... D-63

Table D-48 KI KPXI-DAQ series devices and Digitizer Series Calibrate ...... D-67

Table D-49 KI Route Signal .......................................................................... D-68

Table D-50 KI SSI Control ............................................................................ D-69

Table D-51 KI Error Handler ......................................................................... D-70

Table D-52 Error Codes: KIDAQ LabVIEW VIs ............................................. D-71

Table D-53 Analog Input Range .................................................................... D-73

Table D-54 Valid analog input ranges (specified by module)......................... D-75

Table D-55 Analog Input data format (by Model)........................................... D-76

x KPXI-SDAQ-901-01 Rev. A / January 2007

Page 17

In this section:

Top ic Pa ge

Introduction......................................................................................... 1-2

Safety symbols and terms .............................................................. 1-2

Specifications..................................................................................... 1-3

Unpacking and inspection .............................................................. 1-3

Section 1

Introduction

Features ........................................................................................... 1-2

Applications ...................................................................................... 1-2

Inspection for damage ...................................................................... 1-3

Shipment contents............................................................................ 1-3

Instruction manual ............................................................................ 1-3

Repacking for shipment.................................................................... 1-4

Software ............................................................................................... 1-4

Programming library KDAQ-DRVR................................................... 1-4

KDAQ-LVIEW LabVIEW® driver....................................................... 1-4

Page 18

Section 1: Introduction KPXI Simultaneous A/D Module Reference Manual

Introduction

Model KPXI-SDAQ-4-500K/2M are advanced 4-channel, simultaneous, high performance

multi-function data acquisition cards based on 32-bit PCI architecture. High performance designs

and the state-of-the-art technology make this card ideal for data logging and signal analysis

applications in medical, process control, etc.

This manual is designed to help you use/understand the Model KPXI-SDAQ-4-500K/2M. The

manual describes the versatile functions and the operation theory of the Model

KPXI-SDAQ-4-500K/2M.

Features

The Model KPXI-SDAQ-4-500K/2M Simultaneous A/D PXI Modules provide the following

advanced features:

• 32-bit PCI-Bus, plug and play

• 4-channel simultaneous differential analog inputs

• Model KPXI-SDAQ-4-2M: 14-bit Analog input resolution with sampling rate up to 2MS/s

• Model KPXI-SDAQ-4-500K: 16-bit Analog input resolution with sampling rate up to 500KS/s

• Programmable bipolar/unipolar analog input

• Programmable gain (x1, x2, x4, x8)

• KPXI-SDAQ-4-2M: Total 8K samples A/D FIFO

• Model KPXI-SDAQ-4-500K: Total 512 samples A/D FIFO

• Versatile trigger sources: software trigger, external digital trigger, analog trigger and trigger

from System Synchronization Interface (SSI).

• A/D Data transfer: software polling & bus-mastering DMA with Scatter/Gather functionality

• Four A/D trigger modes: post-trigger, delay-trigger, pre-trigger and middle-trigger

• 2 channel DA outputs with waveform generation capability

• 2K samples output data FIFO for DA channels

• DA Data transfer: software update and bus-mastering DMA with Scatter/Gather functionality

• System Synchronization Interface (SSI)

• A/D/DA fully auto-calibration

• Completely jumper-less and software configurable

Applications

• Automotive Testing

• Transient signal measurement

•ATE

Safety symbols and terms

The following symbols and terms may be found on the Model KPXI-SDAQ-4-500K /

KPXI-SDAQ-4-2M or used in this manual.

The symbol indicates that the user should refer to the operating instructions located in the

!

manual.

The symbol shows that high voltage may be present on the terminal(s). Use standard safety

precautions to avoid personal contact with these voltages.

The symbol on an instrument shows that the surface may be hot. Avoid personal contact to

prevent burns.

1-2 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Page 19

KPXI Simultaneous A/D Module Reference Manual Section 1: Introduction

The WARNING heading used in this manual explains dangers that might result in personal injury

or death. Always read the associated information very carefully before performing the indicated

procedure.

The CAUTION heading used in this manual explains hazards that could damage the unit. Such

damage may invalidate the warranty.

Specifications

Refer to the product data sheet for updated KIDAQ® KPXI Simultaneous A/D PXI Module’s

specifications. Check the Keithley Instruments website at www.keithley.com for the latest updates

to the specifications.

Unpacking and inspection

Inspection for damage

CAUTION Your KIDAQ Model KPXI-SDAQ-4-500K / KPXI-SDAQ-4-2M module contains

electro-static sensitive components that can be easily be damaged by static

electricity.

Therefore, handle the card on a grounded anti-static mat. The operator should

be wearing an anti-static wristband, grounded at the same point as the

anti-static mat.

The Model KPXI-SDAQ-4-500K / KPXI-SDAQ-4-2M was carefully inspected electrically and

mechanically before shipment.

Inspect the card module carton for obvious damages. Shipping and handling may damage the

module. Make sure there are no shipping and handling damages on the module’s carton before

continuing.

After opening the card module carton, extract the system module and place it only on a grounded

anti-static surface with component side up. Save the original packing carton for possible future

shipment.

Again, inspect the module for damages. Report any damage to the shipping agent immediately.

Shipment contents

The following items are included with every Model KPXI-SDAQ-4-500K / KPXI-SDAQ-4-2M order:

• Model KPXI-SDAQ-4-500K / KPXI-SDAQ-4-2M Module

• CD containing required software and manuals

Instruction manual

A CD-ROM containing this User’s Manual and required software is included with each Model

KPXI-SDAQ-4-500K / KPXI-SDAQ-4-2M order. If a hardcopy of the Model KPXI-SDAQ-4-500K /

KPXI-SDAQ-4-2M Reference Manual is required, you can order the Manual Package (Keithley

Instruments Part Number Model KPXI-SDAQ-901-01). The Manual Package includes an

instruction manual and any pertinent addenda.

Always check the Keithley Instruments’ website at www.keithley.com for the latest revision of the

manual. The latest manual can be downloaded (in PDF format) from the website.

KPXI-SDAQ-901-01 Rev. A / January 2007 Return to Section Topics 1-3

Page 20

Section 1: Introduction KPXI Simultaneous A/D Module Reference Manual

Repacking for shipment

Should it become necessary to return the Model KPXI-SDAQ-4-500K / KPXI-SDAQ-4-2M for

repair, carefully pack the unit in its original packing carton or the equivalent, and follow these

instructions:

• Call Keithley Instruments’ repair department at 1-888-KEITHLEY (1-888-534-8453) for a

Return Material Authorization (RMA) number.

• Let the repair department know the warranty status of the Model KPXI-SDAQ-4-500K /

KPXI-SDAQ-4-2M requiring repair.

• Write ATTENTION REPAIR DEPARTMENT and the RMA number on the shipping label.

• Complete and include the Service Form located at the back of this manual.

Software

This section contains information on provided software. Keithley Instruments’ provides versatile

software drivers and packages for different systems. Keithley Instruments not only provides

programming libraries such as DLL’s for most Windows

software packages such as National Instruments’ LabVIEW.

All software options are included in the Keithley Instruments’ CD.

®

based systems, but also drivers for other

1

Programming library KDAQ-DRVR

KDAQ-DRVR includes device drivers and DLL’s for Windows® XP and Windows 2000. Therefore,

all applications developed with KDAQ-DRVR are compatible on Windows XP/2000. The

developing environment can be VB, VC++, Delphi, BC5, or any Windows programming language

that allows calls to a DLL. Documentation includes a User's Guide (refer to

DRVR User’s Guide), and a Function Reference (refer to Appendix B: KDAQ-DRVR Function

Reference).

KDAQ-LVIEW LabVIEW® driver

KDAQ-LVIEW contains the VI’s, which are used to interface with National Instrument's Lab-VIEW®

software package. The KDAQ-LVIEW supports Windows™ XP/2000. The LabVIEW

shipped free with the board — you can install and use them without a license. Documentation

includes an Interface Guide (refer to

and an interface Function Reference (refer to Appendix D: KIDAQ®-LabVIEW Compatible

Function Reference).

Appendix C: KIDAQ®-LabVIEW Compatible Interface Guide),

Appendix A: KDAQ-

®

driver is

1. National Instruments™, NI, and LabVIEW are trademarks of the National Instruments Corporation.

1-4 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Page 21

In this section:

Top ic Pa ge

Introduction......................................................................................... 2-2

Handling precautions ....................................................................... 2-2

Configuration...................................................................................... 2-2

Installation........................................................................................... 2-3

Section 2

Installation

Plug and Play ................................................................................... 2-2

Configuration .................................................................................... 2-2

Troubleshooting................................................................................ 2-2

Page 22

Section 2: Installation KPXI Simultaneous A/D Module Reference Manual

Introduction

This section contains information about handling and installing Keithley Instruments’ KIDAQ®

KPXI series cards:

• Handling precautions

• Configuration

• Installation

Handling precautions

CAUTION Use care when handling the KPXI series cards. KPXI series cards contain

electro-static sensitive components that can be easily damaged by static

electricity.

When handling, make sure to observe the following guidelines:

• Only handle the card on a grounded anti-static mat.

• Wear an an anti-static wristband that is grounded at the same point as the anti-static mat.

Configuration

Plug and Play

As a plug and play component, the board requests an interrupt number via its PCI controller. The

system BIOS responds with an interrupt assignment based on the board information and system

parameters. These system parameters are determined by the installed drivers and the hardware

load recognized by the system. If this is the first time a KPXI series card will be installed on your

Windows

information.

®

system, a hardware driver needs to be installed. Refer to Installation for detailed

Configuration

Configuration is done on a board-by-board basis for all PXI boards on your system. Configuration

is controlled by the system and software. There is no jumper setting required (or available) for

base address, DMA, and interrupt IRQ.

The configuration is not static, but is subject to change with every boot of the system as new

boards are added or removed.

Troubleshooting

If your system doesn't boot or if you experience erratic operation with your PXI board in place, it's

likely caused by an interrupt conflict (perhaps the BIOS Setup is incorrectly configured). In

general, the solution is to consult the BIOS documentation that comes with your system.

2-2 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Page 23

KPXI Simultaneous A/D Module Reference Manual Section 2: Installation

Installation

Step 1. Install driver software

Windows® will find the new module automatically. If this is the first time a KPXI Series card is

running on your Windows system, you will need to install a hardware driver. Use the following

installation procedure as a guide.

NOTE: Keithley Instruments controllers are pre-loaded with the necessary drivers.

For Windows 2000/XP:

1. Insert the CD shipped with the module. The CD should auto load. From the base menu

install the KDAQ-DRVR. This is the hardware driver that recognizes the KPXI Analog

Output Series modules. If the CD does not auto load run, then under

x:\KDAQ-DRVR\DISK1\, you will find SETUP.EXE (x is the drive letter of your CDROM).

This will also run the install.

2. When you complete driver installation, turn off the system.

Step 2. Inspect module

Keeping the “Handling precautions” information in mind, inspect the module for damage. With the

module placed on a firm, flat surface, press down on all socketed IC's to make sure that they are

properly seated.

If the module does not pass the inspection, do not proceed with the installation.

CAUTION Do not apply power to the card if it has been damaged.

The KPXI Series card is now ready for installation.

Step 3. Install module

Remove power from the system and install the KPXI Series card in an available slot.

The PXI connectors are rigid and require careful handling when inserted and removed. Improper

handling of modules can easily damage the backplane.

To insert the module into a PXI chassis, use the following procedure as a guide:

1. Turn off the system.

2. Align the module's edge with the card guide in the PXI chassis.

3. Slide the module into the chassis until resistance is felt from the PXI connector.

4. Push the ejector upwards and fully insert the module into the chassis. Once inserted, a

"click" can be heard from the ejector latch.

5. Tighten the screw on the front panel.

6. Turn on the system.

To remove a module from a PXI chassis, use the following procedure as a guide:

1. Turn off the system.

2. Loosen the screw on the front panel.

3. Push the ejector downwards and carefully remove the module from the chassis.

KPXI-SDAQ-901-01 Rev. A / January 2007 Return to Section Topics 2-3

Page 24

Section 2: Installation KPXI Simultaneous A/D Module Reference Manual

Figure 2-1

Typical PXI module installation

Typical PXI chassis

Front panel

screw

Ejector latch

Modules edge

Step 4. Verify installation

When the system is turned on for the first time with a new module present (or a module in a new

slot), Windows Add New Hardware Wizard attempts to locate the correct driver. If it cannot find

the correct driver, even after you have loaded the driver above in Step 1, then force the Add New

Hardware Wizard to look in Windows system32 directory. The driver files should be in this

location. If they are not, shutdown the system, remove the module, and restart the installation

process.

When the Add New Hardware Wizard finishes, the window will verify whether or not installation

was successful. To confirm if the module is installed correctly at a later time, use Windows Device

Manager. In the Device Manager under KIDAQ Boards, look for a device name matching the

model number of the newly installed board (see

installation is complete. If the board appears with a exclamation point or warning in Device

Manager, the installation was unsuccessful. If unsuccessful, use Device Manager to update the

driver or un-install the module, power down the system, remove the module, and attempt

installation again from Step 1.

Card guide

Figure 2-2 for an example). If it is found,

2-4 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Page 25

KPXI Simultaneous A/D Module Reference Manual Section 2: Installation

Figure 2-2

Device manager (successful installation)

KPXI-SDAQ-901-01 Rev. A / January 2007 Return to Section Topics 2-5

Page 26

Section 2: Installation KPXI Simultaneous A/D Module Reference Manual

This page left blank intentionally.

2-6 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Page 27

In this section:

Top ic Pa ge

Introduction......................................................................................... 3-2

Signal connections ........................................................................... 3-2

Operation Theory .............................................................................. 3-6

Section 3

Operation and Connection

Connectors pin assignment .............................................................. 3-2

Analog Input Signal Connection ....................................................... 3-4

A/D Conversion ................................................................................ 3-6

D/A Conversion .............................................................................. 3-16

Digital I/O........................................................................................ 3-22

General Purpose Timer/Counter Operation.................................... 3-23

Trigger Sources .............................................................................. 3-26

User-controllable Timing Signals.................................................... 3-30

Calibration ......................................................................................... 3-34

Loading Calibration Constants........................................................ 3-34

Auto-calibration............................................................................... 3-34

Saving Calibration Constants ......................................................... 3-35

Page 28

Section 3: Operation and Connection KPXI Simultaneous A/D Module Reference Manual

Introduction

This section contains operation information on KIDAQ® KPXI series cards including signal

connections. Use this information to aid in the understanding of how to configure and program the

KIDAQ

Signal connections

The connectors of the Model KPXI-SDAQ-4-500K/2M, and the signal connection between the

Model KPXI-SDAQ-4-500K/2M and external devices are contained below.

Connectors pin assignment

The Model KPXI-SDAQ-4-500K/2M is equipped with one 68-pin VHDCI-type connector (AMP787254-1). It is used for digital input/output, analog input / output, and timer/counter signals, etc.

The pin assignments of the connectors are defined in

Figure 3-1

68-pin VHDCI-type pin assignment

* SDI for Model KPXI-SDAQ-4-2M only; NC for Model KPXI-SDAQ-4-500K

®

KPXI series modules.

AOEXTREF 8 42 AOGND

SDI3_1 / NC* 9 43 SDI3_0 / NC*

SDI2_1 / NC* 10 44 SDI2_0 / NC*

SDI1_1 / NC* 11 45 SDI1_0 / NC*

SDI0_1 / NC* 12 46 SDI0_0 / NC*

AO_TRIG_OUT 13 47 EXTWFTRG

AI_TRIG_OUT 14 48 EXTDTRIG

GPTC1_SRC 15 49 DGND

GPTC0_SRC 16 50 DGND

GPTC0_GATE 17 51 GPTC1_GATE

GPTC0_OUT 18 52 GPTC1_OUT

GPTC0_UPDOWN 19 53 GPTC1_UPDOWN

EXTTIMEBASE 20 54 DGND

Figure 3-1 and Table 3-1.

CH0+ 1 35 CH0CH1+ 2 36 CH1CH2+ 3 37 CH2CH3+ 4 38 CH3-

EXTATRIG 5 39 AIGND

DA1OUT 6 40 AOGND

DA0OUT 7 41 AOGND

AFI1 21 55 AFI0

PB7 22 56 PB6

PB5 23 57 PB4

PB3 24 58 PB2

PB1 25 59 PB0

PC7 26 60 PC6

PC5 27 61 PC4

DGND 28 62 DGND

PC3 29 63 PC2

PC1 30 64 PC0

PA7 31 65 PA6

PA5 32 66 PA4

PA3 33 67 PA2

PA1 34 68 PA0

3-2 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Page 29

KPXI Simultaneous A/D Module Reference Manual Section 3: Operation and Connection

Table 3-1

68-pin VHDCI-type pin descriptions

Pin # Signal Name Reference Direction Description

1–4 CH<0..3>+ CH0<0..3>- Input Differential positive input

for AI channel <0..3>

5 EXTATRIG AIGND Input External AI analog trigger

6 DA0OUT AOGND Output AO channel 0

7 DA1OUT AOGND Output AO channel 1

8 AOEXTREF AOGND Input External reference for AO

channels

9–12 SDI<3..0>_1 (KPXI-SDAQ-4-2M)

NC (KPXI-SDAQ-4-500K)

13 AO_TRIG_OUT DGND Output AO trigger signal

14 AI_TRIG_OUT DGND Output AI trigger signal

15,16 GPTC<0,1>_SRC DGND Input Source of GPTC<0,1>

17,51 GPTC<0,1>_GATE DGND Input Gate of GPTC<0,1>

18,52 GPTC<0,1>_OUT DGND Input Output of GPTC<0,1>

19,53 GPTC<0,1>_UPDOWN DGND Input Up/Down of GPTC<0,1>

20 EXTTIMEBASE DGND Input External TIMEBASE

21,28,49,5

0,54,62

22,56,23,5

7,24,58,25,

59

26,60,27,6

1,29,63,30,

64

31,65,32,6

6,33,67,34,

68

35–38 CH<0..3>- -------- Input Differential negative input

39 AIGND -------- -------- Analog ground for AI

40–42 AOGND -------- -------- Analog ground for AO

43–46 SDI<3..0>_1 (KPXI-SDAQ-4-2M)

47 EXTWFTRIG DGND Input External AO waveform

48 EXTDTRIG DGND Input External AI digital trigger

55 AFI0 DGND Input Auxiliary Function Input 0

21 AFI1 DGND Input Auxiliary Function Input 1

DGND -------- -------- Digital ground

PB<7,0> DGND PIO* Programmable DIO pins

PC<7,0> DGND PIO* Programmable DIO pins

PA< 7,0> DGND PIO* Programmable DIO pins

NC (KPXI-SDAQ-4-500K)

DGND Input Synchronous digital inputs

of 8255 Port B

of 8255 Port C

of 8255 Port A

for AI channel <0..3>

DGND Input Synchronous digital inputs

trigger

(ADCONV, AD_START)

(DAWR, DA_START)

*PIO: Programmable I/O

KPXI-SDAQ-901-01 Rev. A / January 2007 Return to Section Topics 3-3

Page 30

Section 3: Operation and Connection KPXI Simultaneous A/D Module Reference Manual

Table 3-2

Legend of SSI signals

NOTE The System Synchronization Interface (SSI) signals can be routed to the PXI trigger bus

for multiple module synchronization within a chassis.

SSI timing signal Functionality

SSI_TIMEBASE SSI master: send the TIMEBASE out

SSI slave: accept the SSI_TIMEBASE to replace the

internal TIMEBASE signal.

SSI_ADCONV SSI master: send the ADCONV out

SSI slave: accept the SSI_ADCONV to replace the

internal ADCONV signal.

SSI_SCAN_START SSI master: send the SCAN_START out

SSI slave: accept the SSI_SCAN_START to replace

the internal SCAN_START signal.

SSI_AD_TRIG SSI master: send the internal AD_TRIG out

SSI slave: accept the SSI_AD_TRIG as the digital

trigger signal.

SSI_DAWR SSI master: send the DAWR out.

SSI slave: accept the SSI_DAWR to replace the

internal DAWR signal.

SSI_DA_TRIG SSI master: send the DA_TRIG out.

SSI slave: accept the SSI_DA_TRIG as the digital

trigger signal.

Analog Input Signal Connection

The Model KPXI-SDAQ-4-500K/2M provides 4 differential analog input channels. The analog

signal can be converted to digital values by the A/D converter. To avoid ground loops and get more

accurate measurements from the A/D conversion, it is quite important to understand the signal

source type and how to connect the analog input signals.

Types of signal sources

Ground-Referenced Signal Sources

A ground-referenced signal means it is connected in some way to the building’s system. That is,

the signal source is already connected to a common ground point with respect to the

Model KPXI-SDAQ-4-500K/2M, assuming that the computer is plugged into the same power

system. Non- isolated outputs of instruments and devices that plug into the building’s power

system are ground-referenced signal sources.

Floating Signal Sources

A floating signal source means it is not connected in any way to the building’s ground system. A

device with an isolated output is a floating signal source, such as optical isolator outputs,

transformer outputs, and thermocouples.

Single-Ended Measurements

For single-ended measurement connections, the analog input signal is referenced to the common

ground of the system. In this case, all the negative ends of analog input channels should be

connected to the AIGND on the connector instead of floating. Please refer to the

Figure 3-2.

3-4 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Page 31

KPXI Simultaneous A/D Module Reference Manual Section 3: Operation and Connection

Figure 3-2

Single-ended measurements connections

In single-ended configurations, more electrostatic and magnetic noise couples into the single

connections than in differential configurations. Therefore, the single-ended connection is not

recommended unless minimal wire connections are necessary.

Differential Measurements

Differential Connection for Grounded-Reference Signal Sources

The differential analog input provides two inputs that respond to the signal voltage difference

between them. If the signal source is ground-referenced, the differential mode can be used for the

common-mode noise rejection.

sources under the differential input mode.

Figure 3-3 shows the connection of ground-referenced signal

Figure 3-3

Ground-referenced source and differential input

Differential Connection for Floating Signal Sources

Figure 3-4 shows how to connect a floating signal source to Model KPXI-SDAQ-4-500K/2M in

differential input mode. For floating signal sources, you need to add a resistor at each channel to

provide a bias return path. The resistor value should be about 100 times the equivalent source

impedance. If the source impedance is less than 100ohms, you can simply connect the negative

side of the signal to AGND as well as the negative input of the Instrumentation Amplifier, without

any resistors at all. In differential input mode, less noise couples into the signal connections than in

single-ended mode.

KPXI-SDAQ-901-01 Rev. A / January 2007 Return to Section Topics 3-5

Page 32

Section 3: Operation and Connection KPXI Simultaneous A/D Module Reference Manual

Figure 3-4

Floating source and differential input

Operation Theory

The operation theory of the functions on the Model KPXI-SDAQ-4-500K/2M are described in this

section. The functions include the A/D conversion, D/A conversion, Digital I/O and General

Purpose Counter/Timer. The operation theory can help you understand how to configure and

program the Model KPXI-SDAQ-4-500K/2M.

Model KPXI-SDAQ-4-500K/2M modules are designed that all A/D related timings for multiplexing

A/D sampling are based on scanning. With the exception that there is only one conversion signal

in a scan which could generate up to 4 samples from the different 4 channels at the same time. In

the following description, to conform to the original timing design, we still use “scan” as the unit of

A/D data acquisition. All the DA and GPTC functions are the same in Model KPXI-SDAQ-4-500K/

2M.

A/D Conversion

When using an A/D converter, users should first know about the properties of the signal to be

measured. Users can decide which channel to use and where to connect the signals to the card

(refer

Signal connections for more information). In addition, users should define and control the A/

D signal configurations, including channels, gains, and A/D signal types.

There are 2 ways to initiate A/D conversion: Software conversion with polling data transfer

acquisition mode (Software Polling) or Programmable scan acquisition mode.

The A/D acquisition is initiated by a trigger source; users must decide how to trigger the A/D

conversion. The data acquisition will start once a trigger condition is matched.

After the end of A/D conversion, the A/D data is buffered in a Data FIFO. The A/D data should be

transferred into the PC's memory for further processing.

Model KPXI-SDAQ-4-2M AI Data Format

Synchronous Digital Inputs (for Model KPXI-SDAQ-4-2M only)

When each A/D conversion is completed, the 14-bits converted digital data accompanied with 2

bits of SDI<1..0>_X per channel from J5 will be latched into the 16-bit register and data FIFO, as

shown in

signal with four digital signals. The data format of every acquired 16-bit data is as follows:

Where: D13, D12, D11 ....... D1, D0: 2’s complement A/D 14-bit data

3-6 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Figure 3-5 and Figure 3-6. Therefore, users can simultaneously sample one analog

D13, D12, D11 ....... D1, D0, b1, b0

b1, b0: Synchronous Digital Inputs SDI<1..0>

Page 33

KPXI Simultaneous A/D Module Reference Manual Section 3: Operation and Connection

A

A

r

A

A

A

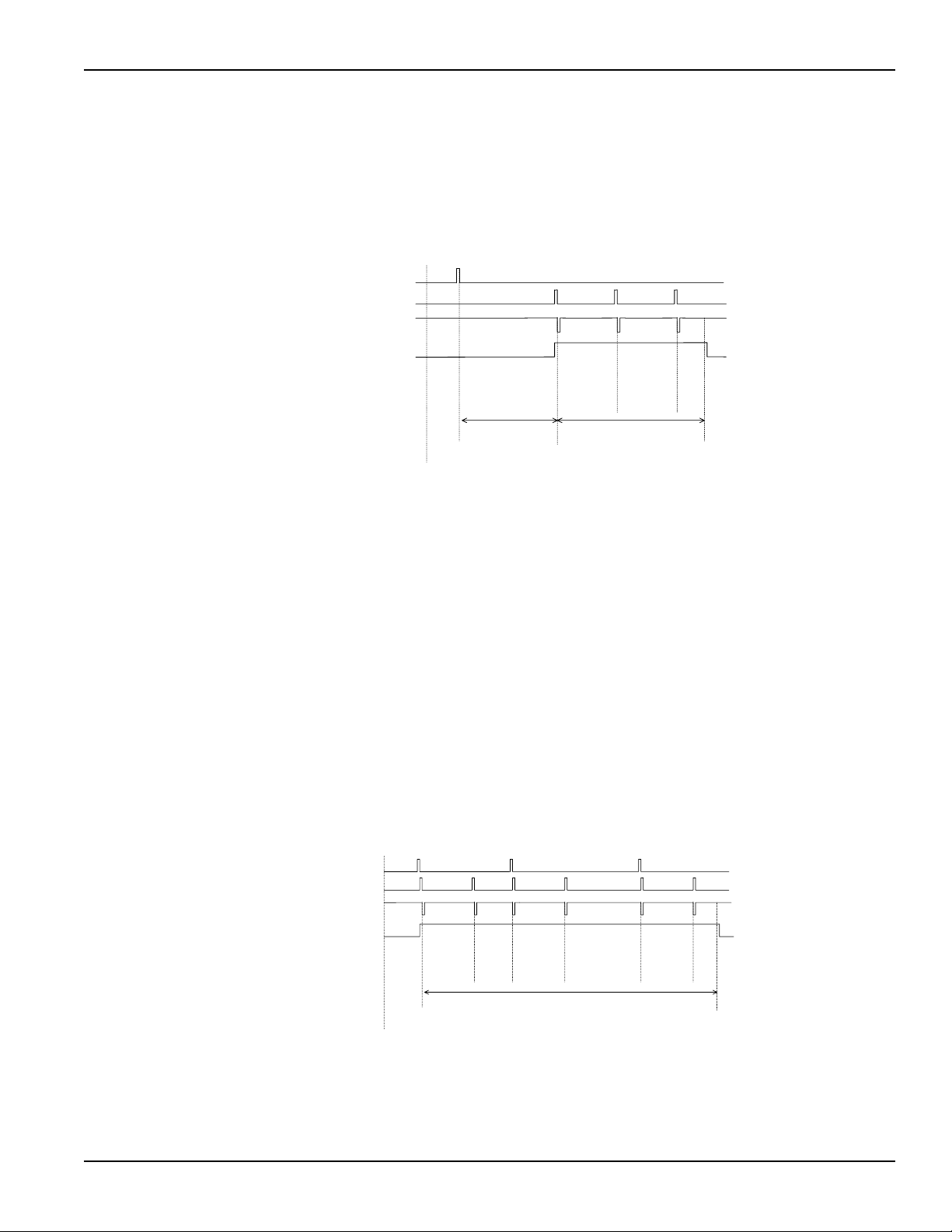

Figure 3-5

Synchronous Digital Inputs Block Diagram

ADC

nADBUSY

SDI<1..0>

D<13..0>

nADBUSY

16-bit

Register

2

AD

14

CLK

16

Data

FIFO

SDI<1..0>

from CN2

From

Instrumentation

mplifie

D_conversion

in

nADCONV

Figure 3-6

Synchronous Digital Inputs timing

D_conversion

nADBUSY

16 bits data(including AD<13..0> and SDI<1..0>

latched into AD Data FIFO

NOTE Since the analog signal is sampled when an A/D conversion starts (falling edge of

A/D_conversion signal), while SDI<1..0> are sampled right after an A/D conversion

completes (rising edge of nADBUSY signal). To be precise: SDI<1..0> are sampled within

220 to 400ns lag to the analog signal, due to the variation of the conversion time of the

A/D converters.

Table 3-3 and Table 3-4 illustrate the ideal transfer characteristics for various input ranges. The

converted digital codes for KPXI-SDAQ-4-2M are 14-bit and 2’s complement, and here we present

the codes as hexadecimal numbers. Note that the last 2 bits of the transferred data, which are the

synchronous digital input (SDI), should be ignored when retrieving the analog data.

NOTE Table 3-3 and Table 3-4 applies to Model KPXI-SDAQ-4-2M only. Also, the last 2 digital

codes are SDI<1..0>.

KPXI-SDAQ-901-01 Rev. A / January 2007 Return to Section Topics 3-7

Page 34

Section 3: Operation and Connection KPXI Simultaneous A/D Module Reference Manual

Table 3-3

Bipolar analog input range and output digital code

Description Bipolar Analog Input Range Digital code

Full-scale Range ±10V ±5V ±2.5V ±1.25V

Least significant bit 1.22mV 0.61mV 0.305mV 0.153mV

FSR-1LSB 9.9988V 4.9994V 2.4997V 1.2499V 1FFF

Midscale +1LSB 1.22mV 0.61mV 0.305mV 0.153mV 0001

Midscale 0V 0V 0V 0V 0000

Midscale –1LSB -1.22mV -0.61mV -0.305mV -0.153mV 3FFF

-FSR -10V -5V -2.5V -1.25V 2000

Table 3-4

Unipolar analog input range and output digital code

Description Unipolar Analog Input Range Digital code

Full-scale Range 0V to

10V

Least significant

bit

FSR-1LSB 9.9994V 4.9997V 2.9999V 1.2499V 1FFF

Midscale +1LSB 5.00061V 2.50031V1.25015V 625.08mV 0001

0.61mV 0.305mV 0.153mV 76.3uV

0 to +5V 0 to +2.5V 0 to +1.25V

Midscale 5V 2.5V 1.25V 625mV 0000

Midscale –1LSB 4.99939V 2.49970V1.24985V 624.92mV 3FFF

-FSR 0V 0V 0V 0V 2000

Model KPXI-SDAQ-4-500K AI data format

The data format of the acquired 16-bit A/D data is Binary coding. Table 3-5 and Table 3-6 illustrate

the valid input ranges and the ideal transfer characteristics. The converted digital codes for

Model KPXI-SDAQ-4-500K are 16-bit and direct binary, and here we present the codes as

hexadecimal numbers.

Table 3-5

Bipolar analog input range and output digital code

Digital

Description Bipolar Analog Input Range

Full-scale

Range

Least significant bit

FSR-1LSB 9.999695V4.999847V 2.499924V1.249962V FFFF

Midscale

+1LSB

Midscale 0V 0V 0V 0V 8000

Midscale -1LSB -305.2uV -152.6uV -76.3uV -38.15uV 7FFF

-FSR -10V -5V -2.5V -1.25V 0000

±10V ±5V ±2.5V ±1.25V

305.2uV 152.6uV 76.3uV 38.15uV

305.2uV 152.6uV 76.3uV 38.15uV 8001

code

3-8 Return to Section Topics KPXI-SDAQ-901-01 Rev. A / January 2007

Page 35

KPXI Simultaneous A/D Module Reference Manual Section 3: Operation and Connection

Table 3-6

Unipolar analog input range and output digital code

Digital

Description Unipolar Analog Input Range