Page 1

KPCMCIA-12AI/16AI PCMCIA

Data Acquisition System

User’s Manual

A GREATER MEASURE OF CONFIDENCE

Page 2

WARRANTY

Hardware

Keithley Instruments, Inc. warrants that, for a period of one (1) year from the date of shipment (3 years for Models 2000, 2001, 2002, 2010 and 2700), the

Keithley Hardware product will be free from defects in materials or workmanship. This warranty will be honored provided the defect has not been caused

by use of the Keithley Hardware not in accordance with the instructions for the product. This warranty shall be null and void upon: (1) any modification of

Keithley Hardware that is made by other than Keithley and not approved in writing by Keithley or (2) operation of the Keithley Hardware outside of the

environmental specifications therefore.

Upon receiving notification of a defect in the Keithley Hardware during the warranty period, Keithley will, at its option, either repair or replace such Keithley Hardware. During the first ninety days of the warranty period, Keithley will, at its option, supply the necessary on site labor to return the product to the condition prior to

the notification of a defect. Failure to notify Keithley of a defect during the warranty shall relieve Keithley of its obligations and liabilities under this warranty.

Other Hardware

The portion of the product that is not manufactured by Keithley (Other Hardware) shall not be covered by this warranty, and Keithley shall have no duty of

obligation to enforce any manufacturers' warranties on behalf of the customer. On those other manufacturers’ products that Keithley purchases for resale,

Keithley shall have no duty of obligation to enforce any manufacturers’ warranties on behalf of the customer.

Software

Keithley warrants that for a period of one (1) year from date of shipment, the Keithley produced portion of the software or firmware (Keithley Software) will

conform in all material respects with the published specifications provided such Keithley Software is used on the product for which it is intended and otherwise in accordance with the instructions therefore. Keithley does not warrant that operation of the Keithley Software will be uninterrupted or error-free and/

or that the Keithley Software will be adequate for the customer's intended application and/or use. This warranty shall be null and void upon any modification

of the Keithley Software that is made by other than Keithley and not approved in writing by Keithley.

If Keithley receives notification of a Keithley Software nonconformity that is covered by this warranty during the warranty period, Keithley will review the

conditions described in such notice. Such notice must state the published specification(s) to which the Keithley Software fails to conform and the manner

in which the Keithley Software fails to conform to such published specification(s) with sufficient specificity to permit Keithley to correct such nonconformity. If Keithley determines that the Keithley Software does not conform with the published specifications, Keithley will, at its option, provide either the

programming services necessary to correct such nonconformity or develop a program change to bypass such nonconformity in the Keithley Software.

Failure to notify Keithley of a nonconformity during the warranty shall relieve Keithley of its obligations and liabilities under this warranty.

Other Software

OEM software that is not produced by Keithley (Other Software) shall not be covered by this warranty, and Keithley shall have no duty or obligation to

enforce any OEM's warranties on behalf of the customer.

Other Items

Keithley warrants the following items for 90 days from the date of shipment: probes, cables, rechargeable batteries, diskettes, and documentation.

Items not Covered under Warranty

This warranty does not apply to fuses, non-rechargeable batteries, damage from battery leakage, or problems arising from normal wear or failure to follow

instructions.

Limitation of Warranty

This warranty does not apply to defects resulting from product modification made by Purchaser without Keithley's express written consent, or by misuse

of any product or part.

Disclaimer of Warranties

EXCEPT FOR THE EXPRESS WARRANTIES ABOVE KEITHLEY DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION, ALL IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEITHLEY DISCLAIMS ALL WARRANTIES WITH RESPECT TO THE OTHER HARDWARE AND OTHER SOFTWARE.

Limitation of Liability

KEITHLEY INSTRUMENTS SHALL IN NO EVENT, REGARDLESS OF CAUSE, ASSUME RESPONSIBILITY FOR OR BE LIABLE FOR: (1)

ECONOMICAL, INCIDENTAL, CONSEQUENTIAL, INDIRECT, SPECIAL, PUNITIVE OR EXEMPLARY DAMAGES, WHETHER CLAIMED

UNDER CONTRACT, TORT OR ANY OTHER LEGAL THEORY, (2) LOSS OF OR DAMAGE TO THE CUSTOMER'S DATA OR PROGRAMMING, OR (3) PENALTIES OR PENALTY CLAUSES OF ANY DESCRIPTION OR INDEMNIFICATION OF THE CUSTOMER OR OTHERS FOR

COSTS, DAMAGES, OR EXPENSES RELATED TO THE GOODS OR SERVICES PROVIDED UNDER THIS WARRANTY.

Keithley Instruments, Inc. 28775 Aurora Road • Cleveland, Ohio 44139 • 440-248-0400 • Fax: 440-248-6168

1-888-KEITHLEY (534-8453) • www.keithley.com

Sales Offices: BELGIUM: Bergensesteenweg 709 • B-1600 Sint-Pieters-Leeuw • 02-363 00 40 • Fax: 02/363 00 64

CHINA: Yuan Chen Xin Building, Room 705 • 12 Yumin Road, Dewai, Madian • Beijing 100029 • 8610-6202-2886 • Fax: 8610-6202-2892

FINLAND: Tietäjäntie 2 • 02130 Espoo • Phone: 09-54 75 08 10 • Fax: 09-25 10 51 00

FRANCE: 3, allée des Garays • 91127 Palaiseau Cédex • 01-64 53 20 20 • Fax: 01-60 11 77 26

GERMANY: Landsberger Strasse 65 • 82110 Germering • 089/84 93 07-40 • Fax: 089/84 93 07-34

GREAT BRITAIN: Unit 2 Commerce Park, Brunel Road • Theale • Berkshire RG7 4AB • 0118 929 7500 • Fax: 0118 929 7519

INDIA: Flat 2B, Willocrissa • 14, Rest House Crescent • Bangalore 560 001 • 91-80-509-1320/21 • Fax: 91-80-509-1322

ITALY: Viale San Gimignano, 38 • 20146 Milano • 02-48 39 16 01 • Fax: 02-48 30 22 74

JAPAN: New Pier Takeshiba North Tower 13F • 11-1, Kaigan 1-chome • Minato-ku, Tokyo 105-0022 • 81-3-5733-7555 • Fax: 81-3-5733-7556

KOREA: 2FL., URI Building • 2-14 Yangjae-Dong • Seocho-Gu, Seoul 137-888 • 82-2-574-7778 • Fax: 82-2-574-7838

NETHERLANDS: Postbus 559 • 4200 AN Gorinchem • 0183-635333 • Fax: 0183-630821

SWEDEN: c/o Regus Business Centre • Frosundaviks Allé 15, 4tr • 169 70 Solna • 08-509 04 679 • Fax: 08-655 26 10

SWITZERLAND: Kriesbachstrasse 4 • 8600 Dübendorf • 01-821 94 44 • Fax: 01-820 30 81

TAIWAN: 1FL., 85 Po Ai Street • Hsinchu, Taiwan, R.O.C. • 886-3-572-9077• Fax: 886-3-572-9031

4/02

Page 3

KPCMCIA-12AI/16AI

PCMCIA Data Acquisition System

User’s Manual

©1999, Keithley Instruments, Inc.

All rights reserved.

Cleveland, Ohio, U.S.A.

Fourth Printing, August 2002

Document Number: 98933 Rev. D

Page 4

Manual Print History

The print history shown below lists the printing dates of all Revisions and Addenda created for this manual. The Revision

Level letter increases alphabetically as the manual undergoes subsequent updates. Addenda, which are released between Revisions, contain important change information that the user should incorporate immediately into the manual. Addenda are numbered sequentially. When a new Revision is created, all Addenda associated with the previous Revision of the manual are

incorporated into the new Revision of the manual. Each new Revision includes a revised copy of this print history page.

Revision A (Document Number 98933)................................................................................................... July 1997

Revision B (Document Number 98933).......................................................................................... December 1997

Revision C (Document Number 98933)......................................................................................... September 1999

Revision D (Document Number 98933)............................................................................................... August 2002

All Keithley product names are trademarks or registered trademarks of Keithley Instruments, Inc.

Other brand and product names are trademarks or registered trademarks of their respective holders.

Page 5

Safety Precautions

The following safety precautions should be observed before using

this product and any associated instrumentation. Although some instruments and accessories would normally be used with non-hazardous voltages, there are situations where hazardous conditions

may be present.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. Read and follow all installation,

operation, and maintenance information carefully before using the

product. Refer to the manual for complete product specifications.

If the product is used in a manner not specified, the protection provided by the product may be impaired.

The types of product users are:

Responsible body is the individual or group responsible for the use

and maintenance of equipment, for ensuring that the equipment is

operated within its specifications and operating limits, and for ensuring that operators are adequately trained.

Operators use the product for its intended function. They must be

trained in electrical safety procedures and proper use of the instrument. They must be protected from electric shock and contact with

hazardous live circuits.

Maintenance personnel perform routine procedures on the product

to keep it operating properly, for example, setting the line voltage

or replacing consumable materials. Maintenance procedures are described in the manual. The procedures explicitly state if the operator

may perform them. Otherwise, they should be performed only by

service personnel.

Service personnel are trained to work on live circuits, and perform

safe installations and repairs of products. Only properly trained service personnel may perform installation and service procedures.

Keithley products are designed for use with electrical signals that

are rated Installation Category I and Installation Category II, as described in the International Electrotechnical Commission (IEC)

Standard IEC 60664. Most measurement, control, and data I/O signals are Installation Category I and must not be directly connected

to mains voltage or to voltage sources with high transient over-voltages. Installation Category II connections require protection for

high transient over-voltages often associated with local AC mains

connections. Assume all measurement, control, and data I/O connections are for connection to Category I sources unless otherwise

marked or described in the Manual.

Exercise extreme caution when a shock hazard is present. Lethal

voltage may be present on cable connector jacks or test fixtures. The

American National Standards Institute (ANSI) states that a shock

hazard exists when voltage levels greater than 30V RMS, 42.4V

peak, or 60VDC are present. A good safety practice is to expect

that hazardous voltage is present in any unknown circuit before

measuring.

Operators of this product must be protected from electric shock at

all times. The responsible body must ensure that operators are prevented access and/or insulated from every connection point. In

some cases, connections must be exposed to potential human contact. Product operators in these circumstances must be trained to

protect themselves from the risk of electric shock. If the circuit is

capable of operating at or above 1000 volts, no conductive part of

the circuit may be exposed.

Do not connect switching cards directly to unlimited power circuits.

They are intended to be used with impedance limited sources.

NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to limit fault current and voltage to the card.

Before operating an instrument, make sure the line cord is connected to a properly grounded power receptacle. Inspect the connecting

cables, test leads, and jumpers for possible wear, cracks, or breaks

before each use.

When installing equipment where access to the main power cord is

restricted, such as rack mounting, a separate main input power disconnect device must be provided, in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any

other instruments while power is applied to the circuit under test.

ALWAYS remove power from the entire test system and discharge

any capacitors before: connecting or disconnecting cables or jumpers, installing or removing switching cards, or making internal

changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always

make measurements with dry hands while standing on a dry, insulated

surface capable of withstanding the voltage being measured.

The instrument and accessories must be used in accordance with its

specifications and operating instructions or the safety of the equipment may be impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating information, and as shown on the instrument or test fixture panels, or

switching card.

When fuses are used in a product, replace with same type and rating

for continued protection against fire hazard.

Chassis connections must only be used as shield connections for

measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use of a

lid interlock.

5/02

Page 6

If or is present, connect it to safety earth ground using the

wire recommended in the user documentation.

!

The symbol on an instrument indicates that the user should refer to the operating instructions located in the manual.

The symbol on an instrument shows that it can source or measure 1000 volts or more, including the combined effect of normal

and common mode voltages. Use standard safety precautions to

avoid personal contact with these voltages.

The WARNING heading in a manual explains dangers that might

result in personal injury or death. Always read the associated information very carefully before performing the indicated procedure.

The CAUTION heading in a manual explains hazards that could

damage the instrument. Such damage may invalidate the warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and

all test cables.

To maintain protection from electric shock and fire, replacement

components in mains circuits, including the power transformer, test

leads, and input jacks, must be purchased from Keithley Instruments. Standard fuses, with applicable national safety approvals,

may be used if the rating and type are the same. Other components

that are not safety related may be purchased from other suppliers as

long as they are equivalent to the original component. (Note that selected parts should be purchased only through Keithley Instruments

to maintain accuracy and functionality of the product.) If you are

unsure about the applicability of a replacement component, call a

Keithley Instruments office for information.

To clean an instrument, use a damp cloth or mild, water based

cleaner. Clean the exterior of the instrument only. Do not apply

cleaner directly to the instrument or allow liquids to enter or spill

on the instrument. Products that consist of a circuit board with no

case or chassis (e.g., data acquisition board for installation into a

computer) should never require cleaning if handled according to instructions. If the board becomes contaminated and operation is affected, the board should be returned to the factory for proper

cleaning/servicing.

Page 7

1 Introduction

Table of Contents

Getting started ...................................................................................................................................................... 1-2

Features ................................................................................................................................................................ 1-2

Technical support................................................................................................................................................. 1-3

2 Installation

Hardware setup ....................................................................................................................................................2-2

Software setup......................................................................................................................................................2-2

3 Theory of Operation

Introduction.......................................................................................................................................................... 3-2

DC/DC power supply...........................................................................................................................................3-2

Analog input multiplexer .....................................................................................................................................3-2

Programmable gain control.................................................................................................................................. 3-3

Scan list ................................................................................................................................................................ 3-3

Trigger circuit ......................................................................................................................................................3-3

A/D converter and data FIFO............................................................................................................................... 3-4

Interrupt and status...............................................................................................................................................3-4

Digital I/O ............................................................................................................................................................3-4

A/D state machine................................................................................................................................................ 3-5

4 I/O Connections

Cable assembly ....................................................................................................................................................4-2

i

Page 8

5 Optional Accessories

Introduction ..........................................................................................................................................................5-2

Attaching accessories ...........................................................................................................................................5-2

Attaching an STP-37 screw terminal panel ..................................................................................................5-2

Attaching an EXP-1600 expansion accessory..............................................................................................5-3

Attaching multiple EXP-1600 expansion accessories..................................................................................5-4

A Specifications

B PCMCIA Interface

Introduction .........................................................................................................................................................B-2

Configuration and option register (COR)............................................................................................................B-3

Card configuration and status register (CCSR) ................................................................................................... B-3

C I/O Registers

Introduction .........................................................................................................................................................C-2

Data FIFO register (base + 0)..............................................................................................................................C-2

Data FIFO operation modes ........................................................................................................................C-3

Mode setting ................................................................................................................................................ C-4

FIFO flags.................................................................................................................................................... C-4

Scan list queue register (base + 1, write only).....................................................................................................C-5

Scan list queue programming ...................................................................................................................... C-5

Channel configuration ................................................................................................................................. C-6

Analog input offset correction.....................................................................................................................C-7

Control register (base + 2, write)......................................................................................................................... C-7

Clock source ................................................................................................................................................ C-7

Expansion mode ..........................................................................................................................................C-7

Interrupt enable............................................................................................................................................ C-7

Trigger mode ............................................................................................................................................... C-8

Trigger source.............................................................................................................................................. C-8

Trigger edge.................................................................................................................................................C-8

Status register (base + 2, read) ............................................................................................................................C-8

Digital output register (base + 3, write)...............................................................................................................C-9

Digital input register (base + 3, read)..................................................................................................................C-9

Pacer clock (base + 4, +5, +6, write only)......................................................................................................... C-10

Auxiliary control register (base + 7, write only) ............................................................................................... C-11

Trigger/arm command ............................................................................................................................... C-11

Flush data FIFO command ........................................................................................................................ C-11

Flush scan list queue command.................................................................................................................C-11

Stop A/D command ................................................................................................................................... C-12

Data FIFO program/access control............................................................................................................ C-12

Scan rate selection ..................................................................................................................................... C-13

ii

Page 9

3 Theory of Operation

List of Illustrations

Figure 3-1 State transition diagram of A/D conversion process............................................................................................ 3-5

4 I/O Connections

Figure 4-1 KPCMCIA-12AI/16AI PC card D-37 output connector, KCAB-AI................................................................... 4-3

5 Optional Accessories

Figure 5-1 Attaching an STP-37 screw terminal panel.......................................................................................................... 5-2

Figure 5-2 Attaching an EXP-1600 expansion accessory......................................................................................................5-3

Figure 5-3 Attaching multiple EXP-1600 expansion accessories..........................................................................................5-4

C I/O Registers

Figure C-1 Pacer clock block diagram ................................................................................................................................ C-10

iii

Page 10

4 I/O Connections

List of Tables

Table 4-1 KPCMCIA-12AI/16AI PC card cable mapping ..................................................................................................4-2

B PCMCIA Interface

Table B-1 PCMCIA configuration registers ........................................................................................................................ B-2

Table B-2 COR bit definitions ............................................................................................................................................. B-3

Table B-3 CCSR bit definitions ........................................................................................................................................... B-3

C I/O Registers

Table C-1 KPCMCIA-12AI/16AI PC card register map..................................................................................................... C-2

Table C-2 Data FIFO register bit allocation ........................................................................................................................ C-2

Table C-3 Data FIFO operation mode ................................................................................................................................. C-3

Table C-4 Data FIFO threshold setting................................................................................................................................ C-3

Table C-5 Data FIFO flag status .......................................................................................................................................... C-4

Table C-6 Scan list queue entry bit definitions.................................................................................................................... C-5

Table C-7 Scan list queue programming example 1 ............................................................................................................ C-6

Table C-8 Scan list queue programming example 2 ............................................................................................................ C-6

Table C-9 Control register bit definitions ............................................................................................................................ C-7

Table C-10 Status register bit definitions............................................................................................................................... C-8

Table C-11 Digital output register bit definitions .................................................................................................................. C-9

Table C-12 Digital input register bit definitions .................................................................................................................... C-9

Table C-13 Auxiliary control register bit definitions........................................................................................................... C-11

Table C-14 Data FIFO threshold setting .............................................................................................................................. C-12

v

Page 11

1

Introduction

Page 12

1-2 Introduction KPCMCIA-12AI/16AI User’s Manual

Getting started

The KPCMCIA-12AI/16AI PC cards are PCMCIA type II data acquisition systems with eight

differential or 16 single-ended analog input channels. The number of input channels can be

expanded to 256 with input expansion cards. Each channel has a bipolar input range of ±10V,

±5V, ±2.5V, or ±1.25V (programmable gains of 1, 2, 4, or 8). These PC cards support sampling

rates up to 100kHz at either 12-bit or 16-bit resolution.

Equipped with a data FIFO (first in first out) of 2048 samples, the KPCMCIA-12AI/16AI PC cards

can achieve full-speed data acquisition under Windows 95/98 and Windows NT. The cards have a

scan FIFO of the same size that supports full-speed, random-order channel scanning and gain

selection for all the input channels (up to 256 channels when using the input expansion cards).

These PC cards also include a 24-bit pacer clock and a programmable divided-by-2, by-10, or by 100 pre-scaler. The pacer clock can also be used with an external clock source. With the 10MHz

internal clock source, the pacer clock can generate accurate sampling rate from 0.006Hz to 100kHz.

Both cards have four digital inputs and four digital output channels, which are all TTL compatible

and may be used for control or monitoring in addition to analog data acquisition.

The DriverLINX software drivers provided support various programming languages including

Visual C/C++, Visual Basic and Delphi. A Dynamic Link Library (DLL) is provided for all programming languages under Microsoft Windows, as well as the Visual Basic Controls (VBX). The

KPCMCIA-12AI/16AI PC card also has turn-key software supports for TestPoint and LabView.

Features

The KPCMCIA-12AI/16AI is provided with a KCAB-AI cable with an industry standard D-37

female connector for interfacing to optional terminal blocks and expansion boards. These

optional accessories are described in Section 5.

The KPCMCIA-12AI/16AI PC card offers the following features:

•

12- or 16-bit resolution

Eight differential or 16 single-ended analog input channels, expandable to 256 channels

•

•

Bipolar input range up to ±10V

•

Truly programmable gains of 1, 2, 4, or 8

Full-speed channel scanning and gain selection for all analog input channels

•

•

Data FIFO of 2048 samples

Sampling rate up to 100kHz

•

•

24-bit pacer clock with variable pre-scalers and external clock source*

Digital input/output channels

•

•

Flexible trigger mode (internal/external*, one-shot/continuous, rising/falling edge)

Software drivers for Windows 95/98 and Windows NT as well as canned software packages

•

for TestPoint. An optional LabView driver is available.

*NOTE In “Paced” mode, the same input pin is shared between external clock and external trigger,

therefore only one function can be used (not both simultaneously).

Page 13

KPCMCIA-12AI/16AI User’s Manual Introduction 1-3

Technical support

Before returning any equipment for repair, call Keithley Instruments, Inc., for technical support

at:

1-888-KEITHLEY

Monday - Friday, 8:00 a.m. - 5:00 p.m., Eastern Time

An applications engineer will help you diagnose and resolve your problem over the telephone.

If a telephone resolution is not possible, the applications engineer will issue you a Return Material

Authorization (RMA) number and ask you to return the equipment. Include the RMA number

with any documentation regarding the equipment.

When returning equipment for repair, include the following information:

•

Your name, address, and telephone number.

•

The invoice or order number and date of equipment purchase.

A description of the problem or its symptoms.

•

•

The RMA number on the outside of the package.

Repackage the equipment using the original anti-static wrapping, if possible, and handle it with

ground protection. Ship the equipment to:

ATTN: RMA # __________

Repair Department

Keithley Instruments, Inc.

28775 Aurora Road

Cleveland, OH 44139

Telephone 1-888-KEITHLEY

FAX (440) 248-6168

NOTES If you are submitting your equipment for repair under warranty, you

must include the invoice number and date of purchase.

To enable Keithley Instruments, Inc., to respond as quickly as possible,

you must include the RMA number on the outside of the package.

Page 14

2

Installation

Page 15

2-2 Installation KPCMCIA-12AI/16AI User’s Manual

Hardware setup

To install the KPCMCIA-12AI/16AI PC card, insert the adapter into any type II PCMCIA socket.

All other configuration options are determined by the DriverLINX Software operating system as

discussed in your DriverLINX manuals.

Software setup

Refer to your DriverLINX documentation for a detailed description of the software installation

procedure.

Page 16

3

Theory of Operation

Page 17

3-2 Theory of Operation KPCMCIA-12AI/16AI User’s Manual

Introduction

The KPCMCIA-12AI/16AI PC card consists of eight differential or 16 single-ended analog input

channels. Each channel has a bipolar input range from –0.01V (gain = 1000), –0.1V (gain = 100),

–1V (gain = 10), and –10V (gain = 1) with programmable gains of 1, 10, 100, and 1000. The

A/D converter, either 12-bit or 16-bit, can be operated at its top speed of 100,000 samples per

second (10 µ s per sample).

The A/D converter uses left-justified 2 s complement coding. For the 16-bit version, its output

ranges from -32768 to 32767. However, the 12-bit version will have its 12-bit result occupying

the most significant 12 bits and will pad its least significant four bits with all zeroes to make a

16-bit output word for each converted input sample.

The KPCMCIA-12AI/16AI PC card can be operated as an I/O device, occupying eight consecutive bytes in the I/O address space. It can also be configured to operate via a memory mapped

I/O. It fully complies with the PCMCIA standard 2.10 as a type II card. The card does not have

any jumpers or DIP switches; all of its configurable features are programmable.

Functionally, the KPCMCIA-12AI/16AI PC card consists of the following components: the

DC/DC power supply, analog input multiplexer, programmable gain control, A/D converter, data

FIFO, scan list, trigger control, pacer clock, interrupt and status, digital I/O, as well as the associated control circuits.

DC/DC power supply

The KPCMCIA-12AI/16AI PC card uses a standard 5V power supply for its digital circuit. The

–15V power supplies are used for the analog front end, and the analog +5V power supply is used

for the A/D converter. All are generated by a DC/DC converter off the +5 digital input power

supply from the PCMCIA connector. The DC/DC converter takes 140mA, 78% of the 180mA

total load current, from the input power supply.

According to the new PCMCIA specification, any card that takes more than 100mA cannot be

turned on when the card is inserted until it is intentionally accessed. The KPCMCIA-12AI/16AI

PC card will support the new specification by providing a unique power-down mode control.

When the card is first plugged in, powered up, or reset, the DC/DC converter shuts off. Only the

digital portion is up and running, taking only 40mA from the input +5V power supply. Fullpowered mode can then be activated by software.

Analog input multiplexer

The differential or single-ended configuration is selected by software. The expansion cards can

only be used on single-ended channels. The single-ended/differential selection should be the

same for all the internal channels (e.g., all eight channels as differential or all 16 channels as

single-ended). Having some channels configured as single-ended and others as differential could

cause confusion and unexpected signal errors.

In a differential configuration, there are at most eight channels. However, if you specify channel

8 to 15 in the differential configuration, the inputs will be shorted to ground for the system offset

measurement. The readings taken under these circumstances can be used for offset correction.

The input multiplexers have built-in protection against overvoltage when the board is powered

on and off. The protection mechanism will isolate the input from the rest of the board as long as

the input voltage is within the protection range of –30V.

Page 18

KPCMCIA-12AI/16AI User’s Manual Theory of Operation 3-3

Programmable gain control

The KPCMCIA-12AI/16AI PC card has an internal gain of 1, 10, 100, and 1000. The gain can be

changed from channel to channel when scanning through the channels. There is a programmable

gain instrumentation amplifier with gains of 1, 10, 100, and 1000. The internal gain selection is

specified in the scan list entry by software. The internal gain selection determines the gain of the

analog front end.

The settling time of the analog front end meets the speed requirement. However, if the amplifier

is saturated, it may need a longer amount of time to recover, which may cause distortion in the

input signal to the A/D converter. Amplifier saturation should be avoided (use low gains or attenuate the input signal).

Scan list

One entry to the scan list contains a 16-bit word or two eight-bit bytes. It specifies the internal

channel selection and gain selection (in the high byte or MSB), the external channel and gain

selection (in the low byte or LSB), as well as other control and configuration settings.

The external selections are used for channels on the expansion cards, while internal ones are used

for channels on the KPCMCIA-12AI/16AI PC card.

The expansion cards are not included as part of the KPCMCIA-12AI/16AI data acquisition system. However, they can be purchased separately from Keithley.

The number of entries in the scan list ranges from 1 to 2048. There are no dependencies implied

among the entries of the scan list. You may choose any valid gain combination for any channel,

internal or external. The channels can be scanned in any order as required, repeated or not, with

the same or different gain for each entry.

The differential/single-ended selection should be the same for all the entries in the scan list. The

single-ended configuration should be selected if one or more expansion cards are connected to

the KPCMCIA-12AI/16AI PC card.

The synchronous sample and hold selection is reserved for the expansion cards.

Trigger circuit

*NOTE In “Paced” mode, the same input pin is shared between external clock and external trigger,

The KPCMCIA-12AI/16AI PC card can be triggered by the software (or an internal trigger as

compared to that coming from an external TTL signal), the external TTL signal*, or the pacer

clock. For the external TTL trigger, an active trigger edge can be selected for either the low-tohigh transition or the high-to-low transition.

In one-shot trigger mode, one trigger, either internal or external, starts one scan of all the channels

specified in the scan list. The pacer clock does not have any effect in this mode. Multiple scans

can be realized by issuing (or receiving) multiple triggers.

In continuous trigger mode, the software or TTL trigger starts a series of scans in which the first

is initiated immediately upon receiving the trigger, while the rest are carried out each time the

pacer clock fires. The process continues until software issues an A/D stop command.

If the internal trigger (or the software trigger) is selected, a trig/arm command from software

serves as a trigger as soon as it is received by the PC card. For the external trigger source, the

same command is taken as an arm command, which arms the PC card so the first proper trigger

edge since receiving the arm command serves as the trigger. Any trigger edges before the first one

are ignored. Unexpected edge transitions during the configuration of the trigger source and edge

will not be taken as triggers as long as the PC card is not armed.

therefore only one function can be used (not both simultaneously).

Page 19

3-4 Theory of Operation KPCMCIA-12AI/16AI User’s Manual

A/D converter and data FIFO

The KPCMCIA-12AI/16AI PC card always assumes a bipolar input range of –10V if the gain is

one. The output data format will always be in 2 s complement (and left justified for 12-bit versions). The data acquisition time of the A/D converter is 2 µ s, and its conversion time is no more

than 8 µ s. The output of the A/D converter is fed into the data FIFO, providing 2048 samples for

data buffering.

The hardware design guarantees that the A/D converter, once triggered, will do a conversion for

every analog input channel specified in the scan list at the specified scan speed and feed the results

into the data FIFO. In between scans, the PC card waits until another trigger occurs (one-shot

mode) or the pacer clock fires (continuous mode).

The data FIFO has two programmable thresholds, one for almost full and the other for almost

empty. The KPCMCIA-12AI/16AI PC card only uses the almost-full threshold and ignores the

almost-empty one. Upon power-up or reset, the almost-full threshold defaults to 7 bytes to full

(3.5 samples).

When the FIFO is full, no more samples can be written into the FIFO. At the end of each scan,

the KPCMCIA-12AI/16AI PC card sets a data-lost flag if the data FIFO is already full.

Interrupt and status

The KPCMCIA-12AI/16AI PC card has two interrupt sources: the end-of-scan (EOS) interrupt

and the FIFO threshold interrupt. These interrupts are used as follows:

•

•

Digital I/O

The KPCMCIA-12AI/16AI PC card has one digital input port (base + 3, read only) of four bits

(bits 0 through 3) and one digital output port (base + 3, write only) of four output bits (bits 0

through 3). The output port is latched, but the input port is not.

Four input lines are connected to the digital input port; each represents one bit in the port. When

reading the digital input port, the CURRENT status of the digital input lines are returned to the

host.

All of the four input lines are shared with other functions. Bit 0 will be shared as the external trigger and external paced clock input, while bit 2 is shared as the external burst clock input. Bits 1

and 3 are taken over as the external gain selection lines if one or more expansion cards are connected and an expansion bit is set by software. Nevertheless, the current status of the digital input

lines will always be returned when the host reads the digital input port. It does not matter if the

lines are shared or not.

When the EOS interrupt is enabled, an interrupt is sent to the host at the end of each scan of

the channel list. If there is only one channel in the scan list, the EOS interrupt is reduced to

an EOC (end-of-conversion) interrupt.

The FIFO threshold interrupt, when enabled, is sent to the host when the almost-full flag is

set. The host can then move a block of samples from the FIFO.

The four digital output lines will be taken over as the external channel selection lines if an expansion bit is set by software. In that case, the digital output lines will be driven by the external channel selection bits of the current scan list entry. Otherwise, they will be connected to the latched

bits 0 through 3 of the digital output port.

Page 20

KPCMCIA-12AI/16AI User’s Manual Theory of Operation 3-5

A/D state machine

The KPCMCIA-12AI/16AI PC card has an internal state machine (Figure 3-1) that controls the

A/D operation.

The state machine defaults to state S0 after power-up or reset. The normal state of flow is first

from S0 to S3, initiated by a scan list (queue) flush command (RSTQ). Then, the queue is

programmed. Thereafter, state machine moves from S3 back to S0. The S3-to-S0 step initiated by

issuing a flush-data FIFO command (RSTF) which sets up the gain and channel selections for

the first channel in the scan list and then waiting for a trigger to start the scan. When the trigger

(ADCLK) comes, the state machine moves from S0 to S1, and the A/D conversion starts once it

moves to S1. The state machine waits at S2 until the conversion is done. At that time, it moves to

S4 where the A/D conversion result is written into the data FIFO. The scan rate is determined by

the time the state machine moves from S1 to S4, which can be set to 10, 20, or 40 µ s. If there are

more channels to scan in the list, the state machine goes to S1 for another conversion loop.

Otherwise, it returns to S0 and waits for another trigger (or a sampling pulse from the pacer clock

if it is in the continuous trigger mode). Any time during data acquisition, an A/D stop command

will clear RUN to zero and eventually stop the data acquisition by moving the state machine back

to S0.

Figure 3-1

State transition diagram of A/D conversion process

~RSTF

~ADCLK*

~RSTQ

S0

RSTF

RSTQ

ADCLK*

~RSTQ

~RUN + 1st

S3

S1

RUN*~1st

Wait A/D

Conversion

S2

~BUSY

S4

BUSY

Page 21

4

I/O Connections

Page 22

4-2 I/O Connections KPCMCIA-12AI/16AI User’s Manual

Cable assembly

The KPCMCIA-12AI/16AI is provided with an 18 in. cable terminating in a 37-pin D-type

female connector as defined in Table 4-1 and Figure 4-1. Also shown is the corresponding PC card

32-pin connector pinout.

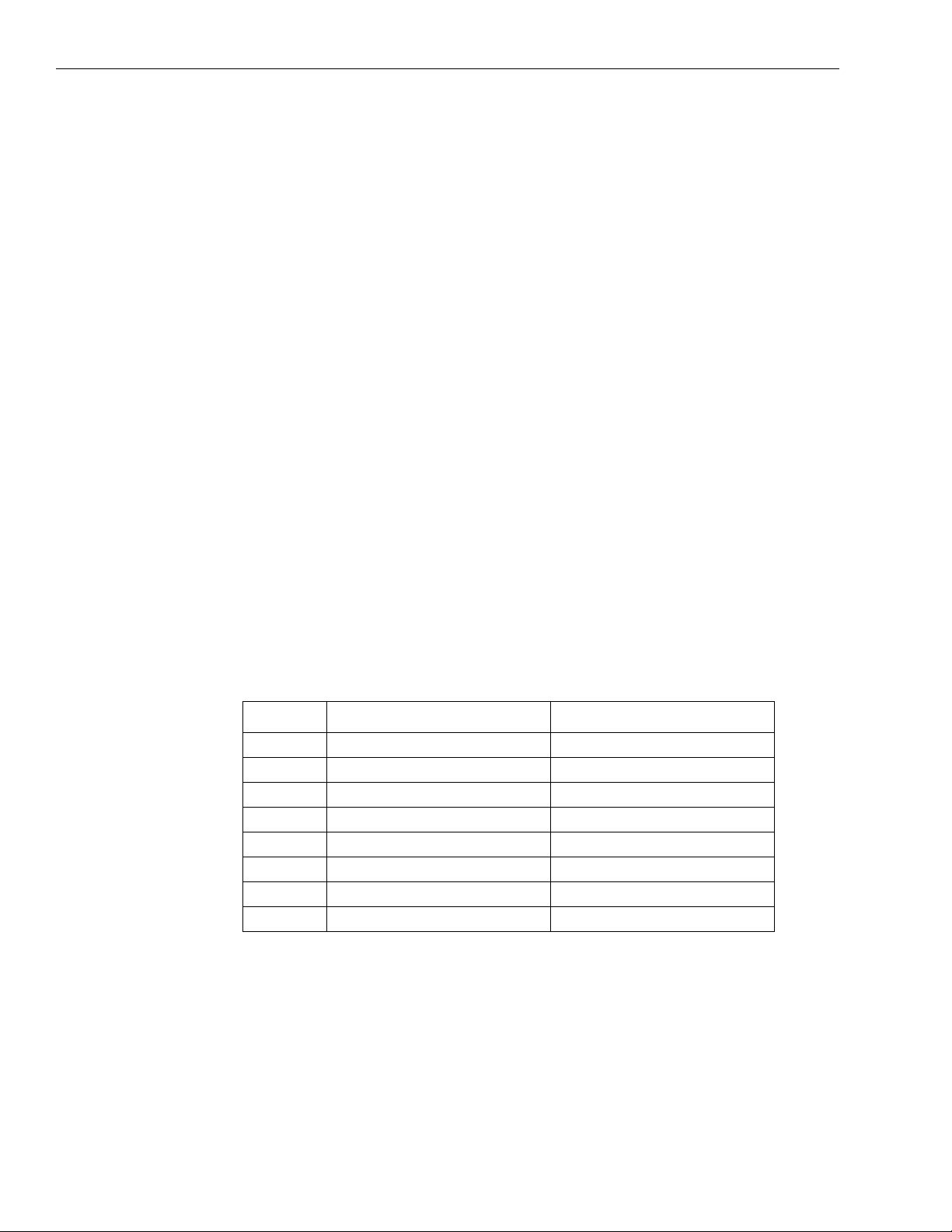

Table 4-1

KPCMCIA-12AI/16AI PC card cable mapping

PC card 32-pin

connector

32 37 Channel 0 (+) Channel 0 A/D input, differential/single-ended

31 18 Channel 0 (-) Channel 8 A/D input, differential/single-ended

30 36 Channel 1 (+) Channel 1 A/D input, differential/single-ended

29 17 Channel 1 (-) Channel 9 A/D input, differential/single-ended

28 35 Channel 2 (+) Channel 2 A/D input, differential/single-ended

27 16 Channel 2 (-) Channel 10 A/D input, differential/single-ended

26 34 Channel 3 (+) Channel 3 A/D input, differential/single-ended

25 15 Channel 3 (-) Channel 11 A/D input, differential/single-ended

24 33 Channel 4 (+) Channel 4 A/D input, differential/single-ended

23 14 Channel 4 (-) Channel 12 A/D input, differential/single-ended

22 32 Channel 5 (+) Channel 5 A/D input, differential/single-ended

21 13 Channel 5 (-) Channel 13 A/D input, differential/single-ended

20 31 Channel 6 (+) Channel 6 A/D input, differential/single-ended

19 12 Channel 6 (-) Channel 14 A/D input, differential/single-ended

18 30 Channel 7 (+) Channel 7 A/D input, differential/single-ended

17 11 Channel 7 (-) Channel 15 A/D input, differential/single-ended

16 29 GND

15 1 Full power (org. D/A 0 ref. in) 1/0 : Full power/Power down

14 26 SSH (org. D/A 1 ref. in) Synchronous sample hold

13 25 Digital in bit 0 (shared) External trigger (same as in DAS-16)

12 6 Digital in bit 1 (normal mode) External gain, LSB (expansion mode)

11 24 Digital in bit 2 (shared) External clock (org. DAS-16 Ctr 0 Gate)

10 5 Digital in bit 3 (normal mode) External gain, MSB (expansion mode)

9 23 Digital out bit 0 (normal mode) External channel bit 0 (expansion mode)

8 4 Digital out bit 1 (normal mode) External channel bit 1 (expansion mode)

7 22 Digital out bit 2 (normal mode) External channel bit 2 (expansion mode)

6 3 Digital out bit 3 (normal mode) External channel bit 3 (expansion mode)

5 7 GND

4 28 GND

3 19 GND

2 19 GND

1 27 Reserved D/A output channel 1

D-37 pin

connector

Name Description

Page 23

KPCMCIA-12AI/16AI User’s Manual I/O Connections 4-3

Figure 4-1

KPCMCIA-12AI/16AI PC card D-37 output connector, KCAB-AI

GND

Ch0- / Ch8

Ch1- / Ch9

Ch2- / Ch10

Ch3- / Ch11

Ch4- / Ch12

Ch5- / Ch13

Ch6- / Ch14

Ch7- / Ch15

N/C

Reserved

N/C

GND

DI1 / GS0

DI3 / GS1

DO1 / CS1

DO3 / CS3

N/C

Full Power

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

37

Ch0+ / Ch0

36

Ch1+ / Ch1

35

Ch2+ / Ch2

34

Ch3+ / Ch3

33

Ch4+ / Ch4

32

Ch5+ / Ch5

31

Ch6+ / Ch6

30

Ch7+ / Ch7

29

GND

28

GND

27

Reserved

26

SSH

25

DI0 / Ext. Trigger, Ext. clock (Paced mode)

24

DI2 / Ext. Clock (Burst mode)

23

DO0 / CS0

22

DO2 / CS2

21

N/C

20

N/C

Page 24

5

Optional Accessories

Page 25

5-2 Optional Accessories KPCMCIA-12AI/16AI User’s Manual

Introduction

This section describes how to attach accessories to the KPCMCIA-12AI/16AI PC card.

Attaching accessories

You can use an STP-37 screw terminal panel or an EXP-1600 expansion accessory with the

KPCMCIA-12AI/16AI PC card. The following paragraphs describe how to attach these

accessories.

Attaching an STP-37 screw terminal panel

The screw terminals on the STP-37 screw terminal panel let you connect field wiring to a

KPCMCIA-12AI/16AI PC card. In addition, the STP-37 contains CJC circuitry for measuring

thermocouple input when interfaced to high gain cards and/or expansion boards.

The STP-37 contains 41 screw terminals. Screw terminals 1 to 37 are used to access KPCMCIA12AI/16AI PC card functions. Note that screw terminal 38 is not used. The three screw terminals

in the screw terminal block labeled P2 are used to access the CJC sensor on the panel.

To attach an STP-37 to a KPCMCIA-12AI/16AI PC card, refer to Figure 5-1 and perform the

following steps:

1. Attach the 32-pin (smaller) end of the KCAB-AI cable to the 32-pin connector on the

KPCMCIA-12AI/16AI PC card.

2. Attach the 37-pin (larger) end of the KCAB-AI cable to the J1 connector on the STP-37.

NOTE The cables are keyed so you only can connect them one way.

Figure 5-1

Attaching an STP-37 screw terminal panel

For CJC sensor

19

20

1

38

KPCMCIA-12AI/16AI

KPCMCIA-12AI/16AI

P2

KCAB-AI

J1

STP-37

Page 26

KPCMCIA-12AI/16AI User’s Manual Optional Accessories 5-3

Attaching an EXP-1600 expansion accessory

Each EXP-1600 expansion accessory provides up to 16 different analog input channels (0 to 15).

Screw terminals are provided on the following removable field wiring accessories:

• FWA-EXP — Attach the FWA-EXP directly to the J1 connector on the EXP-1600; it pro-

vides 48 screw terminals, two screw terminals for each channel (CHxx HI and CHxx LO

where xx is the number of the analog input channel) and 16 screw terminals for miscellaneous functions. Connect one FWA-EXP to each EXP-1600 you are using.

• FWA-37U — Attach the FWA-37U directly to the P4 connector on the EXP-1600; it pro-

vides 40 screw terminals that let you access the other functions of the KPCMCIA-12AI/16AI

PC card. Connect an FWA-37U to the first EXP-1600 only.

To connect an EXP-1600 to a KPCMCIA-12AI/16AI PC card, refer to Figure 5-2 and perform

the following steps:

1. Attach the 32-pin (smaller) end of the KCAB-AI cable to the 32-pin connector on the

KPCMCIA-12AI/16AI PC card.

2. Attach the 37-pin (larger) end of the KCAB-AI cable to the 37-pin end of the CAB-3740/F

cable.

3. Attach the 40-pin end of the CAB-3740/F cable to the P2 connector on EXP-1600.

4. Attach an external +5V power supply (such as the PWR-5V or PWR-5V/E) to one of the

external power connectors on the EXP-1600. The switch signal located on the EXP-1600

board must be set to external (EXT). If you set them to internal (INT), the EXP-1600 will not

function and the KPCMCIA-12AI/16AI PC card may be damaged.

NOTE The cables are keyed so you only can connect them one way.

NOTE EXP-1600 expansion boards have been modified so the current

demand from the KPCMCIA-12AI/16AI is 300nA or less. To resume

proper operation of the PC card, use revision H or later expansion

boards. EXP-1600 boards previous to revision H demand excessive

current from the KPCMCIA-12AI/16AI PC card. Refer to the

EXP-800/1600 User’s Guide for more information.

Figure 5-2

Attaching an EXP-1600 expansion accessory

CAB-3740/F

KCAB-AI

J1

P4

FWA-EXP

FWA-E37U

KPCMCIA-12AI/16AI

KPCMCIA-12AI/16AI

PWR5V

P2

EXP-1600

P3

Page 27

5-4 Optional Accessories KPCMCIA-12AI/16AI User’s Manual

Attaching multiple EXP-1600 expansion accessories

You can attach up to 16 EXP-1600 expansion accessories to provide up to 256 analog input channels by attaching the expansion accessories in a daisy-chain configuration using a CAB-40 or

CAB-40/1 cable.

The first expansion accessory in the daisy chain is associated with on-card channel 0, the next

expansion accessory is associated with on-card channel 1, etc. Specify the associated on-card

channel by setting the jumper on each expansion accessory. Use a unique jumper setting for each

expansion accessory.

You can access any unused on-card channels by attaching an FWA-37U field wiring accessory to

the first EXP-1600 expansion accessory in the daisy-chain configuration.

To attach multiple EXP-1600 expansion accessories to the KPCMCIA-12AI/16AI PC card, refer

to Figure 5-3 and perform the following steps:

1. Connect the first EXP-1600 to the KPCMCIA-12AI/16AI PC card as described in the

previous paragraph. To connect additional EXP-1600 expansion accessories, attach one end

of the CAB-40 (4 in. long) or CAB-40/1 (18 in. long) cable to either the P2 or P3 connector

on the previous expansion accessory and attach the other end of the cable to either the P2 or

P3 connector on the next expansion accessory in the chain. Note that P2 and P3 are identical

connectors.

2. Attach +5V power to all the EXP-1600 expansion accessories. If desired, you can connect

multiple EXP-1600s to a single PWR-5V or PWR-5V/E power supply using CAB-PWR or

CAB-PWR/1 cables; attach one end of a CAB-PWR or CAB-PWR/1 cable to the unused

power connector on the first expansion accessory and the other end of the cable to either

power connector on the next expansion accessory in the chain. Note that the two power connectors are identical.

Figure 5-3

Attaching multiple EXP-1600 expansion accessories

KCAB-AI

KPCMCIA-12AI/16AI

KPCMCIA-12AI/16AI

PWR-5V

CAB-3740/F

EXP-1600

CAB-40

CAB-PWR

FWA-EXP

FWA-37U

EXP-1600

CAB-40

CAB-PWR

FWA-EXP

FWA-EXP

EXP-1600

Page 28

A

Specifications

Page 29

µ

A-2 Specifications KPCMCIA-12AI/16AI User’s Manual

A/D converter 12-Bit version 16-Bit version

Acquisition + conversion 2 µ s + 8 µ s2

Monotonicity No missing codes No missing codes

Integral linearity error ±1 LSB ±3 LSB

Differential linearity error ±1 LSB +3/-2 LSB

Full-scale error ±0.5% ±0.5%

Aperture delay 40ns 40ns

Analog input

Number of input channels Eight differential/16 single-ended, expandable to 256

Input range ±10, ±5, ±2.5, ±1.25V

Programmable gain 1, 2, 4, 8

Maximum overvoltage ±30V

Input impedance 100M Ω (DC)

A/D miscellaneous specifications

Data FIFO depth 2048 samples

Scan list length 2048 entries

Scan speed 10 µ s, 20 µ s, 40 µ s

Trigger source Internal (software)/External (TTL)

Trigger mode Continuous/One-shot

External (TTL) trigger* 0.8V (low)/2.2V (high), rising/falling edges

Latency to A/D scan < 1 µ s

Sampling Rate 0.006Hz to 100kHz (with internal clock source)

External clock rate* DC-5MHz

*NOTE In “Paced” mode, the same input pin is shared between external clock and exter-

nal trigger, therefore only one function can be used (not both simultaneously).

s + 8 µ s

Digital I/O

Digital input channels 4 (no latch)

Digital output channels 4 (latched)

Maximum source current 0.5mA

Maximum sinking current 2.5mA

Minimum logic 1 level 2.4V

Maximum logic 0 level 0.8V

General specifications

Power consumption 160mA (full power), 40mA (power down)

Operating temperature 0˚ to 50˚C

Storage temperature 0˚ to 70˚C

Humidity 0˚ to 95%, non-condensing

Size (cable not included) Standard PCMCIA type II

Weight 1.5 oz (for reference only)

Page 30

B

PCMCIA Interface

Page 31

B-2 PCMCIA Interface KPCMCIA-12AI/16AI User’s Manual

NOTE A typical user of this manual does not need to read the material in this

section. If you write a custom program, write it to work through

DriverLINX, using the many interface and support features of

DriverLINX. Register-level programming of the card is not

recommended. This section is provided only for an advanced

programmer who must write a specialized driver.

Introduction

Information in this section is provided for those who need low-level PCMCIA interface details to

the KPCMCIA-12AI/16AI PC card. The client driver or the enabler that comes with the PC card

is sufficient for most applications.

The KPCMCIA-12AI/16AI PC card performs data acquisition for all host computers equipped

with a version 2.1 compliant PCMCIA interface. The PC card, a name given to all PCMCIA

interface cards, has a form factor of type II (5mm thick).

Due to the PCMCIA interface, the PC card is highly flexible with respect to addressing and interrupt level use. It can be configured either as a memory only interface or as an I/O interface and

can be powered up or down with the help of the PCMCIA card and socket services software. The

KPCMCIA-12AI/16AI PC card provides a single interrupt that can be routed to any system interrupt via the PCMCIA socket controller.

There are two sets of registers on the KPCMCIA-12AI/16AI PC card: the configuration registers

and program registers.

The configuration registers are those as defined in the PCMCIA 2.1 specification. The PCMCIA

configuration registers are located in the PC card’s configuration space at offset 8000H. Configuration space also contains the Card Information Structure (CIS). This memory is located at offset

0000H in the configuration space. The CIS memory contains information about the PC card as

defined by the PCMCIA 2.1 specification. Using the standard card and socket services software

is the recommended method for setting up the configuration and power-up/down control of the

PC card even though an enabler can be used.

Program registers are the registers that fall under program control and belong to the KPCMCIA12AI/16AI PC card. The I/O location of these registers are controlled by the PCMCIA socket configuration and by the contents of the PCMCIA configuration registers. Refer to Appendix C for

more information.

Two PCMCIA configuration registers are supported by the KPCMCIA-12AI/16AI PC card: the

Configuration Option Register (COR) and the Card Configuration and Status Register (CCSR),

as shown in Table B-1.

Table B-1

PCMCIA configuration registers

Offset Access Description

0x8000 R/W Configuration option register

0x8002 R/W Card configuration and status register

Page 32

KPCMCIA-12AI/16AI User’s Manual PCMCIA Interface B-3

Configuration and option register (COR)

Refer to Table B-2. Bits 7 and 6 of the COR are defined by the PCMCIA standard as the SRESET

and the LevlREQ bits. A 1 written into the SRESET bit puts the card into a reset state, while a 0

moves it out of the reset state. When the card is in the reset state, it behaves as if a hardware reset

is received from the host. The LevlREQ bit controls the type of interrupt signal generated by the

PC card. Setting the configuration index bits to 0 makes the PC card a memory only card

(accessed only by memory read/write operations), while setting the bits to 1 makes the card a

standard I/O card.

Table B-2

COR bit definitions

Bit Name Description

7 SRESET 1 = Put the card into reset state

0 = Get out of reset state

6 LevlREQ 1 = Level mode interrupt

0 = Edge mode interrupt

5-0 Index Bits 000000 = Memory mode

000001 = I/O mode

Card configuration and status register (CCSR)

Refer to Table B-3. The KPCMCIA-12AI/16AI PC card uses two bits in this register. When bit 1

is set to 1, it indicates a pending interrupt. The bit remains as 1 until the software clears the interrupt source. Bit 2 is used for power-down control. Setting this bit to 1 puts the card into powerdown mode, while a 0 brings it back to full-powered mode. The rest of the bits are not used.

Table B-3

CCSR bit definitions

Bit Name Description

7-3 Not used Reserved, all 0 when writing and reading

2 PwrDwn 1 = Power-down mode

0 = Full-powered mode

1 Intr 1 = Interrupt pending

0 = No interrupt pending

0 Reserved Reserved as 0

The first S0-S3-S0 trip must be followed as described above. These two commands to the PC card

must be issued: the flush scan list command (RSTQ) and then the flush data FIFO command

(RSTF). The scan list is programmed after the RSTQ command and before the RSTF command.

Once the flush data FIFO command is issued, the PC card prepares the first channel in the scan

list, and then returns to state S0 to wait for the first trigger. This setup guarantees that the scan list

and the data FIFO are flushed properly for the expected data acquisition.

NOTE Any time the data FIFO is flushed, the default threshold setting will be

restored (7 bytes to full) by the hardware. Always program the data

FIFO threshold after the flushing if the required threshold is different

from the default.

Page 33

C

I/O Registers

Page 34

C-2 I/O Registers KPCMCIA-12AI/16AI User’s Manual

NOTE A typical user of this manual does not need to read the material in this

section. If you write a custom program, write it to work through

DriverLINX, using the many interface and support features of

DriverLINX. Register-level programming of the card is not

recommended. This section is provided only for an advanced

programmer who must write a specialized driver.

Introduction

The KPCMCIA-12AI/16AI PC card uses eight consecutive I/O locations within the system

I/O address space. The eight I/O locations used by the PC card are summarized in Table C-1.

Table C-1

KPCMCIA-12AI/16AI PC card register map

Address lines

(A2A1A0) I/O address Port access Register description

000 base + 0 Read/Write Data FIFO

001 base + 1 Write only Scan list (queue)

010 base + 2 Write

Read

011 base + 3 Write

Read

100 base + 4 Write only Pacer clock, low byte

101 base + 5 Write only Pacer clock, middle byte

110 base + 6 Write only Pacer clock, high byte

111 base + 7 Write only Auxiliary control register

Control register

Status register

Digital output register

Digital input register

All registers are 8-bit wide. Each register is discussed in detail in the following paragraphs.

Data FIFO register (base + 0)

The data FIFO register is the access port to the data FIFO, which can hold up to 2048 data words

of the A/D conversion result. The port is also used to program the data FIFO thresholds, as

explained later in this section.

NOTE Although the data FIFO register is 8-bit wide, the register must be

accessed as a 16-bit word to guarantee integrity. The low byte (LSB,

or the least significant byte) should always be accessed first followed

by the high byte (MSB, or the most significant byte).

Two consecutive bytes should be read from (written into) the port each time it is accessed.

Table C-2 illustrates the bit allocation.

Table C-2

Data FIFO register bit allocation

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

LSB

MSB

D7 D6 D5 D4 D3 D2 D1 D0

D15 D14 D13 D12 D11 D10 D9 D8

Page 35

KPCMCIA-12AI/16AI User’s Manual I/O Registers C-3

Data FIFO operation modes

Depending on the mode of operation, the 16-bit word read from or written into the register has

different meanings, as described in Table C-3.

Table C-3

Data FIFO operation mode

Mode Selection bit A/D Access Operation

0 0, threshold Idle Read

Write

1 1, data FIFO Idle Read

Write

2 0, threshold Run Read

Write

3 1, data FIFO Run Read

Write

The selection bit is also called the program/access control bit, as defined in the auxiliary control

register (base + 7). Refer to “Auxiliary control register (base + 7, write only)” for more information about setting the bit and issuing commands to change the status of the A/D conversion (from

scan to idle or vice versa).

Mode 0 is the FIFO program mode under which the two consecutive words (four bytes) written

into the register address set the almost-full and almost-empty thresholds (in bytes). The first word

specifies the almost-empty threshold (not used; can be set to anything), while the second word

determines the almost-full threshold. The threshold should be set to a value from 1 to FIFO size

minus 1 (default is 7 when reset or power up). Refer to Table C-4.

Table C-4

Data FIFO threshold setting

Threshold Default Threshold range Suggested value

Verify data FIFO threshold

Program data FIFO threshold

Read data FIFO

Write data FIFO (diagnosis)

Verify data FIFO threshold

Not allowed

Read data FIFO

Not allowed

Almost empty 7 Irrelevant Irrelevant

Almost full 7 1..4095 bytes 2048 bytes

Mode 1 is the FIFO test mode in which the data bytes are written into the data FIFO and read back

from it. The FIFO flags change according to the data bytes available in the data FIFO and the configured threshold. Refer to “Status register (base + 2, read)” for information about the FIFO

empty, almost-full, and full flags.

Mode 2 should be avoided. The data bytes cannot be written into the FIFO under this mode. The

bytes read from the FIFO will be the same as in mode 0.

Mode 3 is the data transfer mode. Data bytes are written into the FIFO by the A/D converter, while

the data byte read from the address is the first available byte in the data FIFO if it is not empty.

Otherwise, the most recent byte written into the FIFO will be returned. The data FIFO register is

read-only under this mode; i.e., you cannot write data bytes into the data FIFO through I/O

instructions.

Page 36

C-4 I/O Registers KPCMCIA-12AI/16AI User’s Manual

Mode setting

The FIFO operation mode setting is always initiated with the data FIFO flush command refer to

“Auxiliary control register (base + 7, write only” with the access/program bit set to 0 (bit 0 at

base + 7) before the data acquisition is started. This setting brings it to mode 0 (threshold setting

mode). After the threshold is programmed or verified, set the bit to 1 so the following read/write

operation to the FIFO is the data access operation.

The KPCMCIA-12AI/16AI PC card is in idle mode before it is triggered into the run mode. For

one-shot operation, the PC card is set to run mode after it receives the trigger signal. It does not

return to the idle mode until the specified scan list is completed or an A/D stop command is

received. Refer to “Stop A/D command” for more information. For continuous trigger operation,

the PC card will stay in run mode after being triggered until an A/D stop command is received.

FIFO flags

When reading the register under mode 1 or 3, the first available data byte from the data FIFO is

returned if it is not empty. Otherwise, the returned byte is not defined. The FIFO empty flag will

be set immediately after the last byte is read from the FIFO, while the FIFO full flag will be

cleared after reading the data FIFO register provided there are no more data bytes written into the

FIFO by the A/D converter under mode 1 or 3. The same happens to the FIFO almost-full flag if

the data bytes available in the FIFO are less than the almost-full threshold. Refer to Table C-5. In

the first column of Table C-5, threshold is the almost-full threshold as explained before, and FIFO

size is measured in bytes, 4096.

Table C-5

Data FIFO flag status

Data bytes in FIFO Empty Almost full Full

0 True False False

1 to (Threshold - 1) False False False

Threshold to (FIFO size - 1) False True False

FIFO size (4096 bytes)* False True True

* 2048 samples/data words.

Page 37

KPCMCIA-12AI/16AI User’s Manual I/O Registers C-5

Scan list queue register (base + 1, write only)

The scan list queue register is the access port to the scan list queue, which can hold up to 2048

entries (each has two bytes). Each entry specifies an analog input channel and its associated gain

as well as other settings.

NOTE Although the scan list queue register is eight bits wide, the register

must be accessed as a 16-bit word to guarantee integrity. The low byte

(LSB, or the least significant byte) should always be accessed first followed by the high byte (MSB, or the most significant byte).

The bit definitions of entries to the scan list queue are explained in Table C-6.

Table C-6

Scan list queue entry bit definitions

Bit Byte Definition Explanation

15 MSB Reserved as 0

14 MSB Analog input mode 1/0 : differential/single-ended

13-12 MSB Internal gain selection 00/01/10/11 : 1/2/4/8

11-8 MSB Internal channel selection 0000..1111 : channel 0..15

7 LSB Starting channel mark Set to 1 for the first entry in the list

Set to 0 for all the rest entries

6 LSB Reserved for expansion cards (as SSH)

5-4 LSB External gain selection 00/01/10/11 : 1/2/4/8 (or 1/10/100/1000)

3-0 LSB External channel selection 0000..1111 : channel 0..15

Scan list queue programming

The scan list queue must be programmed when the KPCMCIA-12AI/16AI PC card is idle. Each

queue entry contains two bytes as described previously. The integrity of the entry must be guaranteed. The scan list queue is write only.

The scan list queue should be flushed before writing any entries into it. Refer to “Auxiliary control

register (base + 7, write only)” for scan list queue reset information.

The first entry of the queue should have bit 7 (LSB) set to 1 as the first channel mark. All the rest

of the entries, if any, should have the bit set to 0.

The synchronous sample hold bit (LSB) is not used by the PC card. It is reserved for the expansion cards.

Page 38

C-6 I/O Registers KPCMCIA-12AI/16AI User’s Manual

Example 1

In Table C-7, the following entries to the queue specify a scan list of three single-ended internal

channels, 0, 12, and 7, with a gain of 2 for channel 0 and a gain of 4 for channel 12 and 7.

Table C-7

Scan list queue programming example 1

Entry Binary Hex Explanation

1 0001 0000 1000 0000 0180 Select channel 0, gain 2, first entry

2 0010 1100 0000 0000 2C00 Select channel 12, gain 4

3 0010 0111 0000 0000 2700 Select channel 7, gain 4

Example 2

In Table C-8, the following entries to the queue specify a scan list of four differential internal

channels, 2, 1, 6, and 7, with a gain of 1 for all the channels.

Table C-8

Scan list queue programming example 2

Entry Binary Hex Explanation

1 0100 0010 1000 0000 4280 Select channel 2, gain 1, first entry

2 0100 0001 0000 0000 4100 Select channel 1, gain 1

3 0100 0110 0000 0000 4600 Select channel 6, gain 1

4 0100 0111 0000 0000 4700 Select channel 7, gain 1

Channel configuration

Bits 5 and 4 (LSB) in a queue entry specify the gain on the external expansion card for the external

channel selected by bits 3 through 0 of the same byte. Each expansion card has up to 16 channels

(0, 1, 2, ..., 15). Each channel may have a gain of 1, 2, 4, or 8 if it is a low gain expansion card or

1, 10, 100, or 1000 if it is a high gain expansion card.

If there is no expansion card for the specified internal channel, the external channel and gain

selection in the LSB is ignored. However, the first channel mark on bit 7 should always be set

properly.

The internal channel is selected by bits 8 through 11 (MSB), while the internal gain for the

selected channel is specified by bit 12 and 13 (MSB). The internal gain can only be 1, 2, 4, or 8.

Bit 14 (MSB) determines whether the input is differential (1) or single-ended (0). There are 16

singled-ended channels but only eight differential channels. This bit should always be set to 0 if

the selected internal channel is connected to an expansion card because the output from the

expansion cards is always single-ended.

Bit 15 (MSB) is not used by the KPCMCIA-12AI/16AI PC card. It should be set to 0.

Page 39

KPCMCIA-12AI/16AI User’s Manual I/O Registers C-7

Analog input offset correction

The input to the A/D converter will be shorted to ground if bit 14 (MSB) is set to 1 while the internal channel selection of bits 8 through 11 specifies internal channel 8 or above. This can be used

for analog input offset correction.

Control register (base + 2, write)

The control register specifies the pacer clock source and pre-scaler, the expansion mode, interrupt

enable control, and the trigger control as shown in Table C-9.

Table C-9

Control register bit definitions

Bit Function Explanation

7-6 Pacer clock source and pre-scaler 00 : External clock

01 : Internal, 5MHz

10 : Internal, 1MHz

11 : Internal, 100kHz

5 Expansion mode 0/1 : disable/enable

4 EOS interrupt 0/1 : disable/enable

3 FIFO interrupt 0/1 : disable/enable

2 Trigger mode 0/1 : one-shot/continuous

1 Trigger source 0/1 : internal/external

0 Trigger edge 0/1 : rising/falling

Clock source

The external clock source, if selected, must not exceed 5MHz with a minimum pulse width of

200ns. The external clock frequency can be as low as DC, and there is no limit on maximum pulse

width.

Expansion mode

Bit 5 has to be set to 1 if there is one (or more) expansion cards connected to the KPCMCIA12AI/16AI PC card. This setting also means that all the digital output lines (bits 0 to 3) will be

used for external channel selection and two of the four digital input lines (bits 1 and 3) will be

used for external gain selection.

Interrupt enable

Bits 4 and 3 are used for interrupt enable control. The end-of-scan (EOS) interrupt is enabled (disabled) by setting bit 4 to 1 (0). Setting bit 3 to 1 (0) enables (disables) the data FIFO interrupt

when the A/D data FIFO becomes almost full (data available in the FIFO passes the almost-full

threshold). Since the EOS and FIFO threshold events are latched into the status register, temporarily disabling the interrupt and then enabling it will not lose an interrupt as long as no repeated

events occur during the time the interrupt is disabled.

Page 40

C-8 I/O Registers KPCMCIA-12AI/16AI User’s Manual

Trigger mode