Page 1

PDMA-16 Parallel Digital Interface Board

User Guide

A GREATER MEASURE OF CONFIDENCE

Page 2

WARRANTY

Hardware

Keithley Instruments, Inc. warrants that, for a period of one (1) year from the date of shipment (3 years for Models 2000, 2001, 2002, 2010 and 2700), the

Keithley Hardware product will be free from defects in materials or workmanship. This warranty will be honored provided the defect has not been caused

by use of the Keithley Hardware not in accordance with the instructions for the product. This warranty shall be null and void upon: (1) any modification of

Keithley Hardware that is made by other than Keithley and not approved in writing by Keithley or (2) operation of the Keithley Hardware outside of the

environmental specifications therefore.

Upon receiving notification of a defect in the Keithley Hardware during the warranty period, Keithley will, at its option, either repair or replace such Keithley Hardware. During the first ninety days of the warranty period, Keithley will, at its option, supply the necessary on site labor to return the product to the condition prior to

the notification of a defect. Failure to notify Keithley of a defect during the warranty shall relieve Keithley of its obligations and liabilities under this warranty.

Other Hardware

The portion of the product that is not manufactured by Keithley (Other Hardware) shall not be covered by this warranty, and Keithley shall have no duty of

obligation to enforce any manufacturers' warranties on behalf of the customer. On those other manufacturers’ products that Keithley purchases for resale,

Keithley shall have no duty of obligation to enforce any manufacturers’ warranties on behalf of the customer.

Software

Keithley warrants that for a period of one (1) year from date of shipment, the Keithley produced portion of the software or firmware (Keithley Software) will

conform in all material respects with the published specifications provided such Keithley Software is used on the product for which it is intended and otherwise in accordance with the instructions therefore. Keithley does not warrant that operation of the Keithley Software will be uninterrupted or error-free and/

or that the Keithley Software will be adequate for the customer's intended application and/or use. This warranty shall be null and void upon any modification

of the Keithley Software that is made by other than Keithley and not approved in writing by Keithley.

If Keithley receives notification of a Keithley Software nonconformity that is covered by this warranty during the warranty period, Keithley will review the

conditions described in such notice. Such notice must state the published specification(s) to which the Keithley Software fails to conform and the manner

in which the Keithley Software fails to conform to such published specification(s) with sufficient specificity to permit Keithley to correct such nonconformity. If Keithley determines that the Keithley Software does not conform with the published specifications, Keithley will, at its option, provide either the

programming services necessary to correct such nonconformity or develop a program change to bypass such nonconformity in the Keithley Software.

Failure to notify Keithley of a nonconformity during the warranty shall relieve Keithley of its obligations and liabilities under this warranty.

Other Software

OEM software that is not produced by Keithley (Other Software) shall not be covered by this warranty, and Keithley shall have no duty or obligation to

enforce any OEM's warranties on behalf of the customer.

Other Items

Keithley warrants the following items for 90 days from the date of shipment: probes, cables, rechargeable batteries, diskettes, and documentation.

Items not Covered under Warranty

This warranty does not apply to fuses, non-rechargeable batteries, damage from battery leakage, or problems arising from normal wear or failure to follow

instructions.

Limitation of Warranty

This warranty does not apply to defects resulting from product modification made by Purchaser without Keithley's express written consent, or by misuse

of any product or part.

Disclaimer of Warranties

EXCEPT FOR THE EXPRESS WARRANTIES ABOVE KEITHLEY DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION, ALL IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEITHLEY DISCLAIMS ALL WARRANTIES WITH RESPECT TO THE OTHER HARDWARE AND OTHER SOFTWARE.

Limitation of Liability

KEITHLEY INSTRUMENTS SHALL IN NO EVENT, REGARDLESS OF CAUSE, ASSUME RESPONSIBILITY FOR OR BE LIABLE FOR: (1)

ECONOMICAL, INCIDENTAL, CONSEQUENTIAL, INDIRECT, SPECIAL, PUNITIVE OR EXEMPLARY DAMAGES, WHETHER CLAIMED

UNDER CONTRACT, TORT OR ANY OTHER LEGAL THEORY, (2) LOSS OF OR DAMAGE TO THE CUSTOMER'S DATA OR PROGRAMMING, OR (3) PENALTIES OR PENALTY CLAUSES OF ANY DESCRIPTION OR INDEMNIFICATION OF THE CUSTOMER OR OTHERS FOR

COSTS, DAMAGES, OR EXPENSES RELATED TO THE GOODS OR SERVICES PROVIDED UNDER THIS WARRANTY.

Keithley Instruments, Inc. 28775 Aurora Road • Cleveland, Ohio 44139 • 440-248-0400 • Fax: 440-248-6168

1-888-KEITHLEY (534-8453) • www.keithley.com

Sales Offices:BELGIUM: Bergensesteenweg 709 • B-1600 Sint-Pieters-Leeuw • 02-363 00 40 • Fax: 02/363 00 64

CHINA: Yuan Chen Xin Building, Room 705 • 12 Yumin Road, Dewai, Madian • Beijing 100029 • 8610-6202-2886 • Fax: 8610-6202-2892

FINLAND: Tietäjäntie 2 • 02130 Espoo • Phone: 09-54 75 08 10 • Fax: 09-25 10 51 00

FRANCE: 3, allée des Garays • 91127 Palaiseau Cédex • 01-64 53 20 20 • Fax: 01-60 11 77 26

GERMANY: Landsberger Strasse 65 • 82110 Germering • 089/84 93 07-40 • Fax: 089/84 93 07-34

GREAT BRITAIN: Unit 2 Commerce Park, Brunel Road • Theale • Berkshire RG7 4AB • 0118 929 7500 • Fax: 0118 929 7519

INDIA: Flat 2B, Willocrissa • 14, Rest House Crescent • Bangalore 560 001 • 91-80-509-1320/21 • Fax: 91-80-509-1322

ITALY: Viale San Gimignano, 38 • 20146 Milano • 02-48 39 16 01 • Fax: 02-48 30 22 74

JAPAN: New Pier Takeshiba North Tower 13F • 11-1, Kaigan 1-chome • Minato-ku, Tokyo 105-0022 • 81-3-5733-7555 • Fax: 81-3-5733-7556

KOREA: 2FL., URI Building • 2-14 Yangjae-Dong • Seocho-Gu, Seoul 137-888 • 82-2-574-7778 • Fax: 82-2-574-7838

NETHERLANDS: Postbus 559 • 4200 AN Gorinchem • 0183-635333 • Fax: 0183-630821

SWEDEN: c/o Regus Business Centre • Frosundaviks Allé 15, 4tr • 169 70 Solna • 08-509 04 679 • Fax: 08-655 26 10

SWITZERLAND: Kriesbachstrasse 4 • 8600 Dübendorf • 01-821 94 44 • Fax: 01-820 30 81

TAIWAN: 1FL., 85 Po Ai Street • Hsinchu, Taiwan, R.O.C. • 886-3-572-9077• Fax: 886-3-572-9031

4/02

Page 3

PDMA-I

6

Parallel Digital Interface Board

User Guide

Keithley Instruments, Inc.

Aurora Road, Cleveland,

28775

Technical

Monday ~ Friday

Support:

Fax:

http://www.keithle yxom

1-888-KEITHLEY

8:OO

a.m.

(440)

248-6168

to

OH

5:OO

44139

p.m.

(EST)

Q

1986

Keithley

All

Cleveland,

Second

[hruiiient

righls

Ohio,

Prinling,

Number:

Instruments,

reservad.

U

S.A.

Jdnuilry

1992

24885

Inc.

Rev.

B

Page 4

BasicLM

IBM"

is

PC,

XT,

is a trademark

of

Dartmouth College.

a registered trademark

AT,

PS/2,

and Micro Channel Architecture@

of

International Business Machines Corporation

arc tradcrnarks

of

Intcrnational Busincss Machincs Corporation.

Microsofta

Turbo

Tnirxnialion

is a registered trademark

C"

IS

a

registered trademark

1-ui-nished

hy

Keithley

assumes no responsihility for

that

partics

may result from

Keithley Instruments.

Keithley Instruments assumes no responsibility for damages consequent to

the use

of

this product. This product is not designed with components of

reliability suitable for use in life support

the

its

use

usc.

ol'

Microsol'L Corporation.

ot

Borland International

Inslrumenls

of

such information nor for any infringements

No

liccnsc

is believed

is

granted

to

be accurale

by

implication or otherwise under any patcnt rights

WARNING

or

critical applications.

and

reliahle. However, Keilhley

of

patents or other rights of third

a

level

Instrurnenls

of

of

Page 5

Safety Precautions

The following safety precautions should be observed before using

this product and any associated instrumentation. Although some instruments and accessories would normally be used with non-hazardous voltages, there are situations where hazardous conditions

may be present.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. Read and follow all installation,

operation, and maintenance information carefully before using the

product. Refer to the manual for complete product specifications.

If the product is used in a manner not specified, the protection provided by the product may be impaired.

The types of product users are:

Responsible body is the individual or group responsible for the use

and maintenance of equipment, for ensuring that the equipment is

operated within its specifications and operating limits, and for ensuring that operators are adequately trained.

Operators use the product for its intended function. They must be

trained in electrical safety procedures and proper use of the instrument. They must be protected from electric shock and contact with

hazardous live circuits.

Maintenance personnel perform routine procedures on the product

to keep it operating properly, for example, setting the line voltage

or replacing consumable materials. Maintenance procedures are described in the manual. The procedures explicitly state if the operator

may perform them. Otherwise, they should be performed only by

service personnel.

Service personnel are trained to work on live circuits, and perform

safe installations and repairs of products. Only properly trained service personnel may perform installation and service procedures.

Keithley products are designed for use with electrical signals that

are rated Installation Category I and Installation Category II, as described in the International Electrotechnical Commission (IEC)

Standard IEC 60664. Most measurement, control, and data I/O signals are Installation Category I and must not be directly connected

to mains voltage or to voltage sources with high transient over-voltages. Installation Category II connections require protection for

high transient over-voltages often associated with local AC mains

connections. Assume all measurement, control, and data I/O connections are for connection to Category I sources unless otherwise

marked or described in the Manual.

Exercise extreme caution when a shock hazard is present. Lethal

voltage may be present on cable connector jacks or test fixtures. The

American National Standards Institute (ANSI) states that a shock

hazard exists when voltage levels greater than 30V RMS, 42.4V

peak, or 60VDC are present. A good safety practice is to expect

that hazardous voltage is present in any unknown circuit before

measuring.

Operators of this product must be protected from electric shock at

all times. The responsible body must ensure that operators are prevented access and/or insulated from every connection point. In

some cases, connections must be exposed to potential human contact. Product operators in these circumstances must be trained to

protect themselves from the risk of electric shock. If the circuit is

capable of operating at or above 1000 volts, no conductive part of

the circuit may be exposed.

Do not connect switching cards directly to unlimited power circuits.

They are intended to be used with impedance limited sources.

NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to limit fault current and voltage to the card.

Before operating an instrument, make sure the line cord is connected to a properly grounded power receptacle. Inspect the connecting

cables, test leads, and jumpers for possible wear, cracks, or breaks

before each use.

When installing equipment where access to the main power cord is

restricted, such as rack mounting, a separate main input power disconnect device must be provided, in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any

other instruments while power is applied to the circuit under test.

ALWAYS remove power from the entire test system and discharge

any capacitors before: connecting or disconnecting cables or jumpers, installing or removing switching cards, or making internal

changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always

make measurements with dry hands while standing on a dry, insulated

surface capable of withstanding the voltage being measured.

The instrument and accessories must be used in accordance with its

specifications and operating instructions or the safety of the equipment may be impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating information, and as shown on the instrument or test fixture panels, or

switching card.

When fuses are used in a product, replace with same type and rating

for continued protection against fire hazard.

Chassis connections must only be used as shield connections for

measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use of a

lid interlock.

5/02

Page 6

If or is present, connect it to safety earth ground using the

wire recommended in the user documentation.

!

The symbol on an instrument indicates that the user should refer to the operating instructions located in the manual.

The symbol on an instrument shows that it can source or measure 1000 volts or more, including the combined effect of normal

and common mode voltages. Use standard safety precautions to

avoid personal contact with these voltages.

The WARNING heading in a manual explains dangers that might

result in personal injury or death. Always read the associated information very carefully before performing the indicated procedure.

The CAUTION heading in a manual explains hazards that could

damage the instrument. Such damage may invalidate the warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and

all test cables.

To maintain protection from electric shock and fire, replacement

components in mains circuits, including the power transformer, test

leads, and input jacks, must be purchased from Keithley Instruments. Standard fuses, with applicable national safety approvals,

may be used if the rating and type are the same. Other components

that are not safety related may be purchased from other suppliers as

long as they are equivalent to the original component. (Note that selected parts should be purchased only through Keithley Instruments

to maintain accuracy and functionality of the product.) If you are

unsure about the applicability of a replacement component, call a

Keithley Instruments office for information.

To clean an instrument, use a damp cloth or mild, water based

cleaner. Clean the exterior of the instrument only. Do not apply

cleaner directly to the instrument or allow liquids to enter or spill

on the instrument. Products that consist of a circuit board with no

case or chassis (e.g., data acquisition board for installation into a

computer) should never require cleaning if handled according to instructions. If the board becomes contaminated and operation is affected, the board should be returned to the factory for proper

cleaning/servicing.

Page 7

~

....

CHAPTER

1

:

INTRODUCTION

Contents

1.1 General Description

1.2 Applications

1.3 Features

1.4 Accessories

CHAPTER

CHAPTER

2:

INSTALLATtON

2.1 Unpacking

2.2 Backing

2.3 Base Address Switch

2.4 Other Settings

2.5

2.6 3oard Installation

3.1

3.2 Ports A

3.3

3.4 Interrupt Control Register

3.5

I/O

Connector

3:

REGISTER STRUCTURES

I/O

Map

DMA Control Register

8254 Timer

.......................................

.........................................

.......................................

&

Inspecting

Up

Distribution Software

.........................................

&

B

.......................................

.......................................

...................................

................................

...........................

..................................

......................................

.....................................

....................................

.................................

................................

1.1

1.1

1.1

1.2

2.1

2.1

2.2

2.3

-2-4

2.5

3.1

3.1

3.2

3.3

3.3

CHAPTER

CHAPTER

4:

PROGRAMMING

4.1 The PDMA-16 Call Modes

4.2 Programming In BASlCA

Loading The Machine Language CALL Routine PDMAl6.BIN

Format

Execution Times

4.3 Programming In QuickBASIC

Loading The Program

Declaring The Driver

Format

Making Executable Programs

5:

THE

MODE

5.1

5.2

5.3

5.4

5.5

5.6

5.7

5.8

5.9

5.10

5.11

Overview

MODE

MODE 1

MODE 2: Return Status

MODE

MODE 4: Digital Output

MODE

MODE

MODE

MODE

MODE 9: Allocate Memory For DMA

0:

:

3:

5:

6:

7:

8:

FOR

Of

The CALL Statement

Of

The Call Statement

CALLS

........................................

Initialize The PDMA-16 Driver & Check Hardware

Set

Up

&

Set Timer Rate

Digital Input

Auxiliary Output

Setup & Interrupt Enable

Disable Interrupt

THE CALL

MODES

IN BASICA & QUICKBASIC

...............................

................................

..........

..........................

.

Compiled BASIC

........................

.............................

................................

...............................

...........................

...........................

............

Perform DMA Transfer

......................

................................

...............................

................................

.................................

...............................

.........................

..............................

........................

4.1

4.1

4.1

4.3

4.4

4.4

4.4

-4-5

4.5

4.7

5.1

5-1

5.2

5.5

5.6

5-7

5-8

5-9

5-10

5-12

5-13

-v-

Page 8

Con

tents

5.12 MODE

5.13

5.14

CHAPTER

6.1 The

6.2

CHAPTER

7.1 Typical Handshake Connection

7.2

7.3 High Speed

7.4

CHAPTER

8.1 Senrice & Repair.

8.2

MODE 11

MODE

6:

PROGRAMMABLE INTERVAL

Reading & Loading

7:

APPLICATIONS

Waveform Generation

Combined

8:

MAINTENANCE & REPAIR

Performing Your Own Repairs

10:

Deallocate Memory Segment

:

Move Data From Source

12:

Disable DMA

8254

Programmable Interval

The

AID

Conversion

A/D

8t

D/A Conversion Using Directional Controls

...................................

.....................

To

Destination.

..............................

TIMER

Timer

Counters.

............................

With

a D/A Converter.

.............................

............................

.......................

..........................

....................

...............

............

5-14

5-14

5-15

6-1

6-3

7-1

7-2

7-3

7-4

8-1

8-1

APPENDICES

A

Appendix

Appendix

Appendix C Understanding DMA

Appendix D Modes

Appendix

Appendix F PDMA-16 PCF

Specifications

B

Summary

9

E

Storage

Of

Error Codes

i3

10:

AllocatelDeallocate

of

Integer Variables

DMA

...

Buffers

-

vi-

Page 9

CHAPTER

1

.I

GENERAL

The

PDMA-15

plugs directly into an expansion slot

AT&T

rear mounting plate.

63300.

1

DESCRIPTION

high-speed, labit, paralleldigital interface card

All

digital

1/0

feeds

of

the IBM

through

PC/XT/AT

a 37-pin,

D-type,

INTRODUCTION

with

DMA (Direct Memory Access)

and compatible machines, including the

male connector

that

projects through the

Compared with standard digital

with its internal

than can be achieved with programmed

around

rate of the computer's main processor and the clock supplied

transfer rates of 200,000 bytes/sec or 120,000 words/sec are possible on

4.77h4Hz

time.

constantly output

1.2

Typical applications for the

1.

2.

3.

4.

5.

5-IOKHz).

It

is

APPLICATIONS

Interface

Arbitrary waveform generation with an external D/A converter.

High-speed

High-speed digital stimulus

Fast block transfer of data between computers.

clock.

possible

for

DMA

and interrupt-control hardware is capable

Actual DMA data transfer rates are computer dependent, influenced by the clock

Note

that the

to

transfer any number

or

input to a bIock

high-speed digital peripherals.

A/D

conversion with an external

1/0

boards

DMA

controller may address only one page (64Kbytes)

of

PDMA-16

for

testing

(such

as the Keithley MetraByte PIO-121, the PDMA-16

1/0

transfers

of

bytes

memory using the

are as follows:

and

through

up

A/D

control.

the

to

to

this

limit as a singleshot operation,

DMA

converter.

of

much higher data transfer

main

processor (at best limited

the

8237

DMA controller. Continuous

a

standard

IBM

of

Controller's Auto-initialize Mode.

rates

PC

with

memory at a

or

to

to

6.

Interrupt or DMA driven background data transfers.

7.

High sink current

8.

Data line monitoring.

9.

Transient generation and monitoring.

1.3

FEATURES

The PDMA-16 includes the following features:

1.

Two

8-bit

1/0

The ports are addressable as normal 1/0 locations using programed transfer

instructions), or by using the

at

high

speed

lTL

digital

ports,A

to/from the ports from/to memory. DMA transfers maybe bytes (&bit) through

and

1/0

B.

Each port is settable as an input

Pc's

internal 8237

(24mA sink current).

DMA

or

output under software control.

controller. Data may

(IN

and

OUT

be

directly transferred

1/0

1-1

Page 10

PDMA-16

USER GUIDE

the A Port

DIRECTION outputs provide information on the current direction of the

interface to devices capable

AUXl

utilized in general control

use as a regular

2.

A

DMA transfer may

The internal timer consists

counter.

choice of external signal

the

XFER

transfer to/from memory is acknowledged

the high state. The operating DMA level is selectable as either Level

The user

commencing transfers.

3.

An

interrupt channel

Level

pin, a periodic interrupt

from the

only,

or

words

-

AUX3

(2-7)

are

available from the DMA and Interrupt Control Registers and can

port

for

be

This

provides a

REQUEST input, the

is

required

and

8237

to

is

choose

DMA controller.

(16

bit) using both the A and B Ports. The A DIRECTION and

of

bidirectional data transfer.

and

handshake functions. In

programmed

initiated by

of

a

loMHz

clock

rate ranging from

or

internal clock

XFER

initialize the

also provided. Software control allows

between a positive-

from

the

I/O.

an

external signal

crystal oscillator divided through two

2.5MHz

is

via

software

ACKNOWLEDGE

by

the

XFER

8237

DMA

controller

or

negative-edge external interrupt on the

PDMA-16's

internal timer,

In

Byte

(XFER

to

control.

output goes low. Completion

ACKNOWLEDGE

on

addition,

DMA transfers, the

REQUEST)

0.0023Hz

the

PC

you

or

a terminal interrupt generated

B

ports

to

simplify

three

auxiliary outputs,

be

further

B

Port

is

or

by

the internal timer.

sections

(about 8 pulses/hr), The

On

receipt

1

system board before

to select the active Intempt

of

a positive edge on

output returning to

or

3

under software control.

of an

of

INTERRUPT

free

8254

the

for

1.4

ACCESSORIES

A

set

of

software drivers for interpreted Microsoft BASIC, compiled BASIC,

Assembly Language are included in the Distribution Software. Because

applications, interrupt service routines, etc. the drivers perform basic

functions such as setting up the

the

for

user-developed drivers. Some simple

driver (PDMA.ASM) is supplied and can serve as a starting point for more application-specific,

DMA

Controller and internal Timer. Fully commented source code

BASIC

test and example programs are also included.

...

and

QuickBASIC, and

of

variety of possible

commom-to-all-application

1-2

Page 11

CHAPTER

This

chapter contains instructions for the installing the

compatible models. The chapter

describes how to make

Switch and the

2.1

UNPACKING & INSPECTING

1.

Unpack the board

in case the board must

2.

Check to

missing items

2

a

back-up

1/0

Connector and procedures for installing the PDMA-16 are

down

to its anti-static pack ping.

be

returned to the factory for repair.

be

sure

you have received every item

to

the manufacturer.

begins

copy

INSTALLATION

PDMA-16

with procedures for unpacking and inspection. It then

of

the Distribution Software. Descriptions of the 3ase Address

If

possible, retain the outer packing material

on

the packing list has been shipped. Report any

in an

IBM

PC/XT/AT

also

and

given.

3.

Holding wrapped PDMA-16 Board in one hand, place your other hand firmly on a metal

be

of the system chassis (which must

your body, preventing damage from such a charge to the board.)

4.

Carefully remove the board from its anti-static wrapping.

5.

Inspect the board and any other components for shipping damage. If damage is detected, return

the board to the manufacturer.

You are now ready to install your PDMA-16. Set the Base Address Switch if necessary

2.3).

Then, install the board as described in section

2.2

BACKING UP

As

soon

as

possible, make a working copy

copy on diskettes

your original software in

To

make a working copy of your Distribution Software, you will use the

function according to one

or

THE

on the

a

DISTRIBUTION

PC

Hard Drive. In either case, making a working copy allows you

safe place

of

the instructions in the following

grounded).

of

as

a

backup.

your Distribution Software.

(This

procedure drains any static electricity from

2.5.

SOFTWARE

two

You

Dos

subsections.

COPY

portion

(see

Section

may put the working

to

store

or

DISKCOPY

To

Copy

In either

Software; the

one (or moreas needed) formatted diskettes on hand

First, place your Distribution Software diskette in your

A:

.

Distribution

of

these instructions,

target

Then,

use

Software

the

diskette will

one of the following instructions to copy the diskette

To

Another

source

be

diskette will

the diskette you will copy to. Before

Diskette

be

the diskette containing your Distribution

you

start,

be

sure

to

serve as target diskettes,

Pc's

A

Drive and

files.

log

to

that drive by typing

to

have

2-1

Page 12

PDMA-16

If

your

Drive

USER GUIDE

PC

has just one diskette drive (Drive

A

also

serves as Drive

B)

A),

type

COPY

and

follow the instructions on the

*

.

*

B

:

(in a singledrive

screen.

FC,

If you prefer to

A: A:

DISKCOPY.COM, in

If

above) and follow the instructions

If

A: B:

and folIow instructions

your

PC

you prefer

and

DISKCOPY.COM,

To

Copy Distribution

Before copying Distribution Software to a hard drive, make a directory on the hard drive to contain

the files. While the directory name

1.

After making a directory named

A Drive

2.

Then,

type

needed) to the

When

you

finish

humidty, and dust) for possible future use as a backup.

use

the

DOS

DISKCOPY function, instead

on

the screen.

your

DOS files.

has

two

diskette drives (Drive A and Drive

on

the screen.

to

use

the

DOS

DISKCOPY

follow instructions

in

your

DOS

on

files.

Software

is

your

PDMAlC

and

log

to

that drive

COPY

* . *

PDMAl6

copying your Distribution Software, store

by

typing

path\PDMAlC,

directory.

function, instead

the screen.

To

The

choice,

,

A

:

place your Distribution Software diskette in

.

of

COPY, you

This

alternative is faster, but requires access

B),

type

COPY

of

COPY, you

This

alternative is faster,

PC

Hard

the

following instructions use

where

Drive

path

is

the

drive designation and

it

in a safe place (away

will

* . *

will

but

requires access

type

DISKCOPY

B

:

(the same as

type

DISKCOPY

PDMAZ6.

Dos

from

heat,

to

to

your

path

PC's

(if

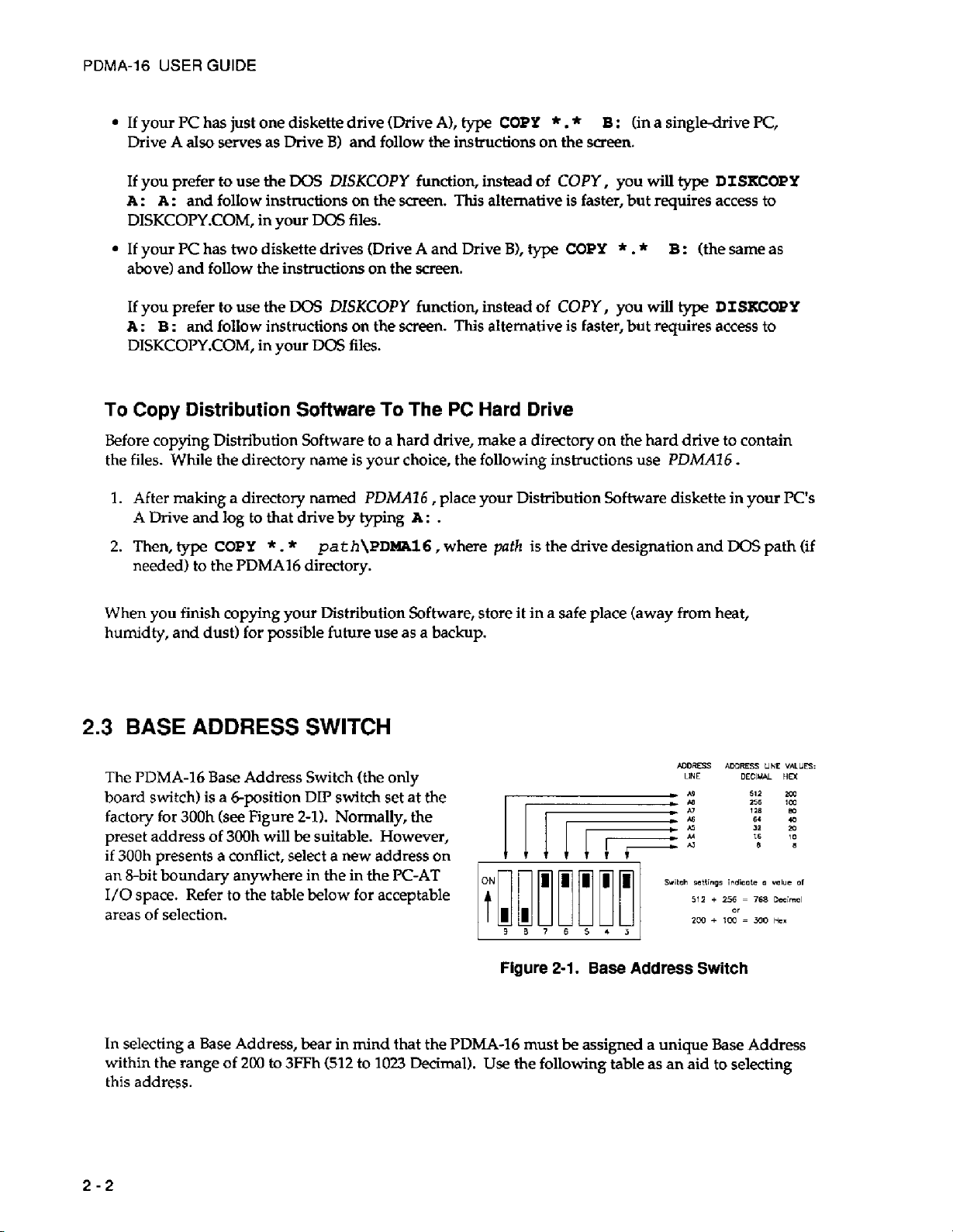

2.3

BASE ADDRESS SWITCH

The PDMA-16 Base Address Switch (the

board

switch)

factory for

preset address

if

300h

presents a conflict, select a new address

an

8-bit boundary anywhere in the in the

I/O

space. Refer

areas

of

In selecting a Base Address, bear in mind that the PDMA-16 must

within the

this address.

is

300h

of

selection.

range

a

&position

(see

Figure

300h will be suitable. However,

to

the table below for acceptable

of

200

to

DIP

2-11.

3FFh

switch set at the

Normally, the

(512 to

only

PC-AT

1023

on

Decimal).

Figure

Use

NDRSS

LINE

2-1.

Base

Address

be

assigned a unique Base Address

the following table as an aid

Switch

ADDRESS

DECIUAL HD:

to

selecting

UNE

VALUES:

2-2

Page 13

CHAPTER

2:

INSTALLATION

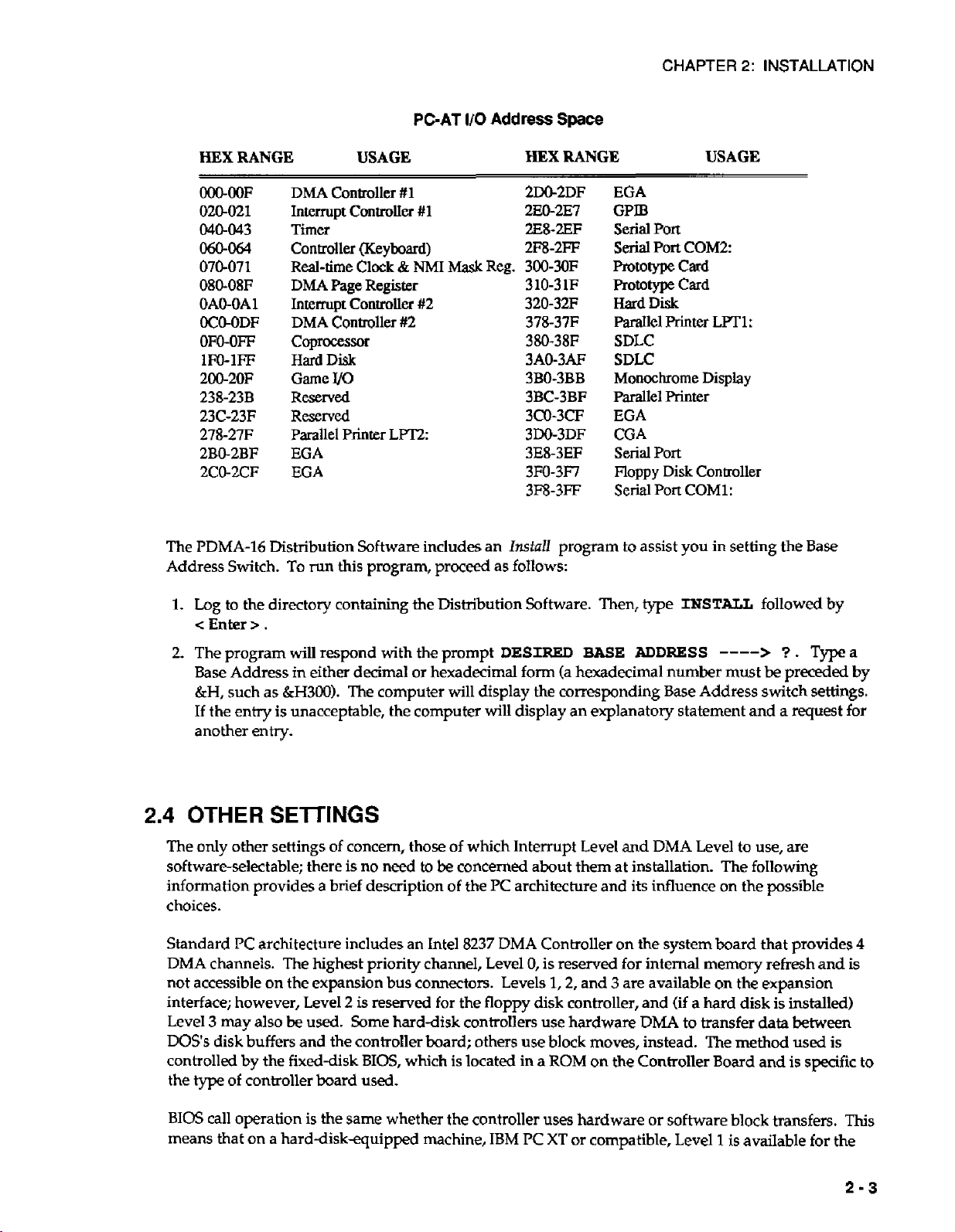

HEX RANGE USAGE

DMA

OOO-OOF

020-021

040-043

060-064

070-071

080-08F

OAO-OA1

OC@ODF

OM)-OFF

1m-IFF

200-2OF

238-23B

23C-23F

278-27F

2BO-2BF

2C0-2CF

The

PDMA-16

Address Switch.

Distribution Software includes an

Controller

Interrupt

Timer

Controller (Keyboard)

Real-time

DMA

Page

Intermpt

DMA

Controller

Coprocessor

Hard

Disk

UO

Game

RWXVed

RWXVed

Parallel

EGA

EGA

To

run this program, proceed as follows:

#1

ControlIer

Clock

&

Register

Controller

#2

Printer

LFT2

PGAT

#1

NMI

Mask

#2

I/O Address

HEX

2W2DF

2EO-2E7

2E8-2EF

2m-2FF

300-3OF

Reg.

310-3 1F

320-32F

378-3380-38F

3AO-3AF

3BO-3BB

3BC-3BF

3CO-3CF

3DO-3DF

3E8-3EF

3m-3F7

3F8-3FF

Install

Space

RANGE

EGA

GPIB

Serial

Port

Serial

Port

mtotypecard

prototype

Hard

Disk

ParaIlel

SDLC

SDLC

Monochrome Display

Parallel Printer

EGA

CGA

Serial

Port

Floppy

Serial

Port

program to assist

USAGE

COM2

Card

Printer

Disk

LFT

Controller

COM1:

you

in

1

:

setting the

Base

1.

Log

to the directory containing the Distribution Software. Then, type

<

Enter

>

.

2.

The program will respond with the prompt

Base Address

&H,

such as

If

the entry

another

2.4

OTHER

The only other settings of concern, those of which Interrupt Level and

softwareselectable; there

information provides

choices.

3

may

disk

type

of

PC

Standard

DMA channels. The highest priority channeI, Level

not accessible on the expansion bus connectors. Levels

interface; however, Level

Level

DOS’s

controlled by the fixed-disk

the

in

either decimal or hexadecimal form (a hexadecimal

&H300).

is

unacceptable, the computer

entry.

The computer will display the corresponding Base Address switch settings.

SElTINGS

is

no

need

to

a

brief description of the

architecture includes an Intel

2

is reserved for the floppy disk controller, and

also

be

used.

Some

hard-disk controllers use hardware

buffers

controller board

and the controller board; others

BIG,

which

used.

be

is

DESIRED

will

display an explanatory statement and a request

concerned about them at installation. The following

PC

architecture and its influence on the possible

8237

DMA

0,

use

located in a ROM on the Controller Board and is

BASE

Controller on the system board that provides

is reserved

1,2,

and 3 are available on the expansion

block

moves, instead. The method

ADDRESS

number

DMA

for

internal

(if

DMA

INSTALL

Level

memory

a hard disk

to transfer data between

---->

must

to

followed

?

.

Type

be

preceded by

use, are

refresh and

is

installed)

used

by

is

specific

a

for

4

is

to

BIOS

call operation is the same whether the controller uses hardware

means that on a harddiskequipped machine,

IBM

PC

XT

or

or

compatible, Level

software block

1

is

available

transfers.

for

This

the

2-3

Page 14

PDMA-16

USER

GUIDE

PDMA-16;

Levels

when a hard disk is included. Selection

the

PDMA-16

The

PDMA-16

Levels

Bits

4-6

It

is possible to operate more

placed at different

same interrupt and

Level

3

may

also

1

and 3 are both available.

Control Register.

may

also

generate interrupts

(2

thru

7).

Like

the

DMA

of the

PDMA-16's

1/0

Interrupt Control Register.

addresses. Since the interrupt and

DMA

channels may

be

available.

Also,

On

floppy-diskanly machines

the

IBM PC/AT

of

the

DMA

on

any

always

Level 1 or 3 is

of

the

available

level, the active Interrupt Level is

than

one

PDMA-16

in a single computer. In

DMA

be

shared

among boards as long as they are individually

has

Levels 1 and 3 available even

under

software

expansion-connector Interrupt

selected

this

channels employ tri-state drivers, the

enabled and disabled in sequence by the controlling software. If the boards are to

simultaneous

2.5

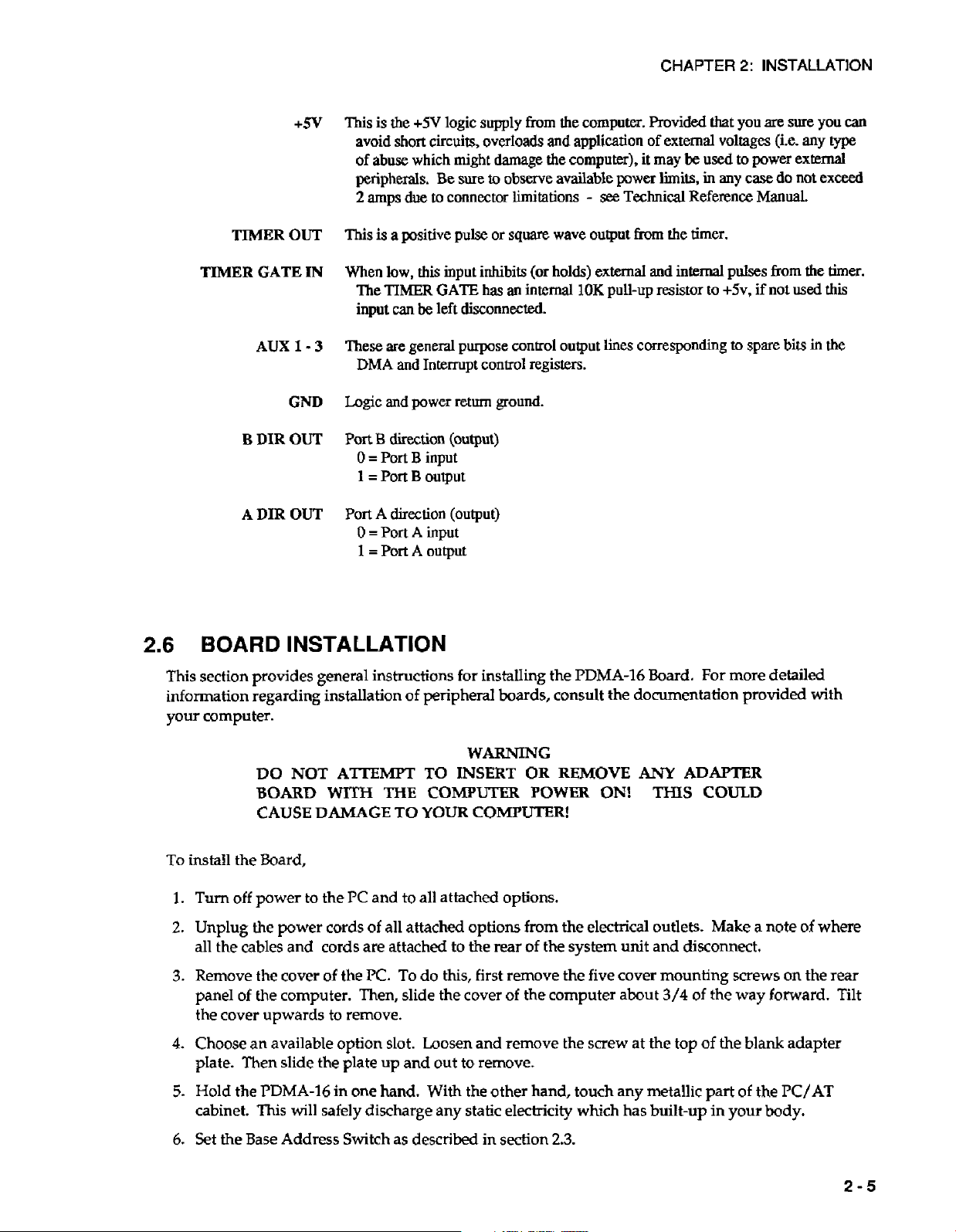

I/O

A

standard 37-pin,

I/O.

The mating connector is a standard, 37-pin

female

such

connections. Insulation displacement

readily available (for example,

manufacturers make equivalent

access connections with screw connectors,

manufacturer's

The

1/0

described in Figure

follow.

DMA

and interrupts,

they

must operate on different

CONNECTOR

D-type

as

an ITT/Cannon #DC37S for soldered

STA-U

Connector and its signal conductor functions are

2-2

Figure

2-2. Main

male connector is

used

for

all

D-type

(ff

Amp

parts.

at cable)

#745242-1).

If you wish to

use

types

Other

the

Universal Screw Connector Board.

and the table

I/O

of

functions that

Connector

are

IeveIs.

XFER

ACK.

XFER

ma.

INTERRUPT

A7

El6

OUT

IN

IN

(IBM

PC or compatible),

control by Bit 6 of

by

software control

case

boards should

perform

F-----.

37

'

36

35

34

33

32

31

30

'

29

28

27

26

25

24

23

4

22

21

20

>

A

DIR.

OUT

GND

GND

GND

CND

GND

GND

GND

B

DfR.

OUT

GND

GND

AUX.

3

OUT

AUX. 2 OUT

AUX.

1

OUT

TIMER

GATE

TIMER

OUT

POWER

1%

>

COMPUTER

using

be

IN

FROM

2-4

SIGNAL

NAME FUNCTION

INTERRUPT

XFER. REQ.

XFER.

ACK.

80

A0

IN

IN

OUT

-

B7

-

A7

This

is

a

positive or negative edge triggered intempt input.

edge

is

selected

A

positive

the

DMA

On

receipt

finished

data

is

on

mode.

Port

B

data

Port A data

I10

Signal

by

bit

edge

on

this

control

register

of

a

XFER.

the

byte

or

the

port(s)

(input/output)

(input/output)

Functions

DO

of

the

input initiates

=

0.

REQ.

the

word

transfer,

in

output

interrupt

a

XFER.

XFER.

mode,

control

DMA

ACK.

ACK.

or

that

register.

transfer

goes

returns

data

has

with

low.

been

The

slope

DMA

enabled

After

the

high

indicating

aansferred

of

8237

the

trigger

and

DMA

that

in

input

D3

of

has

valid

Page 15

TIMER

TIMER

B

A

OUT

GATE

AUX

GND

DIR

OUT

DIR

OUT

+5V

IN

1

-

3

This

is

the

+5V

avoid

short

of

abuse which might

peripherals.

2

amps

due

This

is

a positive

When

low,

this

The

TIMER

input

can

be

These

are

general

DMA

and

Logic

and

power

Port

B

direction

0

=

Port

B

1

=

Port

B

Port

A

direction

0

=

Port

A

1

=

Port

A

logic supply from

circuits, overIoads

damage

Be

sure

to

observe available

to connector

pulse

input

GATE

left

disconnected.

purpose

Interrupt

return

(output)

input

output

(output)

input

output

limitations

or

square

inhibits

has

an

control

control

ground.

the

and

the

wave

(or

holds)

internal

output

registers.

computer.

application

computer),

power

-

see

Technical Reference

output from

external

1OK

pull-up

lines

corresponding

CHAPTER

Provided

of

external

it

may

be

limits,

the

and

internal

resistor

that

voltages

used

in

any

timer.

to

2:

INSTALLATION

you

are

(i.e. any

to

power

case

do

Manual.

pulses

from

+5v,

if not

to

spare

bits

sure

you

external

not

exceed

the

used

in

can

type

timer.

this

the

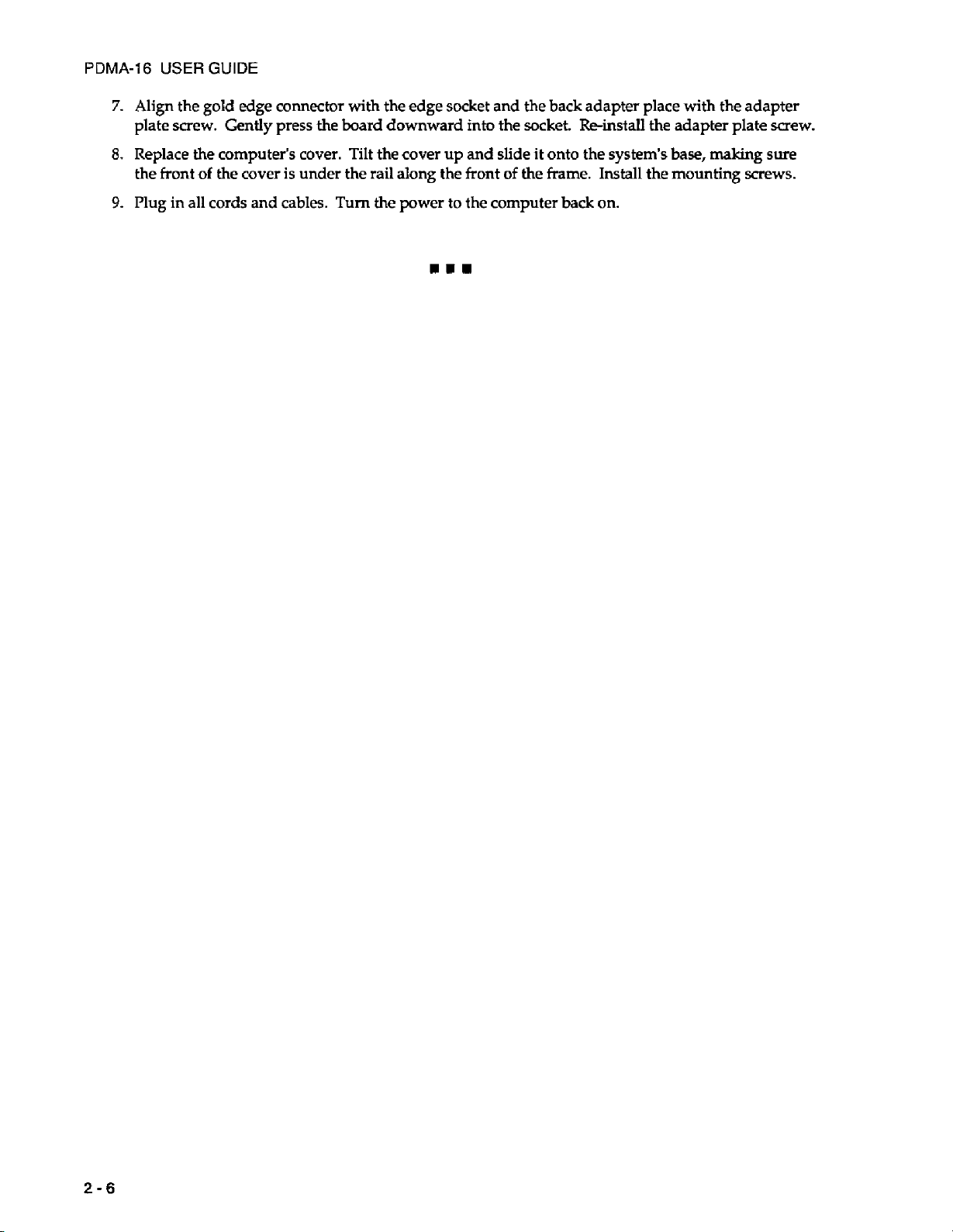

2.6

BOARD

This

section provides general instructions

information regarding installation of peripheral boards, consult the documentation provided

your computer.

To

install

1.

2.

3.

4.

5.

the

Turn

off

Unplug the power cords

all the cables and cords are attached to the rear

Remove the cover of the

panel

of

the cover upwards

Choose an available option slot. Loosen and remove the screw at

plate. Then slide the plate up and out

Hold the

cabinet.

INSTALLATION

for

instalIing the

WARNING

DO

NOT

BOARD

CAUSE

Board,

power to the

WITH

DAMAGE

ATEMTT

PC

and

of

TO

INSERT

THE

COMfuTER

TO

YOUR

to

all attached options.

all attached options from the electrical

COMPUTER!

OR REMOVE

of

PC. To

the

computer. Then, slide the cover

to

remove.

PDMA-16

This

in one hand. With the other hand, touch any metallic part

will safely discharge any static electricity which has built-up in your

do this, first remove the five cover mounting screws

of

the computer about

to

remove.

PDMA-16

Board. For more detailed

ANY

POWER

the system unit and disconnect.

ON!

THIS

outlets.

3/4

the

top

ADAPTER

COULD

Make a note

of the way forward. Tilt

of

the

blank adapter

of

the

body.

with

of

where

on

the rear

PC/AT

6.

Set

the Base Address Switch as described

in

sedion

2.3.

2-5

Page 16

PDMA-16

7.

Align the gold edge connector with the edge socket and the back adapter place with the adapter

plate screw. Gently press

8.

Replace the computer's cover.

the front

USER

GUIDE

of

the cover

the

board downward into the socket. Reinstall the adapter plate screw.

Tilt

the cover up and slide it onto the system's

is

under the rail along the front

of

the frame.

Install

base,

making

the mounting screws.

sure

9. Plug

in all cords and cables.

Turn

the power

to

the computer back on.

2-6

Page 17

CHAPTER

3

At the lowest level, the

these are the

languages have equivalent instructions (for example,

of

these functions

Although not demanding,

the devices, data format, and architecture

3.1

I/O

PDMA-16

space, as shown in the following table.

ADDRESS

I"Q0

MAP

boards

PDMA-16

and

usually

use

16

is

programmable via

OUT

X,Y

functions.

invoIves formatting data and dealing with absolute

this

type

of

programming requires that you have a

of

the PDMA-16.

consecutive addresses starting at the Base Address in the computer's

FUNCTION

REGISTER

I/O

(Input/Output)

Assembly

Language and

IN

AL,DX

and

STRUCTURES

most

OUT

instructions.

other high- level

DX,AL

in

1/0

addresses.

full

understanding

TYPE

In

BASIC,

Assembly).

1/0

Use

of

Base

Address4

Base

Address+l

Base

Address+:!

Base

Address+3

Base

Address4

Base

Address+S

Base

Address4

Base

Address+7

Note that addresses

3.2

PORTS

Port

A data corresponds one-for-one

transfers the Least Significant Byte and

transfers, Port

ports

A

and B can always

or

not they are involved in DMA transfers.

byte transfers are taking pIace through port

A

81

A

becomes

B

A

Port

B

Port

DMA

Interrupt

Counter

Counter

Counter

Counter Control

Counter

Base

the

default

be

written

Conaol

Control

0

1

2

Status

Address

with

Port

I/O

to

and read

+4

thru

+7

correspond to the

the data bus. When transferring

B

transfers the Most Significant Byte.

port

(you cannot use Port B for DMA byte transfers).

as

standard

Port

E

can

be

used

A.

1/0

ports

as a standard

ReaWrite

Read/Write

Reamrite

Read/Write

Read/Writ&

Read/write

Read/Write

Write

Read

8254

words

by

an

1/0

1/0

timer.

by

DMA,

For

Port

DMA byte

A

Both

instruction whether

port

while DMA

The

Port A data

Base+O

format

A7

is

as

follows:

A6

A5

A4

A3

A2

A1

A0

3-1

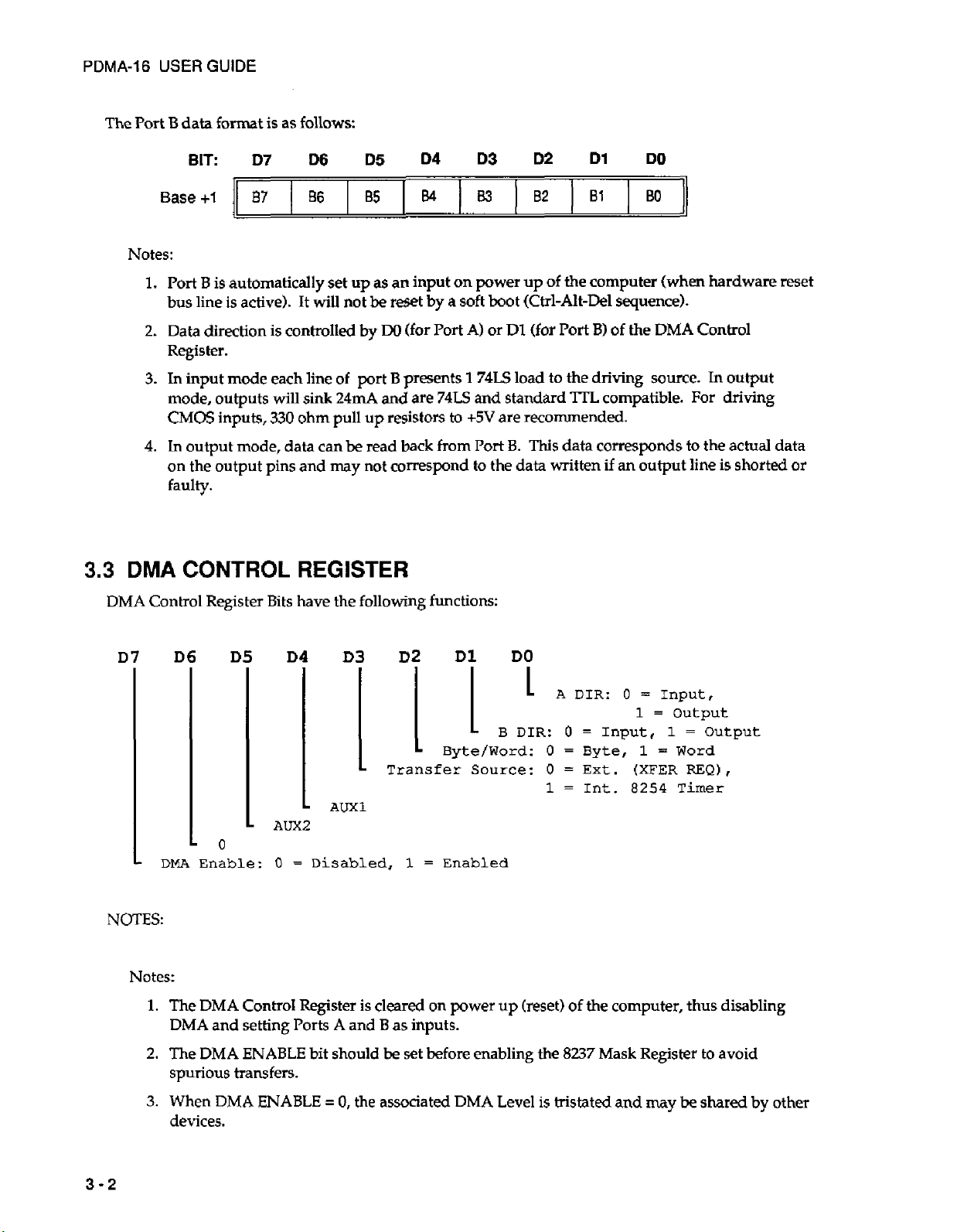

Page 18

PDMA-16

The

Port B data format

USER

GUIDE

is

as

follows

3.3

DMA

Base+1

B7

86

B5

EM

Notes:

1.

Port

B

is automatically

bus line

2.

Data direction is controlled

Register.

3.

In

mode, outputs

CMOS

4.

In output mode, data can

is

active).

input mode

inputs,

each

will

330

on the output pins and

set

up

It

wiU

not

line

of

sink

24mA

ohm pull

be

may

as

an input

be

rewt

by

W

port

B

and

up

resistors

read

not

correspond

by

(for

Port

presents

are

74LS

back

from

faulty.

DMA

CONTROL

REGISTER

Control Register Bits have the following functions:

I33

on

power up

a

soft

A)

1

74LS

and

to

+5V

Port

to

02

boot

(Ctrl-Alt-Del

or

Bl

(for

load

standard

81

of

the computer (when hardware reset

Port

3)

to

the driving source.

TTL

are recommended.

8.

This

data corresponds

the

data

written

I30

sequence).

of

the

DMA

Control

In

output

compatible. For driving

to

the

actual

if

an

output

line is shorted

data

or

I

NOTES:

Notes:

1.

2.

3.

D

DMh

The

DMA

The

D

0

Enable:

DMA

Control Register is cleared

and setting Ports A and B as inputs.

DMA

ENABLE bit should

spurious transfers.

When

DMA

ENABLE

devices.

D4

AUX2

0

=

D

AUXl

Disabled,

=

0,

the associated

B2

L

Transfer

1

=

on

be

set

before

D1

Byte/Word:

Enabled

power

DO

I

B

DIR:

Source:

up

(reset)

enabling

DMA

Level

0

=

0

=

0

=

1

=

of

the 8237

is

tristated

1

=

output

Input,

Byte,

Ext.

Int. 8254

1

1

=

(XFER

=

Output

Word

REQ),

Timer

the computer, thus disabling

Mask

Register

and

my

to

avoid

be

shared

by other

3-2

Page 19

4.

3.4

INTERRUPT

The

Interrupt

The

AUXl

brought

out

Control Register

and

AUX2

bits correspond

to

provide additional

to

unused

outputs

CONTROL REGISTER

bits

have the following functions:

on the

CHAPTER

bits.

For convenience, these have been

rear

connector.

3:

REGISTER STRUCTURES

D7

-

Notes:

D

-0

-0

IN'I

1.

The Interrupt

interrupts.

2.

The

INT

Register to avoid generation

3.

When

N

other devices.

Control

ENABLE

bit shouId

ENABLE = 0,

T

-

Am3

Register

is

cleared

be

set before enabling the

of

spurious interrupts.

on

the associated Interrupt

1

Slope:

00

=

External

01 = 8237

10

=

11

=

8254

8237

Terminal

Timer

Terminal

power-up (reset)

8E9

Level

is

Input

of

Interrupt

tristated

0

=

+

Edge,

1

=

-

Edge

the computer,

Controller

thus

Mask

disabling

and available for use by

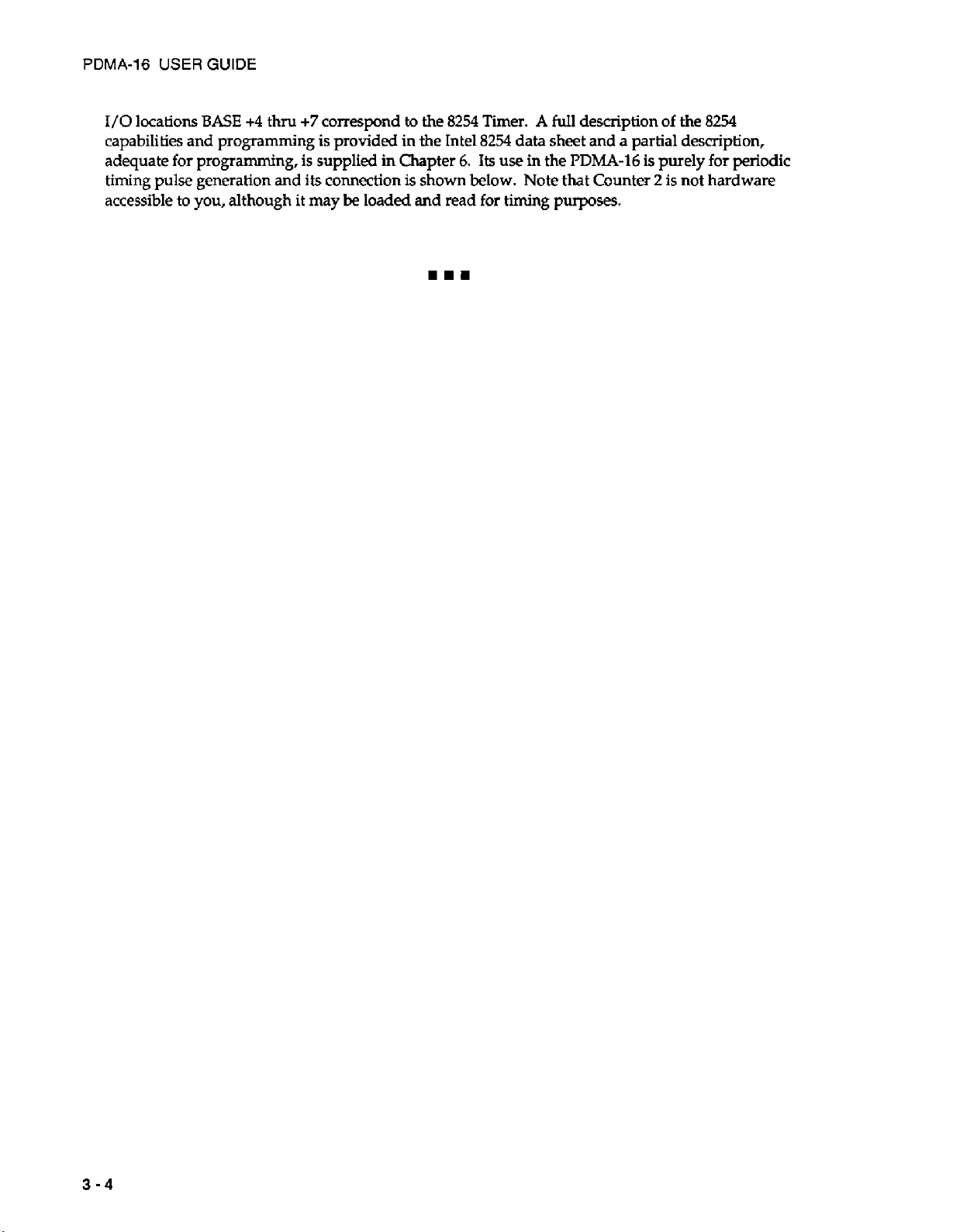

3.5

4.

The

Am3

bit corresponds to an unused bit.

provide an additional output on the rear connector.

8254

10

XTAL

CLOCK

i

5v

TIMER

MHZ

2

GATE

CLOCK

GATE

CLOCK

I14V

.

-.

1

OK

GATE

CLOCK

r----------~-~~--------------

0

0

1

I

1

2

2

Diagram

CLOCK

CLOCK

CLOCK

of

8254

8254

1N

16-BIT

IN

16-BIT

IN

16-BIT

connection

For

convenience,

TIMER COUNTER

COUNTER

DOWN

COUNTER

DOWN

COUNTER

DOWN

0

COUNTER

1

COUNTER

2

COUNTER

in

0

UT

PDMA-16.

it

has been

I

I

!

TO

I-

I

INTERNAL CIRCUITS

N.C.

brought

out

to

3-3

Page 20

PDMA-16

I/O

USER

locations

GUIDE

BASE

+4

capabilities and programming

adequate

for

programming, is supplied in Chapter

timing pulse generation

you,

accessible to

although

thru

and

+7

correspond to the

is

provided

its

connection

it

may

be

loaded and read

in

the

is

shown

8254

Intel

6.

Timer.

8254

Its

below.

for

A

fuIl

description

of

data sheet and a partial description,

use

in

the

PDMA-16

Note that Counter

timing

purposes.

is purely

2

is

the

not

8254

for

periodic

hardware

3-4

Page 21

CHAPTER

4

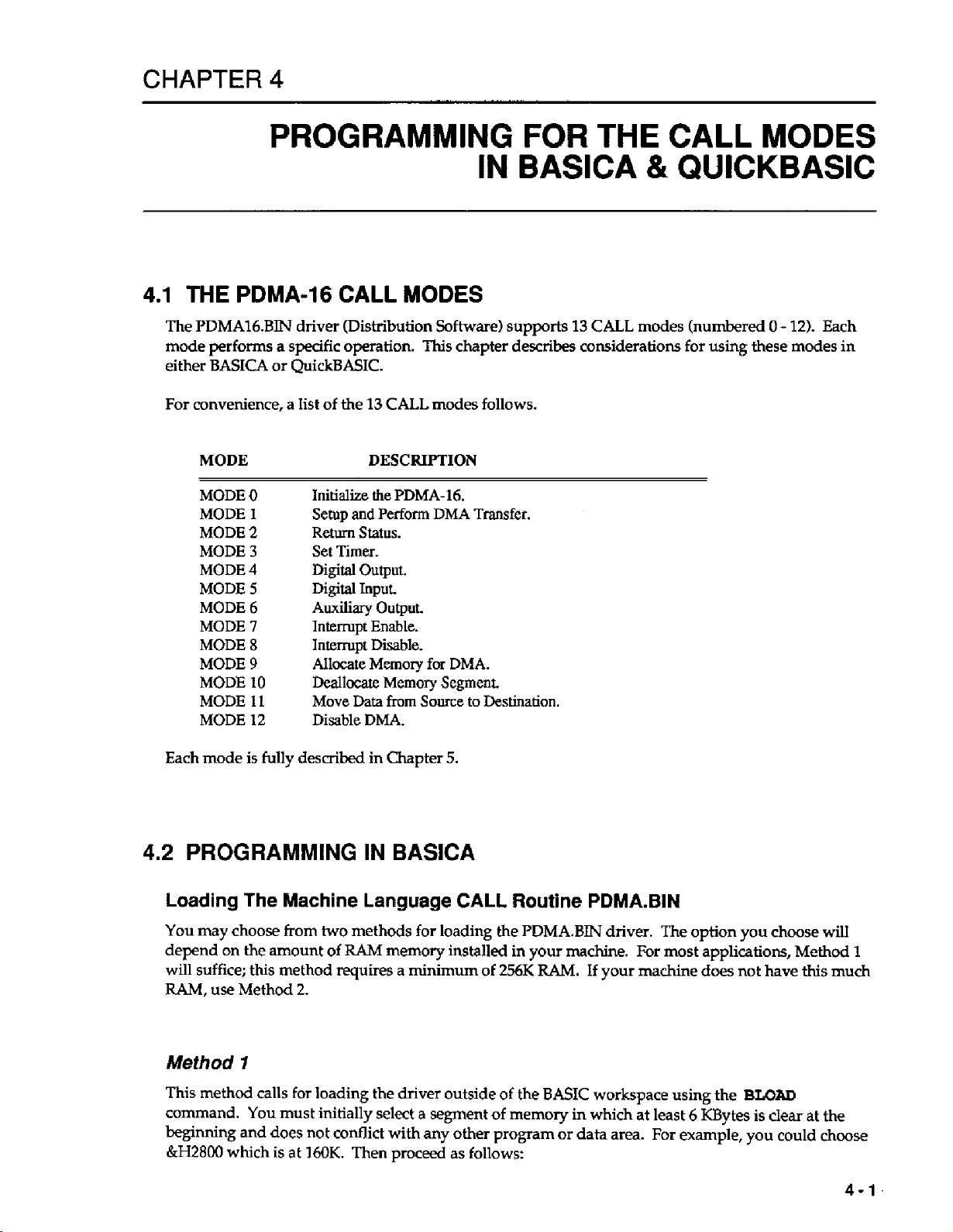

4.1

THE

The

PDMAldBIN

mode perfoms

either

BASICA

For

convenience, a Iist of

MODE DESCRIPTION

MODE

MODE

MODE

MODE

MODE

MODE

MODE

MODE

MODE

MODE

MODE

MODE

MODE

PROGRAMMING

PDMA-16

a

specific operation.

or

QuickBASIC.

0

1

2

3

4

5

6

7

8

9

10

11

12

CALL

driver (Distribution Software) supports

the

Initialize the

Setup

and

Return

Set

Timer.

Digital

Digital

Auxiliary

Interrupt

Interrupt

Allocate Memory

Deallocate Memory Segment.

Move Data

Disable

13

CALL

PDMA-16.

Perform

Status.

Output.

Input

Output.

Enable.

Disable.

from

DMA.

MODES

This

modes follows.

DMA

for

Source

IN

chapter

Transfer.

DMA.

to

Destination.

FOR

THE

BASICA

13

CALL

describes

considerations for using these modes in

CALL

&

QUICKBASIC

modes (numbered

MODES

0

-

12).

Each

Each mode is

4.2

PROGRAMMING

fully

described in Chapter

IN

BASICA

Loading The Machine Language

You

may

choose

depend

will suffice;

RAM,

on

use Method

Method

This

method

command. You must initially select a segment

beginning and

&H2800

which

from

two

methods for loading the

the

amount

this

method requires a minimum

2.

of

RAM

memory

I

calls

for

loading the driver outside

does

not conflict with any other program

is

at

160K.

Then proceed as follows:

5.

CALL

installed

of

of

Routine

PDMA.BIN

in

your

256K

RAM.

of

the

memory in which

machine.

BASIC

or

data area.

PDMA.BIN

If

your

workspace using

driver. The option you choose

For

most applications, Method

machine does not have

the

BLOAD

at

least 6 KBytes

For

example,

is

you

this

clear

at

could choose

will

1

much

the

4-1

Page 22

PDMA-16

USER

GUIDE

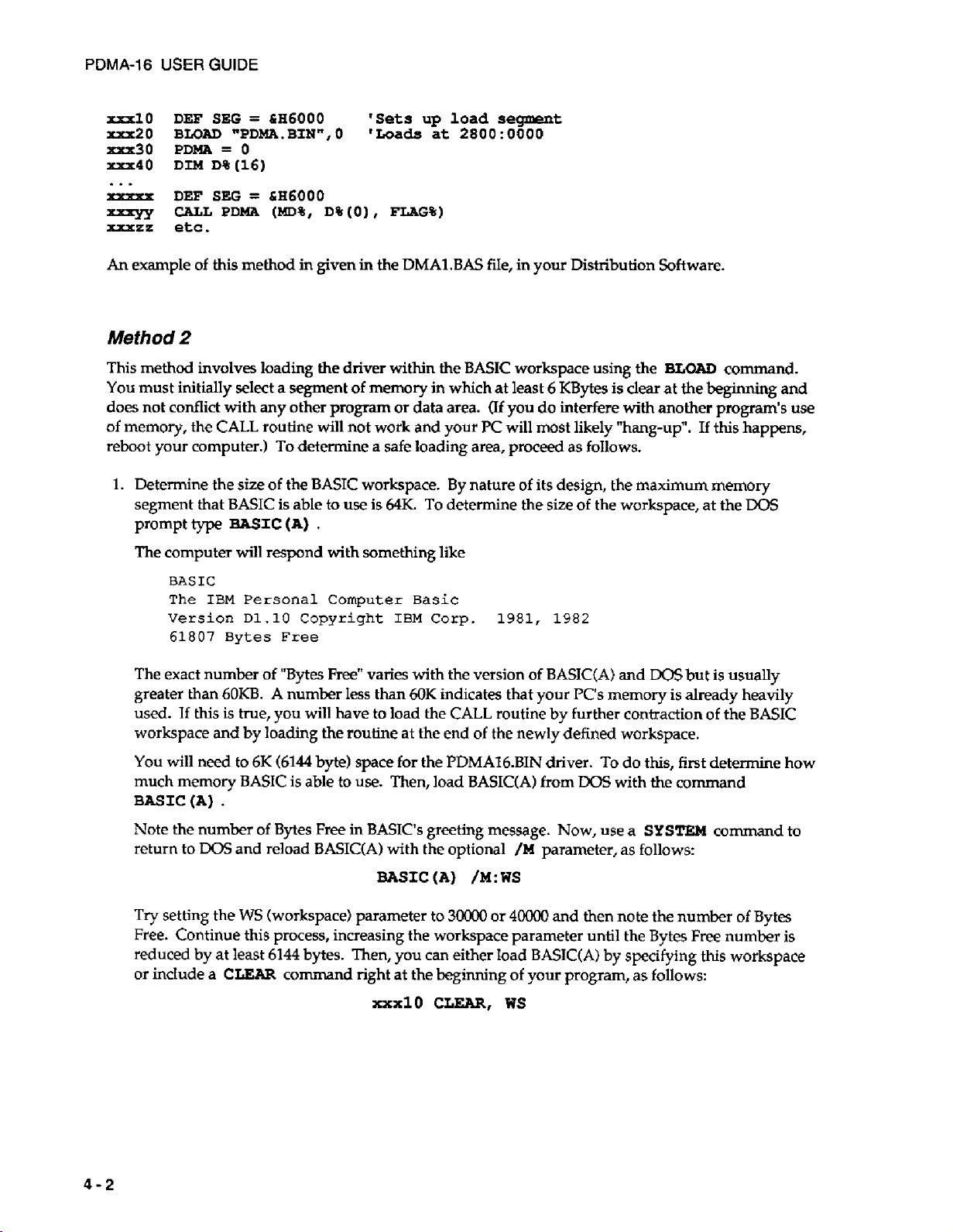

rxxlo

xxx20

-30

-40

DEF

SEG

BLOAD

PDMA

DIM

D%(16)

=

hH6OQO

nPDMA.BINn,O

=

0

'Sets

'Loads

up

load

at

28OQ:QOOQ

...

xxxxx

xxqy

xxxzz

An

Method

This method involves loading

You

does not conflict with

of

memory, the

reboot your computer.)

1.

DEF

SEE

=

CALL

PDMA

etc.

example of this method in given

&H6000

(MD%,

D%(o),

in

the

FLAG%)

DMA1.BAS

2

the

driver within the

must initially select a segment of memory in which at least

any

other

CALL

routine will not work and your K will most likely "hang-up". If

To

Determine the size of the

segment that

prompt

type

BASIC

BASIC

is able

(A)

program

determine a safe loading area, proceed

BASIC

to

use

.

or

data area.

workspace.

is

64K.

The computer will respond with something like

BASIC

By

To

determine the

segment

fiIe, in your Distribution Software.

workspace using the

6

Of

you

do

nature

of

its design, the

size

KBytes

is

interfere

as

follows.

of

the workspace, at the

BLOAD

clear at the

with

another program's use

maximum

command.

beginning

this

and

happens,

memory

DOS

BASIC

The

IBM

Personal

Version

61807

D1.10

Bytes

The exact number of "Bytes

greater

used.

workspace and

You

much memory

BASIC(A)

Note the number

return to

Try

than

6OKB.

If

this is true, you will have to load the

will need to

A

by

loading the routine at the end

6K

(6144

BASIC

.

of

Bytes Free in

Dos

and reload

setting the

WS

(workspace) parameter

Computer

Copyright

Free

Free"

varies with the version of

number Iess than

byte) space for the

is

able to

use.

BASIC's

BASIC(A)

BASIC

Basic

IBM

Corp.

6OK

indicates that

CALL

of

the newly defined workspace.

PDMAl6.BIN

Then, load

BASIC(A1

greeting message.

with the optional

(A)

/M:WS

to

3oooO

or

1981, 1982

BASIC(A1

your

Pc's

routine

by

further contraction

driver.

from

DOS

Now,

/M

parameter, as follows:

4oooO

and then note the

and

Dos

memory is already heavily

To

do this, first determine how

with the command

use

a

SYSTEM

Free. Continue this process, increasing the workspace parameter until the Bytes

reduced by at least

or inciude a

CLEAR

6144

bytes. Then, you can either load

command right at the beginning of

XXxlO

CLEAR,

BASIUA)

your

ws

by

specifying

program, as follows:

but

is usually

of

the

command

number

Free

of

number

this workspace

BASIC

to

Bytes

is

4-2

Page 23

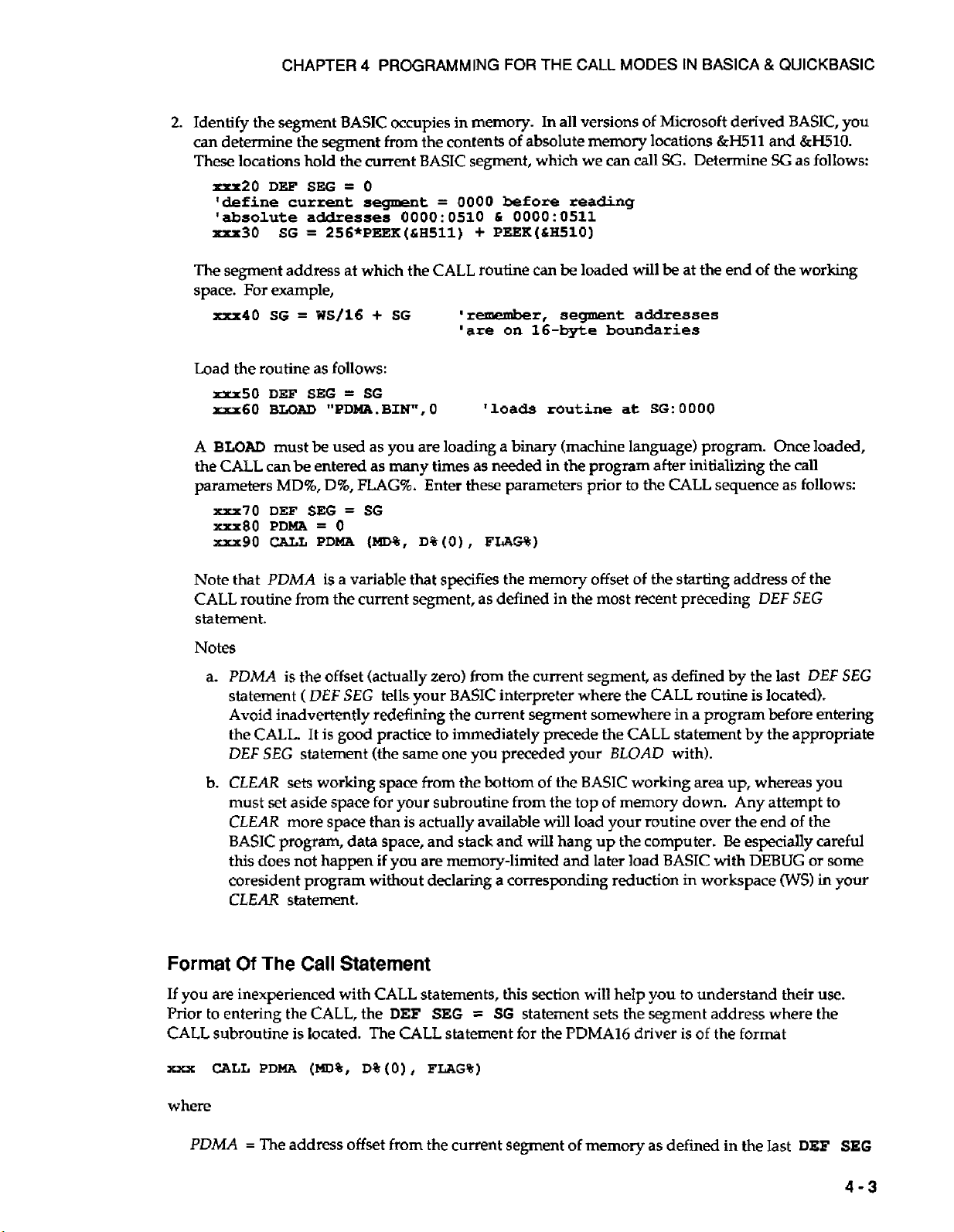

2.

Identify the segment

CHAPTER 4 PROGRAMMING

BASIC

occupies in memory. In

FOR

THE CALL

all

MODES

versions of Microsoft derived BASIC,

can determine the segment from the contents of absolute memory locations

These locations hold the current BASIC segment, which we can call

ru20

'define current segment

'absolute

xu30

DEF SEG

SG

=

0

addresses 0000:0510 & 0000:0511

=

256*PEEK(&H511) + PEEK(LH510)

=

0000

before reading

IN

BASICA & QUICKBASIC

SG.

&mll

Determine

and

SG

you

&H510.

as follows:

The segment address at

For

space.

xxxrl0

Load

srr50

xu60

A

BLOAD

example,

SG

=

the

routine as follows:

DEF SEG

BLOAD

must

be

the CALL canbe entered as many times

parameters MD%, D%,

-70

-80

-90

Note that

DEF

PDMA

CALL

PDMA

SEG

which

WS/lS

=

"PDMA.

used

FLAG%.

=

=

0

PDMA

the CALL routine

+

SG

SG

BIN",

as

you are loading a binary (machine language) program. Once loaded,

'ratuxrhr,

'are

0 'loads

as

Enter these parameters prior to the

SG

(MD%,

D%(O),

FL?iG%)

can

be

loaded will

on

segment addresses

16-byte

routine

boundaries

needed in the program after initializing the

is a variable that specifies the memory offset

be

at the end

at

1G:OOOO

CALL

of

the starting address

sequence as follows:

CALL routine from the current segment, as defined in the most recent preceding

statement.

Notes

a.

PDMA

statement ( DEF

Avoid inadvertently redefining the current segment somewhere in

the

DEF SEG

is the offset (actually zero)

SEG

tells

CALL.

It

is

good

practice to immediately precede the CALL statement by the appropriate

your

from

BASIC interpreter where

statement (the same one you preceded your

the current segment, as defined by the last

the

CALL routine is located).

a

program

BLOAD

with).

of

the working

call

of

DEF

SEG

DEF

before

the

SEG

entering

CLEAR

b.

sets working

space

from the bottom

must set aside space for your subroutine

CLEAR

more space than

is

actually available will load

BASIC program, data space, and stack and will hang up the computer.

this

does

not happen

if

you are memory-limited and later load BASIC with DEBUG or

coresident program without declaring a corresponding reduction in workspace

CLEAR

Format

Of

If you are inexperienced with CALL statements,

Prior

to

entering the

CALL subroutine

xxx

CALL

statement.

The

is

PDMA

Call

Statement

CALL,

located.

(MD%,

this

the

DEF

SEG

=

SG

The

CALL statement for the PDMA16 driver

D%(O),

FLAG%)

where

PDMA = The address offset from the current segment

of

the

from

the

BASIC

top

working area

of

memory down. Any attempt to

your

routine over the end

up,

whereas you

of

Be

especially careful

the

(WS)

section

Statement sets the segment address where the

will

help you

of

memory as defined in the Jast

to

understand their

is

of

the format

DEF

some

in

use.

your

SEG

4-3

Page 24

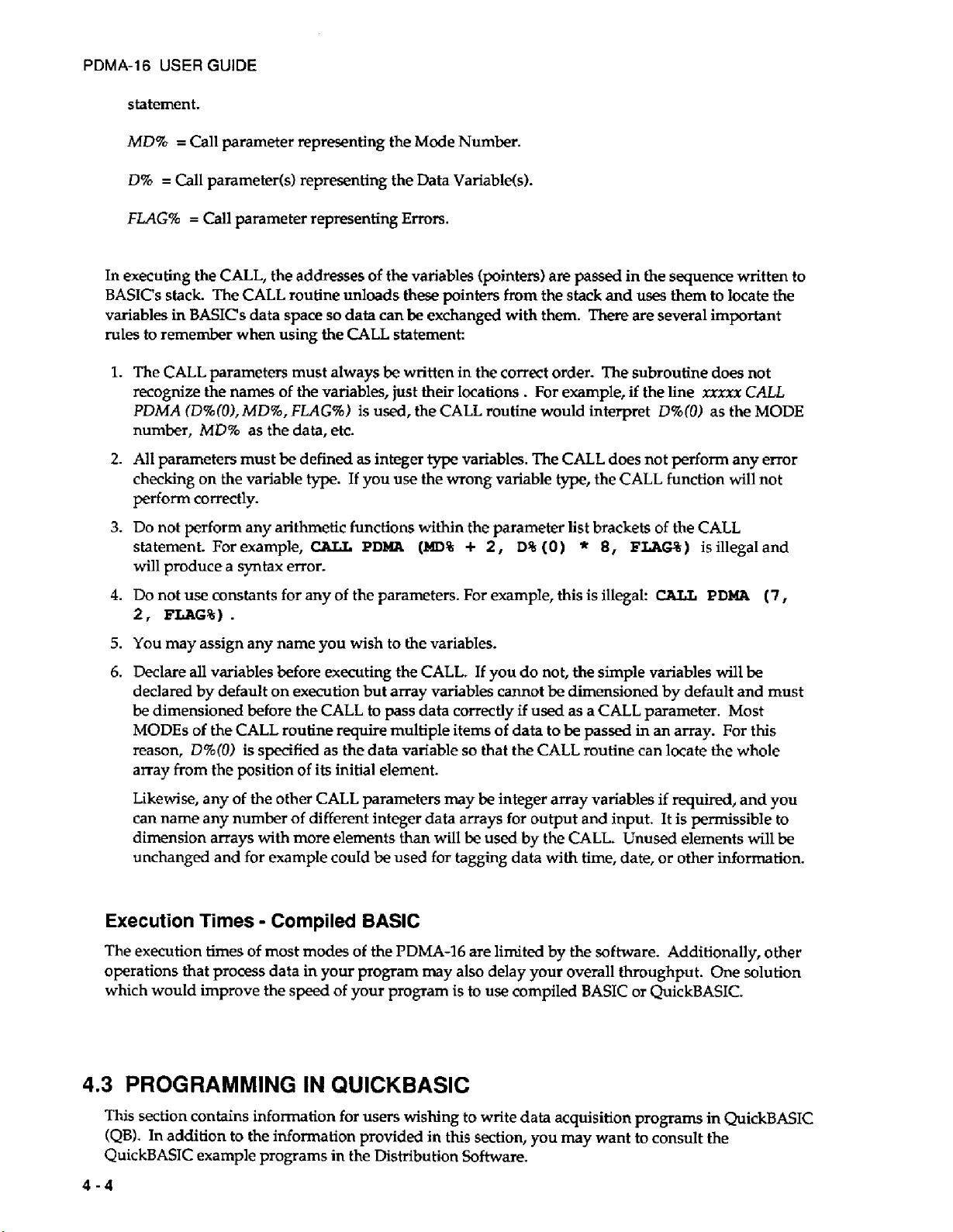

PDMA-16

statement.

USER

GUIDE

MD%

D%

FLAG%

In executing

BASIC's stack. The CALL routine unloads

variables in BASICS data space

rules to remember when using the

1.

2.

3.

=

Call parameter representing the

=

Call parameterb) representing the Data Variable(s).

=

Call parameter representing

the

CALL, the addresses of the variables (pointers) are

so

data can

CALL

The CALL parameters must always

recognize the names of the variables, just their Iocations . For example,

PDMA

number,

All parameters must be defined as integer

checking on the variable

perform

Do not

statement. Forexample,

will produce a syntax error.

(D%(O),

MD%, FLAG%)

MD%

correctly.

perform

any arithmetic functions

as the data, etc.

type.

CALL

is used, the CALL routine would interpret

If

you use the wrong variable

PDMA

Mode

Number.

Errors.

these

pointers

be

exchanged with them. There are several important

statement:

be

written in the correct order. The subroutine does

type

from

the stack and

variables. The CALL does not

type,

within

(MD%

the parameter list brackets of the CALL

+

2,

D%

(0)

passed

in the sequence written to

uses

them

to locate the

if

the line

D%(O)

wcxxll

as the MODE

perform

the CALL function will not

*

8,

FLAG%)

isillegaland

not

CALL

any error

4.

Do

not

use

constants for any

2,

FLAG%)

5.

You

may assign any name you wish

6.

Declare all variables before executing the CALL. If you do not, the simple variables

declared by default on execution but array variabIes cannot be dimensioned by default and must

be dimensioned before the CALL to

MODES

reason,

array from

Likewise, any

can name any number of different integer data arrays for output and input. It is permissible to

dimension arrays with more elements than will

unchanged and for example could

Execution

The execution times

operations that process data in your program may also delay your overall throughput. One solution

which would improve the speed of your program

.

of

the CALL routine require multiple items of data to

D%(O)

is

the

position

of

Times

of

specified

the

other CALL parameters

-

Compiled BASIC

most modes of the PDMA-16 are limited by the software. Additionally,

of

the parameters. For example, this is illegal:

to

pass

as the data variable

of

its initial element.

be

used

CAU

the variables.

data correctly if used as a CALL parameter. Most

be

passed in an array. For

so

that the CALL routine can locate the whole

may

be

integer array variables if requid, and you

be

used

by the CALL. Unused elements will be

for

tagging data with time, date,

is

to

use

compiled

SASIC

or

or QuickBASIC.

PDMA

will

other information.

(7,

be

this

other

4.3

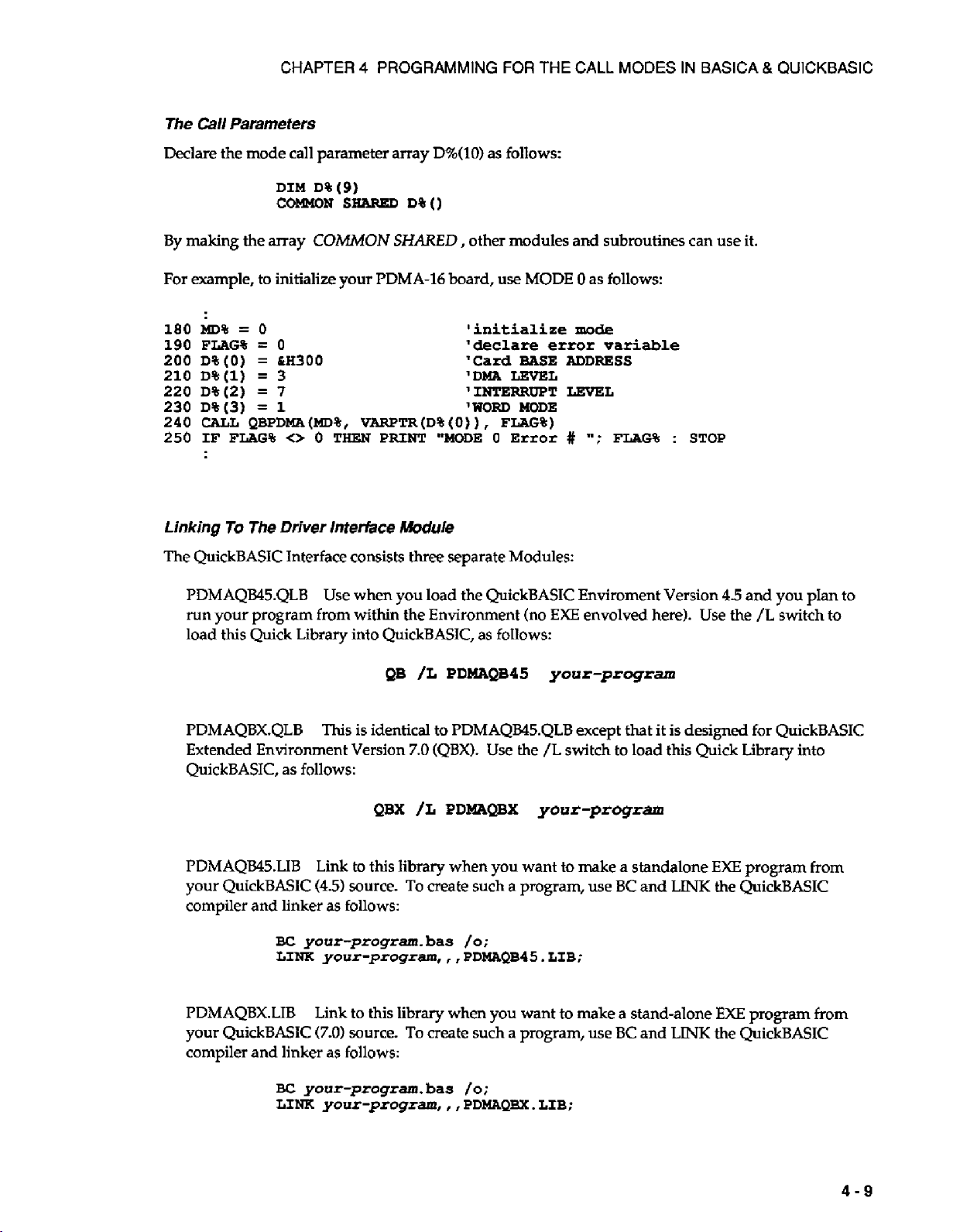

PROGRAMMING

This section contains information for users wishing to write data acquisition programs in QuickBASIC

(QB).

In addition to the information provided in this section, you may want to consult the

QuickBASIC example programs in the

4-4

IN

QUICKBASIC

Distribution

Software.

Page 25

CHAPTER

4

PROGRAMMING

FOR

THE

CALL

MODES

IN

BASICA

B

QUICKBASIC

Loading

A

QuickBASIC program will

Software contains the following linkable driver/Iibraries:

Load the PDMAQB45.QLB

the

To

load an application program (such as

Library and EXG3.BAS together by typing

Use PDMAQBX.QLB in an identical manner when using the QuickBASIC Extended Enviroment

(QBX)

The

Program

PDMAQB45.QLB

PDMAQBX.QLB

PDMAQB45,LIB

/L

switch,

Version

as

7.0.

follows:

have

Load

4.5

Load

LINK

Quick

QB

to

make calls to an external driver/library.

this

Quick Library into

or

lower,

this

Quick

Library

this

library

to

Library into

/L

PDLdAQB45.

EXG3.BAS)

your

QB

your

QuickBASIC

into

your

QuickBASIC

stand-alone QuickBASIC

the

QB environment from the

along

with

/L

PDMAQB45

Your

Integrated

Extended

Environment Version

Environment Version

program.

Dos

the Quick Library,

EXG3

.

Distribution

command Iine using

you

load the Quick

7.0

Declaring The Driver

Before you

application. Make this declaration by inserting the following at the beginning of your program:

where

NOTE:

Format

Unlike BASICA, the first and third parameters in

parameter is passed

represent the offset of the command integer array.

function

use

the driver/library,

DECLARE

QBPDMA

Of

as

follows:

is

All subroutine DECLARES in your program

allocated.

segment. All arrays

QuickBASIC assumes $STATIC data (Default data segment) unless otherwise specified.

The Call Statement

SW

the common entry point to the driver/library

$DYNAMIC

as a

pointer.

you

must declare the CALL label to make it known to your

QBPDMA

used

This

(MODE%,

BWAL

dunmy%,

for

MUST

data

is

allocated space

for

data acquisition

QB

are passed

arrangement is necessary because

To

pass the actual offset,

in

must

be

the

FAR

be

as

variables while the second

FLAG%)

driver modes.

before any

heap, outside the default data

declared as $DYNAMIC;

$DYNAMIC

the

second parameter

use

the

VARPTR

arrays are

must

where

MD%

is the Mode number,

4-5

Page 26

PDMA-16

USER

GUIDE

D%(N)

The VARPTR function returns the address

driver uses that value as a pointer

D%

is declared as a $STATIC array since it must reside in the default data segemnet in order to

relative to

the

QB

data segment, as required by the driver. Since

external driver, declare this parameter as an inter-module global variable,

D;M

D%(16)

COMMON SHARED D%

The

COMMON

module level

makes this variable visible between modules, and

makes

it

may declare any large

RI&d

$DYNAMIC

DIM

DMA%

(10000)

is the parameter array, and FLAG% returns detected errors.

()

known

$DYNAMIC

globaIly

of

D%(O),

to

the first element

in

this module.

which

of

our

After

you

pass

command integer array

declaring all your $STATIC variable, you

arrays for DMA data acquisition.

D%

the

as a

value

is

passed

as

SHARED

to

the driver. The

D%.

to and returned by the

folIows:

statement at the

be

NOTE:

All

$DYNAMIC

data declaration must occur

statements in your program.

flreceed

all

executablestafemmnts

AFIER

If

you get the

,

double check the order

QB

error

all

COMMON

$DYNAMIC declarations.

See

Section

Language Reference Manual

To

summarize, your program header should

2.5

($STATIC

and

$DYNAMIC

for

Arrays) and

a detailed discussion

look

as

(COMMON

of

the

factors

follows:

...

DECLARE

SUB

QBPDMA

(MODE%,

BWAL

dummy%,

FLAG%)

...

DIM

D%(16)

COMMON

k&i

DIM

SHARED

$DYMIMIC

DMA%

(10000)

D%

()

Parameter

I

DMA array