Page 1

Page 2

Tektronix,

Inc.

p.0.

Box

500

Beaverton,

Oregon

97077

COMMlTED

EXCELLENCE

INSTRUCTION

MANUAL

Serial

Number

070-2692-

00

First

Printing

MAR

1979

Page 3

WARRANTY

his

Tektronix product is

1

~d

against

defect

rials

and

orkmanship, under normal

use,

for

a

period

of

one

year

rrom

date

f

initial shipment.

Tektronix

will repair

or

replace, at its

option,

bose

products determined to

be

defective within the warranty

eriod and returned, freight prepaid,

to

a

Tektronix Service Center.

here

is

no

implied warra itness

of

purpoa

art

numl

ive

mate

nty

for

f

i

for

ierl

lease

direct all

I

vice

or

replacerr

earest Tektronix

aerrlce

lvertrer

or

Field

Office;

include

the

rypr

or

Jer

of

th

requests

..--..I--

be.

lent

par'

vright

@

tents

oft

.

.

ct

and

it s serial

number.

nix, Inc.

lay

not

b

-.

ts

to

the

-I

--

his publication

rr

e

reprad

vllJ

,,, ,,,

without the

permission

of

Tektronix,

Inc.

Prod

cove

lucts

of

red

by

Tektro

U.S.

an

nix,

Inc

d

foreis

.

and

its

subsidiaries

are

In

patents

and/or

pending

patents.

TEKTRONIX

E-MOBILE,

and

@

are

registered

traaemar~s

or

r

edronix,

1

Printed

in

U.S.A.

privileges are reservt

nc.

3nd

pril

Page 4

TABLE

OF

CONTENTS

Page

................................................

LIST

OF

ILLUSTRATIONS

iv

.......................................................

LISTOFTABLES

V

...........................................

OPERdTORS

SAFETY SUMMARY

~ii

............................................

SERVICING

SAFETY

SUMMARY ix

SECTION

1

SPECIFICATIOM

...........................................

Introduction 1-1

..................................

Performance Conditions 1-1

........................

Electrical Characteristics (Front Panel) 1-1

........................................

Dc

Voltmeter 1-1

........................................

Ac

Voltmeter

1-2

..........................................

Ohmmeter

1-3

........................................

Dc

Ammeter 1-3

........................................

Ac

Ammeter

1-4

......................

Electrical Characteristics

(Rear

Interface)

1-4

Dc

Voltmeter

........................................

1-4

........................................

Ac

Voltmeter 1-5

..........................................

Ohmmeter

1-6

.........................................

Miscellaneous 1-7

..............................

Environmental Characteristics

1-7

........................................

DM

505 Only 1-7

.....................................

TM

500

Systems

1-8

..................................

Physical Characteristics 1-9

SECTION

2

OPERATING INSTRUCTIONS

...................................

l nstallation l nstructions 2-1

.................................

Controls

and

Connectors

2-2

.................................

Operators Familiarization

2-2

...........................

General Operating Information

2-2

....................................

l

nput

Connections

2-4

...................................

Si ne-wave Response

2-4

...............................

Dc

Voltage Measurements 2-4

..............................

Dc

Current Measurements

2-4

.....................

Ac

Voltage

and

Current Measurements

2-4

Resistance Measurements

...............................

2-4

Packaging Information

...................................

2-5

Page 5

TABLE

OF

CONTENTS

(cont)

Page

SECTION

6

OPTIONS ..............................................

61

SECTION

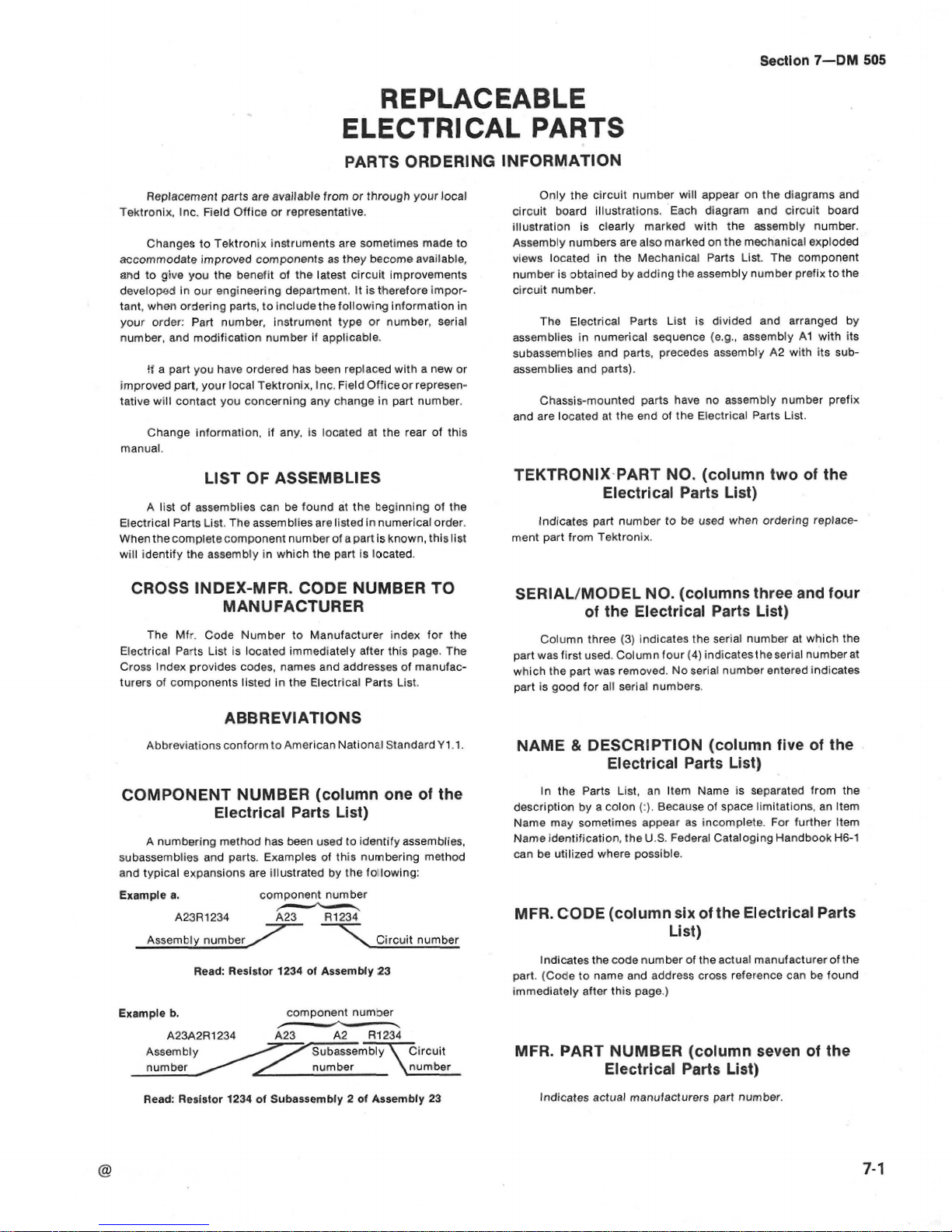

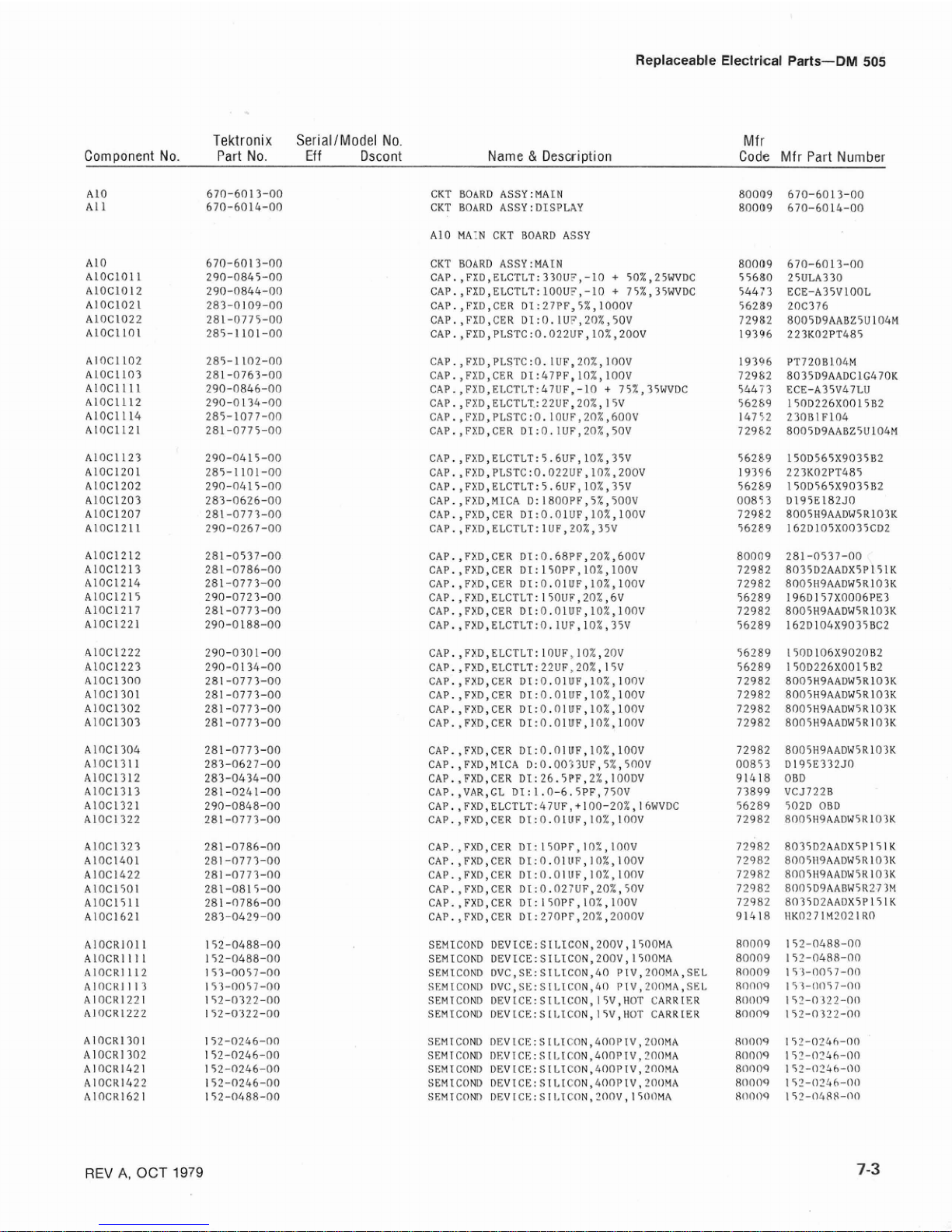

7

REPLACEABLE ELECTRICAL

PARTS

SECTION

8

DIAGRAMS

AND

CIRCUIT

BOARD

ILLUSTRATIONS

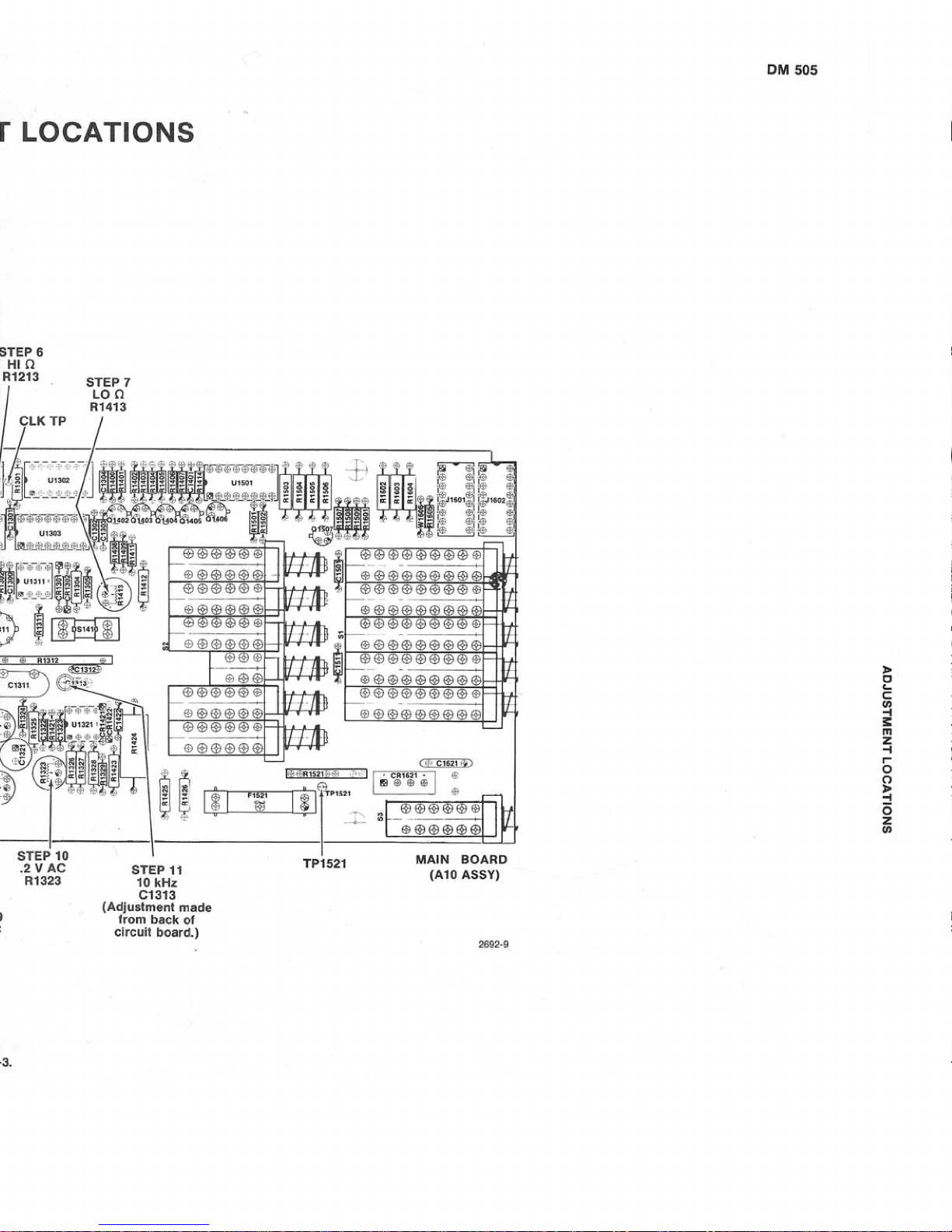

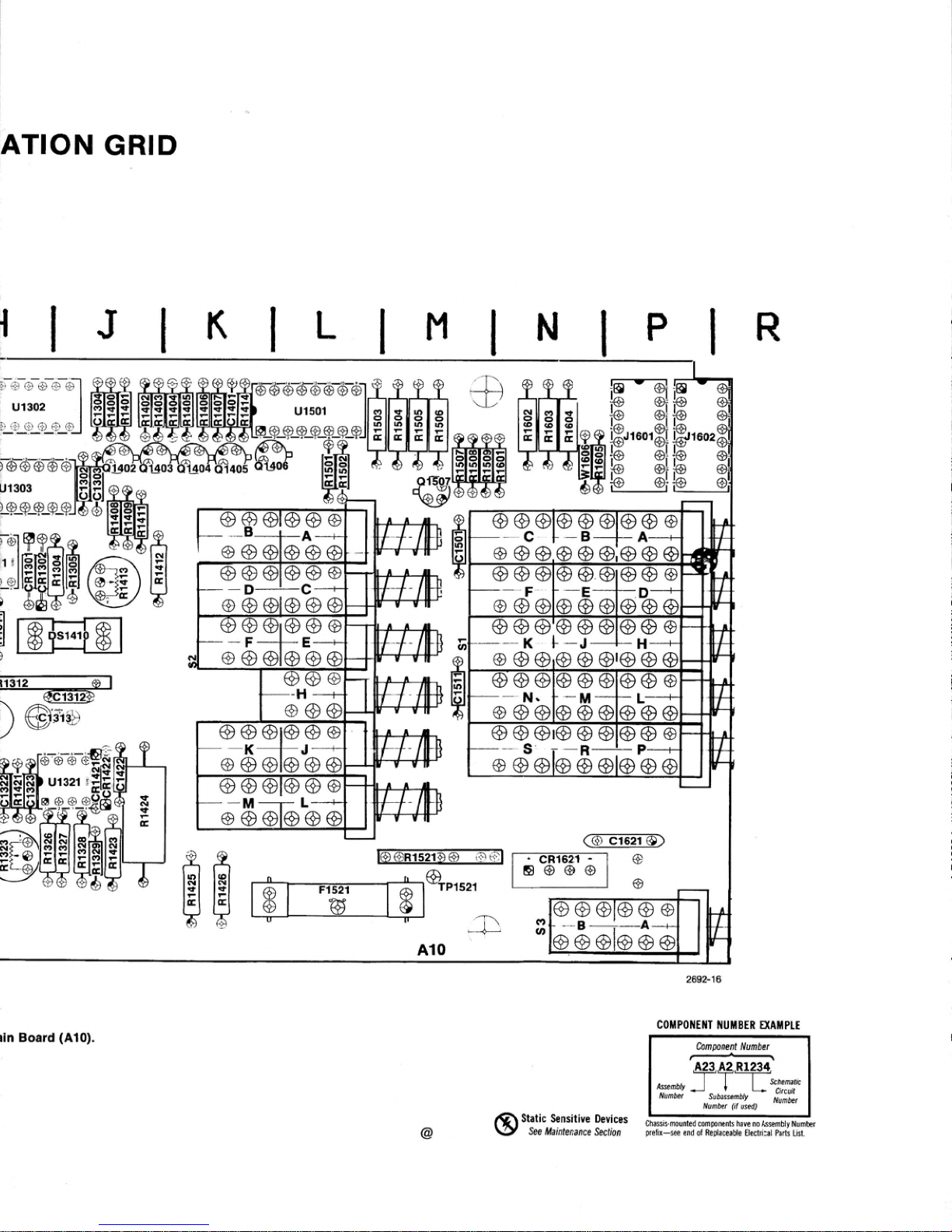

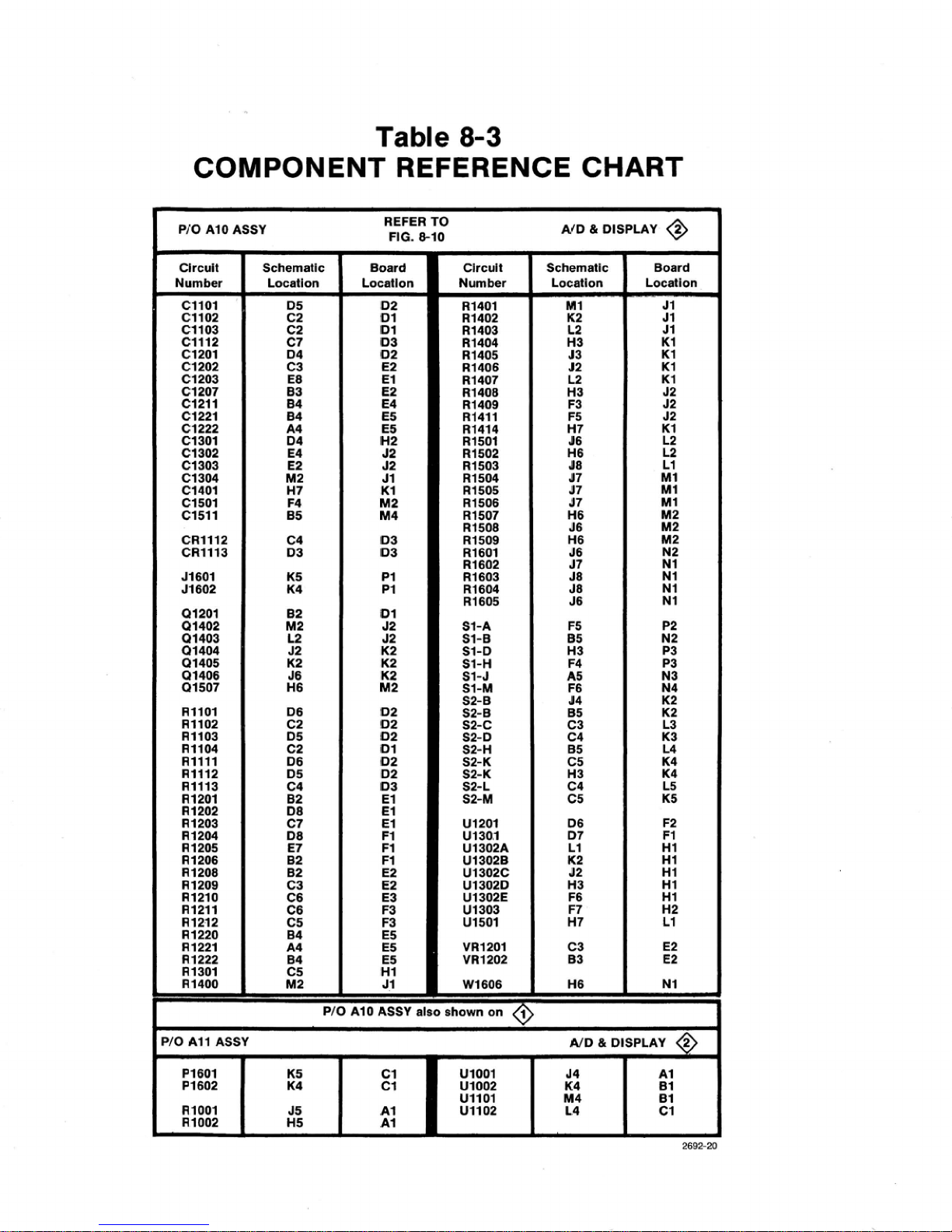

Simplified

Block

Diagram

Rear

Interface

Connections

ND

Block

Diagram

Adjustment

Locations

Troubleshooling

Flow

Charts

Parts

Locations

Component

Reference

Charts

Schematics

SECTION

9

REPLACEABLE

MECHANICAL

PARTS

AND

EXPLODED

VIEW

CHANGE

INFORMATION

iii

Page 6

Fig.

No.

Frontis

LIST

OF

ILLUSTRATIONS

Description

....................................

DM

505

Digital Multimeter

...............................

DM

505

Installation and Removal

............................

Front

Panel

Controls and Connectors

........................

Simplified Diagram

of

the

Ohms

Converter

....................................

Auto-zero timing intervars

..................................

Measurement

interval

timing

DM

505 Simplified Block

Diagram

8-2

A/D

Converter Block

Diagram

8-3

Adjustment Locations

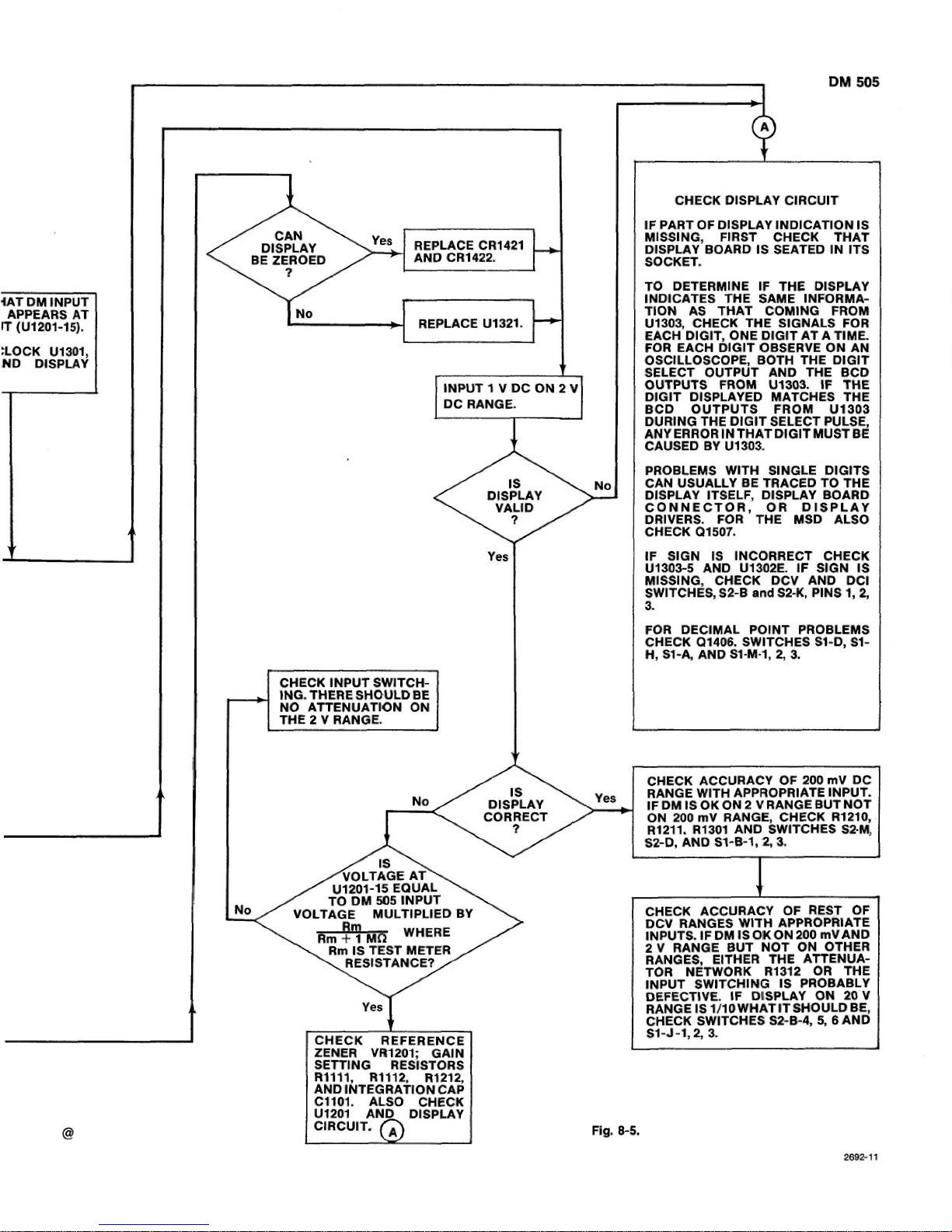

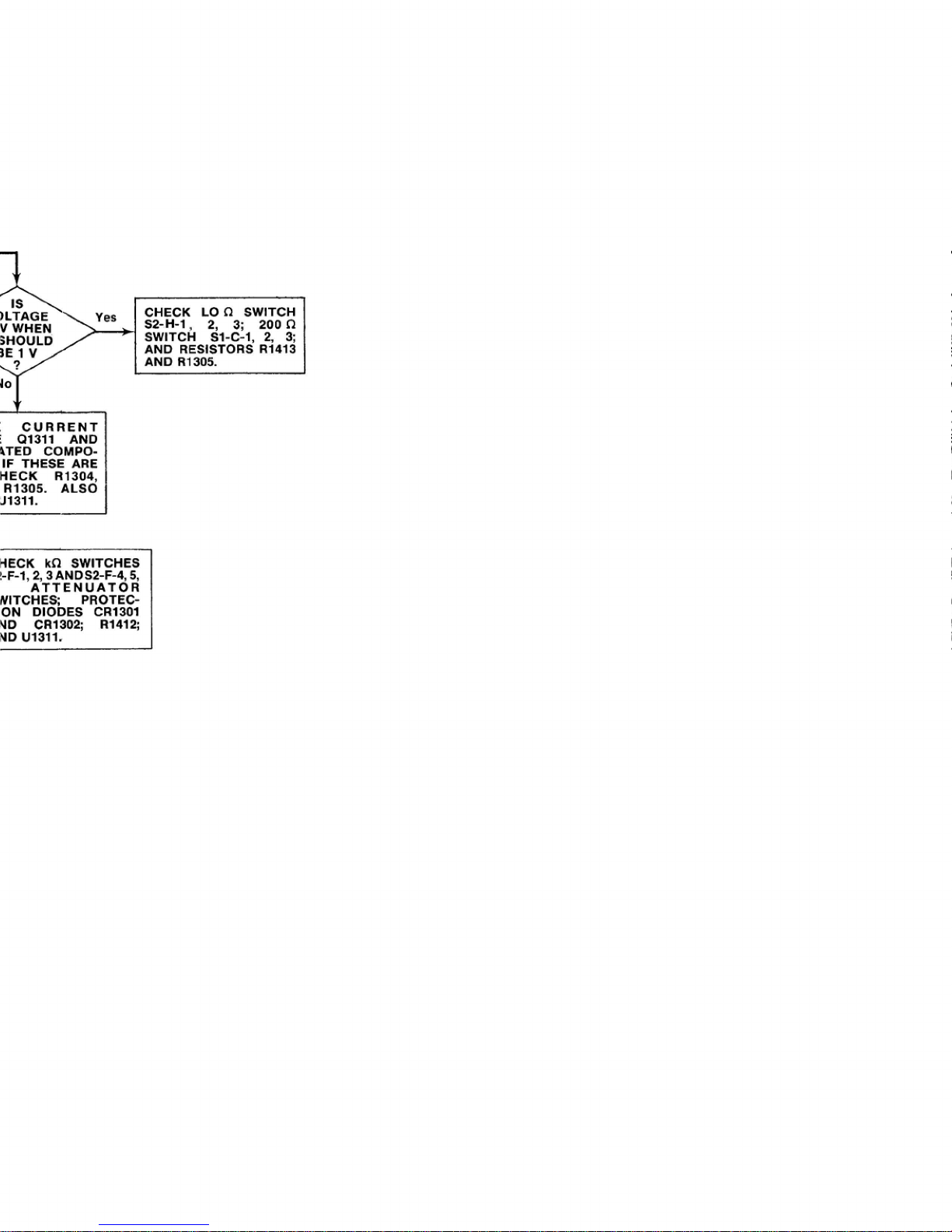

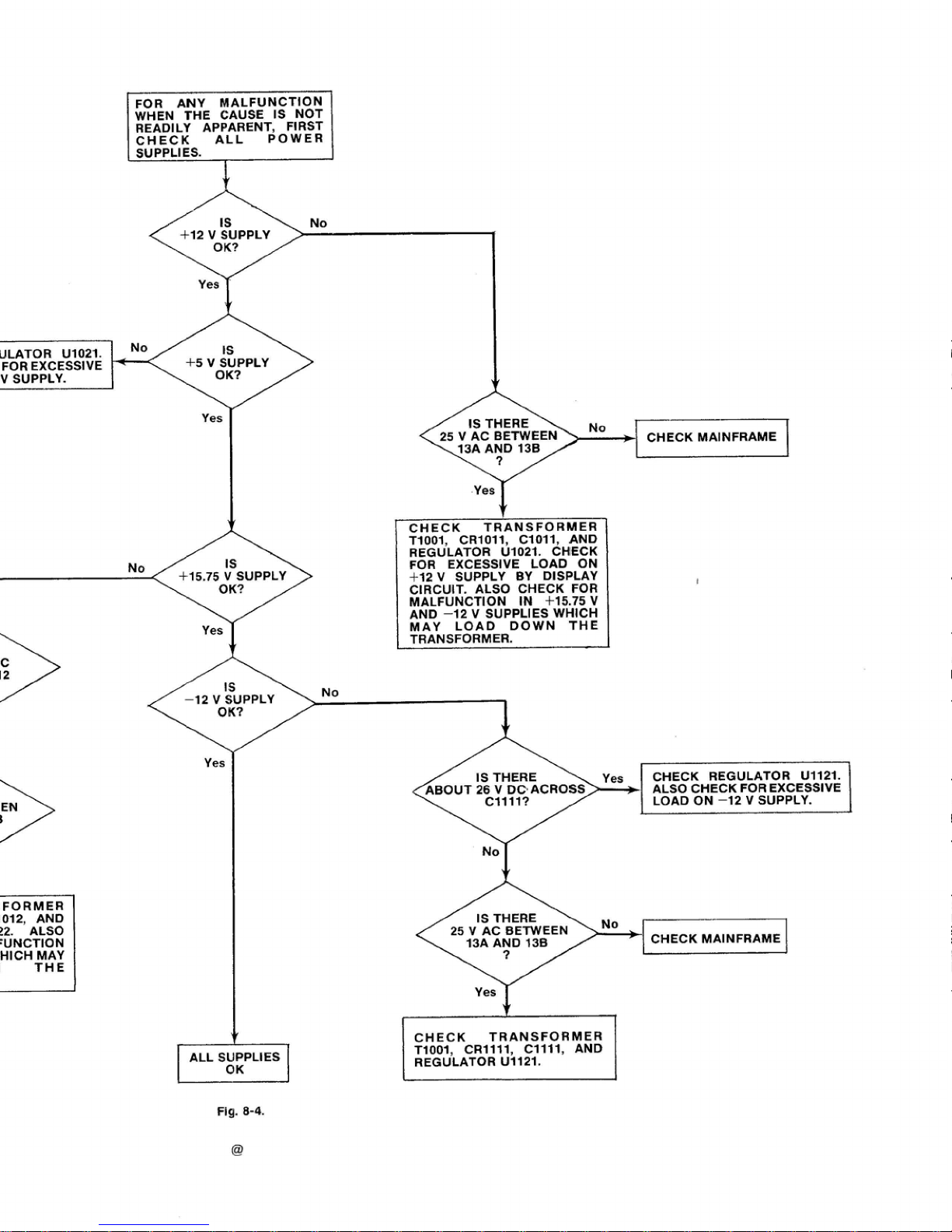

TROUBLESHOOTING

FLOW

CHARTS

Power

Supplies

Dc

Volts

Dc

Current

Ohms

Ac

Volts

Ac

Current

Main

Board

(A10)

Display

Board

(A1

1)

Page

No.

Page 7

LIST

OF

TABLES

Title

Page

No

.

ELECTRICAL CHARACTERISTICS (Front Panel)

1-1

DcVoltmeter

................................................

1-1

.................................................

1-2

AC

Voltmeter

1-2

..................................................

1-3

Ohmmeter

1-3

ELECTRICAL

CHARACTERlSTlCS

(Rear

Interface)

1-6

DcVoltmeter

................................................

1-4

1-7

AcVoltmeter

................................................

7-5

1-8 Ohmmeter

..................................................

1-6

.................................................

1-9 Miscellaneous 1-7

ENVIRONMENTAL CHARACTERISTICS

1-10

DM

505

Only

................................................

1-7'

..............................................

1-1

1

TM500Systems

1-8

PHYSICAL CHARACTERISTICS

Physical

Characteristics

........................................

1-9

.....................................

Current

Mode

input

Resistance

2-4

...............................

Ohmmeter Source Current

and

Voltage

2-5

Ohms

Converter Source Current

and

Maximum Full-scale Voltage

............

3-2

List

of

Equipment Requirements

....................................

4-1

............................................

Dc

Voltage

Accuracy

4-3

Ac

Voltage

Accuracy

.........................

...

................

4-4

................................................

Ohms Accuracy 4-6

............................................

Dc

Current Accuracy

4-6

............................................

Ac

Current Accuracy 4-7

Dc

Voltage Accuracy for

Rear

l

nterface

...............................

4-7

...............................

Ac

Voltage

Accuracy

for

Rear l nterface 4-8

...................................

Ohms Accuracy

for

Rear

Interface

4-8

.......................

Relative Susceptibility

to

Static Discharge

Damage

5-2

Rear

Interface

Connector

Assignments

Component

Reference

Chart

@

Component

Reference

Chart

@

Page 8

Page 9

OPERATORS

SAFETY

SUMMARY

The general

safety

information in this

part

of

the

summary is for both operating and servicing

personnel.

Specific

warnings

and

cautions will be

found

throughout

the

manual

where

they

apply,

but

may

not

appear

in

this

summary.

TERMS

In

This

Manual

CAUTION

statements

identify conditions

or

practices

that could

result

in damage

to

the

equipment

or

other

property.

WARNlNG

statements

identify conditions

or

practices

that

could

result

in

personal

injury

or

loss

of

life.

As

Marked

on

Equipment

CAUTION

indicates

a

personal

injury

hazard

not immediately accessible

as

one

reads

the

marking, or

a

hazard

to

property

including

the

equipment itself.

DANGER

indicates

a

personal

injury

hazard

immediate1

y

accessi

bleas

one

reads

the marking.

SYMBOLS

In

This

Manual

This

symbol indicates

where

applicable cautionary

or

other information

is

to be

found.

As

Marked

on

Equipment

/j

DANGER

-

High

voltage.

@

Protective

ground (earth) terminal.

ATTENTION - refer

to

manual.

vii

Page 10

Power

Source

This

product is intended to operate in a power module connected

to

a

power source that will

not

apply

more than

250

volts rms between the supply conductors or between either

supply

conductor

and

ground. A protective ground connection by

way

of

the grounding conductor

in

the

power

cord

is essential for

safe

operation.

Grounding

the

Product

f

his product

is

grounded through

the

grounding conductor of the power module power cord.

To avoid

electrical

shock,

plug the power

cord

into a properly

wired

receptacle before

connecting to

the

product input or output terminals.

Upon

loss

of

the protective-ground

connection,

all accessible conductive

parts

(including knobs and controls

that

may

appear

to

be

insulating), can render

an

electric

shock.

Use

the

Proper

Fuse

To

avoid fire hazard, useonly the fusespecified in

the

parts list for your

product,

and

which

is

identical

in

type, voltage rating,

and

current rating.

Refer fuse replacement

to

qualified service personnel

Do

Not

Operate

in

Explosive

Atmospheres

To

avoid explosion,

do

not operate this product in

an

atmosphere of explosive gases unless

it

has been specifically certified for such operation.

De

Not

Remove

Covers

or

Panels

To

avoid personal injury,

do not

remove

the

product covers

or

panels.

Do

not operate the

product without

the

covers

and panels properly installed.

Do

Not

Operate

Without

Covers

To

avoid personal injury, do not

operate

this pr~duct without

covers

or panels installed.

Do

not

apply power to the plug-in

via a plug-in extender.

viii

Page 11

SERVICING

SAFETY

SUMMARY

FOR

QUALIFIED

SERVICE

PERSONNEL

ONLY

Refer

also

to

the

preceding

Operators

Safety

Summary.

Do

Not

Service

Alone

Do

not

perform internal service or

adjustment

of

this

product unless

another

person capable

of

rendering first aid and

resuscitation

is present.

Use

Care

When

Servicing

With

Power

On

Dangerous

voltages

exist

at

several

points

in

this

product.

To

avoid

personal injury,

do

not

touch

exposed

connections

and

components while power

is

on.

Disconnect

power

before

removing protective

panels,

soldering,

or

replacing corn

ponents.

Power Source

This

product

is

intended to

operate

in

a

power

module

connected

to

a

power

source

that

will

not

apply

more

than

250 volts rms

between

the

supply

conductors

or

between

either supply

conductor

and

ground. A protective ground connection

by

way

of

the

grounding

conductor

in

the

power cord is essential

for

safe

operation.

Page 12

Page 13

Section

1-DM

505

SPECIFICATION

Introduction

The

DM

505

Digital M ultimeter measures

resistance,

dc

or

ac

voltage, and

dc

or

ac current.

The

AC

functions

respond

to

the average value of an

ac

current or voltage

and

the

readout displays the sinusoidal rms value. In the

resistance

mode

of

operation, the HI

n-LO

fi

pushbut-

ton selects either

of

two

full-scale

probe

tip voltages.

The

front panel

pushbuttons

select the functions and

ranges.

The

INPUT pushbutton selects front panel

con-

nector input

(

EXT)

for current, voltage

and

resistance

measurements, or

rear

interface

connector input (INT) for

voltage

and

resistance measurements.

The

readout is

a

3

1/2

digit display

using

seven-segment

LED.

The

decimal

point

is automaticaSly positioned

by

the range pushbut-

tons.

The polarlty signs for

dc

voltage and dc current

measurements are

also

displayed automatically.

A

blink-

ing display indicates overrange except

on

the

1000

Y

dc

and

500

Y

ac

ranges.

The

reading rate

IS

approximately

three readings per second.

Performance

Conditlons

The

electrical characteristics

are

valid only

if

the

DM

505

has been calibrated

at

an ambient temperature

between

+21°C

and

i-25"

C

and

is operating

at

an ambient

temperature between

O0

C

and

4-50"

C,

unless otherwise

noted.

Items listed

in

the Performance Requirements

column

of

the Electrical Characteristics are verif

led

by

completing

the Performance

Check

in

this manual. Items listed in the

Supplemental Information column

are not verified in this

manual.

They

areeither explanatory notes or

performance

characterist~cs for

which

no limits are specified.

ELECTRICAL

CHARACTERlSTlCS

Front Panel

Table

1-1

0C

VOLTMETER

Supplemental

information

Characteristics

Accuracy for the

200

mV,

2

V,

20

V,

200

V,

and

1000

V

ranges:

+I

8"

C

to

+28"

C

200

mV

to

200

V

ranges

1000

Y

range

Performance

Requirements

+(O.l%

of reading

+

0.05°h

of full

scale)

f

(0.1%

of reading

+

O.T%

of

full

scale)

O°C

to

+18"C,

+28"C

to

+50°C

200

mV

to

200

V

ranges

1006

V

range

Common

Mode

Rejection

Normal

Mode

Rejection Ratio

Maximum Resolution

Response Time

Input Resistance

it(0.2%

of

reading

+

0.1

%

of

full scale)

f

(0.2%

of reading

f

0.2%

of

full scale)

3100

dB

at

dc.

280

dB

at

50

to

60

Hz.

350

dB

at

50

and

60

Hz

k0.2

Hz.

Verified with

1

kR

unbalance at

the

LOW

terminal.

(Clock frequency:

20.48

kHz

tl%.)

1

00

pV

<0.5

second to rated accuracy.

f

0

Mfl

f

0.5%.

Page 14

Table

1-1

(cont)

Table

1-2

AC

VOLTMETER

Characteristics

Maximum

lnput

Voltage

VOLTS/R

to

LOW

1-2

REV

A

OCT

1979

Performance Requirements

Supplemental

Information

1000

V

peak.

VOLTS/R to Ground

LOW

to

Ground

Supplemental Information

Charaderlstics

Accuracy

for

the

200

mV,

2

V,

20

V,

200

V

and

500

V

ranges:

+lBO

C

to

+28'

C

200

mV

to

200

V

ranges

45

Hz-10

kHz

sine

wave

25-45

Hz,

10-20

kHz

sine

wave

1000

V

peak.

1000

V

peak.

Performance

Requirements

f

(0.5%

of reading

+

0.1

%

of full scale)

f

(1%

reading

+

0.1%

of

full

scale)

500

V

range

25

Hz-10

kHz

sine wave

f

(1%

of

reading

1-

0.4%

of full scale)

0°

C

to

+18"

C,

+28"

C

to

4-50" C

200

mV

to 200

V

ranges

45

Hz-10

kHz

sine

wave

&(I%

of

reading

+

0.15%

of

full scale)

25-45

Hz,

1G20

kHz

sine

wave

f

(1.5%

of

reading

+

0.15% of

full

scale)

500

V

range

25

Hz-10

kHz

sine

wave

Common

Mode

Rejection

Ratio

Maximum Resolution

Response

Time

f

(1.5%

of reading

+0.6Oh

of

full scale)

250

dB

at

50

to

60

Hz.

Verified with

1

kR

unbalance

at

the

LOW

connector.

100

pV.

<1.5

seconds,

within

specified

accuracy

on

measurements

within

any

one

range.

Input

Impedance

Maximum

lnput Voltage

VOLTS/R

to

LOW

10

MR

+0.50J0

paraHeled

by

less

than

130

pF.

566Y

ac

rms

or600Vdc,

nottoexceed

1000

Y

peak.

VOLTS/fl

to

Ground

LOW

to

Ground

500

V

ac

rms

or

600

Vdc,

not

to

exceed

1000

V

peak.

500

V

ac

rms

or

600

Vdc,

not

to

exceed

1000

V

peak.

Maximum

Volt-Hz

Product

107

VaHz.

Page 15

Table f -3

OHMMETER

f

f

8°C

to

+2a°C

200

R

range

200

R

range

pproximatel

y

f

6

V.

Table

1-4

PC

AMMETER

CharaeZerEstlcs

Accuracy

for

the

200

PA,

2

rnA,

20

mA,

200

rnA

and

2000

mA

ranges:

+lg°C

to

+2g°C

0°Cto+180C,+z80Cto+~~0C

Response

Time

Maximum

Open

Circuit

Input

Voltage

mA

to

LOW

Performance

Requirements

f

(0.3%

of

reading

+

0.05% of

full

scale)

f(O.4Y0ofreading+O.l%offullscale)

Supplemental

Information

<0.5

second.

250

V

peak.

Page 16

TaMe

1-4

(cont)

Characteristics

Maximum

Floating

Voltage

mA

to

Ground

Low

to

Ground

Table

1-5

1000

V

peak.

1000

Y

peak.

Maximum Resolution

kC

AMMETER

Performance

Requirements

0.1

PA.

Accuracy

for

the

200

PA,

2

mA,

20

mA,

200

mA,

and 2000

rnA

ranges:

45

Hz

to

10 kHz

Response f ime

Maximum

Open

Circuit

Input

Voltage

Maximum

Floating Voltage

Supplemental

Information

ELECTRICAL

CHARACTERISTICS

Rear

Interface

fable

1-6

DC

VOLTMETER

Characteristics

Performance Requirements Supplemental

1nformatlon

Accuracy

for

the

200

mV,

2

V,

20

V,

200

V

and

1000 V ranges:

200

mV

to

200

V

ranges

1000

V

range

f

(Q.tYo

of

reading

+

0.05% of full scale)

f

(0.1%

of

reading + 0.1%

of

full

scale)

Page 17

Table

1-6

(cont)

Supplemental

Information

200

mV

to

200

V

ranges

1000

V

range

f

(0.2%

of

reading

4-

0.1%

of

full

scale)

f

10.2%

of

reading

t

0.2%

ot

full

scale)

Maximum

Resolution

--

Response

Ti

rn

e

lnput

Resistance

<0.5

second

to

rated

accuracy.

Maximum

lnput Voltage

Pin

28B

to

Pin

28A

200

V

peak.

Pin

28B

to

Ground

200

V

peak.

Pin

28A

to

Ground

200

V

peak.

Table

1-7

AC

VOLTMETER

Performance

Requirements

Supplemental

Imformation

Charaderisttics

Accuracy

for

the

200

mV,

2

V,

20

V,

200

V

and

500

V

ranges:

200

mV

to

2

V

ranges

45

Hz-10

kHz

sine

wave

f(0.5%

of

reading

f

O.lP/o

of

full

scale)

25-45

HZ,

110-20

kHz

sine

wave

20

V

to

200

V

ranges

25

Hz-20

kHz

sine wave

f

(I0h

of

reading

+

0.1%

of

full scale)

+(lO/o

of

reading

+

0.I0/o

of full scale)

500

V

range

(max.

input:

200

V)

25

Hz-10 kHz

sine

wave

f

(1%

of

reading

-t

0.4O/o

of full

scale)

200

mV

to

2

V

ranges

45

Hz-10 kHz

sine

wave

25-45

Hz,

10-20

kHz

sine

wave

20

V

to

200

V

range

f

(1%

of

reading + 0.15%

of

full scale)

f

(1.5%

of

reading

+

0.15°h

of

full

scale)

25

Hz-20

kHz sine

wave

f

(1.5%

of

reading

+

0.1

Soh

of

full

scale)

500

Y

range

(max.

input:

200

V)

.

f

(1

-5%

of

reading + 0.6%

of

full scale)

25

Hz-10 kHz

sine

wave

Page 18

Table

1-7

(cont)

Table

1-8

OHMMETER

+lB°C

to

+28OC

200

!J

range

200

fl

range

reading

$

0.15%

of

full

scale

Supplemental

Infwrnation

I00

pV

<I

.5

seconds,

within

specified

accuracy

on

measurements

within

any

one range.

200

V

peak.

200

V

peak.

200

Y

peak.

Characteristics

Maximum

Resolution

Response

Time

Maximum

l

nput

voltage

Pin

288

to

Pin

2814

Pin

288

to

Ground

Pin

28A

to

Ground

Maximum

Volt-Hz

Product

lo7

V~HZ.

Performance

Requirements

Page 19

Table

1-9

MISCELLANEOUS

ENVIRONMENTAL

CHARACTERISTICS

Table

1-10

DM

505

ONLY"

Operating

Operating

i-30°C

and

+50°C

at

90%,

1-5

-O%I~

-T-28800B,

class 5 with

Operating

0.64

mrn

(0.025")

disp.,

5-55-5

H?

Test

to

MI L-t-28&00B, class

3.

(sine

wave)

75

min. total.

Non-operating

50 g (1/2

sine)

11

ms*

Test

to MIL-T-288OOB, class

3.

Operating

45O

or

4"

or

equilibrurn,"'

Test

to

M

l

t-T-28800B, class

3.

Supplemental

lnformatlon

Approximately

8

W.

Characteristics

Power

Consumption

Performance

Requlrements

Reading

Rate

Over-range

Cali

bration

Interval

Warm-up

Tirna

3

per

second.

Flashing display

(except

1000 V dc and

500

Y

ac

ranges).

fOOQ

hours

or

six

months, whichever

occurs

first.

30

minutes

(60minutesaFterstorage

in

high

humidity

environment).

Page 20

Table

1-10

(cont)

'See

Table

1-11

for

system

envfronmental characterlstlcs.

Characteristics

E.M.C.

Operating

Electrical Discharge

Operating

Transportation

with

power

module.

Description

30

Hz

to

1

GHZ~

Test

to

MI

L-T-288008,

class

3.

20

kV

rna~.~

Charge applied to

each

protruding

area

of

the

product under test except the input

terminals.

Qualified under National

Safe

Transit

Association Preshipment Test Procedures,

Project

1

A-B-1

and

Project

t A-B-2.

'without

power

module.

d~ernperature:

Durlng

$ow

temperature

test

MIL-T-28800B,

paragraph

4.5.5.1.3(b)

for

dass

5,

steps

4

and

5

shall

be

per-

formed

before

step

2,

Also,

the

instrument shall not

be

operating

durhg

step

6,

paragraph

4.5.51.3(e),

class

5.

Whlle

aperating,

condensed

molsture

shall not

be

present

on

class

5

Instruments.

Drying

of

the

instrument

for

thFs

class

may

be

performed

in

a

suitable

chamber,

if

necessary.

CHumldlty: The

20

V

ac

and

200

Y

ac

ranges

shall

be

derated

to

f

25%

of

readlng

+2

counts.

Note:

All

performance

requirements

are

met

while

operating

at

w95%

relative humldlty

at

f

30°C

and

f

50°C

with

on

hour wnrmup.

Table

1-11

TM

500

SYSTEMS

I

Characteristics

Temperature

TM

501

TM

503

TM

504

TM

506

TM

515

Operating

Non-operating

Meets

same

test standards

as

plug-in.

Meets

same

test

standards

as plug-in.

Humidity

Operating Meets same Zest standards

as

plug-in.

Non-operating

Altitude

Meets

same

test standards

as

plug-in.

Operating

Meets

same

test standards as plug-in.

Non-operating

I

Meets

same test standards

as

plug-in.

Page 21

PHYSICAL

CHARACTERISTICS

Table

1-12

TM

515

0.38

mm

(0.015

in)

disp.

10-55

Hz

(sine

wave)

75

min.

30

g

(1/2

sine)

11

ms,

18

shocks

CharacterlsUcs

TM

501

TM

503

TM

504

TM

506

Characteristics

Deswlption

Bench

Handling

Qperati

ng

Electrical

Discharge

Operating

Transportation

Vibration

Package

Drop

Finish

Net

Weight

Overall

Dimensions

Meets

same

test

standards

as

plug-in.

Meets

same

test

standards

as

plug-in.

Meets

same

test

standards

as

plug-in.

Meets

same

test

standards

as

plug-in.

VI

bration

Operating

Shock

Operating

Anodized aluminum panel

and

chassis.

2.2

I

bs

(exclusive

of

probes)

(1

kg).

2.m

in

(86.8

mm)

W X 11.240

in (285.3

mm) D X

4.961

in

(125.9

mm)

H.

0.26

mm

(0.01

0

in)

disp.,

j0-55

Hz

(sine

wave)

75

min.

total

20

g

(1/2

sine)

11

ms

18

shocks

Page 22

Page 23

Section

2-DM

505

OPERATING

INSTRUCTIONS

Installation Instructions

The

DM

505

is calibrated

and

ready to

use

when

received.

It

operates

in

one

compartment

of

a

TM

500-

series power module. Refer

to

the power

module

i

nstruc

tion manual

for

line voltage requirements and

power

module

operation.

Turn

the

power

module

off

before

inserting

the

plug-

in;

otherwise,

damage

may

occur

to

fhe

plug-in

drcuitry.

Check to

see

that

the

plastic barriers on the inter-

connecting

jack

of

the selected

power

module

compart-

ment

match

the cut-outs in

the

DM

505 circuit

board

edge

connector.

Align

the

DM

505

chassis

with

the upper

and

lower

guides

(see

Fig.

2-1)

of

the

selected

compartment.

Push

the

DM

505

in

and

press

firmly

to

seat

the

circuit

board

in

the interconnecting

jack.

Pull

out

the

power

switch

Qn

the

power

module.

One

or

more

characters

in

the

LED

display should now

be

visible.

To

remove the

DM

505,

pull

on

the

release

latch

(located

in

the

lower

left

corner)

until

the

i

ntereonnecting

jack

disengages and the

DM

505 slides

out.

Rg.

2-1.

DM

505

Installation

and

remova!.

Page 24

CONTROLS

AND

CONNECTORS

DISPLAY

@

Display

3

1/2

digit

LED

readout with decimal point

auto-

matically positioned by

the

range pushbuttons.

VOLTS

Selects

dc

voltage function.

@VOLTS

AC

pushbutton

Selects

ac

voltage function.

RESISTANCE

@

kn

pushbutton

Selects resistance function,

Pushbutton

In

selects full scale probe

tip

voltage

of

0.2

V

in all ranges. Pushbutton

out

selects full scale

probe

tip

voltage

of

2

V

except

in the

200

R

range

which is

0.2

V.

CURRENT

Selects dc current function.

@m~

AC

pushbutton

Selects

ac

current function.

CONNECTORS

A

Refer to Input Connections in theoperating Instruc-

tions.

@

mA

Connector

Use

with

LOW

input connector for current

measurements.

@

LOW

Connedw

Common input

connector

for all measurements.

@

voLTwn

Connector

Use

with

LOW

input

connector

fw

voltage

and

resistance measurements.

@

Ground

Binding

Post

Chassis ground.

RANGE

SELECTION

@

Range

Select

Pushbuttons

Select

the

desired measurement range.

@

Release

Latch

Pull

to

remove plug-in.

@

IN

PUT

EXT- I NT

Pushbunon

Refer

to

Input Connections

in

the

Operating Instruc-

tions.

Pushbutton

out

{EXTI

selects front

panel

input con-

nectors;

pushbutton

in

(INTI selects rear interface

input

terminals for

dc

and

ac

volts

and

resistance

measurements only.

OPERATORS

FAMILIARIZATION

General

Operating

lnf

ormation

With the DM

505

properly installed

in

the

power

module, allow thirty minutes warmuptimefor operation

to

specified

accuracy. Select

the

desired measurement f unc-

tion

and

range.

When

the

value

of

the

quantity

being

measured

is

unknown,

setect

the highest

range first.

Decrease

the

range

setting

until the display blinks to

indicate over-range. Then

change

the range pushbutton

to the

next

higher range. This method obtains

maximum

resolution.

1

WARNING

)

To

avoid

shock

hazard

from

voltages

measured

by

the

DM

505:

I,

Avoid

all

contact

with

the

voltage

source

being

meas

wed.

2.

Disconnect

probes

from

circuit

undertest

before

disconnecting

probes

from the

DM

505,

or

before

removing

the

DM

505

from

the

power

module.

Page 25

Operating Instructions-DM

505

cor

Fig.

2-2.

Front panel controls and connectors.

Page 26

Input

Connections

A

DC

Current

Measurements

The INPUT EXT-INT pushbutton selects front panel

or

rear Interface input.

Three input connectors provide front panel measure-

ment connections. The

YOLTS/Tr

and

LOW

input connec-

tors are used for

ac

or dc voltage

or

resistance

measurements.

The

mA and LOW input connectors are

used for

ac

or

dc

current measurements. Rear interface

pins 28B

(HI)

and

T8A

(LO) are used for rear interface

voltage and resistance measurements.

Norml

rneasure-

rnent conditions

are

with the

LOW

terminal ungrounded.

A

connection between the

LOW

input connector and the

ground terminal may be made to

referencetheinput tothe

DM

505

chassis

ground.

Use

caution,

as

the Lowterminal

is then connected

ta

earth ground through the power

module three-wire

power

cord. False readings may

be

obtained due to ground loops.

The

maximum

input

voltage

is

I

kV

peak

at

the

front

panel

connectors and

200

Y

peak

at

the

rear

inter-

face

connectors.

The

front

panel

VOLTSIfl

and

LOW

connectors

may

be

floated

at

I

kVmaximum

above

ground.

fhe

rear

input

connector

200

V.

Sine-wave

Response

The

DM

505

responds to the average value

of

an

ac

or

dc current or voltage and the readout displays the

sinusoidal rms value. The effective or rms

value

of a sine-

wave

is

0.707 times the peak voltage or current.

The

average

value

is

0

636

of

the

peak

value. The scale factor of

the

DM

505 is 0.636/0.107 or 0.9.

To

obtain the average

value

of

a

sinusoidal input voltage or current, multiply the

DM

505

readout

by

0.9.

'DC

Voltage

Measurements

Press the VOLTS

DC

pushbutton and an appropriate

range button. Apply the voltage to be

measured

to

the

LOW and

VOLTS/n

input connectors. 0 bserve

the

max-

imum input voltage ratings

as

indicated on the front panel.

The readout displays

a

f

if the input to the VOLTS/R

connector

is

positive with respect to the

LOW

input

connector.

A

-

is

displayed

if

the input

at

the

LOW

input

connector

is

the more positive. With the

LOW

and

VOLTS/n input connectors shorted, the display reads

zero

+

one count.

Press

the

mA

DC

pushbutton

and

an appropriaterange

button. Connect the

dc

current to

be

measured tathe

LOW

and

mA

input connectors. Conventional current flowing

into the

mA

connector and out

of

the

LOW

connector

(or

electron

flow

into the

LOW

connector and out

of

the mA

connector) indicates

a

+

on the display. The input

resistance in the current mode is listed in Table

2-T.

Table

2-1

AC

Voltage

and

Current

Measurements

CURRENT

MODE

INPUT

RESISTANCE

For ac voltage measurements, press the VOLTS

AC

pushbutton and an appropriate

range

button. Connect

the

unknown voltage

to

the LOWand VOLTS/R input connec-

tors.

Range

200 PA

2

mA

20

mA

200

mA

2000

mA

To measure

ac

current,

press

the

rnA

AC

pushbutton

and an appropriate range button. Connect the unknown

ac current

to

be measured to the

mA

and

LOW

input

connectors. The input resistance in

the

current mode

is

listed in Table 2-1.

Approximate

Resistance

1001

R

100.4

R

10.25

R

1.2

R

0.25

R

Resistance

Measurements

Press the

kfl

pushbutton and

an

appropriate

range

button.

Also,

press

the

HI

n-LO

fl

button for

a

maximum

full-scale probe-tip voltage

of

0.2

V.

Release the HI n-LO

R

button

(out

position) for a maximum full-scale probe-tip

voltage

of

2 V (except on the

200

fl

range which is

0.2

V).

The

low probe-tip voltage is

useful

for

making

in-circuit

measurements without forward-biasi ng silicon diodes or

transistor junctions.

The

kR

mode

provides an accurate constant current

at

the

LOW

and VOLTS/n input connectors. Refer to Table

2-1

for the value

of

current and maximum voltages across

the input terminals for full

scale

display readings (instru-

ment

not

over-ranged). The maximum (open circuit)

voltage available from the

YOLTS/fl terminal to the LOW

terminal

in

the

resistance

mode

is about

+6

V.

REV

A

OCT

1979

Page 27

Operating

rnstructions-DM

505

Ta'ble

2-2

If

the Tektronix instrument is

to

be

shiw~ed

to

a

. .

OHMMETER

SOURCE

CURRENT

AND

VOLTAGE

Tektronix

Service Center

for

service or repair, attach

a

tag

showing owner

(with

address) and the name

of

an

Packaging

Information

individual

at

your firm

that

can

be

contacted. Include

the

complete instrument serial number and a description of

the

service required.

Save

and

re-use

the

package

in which your i nstrurnent

was

shipped. If

the

original packaging

is

unfit

for

use

or

not available, repackage

the

instrument

as

follows:

Surround

the

instrument with polyethylene

sheeting

to

protect the finish of

the

instrument. Obtain

a

carton

of

corrugated cardboard

of

the

correct

carton

strength

and having

inside dimensions

of

no

less

than 6 inches

more

than the instrument dimensions. Cushion the

instrument

by

tightly packing 3 inches

of

dunnage

or

urethane foam between carton and instrument on

all

sides.

Seal

the

carton with shipping tape or

an

in-

dustrial stapler.

A

list

of

standard aecessaries

(and

part numbers)

is

The

carton

test

strength

for

this instrument is

200

located

in

the Replaceable Mechanical

Parts

list.

pounds

per square inch.

Page 28

Page 29

Section

3-DM

505

THEORY

OF

OPERATION

The

basic circuitry

of

the

DM

505

consists

of

an analog-

to-digital

(AID)

converter, display decoders and drivers,

a

clock,

and

power supplies (see the Block Diagram in the

Diagrams section at the back

of

this

manual). These

sections form

a

digital voltmeter that

measures

1.999 Vdc

full

scale.

A gain switch in the

AID

converter allows

measurement

of

199.9

mV

full scale.

An

attenuator

enables

measurement of

19.98,

199.9,

and 1000

Vdc

full

scale.

Ac

voltages are measured by passing the input

signal through

a

precision rectifier circuit

that

converts

ac

voltages to dc (an

ac

converter). Resistances are

measured

by

forcing a known current

from

the

ohms

converter through

the

unknown resistanceand measuring

the voltage across the unknown resistance.

Low

resistance current shunts permit measurement of

ac

and

dc currents.

NOTE

In

the

following

descriptions,

the

mond

by

each

tjtle

refers

to

the

circuit diagram in

the

Diagrams

manual.

numbered

dia-

,

corraspondrng

section

of

this

Attenuator

and

Input

Switching

@

With the

INPUT

EXT-INf pushbutton

in

the EXf

position,

the

input

is

measured at the front panel connec

tors. Resistances and voltages are measured between the

VOLTS/R

and

LOW

connectors

and

current

is

measured

between the

mA and

LOW

connectors.

In

t

he

I

NT

position,

switch

S3

A,8

selects

the input at rear interface pins

288

(HI) and

28A

(LO)

for rear interface measurement

of

resistances and voltages. Thef ront panel input impedance

is

10

MR

paralleled

by

less than

100

pF.

The

VOLTS/R and

LOW

input connectors are con-

nected across

R1312, a voltage divider.

An

input measured

from

thejunction

of

R13$2A

and R1312B

is

attenuated by

a

factor of

100.

On

the 1 kVdc scale,

the

input is measured

from

the

junction

of

R1312B and R1312Cand isattenuated

by a factor of 1000.

Capacitors

C1312,

C1313,

and

C1311

compensate

the

attenuator for accurate

ac

signal

measurement. Capacitor

GI313 is

adjusted

at

10

kHzfor

a

flat frequency response.

One

solder-in shield and two additional shields

at-

tached just inside the

side

covers

shunt

stray capacitance

across the attenuator to ground when measuring floating

ac

voltages.

AC

Converter

@

In the

VOLTS

AC

mode, dc input voltages are blocked

by

capacitor C2114.

The

input

of

U1321 is protected

against excessive input voltages

by

R1424, CR1421, and

CR1422.

Ac

signals

are

buttered by unity gain amplifier

U1321 and applied to the active rectifier circuit U1211,

which

has

high-speed diodes, CR1221 and CR1222, in the

feedback loop. Thiscircuit configuration eliminatesthe

dc

voltage drop of the diodes.

The

half-wave rectified

ac

is

filtered

by

three-pole filter R1221, '21222, R1222, C1211,

Ri220,

and C1221 to provide ripple-free

dc

voltage

to

the

A/D

converter.

The

active rectifier and filter respond

to

the

average

value

of

an ac signal,

but

the

circuit gain is

calibrated to produce

a

dc

output equivalent

to

the rms

value of

a

a1

ne-wave input.

The

basic

gain

of the

ac

converter is adjusted by

R1322

for the

2

Yac

range

and

R1323 fine-trims the gain for

200

mVac

range.

l ntegrated circuit U1211

has

feed-

forward compensation provided by

C1212,

Ct

213,

and

R1216 to obtain

maximum

bandwidth,

Both the 20

Vac

and

200

mVac

ranges

use

U1211 at again

10

times the gain

on the

ot

her ranges. The

500

Vac range

connects

R1423

as

an additional attenuator

to

accommodate larger input

voltages.

Dc

feedback for U1211

is

provided by the

network

consisting

of R1223, R1224, and C1223.

Dc

offset

for

U12t

1

is

provided

by

R1321, the

AC f ERO

ADJ.

Ohms

Converter

@

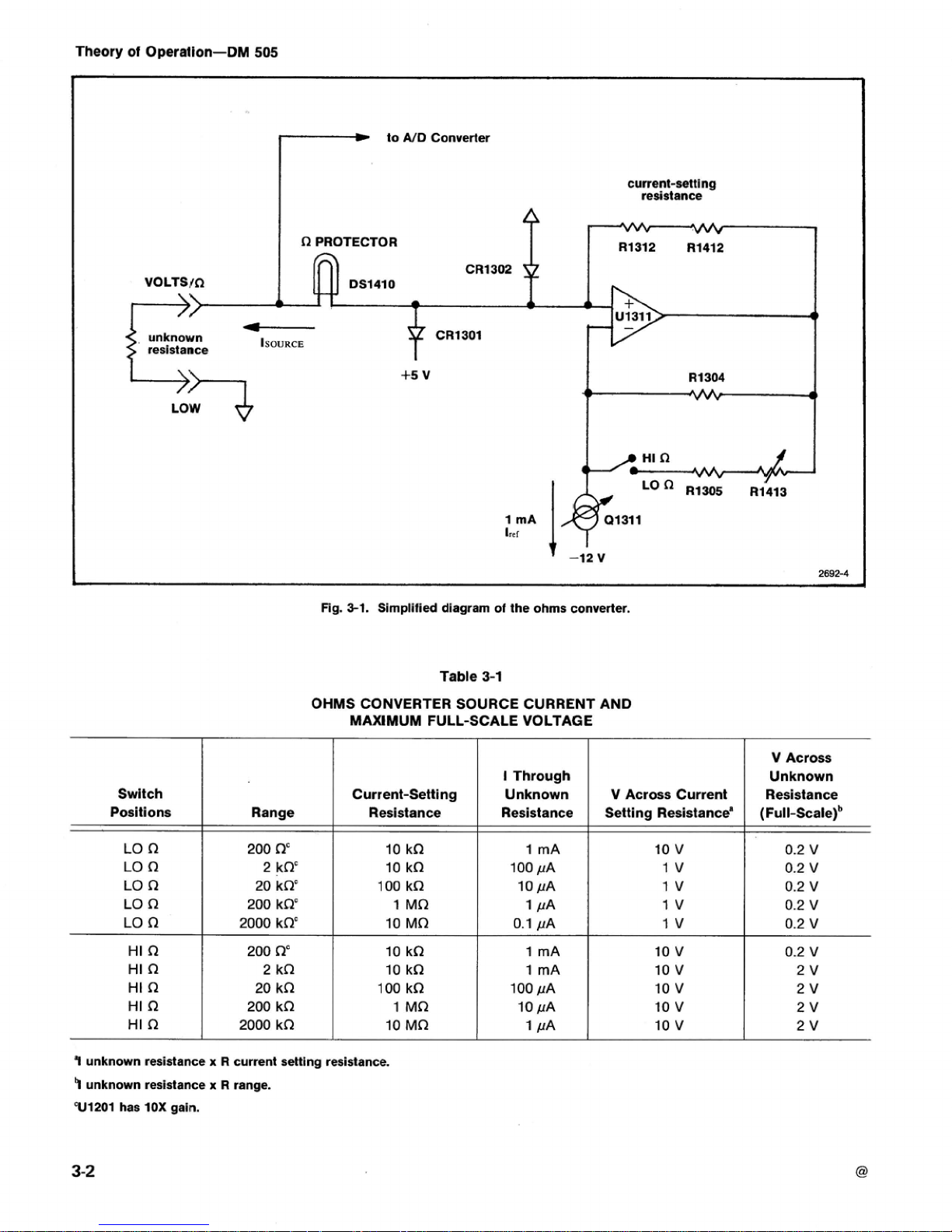

The ohms converter consists of precision current

source

01 31 1

and

floating current mirrar U1311 (see Fig.

3-1). Transistor Q1311 generates a relatively low

temperature coefficient current,

by

mirroring the voltage

from

Zener diode VR1211 across R1215 and R1213.

The

current at

the

collector

of

Q1311 E is approximately

i

rnA

and is adjusted by R1213, the

HI

fl

ADJ.

This

reference

current

from

Q1311 B appears at the inverting terminal

of

U1311. The output of Q1311 sources current through

R1304 to stabilize the reference current. In the HI

R

position, the output

of

U1311 is elevated 10 V above its

input. In the

LO

R

position,

S2-H

connects R1305 and

R1413 in parallel with R1304, lowering the

output

voltage

of

U1311 and reducing thereferencecurrent to U1311 pin

2

by

a

factor of 10. Table 3-1 lists the values

of

source

current for the resistance ranges in the HI

il:

and LO

R

positions. Resistor R1413 adjusts the

LO

reference

current to one-tenth

of

the

HI

Cl

reference current.

Page 30

Theory

of

Operalton-DM

505

I

>

to

A/D

Converter

curred-Wing

reQstance

n

PROTECTOR

~1312 131412

CR1302

VOLTSlR

OS1410

unknown

ISOURCE

CRf

SO1

resistance

+5

V R1304

LOW

tll

R

I

mA

lr

ci

26924

J

Fis

3-1.

Simplified diagram

ol

the

ohms converter.

Table

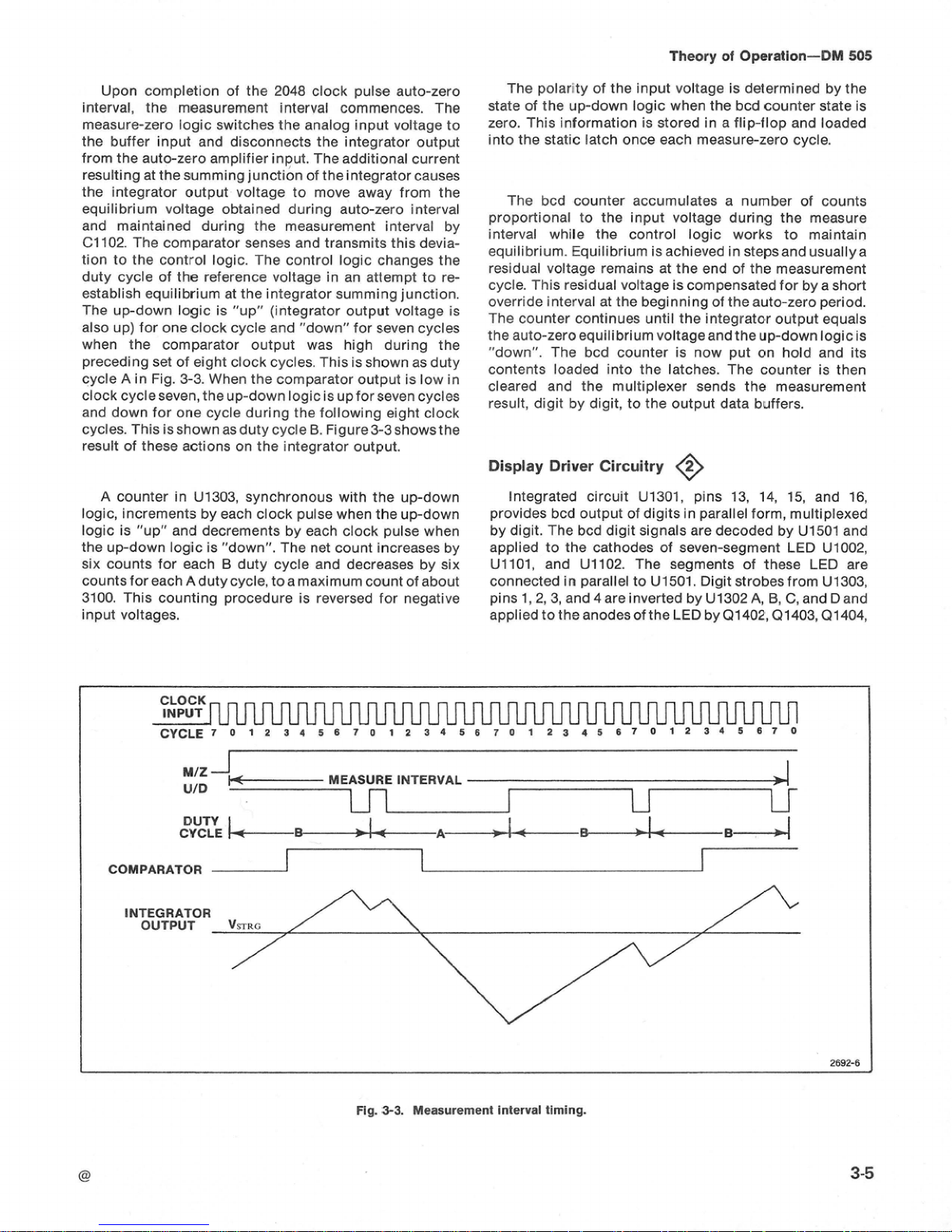

3-1

OHMS

CONVERTER

SOURCE

CURRENT

AND

MAXtMUIYI

FULLSCALE

VOLTAGE

.I

unknown

reslstame

x

R

current

setting

resistance

9

unknown

resistamce

x

R

range.

%I1201

has

1OX

galn.

Swltch

Positions

LO

Sl

LO

n

LO

12

LO

R

LO

R

HI

R

HI

n

HI

R

HI

R

HI

R

Range

---

200

flc

2

k~'

2Q

kRG

200

kQc

2000

kRc

200

RE

2

kn

20

kR

200

kR

2000

kR

Current-Setting

Resistance

I

Through

Unknown

Resistance

10

kR

10

kn

100

kR

1

MR

10

Mfl

10

kR

10

kn

100

kR

1

Mfl

10

MR

V

Across

Current

Setting

Resistance'

V

Across

Unknown

Resistance

(Full-S~ale)~

1

mA

100

PA

10

PA

1

PA

0.1

pA

1

mA

1

m~

100

PA

10

PA

1

PA

10

V

tv

1

V

f

V

1

V

10

V

10

v

10

V

10

V

10

V

0.2

V

0.2

v

0.2

V

0.2

V

0.2

V

0.2

V

2v

2V

2V

2V

Page 31

Theory

of

Operation-DM

505

The output voltage of

U1311

is applied across sections

of

the

attenuator

R1312

(and

R1412for

the

200

kn range)

which

serves

as a current setting resistance. The voltage

across

R1312

and

R1412

is equal to

the

voltage

across

R1304.

The current through

R1312

flows through lamp

DS1410

and out

the

VO

LTS/R terminal through the

unknown resistance. The range switches select sections

of

the attenuator

so

that different values of current can

be

sourced out

of

the VOLTS/I1 terminal.

The

voltage

developed across the unknown resistance

is

then

measured by the

ASD

converter.

Diodes

CR1301

and

CR1302

and

lamp

DSt4lO

protect

the

ohms converter from

excessive

dc

and

ac

input

voltages. If

an

excessive voltage is applied to a resistance

range, the voltage is clamped by

CR1302

and

GR1301

and

appears across lamp

PS1410.

As

the filament

of

DS1410

warms

up,

the rmistance of thefilament increases, limiting

the current through the diode clamps.

DS1410

is rated

to

handle

125

V

rms indefinitely and

250

V

rms for a Fimited

time. Voltages in

excess

of these ratings cause

DSI410

to

act

as a

fuse. Diode

CR1301

also limits

the

open

circuit

voltage

at

the VOLTS/R input connector to approximately

+6

V.

Current

Shunts

@

The

current shunts in the

DM

505

consist of

R1425,

Rl426,

and t hick-film resistor network

R1521,

connected

between

the

mR

and LOW input terminals.

These

resistors

convert the input current to

a

voltage for measurement by

the

DM

505

circuitry. The maximum full

scale

voltage

developed across the current shunts

at

the

maximum full

scale current

is

0.2

volt. In the

dc

current mode, this

voltage is switched directly to the

ND

converter. In the ac

current

mode,

the current shunt voltage is first routed

through the

ac converter. The current shunts

are

protected by the diodes in

CR1621.

If

the

voltage across

the current shunts exceeds approximately

1.2

V,

the

diodes in

CR1621

begin

conducting, shunting current

around the resistors. The maximum voltage drop across

the current shunts in

an

overload condition is

ap-

proximately

1.5

V.

An input current exceeding

2

A opens

fuse

F1521.

The

DM

505

measures

voltages

up to

1

kV

peak above

chassis

ground

(200

V

peak above ground

at

the rear

interface input). Isolation

is

accomplished with power

transformer

Tl001,

which is powered from

the

25

Vac

floating windings

13A

and

138

of the power module.

Transformer

Kl 001

converts the

25

Vac to a secondary

output of

47

V

rrns, center-tapped, across pins

7

to

9,

and

12

V

rms across pins

lOto 12.

The 47 Y rms is rectified

by

CR1111

and filtered by capacitors

C1012

and

Clll

f

to

provide approximately + and

-

26

V

unregulated. The

positive voltage across

ClOl2

is

regulated

to

+15.75

V

by

U1022,

and

shunt resistors

R1122

and

R1021.

Resistor

R1021

adjusts the output voltage

for

the

minimum

+15.75

V required for proper ohms converter operation.

The

negative

voltage

across

Cllll

is

regulated to

-12

V

by

Uf 121.

The

current pulled from

each

of these supplies

is approximately

40

rn

A.

Capacitor

C1021

equalizes un-

balanced capacitance between the secondary windi ngs of

T1001,

pins

7,

8, and

9.

Capacitor

C1021

reduces any

60

Hz

common

mode

signal appearing between the front

panel input terminals of the

DM

505

and chassis ground.

The

12

V

rrns

from the secondary

of

TI

001,

pins

10

to

12,

is rectified

by

CRfOll

to provide approximately

+I2

Y

unregulated to the display anode drivers. The

+12

V

across

ClOf

I

is regulated to

+5

V

by

U1021.

Clock

9

The clock signals for

U1303

are generated

by

U1301,

a

free-running multivibrator

wit

h

a

frequency determined by

C1203, R1205, R1204,

and

R1202.

CLOCK

FREQ

ADJ

R1202

sets the clock frequency to

20.48

kHz,

a

multipEe

of

the

line frequency. Components

of

50

Hz or 60 Hz

at

the

input terminals are rejected since they

are

of

equal

magnitude during the up and down portions

of

the

measurement cycle,

Analog

to

Digital Converter

@

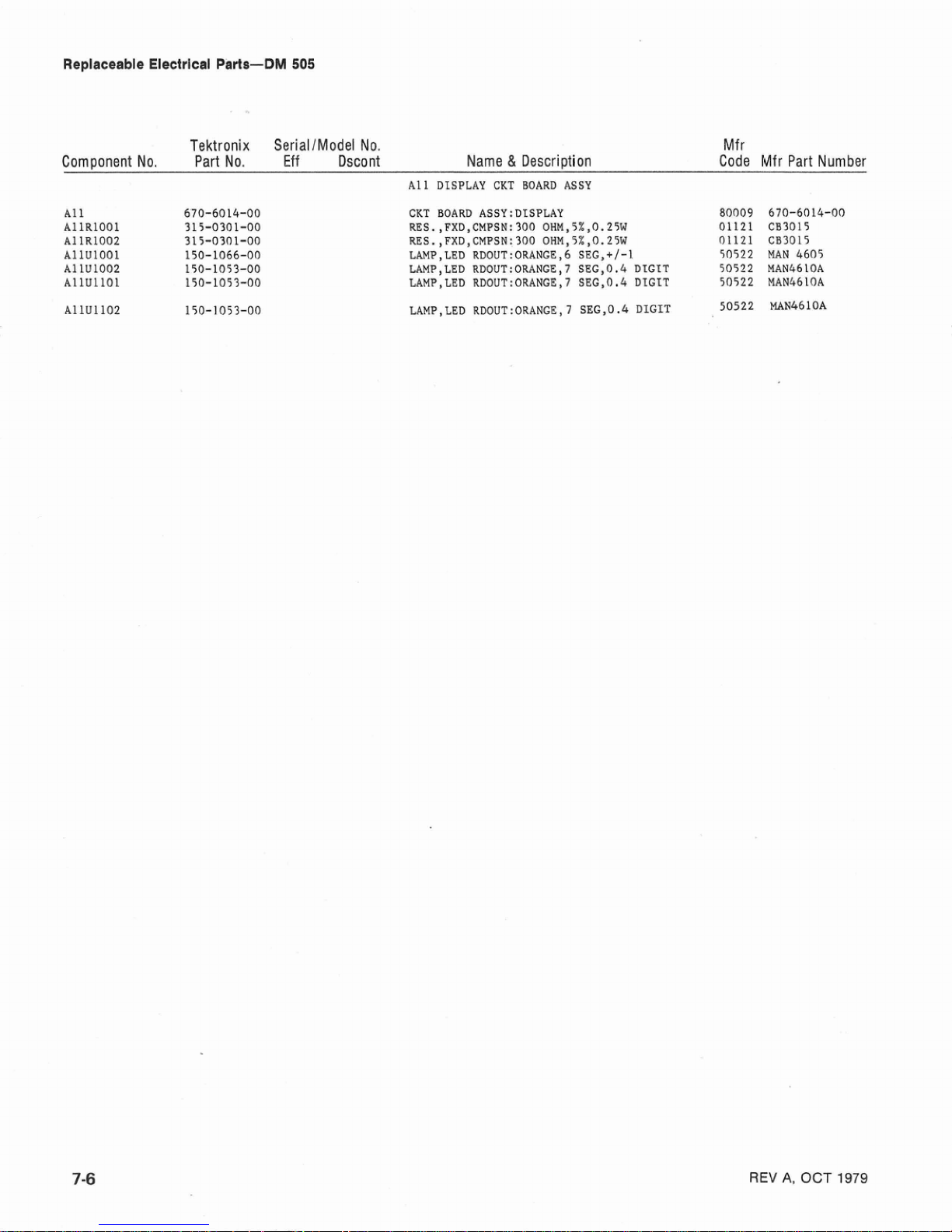

Integrated circuit

U1201

comprises

the

analog section

of the analog-to-digital

(#D)

converter

and

U1303

con-

tains the necessary control logic.

The

A/D

converter in the

DM

505

operates

on

the charge balancing principle. The

input voltage is converted to

a

current that charges

capacitor

Cf 101

in an integrator circuit. Charging con-

tinues until the capacitor voltage crosses afixedthreshold

level. Then

a

reference current larger than

the

maximum

input current

is

subtracted from the input current and the

capacitor discharges until

the

threshold level is crossed

again. This process

is

repeated until the measurement

interval is over. During the measurement interval,

a

counter in

U1303

accumulates clock pulses from clock

generator

U1301

when only the input signal

is

applied to

the integrator,

and

subtracts clock pulses

when

both the

input

signal and the reference current are applied to

the

integrator, resulting in a net count proportional to the

input voltage. This conversion occurs in

U1201

and

is

controlled

by

U1303.

Refer

to

Fig.

8-2

in the Diagrams

section.

Integrated circuit

U1201

also contains automatic zero-

ing

circuitry. Between meaurement intervals, the input of

U1201

is

switched to ground and an auto-zero voltage,

related

to

the offset voltages

in

U1201,

is stored across

auto-zero capacitor

C1102.

This auto-zero voltage is

converted to

a

current and subtracted from the input

current

at

the integrator

so

that errors due to

offset

Page 32

Theory

of

Operalion-DM

SO5

voltages and ground offsets are compensated.

The

reference voltage for

U1201

is

supplied

by

a

temperature

stable diode,

VR1201.

Resistors

R1111

and

R1112

(the

2

Vdc

ADJ)

convert the

reference

voltage

to

a

reference

current

for

the integrator, The gain of the integrator is

switchable from

one

to

ten

by

placing

R1210,

R1211,

and

R1301

in parallel with

R1212.

This gain increases

the

integrator input current derived from the input signal by

a

factor

of

ten. Resistor

R1210

allows the total parallel

resistance

to

be

closely trimmed for proper

gain

for the

200

mVdc

range. Resistor

R1113

and

low-leakage diodes

CR1113

and

CR1112

provide input protection for

U1201.

Capacitor

C1201

and resistor

R1113

increase the normal

mode rejection

of

U1201.

Transistor

Q1201

and

DC

ZERO

ADJ

resistor

R1104

set the dc zero of

Ut201,

Integrated

circuit

U1201

receives commands from

U1303

via two

digital linescalled "measure-zero"

(U1201,

pin

3)

and

"up

down"

(U1281,

pin

4).

The

"up-down" line controls the

direction

of

counting and integration.

The

"'measure-

zero" line determines whether

the

input

of

U1201

receives

the input signal or is connected

to

ground. Integrated

circuit

U1201

provides an output

to

U1303

through

a

"comparator" line

(U1201,

pin

5).

The comparator line

signals the counter in

U1303

when

the integrator has

passed the threshold. The outputs

of

U1303

control the

d~splay through

the

display driver circuitry.

A

detailed description

of

the operation of the

A/D

converter follows.

The

20.48

kHz clock frequency from

U1301

is divided

by

the time

base

counter

into

groups

of

6144

pulses.

Measurement takes place

for

4096

of

these

pulses and

automatic zeroing

takes

place for

2048

pulses.

During

the

auto zero interval, the input of the buffer

amplifier is grounded.

The

buffer offset current also

offsets the

output

of

the integrator.

The

offset

at

the

integrator output passes through

R1103

to

the

plus input

of the auto-zero amplifier.

The output

of

the

unity gain

auto-zero amplifier compensates for this offset current at

the summing node (pin

9)

at the integrator input. The

reference current through

Rl

f

11

and

R1112

from the

reference voltage source is applied for four clock cycles

and disconnected for the next four cycles by the

U/D

control logic. The reference current is connected to

R1112

when the updawn logic is low. Equilibrium

for

the

entire

integrating

and

auto-zero system is obtained when the

sum

of

the average currents at the integrator summing

junction

equals zero. Capacitor

GI102

charges to the

equilibrium voltage and maintains this

voltageat

the

auto-

zero amplifier input during

the

measurement interval

when the switch from the integrator output is

open.

See

Fig.

3-2

for functional timing during theauto-zerointerval.

The

fifty percent

duty

cycle

of

the

up-down

counter

is

overridden

at

the

start of

the

auto-zero interval. This

override period permits the output of the integrator to

come

to

V,, and

Cf

102

to

assume this

voltage.

Fig.

3-2.

Auto-zero

timing intervals.

I

d

.

YOVERRiDE

r

1

AUTO-ZERO

-

U/D

I

I

1

COMPARATOR

I

I

1

I

1

INTEGRATOR

OUTPUT

2692-5

Page 33

Theory

of

Operation-DM

505

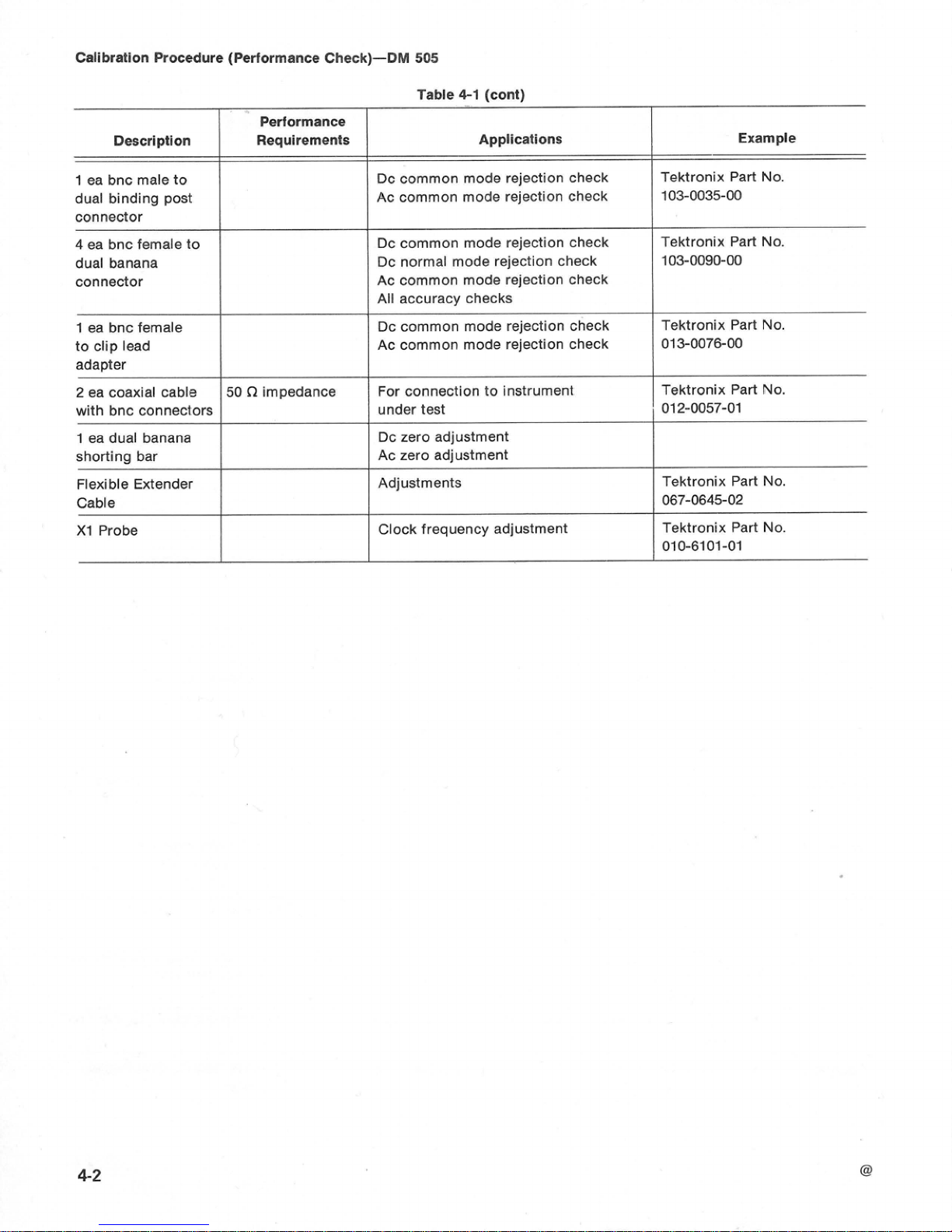

Upon completion of the

2048

clock pulse auto-zero

interval,

the

measurement interval commences.

The

measure-zero logic switches the analog input voltage to

the

buffer

input and disconnects the integrator

output

from the auto-zero amplifier input.

The

additional current

resulting at the summing junction of theintegrator

causes

the integrator output voltage to

move

away from the

equilibrium voltage obtained during auto-zero interval

and

maintained during the measurement interval

by

C1102.

The

comparator senses and transmits this devia-

tion to

the

control logic.

The

control logic changes the

duty cycle of

the

reference voltage in

an

attempt

to re-

establish equilibrium at the integrator summing

junctfon.

The

up-down logic

is

"up" (integrator output voltage is

also

up)

for

one

clock

cycle

and

"down" for seven cycles

when the comparator output

was high during the

preceding set of eight

clock cycles.

This

is

shown

as

duty

cycle

A

in Fig.

3-3.

When

the

comparator output is

low

in

clock cycle

seven,

the up-down logic

is

up

for

seven

cycles

and down for

one

cycle during the following eight clock

cycles.

This

is

shown

as

duty cycle

B.

Figure3-3 showsthe

result

of

these actions on the integrator output.

A

counter in U1303, synchronous with

the

up-down

logic, increments by

each clock pulse when the up-down

logic is

"up"

and

decrements

by

each

clock pulse when

the up-down

Iogic

is

"down".

The

net

count increases

by

six

counts

for each B duty cycle and decreases by six

counts for

each

Aduty cycle, toa maximum count

of

about

3100.

This

counting procedure is reversed

for negative

input voltages.

The

polarity

of

the input voltage is determined by the

state

of

the

updown

logic

when

the bcd counter state is

zero. This information

is

stored in a flip-llop and

loaded

into

the

static latch Once

each

measurezero cycle.

The bcd counter accumulates a number of counts

proportional to the input voltage during the measure

interval

while

the

control logic works

to

maintain

equijibrium. Equilibrium is achieved in

steps

and usual1 ya

residual voltage remains

at

the

end

of the measurement

cycle.

This

residual voltage is Compensated for by a short

override interval at

the

beginning

of

the auto-zero period.

The

counter

continues

until the integrator output equals

the auto-zeroequilibrium voltageand the up-down logic is

"down".

The

bcd

counter is

now

put

on

hold and its

contents

Zoaded into the latches. The counter

is

then

cleared and

the

multiplexer sends the measurement

result, digit

by

digit,

to

the

output

data

buffers.

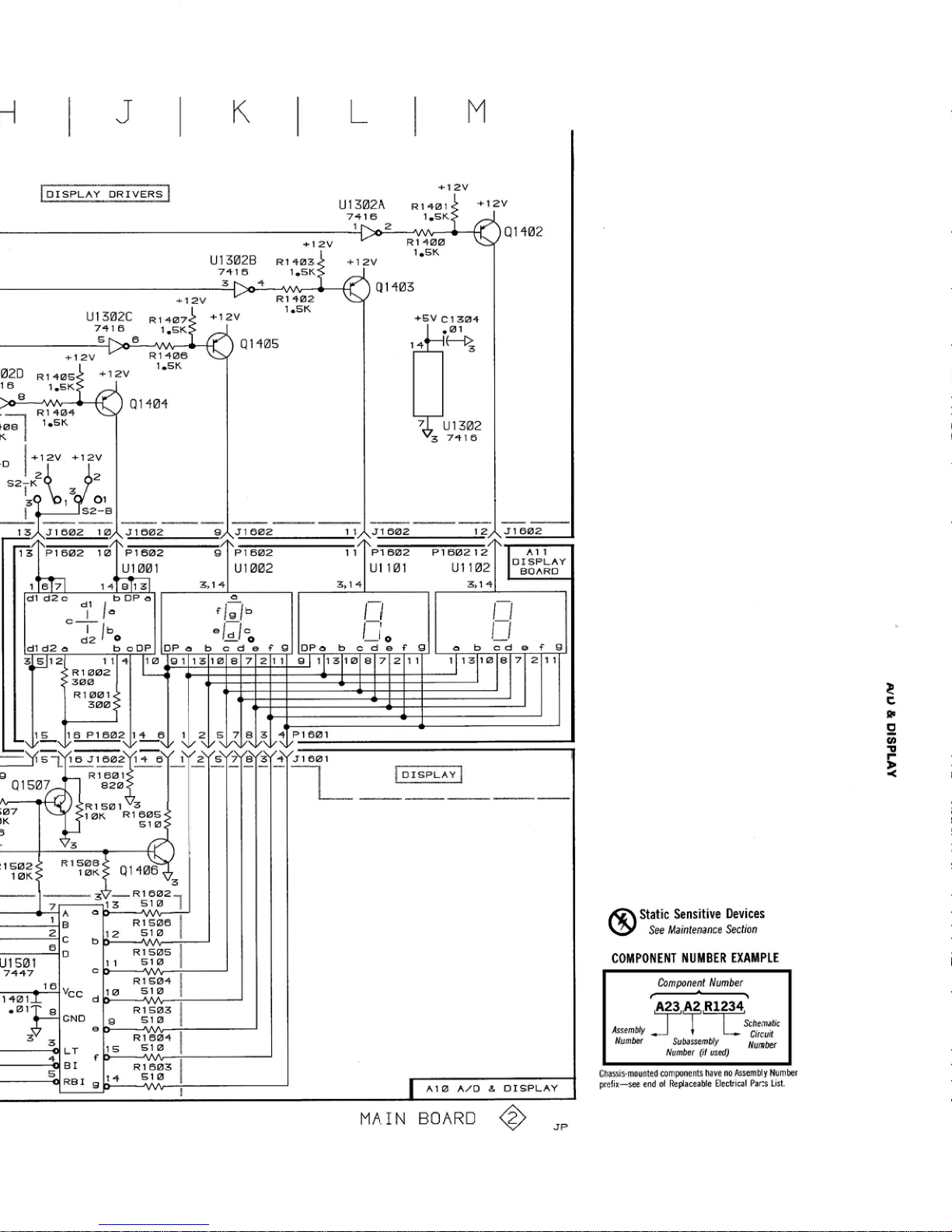

Display

Driver

Circuitry

@

Integrated circuit

U1301,

pins

13,

14,

15,

and 16,

provides

bcd

output of digits

in

parallel form, multi;plexed

by digit.

The

bcd digit signals are decoded by

U1501

and

applied

to

the cathodes

of

seven-segment

LED

Uf

002,

U1101,

and U1102.

The

segments of these LED are

connected

in parallel

to

U1501. Digit strobesfrom U1303,

pins

7,2,3,

and 4 are inverted by U 1302

A,

B,

C,

and D and

applied to the anodesof the

LED

by Q1402, Q1403, Q1404,

CLOCK

INPUT

CYCLETO

r2

345s

70

12345s

71

9

Z~~SB~O

12

34s

et

o

MI'

u/a

4-

MEASURE

INTERvM

c"Y"CyE

LdAA&

B-1

COMPARATOR

I

I

I

INTEGRATOR

OUTPUT

VS~RG

269M

Fig.

3-3.

Measurement

Interval

timing.

Page 34

Theory

of

Operation-DM

505

and Q1405.

The

segment

information at

the

cathode

of

each

LED

is displayed

as

its anode is strobed high.

The

display

is strobed

in

the

following

order:

digit

1,3,2,

and

4.

Digit

f

is

the

least

significant and digit 4 is

the

most

significant (1

or

0). The

digit strobes are also routed

through

sections

of

the

range switches

to providedecimal

point

information to

the

display. Transistor

Q1507

con-

trols the most signifFcant digit, U1001.

The

sign

is enabled

by

switches

S2K

and

S2B,

which

connect

thesign

anodes (t11001

pins

1,6,and7) to+12

V.

The

cathode

of

the

negative

segment

of

the

sign (pin

4)

is

hard-wired

low

through

R1601.

The

sign

of

the

input

from

U1303,

pin

5,

is

buffered through U1302Etothe

cathodes

of

the

positive

segments

of the

sign

(U1001,

pins 3 and

5).

If

the

sign

has

been

enabled

by

S2K