Page 1

DDR Analysis

Memory Interface Electrical Verification and Debug Solution

Printable Application Help

*P077023110*

077-0231-10

Page 2

Page 3

DDR Analysis

Memory Interface Electrical Verification and Debug Solution

Printable Application Help

www.tektronix.com

077-0231-10

Page 4

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its subsidiaries or suppliers, and are

protected by national copyright laws and international treaty provisions. Tektronix products are covered by U.S. and foreign patents, issued

and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges

reserved.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

Contacting Tektronix

Tektronix, Inc.

14150 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

USA

For product information, sales, service, and technical support:

■

In North America, call 1-800-833-9200.

■

Worldwide, visit www.tektronix.com to find contacts in your area.

Page 5

Table of Contents

Welcome ............................................................................................................................................................. xi

Introduction to the application

Related documentation .................................................................................................................................. 1

Conventions ................................................................................................................................................... 1

Technical support ........................................................................................................................................... 2

Customer feedback ........................................................................................................................................ 2

Getting started

Product description ........................................................................................................................................ 5

DDRA prerequisites ....................................................................................................................................... 6

Requirements and restrictions ....................................................................................................................... 6

Supported probes ........................................................................................................................................... 6

Installing the application ................................................................................................................................. 7

About DDRA ................................................................................................................................................... 8

Operating basics

About basic operations ................................................................................................................................... 9

Starting the application ............................................................................................................................. 9

Menu controls ........................................................................................................................................... 9

Virtual keypad ........................................................................................................................................... 9

Tips on the DDRA user interface ............................................................................................................ 10

Basic oscilloscope functions ........................................................................................................................ 11

Application directories ............................................................................................................................ 11

File name extensions ............................................................................................................................. 11

Returning to the application .................................................................................................................... 11

Control panel .......................................................................................................................................... 11

Saving and recalling setups ......................................................................................................................... 12

Saving a setup ........................................................................................................................................ 12

Recalling a saved setup ......................................................................................................................... 12

Recalling the default setup ..................................................................................................................... 13

Search and mark .......................................................................................................................................... 13

Limits ............................................................................................................................................................ 14

Dynamic limits .............................................................................................................................................. 15

DDR Analysis Printable Application Help

i

Page 6

Table of Contents

Setting up DDR for analysis ......................................................................................................................... 16

DDR standards and their measurements ............................................................................................... 16

Derating .................................................................................................................................................. 25

About DDR analysis ............................................................................................................................... 28

Step 1: Generation rate and levels ......................................................................................................... 28

Step 2: Interposer filter ........................................................................................................................... 31

Step 3: Measurements and sources ....................................................................................................... 33

Step 4: Burst detection method .............................................................................................................. 38

Step 5: Burst detection settings .............................................................................................................. 42

Step 6:Thresholds and scaling ............................................................................................................... 42

DQ-DQS phase alignment ...................................................................................................................... 44

Chip select latency + DQ-DQS phase alignment ................................................................................... 46

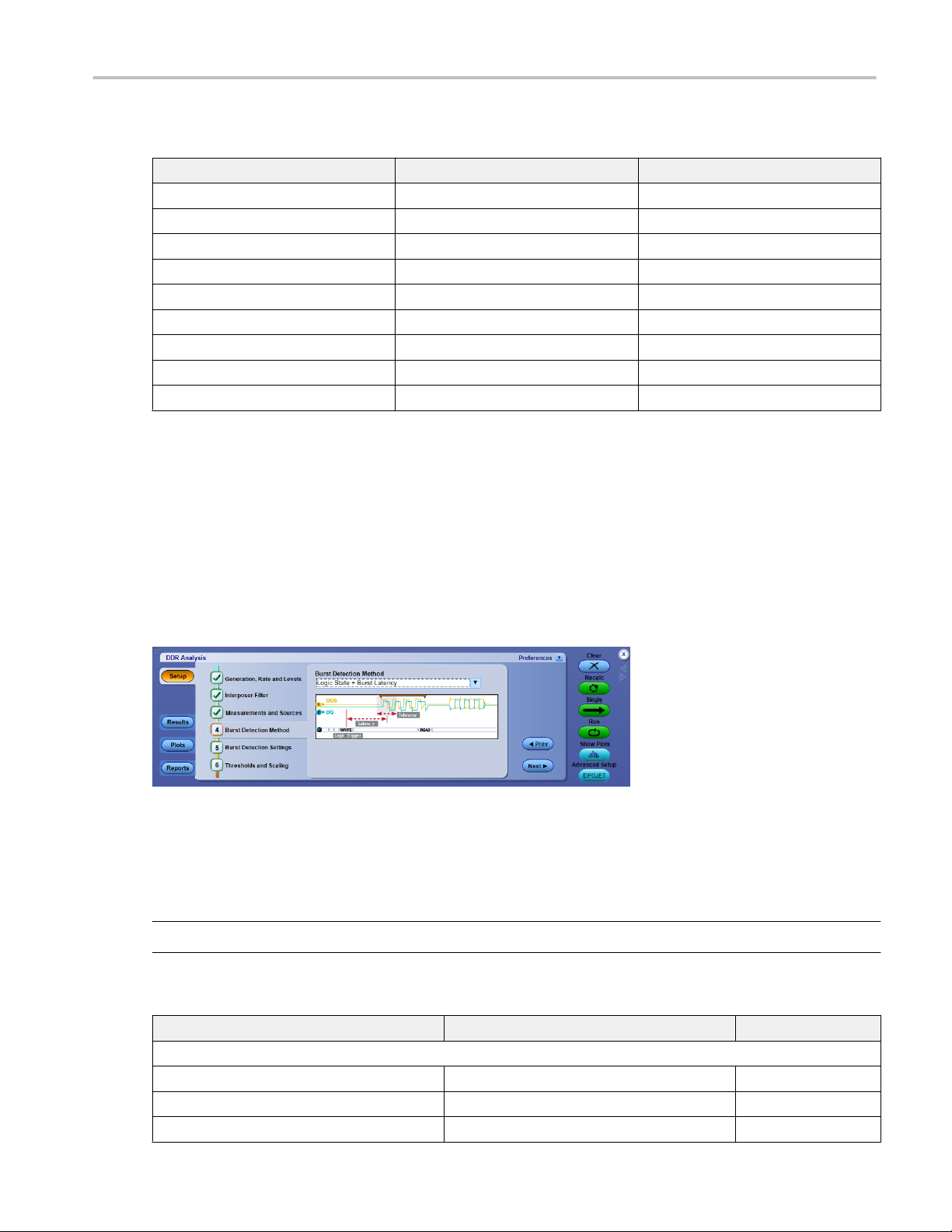

Logic state + burst latency ...................................................................................................................... 47

Visual search .......................................................................................................................................... 50

Measurement levels ............................................................................................................................... 53

Hints ....................................................................................................................................................... 54

Results as statistics ................................................................................................................................ 54

Plots ....................................................................................................................................................... 55

Reports ................................................................................................................................................... 55

Switching between the DDRA and DPOJET applications ...................................................................... 55

Salient features of MSO-DDRA integration ............................................................................................ 56

Tutorial

Introduction to the tutorial ............................................................................................................................. 57

Setting up the oscilloscope .......................................................................................................................... 57

Starting the application ................................................................................................................................. 57

Waveform files ............................................................................................................................................. 57

Recalling a waveform file ............................................................................................................................. 57

Taking a measurement ................................................................................................................................ 58

Parameters

About parameters ......................................................................................................................................... 61

Step 1: Generation rate and levels parameters ........................................................................................... 61

Step 2: Interposer filter parameters .............................................................................................................. 62

Step 3: Measurement and sources parameters ........................................................................................... 62

Step 4: Burst detection method parameters ................................................................................................. 63

Step 5: Burst detection settings parameters ................................................................................................ 63

Step 6: Thresholds and scaling parameters ................................................................................................. 65

ii DDR Analysis Printable Application Help

Page 7

Table of Contents

Reference

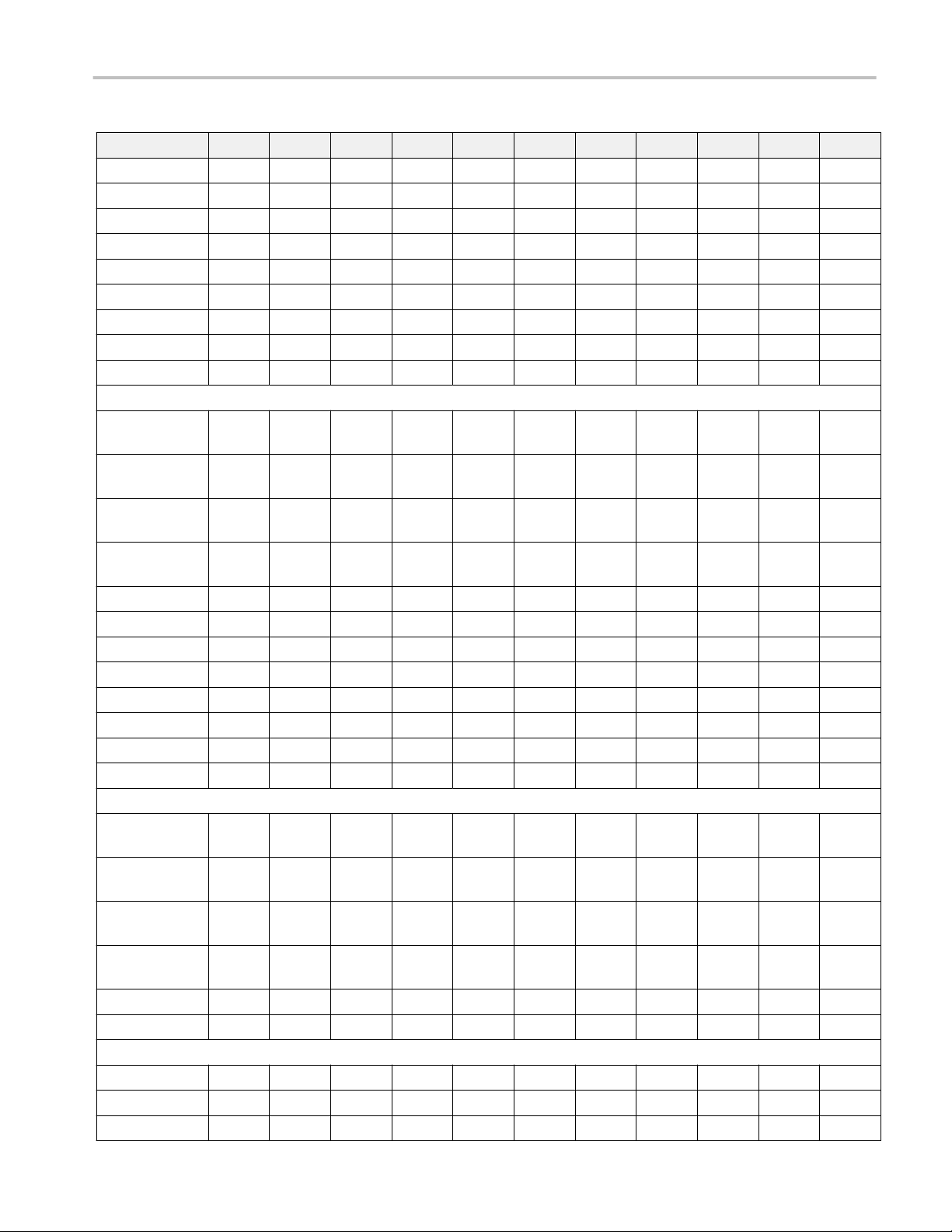

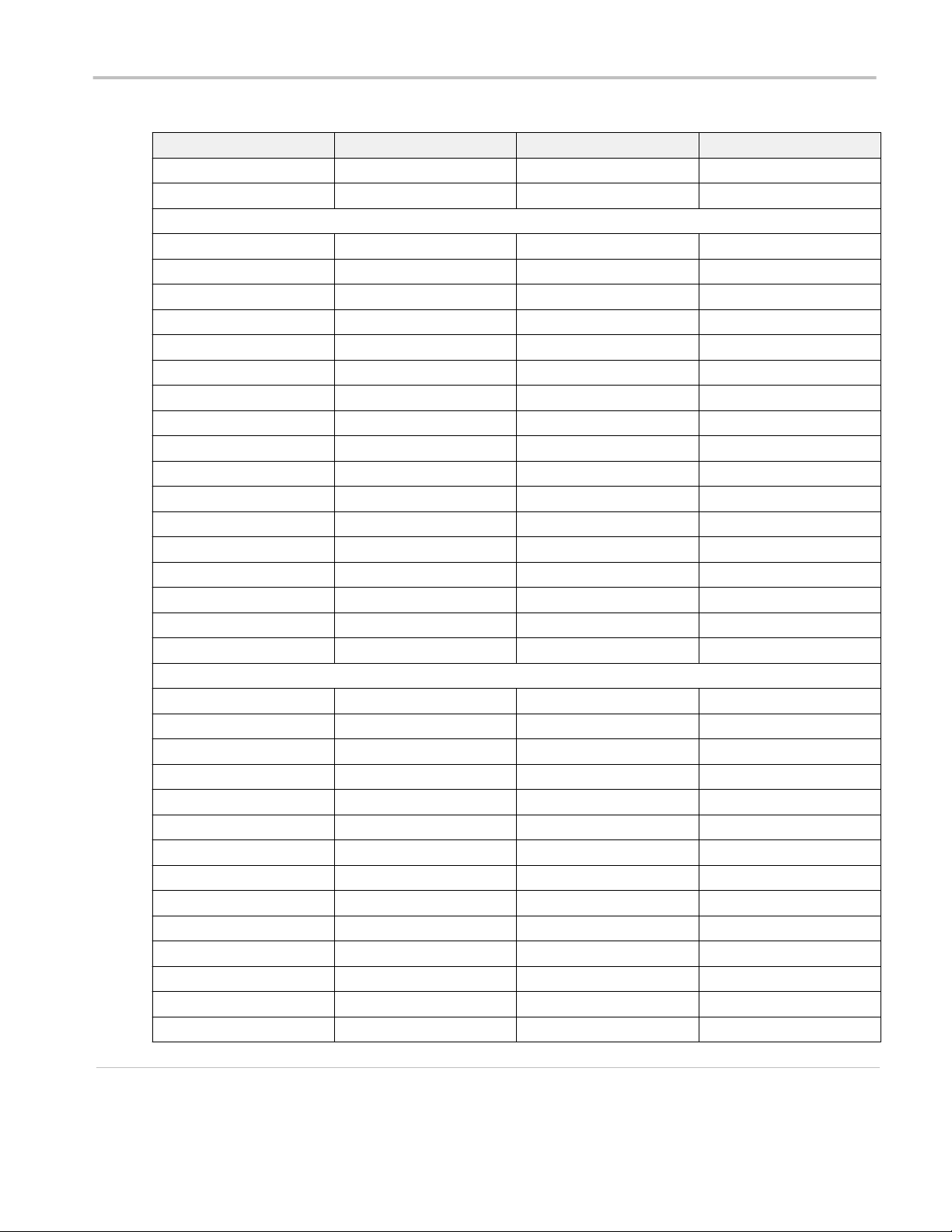

DDR measurement sources ......................................................................................................................... 67

DDR2 measurement sources ....................................................................................................................... 69

DDR3 measurement sources ....................................................................................................................... 73

DDR3L measurement sources ..................................................................................................................... 77

DDR4 measurement sources ....................................................................................................................... 81

GDDR5 measurement sources .................................................................................................................... 84

LPDDR measurement sources .................................................................................................................... 86

LPDDR2 measurement sources .................................................................................................................. 88

LPDDR3 measurement sources .................................................................................................................. 92

LPDDR4 measurement sources .................................................................................................................. 96

Measurement range limits ............................................................................................................................ 99

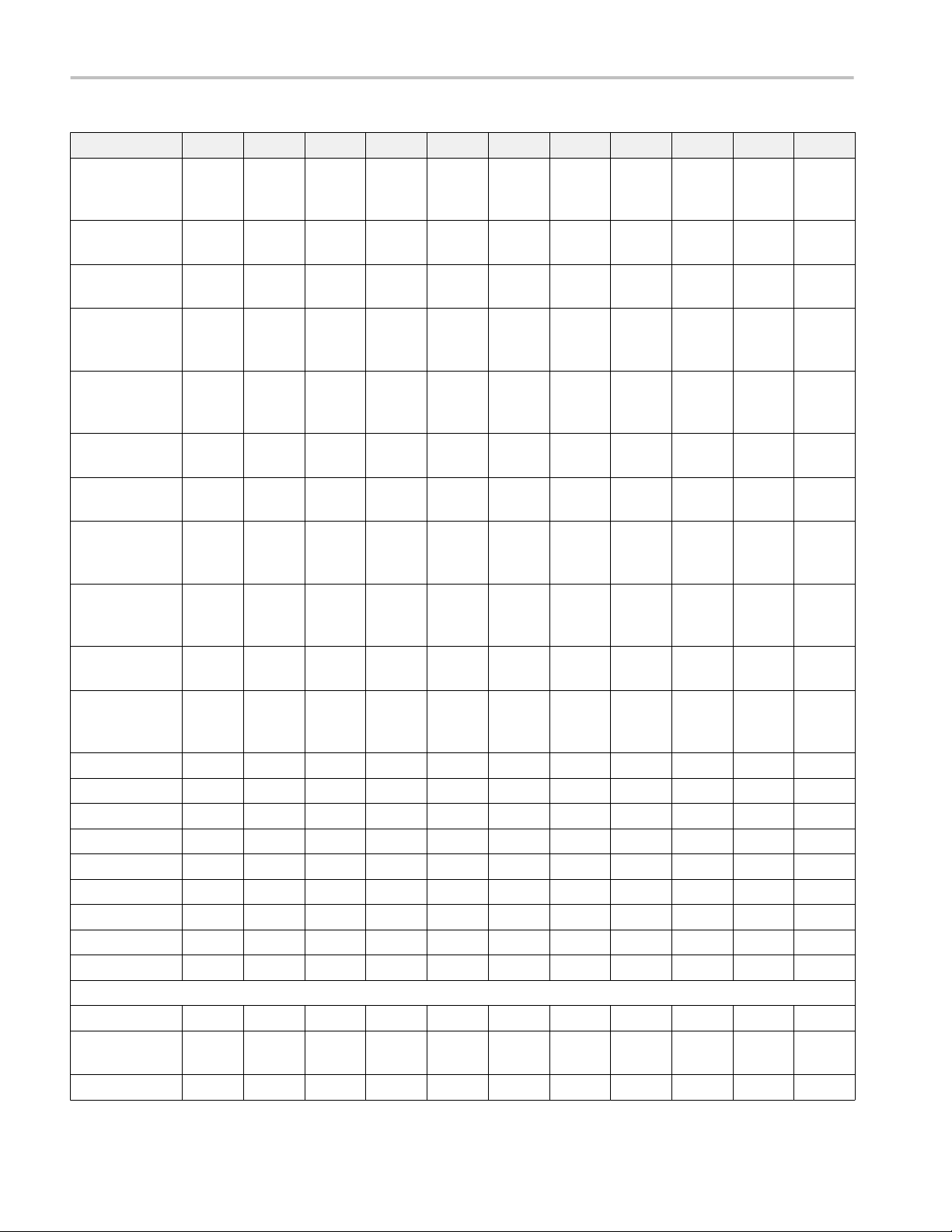

Dynamic limits for DDR measurements ..................................................................................................... 100

Dynamic limits for DDR2 measurements ................................................................................................... 101

Dynamic limits for DDR3 measurements ................................................................................................... 101

Dynamic limits for DDR3L measurements ................................................................................................. 102

Dynamic limits for DDR4 measurements ................................................................................................... 103

Dynamic limits for LPDDR measurements ................................................................................................. 104

Dynamic limits for LPDDR2 measurements ............................................................................................... 104

Dynamic limits for LPDDR3 measurments ................................................................................................. 105

Dynamic limits for LPDDR4 measurements ............................................................................................... 106

Vih-Vil reference levels .............................................................................................................................. 107

Using digital channels ................................................................................................................................ 109

Error codes and warnings .......................................................................................................................... 116

Algorithms

About algorithms ........................................................................................................................................ 121

Write measurements .................................................................................................................................. 121

Data eye height .................................................................................................................................... 121

Data eye width ...................................................................................................................................... 122

DDRARXMask ...................................................................................................................................... 122

tDQSS .................................................................................................................................................. 123

tDQS2DQ ............................................................................................................................................. 123

VIHL_AC .............................................................................................................................................. 124

SRIN_dIVW_Rise ................................................................................................................................. 124

SRIN_dIVW_Fall .................................................................................................................................. 124

TdIPW-High .......................................................................................................................................... 124

DDR Analysis Printable Application Help iii

Page 8

Table of Contents

TdIPW-Low ........................................................................................................................................... 124

Differential DQS measurements ................................................................................................................ 124

Input Slew-Diff-Rise(DQS) ................................................................................................................... 124

Input Slew-Diff-Fall(DQS) ..................................................................................................................... 125

tDH-Diff(base) ...................................................................................................................................... 125

tDH-Diff(derated) .................................................................................................................................. 126

tDH-Diff(Vref-based) ............................................................................................................................. 126

tDS-Diff(base) ....................................................................................................................................... 126

tDS-Diff(derated) .................................................................................................................................. 127

tDS-Diff(Vref-based) ............................................................................................................................. 127

tDQSH .................................................................................................................................................. 127

tDQSL ................................................................................................................................................... 128

tDSS-Diff .............................................................................................................................................. 128

tDSH-Diff .............................................................................................................................................. 128

tDQSS-Diff ............................................................................................................................................ 128

Single ended DQS ..................................................................................................................................... 128

Slew Rate-Hold-SE-Fall(DQS) ............................................................................................................. 128

Slew Rate-Hold-SE-Rise(DQS) ............................................................................................................ 129

Slew Rate-Setup-SE-Fall(DQS) ........................................................................................................... 129

Slew Rate-Setup-SE-Rise(DQS) .......................................................................................................... 129

tDS-SE(base) ....................................................................................................................................... 129

tDIPW-SE ............................................................................................................................................. 129

tDSS-SE ............................................................................................................................................... 129

tDSH-SE ............................................................................................................................................... 129

tDQSS-SE ............................................................................................................................................ 130

tDH-SE(base) ....................................................................................................................................... 130

tDVAC(CK) ................................................................................................................................................. 130

tWPRE ....................................................................................................................................................... 130

tWPST ........................................................................................................................................................ 131

tWRPDE ..................................................................................................................................................... 132

tWRSRE ..................................................................................................................................................... 132

Differential DQS read measurements ........................................................................................................ 132

tDQSCK-Diff ......................................................................................................................................... 132

tDQSQ-DBI ........................................................................................................................................... 133

tDQSQ-Diff ........................................................................................................................................... 133

tAC-Diff ................................................................................................................................................. 133

tQH ....................................................................................................................................................... 133

SRQdiff-Rise(DQS) .............................................................................................................................. 134

SRQdiff-Fall(DQS) ................................................................................................................................ 134

iv DDR Analysis Printable Application Help

Page 9

Table of Contents

Single-ended DQS read measurements .................................................................................................... 135

tDQSQ-SE ............................................................................................................................................ 135

tDQSCK-SE .......................................................................................................................................... 135

DDR2-tDQSCK ..................................................................................................................................... 135

Slew rate DQ .............................................................................................................................................. 136

SRQse-Fall(DQ) ................................................................................................................................... 136

SRQse-Rise(DQ) .................................................................................................................................. 136

tRDPDE ...................................................................................................................................................... 137

tRDSRE ...................................................................................................................................................... 137

tRPRE ........................................................................................................................................................ 137

tRPST ......................................................................................................................................................... 138

DQ measurements ..................................................................................................................................... 139

Slew Rate-Hold-Fall(DQ) ...................................................................................................................... 139

Slew Rate-Hold-Rise(DQ) .................................................................................................................... 139

Slew Rate-Setup-Fall(DQ) .................................................................................................................... 139

Slew Rate-Setup-Rise(DQ) .................................................................................................................. 139

Clock(Diff) measurements .......................................................................................................................... 139

SSC Downspread(CK) ......................................................................................................................... 139

SSC mod Freq(CK) .............................................................................................................................. 140

SSC Profile(CK) ................................................................................................................................... 140

tCH ....................................................................................................................................................... 140

tCK ....................................................................................................................................................... 140

tCL ........................................................................................................................................................ 140

tCH(abs) ............................................................................................................................................... 140

tCH(avg) ............................................................................................................................................... 141

tCK(abs) ............................................................................................................................................... 141

tCK(avg) ............................................................................................................................................... 141

tCL(abs) ................................................................................................................................................ 141

tCL(avg) ................................................................................................................................................ 142

tHP ....................................................................................................................................................... 142

tERR ..................................................................................................................................................... 142

tJIT(cc) ................................................................................................................................................. 143

tJIT(duty) .............................................................................................................................................. 143

tJIT(per) ................................................................................................................................................ 144

VID(ac) ................................................................................................................................................. 144

Input Slew-Diff-Rise(CK) ...................................................................................................................... 144

Input Slew-Diff-Fall(CK) ........................................................................................................................ 144

Clock (Single ended) .................................................................................................................................. 145

AC-Overshoot(CK#) ............................................................................................................................. 145

DDR Analysis Printable Application Help v

Page 10

Table of Contents

AC-Overshoot(CK) ............................................................................................................................... 145

AC-OvershootArea(CK#) ...................................................................................................................... 145

AC-OvershootArea(CK) ........................................................................................................................ 146

AC-Undershoot(CK#) ........................................................................................................................... 146

AC-Undershoot(CK) ............................................................................................................................. 146

AC-UndershootArea(CK#) .................................................................................................................... 147

AC-UndershootArea(CK) ...................................................................................................................... 147

CKslew-Fall(CK) ................................................................................................................................... 148

CKslew-Fall(CK#) ................................................................................................................................. 148

CKslew-Rise(CK) ................................................................................................................................. 148

CKslew-Rise(CK#) ............................................................................................................................... 148

VIN(CK) ................................................................................................................................................ 148

VIN(CK#) .............................................................................................................................................. 148

Vix(ac)CK ............................................................................................................................................. 148

Vox(ac)CK ............................................................................................................................................ 149

VSWING(MAX)CK# .............................................................................................................................. 149

VSWING(MAX)CK ................................................................................................................................ 149

VSEH(AC)CK ....................................................................................................................................... 149

VSEH(AC)CK# ..................................................................................................................................... 150

VSEH(CK#) .......................................................................................................................................... 150

VSEH(CK) ............................................................................................................................................ 150

VSEL(AC)CK# ...................................................................................................................................... 151

VSEL(AC)CK ........................................................................................................................................ 151

VSEL(CK#) ........................................................................................................................................... 151

VSEL(CK) ............................................................................................................................................. 151

DQS(Single ended) measurements ........................................................................................................... 151

Vix(ac)DQS .......................................................................................................................................... 151

Vox(ac)DQS ......................................................................................................................................... 151

AC-Overshoot(DQS) ............................................................................................................................ 152

AC-Overshoot(DQS#) .......................................................................................................................... 152

AC-OvershootArea(DQS#) ................................................................................................................... 152

AC-OvershootArea(DQS) ..................................................................................................................... 153

AC-Undershoot(DQS) .......................................................................................................................... 153

AC-Undershoot(DQS#) ........................................................................................................................ 153

AC-UndershootArea(DQS#) ................................................................................................................. 154

AC-UndershootArea(DQS) ................................................................................................................... 154

WCK (Diff) .................................................................................................................................................. 155

SSC Downspread(WCK) ...................................................................................................................... 155

SSC mod Freq(WCK) ........................................................................................................................... 155

vi DDR Analysis Printable Application Help

Page 11

Table of Contents

SSC Profile(WCK) ................................................................................................................................ 155

tDVAC(WCK) ........................................................................................................................................ 155

tWCK .................................................................................................................................................... 155

tWCK-DJ .............................................................................................................................................. 155

tWCKH ................................................................................................................................................. 156

tWCKHP ............................................................................................................................................... 156

tWCKL .................................................................................................................................................. 156

tWCK-Rise-Slew ................................................................................................................................... 156

tWCK-Fall-Slew .................................................................................................................................... 156

tWCK-RJ .............................................................................................................................................. 156

tWCK-TJ ............................................................................................................................................... 156

VWCK-Swing ........................................................................................................................................ 157

WCK (Single ended) .................................................................................................................................. 157

VIN(WCK) ............................................................................................................................................. 157

VIN(WCK#) ........................................................................................................................................... 157

Vix(ac)WCK .......................................................................................................................................... 157

VOL(WCK) ........................................................................................................................................... 157

VOH(WCK) ........................................................................................................................................... 157

VOL(WCK#) ......................................................................................................................................... 158

VOH(WCK#) ......................................................................................................................................... 158

WCKslew-Fall(WCK) ............................................................................................................................ 158

WCKslew-Fall(WCK#) .......................................................................................................................... 158

WCKslew-Rise(WCK) ........................................................................................................................... 158

WCKslew-Rise(WCK#) ......................................................................................................................... 158

Address-Command measurements ........................................................................................................... 159

AC-Overshoot ....................................................................................................................................... 159

AC-OvershootArea ............................................................................................................................... 159

AC-Undershoot ..................................................................................................................................... 160

AC-UndershootArea ............................................................................................................................. 160

Slew Rate-Hold-Fall(Addr-Cmd) ........................................................................................................... 161

Slew Rate-Hold-Rise(Addr-Cmd) ......................................................................................................... 161

Slew Rate-Setup-Fall(Addr-Cmd) ......................................................................................................... 161

Slew Rate-Setup-Rise(Addr-Cmd) ....................................................................................................... 161

tAH ....................................................................................................................................................... 161

tAPW .................................................................................................................................................... 161

tAS ........................................................................................................................................................ 162

tCIPW-High .......................................................................................................................................... 162

tCIPW-Low ........................................................................................................................................... 162

tCMDH .................................................................................................................................................. 162

DDR Analysis Printable Application Help vii

Page 12

Table of Contents

tCMDPW .............................................................................................................................................. 162

tCMDS .................................................................................................................................................. 162

tIS(base) ............................................................................................................................................... 162

tIH(base) ............................................................................................................................................... 162

tIS(derated) .......................................................................................................................................... 163

tIH(derated) .......................................................................................................................................... 163

tIPW-High ............................................................................................................................................. 163

tIPW-Low .............................................................................................................................................. 163

Refresh ....................................................................................................................................................... 163

tCKSRE ................................................................................................................................................ 163

tCKSRX ................................................................................................................................................ 163

tRFC ..................................................................................................................................................... 164

tREFTR(Read) ..................................................................................................................................... 164

tREFTR(Write) ...................................................................................................................................... 164

tXSNRW ............................................................................................................................................... 164

Power down ............................................................................................................................................... 164

tPD ....................................................................................................................................................... 164

Active ......................................................................................................................................................... 164

tRAS ..................................................................................................................................................... 164

tRC ....................................................................................................................................................... 165

tRCDRD ............................................................................................................................................... 165

tRCDWR ............................................................................................................................................... 165

Precharge ................................................................................................................................................... 166

tPPD ..................................................................................................................................................... 166

tRP(ACT) .............................................................................................................................................. 166

tRP(MRS) ............................................................................................................................................. 166

tRP(REF) .............................................................................................................................................. 167

tRP(SRE) .............................................................................................................................................. 167

tRTPL ................................................................................................................................................... 167

GPIB commands

About the GPIB program ............................................................................................................................ 169

GPIB reference materials ........................................................................................................................... 169

Argument types .......................................................................................................................................... 169

Commands ................................................................................................................................................. 170

DDRA:APPLYBurstconfig ..................................................................................................................... 170

DDRA:ADDALLTerr .............................................................................................................................. 170

DDRA:ADDALLSLewdq ....................................................................................................................... 171

DDRA:ADDALLDiffdqs ......................................................................................................................... 171

viii DDR Analysis Printable Application Help

Page 13

Table of Contents

DDRA:ADDCMDFLTFile ...................................................................................................................... 172

DDRA: ADVBURSTLevelmode ............................................................................................................ 172

DDRA:ADDALLSEdqs .......................................................................................................................... 173

DDRA:ADDMeas .................................................................................................................................. 173

DDRA:ALTernatethresholds ................................................................................................................. 175

DDRA:AMPBasedmargin ..................................................................................................................... 175

DDRA:BURSTIDMethod ...................................................................................................................... 176

DDRA:BURSTDETectmethod .............................................................................................................. 176

DDRA:BURSTLEngth ........................................................................................................................... 177

DDRA:BURSTLAtency ......................................................................................................................... 177

DDRA:BURSTLevelmode .................................................................................................................... 178

DDRA:BURSTTOlerance ..................................................................................................................... 178

DDRA:BUS ........................................................................................................................................... 179

DDRA:CLKFLTFile ............................................................................................................................... 179

DDRA:CSACTive ................................................................................................................................. 180

DDRA:CLEARALLMeas ....................................................................................................................... 180

DDRA:CSSOUrce ................................................................................................................................ 180

DDRA:CLKBARFLTFile ........................................................................................................................ 181

DDRA:CASMAX ................................................................................................................................... 181

DDRA:CASMIN .................................................................................................................................... 182

DDRA:CSLEvel .................................................................................................................................... 182

DDRA:CSMOde ................................................................................................................................... 182

DDRA:CUSTOMRate ........................................................................................................................... 183

DDRA:DATAHIGH ................................................................................................................................ 183

DDRA:DATALOW ................................................................................................................................ 184

DDRA:DQSBARFLTFile ....................................................................................................................... 184

DDRA:DQSFLTFile .............................................................................................................................. 185

DDRA:DQFLTFile ................................................................................................................................. 185

DDRA:DATAMID .................................................................................................................................. 186

DDRA:DATARate ................................................................................................................................. 186

DDRA:DQDQSLEVELSTAtus? ............................................................................................................ 187

DDRA:FLTtype ..................................................................................................................................... 187

DDRA:GENeration ............................................................................................................................... 187

DDRA:HYSTEREsis ............................................................................................................................. 188

DDRA:HORIzontalscaling .................................................................................................................... 188

DDRA:ISOLBurstlen ............................................................................................................................. 189

DDRA:LASTError? ............................................................................................................................... 189

DDRA:LOGICTrigger ............................................................................................................................ 189

DDRA:MEASType ................................................................................................................................ 190

DDR Analysis Printable Application Help ix

Page 14

Table of Contents

DDRA:MARGIN .................................................................................................................................... 190

DDRA:POSTamble ............................................................................................................................... 190

DDRA:PREAmbletype .......................................................................................................................... 191

DDRA:PTPeak ..................................................................................................................................... 191

DDRA:RXMASKFile ............................................................................................................................. 191

DDRA:SOURCE:CLOCK ..................................................................................................................... 192

DDRA:SOURCE:STROBE ................................................................................................................... 192

DDRA:SOURCE:DATa ......................................................................................................................... 193

DDRA:SOURCE? ................................................................................................................................. 193

DDRA:SOURCE:CLOCKBar ................................................................................................................ 194

DDRA:SOURCE:STRObebar ............................................................................................................... 194

DDRA:STROBEHIGH .......................................................................................................................... 195

DDRA:STROBEMID ............................................................................................................................. 195

DDRA:STROBELOW ........................................................................................................................... 195

DDRA:SOURCE:WCKBar .................................................................................................................... 196

DDRA:SOURCE:WCK ......................................................................................................................... 196

DDRA:SYMBOLFile ............................................................................................................................. 197

DDRA:THREShold ............................................................................................................................... 197

DDRA:TDQS2DQMode ........................................................................................................................ 198

DDRA:TDQS2DQ ................................................................................................................................. 198

DDRA:TCKAVG ................................................................................................................................... 198

DDRA:TIMGMode ................................................................................................................................ 199

DDRA:TCKAVGMIN ............................................................................................................................. 199

DDRA:VCENTCA ................................................................................................................................. 199

DDRA:VCENTDQ ................................................................................................................................. 200

DDRA:VDD ........................................................................................................................................... 200

DDRA:VDDMode .................................................................................................................................. 201

DDRA:VERTicalscaling ........................................................................................................................ 201

DDRA:VERsion? .................................................................................................................................. 202

DDRA:VIHACMin? ............................................................................................................................... 202

DDRA:VIHDCMin? ............................................................................................................................... 202

DDRA:VILACMax? ............................................................................................................................... 203

DDRA:VILDCMax? ............................................................................................................................... 203

DDRA:VREF ......................................................................................................................................... 203

DDRA:VREFDC? ................................................................................................................................. 204

DDRA:VREFMode ................................................................................................................................ 204

DDRA:WRITEAmpgtread ..................................................................................................................... 204

DDRA:WCKBARFLTFile ...................................................................................................................... 205

DDRA:WCKFLTFile .............................................................................................................................. 205

x DDR Analysis Printable Application Help

Page 15

Welcome

DDR (Dual Data Rate) is a dominant and fast-growing memory technology. It offers the high data transfer rates needed for

virtually all computing applications, from consumer products to the most powerful servers. The high speeds of these signals

require high performance measurement tools.

The DDRA application includes compliance measurements as part of our DDR Analysis solution. The DDR Analysis solution

enables you to achieve new levels of productivity, efficiency, and measurement reliability. It requires the Jitter and Eye Diagram

Analysis tool (Opt. DJA) and the Advanced Search and Mark capability (Opt. ASM).

Some of the DDRA features are:

■

Provides debug, analysis, and compliance in one solution for multiple DDR standards such as DDR, DDR2, DDR3, DDR3L,

DDR4. LPDDR, LPDDR2, LPDDR3,LPDDR4, GDDR3, and GDDR5.

■

Enables analysis of compliance measurements either through the DDRA or DPOJET application for all bursts in an

acquisition.

■

Differentiates data reads from writes, or analyzes signal integrity on the clock or on a data (DQ) line during Read or Write

cycles, or measures Data to Strobe setup and hold during Write cycles.

■

Includes limit files to test measurement pass/fail status per standard, speed grades and speed bins. Supports non-standard

speed grades.

■

Provides both single-ended and differential measurements on Data, Strobe, Clock, Address and Command signals.

■

Includes comprehensive measurement statistics.

■

Includes sophisticated graphical analysis tools such as Histograms, Time Trends, Spectrums, Bathtub Plots, and Real-Time

Eye® diagrams with superimposition of the strobe eye with the data eye.

■

Produces consolidated reports automatically with pass/fail information, statistical measurement results, setup information,

limits information, waveform path location, plots and user comments, if any.

■

Automatically applies signal slew rate derating of measurement limits for Address/Command and data signals.

■

Dynamically normalizes limits for clock measurements such as tERR based on the measured tCK(avg).

■

Logic state configuration using the DDRA user interface.

DDR

DDR is the DRAM (Dynamic Random Access Memory) technology responsible for increasing data transfer rates to meet highspeed requirements and data capacity of computer systems.

DDR2

DDR2 is the Double Data Rate 2 SDRAM and is widely available in products with data rates up to 1066MT/s.

DDR3

DDR3 DRAM memory is widely available in products and extends data rates to 1600 MT/s and faster rates to come.

DDR3L

DDR3L (low voltage) DRAM memory is widely available in products and extends data rates to 1600 MT/s and faster rates to

come.

DDR4

DDR4 DRAM memory is widely available in products and extends data rates to 3200 MT/s and faster rates to come.

DDR Analysis Printable Application Help xi

Page 16

Welcome

Low Power DDR

LPDDR (Low Power DDR) is a technology for mobile phones and portable computing devices, driven by the need for faster

operation with long battery life.

Low Power DDR2

LPDDR2 (Low Power DDR2) is a technology for mobile phones and portable computing devices as it supports advanced power

management. Includes a reduced interface voltage of 1.2 V from the 1.8 V specification as compared to LPDDR memory

technology. This results in a power consumption reduced by over 50%.

Low Power DDR3

LPDDR3 (Low Power DDR3) is a technology for mobile phones and portable computing devices as it supports advanced power

management. Includes a reduced interface voltage of 1.2 V from the 1.8 V specification as compared to LPDDR memory

technology. This results in a power consumption reduced by over 50%.

LPDDR4

LPDDR4 (Low Power DDR4) is an emerging technology for mobile phones and portable computing devices as it supports

advanced power management. Includes a reduced interface voltage of 1.1 V from the 1.8 V specification as compared to LPDDR

memory technology.

Graphic DDR3

GDDR3 (Graphic DDR) offers faster access and is used in graphics-intensive applications such as video cards and gaming

systems.

GDDR5

GDDR5 (Graphic DDR) is a type of high performance dynamic random-access graphics card memory designed for applications

requiring high bandwidth.

xii DDR Analysis Printable Application Help

Page 17

Introduction to the application

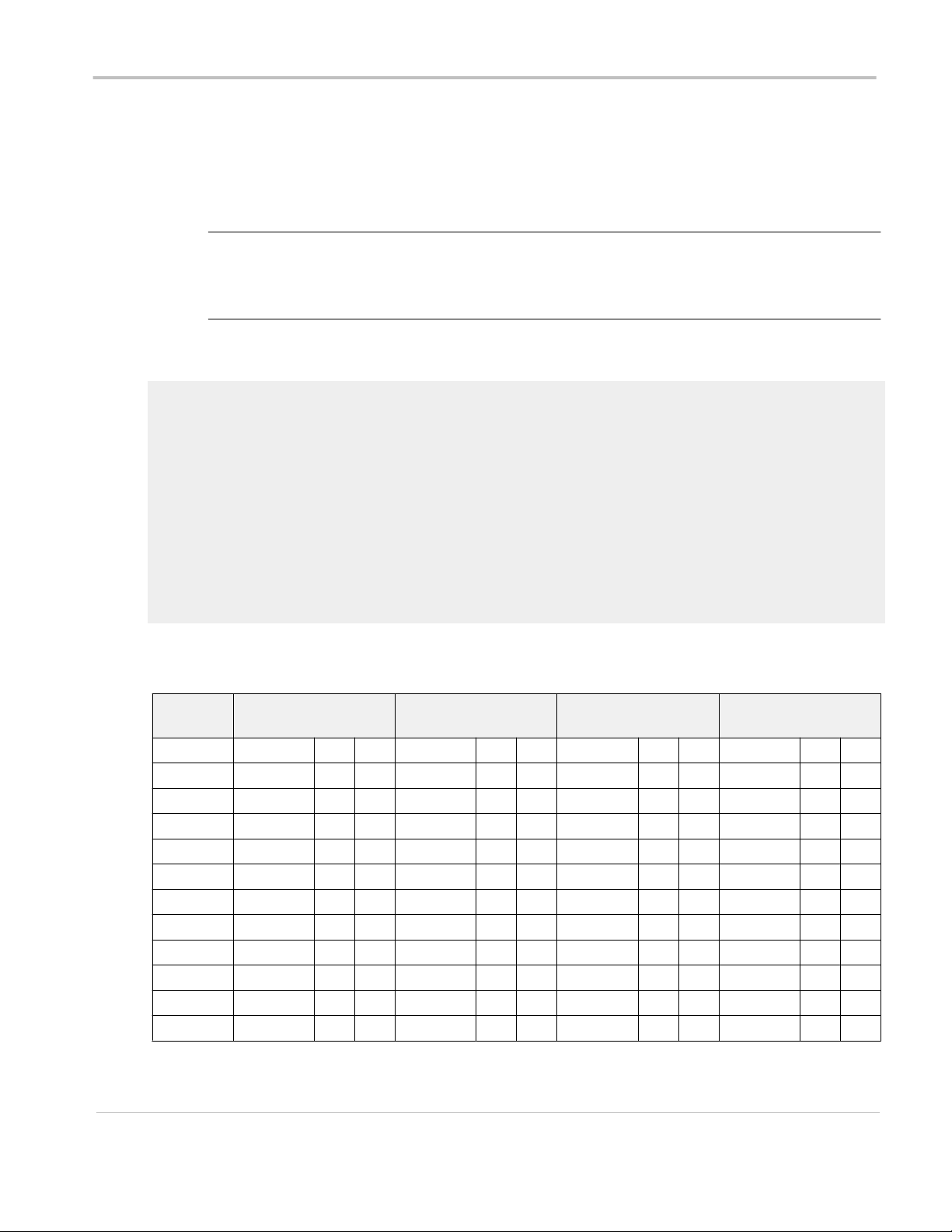

Related documentation

Tektronix manuals are available at: www.tektronix.com/manuals and www.tektronix.com/software. Use the following table to

determine the document that you need:

Table 1: List of reference documents

For information on Refer to

■

Operating the Oscilloscope

■

Software warranty

■

List of available applications

■

Compatible oscilloscopes

■

Relevant software and firmware version numbers

■

Applying a new option key label

■

Installing an application

■

Enabling an application

Oscilloscope user manual.

Oscilloscope user online help.

Optional Applications Software on Windows-Based

Oscilloscopes Installation Manual, which is provided on the

Optional Applications Software on Windows-Based

Oscilloscopes DVD, in the Documents directory.

■

Downloading updates from the Tektronix Web site

Conventions

Online Help uses the following conventions:

■

When steps require a sequence of selections using the application interface, the “>” delimiter marks each transition between

a menu and an option. For example, Analyze> DDR Analysis.

■

The terms “DDR application” and “application” refer to DDRA.

■

The term “DPOJET application” or “DPOJET” refers to Jitter and Eye Diagram Analysis Tool.

■

The term “oscilloscope” refers to any product on which this application runs.

■

The term “DUT” is an abbreviation for Device Under Test.

■

The term “select” is a generic term that applies to the methods of choosing an option: with a mouse or with the touch screen.

■

User interface screen graphics are taken from a DPO7000 series oscilloscope.

You can find a PDF (portable document format) file for this document in the Documents directory on the Optional Applications

Software on Windows-Based Oscilloscopes DVD. The DVD booklet contains information on installing the application from the

DVD and on how to apply a new label.

DDR Analysis Printable Application Help

1

Page 18

Introduction to the application

Table 2: Icon descriptions

Icon Meaning

This icon identifies important information.

This icon identifies conditions or practices that could result in loss of data.

This icon identifies additional information that will help you use the application more efficiently.

Technical support

Tektronix welcomes your comments about products and services. Contact Tektronix through mail, telephone, or the Web site.

Click Contacting Tektronix for more information. Tektronix also welcomes your feedback. Click Customer feedback for

suggestions for providing feedback to Tektronix.

Customer feedback

Tektronix values your feedback on our products. To help us serve you better, please send us your suggestions, ideas, or other

comments you may have regarding the application or oscilloscope.

Direct your feedback via e-mail to

techsupport@tektronix.com

Or FAX at (503) 627-5695, and include the following information:

General Information

■

Oscilloscope series (for example: DPO7000C or DSA/DPO/MSO70000C/D/DX series) and hardware options, if any.

■

Software version number.

■

Probes used.

Application-specific Information

■

Description of the problem such that technical support can duplicate the problem.

■

If possible, save the oscilloscope and application setup files as .set and associated .xml files.

■

If possible, save the waveform on which you are performing the measurement as a .wfm file.

Once you have gathered this information, you can contact technical support by phone or through e-mail. In the subject field,

please indicate “DDRA Problem” and attach the .set, .xml and .wfm files to your e-mail. If there is any query related to the

actual measurement results, then you can generate a .mht report and send it. If you need to send very large files, technical

support can assist you to transfer the files via ftp (file transfer protocol).

The following items are important, but optional:

■

Your name

■

Your company

■

Your mailing address

2 DDR Analysis Printable Application Help

Page 19

Introduction to the application

■

Your phone number

■

Your FAX number

Enter your suggestion. Please be as specific as possible.

Please indicate if you would like to be contacted by Tektronix regarding your suggestion or comments.

DDR Analysis Printable Application Help 3

Page 20

Introduction to the application

4 DDR Analysis Printable Application Help

Page 21

Getting started

Product description

DDR Analysis is a standard specific solution tool for Tektronix Performance Digital Oscilloscopes (DPO7000C or DSA/DPO/

MSO70000C/D/DX series). DDR Analysis requires Jitter and Eye Diagram Analysis Tool (Opt.DJA) and the advanced Search

and Mark capability (Opt. ASM).

The features of DDRA are:

■

Provides debug, analysis, and compliance in one solution for multiple DDR standards such as DDR, DDR2, DDR3, DDR3L,

DDR4. LPDDR, LPDDR2, LPDDR3, LPDDR4,GDDR3, and GDDR5.

■

Identifies Read and/or Write operations automatically.

■

Custom data rates and input levels to tailor DDRA Read and/or Write burst identification.

■

Provides both single-ended and differential measurements on Data, Strobe, Clock, Address and Command signals.

■

Analyze compliance measurements either through DDRA or Jitter and Eye Diagram Analysis Tool.

■

Limit files to test measurement pass/fail status.

■

Automatically applies signal slew rate derating of measurement limits for Address/Command and data signals.

■

Preferences shortcut available for all DDRA steps. For more details, refer to the DPOJET online help.

■

Logic state configuration using the DDRA user interface.

DDR

DDR is the DRAM (Dynamic Random Access Memory) technology responsible for increasing data transfer rates to meet highspeed requirements and data capacity of computer systems.

DDR2

DDR2 is the Double Data Rate 2 SDRAM and is widely available in products with data rates up to 1066MT/s.

DDR3

DDR3 DRAM memory is widely available in products and extends data rates to 1600 MT/s and faster rates to come.

DDR3L

DDR3L (low voltage) DRAM memory is widely available in products and extends data rates to 1600 MT/s and faster rates to

come.

DDR4

DDR4 DRAM memory is widely available in products and extends data rates to 3200 MT/s and faster rates to come.

Low Power DDR

LPDDR (Low Power DDR) is an emerging technology for mobile phones and portable computing devices, driven by the need for

faster operation with long battery life.

Low Power DDR2

LPDDR (Low Power DDR) is an emerging technology for mobile phones and portable computing devices, driven by the need for

faster operation with long battery life.

DDR Analysis Printable Application Help 5

Page 22

Getting started

Low Power DDR3

LPDDR3 (Low Power DDR3) is a technology for mobile phones and portable computing devices as it supports advanced power

management. Includes a reduced interface voltage of 1.2 V from the 1.8 V specification as compared to LPDDR memory

technology. This results in a power consumption reduced by over 50%.

Low Power DDR4

LPDDR4 (Low Power DDR4) is an emerging technology for mobile phones and portable computing devices as it supports

advanced power management. Includes a reduced interface voltage of 1.1 V from 1.8 V specification as compared to LPDDR

memory technology.

Graphic DDR3

GDDR3 (Graphic DDR) offers faster access and is used in graphics-intensive applications such as video cards and gaming

systems.

GDDR5

GDDR5 (Graphic DDR) is a type of high performance dynamic random-access graphics card memory designed fro applications

requiring high bandwidth.

DDRA prerequisites

To use the DDRA application on instruments using 64-bit operating systems, you need DPOJET Advanced (Opt. DJA) enabled.

Requirements and restrictions

DPOJET (DJA) is required to operate DDRA on your oscilloscope. Also refer to subsequent requirements for DPOJET.

Supported probes

The application supports the following probes:

■

TAP2500

■

TAP1500

■

TCP0030

■

P6158

■

P6101B

■

P6246

■

P6247 (DPO7254 only)

■

P6248 (DPO7254 only)

■

P6249

■

P6150

■

P6158

■

P7240

■

P7260

■

P7330

■

P7340A

6 DDR Analysis Printable Application Help

Page 23

Getting started

■

P7350

■

P7360A

■

P7380A

■

P7313A

■

P7513

■

P7520A

■

P7520

■

P7500 Series TriMode

Installing the application

Refer to the Optional Applications Software on Windows-Based Oscilloscopes Installation Manual for the following information:

■

Software warranty.

■

List of available applications, compatible oscilloscopes, and relevant software and firmware version numbers.

■

Applying a new option installation key label.

■

Installing an application.

■

Enabling an application.

■

Downloading updates from the Tektronix Web site.

You can find a PDF (portable document format) file for this document in the Documents directory on the Optional Applications

Software on Windows-Based Oscilloscopes DVD. The DVD booklet contains information on how to install the application from

the DVD and on how to apply a new option installation key label.

DDR Analysis Printable Application Help 7

Page 24

Getting started

About DDRA

Click Help > About DPOJET to view DDRA application details such as the software released version number, application name

and copyright.

NOTE. The version displayed above is indicative only, the version number displayed will vary depending upon the exact version

of the application installed.

8 DDR Analysis Printable Application Help

Page 25

Operating basics

About basic operations

Starting the application

On the oscilloscope menu bar, click Analyze > DDR Analysis to open the application.

Menu controls

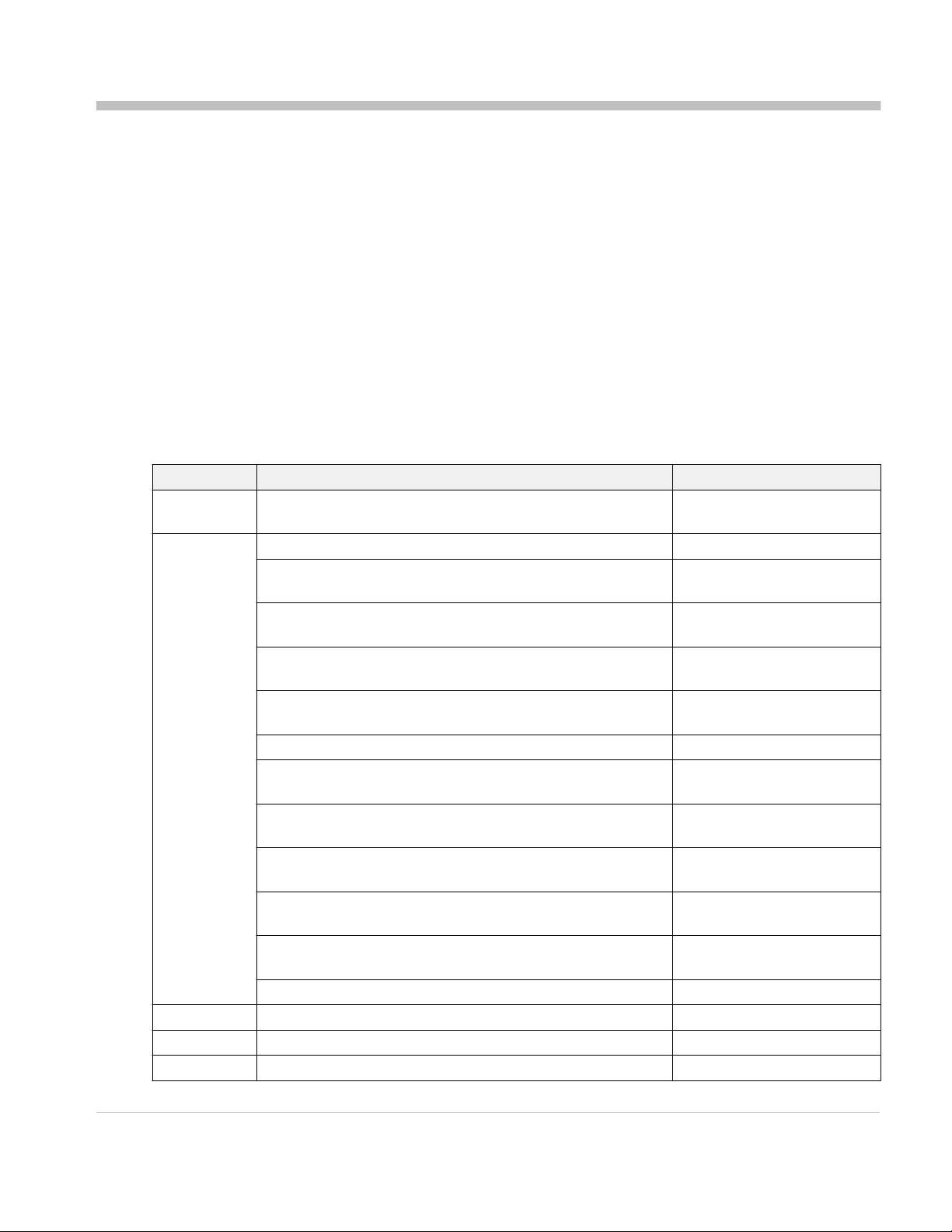

Table 3: Application Menu Controls descriptions

Item Description

Tab Shortcut to a menu in the menu bar or a category of menu options; most tabs are short cuts.

Area Visual frame with a set of related options.

Option button Button that defines a particular command or task.

Field Box that you can use to type in text, or to enter a value with the Keypad or a Multipurpose knob.

Check Boxes Use to select configuration options or clear preferences.

Browse Displays a window where you can look through a list of directories and files.

Command button

Virtual Keypad icon

MP knob references (a or b)

Button that initiates an immediate action such as Run command button in the control

panel.

Click to use on-screen keypad to enter alphanumeric values.

Identifiers that show which Multi Purpose Knob (MPK) may be used as an alternate means to

control a parameter; turn the knob on the oscilloscope front panel to adjust the corresponding

parameter. Also, the value can be entered directly on the MPK display component.

Virtual keypad

Select the

icon and use the virtual keypad to enter alphanumeric values, such as reference voltage levels.

DDR Analysis Printable Application Help 9

Page 26

Operating basics

Tips on the DDRA user interface

Here are some tips to help you with the application user interface:

■

Use the Single button to obtain a set of measurements from a single new waveform acquisition. Pushing the button

again before process is completed will interrupt the processing cycle.

■

Use the Run button

to continuously acquire and accumulate measurements. If prior measurements have been

acquired and have not been cleared, the new measurement are added to the existing set. Push the button again to interrupt

the current acquisition.

■

Use the Recalc button to perform measurements on the waveform currently displayed on the oscilloscope without

performing a new acquisition. This is useful if you wish to modify a configuration parameter and re-run the measurements on

the current waveform.

■

Use the Clear button to clear all existing measurement results. Note that adding or deleting a measurement, or

changing a configuration parameter of an existing measurement, will also cause measurements to be cleared. This is to

prevent the accumulation of measurement statistics or sets of statistics that are not coherent.

10 DDR Analysis Printable Application Help

Page 27

Operating basics

Basic oscilloscope functions

Application directories

The installation directory for DDRA executable files is C:\TekApplications\DDRA for oscilloscope running with Windows

and C:\Users\Public\Tektronix\TekApplications\DDRA for oscilloscopes running with Windows7 operating system. During

installation, the application sets up a limits folder in the user directory. This folder contains limit files for various DDR standards

and speed grades.

For 64-bit systems, the DDRA installer copies the symbol files into the following location: C:\Users\Public\Tektronix

\TekScope\BusDecodeTables\DDR. This is different from the default TekScope location at C:\Users\[Username]

\Tektronix\Tekscope\BusDecodeTables.

File name extensions

Table 4: File name extensions

File Extension Description

.csv An ascii file containing Comma Separated Values. This file format may be read by any ascii text

editor (such as Notepad) or may be imported into spreadsheets such as Excel.

.xml An ascii file containing measurement setup information, limits or other data in Extensible

Markup Language.

.set A binary file containing oscilloscope setup information in a proprietary format.

.mht An HTML archive file, compatible with common Windows applications; contains the full report,

including text and graphics.

.wfm A binary file containing an oscilloscope waveform record in a recallable, proprietary format.

.tsf A symbol file containing various symbols for various logic trigger patterns.

.chm, .pdf Help manuals.

Returning to the application

When you access oscilloscope functions, the DDRA control windows may be replaced by the oscilloscope control windows or by

the oscilloscope graticule. You can access oscilloscope functions in the following ways:

■

From the menu bar on the oscilloscope, choose Analyze > DDR Analysis.

■