Page 1

TM 9-6625-474-14&P-3

TECHNICAL MANUAL

OPERATOR, ORGANIZATIONAL,

DIRECT SUPPORT, AND GENERAL SUPPORT

MAINTENANCE MANUAL

(INCLUDING REPAIR PARTS)

FOR

UNIVERSAL

TEKTRONIX,

COUNTER/TIMER,

MODEL DC 503A

(NSN 6625-01-114-4890)

DEPARTMENT OF THE ARMY

26 DECEMBER 1984

Page 2

WARNING

DANGEROUS VOLTAGE

is used in the operation of this equipment

DEATH ON CONTACT

TM 9-6625-474-14&P-3

personnel fail to observe safety precautions

t if

. .

Never work

may resul

on

electronic equipment unless there is another person nearby who is familiar with the

operation and hazards of the equipment and who is competent in administering first aid. When the

technician is aided by operators, he must warn them about dangerous areas.

Whenever possible, the power supply to the equipment must be shut off before beginning work on the

equipment. Take particular care to ground every capacitor likely to hold a dangerous potential. When

working inside the equipment, after the power has been turned off, always ground every part before

touching it.

Be careful not to contact high-voltage connections when installing or operating this equipment.

Whenever the nature of the operation permits, keep one hand away from the equipment to reduce the

hazard of current flowing through vital organs of the body.

WARNING

Do not be misled by the term “low voltage.”

Potentials as low as 50 volts may cause death under adverse

conditions.

COMMON

any is present on each -

and probe ground straps are electrically connected. Herefore, an elevated reference applied to

as indicated by the yellow warning bands under the probe retractable hook tips.

For Artificial Respiration, refer to FM 21-11,

Power Source

This product is intended to operate in a power module connected to a power source that will not apply more

than 250 volts rms between the supply conductors or between either supply conductor and ground. A

protective ground connection by way of the grounding conductor in the power cord is essential for safe

operation.

a/(b blank)

Page 3

Copyright 1980 Tektronix, Inc. All rights reserved.

Reproduced by permission of copyright owner.

TM 9-6625-474-14&P-3

TECHNICAL MANUAL

DEPARTMENT OF THE ARMY

No. 9-6625-474-14&P-3

Washington, D. C.,

OPERATOR, ORGANIZATIONAL, DIRECT SUPPORT,

AND GENERAL SUPPORT MAINTENANCE MANUAL

(INCLUDING REPAIR PARTS)

FOR

UNIVERSAL COUNTER/TIMER,

TEKTRONIX, MODEL DC 503A

(NSN 6625-01-114-4890)

REPORTING OF ERRORS

You can help improve this manual. If you find any mistakes or if you know of a way

to improve the procedures, please let us know. Mail your Ietter or DA Form 2028

(Recommended Changes to Publications and Blank Forms), direct to: Commander, US Army Missile Command, ATTN: DRSMI-SNPM, Redstone Arsenal, AL

35898-5238. A reply will be furnished to you.

TABLE OF CONTENTS

LIST OF ILLUSTRATIONS

LIST OF TABLES . . . . . . . . . . . . . . . . . . .

SECTION 0

SECTION 1.

SECTION 2.

SECTION 3.

SECTION 4.

SECTION 5.

GENERAL NFORMATION

Scope

indexes of Publications

Forms, Records, and Reports

Reporting Equipment Improvement Recommendations (EIRs)

Administrative Storage

Destruction of Army Electronics Materiel.

SPECIFICATION . . . . . . . . . . . . . . . . . . .

THEORY OF OPERATION.

MAINTENANCE

HEADQUARTERS

26 December 1984

Page

iii

IV

0-1

0-1

0-1

0-1

0-1

0-1

0-1

1-1

2-1

2-1

2-2

2-4

2-4

2-5

2-7

3-1

4-1

4-1

4-8

5-1

This manual is, in part, authenticated manufacturer’s commercial literature. Recommended Spare Parts List has been added to supplement the commercial

literature. The format of this manual has not been structured to consider levels of maintenance.

Page 4

TM 9-6625-474-14&P-3

SECTION 6.

SECTION 7.

SECTION 8.

SECTION 9.

APPENDIX A.

APPENDIX B.

APPENDIX C.

APPENDIX D.

OPTIONS

REPLACEABLE ELECTRICAL PARTS

DIAGRAMS AND CIRCUIT BOARD ILLUSTRATIONS

REPLACEABLE MECHANICAL PARTS

REFERENCES

MAINTENANCE ALLOCATION CHART (MAC)

RECOMMENDED SPARE PARTS LIST

MANUAL CHANGE INFORMATION

TABLE OF CONTENTS (CONT)

Page

6-1

7-1

8-1

9-1

A-1

B-1

C-1

D-1

ii

Page 5

LIST OF ILLUSTRATIONS

TM 9-6625-474-14&P-3

Fig. No.

0-1

2-1

2-2

2-3

2-4

2-5

2-6

3-1

4-1

4-2

4-3

4-4

5-1

5-2

5-3

5-4

5-5

5-6

5-7

5-8

5-9

5-10

Title

DC 503A Universal Counter/Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Plug-ln lnstallation/Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Controls and Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Triggering Circuit Response to Improper (A) and

Proper (B) Level Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Representation of lnterval Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . .

Typical CHAand CH B Level out Voltage Settings for

Various Time interval Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

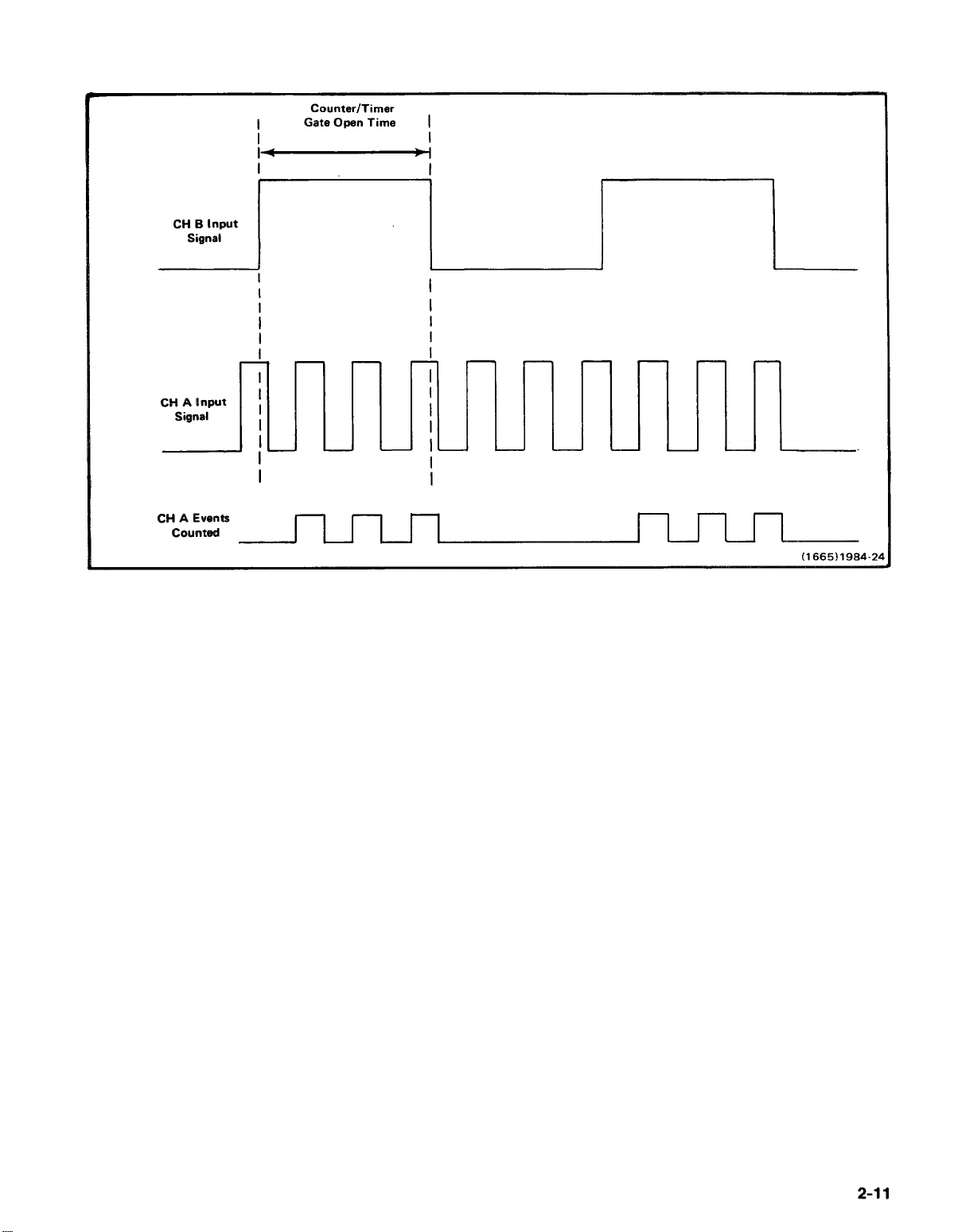

Illustration ofCH A Events Counted from Portion of

CH A Signal Pulses during the Counter Gate Open

Time (Controlled by the CH B Signal) . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Typical DC 503A Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Check Set-Up for the High Frequency Sensitivity

Using X1 and X5 Attenuation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Check Set-Up for Low Frequency ac and dc Sensitivity . . . . . . . . . . . . . . .

Check Set-Up for Minimum Pulse Width Signals . . . . . . . . . . . . . . . . . . . . .

Check Set-Up for Trigger Level Range (3.5V) and

Accuracy

(Y20mVf0.59’0

of Reading) . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Typical Square Pin Assembly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Exploded View of Circuit Board Pin and Ferrule . . . . . . . . . . . . . . . . . . . . . .

Dual Entry Circuit Board Pin Socket . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bottom Entry Circuit Board Pin Socket . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Orientation and Disassembly of Multipin Connectors . . . . . . . . . . . . . . . . .

Rear Frame Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Board Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pushbutton Switch Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Rear Interface Connector Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Rear Interface Timing for a Display of 1079.0674 . . . . . . . . . . . . . . . . . . .

Page

0-2

2-1

2-3

2-5

2-9

2-10

2-11

3-5

4-4

4-6

4-8

4-12

5-3

5-3

5-4

5-4

5-4

5-5

5-5

5-5

5-7

5-8

iii

Page 6

TM 9-6625-474-14&P-3

LIST OF TABLES

Table No.

1-1

1-2

1-3

1-4

2-1

2-2

2-3

2-4

2-5

3-1

4-1

5-1

Title

Electrical Characteristics . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Environmental . . . ....... . . . . . . . . . . . . . . . . . . . . . . . . . . .

Physical Characteristics ... . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frequency A Display Check. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page

1-2

1-7

1-7

1-8

2-5

Period B, Time A-B, Width B (Timing Mode)

Display Check

2-6

Period B, Time A- B, Width B (Averaging Mode)

Display Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ratio A/B and Events A During B Display Check . . . . . . . . . . . . . . . . . . . . .

Gate Time vs Measurement Resolution . . . . . . . . . . . . . . . . . . . . . .

PROM Selection Code . . . . . . . . . . . . . . . . . . . . . . . . . . . .

List of Test Equipment Requirements . . . . . . . . . . . . . . . . . . . .

Relative Susceptibility to Static Discharge Damage

2-6

2-6

2-8

3-10

4-2

5-1

iv

Page 7

SECTION 0

GENERAL INFORMATION

TM 9-6625-474-14&P-3

0-1. Scope. This manual contains instructions for

the operator, organizational, direct support, and general support maintenance of and calibration procedures for Tektronix Universal Counter/Timer, Model DC

503A. Throughout this manual, Tektronix Universal

Counter/Timer, Model DC 503A is referred to as the

DC 503A.

0-2. Indexes of publications. a. DA Pam 310-4.

Refer to the latest issue of DA Pam 310-4 to determine whether there are new editions, changes, or

additional publications pertaining to Tektronix Universal Counter/Timer, Model DC 503A.

b. DA Pam 310-7. Refer to the latest issue of DA

Pam 310-7 to determine whether there are modification work orders (MWO’S) pertaining to Tektronix

Universal Counter/Timer, Model DC 503A.

0-3. Forms, Records, and Reports. Department of

Army forms and procedures used for equipment maintenance and calibration are those prescribed by TM

38-750, The Army Maintenance Management System.

Accidents involving injury to personnel or damage to

materiel will be reported on DA Form 285, Accident

Report, in accordance with AR 385-40.

0-4. Reporting Equipment Improvement Recommendations (EIR). If your DC 503A needs im-

provement, let us know. Send us an EIR. You, the

user, are the only one who can tell us what you don’t

like about your equipment. Let us know why you don’t

like the design. Tell us why a procedure is hard to

perform. Put it on an SF 368 (Quality Deficiency

Report). Mail it to Commander, U.S. Army Missile

Command, ATTN: DRSMI-QMD, Redstone Arsenal,

AL 35898-5290. We’ll send you a reply.

0-5. Administrative Storage. To prepare the Tektronix Universal Counter/Timer, Model DC 503A for

placement into and removal from administrative storage, refer to Section 3, Chapter 4, AR 750-25-1,

Maintenance of Equipment and Supplies. Temporary

storage should be accomplished in accordance with

TB 750-25-1, Section 2, Maintenance of Supplies and

Equipment.

0-6. Destruction of Army Electronics

Materiel. Destruction of Tektronix Universal Counter/

Timer, Model DC 503A to prevent enemy use shall be

in accordance with TM 750-244-2.

0-1

Page 8

TM 9-6625-474-14&P-3

0-2

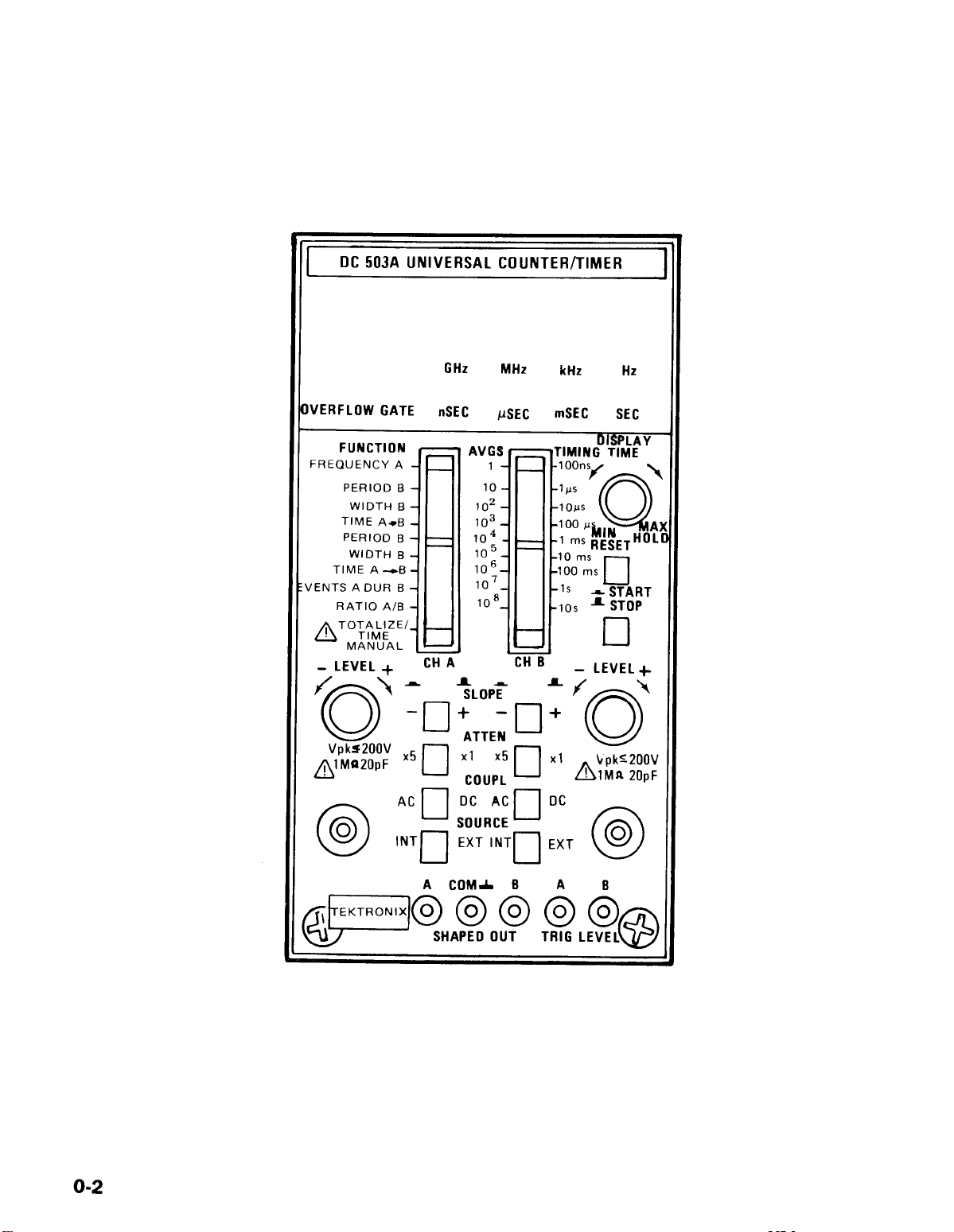

Fig. 0-1. DC 503A Universal Counter/Timer

Page 9

SECTION 1

SPECIFICATION

TM 9-6625-474-14&P-3

Instrument Description

The DC 503A Universal Counter/Timer is designed to

operate in a TM 500-series power module.

The instrument has two input channels, CH A and CH

B, each with 125 MHz capability. Each channel has

separate triggering level, triggering slope, attenuator, and

coupling mode controls.

The DC 503A has eight measurement functions: FREQUENCY A, PERIOD B, WIDTH B, TIME A - B,

RATlO A/B, EVENTS A DURING B, TOTALIZE A, and

TIME MANUAL. All of the modes except FREQUENCY A,

TOTALIZE A, and TIME MANUAL have the capability of

averaging the selected measurement over a range of 1 to

10*

times the input signal. The signals to be counted or

measured can be applied via front panel bnc connectors or

through the rear Interface.

The triggering level for each channel can be monitored

via the front panel or the rear i nterface connections. The

buffered voltage available at these connectors corresponds to the trigger levels set by the front panel

controls.

The output of the internal signal shaping circuits can

also be monitored via front panel connectors. These

shaped signal outputs are useful in setting the triggering

points on complex waveforms.

Instrument Options

Option 01 replaces

(clock) circuit with

temperature controlled oven oscillator for increased accuracy and stability.

Standard Accessories

1 Instruction Manual

1 Cable assembly, bnc-to-tip jack.

Refer to the tabbed Accessories page at the rear of

this manual for more information.

Performance Conditions

The limits stated in the Performance Requirements

columns of the following tables are valid only if the

DC 503A has been calibrated at an ambient temperature

between +20°C and +30°C and is operating at an ambient

temperature between

stated.

the internal 10 MHz time base

a self-contained proportional

NOTE

O“C

and

+50”C,

unless otherwise

Measurement results are displayed in an eight digit

LED readout. The decimal point is automatically positioned and leading zeros are blanked. Single annunciators

(LEDs) are used to indicate register overflow, active gating

interval, and the frequency or time units associated with

the measurement being made.

The DC 503A can be equipped with an optional, oven

controlled, 10 MHz crystal oscillator to obtain a highly

stable and precise internal time base. Both the optional

oscillator and the standard 10 MHz time bases provide

100 ns single shot resolution.

Information given in the Supplemental Information and

Description columns of the following tables is provided for

user information only and should not be interperted as

Performance Check requirements.

The DC 503A must be operated or stored in an

environment whose limits are described under Environmental Characteristics.

Allow at least 20 minutes warm-up time for operation to

specified accuracy, 60 minutes after storage in a high

humidity environment.

1-1

Page 10

TM 9-6625-474-14&P-3

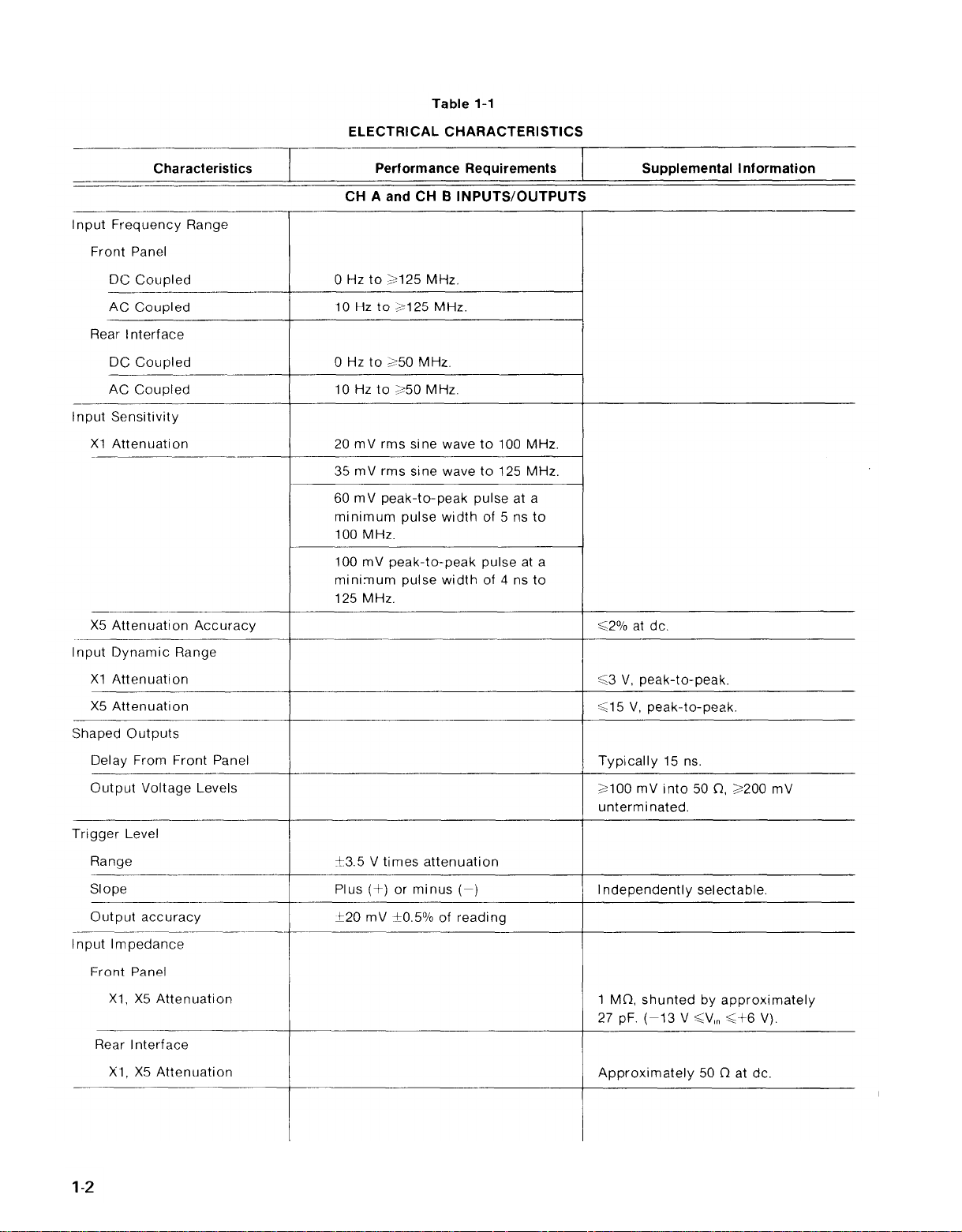

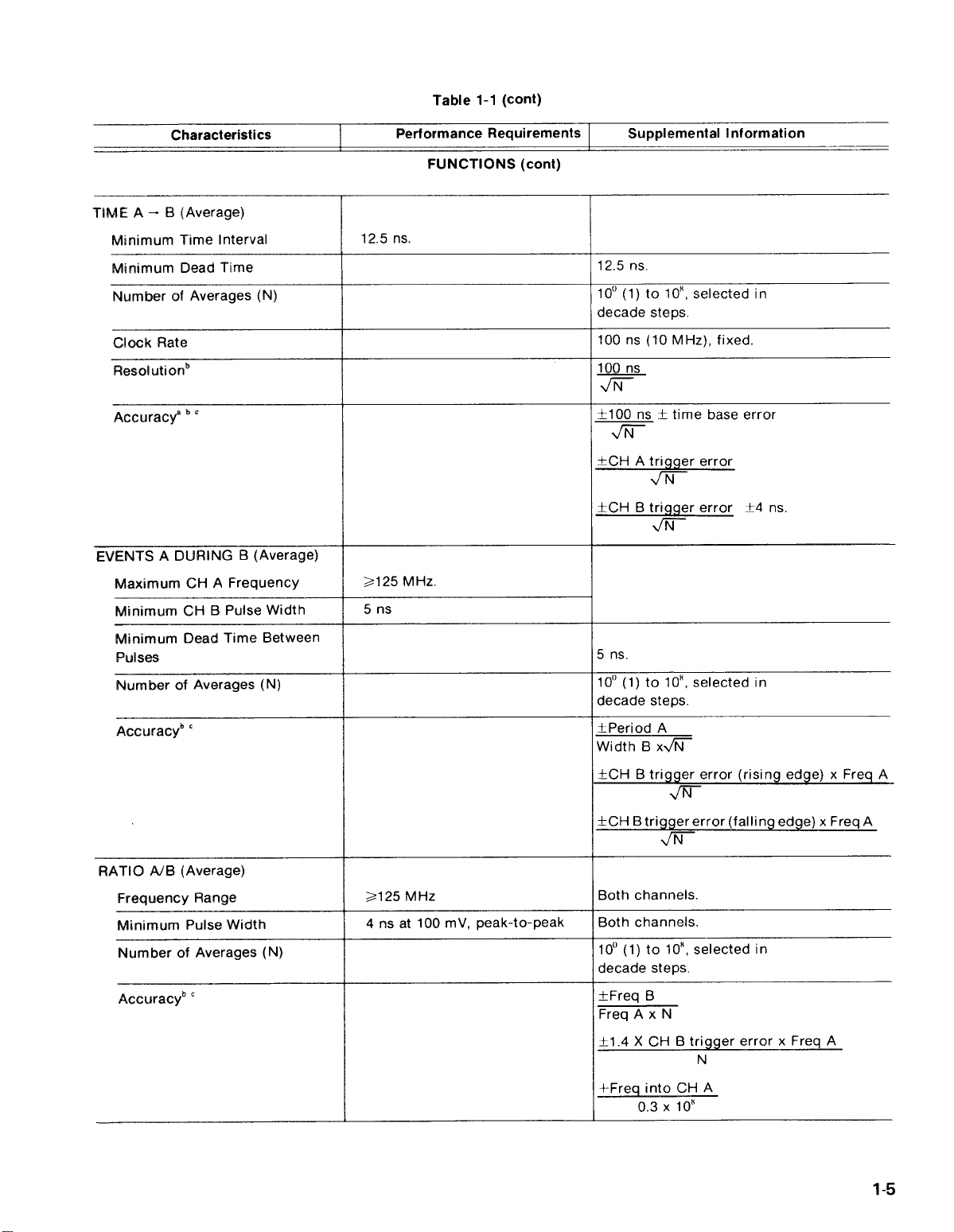

Table 1-1

1-2

Page 11

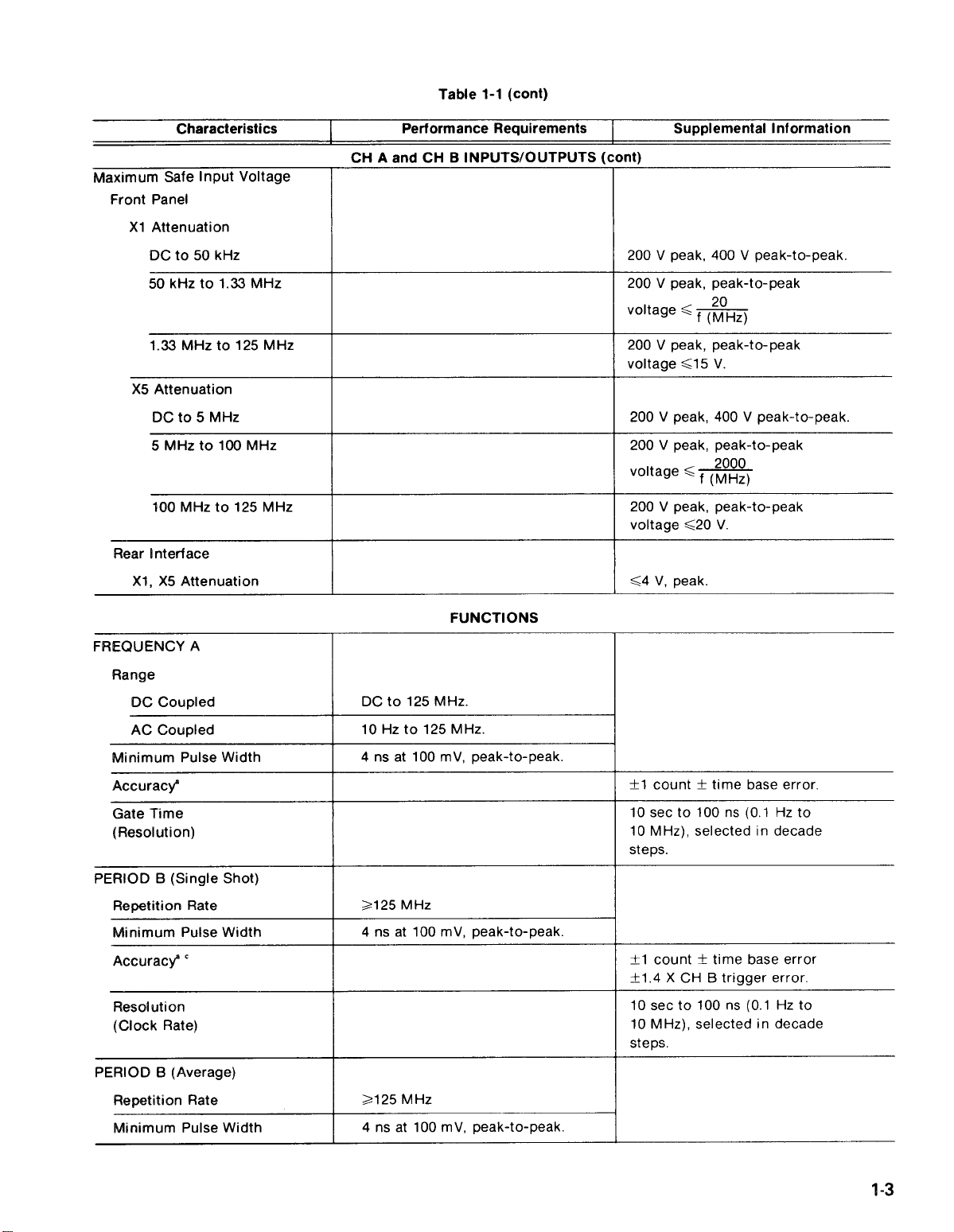

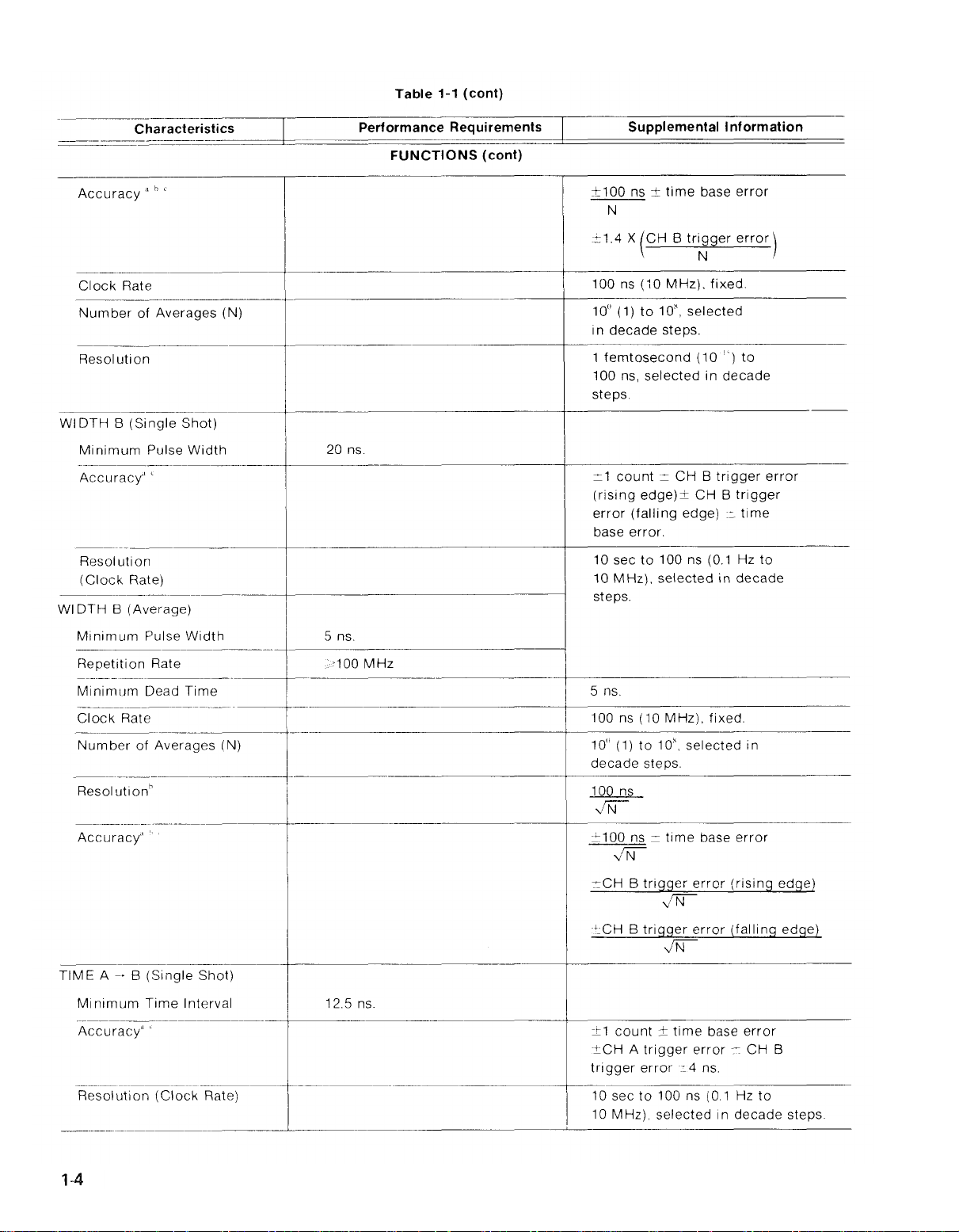

Table 1-1

TM 9-6625-474-14&P-3

1-3

Page 12

TM 9-6625-474-14&P-3

Table 1-1

1-4

Page 13

Table 1-1

TM 9-6625-474-14&P-3

1-5

Page 14

TM 9-6625-474-14&P-3

Table 1-1

1-6

Page 15

Table 1-1

Table 1-2

TM 9-6625-474-14&P-3

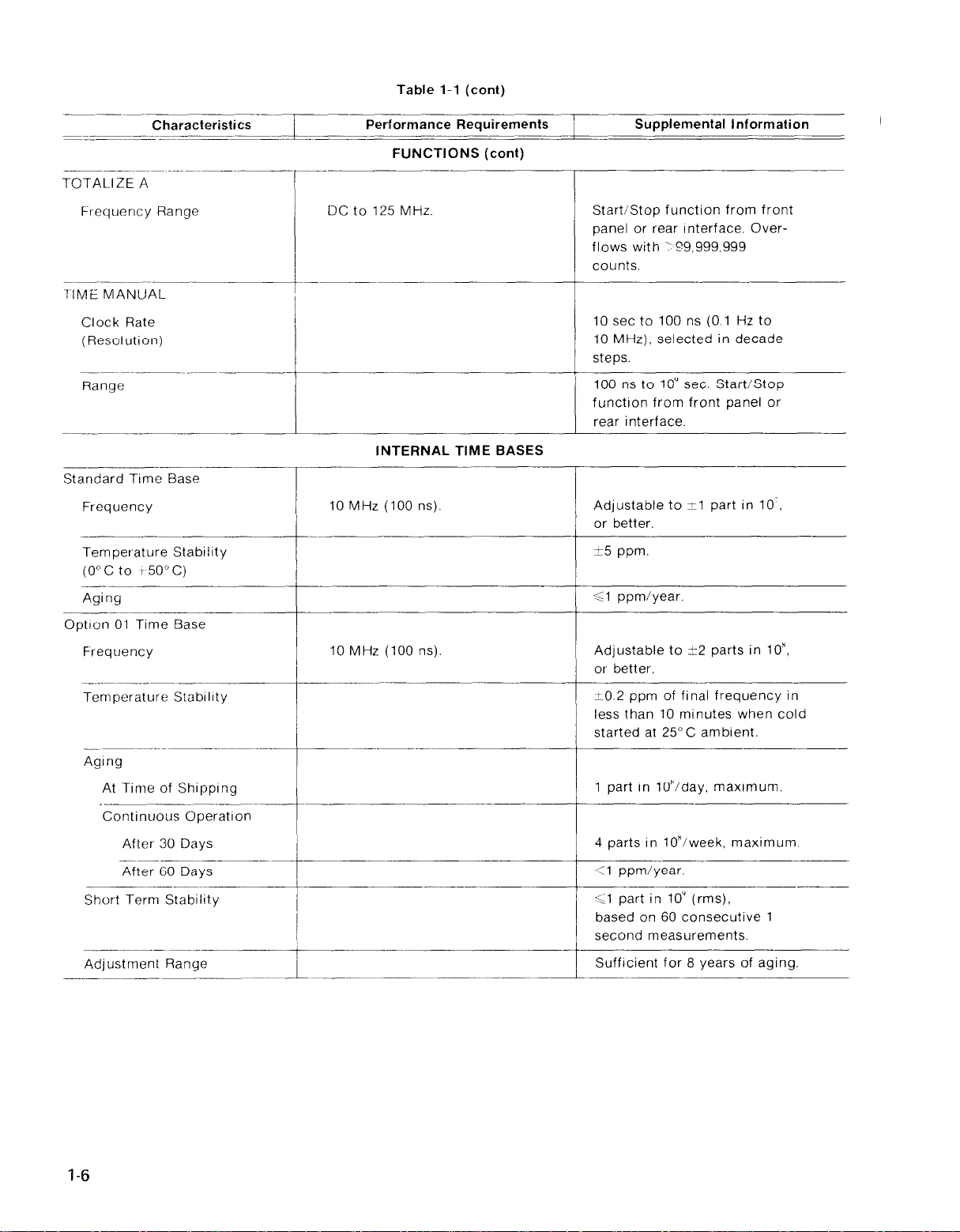

Table 1-3

1-7

Page 16

TM 9-6625-474-14&P-3

Table 1-3

Table 1-4

1-8

Page 17

TM 9-6625-474-14&P-3

SECTION 2

OPERATING INSTRUCTIONS

INTRODUCTION

This section of the manual provides installation and

removal instructions and the operating information re-

quired to obtain the most effective performance from the

instrument. Also included is the function of all front panel

controls and a general description of the operating modes,

which also describes procedures for making basic

measurements.

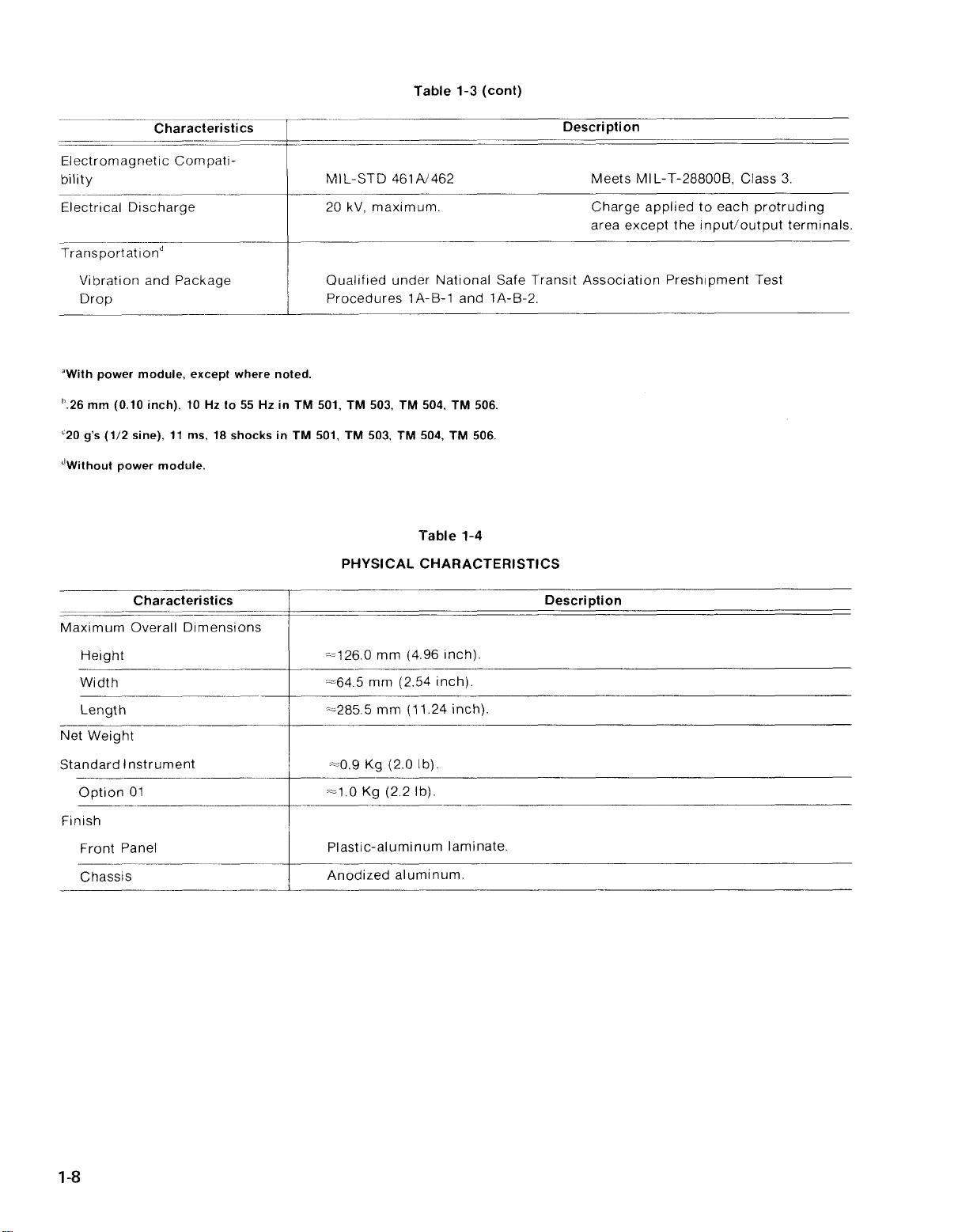

INSTALLATION AND REMOVAL

The DC 503A is calibrated and ready to use when

received. It operates in one compartment of a TM 500-

Series power module. Refer to the power module instruc-

tion manual for line voltage requirements and power

module operation.

To prevent damage to the DC 503A, turn the power

module off before installation or removal of the

instrument from the mainframe. Do not use excessive force to install or remove.

press firmly to seat the circuit board edge connector in the

power module interconnecting jack. Apply power to the

DC 503A by operating the power switch on the power

module.

To remove the DC 503A from the power module, pull

the release latch (located in the lower left corner) until the

interconnecting jack disengages. The DC 503A will now

slide straight out.

Check to see that the plastic barriers on the inter-

connecting jack of the selected power module compart-

ment match the cutouts in the DC 503A circuit board edge

connector. If they do not match, do not insert the

instrument until the reason is investigated. When the units

are properly matched, align the DC 503A chassis with the

upper and lower guides of the selected compartment (see

Fig. 2-1). Insert the DC 503A into the compartment and

Fig. 2-1. Plug-in installation/removal.

2-1

Page 18

TM 9-6625-474-14&P-3

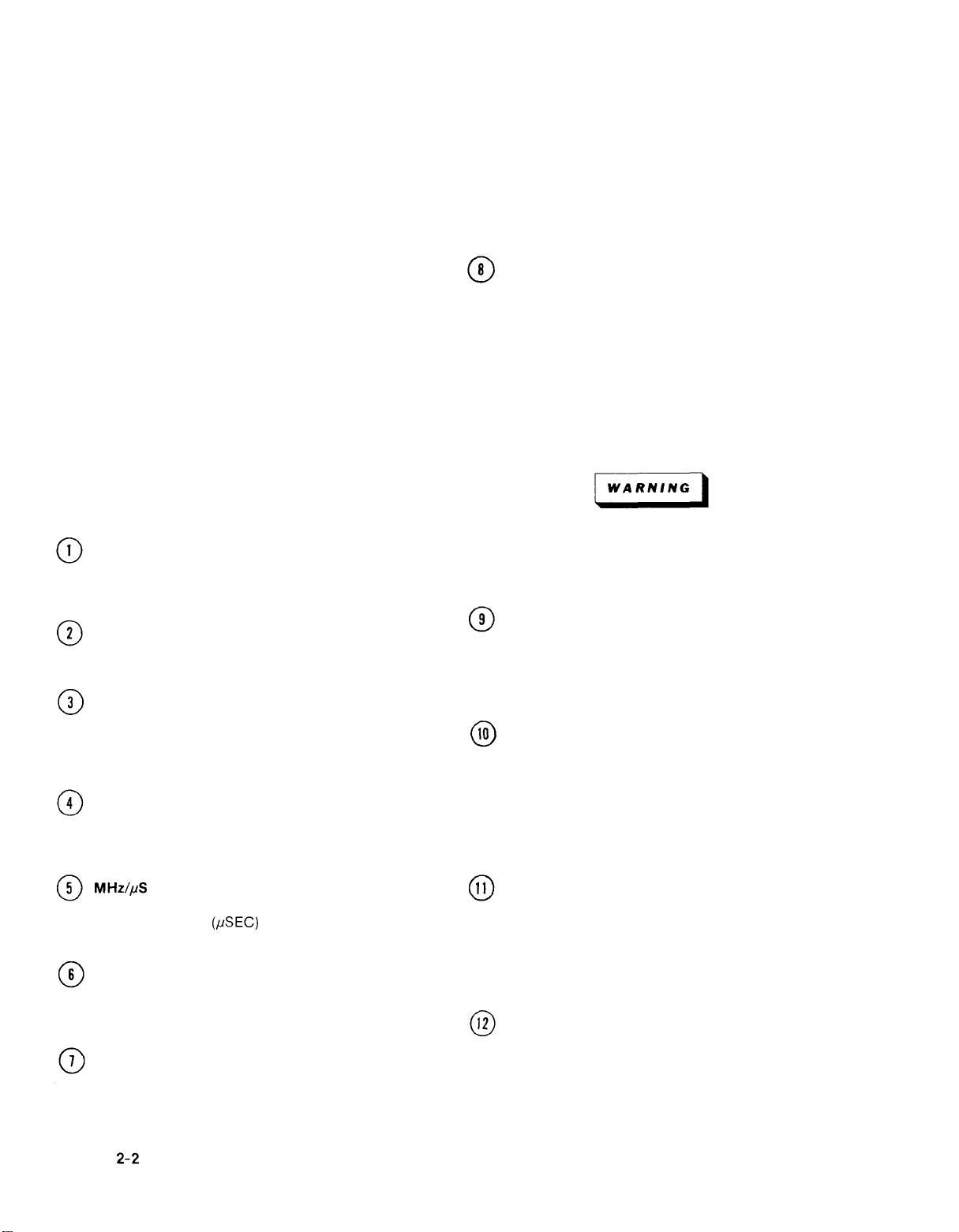

CONTROLS AND CONNECTORS

Even though the DC 503A is fully calibrated and ready

to use, the functions and actions of the controls and

connectors should be reviewed before attempting to use

it.

With the exception of the TOTALIZEA/TIME MANUAL

jumper, which is described in the maintenance section, all

controls for operation of the DC 503A are located on the

front panel. A brief functional description of these controls

follows (refer to Fig. 2-2).

NOTE

Because the Channel A and Channel B controls are

identical, only Channel A will be described.

DISPLAY AND UNIT INDICATORS

DISPLAY READOUT: eight-digit, seven segment

LED readout with automatically positioned decimal

point.

OVERFLOW: when illuminated indicates register

overflow.

MODE SELECTION AND

CONTROL FUNCTIONS

FUNCTION: selects the measurement, events, or

time counting modes for the counter.

NOTE

The TOTALIZE A/TIME MANUAL position is an

"either/or"

MANUAL is selected and set by positioning an

Internal jumper. Placement of this jumper is discussed in the maintenance section.

Unless you are qualified to do so, refer positioning of

this jumper to qualified personnel.

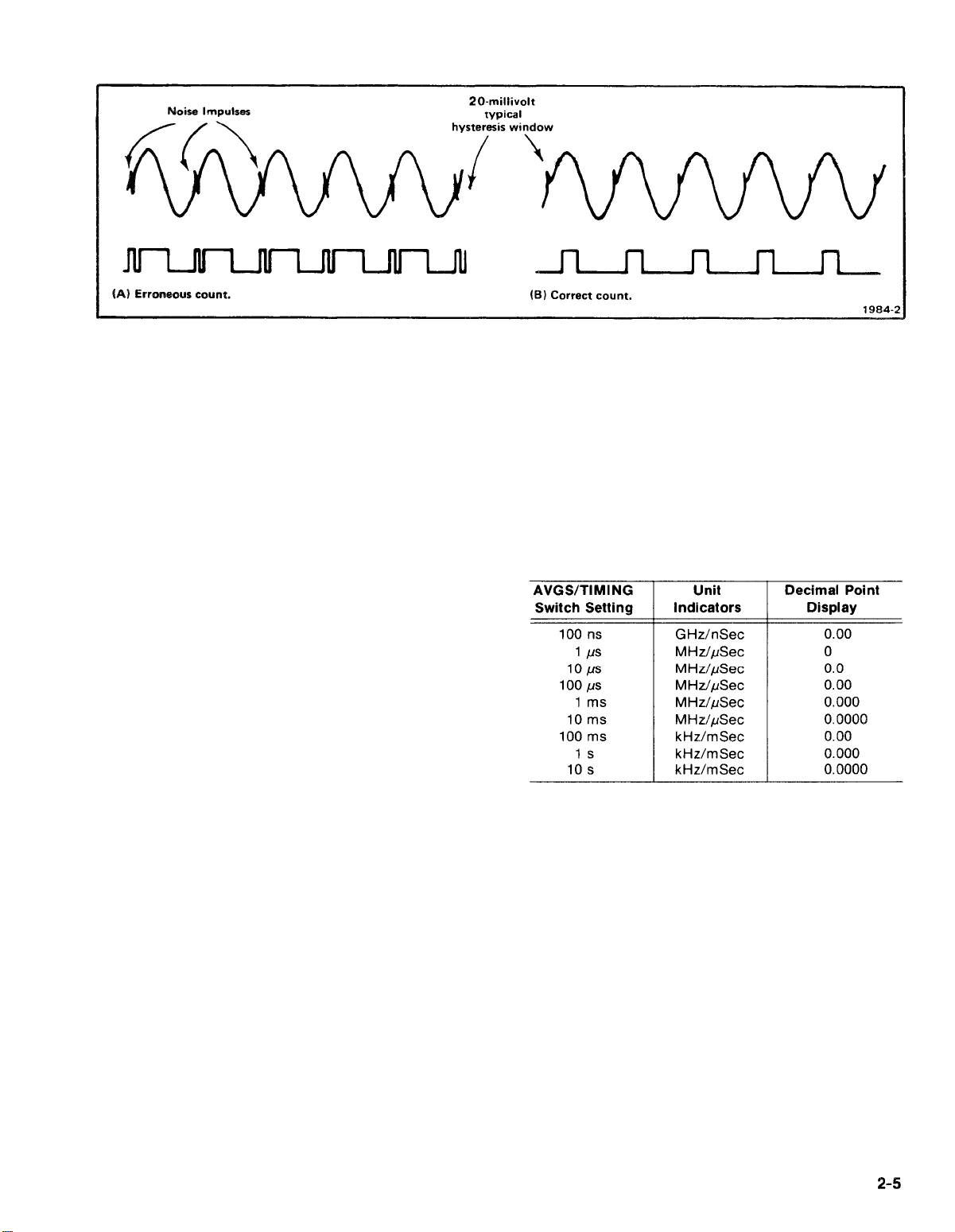

AVGS/TIMING: depending on the position of the

FUNCTION switch, this switch selects the clock rate

which will be counted or the number of

measurements to be averaged.

function.

TOTALIZE A or TIME

GATE: indicates the state of the main gate. When lit,

the main gate is open (the DC 503A is in the process

of making a measurement). When the light is off, the

gate is closed.

GHz/nSEC: when illuminated, indicates the displayed number is gigahertz (GHz) in FREQ A mode

or nanoseconds (nSEC) in a time mode.

MHz/uSEC:

played number is Megahertz (MHz) in FREQ A mode

or microseconds

kHz/mSEC: when illuminated, indicates the displayed number is kilohertz (kHz) in FREQ A mode or

milliseconds (m SEC) in a time mode.

Hz/SEC: when illuminated, indicates the displayed

number is Hertz (Hz) in FREQ A mode or seconds

(SEC) in a time mode.

when illuminated, indicates the dis-

(HSEC)

in a time mode.

2-2

DISPLAY TIME: sets the length of time the reading

will be displayed after the count is made and before

the next measurement is taken, Display time can be

varied from about 0.1 second, fully counterclockwise (ccw), to about 10 seconds fully clockwise

(cw). The HOLD position provides continuous display until reset by pushing the RESET button,

RESET: momentary switch resets the count to zero

when operating in the TOTALIZE A mode. Also acts

as a master reset, ensuring that the readout has been

cleared before the next measurement. Provides a

check of all display LED’s; when pressed, a row of 8’s

will be displayed in the readout window.

START/STOP: push-push switch acts as a manual

gate when the FUNCTION switch is in the

TOTALIZE A/TIME MANUAL position. Button in

Starts the measurement interval gate; button out

terminates the gate.

Page 19

TM 9-6625-474-14&P-3

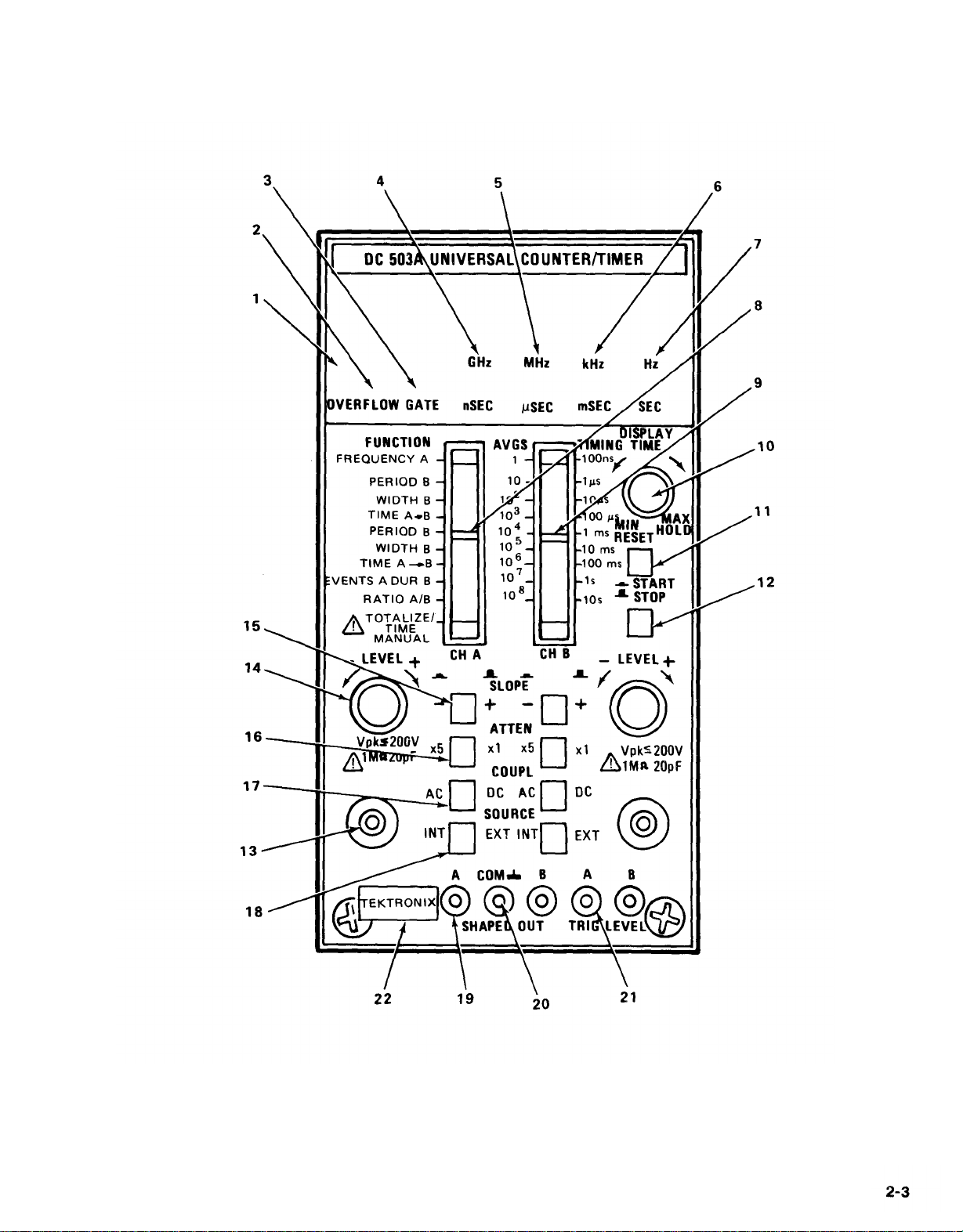

Fig. 2-2. Controls and connectors.

2-3

Page 20

TM 9-6625-474-14&P-3

CHANNEL A INPUT AND LEVEL

FUNCTIONS

CH A INPUT: bnc connector for Channel A signal

input. Input impedance is 1 shunted by approximately 20 pF.

LEVEL: selects the amplitude point on the positive or

negative slope of the input signal at which the

triggering window is placed.

SLOPE: push-push switch selects the slope of the

input signal on which triggering will occur, Button

out selects plus (+) slope; button in minus (–) slope.

ATTEN: push-push switch selects X1 (button out) or

X5 (button in) attenuation of the input signal.

COUPL: push-push switch selects DC (button out)

or AC (button in) coupling of the input signal to the

attenuator circuit.

SOURCE: push-push switch selects the source of

the input signal. Button out, EXT, selects the front

panel connector as a signal source. Button in, INT,

routes the input signal to the counter via the rear

interface connections.

SHAPED OUT A: provides a shaped output signal

derived from the output of the Channel A signal

shaper circuitry.

SHAPED OUT GND: common connector for

Channel A shaped output signals.

TRIG LEVEL A: pin jack permits monitoring of the

Channel A triggering voltage level.

RELEASE LATCH: pull to disengage and remove

DC 503A from the power module.

INPUT CONSIDERATIONS

Input Sources

NOTE

Maximum input voltage limited to 200 V peak.

The SOURCE switch for each channel selects either the

front panel bnc connector (external), or the rear interface

connector (internal) pins. The external inputs present

impedances of approximately 1 paralleled by about 27

pF. The internal input circuits present nominal 50

impedances to match typical coaxial cable signal connections.

Input Coupling

Front panel pushbuttons select ac (capacitive) or dc

(direct) coupling for the input signal of each channel. This

coupling takes place before the signals are passed into the

attenuator circuits.

Attenuators and Maximum Input Volts

For either attenuation factor, X1 or X5, the maximum

safe input voltatage that can be applied to the front panel

bnc connectors is 200 V (peak) from dc to 50 kHz. At

frequencies above 50 kHz, the maximum safe peak-to-

peak input voltage tothe front panel bnc connectors must

be calculated (see Specification section). The maximum

safe input voltage to the rear interface input connectors is

equal to or less than 4 V (dc plus peak ac) from dc to

50 MHz.

Sensitivity and Frequency Range

CH A and CH B will respond to a signal amplitude of

20 mV rms sinewave, times attenuation, to lOO MHzandto

a sinewave of 35 mV rms, times attenuation, to 125 MHz.

[)

Depending on the coupling mode selected, the low

frequency limit for each channel is either zero (dc

coupled) or 10 Hz (ac coupled).

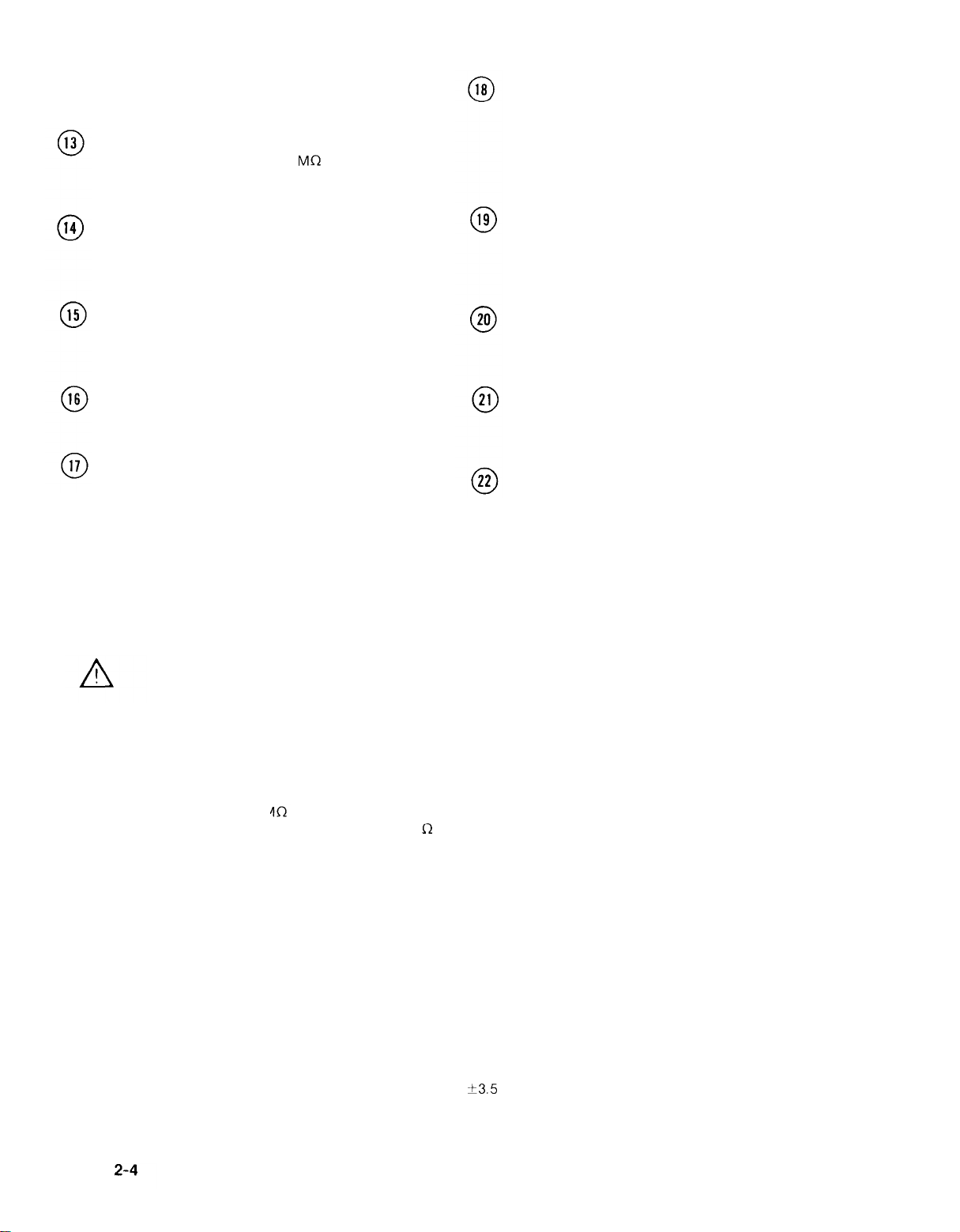

Slope and Level

The SLOPE pushbuttons for each channel determine

whether the trigger circuits will respond to the negative or

positive transition of the input signal.

Refer to Fig. 2-3. The LEVEL control for each channel

allows the operator to move the hysteresis window of the

trigger circuit to an optimum level on the input signal to

ensure stable triggering The LEVEL control adjusts over

+3.5 V, times attenuation, of the input signal. This level

can bemoniiored atthefront panel TRIG LEVEL pin jacks.

2-4

Page 21

TM 9-6625-474-14&P-3

Fig. 2-3. Triggering circuit response to improper (A) and proper (B) level settings.

OPERATORS FAMILIARIZATION

PREPARATION

Turn on the power module to apply power to the

DC 503A. One or more characters in the display should be

visible. Allow twenty minutes warm-up time for operation

to specified accuracy.

DISPLAY TESTS

With no signal applied, test the DC 503A readout

displays and switching logic. The following checks will

test most of the major circuits of the counter and ensure its

readiness to make measurements. If any malfunctions are

encountered, refer

personnel.

Readout Segment

Press the RESET

segments of each digit. A row of 8's should be displayed.

This check of the display devices can be done at anytime.

the condition to qualified service

Test

button to check the seven character

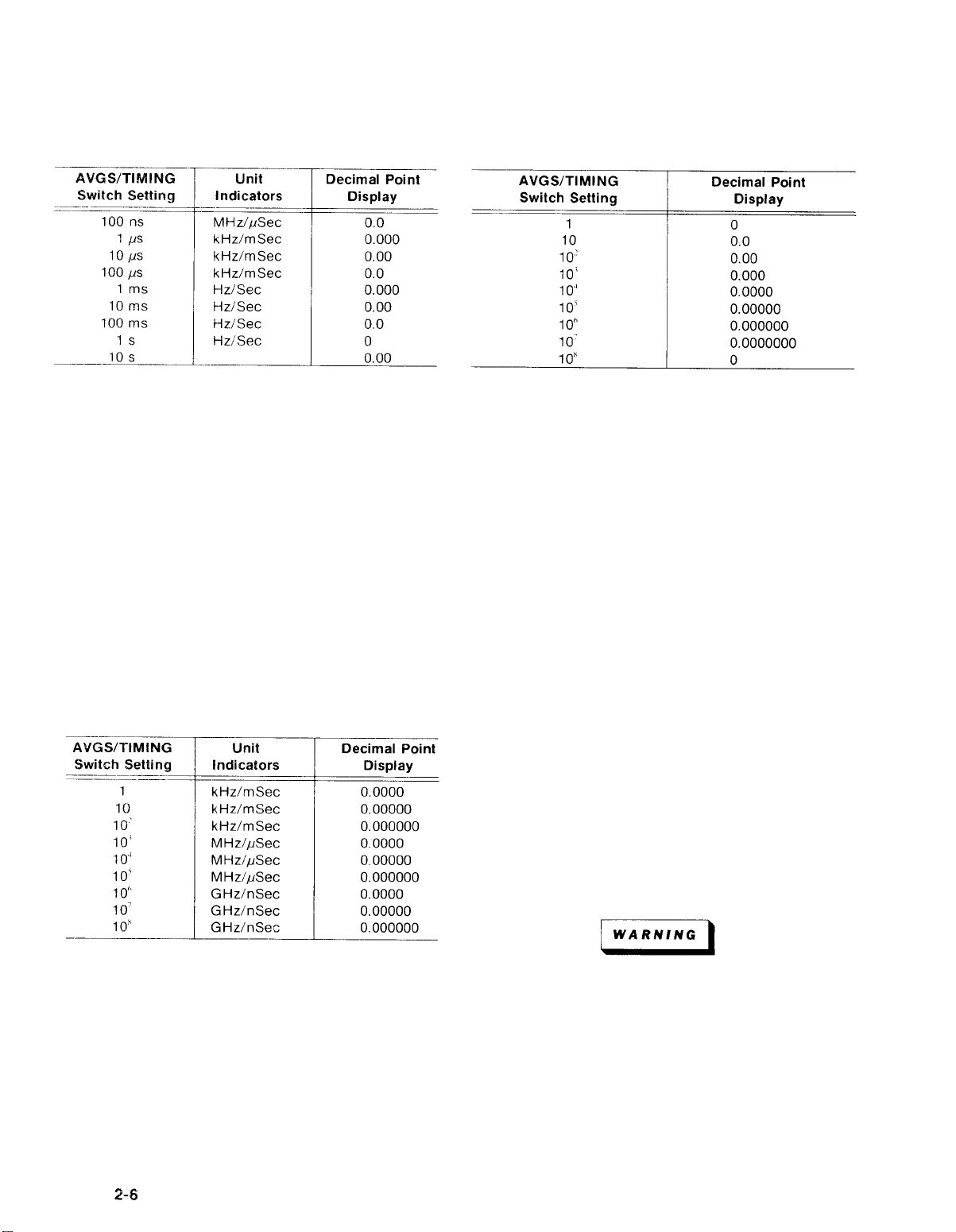

Table 2-1

FREQUENCY A DISPLAY CHECK

With the DISPLAY TIME control in the fully

counterclockwise position, observe that the GATE indicator flashes rapidly for short gate times and more

slowly for longer gate times. Using a short gate time

(100 ms), rotate the DISPLAY TIME control slowly

clockwise. Observe that the GATE indicator stays off for a

longer and longer time, until the control clicks into the

HOLD (detent) position, holding off the gate indefinitely.

Return

counterclockwise position.

the DISPLAY TIME control to the

Frequency A Displays

Set the FUNCTION switch to FREQUENCY A. With the

AVGS/TIMING switch, select a gate time of 100 ns. Check

the decimal point location, leading zero suppression, and

units indicators according to Table 2-1.

Period B, Width B, and Time A - B Displays

Timing Mode. Set the FUNCTION switch to PERIOD B

in the blue area of the front panel and the AVG/TIMING

switch to 100 ns. Observe the correct readout displays as

shown in Table 2-2.

2-5

Page 22

TM 9-6625-474-14&P-3

Table 2-2

PERIOD B, TIME A - B, WIDTH B

(TIMING MODE) DISPLAY CHECK

Set the FUNCTION switch to WIDTH B in the blue area

of the front panel while retaining the setting of the

AVG/TIMING switch; observe the correct readout display.

Set the FUNCTION switch to TIME A - B in the blue

area of the front panel while retaining the setting of the

AVG/TIMING switch; observe the correct readout display.

Table 2-4

RATIO A/B AND EVENTS A

DURING B DISPLAY CHECK

Time Manual Displays

Verify that the jumper located on the Auxiliary Circuit

Board is in the TIME MANUAL position. Set the FUNCTION switch to the TIME MANUAL Position and the

AVGS/TIMING switch to 1 sec.

Averaging Mode. Repeat the preceding checks for

these functions in the dark grey area of the front panel.

Observe the correct readout display for each switch

setting as shown in Table 2-3.

Table 2-3

PERIOD B, TIME A - B, WIDTH B

(AVERAGING MODE) DISPLAY CHECK

Events A During B and Ratio A/B Displays

Set the FUNCTION switch to EVENTS A DURING B

and the AVGS/TIMING switch to 1. Check the readout

displays according to Table 2-4.

Set the FUNCTION switch to RATlO A/B and the

AVGS/TIMING switch to 1. Again check the readout

displays using Table 2-4.

The GATE indicator should light and an advancing

count should be displayed when the START/STOP button

is pushed in. The GATE indicator should go out when the

count is stopped by releasing the START/STOP button.

Check the overflow display by setting the AVGS/TIMING

switch to 100 ns pressing the START/STOP button in, and

letting the count advance, When the last decade (eighth

digit) goes from nine to zero the OVERFLOW indicator will

light. Release the START/STOP button and observe that

the OVERFLOW indicator remains on, but the count does

not change. Pressing the RESET button clears the

overflow condition, sets the count to zero, and extinguishes the OVERFLOW indicator.

Totalize A Display

For this check, the jumper located on the Auxiliary

Circuit Board must be in the Totalize position.

Unless you are qualified to do so, refer placement of

this jumper to qualified personnel.

Set the FUNCTION switch to the TOTALIZE A/TIME

MANUAL position. Observe a zero at the right of the

readout display. The GATE indicator should light when

the START/STOP button is pushed in, and go out when

the button is released. The units indicators and decimal

points should remain off.

2-6

Page 23

TM 9-6625-474-14&P-3

Channel A Slope

Verify that the TOTALIZE/TIME MANUAL jumper is in

the TOTALIZE position. With the FUNCTION switch set to

TOTALIZE A/TIME MANUAL and CH A to + SLOPE

(button out), press the START/STOP button. Turn the CH

A LEVEL control fully clockwise. The readout display

should increase one count each time the control is rotated

from clockwise to counterclockwise (past center position). Verify that the count does not increase when the

control is turned from counterclockwise to clockwise.

Change to - SLOPE (button in) and push the RESET

button to clear the display. The readout should now

increase one count each time the CH A LEVEL control is

rotated from counterclockwise to clockwise (past center).

Turning the control from clockwise to counterclockwise

should not increment the display.

OPERATING MODES

GENERAL

The following discussion provides general information

about each mode of operation and instructions on making

measurements for FREQUENCY A, RATIO A/B, TIME

INTERVAL (WIDTH B and TIME A - B), EVENTS A

DURING B, and TOTALIZE.

FREQUENCY A MODE

In this mode the input signal isconnectedto CH A Input

only, either through the rear interface or the front paneI

connector. Use ac coupling for most frequency

measurements to avoid readjusting the LEVEL control

because of changing dc levels. The repetitive nature of the

signals makes slope selection unnecessary for frequency

measurements. Signals less than 3 volts peak-to-peak

need not be attenuated; larger signals should be

attenuated to within the range of 60 mV to 3 V peak-topeak.

Channel B Slope

Set the FUNCTION switch to PERIOD B, CH B to +

SLOPE (button out), and the AVGS/TIMING switch to 1.

Push the RESET button. Check that the GATE indicator

turns on when the CH B LEVEL control is rotated from

clockwise to the counterclockwise position. Turning the

control back to clockwise should have no effect on the

GATE indicator. Another turn from clockwise to

counterclockwise turns the GATE indicator off.

Change to - SLOPE (button in) and press the RESET

button. Observe that rotating the CH B LEVEL control

from counterclockwise to clockwise and back produces

an action that is just opposite that described in the

preceding paragraph.

changes unreasonably, the DC 503A is not being

triggered properly, either because the controls are not

correctly set or the signal is beyond the capabilities of the

counter.

Measurement Intervals. To adjust the trigger controls,

choose a short gate time such as .1 second or .01 seconds.

This gives rapid feedback via the display whether or not

the counter is being triggered. Final selection of gate time

depends upon the frequency being measured, desired

resolution, and willingness of the operator to wait for a

measurement.

Resolution. A 10 second gate time means the operator

must wait 10 seconds for a measurement to be made and

displayed. This will give 0.1 Hz resolution. A 10 second

count will display fewer than the available eight digits for

any signal below 10 MHz.

Set the FUNCTION switch to FREQUENCY A and, with

the AVGS/TIMING switch, select one of the shorter gate

times. Set the DISPLAY TIME control fully counterclockwise. Connect the signal to be measured to the

input and adjust the LEVEL control for a stable display.

The LEVEL control setting should not be critical unless the

signal amplitude and frequency are close to the specified

limits.

If the count varies from reading to reading, it is

probably caused by jitter in the signal source. If the count

Overflow. Through intentional use of “overflow” dis-

plays, it is possible to improve the resolution of the

counter. Select a gate time that displays the most significant digit as far to the left as possible. Note the numbers

displayed to the right of the decimal. Move the decimal to

the left, by selecting longer gate times, until the desired

resolution is achieved. The OVERFLOW indicator will light

when the most significant number overflows the last

storage register. The relationship between gate time,

measured frequency, displayed digits, and overflow is

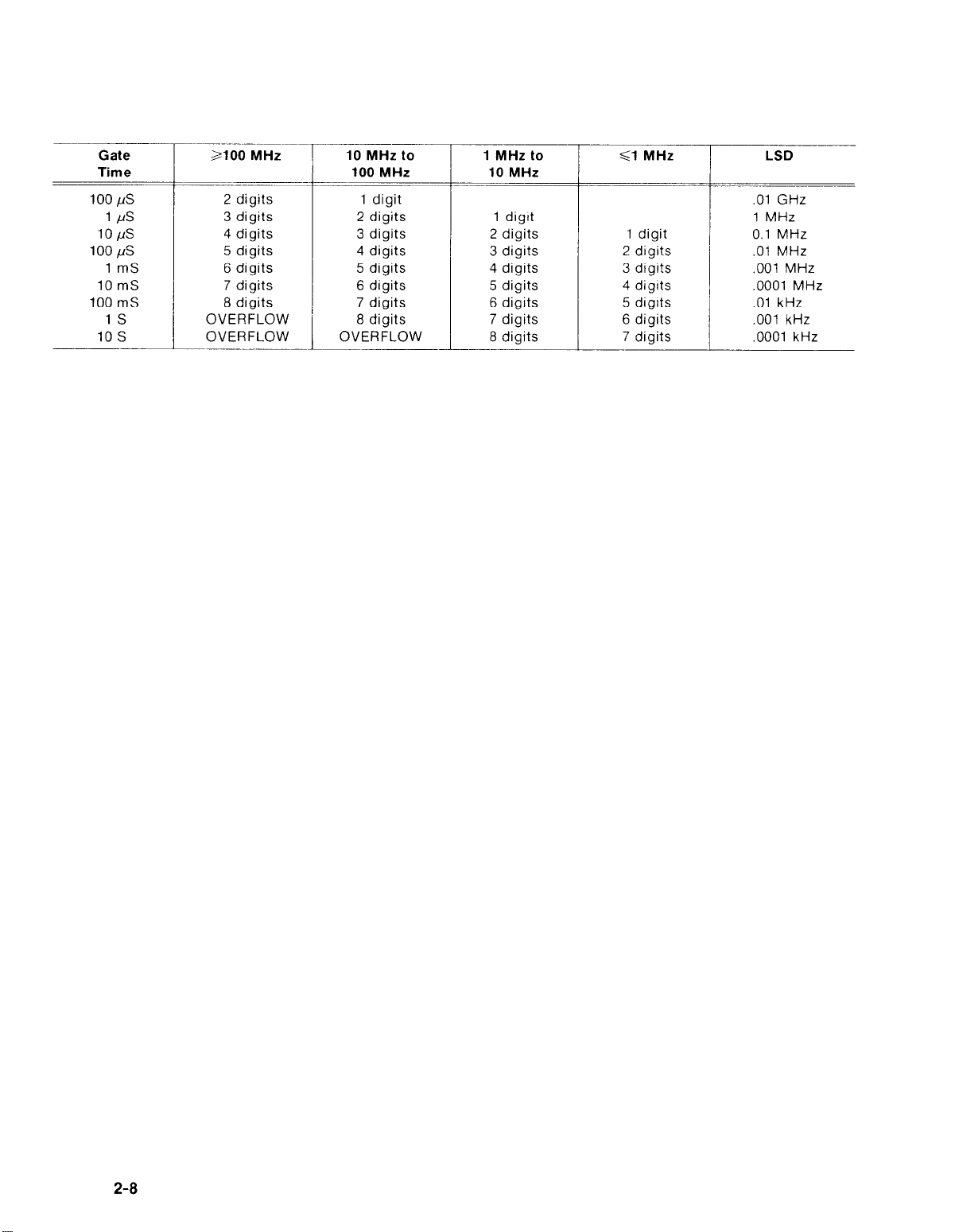

shown in Table 2-5.

2-7

Page 24

TM 9-6625-474-14&P-3

GATE TIME

Table 2-5

VS MEASUREMENT RESOLUTION

Measurement Rate. Once a stable measurement is

obtained, the rate at which measurements are made can

be controlled by the DISPLAY TIME control. Turning the

control clockwise holds off the gate and stores the display

for a longer time before a new measurement is made and

displayed. Display time and gate time together complete a

measurement-display cycle.

The DISPLAY TIME control is uncalibrated and

variable from about 0.1 second (in the MIN position) to

about 5 seconds. At the extreme clockwise end of the

control is a detent position called HOLD. In HOLD, the last

count taken will be stored and displayed for an indefinite

period. A new count and display can be initiated by

pressing the RESET button, moving the DISPLAY TIME

control out of the detent, or changing the gate time.

PERIOD MODES

The period and period average modes allow single

period measurements or multiple period averages to be

made with input frequencies into CH B. These modes are

useful for making low frequency measurements where

maximum resolution is desired without waiting for long

measurement time. Simply stated, the PERIOD B mode

reverses the functions of signal and clock as compared to

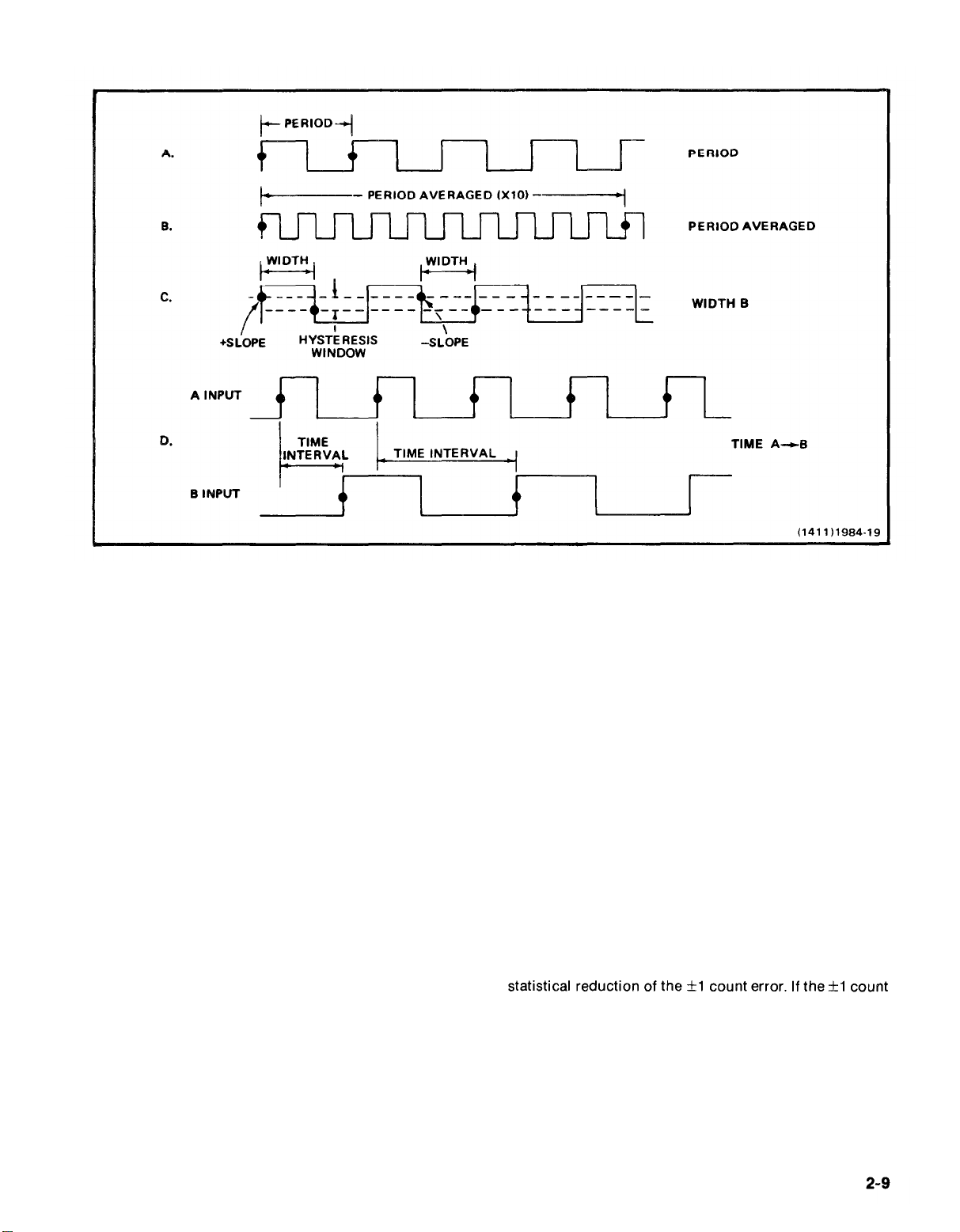

FREQUENCY A mode. Refer to Fig. 2-4A.

Averaging. Resolution and accuracy is improved by

averaging the signal value over a large number of signal

events. This increases the total time to take a measurement, i.e., similar to selecting a longer gate time in

FREQUENCY A mode. Refer to Fig. 2-4B.

preferred. Other wave shapes can be accurately measured

if the amplitude is kept high.

TIME INTERVAL MODES

Two modes of time interval measurement can be

selected: WIDTH B, and TIME A - B. The WIDTH B mode

measures the time between two points on a waveform,

These two points are selected by the CH B triggering

controls such that the counter main gate turns on at the

point selected by the CH B SLOPE and LEVEL controls,

and turns off at the same level but the opposite slope,

Refer to Fig. 2-4C.

The TIME A - B mode measures the time between two

points on two waveforms. These two points are controlled

such that the CH A triggering controls select the point at

which the main gate turns on, andthe CH B controls select

the point at which the main gate turns off. Refer to Fig. 2-

4D.

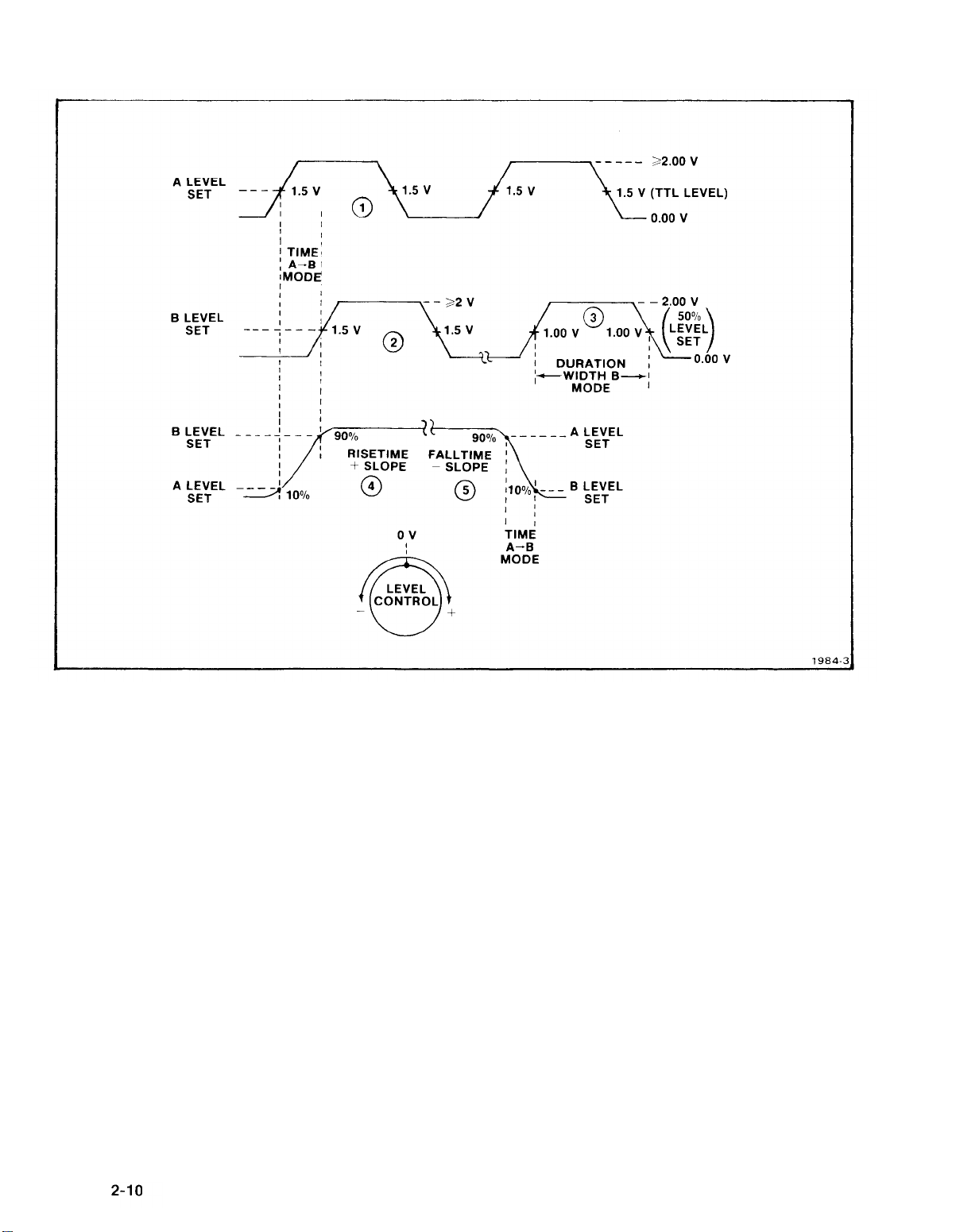

Triggering. The voltage levels necessary to establish

the triggering points on any selected slope are monitored

and set with digital voltmeter readings at the CH A/CH B

TRIG LEVEL pin jacks on the front panel or rear interface

connections. Fig. 2-5 illustrates typical TRIG LEVEL

voltage settings for various time interval measurements.

When making these measurements, each channel must be

dc coupled and coaxial cables must be properly terminated in order to maintain signal fidelity.

Low Frequencies. Period Measurements of signals

below 10 Hz, and particularly in the lowest decade from

0.1 Hz to 1.0 Hz, become rather sensitive to wave shape

and amplitude. Since it is desirable for the signals to pass

through the trigger hysteresis abruptly, square waves are

2-8

WIDTH B Mode. In order to measure pulse duration

(Fig. 2-5, waveform 3), the 50% level must be determined.

Set the FUNCTION switch to WIDTH B and the CH B

LEVEL control fully counterclockwise. Apply the input

signal to the CH B input connector. The GATE indicator

must be off.

Page 25

TM 9-6625-474-14&P-3

Fig. 2-4. Representation of Interval measurements.

Rotate the LEVEL control until the GATE indicator just

come on and record the digital voltmeter reading.

Continue rotating the LEVEL control until the GATE

indicator just goes off and record the digital voltmeter

reading. Subtract the first digital voltmeter reading from

the second and divide by 2; this is the 50% level.

Reset the CH B LEVEL control so that the digital

voltmeter indicates the 50% level. Read the pulse duration

from the DC 503A display.

Time A -

B Mode. This measurement requires input

signals to both CH A and CH B, but the peak-to-peak

signal amplitude should first be determined using the

WIDTH B mode instructions. For TIME A - B

measurements, follow these steps:

1.

Set the FUNCTION switch to WIDTH B.

Referring to WIDTH B mode instructions, determine

2.

the peak-to-peak amplitude and desired triggering

level of the signal to be applied to the Channel B

input.

If the signal to be applied to Channel A input is

3.

different than that being applied to Channel B,

repeat Step 2 for this signal.

4.

Set the Channel B LEVEL control to the desired

triggering level as calculated in Step 2.

5.

Set the FUNCTION switch to TIME A - B.

Set the Channel A LEVEL control to the desired

6.

triggering level as calculated in Step 3.

7.

With signals connected to the proper channels, read

the elapsed time interval between the triggering

level of Channel A and the subsequent triggering

level of Channel B from the DC 503A display.

Time Interval Averaging. Averaging can be used to

increase the accuracy and resolution of repetitive signal

measurements. The basic reason for averaging is the

error is truly random, then as more intervals are averaged,

the measurement will tend to approach the true value of

the time interval. For time interval averaging to work, the

time interval being measured must be repetitive and have a

repetition frequency that is nonsynchronous to the

counter clock rate. The DC 503A will measure up to 10”

averages in both Width B averaging and TIME A - B

averaging.

2-9

Page 26

TM 9-6625-474-14&P-3

Fig. 2-5. Typical CH A and CH B Level Out voltage settings for various time interval measurements.

EVENTS A DURING B MODE

In the EVENTS A DURING B mode, the events applied

to Channel A are counted. The count is gated by the signal

applied to Channel B input. The accumulated total of

events A that arrived during the time signal B was

triggered is displayed in the readout. Refer to Fig. 2-6.

The following procedure can be used to make a

measurement like that shown in Fig. 2-6.

1. Apply the signal to be counted to Channel A. With

the FUNCTION switch at FREQUENCY A, set

Channel A SLOPE switch to + SLOPE. Adjust the

LEVEL control for a stable display.

2. Apply the control signal to Channel B. With the

FUNCTION switch at PERIOD B, set Channel B

SLOPE switch to + SLOPE, Adjust the LEVEL

control for a stable display.

3. Set the FUNCTION switch to EVENTS A DURING B.

When the Channel B signal excursion occurs, Channel

B is triggered andthe gate opens, allowing the Channel A

pulses to be counted.

Averaging. Averaging can be used to Increase the

accuracy and resolution of repetitive event per interval

measurements. As more events are averaged, the

measurement tends to approach the true value of the

number of events per interval.

RATlO MODE

The DC 503A may be used to measure the ratio of two

signals, where one signal is applied to Channel A input

and the other signal is applied to Channel B input.

2-10

Page 27

TM 9-6625-474-14&P-3

Fig. 2-6. Illustration of CH A events counted from portion of CH A signal pulses during the counter gate open time (controlled by

CH B signal).

In the Ratio A/B mode, the frequency of the signal

applied to Channel A is divided by the frequency of the

signal applied to Channel B, and the resultant ratio is

displayed.

measurements, the smallest number of averages that

produces a useful number of digits should be considered.

TIME MANUAL MODE

This mode is a manual analog of the TIME A - B mode.

Triggering. The operation of Channel A and Channel B

trigger controls is the same as for frequency and period

measurements. Set the trigger controls as follows:

1.

Go to the FREQUENCY A mode and adjust the

Channel A trigger controls for a normal frequency

measurement.

Go to the PERIOD B mode and adjust the Channel B

2.

trigger controls for a normal period measurement.

Leaving the Channel A and Channel B trigger

3.

controls as they are, gotothe RATIO A/B mode. The

correct ratio should be displayed.

Resolution. The AVGS/TIMING switch, which controls

the number of averages of the Channel B signal, may now

be set to display maximum resolution. For most

In this mode, only the AVGS/TIMING switch and

START/STOP switch affect the display.

Starting and Stopping. The TIME MANUAL mode may

bethought of as a “stop-watch” type of operation. With the

FUNCTION switch inthe TIME MANUALposition (and the

internal jumper properly positioned), the display starts

counting time-base pulses when the START/STOP switch

is depressed. It will continue to count and display the

accumulated total until the START/STOP switch is released. The last count will then be held in the display until

another START command is given (in which case the

count will again advance), or other controls are actuated.

Pressing the RESET button will return the display to zero.

Changing the setting of the AVGS/TIMING switch will

change the frequency of the time-base pulses being

counted and reset the display to zero. The start/stop

function can also be performed remotely via the rear

interface connections.

2-11

Page 28

TM 9-6625-474-14&P-3

Clocking Rate. When the AVGS/TIMING switch is in

the 1 s position, one-second pulses are being counted and

the display accumulation advances one count per second,

and so on.

Whenever the accumulated count is above 99,999,999,

the OVERFLOW indicator will light to indicate register

overflow; however, the accumulation continues at the

not displayed.

TOTALIZE A MODE

This mode is a manual analog of the FREQUENCY A

mode. lnthismode, signal event sapplied tothe Channel A

input are counted and the accumulated total displayed

during the time the START/STOP button is depressed to

the START position. The main application of this mode is

to accumulate the count of relatively infrequent and

irregular events.

Operation. Apply the signal to Channel A input and set

the trigger controls the same as for a frequency measurement. Only the Channel A trigger controls, the RESET

button, and the START/STOP button affect the display in

this mode.

Starting the Count. Press the START/STOP button and

adjust the Channel A LEVEL control until a count begins to

advance. The accumulated count is displayed in whole

numbers.

will continue to be displayed. No more incoming events

will be added to the total.

Restarting and Resetting. When the START/STOP

button is again depressed, incoming events will advance

the displayed total. Resetting the count to zero can be

done at any time by pressing the RESET button.

Remote start/stop. Starting and stopping the count can

be accomplished remotely via connections to the rear

interface.

REPACKAGING FOR SHIPMENT

If the Tektronix instrument is to be shipped to a

Tektronix Service Center for service or repair, attach a tag

showing: owner (with address) and the name of an

individual at your firm that can be contacted. Include

complete instrument serial number and a description of

the service required.

If the original package is not fit for use or not available,

repackage the instrument as follows:

Surround the instrument with polyethylene sheeting, or

other suitable material, to protect the exterior finish.

Obtain a carton of corrugated cardboard of adequate

strength and having inside dimensions no Iess than six

inches more than the instrument dimensions. Cushion

the instrument by tightly packing dunnageor urethane

foam between the carton and the instrument,

sides, Seal the carton with shipping tape or

dustrial stapler.

on all

an in-

Stopping the Count. If the START/STOP button is

released and no other controls are actuated, the last total

2-12

The carton test strength for your instrument

pounds.

is 200

Page 29

SECTION 3

TM 9-6625-474-14&P-3

THEORY

OF OPERATION

BLOCK DIAGRAM DESCRIPTION

Introduction

For the following block diagram description refer to the

Block Diagram foldout page at the rear of this manual.

Channel A and Channel B Amplifiers

There are two inputs, CH A and CH B. Signals to be

counted or timed are applied to either or both channels via

front panel bnc connectors or via the rear interface. The

front panel inputs for both channels are terminated with an

paralleled with approximately 27 pF. The rear interface

inputs to both channels are terminated with a resistance of

Signal Flouting circuits.

Each channel contains an ac/dc coupling switch, a X1

or X5 attenuation network, a buffer amplifier circuit acting

as a comparator that compares the incoming signal level

against the triggering level as a reference, and

amplifier/Schmitt circuits driving the signal slope selec-

tion functions in the Signal Routing circuits. Each channel

also contains an operational amplifier serving as a X1

buffer circuit, supplying a buffered version of the trigger

level at the front panel tip jacks or rear interface connec-

tions.

NOTE

panel with the proper decimal point location and correct

annunciator illuminated.

The Measurement Cycle Timing circuit determines the

Display Time, clears the Gate Generator circuits, loads

(latches) the decade counters, and resets the counters for

the next measurement cycle in all modes of operation.

PERIOD B (Variable Clock)

In this TIMING mode, the CH B signal is passed

through the Signal Routing circuits to the Gate Generator

Input of the Decade Accumulators and the Measurement

Gate is generated by a single period of the signal from

Channel B. As before, the accumulated count for this

mode and all subsequent modes is latched, decoded from

BCD data to 7-segment information, and displayed on the

front panel with the correct annunciator illuminated and

the proper decimal point location.

PERIOD B (Averageable—100 ns Clock)

For this AVGS mode, the Time Base signal

(10 MHz = 100 ns) is not divided; it is applied through the

Signal Routing circuits directly to the Count Input of the

Decade Accumulators. The CH B signal is routed to the

The remainder of this block diagram description

discusses the signal paths through the remaining

circuit blocks and the typical events related to each

mode of operation (FUNCTION) listed on the front

panel.

FREQUENCY A (Variable Gate)

For this mode of operation the CH A signal passes

directly through the Signal Routing circuits to the Decade

Accumulators. The signal is counted by the 1st DCU, then

the 2nd DCU, and then by the 6-Decade Counter (a total of

eight decades). In the FREQUENCY A mode the Time

generate a Measurement Gate (via the Gate Generator) for

the desired measurement time. At the end of the Measure-

ment Gate interval, the accumulated count is latched in

the 8-Decade Latch/Multiplexer circuits, converted from

BCD to 7-segment information and displayed on the front

of the CH B signal. The Time Base is counted for 10”

periods before the accumulated count is latched for

display.

WIDTH B (Variable Clock)

In this TIMING mode, the 10 MHz Time Base is routed

routed directly to the Count Input of the Decade Accumulators. The CH B signal is used to generate the

Measurement Gate (via the Gate Generator). A single

pulse width at the output of the Channel B amplifier

generates the gate.

WIDTH B (Averageable—lOO ns Clock)

In WIDTH B, AVGS mode, the Time Base signal is not

divided by N; it is routei directly to the Count Input of the

3-1

Page 30

TM 9-6625-474-14&P-3

Counts are accumulated in the decade counters during

either the positive portions of the pulse widths or the

negative portions, dependent on the SLOPE polarity

selection for the Channel B signal.

signals and the Channel A signals are counted during that

time.

TOTALIZE A

In the TOTALIZE A mode the Measurement Gate is

generated by the START/STOP switch on the front panel

or via the Remote Start/Stop line at the rear interface. The

Circuit, and Gate Generator circuits are not used for this

mode. Instead of accumulating clock signals from the

signals are accumulated during the START/STOP interval.

TIME MANUAL (Variable Clock)

For this mode there are no inputs to Channel A or

Circuit whose output is routed directly to the Count Input

of the Decade Accumulators. The Measurement Gate

interval is generated either by using the START/STOP

switch on the front panel or by changing the voltage level

on the Remote Start/Stop input at the rear interface.

EVENTS A DURING B (Averageable)

This mode is exactly like the WIDTH B (Averageable)

mode, except that the output of the Time Base is disabled

and the output of Channel A is applied directly to the

Count Input of the Decade Accumulators. For this mode,

the pulse width at the output of Channel B is routed to the

produce the Measurement Gate Interval. The Channel A

events are averaged for 10” pulse widths from Channel B.

RATIO A/B (Averageable)

Decade Accumulators, 6-Decade Counter/8Decade Latch

The 1st DCU consists of ECL flip-flops, requiring

ECL/TTL conversion to drive the first decade latch The

2nd DCU operates at TTL levels and drives the second

decade latch directly. From that point, there are six more

internal counters and six more decades of latch, all

contained in one integrated circuit. This arrangement

provides a total of eight decades of count and eight

decades of latch.

The 6-Decade Counter/8-Decade Latch circuit has its

own internal oscillator to generate the Time Slot information. It also generates the Scan Clock, Overflow, and BCD

output data. Between the time slots and BCD data there is

enough information to drive the Display. The zero blanking function is also provided internally.

Measurement Cycle Timing

The display timing, reset, clear, and load (latch)

functions for the decade counters are provided by the

Measurement Cycle Timing circuit.

Decimal Point and Annunciator Encoder

The Time Base output is disabled and not used for this

mode; Channel A signals are routed directly to the Count

3-2

The decimal point location is determined by encoding

circuits using the time slot information and information

Page 31

TM 9-6625-474-14&P-3

derived from two programmable read-only memory

(PROM) devices that look at the settings for the FUNCTlON and AVGS/TIMING Switching Logic circuits. Four

of the six annunciators are also encoded with data from

the PROM devices.

Time

Base

The standard 10 MHz (100 ns) clock is generated by a

crystal controlled Colpitts oscillator The Option 01

DETAILED CIRCUIT DESCRIPTION

Introduction

Complete schematic diagrams are found in the

Diagrams and Illustrations section at the rear of this

manual. Refer to the preceding Block Diagram Descrip-

tion and to the indicated schematic diagram numbers

throughout the following circuit description.

CH A and CH B Amplifiers

counter has a 10 MHz, self contained, proportional

temperature controlled oven oscillator for increased ac-

curacy and stability.

Power Supplies

The power supplies for the instrument accepts the raw

+33 Vdc and +11.5 Vdc from the power module and

generate the

power, and the +2.7 Vtermination supply used in the ECL

circuits.

(R1226). Resistor R1627 (R1224) Iimits the high frequency

gate current, while capacitor C1720 (C1120) compensates

for the capacitance around the gate circuitry of the input

differential amplifier.

The input differential amplifier, Q1630 (Q1230), has

very high input impedance and transconductance, High

common mode rejection for the differential amplifier is

provided by a constant current source, Q1620 (Q1220)

and associated components.

+12 V regulated power, the 5 V regulated

NOTE

Since both amplifier circuits are identical, this

description discusses the theory of operation for

Channel A Amplifier with the associated circuit

component for Channel B Amplifier listed in

parenthesis.

The input signal applied to the input bnc connectors of

each channel, J51O (J61O), passes through three switches

to the gate connection of a DMOS FET differential

amplifier, Q1630 (Q1230). The EXT/INT switch, S1732

(S1031), activates relay K181O (K1800) to select either the

front panel input or the rear interface connection, P1900-

16A (P1900-17B). The rear interface input connection is

terminated internally with a 51

After input selection the signal coupling method is chosen

by the ac or dc coupling switch for each channel, S1731

(S1030). The dc component of the signal is removed by

capacitor C1830 (C1030), resulting in a signal that varies

around its average level. Attenuation of the input signal,

X1 or X5, is determined by the setting of S1730 (S1021).

Four diodes, CR1620, CR1720, CR1621, and CR1721

(CR1220, CR1120, CR1221, and CR1121) are provided to

limit the input voltage to Q1630 (Q1230). Clamping occurs

at approximately +6 V or

circuits are protected against excessive current by R1629

f2

resistor, R1731 (R1132).

–13 V. The diode clamping

The other gate of the DMOS FET pair is connected to

the Trigger Level control R500 (R600) and the trigger level

output circuit, U1620 (U1220) and associated components. The Trigger Level control sets the dc reference

level to which the input voltage is compared. The counter

measurements are made with respect to the dc reference

*3.5

level set by R500 (R600). The trigger level range is

The buffer amplifier circuit, U1620 (U1220) and

associated components, has a high input impedance and

approximately unity gain, minim izingthe loading effect on

the differential amplifier. The CH A (CH B) Level Out

value is very close to the dc level set by the Trigger Level

control. Potentiometer R1525 (R1420) is adjusted to

compensate for the offset voltages of the differential

amplifier and buffer circuits.

The output of the DMOS FET pair is applied differentially to the input of a three stage line receiver circuit,

U1530C, U1530B, and U1530A (U1330A, U1330B, and

U1330C). The first stage of the line receiver, U1530C

(U1330A), operates as a transresistance amplifier to lower

the load impedance on the differential amplifier.

The second stage of the line receiver, U1530B

(U1330B), operates as a voltage amplifier with a gain of

V.

3-3

Page 32

TM 9-6625-474-14&P-3

approximately three. The differential output from this

voltage amplifier drives the Schmitt trigger circuit,

U1530A (U1330C). The Schmitt trigger circuit shapes the

input signal and drives the SLOPE selection gates on

schematic 3.

on pin 11. The second rising edge causes U1321B to again

change state. A Iow is clocked through to pin 15 and a high

to pin 14; returning U1321B to its original state after reset.

The circuit is now ready to accept another falling edge

(CH A signal) on pin 11 of U1420C.

Introduction to Signal Routing The end result of two changes of state for U1321 B is

that a pulse width has been generated on pin 15 that goes

high on the rising edge of the CH A signal and goes low on

NOTE

Before reading this part of the detailed circuit

description, refer to the Block Diagram Description

for basic signal path information.

Signal slope selection for each channel of the DC 503A

is provided by exclusive-OR gates, U1421A for Channel A

and U1421 B for Channel B. A high voltage level on pin 5 of

U1421A or pin 7 0f U1421B inverts the input signal on pin 5

or pin 9 of U1421. Both gates have complemented outputs,

pins 2 and 11.

The outputs from the slope selection gates go to the

SHAPED OUT tip jacks, J520 and J540, after buffering by

Q1420 and Q1530, respectively. The Channel A signal also

goes to pin 12 of U1420D and pin 11 of U1420C, while the

Channel B signal goes to pin 5 of U1420A and pin 6 of

B modes (variable clock or

U1420B. In both TIME

averaging), U1420D and U1420A are disabled with high

voltage levels on pins 13 and 4, respectively. With U1420D

and U1420A disabled, the input signals are routed to the

TIME A -

U1420D and U1420A, are also disabled for the TIME

MANUAL mode. The Channel B NOR gate, U1420A, is

disabled for the TOTALIZE A and FREQUENCY A modes;

U1420D is not. Refer to the FUNCTION switch (S1810)

logic pattern on the schematic for specific Iogic levels that

enable or disable the remaining signal routing gates.

B Generator, U1321B. Both NOR gates,

-

the rising edge of the CH B signal.

Signal Routing and Gate Generator

The purpose of the Signal Routing circuit istoroutethe

B, or Time Base (110 ns clock)

CH A, CH B, Time

signals to either the Gate Generator (pin 6 of U141OA), the

+

N Circuit (schematic 6), or directly to the Count Input of

the Decade Accumulators (schematic 4). In some modes

of operation, the signals are routed to the

then back to the Decade Accumulators or Gate Generator

(via the emitter circuits of Q1330 or Q1320).

Refer to Fig. 3-1 for a typical DC 503A timing diagram

and the sources of the count and measurement gate.

-

+

N Circuit and

FREQUENCY A. The object of this mode istocount the

CH A signal and use the Time Base to generate the

Measurement Gate, For this mode, the CH A signal is

routed through U1420D directly to the Decade Accumulators (U1221-9, schematic 4), The Time Base signal

(100 ns clock) is routed through U1320C (pin 10 Iow) and

+

out to the input of the

6). After the Time Base signal has been divided down (to

1 MHz, to 100 kHz, etc) it is routed back to the emitter of

Q1320. This transistor is turned on in the saturated mode

and passes the divided down signal, clocking the Gate

Generator on pin 6 of U141OA and pin 11 of U141OB.

Before a valid Measurement Gate can be generated the

Gate Generator must have been reset (cleared) via

U1320D.

N Circuit (U131OA-6, schematic

Time A -B Generator

Whenever a Reset signal appears on pin 13 of U1321 B,

it sets pin 15 low and pin 14 high. The low on pin 15 enables

U1420C on pin 10 and the high on pin 14 disables U1420B

-

on pin 7. After reset, the Time A

positive transition (rising edge) on pin 11 of U1321B.

The first falling edge (after reset) on pin 11 of U1420C

causes U1321 B to change state; pin 15 goes high, pins 14

and 10 go low. This change of state disables U1420C,

enables U1420B, and sets pin 10 (D input) of U1321B low.

The Time A

until a falling edge (CH B signal) occurs on pin 6 of

U1420B. The failing edge is inverted and clocks U1321B

3-4

-

B Generator remains in this high state

B Generator waits fora

+

The first positive transition of the

causes pin 15 of U141OB to go high. The second positive

:

transition of the

remain low for all other clock transitions until after

U1410A and U1410B are reset by the clear pulse on pin 12

of U1320D.

The output on pin 14 of U141OB is the complement of

the signal on pin 15. Pin 14 goes low and then high with the

first and second clock transitions, remaining high until

after reset (clear). The output on pin 14 is routed through

and inverted by U1330B (pin 7 low), This positive gate is

inverted again by U1220C before acting as the Measure-

ment Gate for the Decade Accumulators.

N clock causes pin 15 to go low and

N clock signal

Page 33

TM 9-6625-474-14&P-3

Fig 3-1.

3-5

Page 34

TM 9-6625-474-14&P-3

The Gate Generator circuit also produces the Latch

Trigger and a complementary Measurement Gate going to

the Measurement Cycle Timing circuit on schematic 5.

The operation of the Latch Trigger circuit is the same for

all modes of operation that requires a Measurement Gate

and will be described only once.

The generation of the Latch Trigger signal starts

whenever pin 3 of U1410A goes high at reset (clear) for the

Gate Generator. At reset, pin 13 of U1330D goes high and

pin 15 goes low. This low is transmitted without inversion

through buffer U1122D. Therefore, the Latch Trigger

signal on pin 14 of U1122D goes low whenever the Gate

Generator is cleared.

As soon as a positive clock edge occurs on pin 6 of

U1410A, pin 3 goes low and pin 15 of U1330D goes

momentarily high. However, pin 15 of U1410B is connected to pin 12 of U1330D and as soon as that signal goes

high, pin 15 of U1330D goes low again. This action causes

a momentary positive pulse immediately after first clocking the Gate Generator. This small pulse does not affect

the operation of the instrument.

At the end of the Measurement Gate, pin 15 of U1410B

goes low again. When this happens there will be a low on

pin 12 and pin 13 of U1330D, causing a low to high

transition on its output. It is the second low to high

transition at the end of the Measurement Gate interval that

produces the Latch Trigger and affects the Measurement

Cycle Timing circuit.

PERIOD B (Variable Clock). For this mode, a Measure-

ment Gate is generated from the Channel B input signal

and the Time Base is counted (divided down or not). Since

this is a single period measurement, the Time Base signal

+

(10 MHz) is again routed to the

N Circuit via U1320C.

During the single period the instrument counts 10 MHz, or

+

1 MHz, or 100 kHz, etc. The

N output again appears at

the emitters of Q1330and Q1320. Forthis mode itis Q1330

that is turned on in a saturated mode, allowing the divided

down Time Base signal to pass on to the Decade

Accumulators.

The Measurement Gate is generated from the CH B

signal with U1420A enabled on pin 4 (low). The single

period signal from CH B passes on through U1421C, then

on through Q1321 because its base is low.

The gate signal generated on pin 14 of U1410B is again

routed through and inverted by both U1330B and U1220C.

PERIOD B (Average). For this mode the Time Base

signal is passed through U1330A directly to the Decade

Accumulators. The Channel B signal is routed to the

+

N

Circuit via U1420A, U1421C, and Q1331 (base is low). The

divided down Channel B signal returns via Q1320 to clock

the Gate Generator.

The first edge to clock the Gate Generator is the first

edge of signal period. That edge is divided down by the

+-

N Circuit to generate the second edge through Q1320

and terminate the Measurement Gate. The instrument is

averaging over 10” number of Channel B signal periods to

generate the Measurement Gate.

WIDTH B (Variable Clock). This mode of operation is

exactly like PERIOD B (Variable Clock), except that the

instrument counts the Time Base signal (divided by N, or

not) during the positive portion or negative portion of the

input signal period to Channel B. Whether the positive

pulse width or negative pulse width is measured depends

on the setting of the SLOPE switch, S1020. The Time Base

signal passes through U1320C, out to the

+ N Circuit,

back in through Q1330 and on to the Decade Ac-

cumulators.

The exclusive-OR gate, U1421C, along with NOR gate,

U1430B, is used to generate a single width measurement.

The Channel B signal appears on pin 14 of U1421C. Pin 15

is low at this time, causing U1421C to operate as a noninverting buffer. When pin 14 goes from low to high, the

output, pin 13, also goes from low to high. The positive

transition is passed through Q1321 (base is low) and

clocks the Gate Generator on the first rising edge of the

Channel B input, starting the Measurement Gate (pin 14 of

U1410B goes low).

Pin 7 of U1430B is at a logic low for this mode. When the

Measurement Gate starts, pin 6 goes low and sets a high

logic level on pin 15 of U1421C. During the Measurement

Gate interval, U1421 C operates as an inverter. The next

falling edge from Channel B (end of the positive pulse) will

cause another positive edge to clock the Gate Generator

and terminate the Measurement Gate. The Measurement

Gate is again routed through U1330B and U1220C,

enabling the Decade Accumulators to count the Time

Base during the positive pulse width.

On the first rising edge of the single period, the start of

the Measurement Gate

IS generated exactly the same as

previously discussed under the FREQUENCY A mode of

operation. On the next rising edge of thesingle period, the

Measurement Gate is stopped with pin 14 of U1410B high

and pin 15 low.

3-6

WIDTH B (Average). This mode of operation is similar

to Period B (Average), except that NOR gates U1430C and

U1430A are involved in the process. With U1430C enabled

on pin 10, the Channel B pulse width passes through

U1430C to pin 4 of U1430A. The Channel B signal also

Page 35

TM 9-6625-474-14&P-3

passes through U1421C, through Q1331, out to the + N internal jumper P1020 (J1020) on schematic 9. Logic gate

Circuit, and back through Q1320 to start the Gate

Generator on the first edge. Pin 14 of U1410B goes low and

sets pin 5 of U1430A low during the Measurement Gate

interval (U1330B is disabled).

U1420D is enabled to allow counting the Channel A

signals, while U1330C is enabled to allow the Measurement Gate, generated by the Start/Stop switch, S1311, ora

Remote Start signal on P1900-26B, to pass through

U1220C to the Decade Accumulators.

Pin 5 of U1430A stays low and keeps the logic gate

enabled for the entire length of time equal to the number of

pulse widths being averaged. The pulse width signals on

pin 4 are gated through and inverted, appearing on pin 10

of U1220C. The Measurement Gate signal out of U1220C

is alternating high and low for the total number of pulse

widths being averaged. The Time Base count is being

accumulated in the Decade Accumulators only during the

times that the Measurement Gate is low on pin 14 of

U1220C. At the end of the averaging cycle, pin 5 of U1430A

goes high, disabling that gate, and preventing any more

counting until the next reset (clear) pulse occurs.

TIME A

-

B (Average). This mode is the same signal

routing as Width B (Average), except that the width is

generated by the Time A

B Generator circuit. The rising

-

edge of the Channel A signal starts the” pulse width, and

then the rising edge of the Channel B signal stops it.

EVENTS A DURING B (Average). Since it is required to

count the number of events coming through Channel A

during N intervals of the Channel B pulse width, U1330A is

disabled on pin 5 to lock out the Time Base, and U1420D is

enabled on pin 13 to allow the Channel A signals to pass

through to the Decade Accumulators.

The Time Base is not used for this mode; logic gates

U1330A and U1320C are disabled. The enabling of

U1430C, Q1331, and Q1320 is redundant; the Measure-

ment Gate is not generated via U1410B.

TIME MANUAL. For this mode, there are no Channel A

or Channel B input signals. The Time Base signals are

-+

routed through U1320C to the

N Circuit and back again

via Q1330 to the Count Input of the Decade Accumulators.

The Measurement Gate is generated and routed through

U1330C exactly like the Totalize A mode.

+

N Circuit

The first decade counter in the

:

N Circuit consists of

U1310A, U1310B, U1411A, U1411B, U1300B, and

associated ECL components. As the operator selects

different positions of the AVGS/TIMING switch, S1010 on

schematic 9, more and more of the remaining dividers

become involved in the counting down process,

generating a delay between the first and second clock

pulses going to the Gate Generator circuit on schematic 3.

The first decade counter is followed by U1400, a single

decade counter, and the remaining dual decade counters,

U1401, U1501, and U1610.

For this mode, the gate interval on pin 5 of U1430A lasts

for pulse widths and the Channel B signal on pin 4 is

again Iogically anded through U1430A to pin 10 of U1220C

(U1330B is disabled). The event count from Channel A is

The clock input to the

U1310A and pin 5 of U1300A. The output from the

Circuit occurs at the wired-OR junction on pins 2 and 7 of

accumulated in the Decade Accumulators exactly like the U1300.

Time Base was for the Width B (Average) mode.

After reset, the first clock pulse edge at pin 6 of U1310A

RATIO A/B (Average). For this mode the instrument is

essentially performing a period average with the Channel

B signal generating the Measurement Gate (divided down

or not, via the

-+

N Circuit), but the Channel A signal is

and pin 5 of U1300A passes through to pin 2 of U1300A

(+

N Output). The next clock edge will also pass through

U1300A if N = 1, or it is going to be held off for the

selected

being counted, rather than the Time Base.

The

The Time Base is disabled via both U1330A (pin 5 is

high) and U1320C (pin 10 is high), and the instrument

counts the Channel A signals passing through U1420D

(Pin 13 is low). The Measurement Gate is passed through

U1330B (pin 7 is low) and U1220C to allow the Channel A

are identified by the logic state pattern for S1010 on

schematic 6; the acutal switch circuit is located on

schematic 9. These settings enable or disable logic gates

U1300C, U1510B, U1510A, U1510C, U1510D, U1511A,

U1511B, or U1511D.

count to accumulate in the Decade Accumulators.

At reset (clear), all of the decade counters are set to a

TOTALIZE A. Whether the instrument is in this mode or

the Time Manual mode is dependent on the position of an

count of nine, causing all of the inputs to U1500 to be set

high and enabling U1300A, Resistors R1302 and R1303

:

N Circuit occurs on pin 6 of

+ N countdown.

+ N setting (1 through

108

or 100 nsthrough 10 s)

+ N

3-7

Page 36

TM 9-6625-474-14&P-3

operate as TTL to ECL level shifters. As the first clock

pulse on pin 5 of U1300A makes a transition from low to

high, the output (pin 2) goes from low to high, Assuming

that the first decade counter has also been reset, pins 9, 10,

and 11 of U1300B are all low with its output (pin 7) also

low. This low on pin 7 allows the first clock pulse to pass

through U1330A. If the instrument is operating in the

mode, pin 5 of U1320A is held low. This ensures that the

counters do not advance or change their “nines” state,

allowing all of the succeeding clock edges to pass through

U1300A.

~-

For the

10 mode, pin 5 of U1320A is no longer held

low and the first decade counter is no longer held reset.

The first clock edge on pin 6 of U1310A passes on through

U1300A. The first clock transition has also caused U1310A

to change state, setting pin 9 of U1300B high. The output

of U1300B and the wired-OR junction goes high and

remains high for the next ten clock edges. After ten

counts, the first decade counter is back to its original state,

setting all three inputs to U1300B low. This causes the

wired-OR junction to go low, allowing the eleventh clock

edge to pass through U1300A. Thus, the first and eleventh

~

clock edges causes the

N Output to go high.

The reason that the decade count does not continue

past the first decade is that pin 5 of U1510B is held low and

pin 6 of U1400

IS held high. For N =

102

(100) pin 4 of

U1401 is held reset (set to nine), but the first decade

counter and U1400 are involved in the countdown

process. The first clock edge through U1300A causes the

:

N Output to go high, and the 101st edge does the same.

The second through one-hundredth clock edges are

suppressed via the wired-OR junction and because the

output of U1400 is changing, this keeps U1300A disabled

until the 101st clock edge occurs.

In any of the averaging modes (PERIOD B, WIDTH B,

A-

TIME

B, EVENTS A DUR B, or RATlO A/B) and

N = 10, it requires eleven periods of the selected mode to

count ten periods. The first clock edge on pin 6 of U1310A

advances the first decade counter, but it

off the first clock edge out of the

IS desired to hold

+

N Circuit. Instead of

setting pins 9, 10, and 11 of U1300B all low at reset (clear)

for the averaging modes, pins 10 and 11 areset lowand pin

9 high; the first flip-flop, U1310A is set rather than reset.

Anytime that the instrument is in an averaging mode and

pin 5 of U1320A is not held low (N = 1), U1310A is set by

the clear pulse via U1300C.

+

In the TOTALIZE A mode the

N Circuit and the

internal Time Base are not used. In the TIME MANUAL

mode, the Time Base signal is divided by N. In both modes

the gate

IS generated by the START/STOP switch input to

CR1222.

For all modes except TOTALIZE A and TIME MANUAL,

the input to pin 3 of U1600B is at a high level. This causes

CR1220 to be forward biased, holding pin 9 of U1310A low

and enabling that flip-flop to change state when clocked

on pin 6, When the instrument is operating in the

TOTALIZE A or TIME MANUAL mode, pin 3 of U1600B is

held low, reverse biasing CR1220 and allowing the clock

input to U1310A to be enabled and disabled by the

START/STOP switch.

Also, for the TIME MANUAL and TOTALIZE A modes