Page 1

特長

■

最 高1.6Gbpsのパ タ ー ン 生 成 / エ ラ ー 検 出 機 能 に よ り、

デジタル通信シグナリング・システムの迅速で正確な特性評

価が可能

■

PRBSパターンまたは8Mビットのユーザ定義パターンによ

り、汎用性の高いデバッグまたは任意のデジタル・シグナリン

グの組み合わせが検証可能

■

内蔵のクロック・ソースによる非常に正確なタイミング

■

設定可能な振幅、オフセット、ロジック・スレッショルド、ター

ミネーションによるシグナリング変動により、レシーバ設計

のストレス・テストが可能

■

差動およびシングル エンド のI/Oにより、 さまざまな通信

バス規格での接続が可能

ビット・エラー・レート・テスタ

BitAlyzer® BAシリーズ

データ・シート

■

BitAlyzer®のError Analysis™によりBER性能 の限界が

すばやく理解でき、デターミニスティック対ランダム・エラー

の評価、詳細なパターン依存エラー解析、エラー・バースト

解析、エラーフリー間隔解析が可能

■

自動測定によるアイ・ダイアグラム表示と高速アイ・マスク・

テストにより、迅速なDUTのシグナル・インテグリティ解

析が可能

■

ANSIのジッタ測定(RJ、DJ、TJ)による、BER 10

のトータル・ジッタにおけるランダム・ジッタとデターミニ

スティック・ジッタの影響の測定が可能

■

Qファクタの測定により、BERに関する垂直アイ開口をすば

やく解析可能

■

自動マスク生成とBER輪郭により、アイ・ダイアグラムの

開口をBERの関数として測定、表示可能

■

FEC(ForwardErrorCorrection)エミュレーションによる、

通信システム設計の内蔵FEC性能検証

■

エラー・マッピング機能により、シグナリング・エラーの

原因と場所の特定のためのデバッグ・サポート

アプリケーション

■

半導体の特性評価

■

アイ・マスクの生成、BER、ジッタ・テスト

■

衛星通信システムの機能テスト

■

無線通信システムの機能テスト

■

光ファイバのシステム/コンポーネント・テスト

■

ForwardErrorCorrection(前方向誤り訂正)の検証

−12

www.tektronix.com/ja

Page 2

2

www.tektronix.com/ja

データ・シート

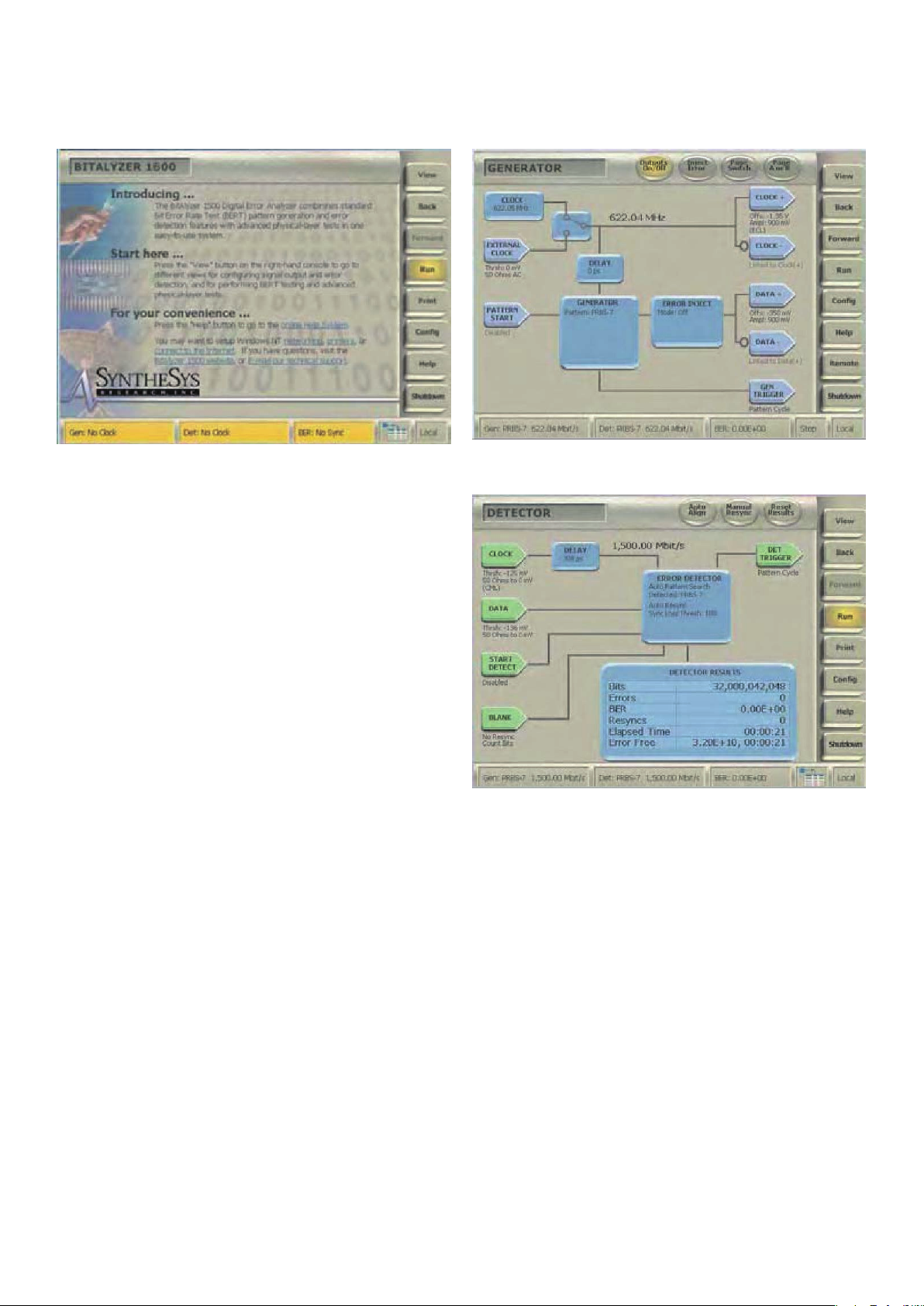

BA1500型、BA1600型のスタート画面。画面右のタッチスクリーン・ボタン

により、表示、動作モードなど、アナライザの設定を行う

より詳細な解析を可能にする妥協のない高性能で、

設計業務を効率アップ

BitAlyzer®シリーズ・ビット・エラー・レート・テスタは、設

計エンジニアが直面する、最先端の電子回路/通信システム設

計の検証、特性評価、デバッグ、テストに関するシグナル・イン

テグリティとBER問題を解決するための優れたソリュー

ションです。

BA1500型、BA1600型は、日々の業務効率を高めるための

信号生成と解析、操作性、デバッグ・ツールなど、優れた性能、

機能を備えています。物理レイヤ・テスト・ツールの統合ソフ

トウェアが利用でき、直感的なユーザ・インタフェースで大き

なデータを簡単に得ることができます。

シンプルなユーザ・インタフェース

BA1500型、BA1600型には、従来のビット・エラー・レー

ト・テスタにはない、最新のユーザ・インタフェースが備わっ

ています。ディスプレイには、操作しやすい操作ボタン、わか

りやすいステータス・リードアウトが表示されます。スタート

画面では、何から操作すればよいか理解できます。インターネッ

ト、テクニカル・サポートへのEメール、ネットワーク/プリン

タの設定などのリンクもあります。アナライザ、解析機能の操

作手順が紹介されているGettingStartedガイドにもアクセス

できます。短時間のうちに、機器の設定、エラー測定、ビット・

エラーの統計測定を実行することができます。

パターン・ジェネレータ

BA1500型、BA1600型にはデータ・ジェネレータ機能が内

蔵されており、5種類の擬似ランダム・データ・ストリームか

ら1つ、または最長8Mビットのユーザ定義のシーケンスを出

力することができます。データの出力は、標準の内蔵クロック・

ソースまたは外部のクロック入力によって制御されます。さま

ざまな 遅 延がサポー ト されており、 ビ ット周期内 に おいて

0.1%の分解 能 で出力ス キューを調 整するこ と ができま す。

ユーザ・データ・パターンは、インポートしたり、内蔵のエディ

タで生成することができます。

直感的なインタフェースにより、パターン生成と内部クロック・ソースが容易に

操作可能

差動とシングルエンドの入力がサポートされ、スレッショルド・レベル、終端電

圧の設定が可能。ロジック・ファミリの名称設定も可能

工場出荷時のプリセットには、一般的に使用されるロジック・

ファミリが含まれています。さらに、クロックとデータは差動、

シングルエンド出力の両方で、振幅とオフセット・レベルが独

立に調整できます。

パターン・ディテクタ

入力データ・ストリームは、期待されるシーケンスに対してビッ

トごとに比較され、エラーが検出されます。入力シーケンスで

検出されたエラーは、内部プロセッサによってリアルタイムに

解析したり、内蔵ハード・ディスクに保存して後から解析する

こともできます。レシーバは、5種類の正または反転の擬似ラン

ダム・シーケンス、または8Mビットのユーザ・パターンと自

動的に同期します。

差動およびシングルエンドの入力がサポートされており、代表

的なロジック・ファミリを含むファクトリ・プリセットのスレッ

ショルド、ターミネーションに調整されます。Auto Scaleに

より、2秒以内でアイの中心を検出することができます。

Page 3

3

www.tektronix.com/ja

ビット・エラー・レート・テスタ - BitAlyzer® BAシリーズ

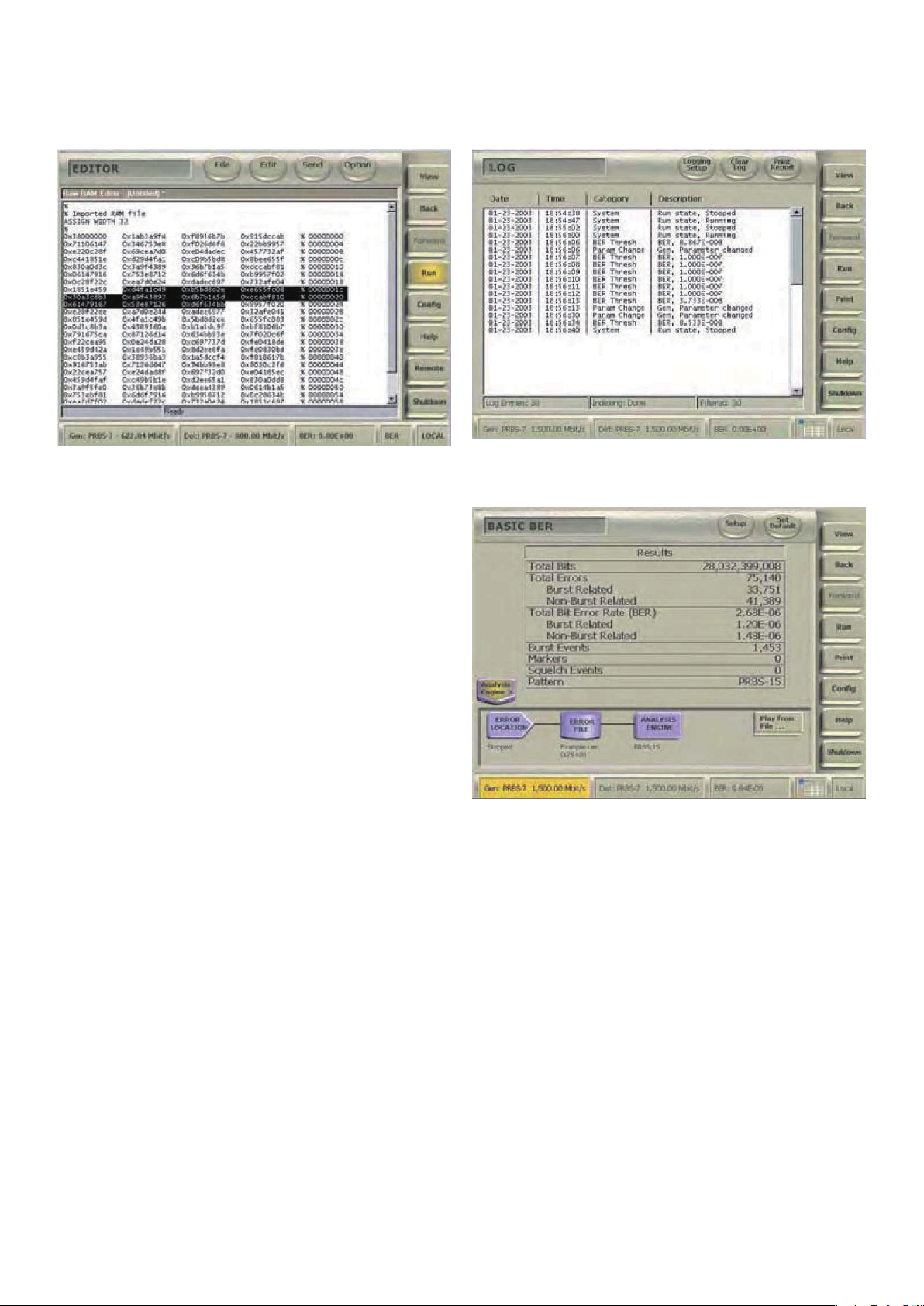

このユーザ・データ・パターンの例は、入力データ・ストリームから取込まれ、

出力データ・シーケンスとしてパターン・ジェネレータに送られる前にマニュア

ルで変更されている

ユーザ・パターン・エディタ

ジェネレータやディテクタ・パターン・メモリのユーザ・デー

タ・パターンは、内蔵のパターン・エディタで生成、変更する

ことができます。データは、エラー・ディテクタ入力からパ

ターン・エディタに取込み、リファレンス・パターンを生成す

ることができます。パターン・エディタは、PRBSキーワード、

繰返しループ、変数割り当てをサポートします。16進、10進、

バイナリに対応します。

パターン・ファイルはWindows NTファイル・システムに保

存され、ネットワーク・インタフェースからインポートしたり、

アクセスしたりすることができます。パターンは、BA1500

型とBA1600型で共有することができます。

エラー・ログ

BERモニタリングの一般的なアプリケーションでは、エラー測

定や、拡張テストにおける目立ったイベントのロギングが必要

になります。BA1500型、BA1600型には内蔵のロギング機

能があり、ユーザによって設定された間隔においてプログラム

可能なスレッショルドよりも悪いBERの値をログするように

設定することができます。BERの値のモニタリングの他に、同

期損失または設定のロギングも行えます。ログ・ファイルは印

刷または保存でき、システム性能を検証していつエラーが発生

したかを簡単に確認することができます。

わかりやすいBERログのユーザ・インタフェース。BERスレッショルドを設定し、

何をログするのかを定義する。ログ間隔は、DetectorビューでBERを測定する

場合の間隔と同じ

個々のエラー・レートとバースト・エラーに対するビット・カウントは、Basic

BERビューに表示される。シンプルに分離することでデバッグに集中できる

基本的なBER統計

エラー位置解析は当社特許の手法であり、PCの処理により、

テ ス ト で 検 出 さ れ た エ ラ ー の 位 置 を 正 確 に 特 定 し ま す。

BitAlyzerは、正確なビットの位置から、シンプルなエラー・レー

トによる方法よりも優れたエラーの依存性と関連性を明らかに

します。

個別のビットとバーストのエラー統計表もモニタし、バースト・

イベントの数、エラー・カウント、エラー・レートを確認する

ことができます。すべてのエラー位置解析データは、リアルタ

イムに解析したり、内蔵のハード・ディスクに保存して後から

解析したりすることもできます。解析エンジンは、ファイル名、

エラー記録モードなどを設定することもできます。

Page 4

4

www.tektronix.com/ja

データ・シート

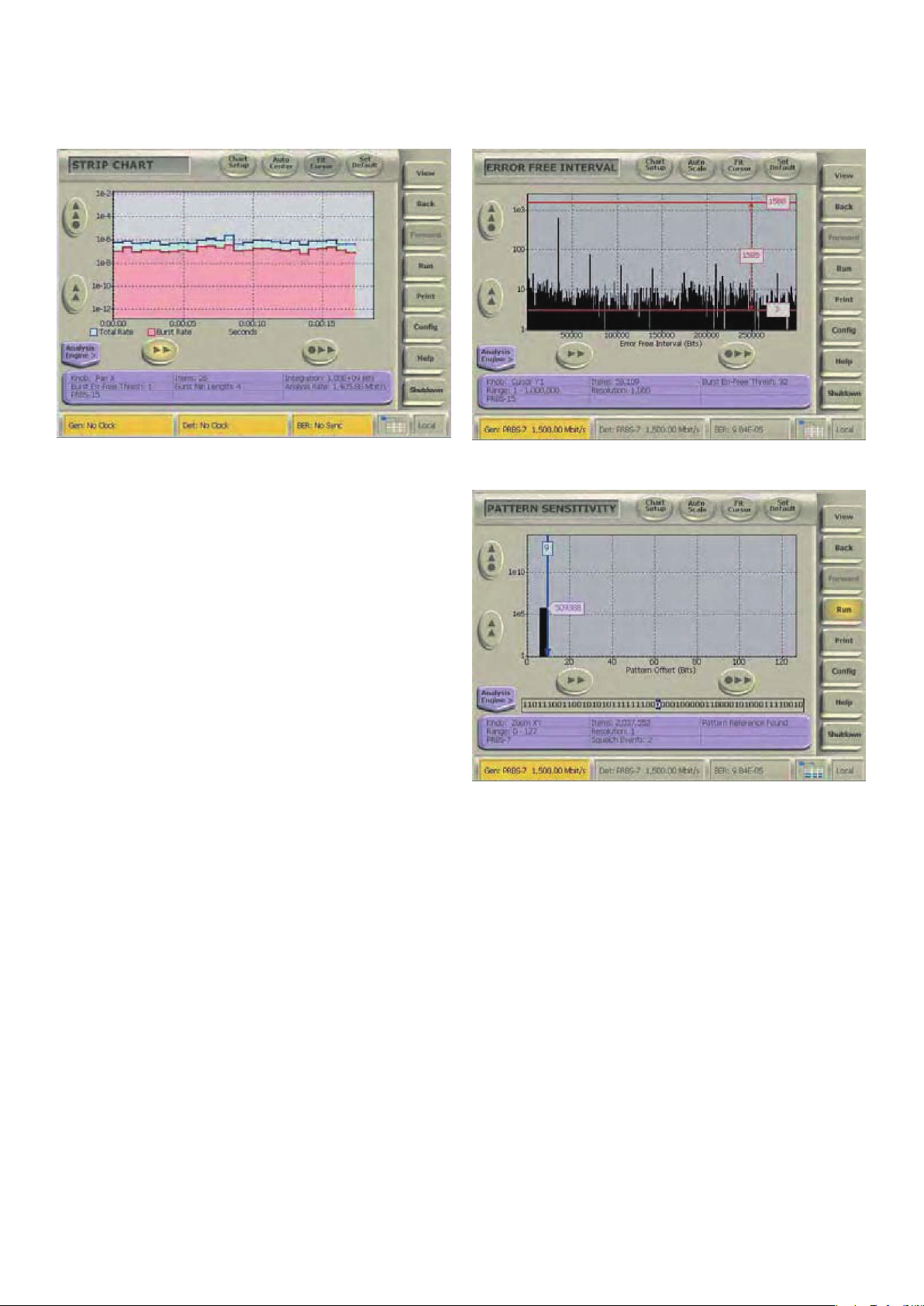

ストリップ・チャートでわかりやすく表示されるビット・エラー・レートのトレン

ド。サーマル・サイクルまたは熱変化条件による通信への影響がトラッキングで

きる

BERのストリップ・チャート

エラー・レートの考察では、トレンドが非常に重要になります。

時間に対する測定変化のモニタには、ストリップ・チャートが

広く使われています。BitAlyzerには内蔵のストリップ・チャー

ト機能があり、時間に対するビット、バースト、トータル・エ

ラー・レートの変化を観測することができます。時間軸の速度

は、各ビット・エラー・レート測定に含まれるビット数によっ

て設定することができます。また、表示のズーム・レベルも設

定できます。

低い頻度で発生する繰返しエラーは、この表示で判断すること

ができます。例えば、6秒おきに発生するバースト・エラーな

どは簡単に特定できます。ストリップ・チャートは、ライブ・

エラー・データまたは保存されたエラー・データ・セットで機

能します。

エラーフリー間隔

エラーフリー間隔解析では、被測定システムで発生するさまざ

まなエラーフリー間隔の頻度を観測することができます。他よ

りも多くエラーフリー間隔が発生する場合、ランダムなエラー

というよりはシステム的なエラーと見ることができます。同時

に、繰返しのエラーフリー間隔は干渉の頻度を示し、何が意図

しないエラーと相関関係にあるのかを知ることができます。

エラーフリー間隔の情報は短時間に蓄積できるため、膨大な

データを取込まなかったり、エラー障害の分離のために長いテ

ストを行ったりしません。BA1500型、BA1600型のエラー

フリー間隔アナライザは、ヒストグラム・ビューの開始ポイン

ト、終了ポイントを設定することで、短い、または長いエラー

フリー間隔の測定を設定することができます。

繰返し性のあるエラーフリー間隔は、システム・エラーであることがわかる。こ

のようなスパイクの検出により、干渉周波数がすばやくわかる

この例では、127ビットのPRBS7パターンが使用され、検出されたエラーがデー

タ・パターンに大きく関係していることがわかる。ヒストグラムの下に表示され

るNRZデータは、カーソル位置でのデータ・ビットを示している

パターン感度

パターン感度解析は、データ依存性のエラー特定に有効な方法

です。このヒストグラムは、使用されるテスト・パターンのビッ

ト・ポジションごとのエラー数を示しています。テスト・パ

ターンは、内蔵のPRBSパターンまたはユーザ定義のパターン

が使用できます。カーソルは、パターン依存性のエラーの位置

およびその周辺のデータ値を知るために使用します。

長いPRBSパターンによる拡張テストは、わずかなエラーで失

敗することがあります。この解析方法を使用すると、すべての

エラーがテスト・パターンの同じビット・シーケンスが原因で

発生するものか、またはパターン内でランダムに分布するもの

かが簡単にわかります。

Page 5

5

www.tektronix.com/ja

ビット・エラー・レート・テスタ - BitAlyzer® BAシリーズ

ビタビ保護通信チャンネルの代表的なバースト長ヒストグラム。カーソルによる

バースト数の測定例

バースト長ヒストグラム

ビット・エラー、バースト・エラーは、さまざまな物理的な現

象が原因で発生します。BitAlyzerは、最大32,000ビット長

のバースト・エラー長を測定し、ヒストグラムで表示できるた

め、エラー・タイプの違いをすばやく区別することができます。

ユーザは、バースト・エラーに合致する要件を定義します。バー

スト長ヒストグラムは、正常の動作の特長として役立つととも

に、エラー訂正符号化システムの設定に役立ちます。

デジタル処理エラーは、繰返しエラー長の原因となりますが、

干渉によってエラー長が変化することがあります。この解析は

エラーフリー間隔解析と共に使用されることがあり、エラーの

サイズと頻度の両方を理解するのに役立ちます。

エラーの相関

システム・アーキテクチャまたは物理現象とビット・エラー統

計間の相関関係を理解することは、多くのエラーの原因特定で

重要になります。エラー位置解析の手法は、この相関性を検出

するために開発されました。相関解析では、ブロック・サイズ

を固定ビット数(データ・バス幅またはパケット・サイズ)、

または外部マーカ入力(ディスク・ドライブのセクタ・マーカ、

またはエンジンのローテーション・マーカなど)で定義した間

隔で設定し、このブロックとエラーにどのような相関関係があ

るかを見ます。

ブロック・サイズ内のすべてのビット位置がエラーの数と等し

い場合、相関性はありません。しかし、ブロック内に特定のオ

フセットが異常に大きい場合は、相関性があります。

MUX/DEMUX回路のテストでは、マルチプレクサの幅との相関性により、エラー

がシリアル・ドメインで発生するのか、またはパラレル・ドメインで発生するの

かがわかる

システム動作では、ブロック・エラー統計の方が正確なビット・エラー測定より

も重要になることが多い。ブロック・サイズは調整でき、ヒストグラムによりさ

まざまな数のエラーで何回ブロックが発生しているかがかわる

ブロック・エラー解析

多くのシステムの性能は、ビット・エラー・レートよりもむし

ろブロック・エラー・レートに関連しています。BA1500型、

BA1600型では、ブロック・サイズを設定し、数多くのエラー

を含むブロックが発生する数のヒストグラムを表示します。

カーソルを使用することで、設定した数以上のエラーを含んだ

ブロックの発生数がわかります。最大ブロック・サイズは40

億ビットであり、通常のブロック・サイズの解析には十分です。

Page 6

6

www.tektronix.com/ja

データ・シート

オプションのアイ・ダイアグラムは、ビット・エラー・レート・テスト実行前の

データ入力波形の品質チェックで使用する

アイ・ダイアグラム

アイ・ダイアグラム表示は、物理レイヤ・オプションに含まれ

ている機能です。この表示はBER機能の電気サンプリングと同

じであり、機器間でケーブルを交換することなくアイ・ダイア

グラムを表示することができます。

立上り/立下り時間、ジッタ、振幅、ノイズ・レベル、アイ開

口比率が自動測定できます。アイ・ダイアグラム周辺がパン/

ズームできるため、ビット・エラー・レート・テストで使用す

る信号の様子を詳細に確認することができます。アイ・ダイア

グラムでは、ユーザの信号とBERデシジョン回路を組み合わせ

た影響が示されます。

マスク・テスト

アイ・マスク・テストは、物理レイヤ・オプションに含まれて

いる機能です。アイ・マスク・テストを高速で実行することは、

テストの作業効率という点で重要になります。一般的なオシロ

スコープでは、固定のサンプリング・レートで実行するため、

長い時間が必要になります。BERベースの方法では、マスク周

囲の内側、上部、下部がテストでき、わずか数秒で確実に測定

できます。

標準のマスク・テンプレートが装備されている他、内蔵のエディ

タで独自のマスクを作成することもできます。BER輪郭解析で

マスクを自動的に作成することもできるため、規定のBERレベ

ルのゴールデン・マスクを作成することができます。マスクは、

スケールと位置を変更することができます。

業界標準のマスク、カスタム・マスクは、内蔵のBERベース手法により数倍も高

速にテストできる

Qファクタは、13秒で表示される。ベスト・デシジョン・レベルはカーソルで

示される。100mV付近の電圧レールは広い標準偏差になっているため、開口の

中心ではない

Qファクタ解析

Qファクタ解析は、物理レイヤ・オプションに含まれている機

能です。時間ドメインにジッタがあるように、振幅ドメインに

はQファクタがあります。Qファクタは、振幅のS/N比を測定

したものであり、垂直方向のアイ開口のクリーン度を示します。

これは、どの程度簡単に1または0のロジックが決定できるか

に関係します。

BitAlyzerはサンプル・レートが高いために効率的に実行でき

るのですが、重要なことは、アイの中央部に近い波形の遷移に

対してのみ実行できることです。これにより、最初にエラーに

なったものがビット・エラーの原因となります。Qファクタ解

析では、期待されるベストな予測BER値と最適なデシジョンレ

ベル電圧が表示されます。

Page 7

7

www.tektronix.com/ja

ビット・エラー・レート・テスタ - BitAlyzer® BAシリーズ

テスト時間を長くすることで、BER輪郭の精度が上げることができる。この例で

は、1分半かけている。最良の予測BERとサンプリング位置を示している

BER輪郭

ビット・エラー・レートの輪郭測定は、物理レイヤ・オプション

に含まれている機能です。この解析では、アイ開口周囲のビッ

ト・エラー・レートを計算し、この結果を付加的なノイズによっ

て予測されるビット・エラー・レート応答曲線にフィットさせ

ます。輪郭の深さは、実際の測定よりも低いレベルで補間され

ます。

BER輪郭は、発生するデシジョン・ポイント変動の量を考慮し

た後のシステムに、どの程度の余裕があるかを把握するために

使用されます。BER輪郭は、既知の良品サンプルに対するマス

ク・テストのためのゴールデン・マスクとしてエクスポートす

ることもできます。

詳細なB ER値の予測の ためには、1e-4 BER以上のB ERデー タは使用しない。

テスト時間が長いほど、測定は正確になる

ジッタ・ピーク

ジッタ・テストは、物理レイヤ・オプションに含まれている機

能です。高速のBERスキャン手法により、ランダム・ジッタ

(RJ)、デターミニスティック・ジッタ(DJ)、トータル・ジッ

タ(TJ)を自動的に測定します。ジッタ測定の精度は使用さ

れるサンプル・サイズに比例しており、BERTスキャン・デー

タを使用した方法ほどデータ収集効率が優れたジッタ測定方法

は他にありません。総合的なBER測定とは、さらに多くのデー

タ・ポイントを使用してBERを補間し、より正確なジッタ測定

を行うことを意味しています。

UI境界から見てジッタ分布の左側と右側は、別々に測定されま

す。中央の緑の領域は、ガウス分布の内側にあるデターミニス

ティック・ジッタを示しています。

Page 8

8

www.tektronix.com/ja

データ・シート

FECパラメータは、ライブまたは記録されたエラー・データ・セットで定義、使

用できる。1回のエラー・データ・セットでさまざまなFE Cアーキテクチャがす

ばやくテストできる

Forward Error Correction(前方向誤り訂正)

エミュレーション・オプション

FECエミュレーション解析は、BA1500型、BA1600型のオ

プションです。当社特許のエラー特定機能により、BitAlyzer

はテストにおけるエラー発生場所を正確に特定することができ

ます。リードソロモン・アーキテクチャなどのブロック・エラー

訂正コードで標準のメモリ・ブロックをエミュレートすること

により、非相関データ・チャンネルからのビット・エラー・レー

ト・データは仮想エラー・コレクタに送られ、推奨されるFEC

手法によって検出することができます。

ユーザはエラー訂正の強さ、インターリーブの深さ、消去機能

を設定することができ、一般的なハードウェア訂正アーキテク

チャとマッチングすることができます。

一次元の訂正では、FECブロックにおけるシンボル数と訂正可

能な数を設定することができます。一次元の訂正は二次元の

インターリーブを先行されることができ、バースト・エラーの

訂正能力を改善することができます。

二次元の訂正は、製品アレイの訂正を補完するために使用する

こともできます。このケースでは、ユーザは製品アレイの行と

列の数、両方の次元の訂正の強さを設定します。テストでエラー

が検出されると、インターリーブの設定にしたがってエミュ

レーション・テーブルに置かれ、テーブルが一杯になると、エ

ラー数が任意のFEC符号ワードの訂正強度を超えていないか

チェックされます。

二次元訂正器では、外部抹消符号を内部符号異常として使用す

るように設定することもできます。このモードでは、1回の大

きなバースト訂正能力が2倍になります。FEC処理において、

各符号が使用された回数と異常の回数が確認できます。符号効

率も計算され、表示されます。

デジタル・チャンネルでBA1600型のFEC解析ツールを使用

すると、チャンネルに存在する実際のエラー統計のアーキテク

チャを調整することができます。チャンネルでパターン感度ま

たはバースト干渉の問題がある場合、この状態はFECにはっき

りと表れます。これは、ホワイト・ノイズのエラーをベースと

する、ソフトウェアによるエラー訂正シミュレーションよりも

優れています。

Page 9

9

www.tektronix.com/ja

ビット・エラー・レート・テスタ - BitAlyzer® BAシリーズ

2Dエラー・マップには、時間またはマイクロ秒でのデータ収集が表示される。ユー

ザ・データのブロックは、欄ごとに並びエラーの相関性が表示される

2Dエラー・マッピング・オプション

2Dエラー・マッピングは、BA1500型、BA1600型のオプ

ション機能です。この解析では、テストで発見されたエラーか

ら二次元のイメージを生成します。通信システムまたは物理的

な相互関係の構造パラメータをベースに、ユーザはブロック係

数を設定します。

エラー・マップは垂直ラスタスキャン・イメージで、エラーに

よるピクセルが表示されます。バーストからのエラーは異なっ

たカラーで表示されるため、バースト・エラーと非バースト・

エラーがわかりやすく区別されます。

ブロック・サイズは、パケット・サイズ、マルチプレクサの幅、

またはインターリーブの深さなどに関係します。ブロック係数

バーストと非バーストは異なった色で表示される。バックグランドのバースト問

題は、他の非バースト・エラー・タイプに重ね合わせられて表示される。非バー

スト・エラー問題は、パケットに約24,500ビット存在する

は、外部のマーカ信号によっても異なったものになります。例

えば、回転ディスク・ドライブのインデックス・マーカは2Dマッ

プで使用でき、ディスク・シリンダの繰返しリードを表示しま

す。ディスクの同じ位置でエラーが繰返し検出される場合は、

エラー・マップにおいて水平方向の縞模様となります。

パケット・サイズまたはマルチプレクサ幅をベースとしたエ

ラー・マッピングにより、エラーがパケットの特定の箇所から

発生するものか、またはマルチプレクサに接続されたパラレル・

バスの特定のビットで発生するものかがわかります。ビジュア

ル・ツールであるため、目視による相関性が確認でき、他のエ

ラー解析技術でも検出の難しいエラー相関性が確認できること

があります。

エラー・マップは、収集された数時間に及ぶデータを移動、ズー

ムすることができます。カーソルで領域を設定すると、領域内

で検出されるエラー数が表示されます。これにより、システム

で発生するエラーの様子が容易に確認できます。

Page 10

10

www.tektronix.com/ja

データ・シート

BA1500型、BA1600型は新しい入力技術を採用しており、

スレッショルドが可変でき、非常に高いデータ・レートの差動

入力信号のDC終端電圧が設定できます。

自動遅延校正

正確な可変遅延設定は、ジッタ、マスク・テスト、アイ・ダイ

アグラムなどの解析で重要になります。従来の可変遅延技術は、

遅かったり、長時間または異なった周波数での遅延校正が維持

できませんでした。

BitAlyzerは、新しい技術により、すべての可変遅延要素を1

秒以内、0.1ps単位での分解能で自動的に校正することができ

ます。非常に高速であるため、温度が変化したり、遅延エラー

の原因となる周波数が発生した場合の再校正に優れています。

1.5Gbps、2V

ク出力

の振幅設定による、BA1600型での代表的なデータ/クロッ

p-p

パターン同期

BA1500型、BA1600型は、PRBSおよびユーザ定義(最高

8Mビット)の両方の同期をサポートしています。他のBERテ

スタと違い、ユーザ定義のパターンは速度と確度という2種類

の方法で同期することができます。速度では、入力データの繰

返しパターンを学習することによりユーザ定義のパターンを同

期します。ユーザ・パターンを数回実行するだけで同期がとれ

るため、ファイバの再計算ループ実験、あるいは高速な再同期

が必要なアプリケーションにおけるユーザ定義のパターンでは

十分高速に実行することができます。確度では、ハードウェア

によるサーチで同期を検出するにように、期待されるユーザ・

パターンをあらかじめロードすることができます。

パターン・ジェネレータ、エラー・ディテクタの外部制御

BERでは、ゲートによるエラー測定、再同期の正確なタイミン

グ、バースト状のパケットのようなデータが必要になることが

あります。BitAlyzerには、エラーをカウントするゲートのため、

および外部再同期制御のためのユーザ・ブランク入力がありま

す。マーカ信号があり、特定のアプリケーションで解析結果を

カスタマイズすることができます。

BitAlyzerは、外部トリガでパターン・ジェネレータをトリガし

てパターン・シーケンスを再スタートすることができます。こ

れにより、外部制御でパケット・タイプのデータを転送したり、

複数のパターン・ジェネレータを同期させることができます。

自動アイ・マスク

アイ・ダイアグラム・テストのマスク・テンプレートは、通常

は良否判定のためにのみ使用されます。業界標準の定義に基づ

くものが多いのですが、特定のデバイスの出力波形の詳細を調

べるための正確なマスクは、製造現場での微小な変動を監視す

るために使用することができます。

ビット・エラー・レートの輪郭解析は、アイの周辺で取込んだ

ビット・エラー・レート・データから生成したアイ・ダイアグ

ラム・マスクを自動的にエクスポートする、ビット・エラー・レー

ト・テスタ初めての機能です。

エラー位置解析

BitAlyzerには、データ・ストリームのエラーごとのビットの

正確な位置を学習し、保存する機能があります。この機能は、

10年にもわたってさまざまなアプリケーションで使用されて

おり、エラーの原因を分離したり、相関関係を検出したり、干

渉を特定したり、一般的な問題を解決することができます。エ

ラー位置解析は、通常のビット・エラー・レート・テストで使

用するのと同じ設定で簡単に実行できます。

アイ・ダイアグラム

アイ・ダイアグラムは効率的に収集し、同じデバイスから取込ん

だビット・エラー・レートのテスト・データと正確に相関を取

ります。デシジョン・ウィンドウ電圧、時間をすばやくポジショ

ニングすることでピクセルごとにサンプリングし、アイ・ダイ

アグラムを生成します。

差動入力

今日の多くの高速通信システムは差動シグナリングを採用して

おり、優れたコモンモード・ノイズ除去性能を実現しています。

このため、真の差動レシーバを使用したビット・エラー・レー

ト測定が必要になります。また、ジッタ測定、アイ・ダイアグ

ラム、マスク・テストなどの解析手法では、ロジック設定のた

めの可変スレッショルド機能も必要になります。

出力ドライバ

BitAlyzerの出力ドライバは、10Gbpsの通信システムで開発

された技術によるものです。正確な設計により、小さなジッタ

出力と高速なエッジ・レートを実現しており、代表的なロジッ

ク・ファミリすべてをカバーする電圧振幅とオフセットに変更

することができます。電流ソースとユーザ・インタフェースに

より、対象インピーダンスと終端電圧を設定し、校正電圧スイン

グを維持します。

Page 11

11

www.tektronix.com/ja

ビット・エラー・レート・テスタ - BitAlyzer® BAシリーズ

性能

ジェネレータ

項目 概要

最高周波数

BA1500型 1500MHz(1.5GHz)

BA1600型 1600MHz(1.6GHz)

最低周波数

内部クロック 800kHz

外部クロック 100kHz

外部クロック/パターン開始 SMA

コンフィグレーション シングルエンド

スレッショルド −2~+4V

終端 −2~+3.3V

クロック/データ出力 SMA

コンフィグレーション 差動

振幅 70mV~+2V

オフセット −1.85~+3.85V

ロジック・ファミリ PECL/LVPECL/LVDSLVTTL/

CML/ECL

立上り/立下り 100ps未満(80ps、代表値)

遅延レンジ 30nsまたは1UI

遅延分解能 0.1%UIまたは1ps

トリガ出力 BNC

タイプ CLK/32またはパターン

パターン位置 プログラマブル

振幅 1V以上

A/Bパターン・ページ・スイッチ BNC

スレッショルド TTL

データ・タイプ

7

擬似ランダム x

ユーザ定義 96ビット~8Mビット

エラー挿入

長さ(ビット) 1、2、4、8、16、32、64、128

周波数 シングルまたは繰返し

ディテクタ

項目 概要

最高周波数 1600Mbps

最低周波数

BER測定 100kbps

自動最適アイ 70Mbps

+x6+1

15

+x14+1

x

20

+x17+1

x

23

+x18+1

x

31

+x28+1

x

2~4Mビット、A/Bページ

32ビット・ワード・サイズ

項目 概要

物理レイヤ・テスト 70Mbps

クロック/データ入力 SMA

コンフィグレーション 差動またはシングル

スレッショルド −2~+4V

ターミネーション −2~+3.3V

遅延レンジ 30nsまたは1UI

遅延分解能 0.1%UIまたは1ps

サンプリング・エッジ クロックの立上りまたは立下り

感度−シングルエンド 60mV

感度−差動 40mV

(代表値)

p-p

(代表値)

p-p

スタート・ディテクト SMA

コンフィグレーション シングルエンド

スレッショルド −2~+4V

ターミネーション −2~+3.3V

機能 トリガ・データの取込み

トリガ出力 BNC

タイプ CLK/32またはパターン

パターン位置 プログラマブル

振幅 1V以上

エラー出力 BNC

機能 エラーで32ビット・パルス

振幅 1V以上

マーカ入力 BNC

スレッショルド TTL

機能 エラー解析ローケータ

最高周波数 4kHz推奨

ブランク入力 BNC

スレッショルド TTL

機能 アクティブでエラーを無視

再同期 エッジでトリガ(オプション)

最小分解能 32ビット

データ・タイプ

7

擬似ランダム x

+x6+1

15

+x14+1

x

20

+x17+1

x

23

+x18+1

x

31

+x28+1

x

ユーザ定義 96ビット~8Mビット

32ビット・ワード・サイズ

再同期

マニュアル 押しボタンまたはブランク

自動 エラー・スレッショルドをプログラム

ユーザ取込み 繰返しパターンの検出

ユーザ・シフト ハードウェア・パターン・サーチ

データ取込み 最大8Mビット取込み

測定 BER、ビット、再同期PG/EDクロック

周波数

Page 12

www.tektronix.com/ja

〒108-6106東京都港区港南2-15-2品川インターシティB棟6階

電話受付時間/ 9:00〜12:0 0・13:00〜19:0 0

(土・日・祝・弊社休業日を除く)

テクトロニクスお客様コールセンター TEL:0120-441-046

ヨッ!

良い オシロ

■

記載内容は予告なく変更することがありますので、あらかじめご了承ください。

©Tektronix

項目 概要

表示内容

ホーム・ビュー スタート・ページ

ジェネレータ ジェネレータの設定

ディテクタ ディテクタの設定

エディタ パターン、マスクの編集

システム ユーティリティ・ツール

ログ ロングタームBERログ

エラー解析 標準

ベーシックBER BER解析表

バースト長 バースト・サイズの履歴

エラーフリー間隔 間隔の履歴

相関性 エラー位置の履歴

パターン感度 パターン内のエラー

ブロック・モード ブロックあたりのエラー履歴

ストリップ・チャート BER対時間チャート

物理レイヤ・テスト オプション

アイ・ダイアグラム アイ・ダイアグラムの表示

BER輪郭 アイ周囲のBERマップ

マスク・テスト マスク・テストの実行

ジッタ解析 DJ/RJ/TJのジッタ測定

Q値解析 Qの設定と表示

エラー位置取込み

ライブ解析 連続

エラー・ロギング容量 最大2GBファイル・サイズ

エラー・イベント/秒 10,000

最大バースト長 32kビット

一般性能

項目 概要

TFTディスプレイ 640×480VGA

タッチ・センサ アナログ抵抗膜

セルフテスト 電源投入時

プロセッサ 500MHzPentium(または同等品)

フロッピー 1.44Mバイト

ハード・ディスク・ドライブ 20Gバイト

キーボード マイクロ

DRAM 64Mバイト

オペレーティング・システム

WindowsNT

(OS)

プリンタ・ポート セントロニクス

モニタ出力 DB-15VGA

マウス PS/2

リモート・コントローラ IEEE-488(GPIB)またはTCP/IP

ネットワーク・インタフェース 100MBEthernet

質量 14.5kg

電源 90~240VAC、270W

寸法 41.9cm(幅)×21.8cm(高さ)×

48.9cm(奥行)

ご発注の際は以下の型名をご使用ください。

製品

型名 オプション 概要

BA1600 1.6Gbpsパターン・ジェネレータ/

エラー・アナライザ

ECC エラー訂正符号化エミュレーションの追加

MAP エラー・マッピング解析機能の追加

PL 物理レイヤ・テスト・ソフトウェアの追加

BA1500 1.5Gbpsパターン・ジェネレータ/

エラー・アナライザ

ECC エラー訂正符号化エミュレーションの追加

MAP エラー・マッピング解析機能の追加

PL 物理レイヤ・テスト・ソフトウェアの追加

*TEKTRONIXおよびTEKはTektronix,Inc.の登録商標です。記載された商品名はすべて各社の商標あるいは登録商標です。

■

記載内容は予告なく変更することがありますので、あらかじめご了承ください。

©Tektronix 2010年11月 65Z-25538-1

Loading...

Loading...