Page 1

TECHNICAL MANUAL

OPERATOR’S, ORGANIZATIONAL, DIRECT SUPPORT,

AND GENERAL SUPPORT MAINTENANCE MANUAL

INCLUDING REPAIR PARTS AND SPECIAL TOOLS LISTS

FOR

OSCILLOSCOPE, TEKTRONIX MODEL R7704

(NSN 6625-00-007-8487)

TM 11-6625-2922-14&P

HEADQUARTERS, DEPARTMENT OF THE ARMY

8 SEPTEMBER 1980

Page 2

WARNING

DANGEROUS VOLTAGES EXIST IN

THIS EQUIPMENT

Dangerous potentials exist at several points throughout this equipment. When the equipment is

operated with the covers removed, DO NOT touch exposed connections or components. Some

transistors have voltages present on their cases. Disconnect power before cleaning the

equipment or replacing parts.

DON’T TAKE CHANCES!

Page 3

Copyright 1970 by Tektronix Inc. All rights reserved. Reproduced by permission of the copyright owner, TEKTRO NIX

INC.

TM 11-6625-2922-14&P

TECHNICAL MANUAL HEADQUARTERS

No. 11-6625-2922-14&P WASHINGTON, DC, 8 September 1980

You can help improve this manual. If you find any mistakes or if you know of a way to

improve the procedures, please let us know. Mail your letter, DA Form 2028 (Recommended

Changes to Publications and Blank Forms), or DA Form 2028-2 located in back of this manual

direct to: Commander, US Army Communications and Electronics Materiel Readiness Command,

ATTN: DRSEL-ME-MQ, Fort Monmouth, NJ 07703.

In either case, a reply will be furnished direct to you.

}

OPERATOR’S, ORGANIZATIONAL, DIRECT SUPPORT, AND

GENERAL SUPPORT MAINTENANCE MANUAL

(INCLUDING REPAIR PARTS AND SPECIAL TOOLS LISTS)

FOR

OSCILLOSCOPE, TEKTRONIX MODEL R7704

(NSN 6625-00-007-8487)

REPORTING ERRORS AND RECOMMENDING IMPROVEMENTS

DEPARTMENT OF THE ARMY

Table of Contents

Paragraph Page

SECTION 0. INTRODUCTION

Scope .................................................................................................................... 0-1 0-1

Indexes of Publications.......................................................................................... 0-2 0-1

Maintenance Forms, Records, and Reports.......................................................... 0-3 0-1

Reporting Equipment Improvement Recommendations (EIR).............................. 0-4 0-1

Administrative Storage .......................................................................................... 0-5 0-1

Destruction of Army Electronics Materiel............................................................... 0-6 0-1

This manual is an authentication of the m anufacturer’s commercial literature which, through usage, has been found to

cover the data required to operate and maintain this equipment. Since the manual was not prepar ed in accordance with

military specifications, the format has not been structured to consider levels of maintenance.

0.1

Page 4

R7704

TABLE OF CONTENTS

SECTION 1. R7704 SPECIFICATION Page Page

Introduction 1-1 First-Time Operation

Table 1-1 Electrical General 2-7

Vertical Deflection System 1-1 Setup Information 2-7

Triggering 1-2 Calibration Check 2-8

Horizontal Deflection System 1-2 Vertical and Horizontal Mode 2-8

Calibrator 1-2 Triggering 2-9

External Z-Axis Input 1-2 Control Illumination 2-10

Signal Outputs 1-3 Readout 2-10

Character Generator 1-4 Beam Finder 2-10

Power Supply 1-4 Z-Axis Input 2-10

Display 1-4 Test Set-Up Chart

Table 1-2 Environmental Characteristics 1-4 General 2-10

Table 1-3 Physical Characteristics 1-5 General Operating Information

Standard Accessories 1-5 Simplified Operating Instructions 2-10

Instrument Options Intensity Controls 2-16

General 1-5 Display Focus 2-16

Option 1 1-5 Trace Alignment Adjustment 2-17

Option 2 1-5 Graticule 2-17

Option 3 1-5 Light Filter 2-17

System Specifications Beam Finder 2-17

Control Illumination 2-17

Readout 2-18

Remote Readout 2-19

SECTION 2 OPERATING INSTRUCTIONS Display Photography 2-19

General 2-1 Vertical and Horizontal Mode Switch

Preliminary Information Logic 2-19

Operating Voltage 2-1 Vertical Mode 2-20

Operating Temperature 2-2 Horizontal Mode 2-21

Rackmounting 2-2 Vertical Trace Separation 2-22

Display Definitions 2-2 Trigger Source 2-22

Plug-In Units X-Y Operation 2-22

General 2-3 Intensity Modulation 2-23

Plug-In Installation 2-3 Raster Display 2-24

Controls and Connectors Calibrator 2-24

General 2-3 Signal Outputs 2-24

Display Controls 2-5 Probe Power Connectors 2-25

Mode Selectors 2-5 Remote Connector 2-25

Output Connectors 2-6 Remote Single-Sweep Reset 2-25

Input Connectors 2-7 Applications 2-26

i

Page 5

R7704

CONTENTS (Cont)

SECTION 3 CIRCUIT DESCRIPTION Page Page

Introduction 3-1 Lubrication 4-3

Block Diagram Visual Inspection 4-3

General 3-1 Semiconductor Checks 4-3

Circuit Operation Recalibration 4-3

General 3-3 Troubleshooting

Logic Fundamentals Introduction 4-3

General 3-3 Troubleshooting Aids 4-3

Symbols 3-3 Troubleshooting Equipment 4-4

Logic Polarity 3-3 Troubleshooting Techniques 4-7

Input/Output Tables 3-4 Special Troubleshooting Information 4-9

Non-Digital Devices 3-4 Corrective Maintenance

Main Interface General 4-18

General 3-7 Obtaining Replacement Parts 4-18

Logic Circuit Soldering Techniques 4-18

General 3-7 Component Replacement 4-19

Horizontal Logic 3-7 Recalibration After Repair 4-25

Z-Axis Logic 3-13 Instrument Repackaging 4-25

Horizontal Binary 3-14

Vertical Binary 3-16

SECTION 5 PERFORMANCE CHECK/CALIBRATION

Plug-In Binary 3-18

1 Clock Generator 3-20 Introduction 5-1

Vertical Chopped Blanking 3-21 Test Equipment Required

Chop Counter 3-24 General 5-1

Vertical Mode Logic 3-26 Test Equipment 5-1

Trigger Selector 3-27 Accessories 5-2

Vertical Interface 3-30 Adjustment Tools 5-2

Vertical Amplifier 3-33 Short-Form Procedure and Index 5-3

Horizontal Interface 3-35 Performance Check/Calibration Procedure

Horizontal Amplifier 3-36 General 5-5

Output Signals 3-38 Preliminary Procedure for Performance

CRT Circuit 3-41 Check Only 5-6

Line to DC Converter/Regulator 3-45 Preliminary Procedure for Complete

Low-Voltage Regulator 3-49 Calibration 5-6

Controls and Cabling 3-53 Preliminary Control Settings 5-6

Readout System Calibration Steps 5-7

Introduction to Readout System 3-54

Circuit Analysis of Readout System 3-60

SECTION 6 RACKMOUNTING

SECTION 4 MAINTENANCE Introduction 6-1

Introduction 4-1 Instrument Dimensions 6-1

Cover Removal 4-1 Rack Dimensions 6-1

Power-Unit Removal 4-1 Slide-Out Tracks 6-1

Preventive Maintenance Mounting Procedure 6-1

General 4-1 Removing or Installing the Instrument 6-5

Cleaning 4-2 Slide-Out Track Lubrication 6-5

ii

Page 6

CONTENTS (Cont)

SECTION 7 ELECTRICAL PARTS LIST Page SECTION 9 MECHANICAL PARTS LIST

Abbreviations and Symbols Mechanical Parts List Information

Parts Ordering Information Index of Mechanical Parts List and

Index of Electrical Parts List Illustrations

Electrical Parts List Mechanical Parts List

Part Number-National Stock Number

Cross Reference Index

SECTION 8 DIAGRAMS AND CIRCUIT BOARD CHANGE INFORMATION

ILLUSTRATIONS Abbreviations and symbols used in this manual are

based on or taken directly from IEEE Standard 260

Symbols and Reference Designators 8-1 "Standard Symbols for Units", MIL-STD-12B and

Voltage and Waveform Test Conditions 8-2 other standards of the electronics industry.

Diagrams Change Information, if any, is located at the rear of

Circuit Board Illustrations this manual.

iii

R7704

Page 7

Page

APPENDIX A. REFERENCES......................................................................................................................A-1

APPENDIX B. COMPONENTS OF END ITEM LIST (Not applicable)

APPENDIX C. ADDITIONAL AUTHORIZATION LIST (Not applicable)

APPENDIX D. MAINTENANCE ALLOCATION

Section I. Introduction............................................................................................................................D-1

II. Maintenance Allocation Chart for Oscilloscope, Tektronix Model R7704 .............................D-3

III. Tool and Test Equipment Requirements for Oscilloscope, Tektronix Model R7704 ............D-4

IV. Remarks................................................................................................................................D-5

APPENDIX E. REPAIR PARTS AND SPECIAL TOOLS LIST (See Section 7, Electrical Parts List)

APPENDIX F. EXPENDABLE SUPPLIES AND MATERIALS LIST (Not applicable)

iv

Page 8

SECTION 0

INTRODUCTION

0-1. Scope

This manual contains instructions for the operation and

organizational, direct support, and general support

maintenance of Oscilloscope, Tektronix Model R7704.

Throughout this manual, Oscilloscope, Tektronix Model

R7704 is referred to as the R7704.

0-2. Indexes of Publications

c. Discrepancy in Shipment Report (DISREP) (SF

Fill out and forward Discrepancy in Shipment

361).

Report (DISREP) (SF 361) as prescribed in AR 5538/NAVSUPINST 4610.33B/AFR 75-18/MCO P4610.19C

and DLAR 4500.15.

0-4. Reporting Equipment Improvement

Recommendations (EIR)

a. DA Pam 310-4.

Pam 310-4 to determine whether there are new editions,

changes, or additional publications pertaining to the

equipment.

b. DA Pam 310-7.

determine whether there are modification work orders

(MWO’s) pertaining to the equipment.

0-3. Maintenance Forms, Records, and Reports

a. Reports of Maintenance

Equipment. Department of the Army forms and

procedures used for equipment maintenance will be

those prescribed by TM 38-750, The Arm y Maintenance

Management System.

Refer to the latest issue of DA

Refer to DA Pam 310-7 to

and Unsatisfactory

b. Report of Packaging and Handling Deficiencies

Fill out and forward DD Form 6 (Pac kaging Im pr ovem ent

Report) as prescribed in AR 735-11/NAVINST

4440.127E/AFR 400-54/MCO 4430.3E and DSAR

4140.55.

If your R7704 needs improvement, let us know. Send us

an EIR. You, the user, are the only one who can tell us

what you don’t like about your equipment. Let us know

why you don’t like the design. Tell us why a procedure is

hard to perform. Put it on an SF 368 (Quality Deficiency

Report). Mail it to Commander, US Army

Communications and Electronics Materiel Readiness

Command, ATT ’N: DRSEL-ME-MQ, Fort Monmouth, NJ

07703. We’ll send you a reply.

0-5. Administrative Storage

To prepare the R7704 for administrative storage,

perform the procedures described in Section 4,

Maintenance, and Section 5, Performance

Check/Calibration. Upon removal from administrative

storage, perform the pr ocedures described in Section 5,

.

Performance Check/Calibration, to determine that the

equipment is fully operational.

0-6. Destruction of Army Electronics Materiel

Destruction of Army electronics materiel to prevent

enemy use shall be in accordance with TM 750-244-2.

0-1

Page 9

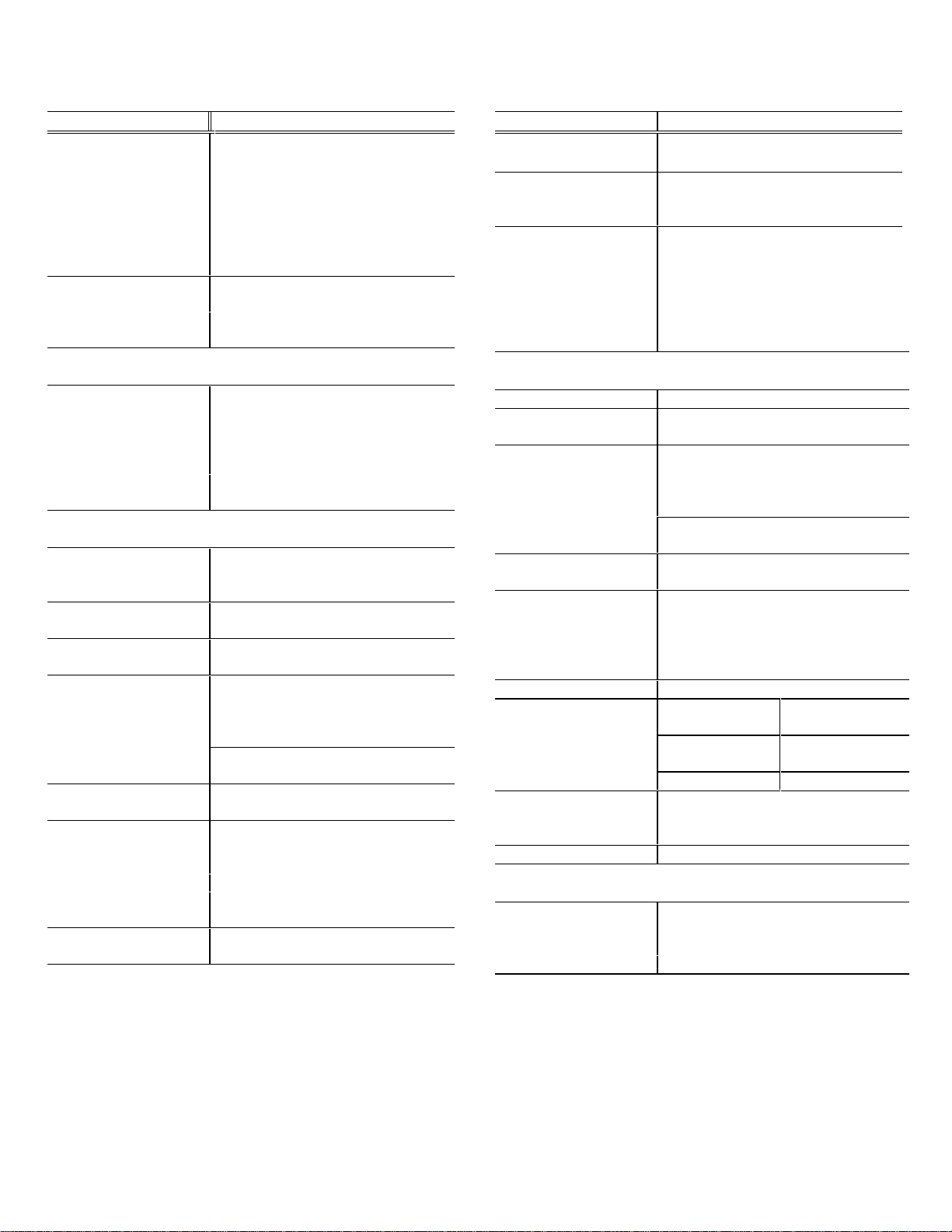

Fig. 1-1. The R7704 Oscilloscope.

Fig. 1-1. The R7704 Oscilloscope

R7704 (A)

Page 10

SECTION 1

R7704 SPECIFICATION

Change information, if any, affecting this section will be found at the rear of the manual.

R7704

Introduction

The Tektronix R7704 Oscilloscope is a solidstate, high performance instrument designed for

mounting in a 19-inch rack (complete rackmounting

information is given in Section 6). This instrument

accepts Tektronix 7-series plug-in units to form a

complete measurement system. The flexibility of this

plug-in feature and the variety of plug-in units available

allow the system to be used for many measurement

applications.

The R7704 has four plug-in com partments . The

left pair of plug-ins is c onnected to the vertical deflec tion

system. The right pair is connected to the horizontal

deflection system. Electronic switching between the

plug-in units connected to each deflection system allows

a dual-trace vertical display and/or a dual-sweep

horizontal display. This instrument features regulated

DC power supplies to assure that performance is not

affected by variations in line voltage and frequency, or by

changes in load due to the varying power requirements

of the plug-in units. Maximum power consumption of this

instrument is about 225 watts (60 hertz, 115-volt line).

The R7704 features a CRT with sm all spot size

and high writing speed. Graticule area is 8 X 10

centimeters. In addition, the instrument contains a

readout system to provide CRT display of alpha-numeric

information from the plug-in units; data such as

deflection factor, sweep rate, etc. can be encoded.

This instrument will meet the electrical

characteristics listed in Table 1-1 following complete

calibration as given in Section 5. The performance

check procedure included in Section 5 provides a

convenient method of check ing instrument performance

without making internal checks or adjustments. The

following electrical characteristics apply over a calibration

interval of 1000 hours and an ambient temperature range

of 0°C to +50° C, except as otherwise indicated.

Warmup time for given accuracy is 20 minutes.

NOTE

Many of the measurement capabilities of this

instrument are determined by the choice of

plug-in units. The following characteristics

apply to the R7704 Oscilloscope only. See

the system specification later in this section

for characteristics of the complete system.

TABLE 1-1.

ELECTRICAL

Characteristic Performance

VERTICAL DEFLECTION SYSTEM

Deflection Factor Compatible with all 7-series plug-

in units.

Deflection Accuracy Less than 1% difference

between vertical compartments.

Low-Frequency

Linearity

Bandwidth Varies with vertical plug-in

Risetime

(A) 1-1

0.1 division or less compression

or expansion of a center

-screen two- division

signal when positioned any-

where vertically within the

graticule area.

selected.

See System Specifications.

Characteristic Performance Requirement

Isolation Between At least 100:1 from DC to 150

Vertical Compartments

Chopped Mode

Repetition rate

Time segment 0.4 to 0.6 microsecond.

from each

compartment

Delay Line Permits viewing of leading edge

Difference in Delay 0.2 nanosecond or less.

Between Compartments

megahertz.

One megahertz ±20%.

of triggering signal

Page 11

Specification-R7704

TABLE 1-1. (cont)

Characteristic Performance

Vertical Display LEFT: Left vertical unit only.

Modes (selected by

front-panel

VERTICAL MODE ADD: Added algebraically.

switch) CHOP: Dual-trace, chopped be-

Trace Separation

Range for

Dual-Sweep A trace.

Modes

Trigger Source

(selected by frontpanel A TRIGGER

SOURCE and B LEFT VERT: From left vertical

unit only.

TRIGGER SOURCE RIGHT VERT: From right vertical

switches) unit only.

HORIZONTAL DEFLECTION SYSTEM

Deflection Factor Compatible with all 7-series plug-

Deflection Accuracy Less than 1% difference

Fastest Calibrated Two nanoseconds/division.

Sweep Rate

Bandwidth at 10%

Down

Without phase DC to at least three megahertz

correction (10-division reference).

With phase DC to at least three megahertz

correction (10-division reference).

Phase Shift Between

Vertical and Horizontal Deflection

Systems

Without phase 2° or less from DC to at least 35

correction kilohertz.

With phase

correction

ALT: Dual-trace, alternate

between vertical units.

tween vertical units.

RIGHT: Right vertical unit only.

B trace can be positioned +4 to

+6 or -4 to -6 divisions from the

TRIGGERING

VERT MODE: Determined by

vertical mode.

in units.

between compartments.

DC to at least six megahertz

(five-division reference).

Adjustable to less than 2° from

DC to two megahertz.

TABLE 1-1. (cont)

Characteristic Performance Requirement

Chopped Mode

Repetition rate

Time segment. 2.0 to 3.0 microseconds

from each com-

partment

Horizontal Display A: A horizontal unit only.

Modes (selected by

front-panel HORIZONTAL MODE

switch) CHOP: Dual-sweep, chopped

Wave Shape Square wave.

Polarity Positive going with baseline at

Output Voltage

Open circuit 40 mV, 0.4 V, 4 V at front-panel

Into 50 ohms 20 mV, 0.2 V, 0.4 V at front-panel

Output Current 40 milliamperes with current-loop

Repetition Rate One kilohertz.

Accuracy +15 ° C to

Voltage and

current

Repetition rate Within 0.25%. Within 0.5%.

Risetime and Falltime

Duty Cycle 50% ± 0.1%.

EXTERNAL Z-AXIS INPUTS

High Sensitivity Input

Sensitivity Two volts peak to peak provides

200 kilohertz ±20%.

ALT: Dual-sweep, alternate be-

tween horizontal units.

ADD: Added alphabetically

between horizontal units

B: B horizontal unit only.

CALIBRATOR

zero volts.

pin jacks.

4 mV and 40 V available at inter-

nal circuit board connections.

pin jacks.

accessory (012-0259-00)

connected between 4 V pin jack

and

ground.

0°C to +50°C

+35°C

Within 1%. Within 2%.

0.25 microsecond or less.

trace modulation over full intensity

range.

(A) 1-2

Page 12

Specification-R7704

TABLE 1-1. (cont)

Characteristic Performance Requirement

Useful input volt- Two volts peak to peak, DC to two

ages versus

repetition frequency

Polarity of

operation

megahertz; reducing to 0.4 volt

peak to peak at 20 meqahertz.

Positive-going signal decreases

trace intensity; negative- going

signal increases trace intensity.

Minimum pulse 30 nanoseconds at two volts.

width that provides intensity

modulation

Input resistance 500 ohms ± 10%.

at DC

Maximum input 15 volts (DC + peak AC).

voltage

High Speed Input

Sensitivity 60 volts peak to peak provides

trace modulation over full

intensity range.

Useful input volt- 60 volts peak to peak, DC to 100

age versus repeti- megahertz.

tion frequency

Polarity of

operation

Positive-going signal decreases

trace intensity; negative-going

signal increases trace intensity.

Minimum pulse 3.5 nanoseconds at 60 volts.

width that provides intensity

modulation

Input resistance 18 kilohms ± 20%.

at DC

Maximum input 60 volts (DC + peak AC); 60 volts

voltage peak to peak AC.

SIGNAL OUTPUTS

+Sawtooth

Source (selected A HORIZ time-base unit or B

by SWEEP HORIZ time-base unit.

switch)

Polarity Positive-going with baseline at

zero volts ± 1 volt (into one

megohm).

TABLE 1-1. (cont)

Characteristic Performance Requirement

Output voltage

Rate of rise

Into 50 ohms 50 millivolts/unit of time ± 15%.

Into one One volt/unit of time ±10%.

1

megohm

Peak voltage

Into 50 ohms Greater than 500 millivolts.

Into one Greater than 10 volts.

megohm

Output resistance 950 ohms ± 2%.

+Gate

Source (selected A HORIZ time-base unit.

by GATE B HORIZ time-base unit.

switch)

Delaying time-base unit (in A

HORIZ compartment).

Output voltage

Into 50 ohms 0.5 volt ± 10%.

Into one 10 volts ± 10%.

megohm

Risetime into 50 20 nanoseconds or less.

ohms

Output resistance 950 ohms ± 2%.

Vertical Signal

Output

Bandwidth Varies with vertical plug-in selec-

ted. See System Specification.

Risetime

Source Determined by B TRIGGER'

SOURCE switch.

Output voltage

Into 50 ohms 25 millivolts/division of vertical

deflection ± 25%.

Into one 0.5 volt/division of vertical deflecmegohm tion ± 25%.

Output resistance 950 ohms ± 2%.

1

Unit of time selected by time-base time/division switch.

1

(A) 1-3

Page 13

Specification-R7704

TABLE 1-1. (cont)

Characteristic Performance Requirement

CHARACTER GENERATOR

Word Location See Fig. 2-5

POWER SUPPLY

Line Voltage Range

AC, RMS (Selected

by Line Selector

assembly on rear

panel).

115-volts nominal 90 to 136 volts.

230-volts nominal 180 to 272 volts.

Line Frequency 48 to 66 hertz (48 to 66 and 360

to 440 hertz with special MOD

101K).

Maximum Power

Consumption 225 watts, 2.8 amperes at 60

hertz, 115-volt line.

DISPLAY

Graticule

Type Internal with variable edge

lighting.

Area Eight divisions vertical by 10 divi-

sions horizontal. Each division

equals one centimeter.

Phosphor P31 standard. Others available

on special order.

Resolution

Horizontal At least 12 lines/division.

Vertical At least 12 lines/division.

Geometry 0.1 division or less total bowing

or tilt of a display horizontal or

vertical line.

Beam Finder Limits display within graticule

area when actuated.

Photographic Writing

Speed (without film

fogging techniques)

Tektronix C-51 At least 3300 centimeters/microCamera with f1.2 second with Polaroid2 Type 410

lens and 1:0.5 film (10,000 ASA) and P31 CRT

object-to-image phosphor.

ratio At least 7000 centimeters/micro-

second with Polaroid Type 410

film (10,000 ASA) and P11 CRT

phosphor.

2

Registered trademark of the Polaroid Corporation.

TABLE 1-1. (cont)

Tektronix C-27 At least 2200 centimeters/microCamera with f1.3

lens and 1:0.5

object-to-image phosphor.

ratio At least 5500 centimeters/micro-

second with Polaroid Type 410

film(10,000 ASA) and P31 CRT

second with Polaroid Type 410

film (10,000 ASA) and P11 CRT

phosphor.

TABLE 1-2.

ENVIRONMENTAL CHARACTERISTICS

Characteristic Performance

NOTE

This instrument will meet the electrical

characteristics given in Table 1-1 over the

following environmental limits. Complete

details on environmental test procedures,

including failure criteria, etc., can be

obtained from Tektronix, Inc. Contact your

local Tektronix Field Office or representative

Temperature Range

Operating 0°C to +50°C.

Non-operating -55°C to +75°C.

Altitude

Operating 15,000 feet.

Non-operating Test limit 50,000 feet.

Electro-magnetic

Interference (EMI)

as tested in MIL-I6181D (when equipped with Option 3

only)

Radiated inter- Interference radiated from the

ference instrument under test within the

given limits from 150 kilohertz to

1000 megahertz.

Conducted Interference conducted out of the

interference instrument under test through the

power cord within the given limits

from 150 kilohertz to 25 mega-

hertz.

Transportation(pack

aged instrument,

without plug-ins) 1A, Category II.

Qualifies under National Safe

Transit Committee test procedure

1-4 (A)

Page 14

Specification-R7704

TABLE 1-3.

PHYSICAL CHARACTERISTICS

Characteristic Performance

Ventilation Safe operating temperature is

maintained by forced-air

cooling.

Automatic resetting thermal

cutout

protects instrument from over-

heating.

Warm-up Time 20 minutes for rated accuracy.

Finish Anodized front panel and

cabinet.

Overall Dimensions

(measured at maximum points)

Height 7.0 inches (17.7 centimeters).

Width 19.0 inches (48.3 centimeters).

Length 22.4 inches (56.9 centimeters)

behind front panel.

24.2 inches (61.7 centimeters)

over-all.

Net Weight (instru- 44 pounds (19.7 kilograms).

ment only)

STANDARD ACCESSORIES

Standard accessories supplied with the R7704

are given in the Mechanical Parts List illustrations. For

optional accessories available for use with this

instrument, see the Tektronix, Inc. catalog.

INSTRUMENT OPTIONS

General

The following options are available for the R7704

and can be installed as part of the instrument when

ordered, or they can be installed at a later time.

Complete information on all options for this instr ument is

given in this manual. For further information on

instrument options, see your Tektronix , Inc. catalog, or

contact your local Tektronix Field Office or

representative.

Option 1

This option deletes the Readout System. Operation

of the instrument is unchanged except that there is no

alphanumeric display on the CRT and the READOUT

control is non-functional. The Readout System can be

added at any time by ordering the readout conversion kit.

Option 2

The X-Y Delay Compensation Network can be added

to the instrument to equalize the signal delay between

the vertical and horizontal deflection systems. When this

network is installed and activated, the phase shift

between the vertical and horizontal channels is

adjustable to less than 20 from DC to two megahertz.

Option 3

With option 3 inst alled, the instrument will meet the

EMI interference specifications given in Table 1-2.

(A) 1-5

Page 15

SYSTEM SPECIFICATIONS

Your Tektronix 7700-series oscilloscope system

provides exceptional flexibility in operation with a wide

choice of general and special purpose plug- in units . T he

type number of a particular plug-in unit identifies its

usage as follows: The first digit (7) denotes the

oscilloscope system for which the plug-in unit is designed

17000-series).

The second letter describes the purpose of the

plug-in unit:

A - Amplifier unit.

Specification-R7704

L - Spectrum analyzer, double width.

M - Miscellaneous.

S - Sampling unit.

T - Sampling time-base unit.

The third and fourth digits of the plug- in type number are

sequence numbers and do not carry any special

connotation.

B - "Real time" time-base unit.

An "N" suffix letter added to the normal four digit type

number identifies a unit not equipped with the circuitry

D - Digital unit.

necessary to encode data for the 7000-series readout

system.

J - Spectrum analyzer, single width.

K - Spectrum analyzer, single width.

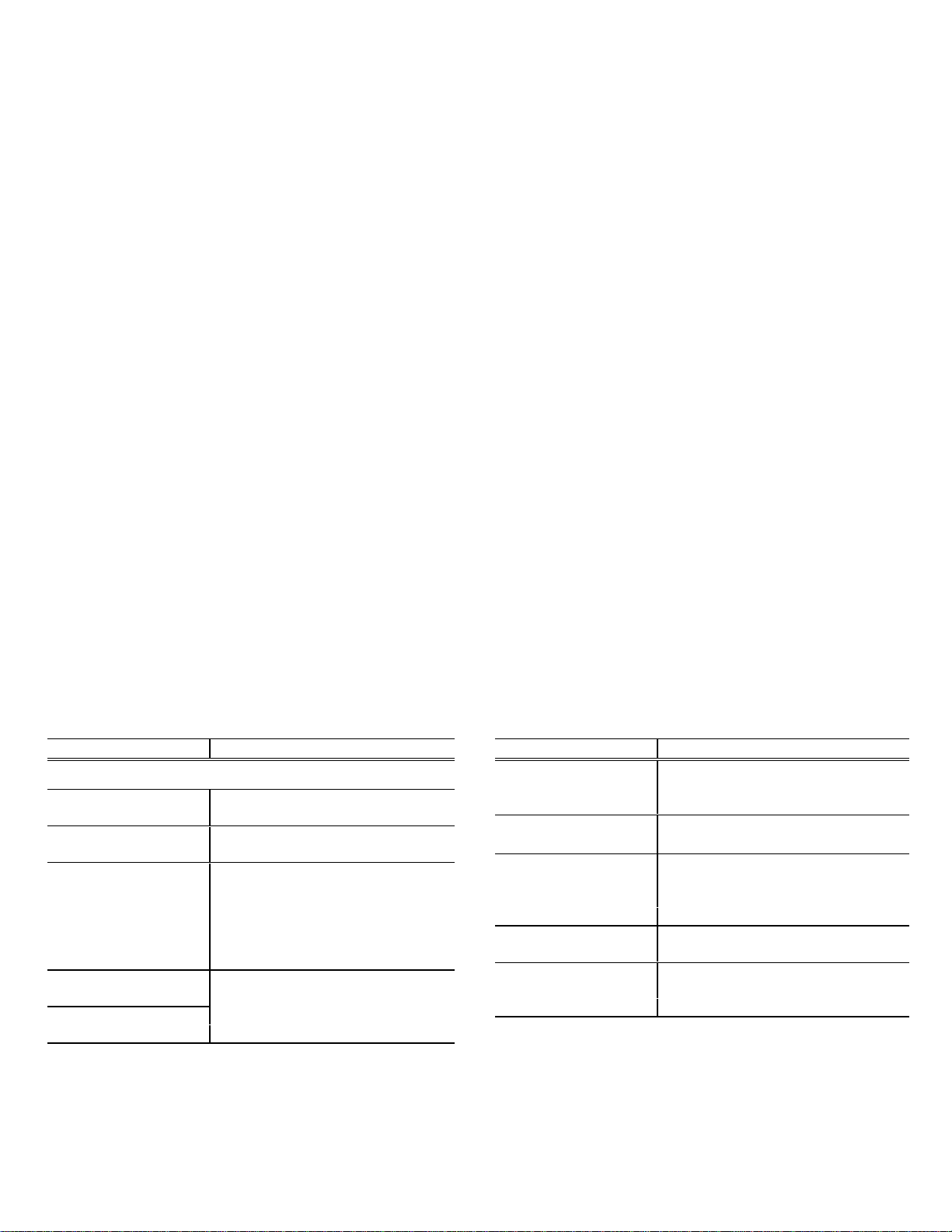

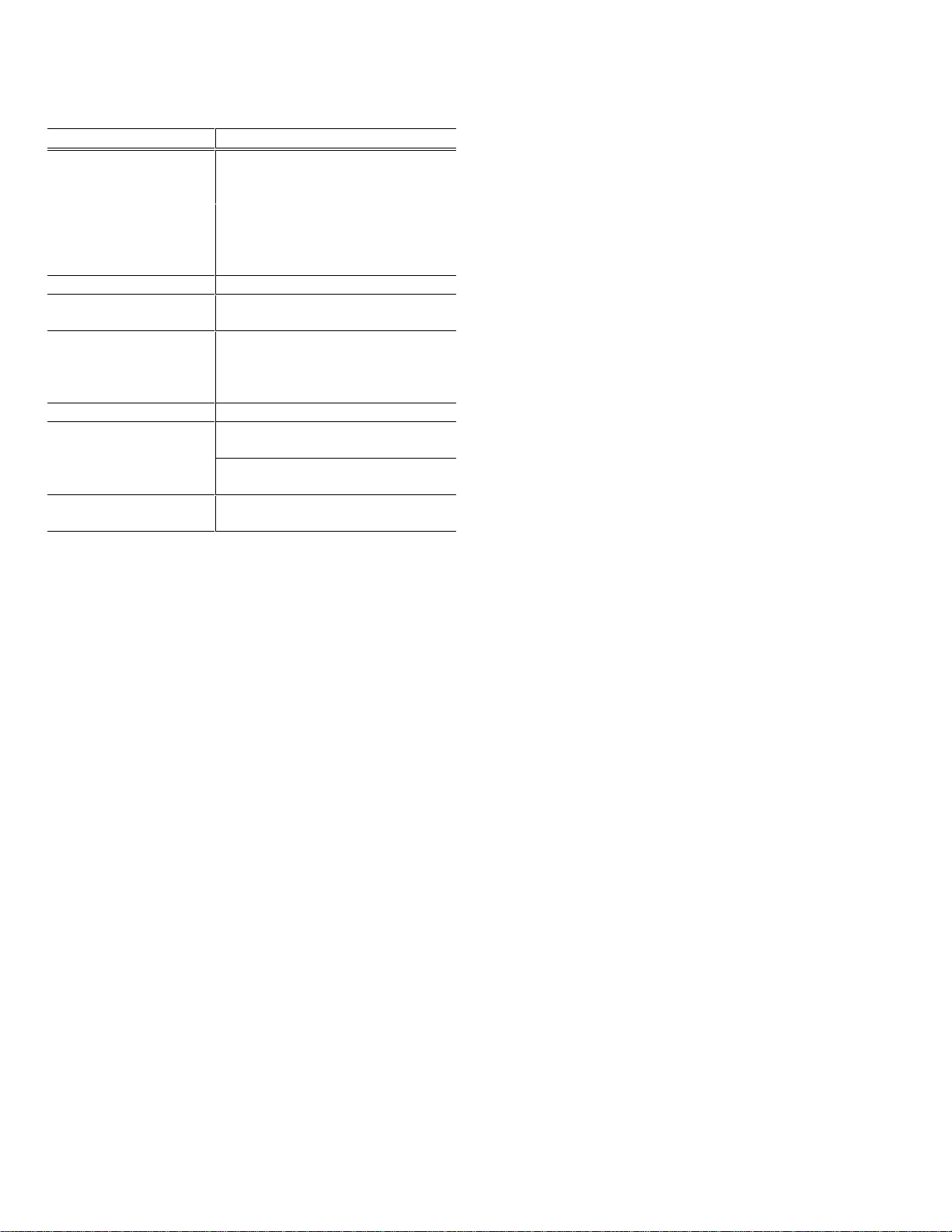

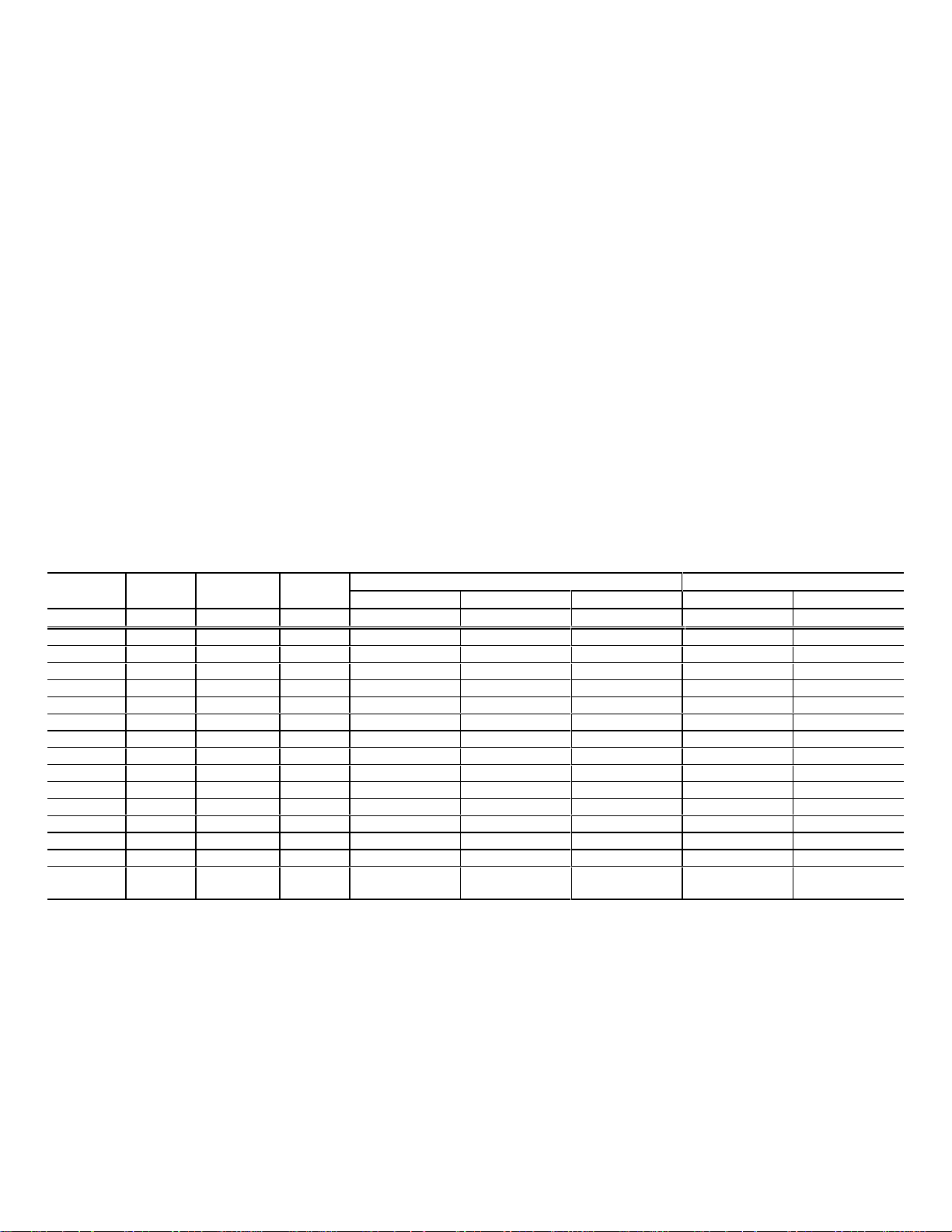

7700-SERIES OSCILLOSCOPE SYSTEM VERTICAL SPECIFICATIONS

This table lists the vertical s pecif ications which are system dependent. For m ore com plete spec ific ations on plug-

in units for the 7000-Series Oscilloscope System, refer to the Tektronix Catalog.

Amplifier Vertical System Deflection Factor Accuracy* SIG OUT

Plug-In EXT CAL INT CAL INT CAL

Unit Probe BW Tr 0 to 50 ° C 15 to 35°C 0 to 50°C BW Tr

7A11 Integral 150 MHz 2.4 ns 2% 3% 4% 60 MHz 5.9 ns

None 105 MHz 3.4 ns 2% 3% 4% 55 MHz 6.4 ns

P6053 105 MHz 3.4 ns 3% 4% 5% 55 MHz 6.4 ns

None 100 MHz 3.5 ns 1.5% 2.5% 3.5% 55 MHz 6.4 ns

7A13 P6053 100 MHz 3.5 ns 1.5% 2.5% 3.5% 55 MHz 6.4 ns

P6055 65 MHz 5.4 ns 1.5% 2.5% 3.5% 45 MHz 7.8 ns

7A14 P6021 50 MHz 7.0 ns 2% 3% 4% 40 MHz 8.8 ns

P6022 105 MHz 3.4 ns 2% 3% 4% 50 MHz 7.0 ns

7A15 None 75 MHz 4.7 ns 2% 3% 4% 50 MHz 7.0 ns

P6053 75 MHz 4.7 ns 3% 4% 5% 50 MHz 7.0 ns

7A16 None 150 MHz 2.4 ns 2% 3% 4% 60 MHz 5.9 ns

P6053 150 MHz 2.4 ns 3% 4% 5% 60 MHz 5.9 ns

7A18 None 75 MHz 4.7 ns 2% 3% 4% 50 MHz 7.0 ns

P6053 75 MHz 4.7 ns 3% 4% 5% 50 MHz 7.0 ns

7A22 None or

any

1.0 MHz

± 10%

350 ns

± 9%

2% 3% 4% 1.0 MHz

± 10%

350 ns

±9%

*Deflection Factor accuracy is checked as follows:

EXT CAL 0° C to 50°C-Plug-in gain set at a temperature within 10°C of operating temperature, using an external calibrator whose

accuracy is within 0.25%.

INT CAL 15°C to 35°C-Plug-in gain set while operating within a temperature range of +15°C to +35°C, using the oscilloscope

calibrator.

INT CAL 0°C to 50°C-Plug-in gain set using the oscilloscope calibrator (within 10°C of the operating temperature} in a temperature

range between 0°C and +50°C.

1-6

Page 16

SECTION 2

OPERATING INSTRUCTIONS

Change information, if any, affecting this section will be found at the rear of this manual.

R7704

General

To effectively use the R7704, the operation and

capabilities of the instrument must be known. This

section describes the operation of the front-, side-, and

rear-panel controls and connectors and gives first time

and general operating information.

PRELIMINARY INFORMATION

Operating Voltage

WARNING

This instrument is designed for operation from

a power source with its neutral at or near earth

(ground) potential with a separate safety-earth

conductor. It is not intended for operation

from two phases of a multi-phase system, or

across the legs of a single-phase, three-wire

system.

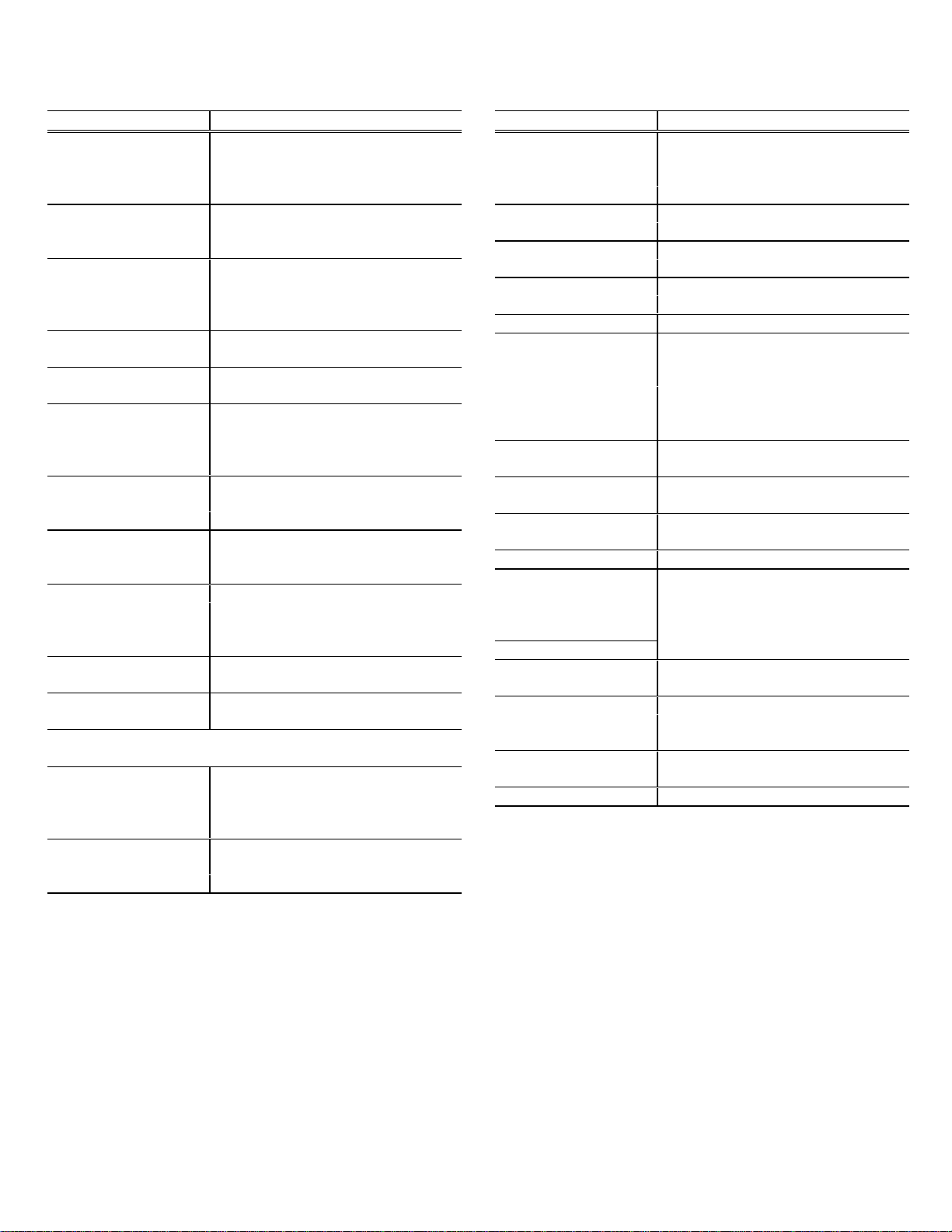

The R7704 can be operated from either a 115volt or a 230-volt nominal line voltage source. T he Line

Selector assembly on the rear panel converts this

instrument from one operating voltage to the other. This

assembly also includes fuses to provide protection for

the line-input portion of this instrument. Use the

following procedure to obtain correct instrument

operation from the line voltage available.

Power Cord Conductor Identification

Conductor Color Alternate

Color

Ungrounded (Line) Brown Black

Grounded (Neutral) Blue White

Grounding (Earthing) Green-Yellow Green-Yellow

4. Re-install the cover and tighten the captive

screws.

5. Before applying power to the instrument, check

that the indicator tab on the switch bar is protruding

through the correct hole for the desired nominal line

voltage.

CAUTION

This instrument may be damaged if operated

with the Line Selector assembly set to

incorrect positions for the line voltage applied.

1. Disconnect the instrument from the power

source.

2. Loosen the two captive screws which hold the

cover onto the selector assembly; then pull to remove

the cover.

3. To convert from 115-volts to 230-volts nominal

line voltage, or vice versa, pull out the Selector switch

bar (see Fig. 2-1) and plug it back into the remaining

holes. Change the line-cord power plug to match the

power-source receptacle or use a 115 to 230-volt

adapter.

REV. C, NOV. 1976 2-1

Fig. 2-1. Line Selector assembly on rear panel (shown with

Fig. 2-1. Line Selector assembly on rear panel (shown

cover removed).

with cover removed).

Page 17

Operating Instructions-R7704

TABLE 2-1.

Regulating Ranges

Line Selector Regulating

Switch Position Range

115 V 90 to 136 volts

230 V 180 to 272 volts

The R7704 is designed to be used with a threewire AC power system. If a three- to two-wire adapter is

used to connect this instrum ent to a two-wire AC power

system, be sure to connect the ground lead of the

adapter to earth (ground). Failure to complete the

ground system may allow the chassis of this instrum ent

to be elevated above ground potential and pose a shock

hazard.

Operating Temperature

The R7704 can be operated where the ambient

air temperature is between 0°C and +50° C. This

instrument can be stored in ambient temperatures

between -55°C and +75°C. After storage at

temperatures beyond the operating limits, allow the

chassis temperature to c ome within the operating limits

before power is applied.

The R7704 is cooled by air drawn in through the

air filter on the rear panel and blown out through the

holes on the right side. Adequate clearance must be

provided at these locations (see Dim ensional Drawing in

Section 7). Allow at least one and one-half inches

clearance behind the air filter and at least one inch on

the right side.

A thermal cutout in this instrument provides

thermal protection and disconnects the power to the

instrument if the internal temperature exceeds a safe

operating level. Power is automatically restored when

the temperature returns to a safe level. O peration of this

instrument for extended periods without the covers may

cause it to overheat and the thermal cutout to open.

Also, check the air filter occasionally; a dirty filter will

prevent adequate air flow into the instrument.

which are defined in the instruction manuals for these

special units. The following terminology will be used

throughout this manual (see Simplified Operating

Instructions in this section for set-up information to obtain

each of these displays).

Single Trace

A display of a single plot produced by one

vertical signal and one sweep.

Dual Trace

A display of two plots produced by two vertical

signals and one sweep.

Dual Sweep

A display of two plots produced by one vertical

signal and two sweeps. Both sweeps operate

independently.

Dual Trace-Dual Sweep

A display of four plots produced by combining

two vertical signals and two sweeps. Each vertical signal

is displayed against each sweep. Both sweeps oper ate

independently.

Independent Pairs

A display of two plots produced by two vertical

signals, each displayed against its own sweep (LEFT

versus B; RIGHT versus A). Both sweeps operate

independently. This simulates a dual-beam display for

most repetitive combinations.

Delayed Sweep-Single Trace

A display of a single plot produced by one

vertical signal and a delayed sweep. Two sweeps are

used to produce this display; the sweeps are operating

with a delaying/delayed relationship where one sweep

(identified as the delaying sweep) delays the start of the

second sweep (identified as the delayed sweep). This

display can be expanded to present two plots, produced

by one vertical signal displayed against both the delaying

and the delayed sweep.

Rackmounting

Complete instructions for rackmounting the

R7704 are given in Section 6.

DISPLAY DEFINITIONS

General

The following definitions describe the types of

displays which can be obtained with an R7704

Oscilloscope system with real-t ime amplifiers, tim e-base

units, or combinations of these. Use of special pur pose

plug-in units may result in different types of displays,

Delayed Sweep-Dual Trace

A display of two plots produced by combining

two vertical signals and a delayed sweep. Two sweeps

are used to produce this display; the sweeps are

operating with a delaying/delayed relationship. Each

vertical signal is displayed against the delayed sweep.

This display can be expanded to present four plots,

produced by displaying

2-2 (A)1

Page 18

Operating Instructions-R7704

both vertical signals against both the delaying and the

delayed sweep.

X-Y

A plot of two variables, neither of which

represents time.

PLUG-IN UNITS

General

The R7704 is designed to accept up to four

Tektronix 7-series plug-in units. This plug-in feature

allows a variety of display combinations and also

allows selection of bandwidth, sensitivity, display mode,

etc. to meet the measurement requirements. In

addition, it allows the oscilloscope system to be

expanded to meet future measurement requirements.

The overall capabilities of the resultant system is in

large part determined by the characteristics of the plugin unit selected. A list of the curr ently available plug-in

units for this instrument along with their major

specifications, is given in Section 1. For mo re complete

information, see the current Tektronix, Inc. catalog.

Plug-In Installation

To install a plug-in unit into one of the plug-in

compartments, align the slots in the top and bottom of

the plug-in with the associated guide rails in the plug-in

compartment. Push the plug-in unit firmly into the plug-in

compartm ent until it locks into place. T o remove a plugin, pull the release latch on the plug-in unit to disengage

it and pull the unit out of the plug-in compartment. Plugin units can be removed or installed without turning off

the instrument power.

The plug-in versatility of the R7704 allows a

variety of display modes with many different plug-ins.

Specific inform ation for obtaining these displays is given

under Display Combinations later in this section.

However, the following information is provided here to

aid in plug-in installation.

To produce a single-trace display, install a

single-channel vertical unit (or dual-channel unit set for

single-channel operation) in either of the vertical

compartments. For dual-trace displays, either install a

dual-channel vertical unit in one of the vertical

compartm ents or install a single channel vertical unit in

each vertical compartment. A combination of a singlechannel and dual-channel vertical unit allows a threetrace display; likewise, a combination of two dualchannel vertical units allows a four-trace display.

For single time-base displays, the tim e-base unit

can be placed in either horizontal compartment.

However, for dual time-base displays, other

considerations must be taken into account. In the ALT

position of the VERTICAL MODE switch and ALT or

CHOP position of the HORIZONTAL MODE switch, the

plug-ins in the LEFT VERT and B HORIZ com partments

are displayed together and the RIGHT VERT and A

HORIZ plug-ins are displayed together (independent

pairs operation). Therefore, the vertical and horizontal

units must be correctly mated if a special display is

desired. If delayed sweep operation is desired, a

delaying time-base unit must be installed in the A HO RIZ

(DELAYING TIME BASE) compartm ent. Any compatible

7B-series unit can be used as a delayed timebase in the

B HOR IZ compartment.

It is not necessary that all of the plug-in

compartments be filled to operate the instrument; the

only plug-ins needed are those required for the

measurement to be made. However, at environmental

extremes, exces s interference may be radiated into this

instrument through the open plug-in compartments.

Blank plug-in panels are available from Tektronix , Inc . to

cover the unused compartments; order Tektronix Part

No. 016-0155-00.

When the R7704 is calibrated in accordance with

the calibration procedure given in this ins tr uct ion manual,

the vertical and horizontal gain are normalized. This

allows calibrated plug-in units to be changed from one

plug-in compartment to another without recalibration.

However, the basic calibration of the individual plug-in

units should be checked when they are installed in this

system to verify their measurement accuracy. See the

operating instructions section of the plug-in unit

instruction manual for verification procedure.

(A) 2-3

X-Y displays can be obtained in two ways with

the R7704 system. If a 7B-series time-base unit is

available which has an amplifier f eature, the X s ignal c an

either be routed through one of the vertic al units via the

internal trigger pickoff circuitry to the horizontal system,

or connected to the external horizontal input connector of

the time-base unit. Then, the vertical signal (Y) is

connected to the remaining vertical unit. Also, a 7Aseries amplifier unit can be installed in one of the

horizontal compartments for X-Y operation.

Special purpose plug-in units ma y have specific

restrictions regarding the plug-in com partments in which

they can be installed. This information will be given in

the instruction manuals for these plug-in units.

CONTROLS AND CONNECTORS

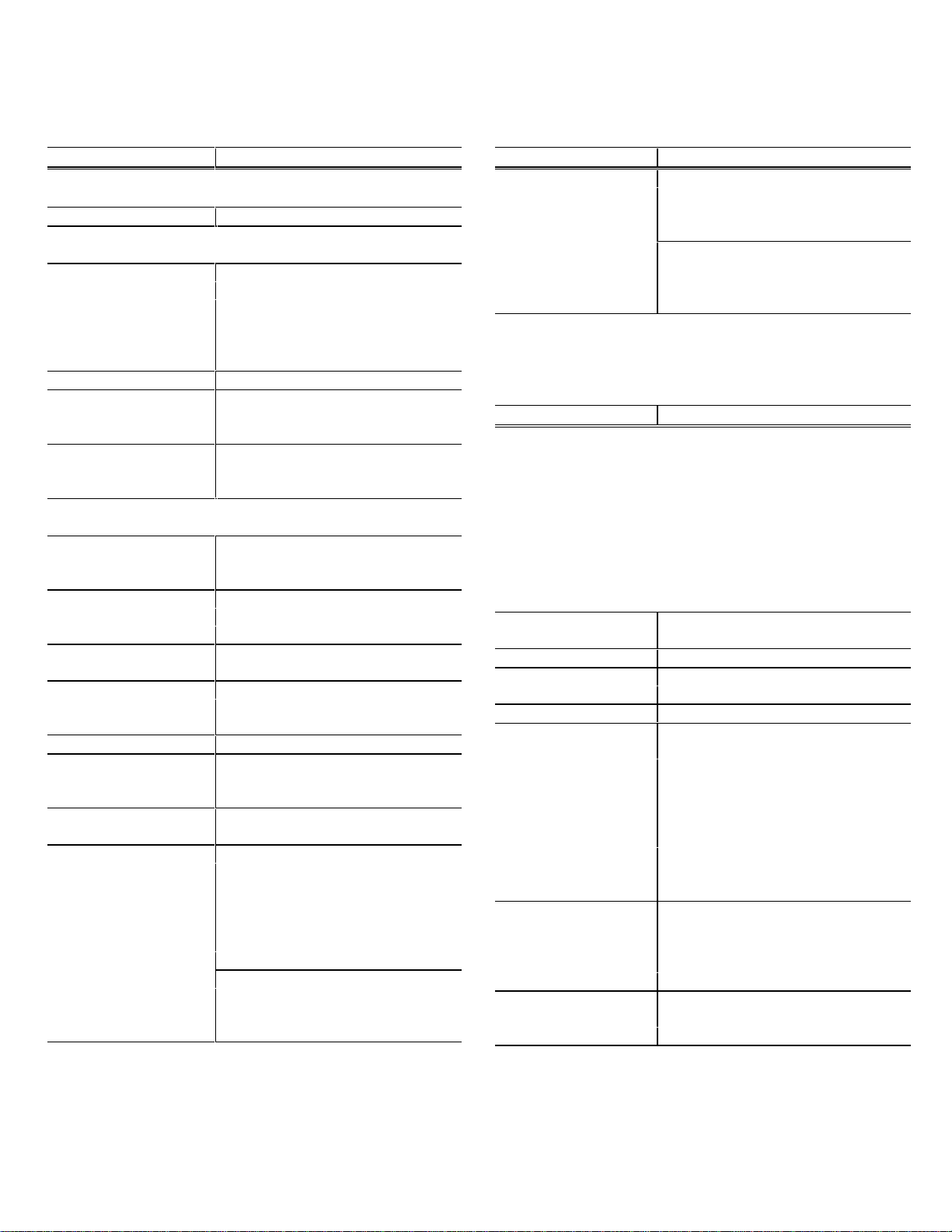

General

The major controls and connectors for operation

of the R7704 are located on the front panel of the

instrument. Some aux iliary functions are pr ovided on the

side, top, and rear panels. Fig. 2-2 shows the front and

rear panels of

Page 19

Operating Instructions-R7704

Fig. 2-2. External controls and connectors

Fig. 2-2. External controls and connectors.

2-4

2-4

(A)

Page 20

R7704. To make full use of the capabilities of this

instrument, the operator should be familiar with the

function and use of each of these controls and

connectors. A brief description of each control and

connector is given here. More detailed operating

information is given under General Operating

Information.

Display Controls

A INTENSITY Controls brightness of the trace

produced by the plug-in unit in the

A HORIZ (DELAYING TIME

BASE) compartment. Light

behind the ’A’ of A INTENSITY

indicates when this control is

operative. Control is inoperative

(light off) when the A plug-in is not

selected for display by the

HORIZONTAL MODE switch or

when the A HORIZ compartment

is vacant.

BEAM FINDER Compresses display within

(PULL LOCK) graticule area independent of

display position or applied

signals. Momentary actuation

provided when button is pressed;

display remains compressed when

knob is pulled outward to lock it in

the "find" position.

TRACE ROTATION Screwdriver adjustment to align

trace with horizontal graticule

lines.

B INTENSITY Controls brightness of the trace

produced by the plug-in unit in the

B HORIZ compartment. Light

behind the ’B’ of B INTENSITY

indicates when this control is

operative. Control is inoperative

(light off) when the B plug-in is not

selected for display by the

HORIZONTAL MODE switch or

when the B HORIZ compartment

is vacant.

FOCUS Screwdriver adjustm ent to provide

optimum display definition.

READOUT Controls brightness of the readout

portion of the CRT. In the display

fully counter-clockwise position,

the Readout System is

inoperative.

GRAT ILLUM Controls graticule illumination.

Operating Instructions-R7704

ASTIG (side panel) Screwdriver adjustment used in

conjunction with the FOCUS control

to obtain a well-defined display.

Does not require readjustment in

normal use.

CONTROL ILLUM Controls illumination level of push(side panel) button switches on the R7704 and

the associated plug-in units.

OFF: All pushbutton lights off. A

and B INTENSITY lights remain

at low intensity to provide a

power-on indication.

LOW: All pushbuttons illuminated

at low intensity.

HIGH: Pushbuttons illuminated at

maximum intensity.

Power

POWER Controls power to instrument.

Line Selector (rear Switching

assembly to select the panel)

nominal operating voltage (115 or

230 volts). The assembly also

includes the input power fuses.

Mode Selectors

VERTICAL MODE Selects vertical mode of operation.

LEFT: Signal from plug-in unit in

LEFT VERT compartment is

displayed.

CHOP: Signals from plug-in units in

both LEFT VERT and RIGHT

VERT compartments are

displayed. Display switched

between vertical plug-ins at a

one megahertz repetition rate.

ADD: Signals from plug-in units in

both LEFT VERT and RIGHT

VERT compartments are

algebraically added and the

algebraic sum displayed on the

CRT.

ALT: Signals from plug-in units in

both LEFT VERT and RIGHT

VERT compartments are

displayed. Display switched

between vertical plug-ins after

each sweep except for delayed

sweep operation. Then, the

display is switched between

vertical

(A) 2-5

Page 21

Operating Instructions-R7704

plug-ins after every second

sweep. When the

HORIZONTAL MODE switch

is set to ALT or CHOP,

independent-pairs operation

is provided.

RIGHT: Signal from plug-in unit

in RIGHT VERT compartment is displayed.

A TRIGGER Selects source of internal trigger

SOURCE signal for the time-base in

the A HORIZ compartment.

VERT MODE: Trigger signal

automatically follows the

vertical display except in

CHOP (vertical); then the

trigger signal is the same as

for ADD.

LEFT VERT: Trigger signal is

obtained from plug-in unit in

LEFT VERT compartment.

RIGHT VERT: T rigger signal is

obtained from plug-in unit in

RIGHT VERT compartment.

HORIZONTAL Selects horizontal mode of

MODE operation.

A: Signal from plug-in unit in the

A HORIZ compartment is

displayed.

ALT: Signals from plug-in units

in both A HORIZ and B

HORIZ compartments are

displayed. Display switched

between horizontal plug-ins

at end of each sweep.

CHOP: Signals from plug-in

units in both A HORIZ and B

HORIZ compartments are

displayed. Display switched

between horizontal plug-ins

at a 0.2-megahertz repetition

rate.

B: Signal from plug-in unit in the

B HORIZ compartment is

displayed.

B TRIGGER Selects source of internal trigger

SOURCE signal for the time-base in

the B HORIZ compartment.

VERT MODE: Trigger signal

automatically follows the vertical

display except in CHOP

(vertical); then trigger signal is

the same as for ADD.

LEFT VERT: Trigger signal is

obtained from plug-in unit in

LEFT VERT compartment.

RIGHT VERT: Trigger signal is

obtained from plug-in unit in the

RIGHT VERT compartment.

VERT TRACE Vertically positions the trace proSEPARATION (B) duced by the plug-in unit in the B

HORIZ compartment up to four

divisions with respect to the trace

produced by the plug-in unit in the

A HORIZ compartment (dualsweep modes only).

Output Connectors

CALIBRATOR (4 V, Calibrator output connectors.

0.4 V, 40 mV, GND)

PROBE POWER Power source for active probe

systems. Two output

connectors provided; one on

front panel and one on rear

panel.

+ SAWTOOTH (rear Provides positive-going sample of

panel) sawtooth signal. SAWTOOTH

switch allows selection of sawtooth

from tim e-base unit in the A HORIZ

compartment or the B HORIZ

compartment.

+GATE (rear panel) Provides positive-going gate signal

coincident with the respective

sweep. GATE switch allows

selection of one of three gate

signals; the A gate from time-base

unit in A HORIZ compartment, the

B gate from time-base unit in B

HORIZ compartment, or the

delayed gate from delaying timebase unit in the A HORIZ

compartment.

SIG OUT (rear panel) Provides output signal from the

vertical plug-in units. Source of

the output signal at the SIG OUT

connector is selected by the B

TRIGGER SOURCE switch (see

B TRIGGER SOURCE for

description of sources

available).

2-6 (A)

Page 22

Input Connectors

Z-AXIS INPUTS Input connectors for intensity

(rear panel) modulation of the CRT display.

HIGH SPEED: Input connector for

high-amplitude, high-frequency

Z-axis signals; usable from DC

to 100 megahertz.

HIGH SENSITIVITY: Input

connector for low-amplitude Zaxis signals; usable for signals

with repetition rates between DC

and 10 megahertz; input voltage

derating necessary between 2

and 10 megahertz.

J1075 REMOTE Nine-pin connector which

CONTROL (rear panel) provides remote single-sweep

reset and ready indication for

the time-base units in the A

HORIZ and B HORIZ

compartments (with compatible

timebase units only) and remote

read-out mode and single-shot

readout operation.

Miscellaneous

Operating Instructions-R7704

READOUT MODE Determines operating mode of the

Readout System.

FREE RUN-REMOTE: Readout

System free runs to present

characters as encoded by plugin

units. Free-running condition

can be interrupted for remote

single-shot operation through

J1075.

GATE TRIG’D: Readout System

is locked out so no characters

are displayed during the sweep

time. At the end of the sweep

gate selected by the GATE

switch, a single frame of all

applicable readout characters is

presented.

Ground (not labeled) Binding post to establish common

ground between the R7704 and any

associated equipment. One gr ound

post provided on the front panel

and one on the rear panel.

FIRST-TIME OPERATION

General

SAWTOOTH (top Selects source of signal for +

panel) SAW-TOOTH connector.

A: Sawtooth output signal

derived from time-base unit

in A HORIZ compartment.

B: Sawtooth output signal

derived from time-base unit

in B HORIZ compartment.

GATE (top panel) Selects source of signal for +

GATE connector.

A: Gate output signal derived

from time-base unit in A

HORIZ compartment.

B: Gate output signal derived

from time-base unit in B

HORIZ compartment.

DLY’D: Gate output signal

derived from delaying timebase unit in A HORIZ

compartment.

The following steps demonstrate the use of the

controls and connectors of the R7704. It is recomm ended

that this procedure be followed com pletely for fam iliarization

with this instrument.

Set-up Information

1. Set the controls as follows:

Front panel

A INTENSITY Counterclockwise

B INTENSITY Counterclockwise

BEAM FINDER Released

READOUT OFF

GRAT ILLUM Counterclockwise

POWER Off

VERTICAL MODE LEFT

A TRIGGER SOURCE VERT MODE

HORIZONTAL MODE A

VERT TRACE Midrange

SEPARATION (B)

B TRIGGER SOURCE VERT MODE

Side panel

CONTROL ILLUM OFF

(A) 2-7

Page 23

Operating Instructions-R7704

2. Connect the R7704 to a power source that

meets the voltage and frequency requirements of this

instrument. If the available line voltage is outside the

limits of the Line Selector switch (on rear panel), see

Operating Voltage in this section.

3. Insert Tektronix 7A-series amplifier units into

both the LEFT VERT and RIGHT VERT compartments.

Insert Tektronix 7B-s er ies time-base units into both the A

HORIZ and B HORIZ compartments.

4. Set the POWER switch to ON. Allow several

minutes warmup so the instrument reaches a normal

operating temperature before proceeding.

5. Set both vertical units for a vertical deflection

factor of two volts/division and center the ver tic al pos ition

controls.

6. Set both time-base units for a sweep rate of 0.5

milliseconds/division in the auto, internal trigger mode.

7. Advance the A INTENSITY control until the trace

is at the desired viewing level (near midrange).

8. Connect the 4 V calibrator pin-jack to the input of

the left vertical unit with a BNC to pin-jack cable

(supplied accessory).

9. Check for a sharp, well-defined display over the

entire trace length (if focused display cannot be obtained,

see Display Focus in this section).

10. Disconnect the input signal and position the

trace with the left vertical unit position control so it

coincides with the center horizontal line of the graticule.

11. If the trace is not parallel with the center

horizontal line, see Trace Alignment Adjustment in this

section.

12. Rotate the GRAT ILLUM control throughout its

range and notice that the graticule lines are illuminated

as the control is turned clockwise (most obvious with

tinted filter installed). Set control so graticule lines are

illuminated as desired.

Calibration Check

13. Connect the 4 V calibrator pin-jack to the input

connector of either vertical unit with the BNC to pin-jac k

2-8 cable (supplied accessory) and a BNC T connector.

Connect the output of the BNC T connector to the input

of the other vertical unit with the 42-inch BNC cable

(supplied accessory).

14. The display should be two divisions in amplitude

with five complete cycles shown horizontally. An

incorrect display indicates that the plug-ins need to be

recalibrated. See the instruction manual of the

applicable plug-in unit for complete information.

Vertical and Horizontal Mode

15. Notice that the position controls of only the left

vertical unit and the A time-base unit have any effec t on

the displayed trace. Position the start of the trace to the

left line of the graticule with the A tim e-base unit position

control and move the trace to the upper half of the

graticule with the left vertical unit position control.

16. Press the RIGHT button of the VERTICAL

MODE switch. Also press the B button of the

HORIZONTAL MODE switch. Advance the B

INTENSITY control until the trace is at the desired

viewing level (about midrange).

17. Notice that the position controls of only the right

vertical unit and the B time-base unit have any effec t on

the displayed trace. Position the start of the trace to the

left graticule line with the B time-base position control

and move the display to the bottom half of the graticule

with the right vertical unit position control.

18. Press the ALT button of the VERTICAL MODE

switch. Notice that two traces are displayed on the CRT.

The top trace is produced by the left ver tical unit and the

bottom trace is produced by the right vertical unit; the

sweep for both traces is produced by the B time-base

unit. Reduce the sweep rate of the B time-base unit to

50 milliseconds/division. Notice that the display

alternates between the left and right vertical plug-ins

after each sweep. Turn the B time-base sweep rate

switch throughout its range. Notice that the display

alternates between vertical units at all sweep rates.

19. Press the CHOP button of the VERTICAL MODE

switch. Turn the B time-base unit sweep rate switch

throughout its range. Notice that a dual-tr ace display is

presented at all sweep rates, but unlike ALT, both

vertical units are displayed on each sweep on a timesharing basis. Return the B time-base unit sweep rate

switch to 0.5 millisecond/division.

20. Press the ADD button of the VERTICAL MODE

switch. The display should be four divisions in

amplitude.

2-8 (A)

Page 24

Operating Instructions-R7704

Notice that the position control of either vertical unit

moves the display. Return the VERTICAL MODE s witch

to the LEFT position.

21. Press the ALT button of the HORIZONTAL

MODE switch. Two traces should be presented on the

CRT. If the display overlaps, adjust the VERT TRACE

SEPARATION (B) control to position one trace to the

bottom of the graticule area. Turn the sweep rate

switches of both timebase units throughout their range.

Notice that each timebase unit controls one of the trac es

independent of the other time-base unit. Also notice that

when one of the time-base units is set to a slow sweep

rate (below about 50 milliseconds/division) sweep

alternation is evident. Only one of the traces is

presented on the CRT at a time. Return the s weep r ates

of both time-base units to 0.5 millisecond/ division.

Adjust the A INTENSITY control. Notic e that it changes

the intensity of the trace produced by the A Timebase

unit only. Likewise, the B INTENSITY control changes

the intensity of the trace produced by the B timebase unit

only. Return both intensity controls to the desired level.

22. Press the CHOP button of the HORIZONTAL

MODE switch. Notice that two traces are s hown on the

CRT in a manner similar to the ALT display. Turn the

sweep rate switches of both time-bas e units throughout

their range. Notice that two traces are displayed on the

CRT at all sweep rates. Also notice that even when both

time-base units are set to a slow sweep rate (50

milliseconds/division or slower), both traces are visible

on the CRT at the same time. Return the sweep rate

switches of both time-base units to 0.5

millisecond/division.

23. Connect the BNC to pin-jack cable to the 0.4 V

calibrator output. Press the CHOP button of the

VERTICAL MODE switch. Four traces should be

displayed on the CRT. If not, adjust the position controls

of the vertical units and the VERT TRACE SEPARATION

(B) control to position the four traces onto the viewing

area. Adjust the position controls of the plug-in units to

identify which traces are produced from each of the plugin units (if vertical units have the identif y feature, it can

be used to identify the traces). Also, set one of the tim ebase units to a sweep rate of one millisecond/division.

Notice that the vertical deflection produced by the LEFT

VERT unit is displayed at the sweep rate of both the A

HORIZ and B HORIZ time-base units and that the

vertical deflection produced by the RIGHT VERT plug-in

unit is also displayed at the sweep rate of both the A

HORIZ and B HORIZ time-base units.

24. Press the ALT button of the HORIZONTAL

MODE switch. Notice that the display is very similar to

the display obtained in the previous step. The main

difference in this display is that the sweeps are pr oduced

alternately by the time-base units (noticeable only at slow

sweep rates).

25. Press the ALT button of the VERTICAL MODE

switch. Notice that only two traces are displayed on the

CRT. Also notice that one of the traces is produced by

the left vertical unit at the sweep rate of the B time-bas e

unit and the other trace is produced by the right vertical

unit at the sweep rate of the A time-base unit. This

feature is called independent-pairs operation, and is

obtained only when the VERTICAL MODE switch is in

the ALT position and the HORIZONTAL MODE switch is

in either the ALT or the CHOP position.

Triggering

26. Press the LEFT button of the VERTICAL MODE

switch and the A button of the HORIZONTAL MODE

switch. Center the display on the CRT with the left

vertical unit position control. Disconnect the input signal

from the right vertical unit input connector . Sequentially

press all of the VERTICAL MODE switch buttons. Notice

that a stable display is obtained in all positions of the

VERTICAL MODE switch (straight line in RIGHT

position).

27. Press the LEFT VERT button of the A T RIG G ER

SOURCE switch. Again, sequentially press all of the

VERTICAL MODE switch buttons. Notice that the

display is again stable in all positions, as in the previous

step.

28. Press the RIGHT VERT button of the A

TRIGGER SOURCE switch. Sequentially press all the

VERTICAL MODE switch buttons and notice that a

stable display cannot be obtained in any position. The

reason for this is that there is no input signal connected

to the right vertical unit. Return the A TRIGGER

SOURCE switch to VERT MODE.

29. The B TRIGGER SOURCE switch operates in a

similar manner to the A TRIGGER SOURCE switch

when the B time-base unit is selected for display.

Control Illumination

30. Notice that only the light associated with the A

INTENSITY control is illum inated. Sequentially press all

the HORIZONTAL MODE switch buttons and notice the

A or B INTENSITY lights; these lights indicate which

intensity control is active. The lights also provide an

indication that the POWER switch is on. Set the

CONTROL ILLUM switch (on left s ide panel) to the LOW

position. Notice that the selected pushbuttons of the

R7704 and the plug-in units are illuminated.

31. Change the CONTROL ILLUM switch to the

HIGH position. Notice that the selected pushbuttons of

the R7704 and the plug-in units are illuminated at

maximum

(A) 2-9

Page 25

Readout

32. Note: This step applies only to instruments

equipped with the Readout System. Turn the READOUT

intensity control clockwise until an alpha-num eric display

is visible within the top or bottom division of the CRT

(reset the FOCUS adjustment if necessary for best

definition of the readout). Change the deflection factor of

the vertical unit that is selected for display. Notice that

the readout portion of the display changes as the

deflection factor is changed. Likewise, change the

sweep rate of the time-base unit which is selected for

display. Notice that the readout display for the time-bas e

unit changes also as the sweep rate is changed.

33. Set the time-base unit for magnified operation.

Notice that the readout display changes to indicate the

correct magnified sweep rate. If a readout-coded 10X

probe is available for use with the vertical unit, install it

on the input connector of the vertical plug-in. Notice that

the deflection factor indicated by the readout is increased

by 10 times when the probe is added. Return the timebase unit to normal sweep operation and disconnect the

probe.

34. Sequentially press all of the VERTICAL MODE

switch buttons and the HORIZONTAL MODE switch

buttons. Notice that the readout from a particular plug- in

occupies a specific location on the display area. If either

of the vertical plug-in units is a dual-tr ac e unit, notic e that

the readout for channel 2 appears within the lower

division of the CRT.

Beam Finder

35. Set the deflection factor of the vertical plug-in

which is displayed to 0.1 volt/division. Notice that a

square wave display is not visible since the deflection

exceeds the scan area of the CRT.

Operating Instructions-R7704

and release. Notice that the display remains within the

viewing area.

Z-Axis Input

38. If an external signal is available (five volts peak to peak minimum), the function of the Z-AXIS INPUTS

can be demonstrated. Remove the BNC cap from the

HIGH SENSITIVITY connector (on r ear panel). Connect

the external signal to both the input connector of the

displayed vertical unit and the HIGH SENSITIVITY

connector. Set the sweep rate of the displayed time

base to display about five cycles of the waveform. Adjust

the amplitude of the signal generator until intensity

modulation is visible on the display (change the ver tical

deflection factor as neces sary to produce an on-scr een

display). The positive peaks of the waveform should be

blanked out and the negative peaks intens ified. Notice

that the setting of the intensity controls determines the

amount of intensity modulation that is visible.

39. Remove the BNC cap from the HIGH SPEED

connector. Disconnect the external signal from the

HIGH SENSITIVITY connector and reconnect it to the

HIGH SPEED connector. Again increase the am plitude

of the signal generator until trace modulation is appar ent

on the displayed waveform. Notice that a higher

amplitude signal is necessary to produce trace

modulation. Again, the positive peaks of the waveform

should be blanked out and the negative peaks

intensified. Also, notice that the setting of the intensity

controls affects the amount of trace modulation. The

major difference between these two methods of

obtaining trace modulation is that the HIGH

SENSITIVITY input is more s ensitive, but that the HIGH

SPEED input has a higher usable frequency range.

Replace the BNC caps on both Z-AXIS INPUTS.

36. Press the BEAM FINDER switch. Notice that the

display is returned to the viewing area in compressed

form. Release the BEAM FINDER switch and notic e that

the display again disappears from the viewing area. Pull

the beam finder outward so it locks in the "find" position.

Notice that the display is again returned to the viewing

area in compressed form, but that in this position it

remains on the viewing area as long as the BEAM

FINDER switch is locked in the outward position.

37. With the BEAM FINDER switch locked in the

outward position, increase the vertical and horizontal

deflection factor until the display is reduced to about two

divisions vertically and horizontally (when the time-base

unit is in the time-base mode, change only the deflection

factor of the vertical unit). Adjus t the position controls of

the displayed vertical unit and the time-base unit to

center 2-10 the compressed display about the center

lines of the graticule. Press the BEAM FINDER switch in

(A) 2-10

40. This completes the basic operating procedure

for the R7704. Instrument operations not explained

here, or operations which need further explanation are

discussed under General Operating Information.

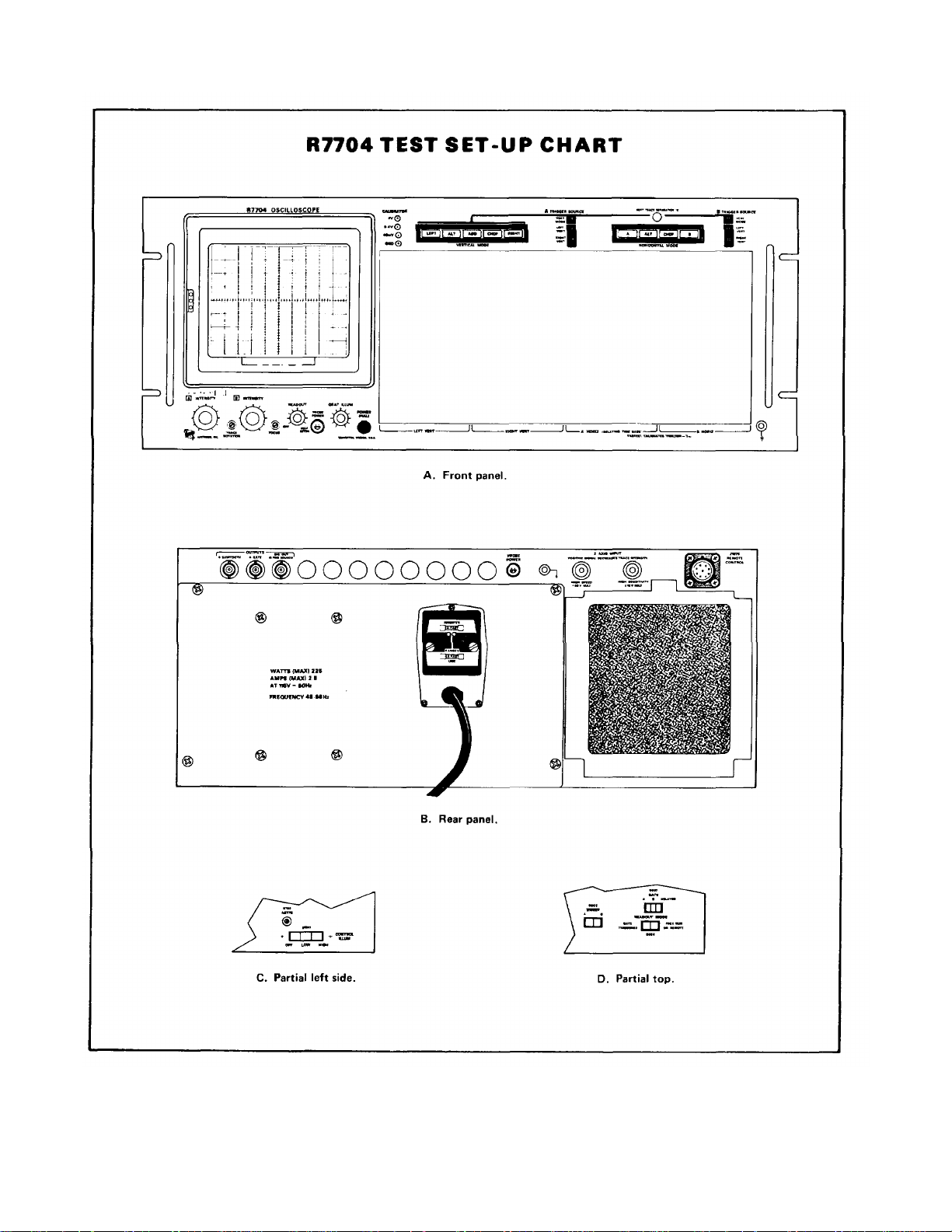

TEST SET-UP CHART

General

Fig. 2-3 shows the front, side, top, and rear panels of

the R7704. This chart may be reproduced and used as a

test setup record for spec ial m easurem ents, applic ations

or procedures, or it may be used as a training aid for

familiarization with this instrument.

GENERAL OPERATING INFORMATION

Simplified Operating Instructions

General. The following information is provided to aid

in quickly obtaining the correct setting for the R7704

controls

Page 26

Operating Instructions-R7704

(A)

Fig. 2-3.

Fig. 2-3.

2-11

Page 27

to present a display. The operator should be familiar with

the complete function and operation of this instrument as

described in this section before using this proc edure. For

detailed operating information for the plug-in units, see the

instruction manuals for the applicable units.

Single-Trace Display. The following procedur e will

provide a display of a single-trace vertical unit against one

time-base unit. For simplicity of explanation, the vertical

unit is installed in the LEFT VERT compartment and the

time-base unit is installed in the A HORIZ compartment.

Other compartments can be used if the following

procedure is changed accordingly.

1. Install 7A-series vertical units in both vertical plug-

in compartments.

2. Press the LEFT button of the VERTICAL MODE

switch.

3. Install a 7B-series time-bas e unit in the A HORIZ

compartment.

4. Press the A button of the HORIZONTAL MODE

switch.

5. Press the VERT MODE button of the A TRIGGER

SOURCE switch.

6. Set the POWER switch to ON. Allow several

minutes warmup.

7. Connect the signals to the input connectors of the

vertical units.

8. Set the vertical units for AC input coupling and

calibrated deflection factors.

9. Set the time-base unit for peak-to-peak auto,

internal triggering at a sweep rate of one

millisecond/division.

10. Advance the A INTENSITY control until a display

is visible (if display is not visible with A INTENSITY at

about midrange, press BEAM FINDER switch and adjust

the vertical deflection fac tor until the display is reduced in

size vertically; then center compressed display with vertical

and horizontal position controls; release BEAM FINDER).

Operating Instructions-R7704

11. Set the vertical deflection factor and vertical

position control for a display which remains within the

graticule area vertical.

12. If necessary, set the time-base triggering controls

for a stable display

13. Adjust the time-base position control so the

display begins at the left line of the graticule. Set the timebase sweep rate to display the desired number of cycles.

Dual-Trace Display. The following procedure will

provide a display of two single-trace vertical units agains t

one-time-base unit.

1. Install 7A-series vertical units in both vertical plug-

in compartments.

2. Press the LEFT button of the VERTICAL MODE

switch.

3. Install a 7B-series time-bas e unit in the A HORIZ

compartment.

4. Press the A button of the HORIZONTAL MODE

switch.

5. Press the VERT MODE button of the A TRIGGER

SOURCE switch.

6. Set the POWER switch to ON. Allow several

minutes warmup.

7. Connect the signals to the input connectors of the

vertical units.

8. Set the vertical units for AC input coupling and

calibrated deflection factors.

9. Set the time-base unit for peak-to-peak auto,

internal triggering at a sweep rate of one

millisecond/division.

10. Advance the A INTENSITY control until a display

is visible (if display is not visible with A INTENSITY at

about midrange, press BEAM FINDER switch and adjust

the vertical deflection fac tor until the display is reduced in

size vertically;

2-12 (A)

Page 28

Operating Instructions-R7704

then center compressed display with vertical and

horizontal position controls; release BEAM FINDER).

11. Set the left vertical unit deflection factor for a

display about four divisions in amplitude. Adjust the

vertical position control to move this display to the top of

the graticule area.

12. Press the RIGHT button of the VERTICAL

MODE switch.

13. Set the right vertical unit deflection factor for a

display which is about four divisions in amplitude (if

display cannot be located, use BEAM FINDER switch).

Position this display to the bottom of the graticule area

with the RIGHT VERT position control.

14. Press the ALT or CHOP button of the VERTICAL

MODE switch. A dual-trace display of the signal from the

LEFT VERT and RIGHT VERT plug-ins should be

presented on the CRT (for more inform ation on c hoice of

dual-trace mode, see Dual-Trace Displays in this

section).

15. If necessary, adjust the time-base triggering

controls for a stable display.

7. Connect the signal to the input connector of the

vertical unit.

8. Set the vertical unit for AC input coupling and

calibrated deflection factors.

9. Set both time-base units for peak-to-peak auto,

internal triggering at a sweep rate of one millisecond/

division.

10. Advance the A INTENSITY control until a display

is visible (if display is not visible with A INTENSITY at

midrange, press BEAM FINDER switch and adjust

vertical deflection factor until display is reduced in size

vertically; then center compressed display with vertical

position control; release BEAM FINDER).

11. Set the vertical unit for a display about four

divisions in amplitude and move the display to the top of

the graticule area with the vertical position controls.

12. If necessary, set the A time-base unit for s table

triggering.

13. Set the A time-base sweep rate for the desired

display.

16. Adjust the time-base position control so the

display begins at the left graticule line. Set the time-base

sweep rate for the desired horizontal display.

Dual-Sweep Display. The following procedure will

provide a dual-sweep display of a single-trace vertical

unit against two time-base units.

1. Install a 7A-series vertical unit in the LEFT VERT

compartment.

2. Press the LEFT button of the VERTICAL MODE

switch.

3. Install 7B-series time-base units in both the A

and B HORIZ compartments.

4. Press the A button of the HORIZONTAL MODE

switch.

5. Press the VERT MODE buttons of the A and B

TRIGGER SOURCE switches.

6. Set the POWER switch to ON. Allow several

minutes warmup.

14. Press the B button of the HORIZONTAL MODE

switch.

15. Advance the B INTENSITY control until a display

is visible (if display is not visible with B INTENSITY at

midrange, press BEAM FINDER switch and adjust the

vertical deflection factor until display is reduced in size

vertically; then center compressed display with vertical

position control; release BEAM FINDER).

16. If necessary, set the B time-base unit for s table

triggering.

17. Set the B time-base unit sweep rate for the

desired display.

18. Press the ALT or CHOP button of the

HORIZONTAL MODE switch (see Dual-Sweep Displays

in this section for further information on selecting sweep

mode).

(A) 2-13

Page 29

Operating Instructions-R7704

19. Adjust the VERT TRACE SEPARATION (B)

control to position the trace produced by the B time-base

unit with respect to the trace produced by the A timebase unit.

Dual Trace-Dual Sweep Displays. The following

procedure will provide a dual-trace, dual-sweep display

of two single-trace vertical units against two time-base

units (four traces displayed on CRT).

1. Install 7A-series vertical units in both vertical

compartments.

2. Press the LEFT button of the VERTICAL MODE

switch.

3. Install 7B-series time-base units in both

horizontal compartments.

4. Press the B button of the HORIZONTAL

DISPLAY switch.

5. Press the VERT MODE buttons of the A and B

TRIGGER SOURCE switches.

6. Set the POWER switch to ON. Allow several

minutes warmup.

7. Connect the signals to the input connectors of

the vertical units.

8. Set the vertical units for AC input coupling and

calibrated deflection factors.

9. Set both time-base units for peak-to-peak auto,

internal triggering at a sweep rate of one millisecond/

division.

10. Advance the B INTENSITY control until a display

is visible (if display is not visible with B INTENSITY at

midrange, press BEAM FINDER switch and adjust the

LEFT VERT deflection factor until display is reduced in

size vertically; then center compressed display with

LEFT VERT position controls; release BEAM FINDER).

11. Set the LEFT VERT deflection factor for a

display which is about two divisions in amplitude and

position the display to the top of the graticule area.

12. If necessary, adjust the B time-base unit

triggering controls for a stable display.

13. Position the start of the trace to the left gratic ule

line with the B time-base unit position control. Set the B

time-base unit sweep rate for the desired display.

14. Press the RIGHT button of the VERTICAL

MODE switch and the A button of the HORIZONTAL

MODE switch.

15. Advance the A INTENSITY control until a display

is visible (if display is not visible with A INTENSITY at

midrange, press BEAM FINDER switch and adjust the

RIGHT VERT deflec tion factor until display is reduced in

size vertically; then center compressed display with

RIGHT VERT position control; release BEAM FINDER).

16. Set the RIGHT VERT deflection factor for a