Page 1

TCL OVERSEAS HOLDINGS LIMITED Service Manual

3

SERVICE MANUAL FOR M28 ONE-CHIP CHASSIS

PART I. Servicing Precautions

When working, the unit is with high voltage about 25KV inside. So, to avoid the risk of electric shock,

be careful to adjust the chassis!

1. Only qualified personnel should perform service procedures.

2. All specification must be met over line voltage ranger of 110V AC to 240V AC 50Hz/60Hz.

3. Do not operate in WET/DAMP conditions.

4. Portions of the power supply board are hot ground. The remaining boards are cold ground.

5. Discharge of CRT anode should be done only to CRT ground strap.

6. When fuse blow, ensure to replace a fuse with the same type and specification.

7. Keep the wires away from the components with high temperature or high voltage.

8. When replacing the resister with high power, keep it over the PCB about 10mm.

9. The CRT anode high voltage has been adjusted and set in the factory. When repairing the chassis,

do not make the high voltage exceed 27.5KV (The beam current is 0uA). Generally, the high voltage

is set on 25.5KV±1.5KV (The beam current is 700uA).

* The values of parameters above are for information only.

10. Before return the fixed unit, do check all the covering of wires to ensure that not fold or not short

with any metal components. Check the entire protection units, such as control knobs, rear cabinet &

front panel, insulation resister & capacitor, mechanical insulators and so on.

11. There are some mechanical and electrical parts associating with safety (EMC) features (Generally

related to high voltage or high temperature or electric shock), these features cannot be found out from

the outside. When replace these components, perhaps the voltage and power suit the requirements, but

efficient X-ray protection may not be provided. All these components are marked with Ì in the

schematic diagram. When replace these, you’d better look up the components listed in this manual. If

the component you replaced not has the same safety (EMC) performance, harmful X-ray may be

produced.

Page 2

4

Service Manual TCL OVERSEAS HOLDINGS LIMITED

PART II -Product Specification

1. Ambient Conditions:

1.1 Ambient Temperatures:

a. Operating: -10 ~ +40ćć

b. Storage: -15 ~ +45ćć

1.2 Humidity

a. Operation: <80%

b. Storage: <90%

1.3 Air Pressure: 86kpa ~ 106kpa

2. GENERAL SPECIFICATION

2.1 MPU & Chroma IC: TMPA8803CSN (One-Chip)

2.2 TV Broadcasting System

PAL DK/BG

SECAM DK/BG

NTSC 3.579/4.43 AV MODE

2.3 Scanning Lines & Frequencies

525/625 lines

15.625KHz/15.75KHz

50/60Hz

2.4 Color Sub-Carrier: 4.433MHz/3.579MHz

2.5 IF: Picture 38.9MHz Sound 5.5/6.5MHz

2.6 Power Consumption: 80W

2.7 Power Supply: AC 220V 50Hz±10%

2.8 Audio Output Power (7%THD): 4W + 4W

2.9 Aerial Input Impedance: 75 Unbalanced Din Jack Ant.Input

2.10 Product Safety Requirement: VDE Approval

2.11 Product EMC/EMI Requirement: FTZ Approval

3. Basic Features of Controller

3.1 Channel Tuning Method: Voltage Synthesizer

Page 3

TCL OVERSEAS HOLDINGS LIMITED Service Manual

3.2 Presettable Program: 100 Programs

3.3 Tuning for VHF and UHF Bands: Auto/Manual/Fine Tuning

3.4 Picture and Sound Adjustment

Bright, Contrast, Color and Volume Control

TINT Control (NTSC)

Sharpness Control

3.5 OSD

General Features (Volume, Brightness, Contrast, Color, Program, Band, Auto Search, Manual,

Tune, Muting, AV and Sleep Timer)

NICAM and Dual Language

German Stereo Indicator

3.6 Sleep Timer: 10-120 Minutes with 10Min.Increment

5

3.7 Auto Off When No Broadcasting Signal: 15 min

3.8 Full Function Infrared Remote Control

3.9 Remote Effective Distance: 8m

4. Construction of Front Panel

Main Power Switch

Remote Sensor

Standby Indicator

Menu Select

TV/AV Select

Program and Volume Up/Down

5. Construction of Real Panel

75 Aerial Terminal

RCA Socket –Audio-R+L In/Out, Video- In/Out

Y/U/V Input

6. Other Information

6.1 Colour Temperature: 9300K X=284 Y=299

6.2 Magnetic Field: Bv=0.2~0.5Gs

Page 4

6

Service Manual TCL OVERSEAS HOLDINGS LIMITED

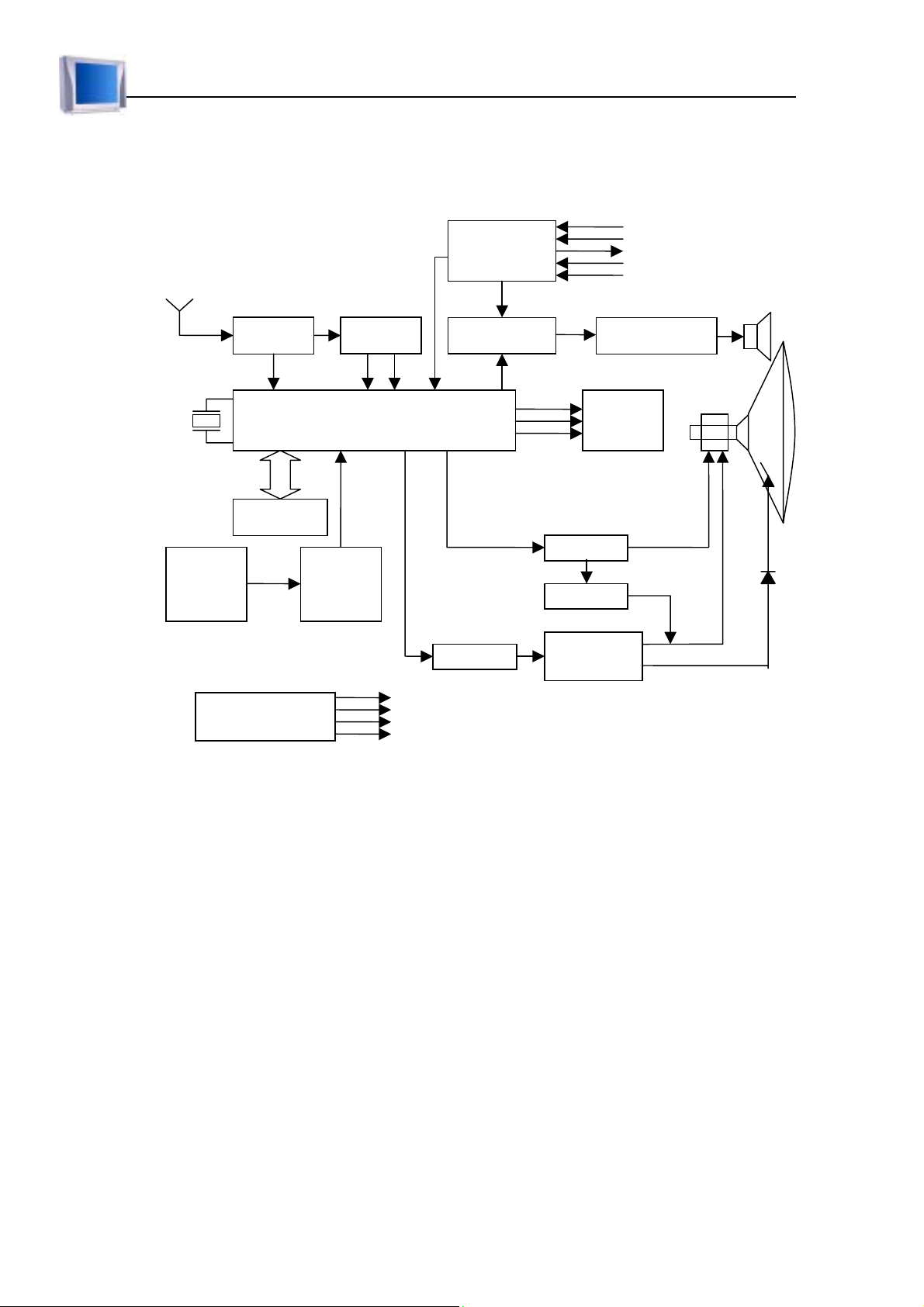

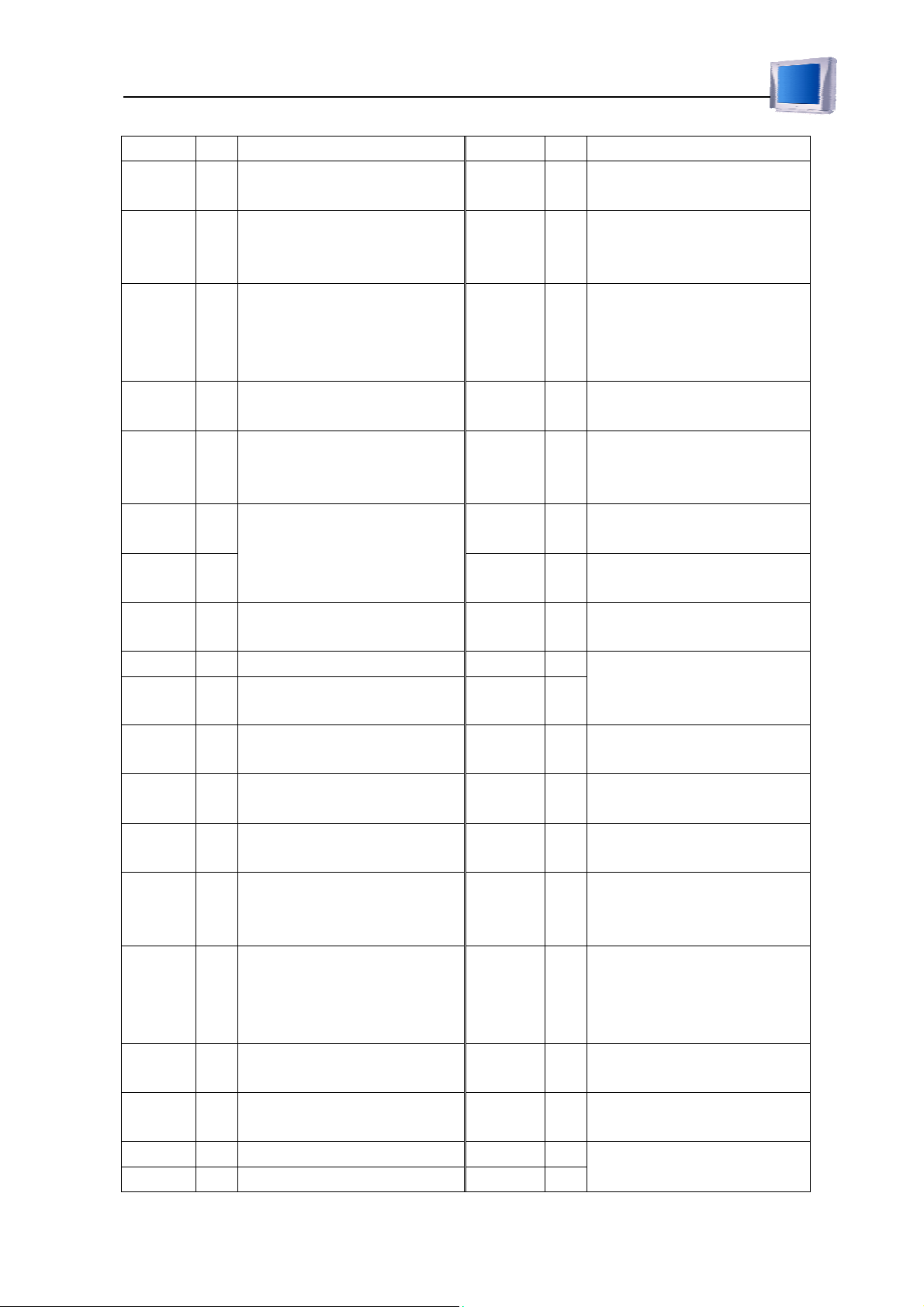

PART III. Brief Introduction on Chassis

AV INPUT/

OUTPUT

RF IN

XTAL

OSC

INFRARED

REMOTE

CONTROL

TUNER SAW

TMPA8803CPN(M28)

I2C BUS

E2PROM

REMOTE

CONTROL

RECEIVER

SWITCH POWER

MC44608

NICAM BD

H DRIVE

R/G/B

V OUTPUT

DPC

H OUTPUT

AUDIO AMP

CRT

DRIVE

FBT

The TV signal is amplified by the frequency mixing circuit of the tuner. Then the tuner output PIF and

SIF signals. The IF signals are amplified about 20dB by the pre IF amplifier (Q101). Having passed

the SAW, the IF signals go into the TMP8803CPN from pin ƻ

42

, ƻ41. The IF signal pass the video

detect circuit to generate CVBS signal. Then the processor deals the signal with luminance and

chroma separation. The processor deals the luminance signal with Y-Delay, Y-Gamma correction, Y-hf

compensation and black strength, all which ensure that there are enough bandwidth and gain with Y

signal, so that the resolution of picture detail is improved and the Y signal is well timed with chroma

signal. The processor also deals the chroma signal with chroma sub-carrier recovery, color system

recognition and color signal decoding, then outputs B-Y and R-Y color difference signal. A matrix

circuit converts the color difference signal (Y, B-Y and R-Y) into primary color signal (R/G/B). On the

other hand, the processor separated the horizontal and vertical sync signal from the CVBS signal

which was generated by video detect circuit. Having passed the horizontal (or vertical) frequency

dividing circuit, the H (or V) OSC signal, which be generated by H-AFC (or V-AFC), is changed to H

(or V) drive signal. The H/V drive signal make the horizontal/vertical circuits and scan output circuit

to generate H/V saw tooth wave

Page 5

TCL OVERSEAS HOLDINGS LIMITED Service Manual

1.Channel Section

The RF signal is converted into IF signal by the tuner. Then the IF signal cross the IF amplifier circuit

(pre IF amplifier) to get a gain about 15dB. By the coupling capacitance (c110) and the match

resistance (R114 56), the input resistance of the pre-IF amplifier match with the tuner. The si gnals

pass a parallel connection circuit with voltage NFB, which combines the advantages of low output

impedance, of wide dynamic range and of less components. R116 is a voltage NFB component, which

is used to adjust the gain in the pass band. Having been amplified by the IF amplifier, the IF signal

pass a SAW, and then come into TMPA8803CSN from pin41 and pin42 with balance. The processor

deal the IF signal with IF detection, PLL demodulation, IF AGC, AFC, video peak detection, and color

system recognition etc., then output a AGC signal from pin 43 to the tuner to adjust the input

amplitude of IF signal. R217, C218 and C219 make up of picture IF PLL circuit, which is used to

control IF detection. IC201 output a sound IF signal from pin 31 and a video signal, which will be

amplified by Q209, from pin30. The processor output a sound system control signal to Q208. If the

processor output a high level from pin59 (sound detection), Q208 is on, and a video signal is separated

from the IF signal by a trap. With capacitance coupling, the video signal comes into IC201 from pin26,

and then it is selected by inner switches and output from pin45. Having come out, the video signal will

be amplified by Q210, and a sync signal will be separated by a sync separate circuit which is made up

by C208, Q202 and Q203. Then the video come into inner 870X CPU module from IC201 pin62 to

detect whether the signal is live signal.

7

Tuning control and band switch control circuits

The processor output a tuning control signal from pin60. The control signal will pass Q103 common

emitter amplifying circuit, then an integrating circuit. Finally, it is added to the VT terminal to provide

all channels’ tuning voltage for the tuner to stabilize the channels.

2.Vertical Output Section

TMPA8803CSN outputs vertical saw-tooth wave from pin 16. It come to pin5 of LA7840 with DC

coupling, and is amplified by inner difference amplifier. Pin4 of LA7840 is the same phase input

terminal. R307 and R308 are DC offset resistances. C305 is a filter capacitor. In application to M28,

pin4 of la7840 is fixed as the DC amplify ref terminal. The amplified saw tooth wave come out la7840

from pin2 and make the deflect coil to generate the deflect current. R314 and C301 filtrate the

inductive interference from the horizontal deflect coil. R317 and C309 are used to eliminate spurious

oscillation generated by the deflect coil and distributed capacitance resonance. C308, R313, C307 and

accessory circuit are in charge of draw AC saw tooth wave out at the deflect coil terminal connected

with R315 & R316, and feedback to the input terminal of la7840 (pin5) to correct the linearity of

horizontal scan. C306 is a high frequency decoupling capacitor. D301 and C303 make up of a voltage

pump up circuit. La7840 output a vertical kickback impulse from pin7 to locate the OSD characters.

3.Horizontal Output Section

The processor outputs horizontal drive impulse from pin 13. The drive impulse is done with voltage

division by R238 and R401, and then comes to the base of the drive triode (Q401). C401 is used to

eliminate the noise in the H drive impulse. T401 is a horizontal drive transformer. Q402 is a horizontal

output triode with a damper inside. L402 is connected with the emitter of the horizontal output diode

to eliminate the radiation and to improve the distortions at the cross of vertical and horizontal white

Page 6

8

Service Manual TCL OVERSEAS HOLDINGS LIMITED

lines. C406 and C402 are retrace capacitors and C421 is an s-correct capacitor. L441 and L442 are

horizontal linear inductors. R441 is used to eliminate the parasitic oscillation caused by horizontal

linear inductors. C420, R413 and D411 are used to correct the M-distortion in horizontal direction.

C422, R415 and R415A are coupling components for the horizontal retrace impulse, which are feed

back to pin 12 of TMPA8803CSN. D404 is a negative peak-killer diode.

Horizontal scanning distortion and the method to compensate it

The deflect coil and the horizontal output triode have some resistance R while they are ducting. The

resistance R will cause the non-linear distortion, which means that the right direction scanning speed

of the electron beam becomes slower, and the right of the raster is compressed to generate distortion.

We use a horizontal linear adjuster to compensate this kind of distortion. We use L412 and L411 as the

H linear adjusters in H scanning section of M28 chassis. R411, which is parallel connected with L411

and L412, is a despiking resistance for preventing the oscillation by compensating inductor and the

stray capacitance. The lin ear adjuster is a transductor coi l with a magnetic core inside. If the curren t,

which pass the linear adjuster coil, increase to a certain value, the magnetic core becomes saturated to

decrease the inductance of the linear adjustment inductor. If the +B is steady, the increase speed of Iy

is faster to compensate the reducing of deflecting current by the resistance R mention above.

We can adjust the magnetic core to chang the inductance of the linear compensate inductor to adjust

the H linearity.

The EHT generation circuit

The FBT supply the anode high voltage, focus voltage and screen voltage for M28 chassis. D401 and

C408 are in charge of regulating the primary impulse of the transformer to output a voltage of 190V

for the video amplifiers. The ( 10 ) ~ ( 8 ) coils of the FBT supply the heater with power. Having

passed the divider and clipping circuits, whi ch are maded up by R415, R415A, C422 and D404, the

H retrace impulses getting out from ( 3 ) ~ ( 10 ) coils are inputed to pin12 of TMPA8803CSN to

generate sand castle impulse.

To limit the beam current in a safe range, we add a ABL circuit in M28 chassis. We add two sampling

resistances (R414, R415) between +24V power supply and pin7 of the FBT. The voltage at the joint of

the two resistances is feed back to pin27 of TMPA8803CSN to control bright and contrast to limit the

beam current. It is also in charge of regulating EHT. C410 is a fliter capacitor for ABL voltage.

The impulses, which are induced by secondary coil 5, are changed to 12V once passed the regulating

and fliting circuit made up by D402 and C413. IC401 change 12V power supply to 9V for many

circuits, such as R/G/B output circuit of TMPA8803CSN, IC4053, pre IF-amplifier circuit, bright dots

killer circuit and S terminal circuit. IC402 outputs a 5V power supply for the keyboard circuit. C418,

C417, C423 and C425 are fliter capacitors. D402 and C413 are incharge of regulating and flitering for

the output of coil6 to supply the V scanning output section with 24V power. The 24V is added to the

upper terminal of the V deflecting yoke as the DC bias for the movement of V center.

Extension distortion and compensation

This kind of distortion is mainly caused by the structure of CRT. Due to the srcreen of SF CRT is not a

ture flat screen, the distances from the deflecting center to the screen are not the same. The scanning

speed of the electron beam is uniform. If the electron beam scannning the screen equally with the

Page 7

TCL OVERSEAS HOLDINGS LIMITED Service Manual

effect of ture linear sawtooth current, the E-W sides of the picture are stretched. That is the extension

distortion. Usually, we add a S-correct capacitor in series with the deflecting coil to compensate this

kind of distortion. The integral character of S-correct capacitor make the current waveform S shape.

So the scanning speed of electron beam at the center of screen is faster than the one at the side. So this

action can correct the extension distortion. C421 is a S-correct capacitor. The capacitance is inverse

ratio with the correcting effect.

9

Page 8

10

Service Manual TCL OVERSEAS HOLDINGS LIMITED

PART IV. IC Pin Description

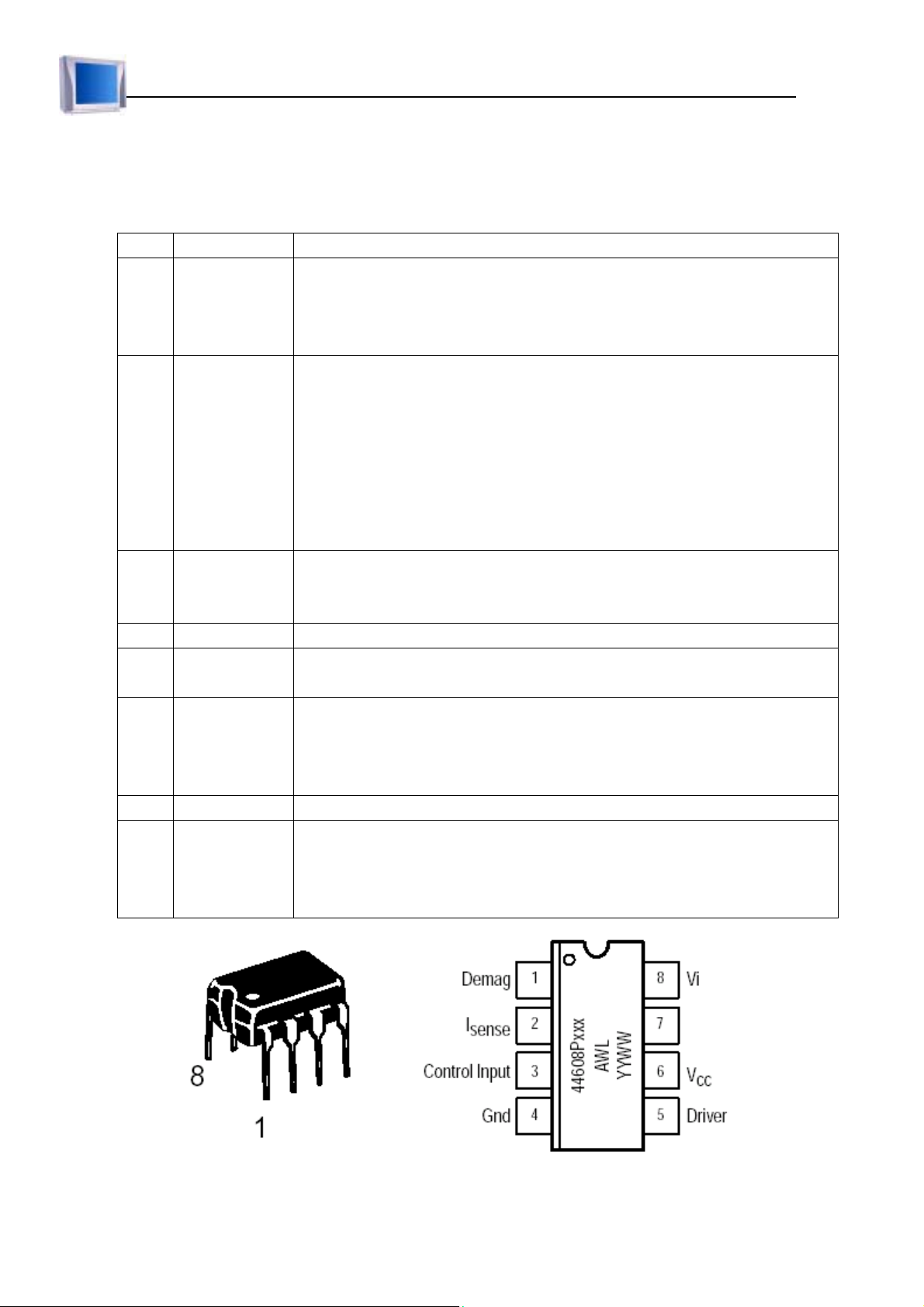

1. MC44608-High Voltage PWM Controller

Pin Name Description

The Demag pin offers 3 different functions: Zero voltage crossing detection

1 Demag

I

2

3

sense

Control Input

4 Ground This pin is the ground of the primary side of the SMPS.

5Driver

V

6

CC

7 This pin is to provide isolation between the Vi pin 8 and the VCC pin 6.

8V

i

(50mV), 24 A current detectionǂ and 120 A current detection. The 24 Aǂǂ

level is used to detect the secondary reconfiguration status and the 120 A level ǂ

to detect an Over Voltage status called Quick OVP.

The Current Sense pin senses the voltage developed on the series resistor

inserted in the source of the power MOSFET. When Isense reaches 1V, the

Driver output (pin 5) is disabled. This is known as the Over Current Protection

function. A 200 A current source is flowing out of the pin 3 during theǂ

start–up phase and during the switching phase in case of the Pulsed Mode of

operation. A resistor can be inserted between the sense resistor and the pin 3,

thus a programmable peak current detection can be performed during the SMPS

stand–by mode.

A feedback current from the secondary side of the SMPS via the opto–coupler is

injected into this pin. A resistor can be connected between this pin and GND to

allow the programming of the Burst duty cycle during the Stand–by mode.

The current and slew rate capability of this pin are suited to drive Power

MOSFETs.

This pin is the positive supply of the IC. The driver output gets disabled when

the voltage becomes higher than 15V and the operating range is between 6.6V

and 13V. An intermediate voltage level of 10V creates a disabling condition

called Latched Off phase.

This pin can be directly connected to a 500V voltage source for start–up

function of the IC. During the Start–up phase a 9 mA current source is internally

delivered to the VCC pin 6 allowing a rapid charge of the VCC capacitor. As

soon as the IC starts–up, this current source is disabled.

Page 9

TCL OVERSEAS HOLDINGS LIMITED Service Manual

OPERATING DESCRIPTION

11

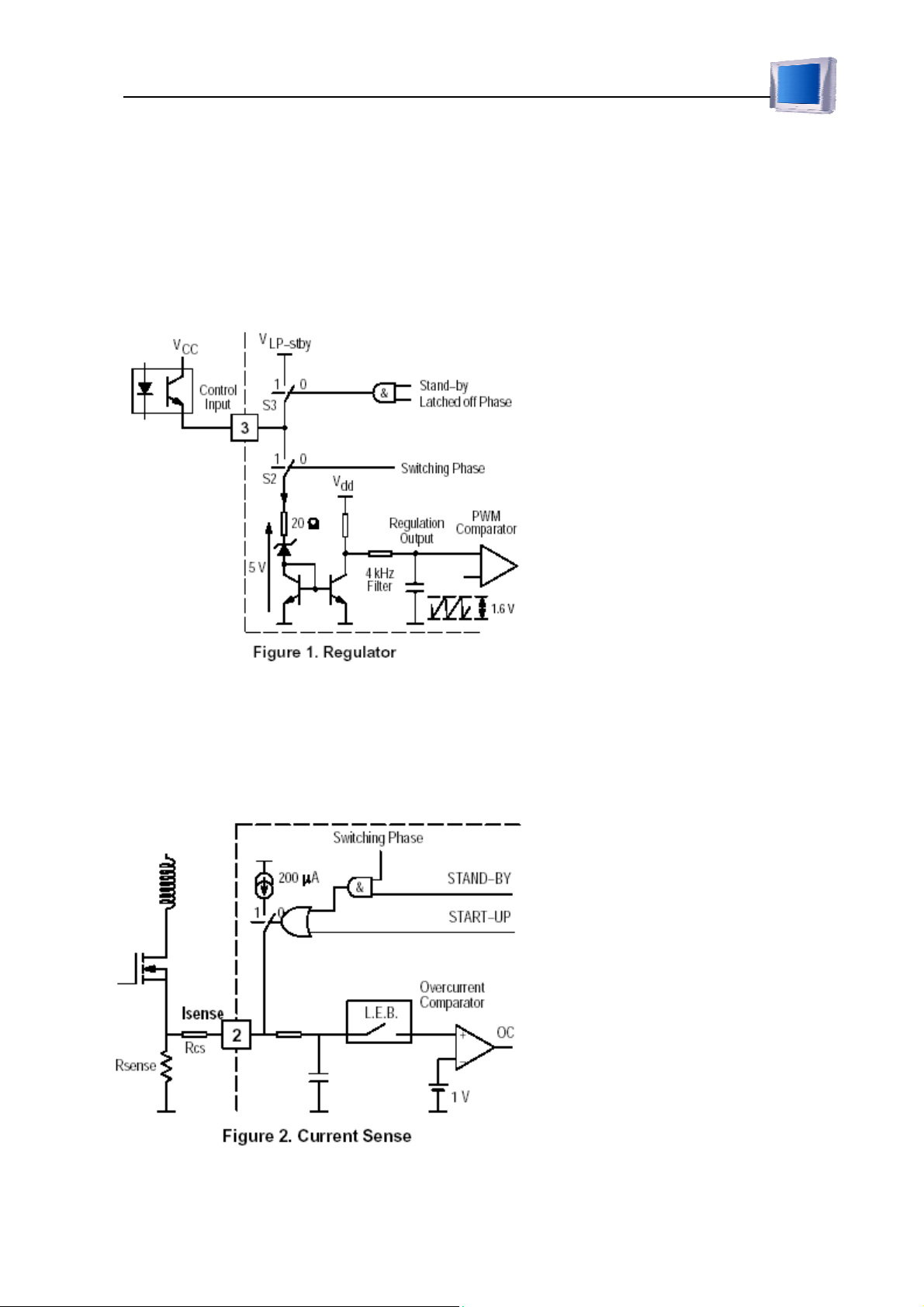

Regulation

The pin 3 senses the feedback current provided by the opto-coupler. During the switching phase the

switch S2 is closed and the shunt regulator is accessible by the pin 3. The shunt regulator voltage is

typically 5V. The dynamic resistance of the shunt regulator represented by the zener diode is 20:.

The gain of the Control input is given on Figure 10 which shows the duty cycle as a function of the

current injected into the pin 3.

A 4KHz filter network is inserted

between the shunt regulator and the

PWM comparator to cancel the high

frequency residual noise.

The switch S3 is closed in Stand–by

mode during the Latched Off Phase

while the switch S2 remains open. (See

section PULSED MODE DUTY

CYCLE CONTROL).

The resistor Rdpulsed (Rduty cycle

burst) has no effect on the regulation

process. This resistor is used to

determine the burst duty cycle described in the chapter “Pulsed Duty Cycle Control” on page 8.

PWM Latch

The MC44608 works in voltage mode. The on–time is controlled by the PWM comparator that

compares the oscillator sawtooth with the regulation block output.

The PWM latch is initialized by the

oscillator and is reset by the PWM

comparator or by the current sense

comparator in case of an over current.

This configuration ensures that only a

single pulse appears at the circuit

output during an oscillator cycle.

Current Sense

The inductor current is converted to a

positive voltage by inserting a ground

reference sense resistor R

Sense

in series

with the power switch.

The maximum current sense threshold is fixed at 1V. The peak

current is given by the following

Page 10

12

Service Manual TCL OVERSEAS HOLDINGS LIMITED

equation:

Ipk

max

= 1/R

(:) (A)

sense

In stand–by mode, this current can be lowered as due to the activation of a 200PA current source:

Ipk

MAX-STBY

The current sense input consists of a filter (6k:, 4pF) and of a leading edge blanking. Thanks to that,

this pin is not sensitive to the power switch turn on noise and spikes and practically in most

applications, no filtering network is required to sense the current.

Finally, this pin is used:

– as a protection against over currents (I

sense

> I)

– as a reduction of the peak current during a Pulsed Mode switching phase.

The overcurrent propagation delay is reduced by producing a sharp output turn off (high slew rate).

This results in an abrupt output turn off in the event of an over current and in the majority of the

pulsed mode switching sequence.

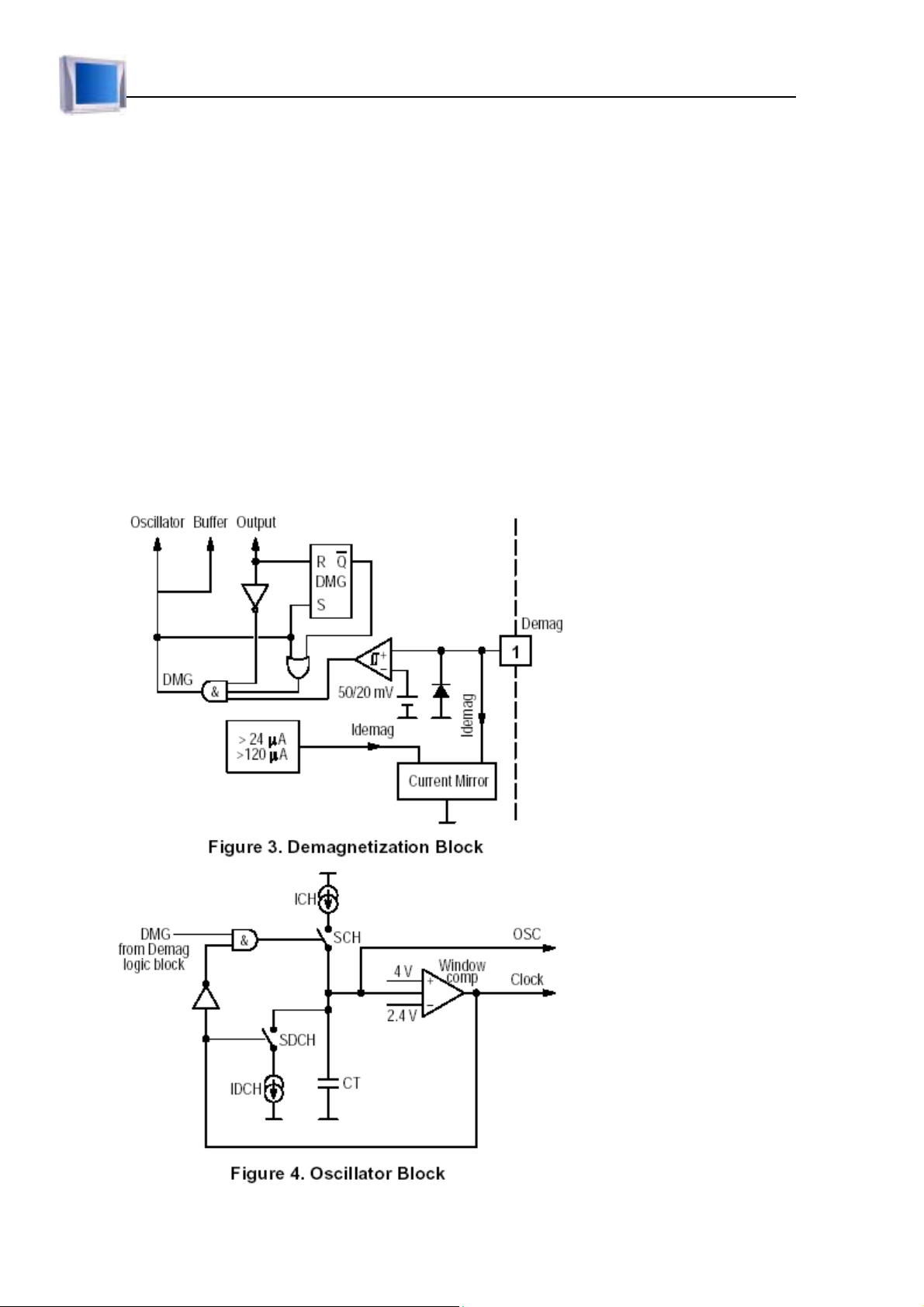

Demagnetization Section

The MC44608 demagnetization

detection consists of a

comparator designed to compare

the V

winding voltage to a

CC

reference that is typically equal

to 50mV.

This reference is chosen low to

increase effectiveness of the

demagnetization detection even

during start–up.

A latch is incorporated to turn

the demagnetization block

output into a low level as soon

as a voltage less than 50 mV is

detected, and to keep it in this

state until a new pulse is

generated on the output. This

avoids any ringing on the input

signal which may alter the

demagnetization detection.

For a higher safety, the

demagnetization block output is

also directly connected to the

Page 11

TCL OVERSEAS HOLDINGS LIMITED Service Manual

13

output, which is disabled during the demagnetization phase.

The demagnetization pin is also used for the quick, programmable OVP. In fact, the demagnetization

input current is sensed so that the circuit output is latched off when this current is detected as higher

than 120PA.

This function can be inhibited by grounding it but in this case, the quick and programmable OVP is

also disabled.

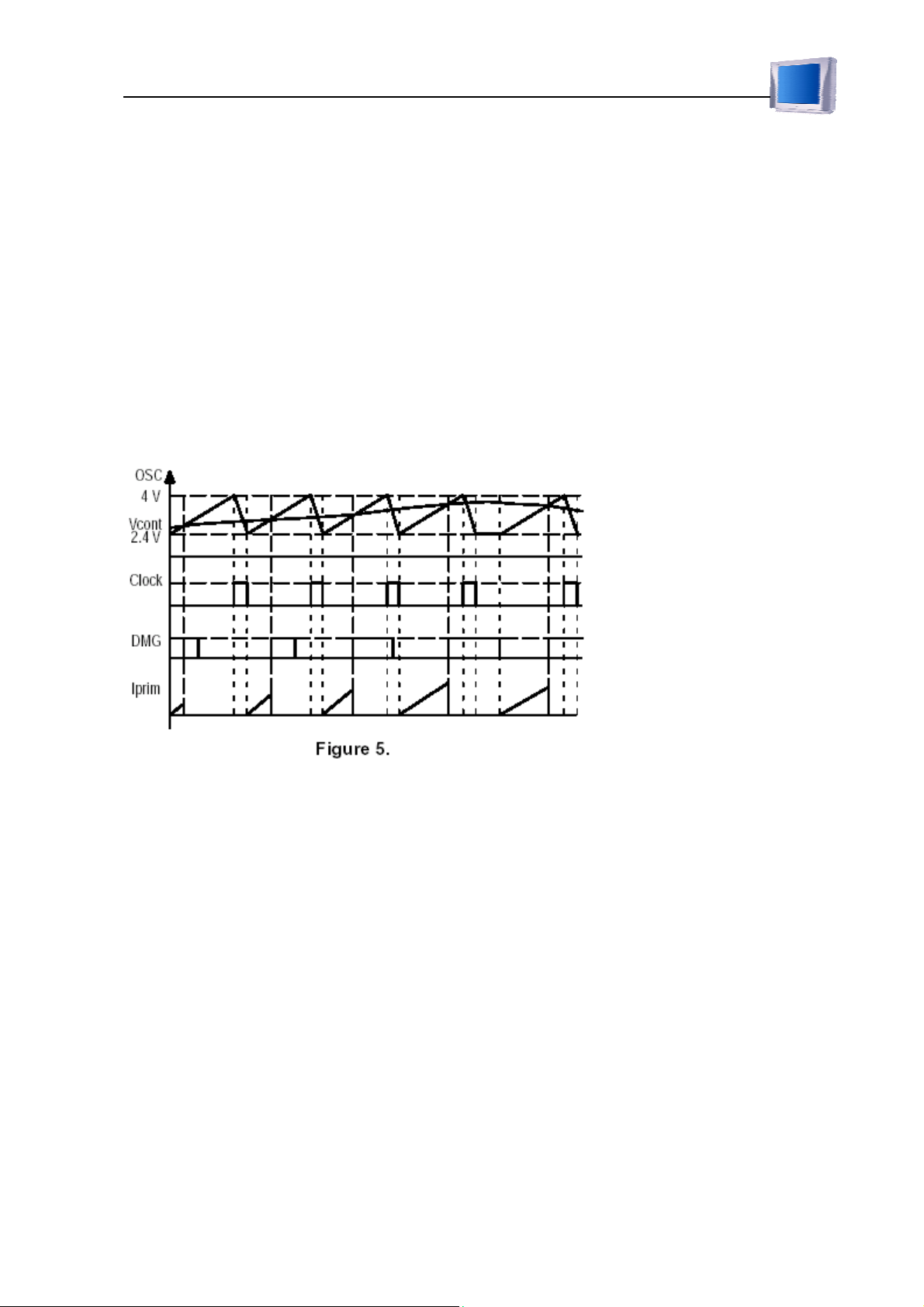

Oscillator

The MC44608 contains a fixed frequency oscillator. It is built around a fixed value capacitor CT

succesively charged and discharged by two distinct current sources ICH and IDCH. The window

comparator senses the CT voltage value and activates the sources when the voltage is reaching the

2.4V/4V levels.

The complete

demagnetization status

DMG is used to inhibit the

recharge of the CT capacitor.

Thus in case of incomplete

transformer demagnetization

the next switching cycle is

postpone until the DMG

signal appears. The

oscillator remains at 2.4V

corresponding to the

sawtooth valley voltage. In

this way the SMPS is

working in the so called SOPS mode (Self Oscillating Power Supply). In that case the effective

switching frequency is variable and no longer depends on the oscillator timing but on the external

working conditions (Refer to DMG signal in the Figure 5).

The OSC and Clock signals are provided according to the Figure 5. The Clock signals correspond to

the CT capacitor discharge. The bottom curve represents the current flowing in the sense resistor Rcs.

It starts from zero and stops when the sawtooth value is equal to the control voltage Vcont. In this way

the SMPS is regulated with a voltage mode control.

Overvoltage Protection

The MC44608 offers two OVP functions:

– a fixed function that detects when V

is higher than 15.4V

CC

– a programmable function that uses the demag pin. The current flowing into the demag pin is

mirrored and compared to the reference current Iovp (120PA). Thus this OVP is quicker as it is not

impacted by the V

inertia and is called QOVP.

CC

In both cases, once an OVP condition is detected, the output is latched off until a new circuit

Page 12

14

Service Manual TCL OVERSEAS HOLDINGS LIMITED

START–UP.

Start–up Management

The Vi pin 8 is directly connected to the HV DC rail Vin. This high voltage current source is

internally connected to the

pin and thus is used to

V

CC

charge the V

capacitor. The

CC

VCC capacitor charge period

corresponds to the Start–up

phase. When the V

voltage

CC

reaches 13V, the high voltage

9mA current source is

disabled and the device starts

working. The device enters

into the switching phase.

It is to be noticed that the maximum rating of the Vi pin 8 is 700V. ESD protection circuitry is not

currently added to this pin due to size limitations and technology constraints. Protection is limited by

the drain–substrate junction in avalanche breakdown. To help increase the application safety against

high voltage spike on that pin it is possible to insert a small wattage 1k: series resistor between the

Vin rail and pin 8.

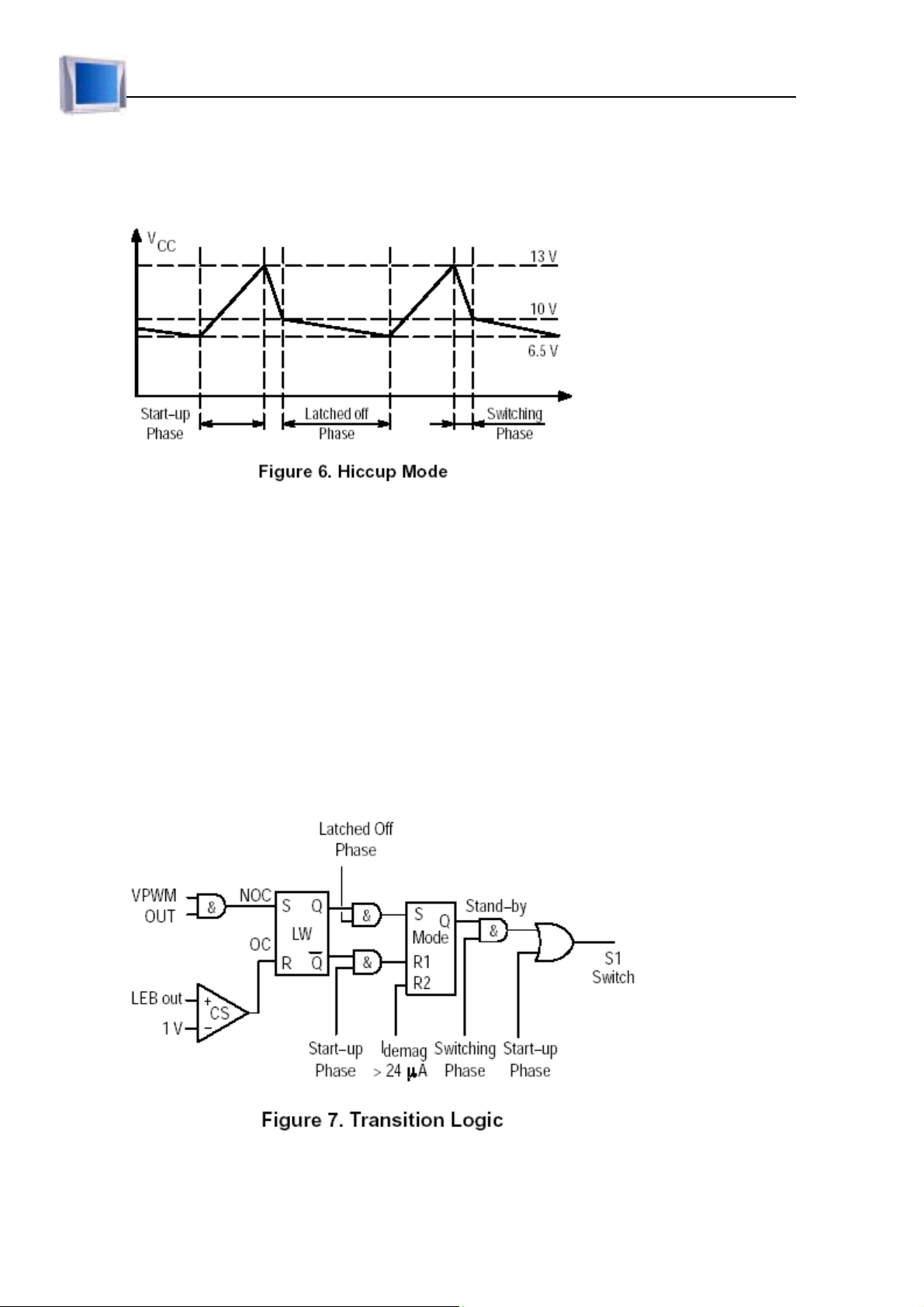

The Figure 6 shows the V

into the V

pin during the switching phase. This case can be encountered in SMPS when the self

CC

voltage evolution in case of no external current source providing current

CC

supply through an auxiliary winding is not present (strong overload on the SMPS output for example).

The Figure 16 also depicts this working configuration.

In case of the hiccup mode, the duty cycle of the switching phase is in the range of 10%.

Mode Transition

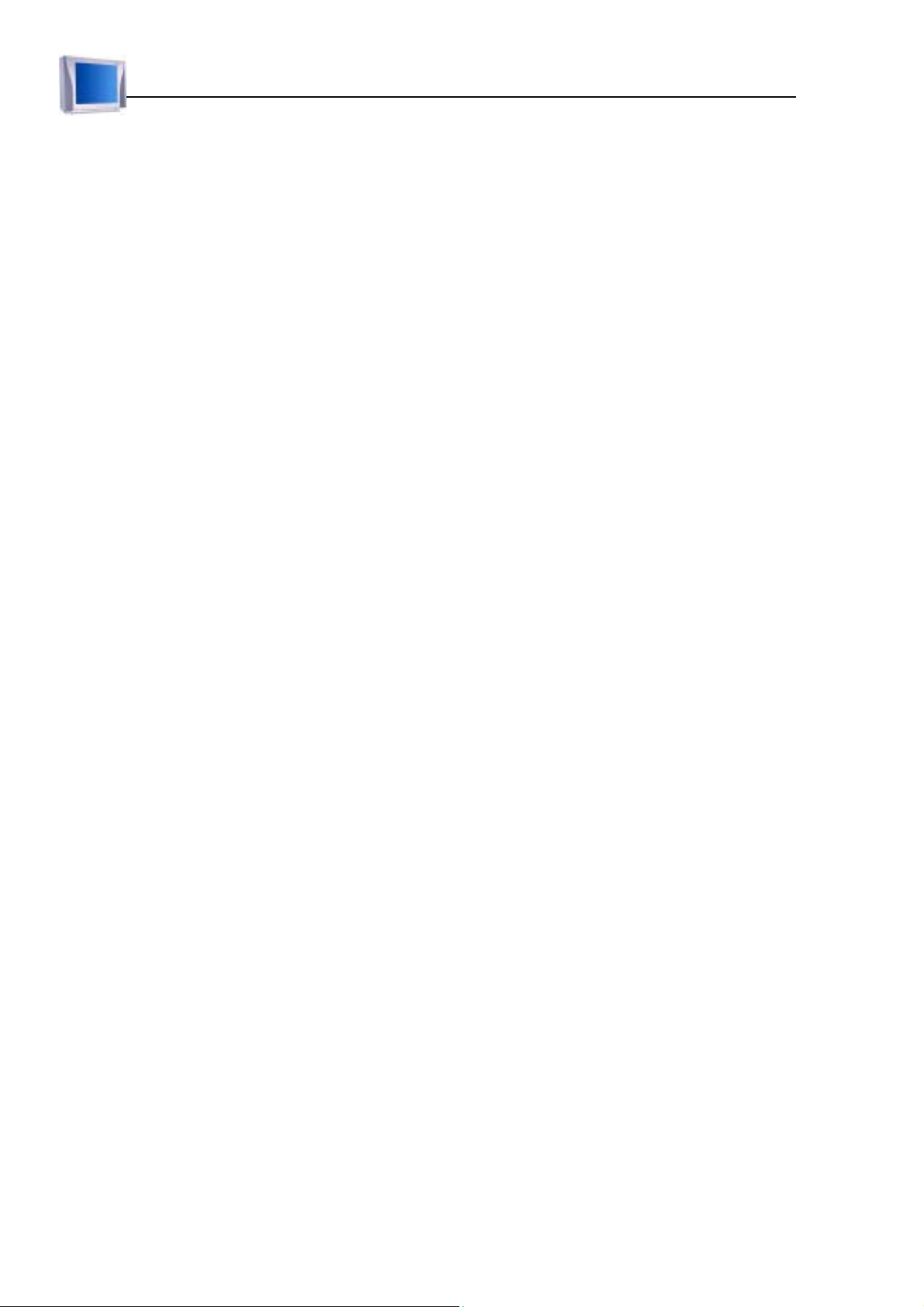

The LW latch Figure

7 is the memory of

the working status at

the end of every

switching sequence.

Two different cases

must be considered

for the logic at the

termination of the

SWITCHING

PHASE:

1. No Over Current

was observed

Page 13

TCL OVERSEAS HOLDINGS LIMITED Service Manual

15

2. An Over Current was observed

These 2 cases are corresponding to the signal labeled NOC in case of “No Over Current” and “OC” in

case of Over Current. So the effective working status at the end of the ON time memorized in LW

corresponds to Q=1 for no over current and Q=0 for over current.

This sequence is repeated during the Switching phase.

Several events can occur:

1. SMPS switch OFF

2. SMPS output overload

3. Transition from Normal to Pulsed Mode

4. Transition from Pulsed Mode to Normal Mode

1. SMPS SWITCH OFF

When the mains is switched OFF, so long as the bulk electrolithic bulk capacitor provides energy to

the SMPS, the controller remains in the switching phase. Then the peak current reaches its maximum

peak value, the switching frequency decreases and all the secondary voltages are reduced. The V

CC

voltage is also reduced. When VCC is equal to 10V, the SMPS stops working.

2. Overload

In the hiccup mode the 3 distinct phases are described as follows (refer to Figure 6):

The SWITCHING PHASE: The SMPS output is low and the regulation block reacts by increasing the

ON time (dmax = 80%). The OC is reached at the end of every switching cycle. The LW latch (Figure

7) is reset before the VPWM signal appears. The SMPS output voltage is low. The V

voltage cannot

CC

be maintained at a normal level as the auxiliary winding provides a voltage which is also reduced in a

ratio similar to the one on the output (i.e. Vout nominal / Vout short–circuit). Consequently the V

CC

voltage is reduced at an operating rate given by the combination VCC capacitor value together with the

I

working consumption (3.2mA) according to the equation 2. When VCC crosses 10V the

CC

WORKING PHASE gets terminated. The LW latch remains in the reset status.

The LATCHED–OFF PHASE: The V

capacitor voltage continues to drop. When it reaches 6.5V

CC

this phase is terminated. Its duration is governed by equation 3.

The START–UP PHASE is reinitiated. The high voltage start–up current source (–I

activated and the MODE latch is reset. The V

voltage ramps up according to the equation 1. When it

CC

= 9mA) is

CC1

reaches 13V, the IC enters into the SWITCHING PHASE.

The NEXT SWITCHING PHASE: The high voltage current source is inhibited, the MODE latch

(Q=0) activates the NORMAL mode of operation. Figure 2 shows that no current is injected out pin 2.

The over current sense level corresponds to 1V.

As long as the overload is present, this sequence repeats. The SWITCHING PHASE duty cycle is in

the range of 10%.

Page 14

16

Service Manual TCL OVERSEAS HOLDINGS LIMITED

3. Transition from Normal to Pulsed Mode

In this sequence the secondary side is reconfigured (refer to the typical application schematic on page

13). The high voltage output value becomes lower than the NORMAL mode regulated value. The

TL431 shunt regulator is fully OFF. In the SMPS stand–by mode all the SMPS outputs are lowered

except for the low voltage output that supply the wake–up circuit located at the isolated side of the

power supply. In that mode the secondary regulation is performed by the zener diode connected in

parallel to the TL431.

The secondary reconfiguration status can be detected on the SMPS primary side by measuring the

voltage level present on the auxiliary winding Laux. (Refer to the Demagnetization Section). In the

reconfigured status, the Laux voltage is also reduced. The V

self–powering is no longer possible

CC

thus the SMPS enters in a hiccup mode similar to the one described under the Overload condition.

In the SMPS stand–by mode the 3 distinct phases are:

The SWITCHING PHASE: Similar to the Overload mode. The current sense clamping level is

reduced according to the equation of the current sense section, page 5. The C.S. clamping level

depends on the power to be delivered to the load during the SMPS stand–by mode. Every switching

sequence ON/OFF is terminated by an OC as long as the secondary Zener diode voltage has not been

reached. When the Zener voltage is reached the ON cycle is terminated by a true PWM action. The

proper SWITCHING PHASE termination must correspond to a NOC condition. The LW latch stores

this NOC status.

The LATCHED OFF PHASE: The MODE latch is set.

The START–UP PHASE is similar to the Overload Mode. The MODE latch remains in its set status

(Q=1).

The SWITCHING PHASE: The Stand–by signal is validated and the 200PA is sourced out of the

Current Sense pin 2.

4. Transition from Stand–by to Normal

The secondary reconfiguration is removed. The regulation on the low voltage secondary rail can no

longer be achieved, thus at the end of the SWITCHING PHASE, no PWM condition can be

encountered. The LW latch is reset.

At the next WORKING PHASE a NORMAL mode status takes place.

In order to become independent of the recovery time SWITCHING PHASE constant on the secondary

side of the SMPS an additional reset input R2 is provided on the MODE latch. The condition

I

<24PA corresponds to the activation of the secondary reconfiguration status. The R2 reset

demag

insures a return into the NORMAL mode following the first corresponds to 1V. START–UP PHASE.

Pulsed Mode Duty Cycle Control

During the sleep mode of the SMPS the switch S3 is closed and the control input pin 3 is connected to

Page 15

TCL OVERSEAS HOLDINGS LIMITED Service Manual

17

a 4.6V voltage source thru a 500: resistor. The discharge rate of the VCC capacitor is given by

I

–latch (device consumption during the LATCHED OFF phase) in addition to the current drawn out

CC

of the pin 3. Connecting a resistor between the Pin 3 and GND (R

drawn from the V

presence of the resistor R

through pin 3. The duration of the LATCHED OFF phase is impacted by the

CC

DPULSED

. The equation 3 shows the relation to the pin 3 current.

DPULSED

) a programmable current is

Pulsed Mode Phases

Equations 1 through 8 define and predict the effective behavior during the PULSED MODE operation.

The equations 6, 7, and 8 contain K, Y, and D factors. These factors are combinations of measured

parameters. They appear in the parameter section “K factors for pulsed mode operation” page 4. In

equations 3 through 8 the pin 3 current is the current defined in the above section “Pulsed Mode Duty

Cycle Control”.

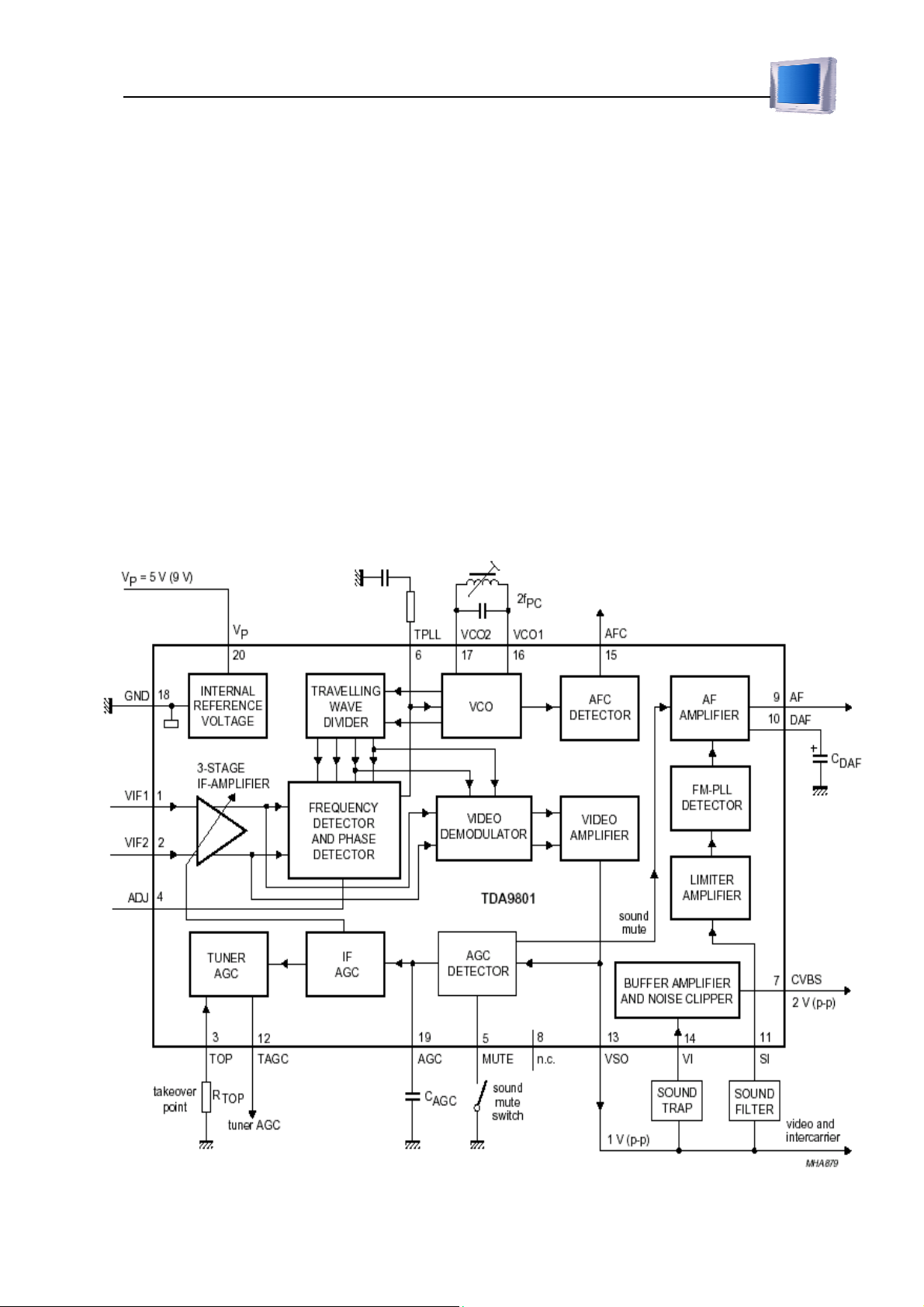

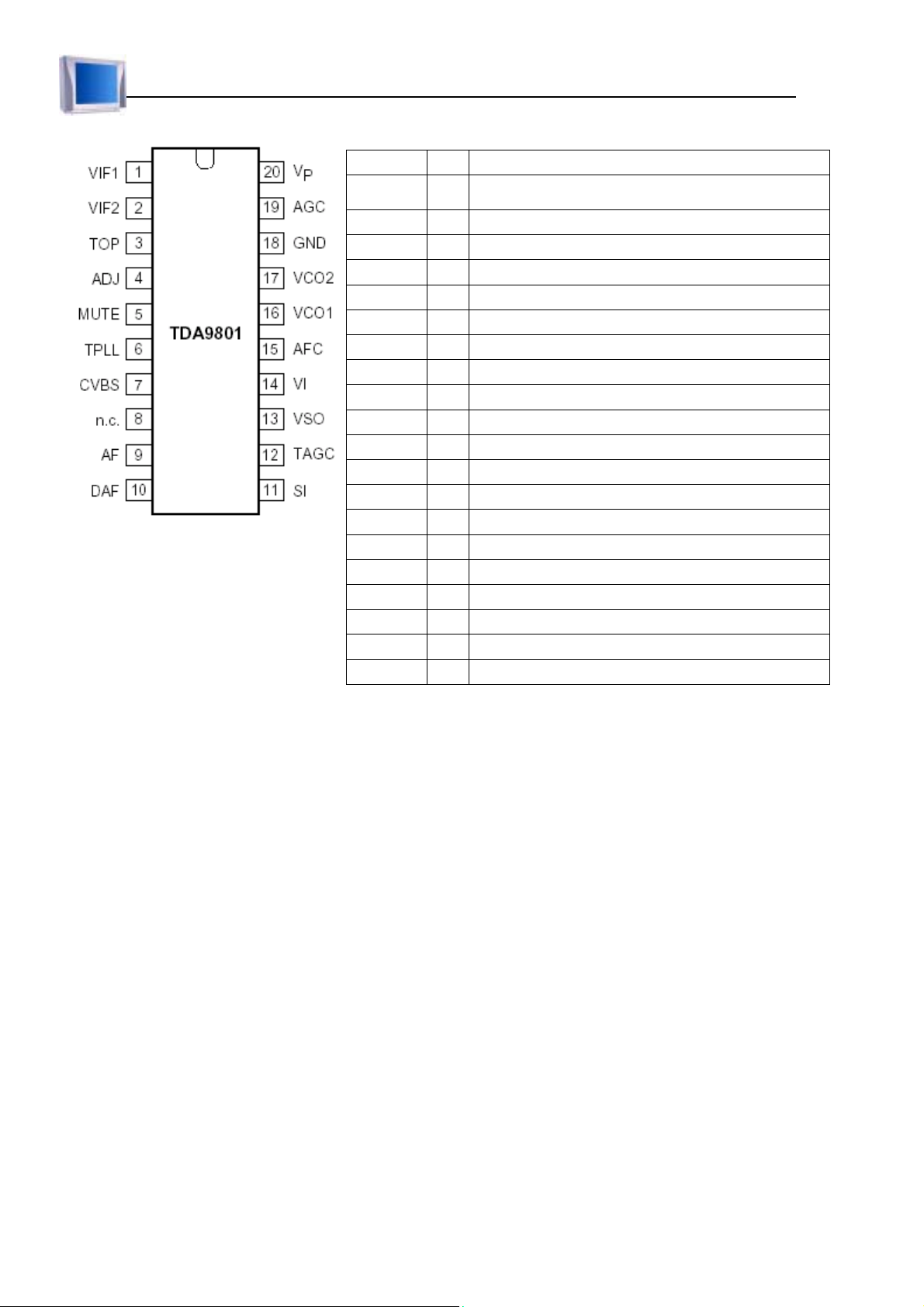

2. TDA9801-Single standard VIF-PLL demodulator and FM-PLL detector

FUNCTIONAL DESCRIPTION

Page 16

18

Service Manual TCL OVERSEAS HOLDINGS LIMITED

SYMBOL PIN DESCRIPTION

VIF1

VIF2 2 VIF differential input 2

TOP 3 tuner AGC TakeOver Point (TOP) connection

ADJ 4 phase adjust connection

MUTE 5 sound mute switch connection

TPLL 6 PLL time constant connection

CVBS 7 CVBS (positive) video output

n.c. 8 not connected

AF 9 AF output

DAF 10 AF amplifier decoupling capacitor connection

SI 11 sound intercarrier input

TAGC 12 tuner AGC output

VSO 13 video and sound intercarrier output

VI 14 buffer amplifier video input

AFC 15 AFC output

VCO1 16 VCO1 reference circuit for 2fPC

VCO2 17 VCO2 reference circuit for 2fPC

GND 18 ground supply (0 V)

AGC 19 AGC detector capacitor connection

VP 20 supply voltage (+5 V)

VIF differential input 1

1

Stage IF amplifier

The VIF amplifier consists of three AC-coupled differential amplifier stages. Each differential stage

comprises a feedback network controlled by emitter degeneration.

AGC detector, IF AGC and tuner AGC

The automatic control voltage to maintain the video output signal at a constant level is generated in

accordance with the transmission standard. Since the TDA9801 is suitable for negative modulation

only the peak sync pulse level is detected.

The AGC detector charges and discharges capacitor C

voltage on capacitor C

AGC is transferred to an internal IF control signal, and is fed to the tuner AGC to

AGC to set the IF amplifier and tuner gain. The

generate the tuner AGC output current on pin TAGC (open-collector output). The tuner AGC takeover

point level is set at pin TOP. This allows the tuner to be matched to the SAW filter in order to achieve

the optimum IF input level.

Frequency detector and phase detector

The VIF amplifier output signal is fed into a frequency detector and into a phase detector. During

acquisition the frequency detector produces a DC current proportional to the frequency difference

between the input and the VCO signal. After frequency lock-in the phase detector produces a DC

current proportional to the phase difference between the VCO and the input signal. The DC current of

Page 17

TCL OVERSEAS HOLDINGS LIMITED Service Manual

19

either frequency detector or phase detector is converted into a DC voltage via the loop filter which

controls the VCO frequency.

Video demodulator

The true synchronous video demodulator is realized by a linear multiplier which is designed for low

distortion and wide bandwidth. The vision IF input signal is multiplied with the ‘in phase’ component

of the VCO output. The demodulator output signal is fed via an integrated low-pass filter (f

= 12

g

MHz) for suppression of the carrier harmonics to the video amplifier.

VCO, AFC detector and travelling wave divider

The VCO operates with a symmetrically connected reference LC circuit, operating at the double

vision carrier frequency. Frequency control is performed by an internal variable capacitor diode.

The voltage to set the VCO frequency to the actual double vision carrier frequency is also amplified

and converted for the AFC output current.

The VCO signal is divided-by-2 with a Travelling Wave Divider (TWD) which generates two

differential output signals with a 90 degree phase difference independent of the frequency.

Video amplifier

The composite video amplifier is a wide bandwidth operational amplifier with internal feedback. A

nominal positive video signal of 1 V (p-p) is present at pin VSO.

Buffer amplifier and noise clipper

The input impedance of the 7 dB wideband CVBS buffer amplifier (with internal feedback) is suitable

for ceramic sound trap filters. Pin CVBS provides a positive video signal of 2 V (p-p). Noise clipping

is provided internally.

Sound demodulation

L

IMITER AMPLIFIER

The FM sound intercarrier signal is fed to pin SI and through a limiter amplifier before it is

demodulated. The result is high sensitivity and AM suppression. The limiter amplifier consists of 7

stages which areinternally AC-coupled in order to minimizing the DC offset.

FM-PLL DETECTOR

The FM-PLL demodulator consists of an RC oscillator, loop filter and phase detector. The oscillator

frequency is locked on the FM intercarrier signal from the limiter amplifier. As a result of this locking,

the RC oscillator is frequency modulated. The modulating voltage (AF signal) is used to control the

oscillator frequency. By this, the FM-PLL operates as an FM demodulator.

AF AMPLIFIER

The audio frequency amplifier with internal feedback is designed for high gain and high

common-mode rejection. The low-level AF signal output from the FM-PLL demodulator is amplified

and buffered in a low-ohmic audio output stage. An external decoupling capacitor CDAF removes the

Page 18

20

DC voltage from the audio amplifier input.

By using the sound mute switch (pin MUTE) the AF amplifier is set in the mute state.

Service Manual TCL OVERSEAS HOLDINGS LIMITED

3. TDA9874A Digital TV sound demodulator/decoder

SYMBOL PIN DESCRIPTION

EXTIR 1 external audio input right channel

EXTIL 2 external audio input left channel

Vref2 3 analog reference voltage for DAC and operational amplifiers

P2 4 second general purpose I/O pin

OUTM 5 analog output mono

VSSA4 6 analog ground supply 4 for analog back-end circuitry

OUTL 7 analog output left

OUTR 8 analog output right

VDDA1 9 analog supply voltage 1; back-end circuitry 5 V

VSSA1 10 analog ground supply 1; back-end circuitry

VSSD1 11 digital ground supply 1; core circuitry

VDDD1 12 digital supply voltage 1; core voltage regulator circuitry

VSSD2 13 digital ground supply 2; core circuitry

TP2 14 additional test pin 2; connected to VSSD for normal operation

NICAM 15 serial NICAM data output (at 728 kHz)

TP1 16 additional test pin 1; connected to VSSD for normal operation

PCLK 17 NICAM clock output (at 728 kHz)

ADDR1 18 first I2C-bus slave address modifier input

XTALO 19 crystal oscillator output

XTALI 20 crystal oscillator input

TEST2 21 test pin 2; connected to VSSD for normal operation

Iref 22 resistor for reference current generation; front-end circuitry

ADDR2 23 second I2C-bus slave address modifier input

VSSA2 24 analog ground supply 2; analog front-end circuitry

VDEC 25 analog front-end circuitry supply voltage decoupling

TEST1 26 test pin 1; connected to VSSD for normal operation

SIF2 27 sound IF input 2

Vref1 28 reference voltage; for analog front-end circuitry

SIF1 29 sound IF input 1

CRESET 30 capacitor for Power-on reset

VSSA3 31 digital ground supply 3; front-end circuitry

VDDA3 32 analog front-end circuitry regulator supply voltage 3 (5 V)

SCL 33 I2C-bus serial clock input

SDA 34 I2C-bus serial data input/output

SDO 35 I2S-bus serial data output

WS 36 I2S-bus word select input/output

SCK 37 I2S-bus clock input/output

Page 19

TCL OVERSEAS HOLDINGS LIMITED Service Manual

SYSCLK 38 system clock output

VDDD3 39 digital supply voltage 3; digital I/O pads

VSSD3 40 digital ground supply 3; digital I/O pads

P1 41 first general purpose I/O pin

MONOIN 42 analog mono input

FUNCTIONAL DESCRIPTION

Description of the demodulator and decoder section

1. SIF INPUTS

Two inputs are provided, pin SIF1 and pin SIF2. For higher SIF

signal levels the SIF input can be attenuated with an internal

switchable ҟ10 dB resistor divider. As no specific filters are

integrated, both inputs have the same specification giving

flexibility in application. The selected signal is passed through

an AGC circuit and then digitized by an 8-bit ADC operating at

24.576 MHz.

21

2. AGC

The gain of the AGC amplifier is controlled from the ADC

output by means of a digital control loop employing hysteresis.

The AGC has a fast attack behaviour to prevent ADC overloads,

and a slow decay behaviour to prevent AGC oscillations. For

AM demodulation the AGC must be switched off. When

switched off, the control loop is reset and fixed gain settings can

be chosen. The AGC can be controlled via the I2C-bus.

3. MIXER

The digitized input signal is fed to the mixers, which mix one or

both input sound carriers down to zero IF. A 24-bit control w

ord

for each carrier sets the required frequency. Access to the mixer

control word registers is via the I

2

C-bus or via Easy Standard Programming (ESP). When receivin

g

NICAM programs, a feedback signal is added to the control word of the second carrier mixer to

establish a carrier-frequency loop.

4. FM AND AM

DEMODULATION

An FM or AM input signal is fed through a switchable band-limiting filter into a demodulator that can

be used for either FM or AM demodulation. Apart from the standard (fixed) de-emphasis

characteristic, an adaptive de-emphasis is available for Wegener-Panda 1 encoded satellite programs.

5. FM

DECODING

A 2-carrier stereo decoder recovers the left and right signal channels from the demodulated sound

carriers. Both the European and Korean stereo systems are supported.

Automatic FM dematrixing is also supported, which means that the FM sound mode identification

Page 20

22

(mono, stereo or dual) switches the FM dematrix directly. No loop via the microcontroller is needed.

Service Manual TCL OVERSEAS HOLDINGS LIMITED

For highly overmodulated signals, a high deviation mode for monaural audio sound single carrier

demodulation can be selected.

NICAM decoding is still possible in high deviation mode.

6. FM

IDENTIFICATION

The identification of the FM sound mode is performed by AM synchronous demodulation of the pilot

and narrow-band detection of the identification frequencies. The result is available via the I2C-bus

interface. A selection can be made via the I2C-bus for B/G, D/K and M standards, and for three

different time constants that represent different trade-offs between speed and reliability of

identification. A pilot detector allows the control software to identify an analog 2-carrier (A2)

transmission within approximately 0.1 s.

Page 21

TCL OVERSEAS HOLDINGS LIMITED Service Manual

23

Automatic FM dematrixing, depending on the identification, is possible.

7. NICAM

DEMODULATION

The NICAM signal is transmitted in a DQPSK code at a bit rate of 728 kbits/s. The NICAM

demodulator performs DQPSK demodulation and passes the resulting bitstream and clock signal to the

NICAM decoder and, for evaluation purposes, to various pins.

A timing loop controls the frequency of the crystal oscillator to lock the sampling instants to the

symbol timing of the NICAM data.

8. NICAM

DECODING

The device performs all decoding functions in accordance with the “EBU NICAM 728 specification”.

After locking to the frame alignment word, the data is descrambled by applying the defined

pseudo-random binary sequence. The device then synchronizes to the periodic frame flag bit C0.

The status of the NICAM decoder can be read out from the NICAM status register by the user. The

OSB bit indicates that the decoder has locked to the NICAM data. The VDSP bit indicates that the

decoder has locked to the NICAM data and that the data is valid sound data. The C4 bit indicates that

the sound conveyed by the FM mono channel is identical to the sound conveyed by the NICAM

channel.

The error byte contains the number of sound sample errors (resulting from parity checking) that

occurred in the past 128 ms period. The Bit Error Rate (BER) can be calculated using the following

equation:

BER = bit errors / total bits §error byte h 1.74 hҏ10

-5

9. NICAM AUTO-MUTE

This function is enabled by setting bit AMUTE to logic 0. Upper and lower error limits may be

defined by writing appropriate values to two registers in the I

2

C-bus section. When the number of

errors in a 128 ms period exceeds the upper error limit, the auto-mute function will switch the output

sound from NICAM to whatever sound is on the first sound carrier (FM or AM) or to the analog mono

input. When the error count is smaller than the lower error limit, the NICAM sound is restored.

The auto-mute function can be disabled by setting bit AMUTE to logic 1. In this case clicks become

audible when the error count increases. The user will hear a signal of degrading quality.

If no NICAM sound is received, the outputs are switched from the NICAM channel to the 1st sound

carrier.

A decision to enable or disable the auto-mute is taken by the microprocessor based on an

interpretation of the application control bits C1, C2, C3 and C4, and possibly any additional strategy

implemented by the user in the microcontroller software.

When the AM sound in NICAM L systems is demodulated in the 1st sound IF and the audio signal

connected to the mono input of the TDA9874A, the controlling microprocessor has to ensure

switching from NICAM reception to mono input, if auto-muting is desired. This can be achieved by

Page 22

24

Service Manual TCL OVERSEAS HOLDINGS LIMITED

setting bit AMSEL = 1 and bit AMUTE = 0.

10. CRYSTAL OSCILLATOR

The digital controlled crystal oscillator (DCXO) is fully integrated. Only an external 24.576 MHz

crystal is required.

11. T

EST PINS

All test pins are active HIGH. In normal operation of the device they can be left open-circuit, as they

have internal pull-down resistors. Test functions are for manufacturing tests only and are not available

to customers.

12. P

OWER FAIL DETECTOR

The power fail detector monitors the internal power supply for the digital part of the device. If the

supply has temporarily been lower than the specified lower limit, the power failure register bit PFR in

subaddress 0, will be set to logic 1. Bit CLRPFR, slave register subaddress 1, resets the Power-on

reset flip-flop to logic 0. If this is detected, an initialization of the TDA9874A has to be performed to

ensure reliable operation.

OWER-ON RESET

13. P

The reset is active LOW. In order to perform a reset at power-up, a simple RC circuit may be used

which consists of an integrated passive pull-up resistor and an external capacitor connected to ground.

The pull-up resistor has a nominal value of 50 k , which can easily be measuredǂ between pins

CRESET and VDDD3. Before the supply voltage has reached a certain minimum level, the state of

the circuit is completely undefined and remains in this undefined state until a reset is applied.

The reset is guaranteed to be active

when:

ҏThe power supply is within the ǂ

specified limits (4.5 to 5.5 V)

ҏThe crystal oscillator (DCXO) is ǂ

functioning

ҏThe voltage at pin CRESET is ǂ

below 0.3VDDD (1.5 V if VDDD

= 5.0 V, typically below 1.8 V).

The required capacitor value

depends on the gradient of the

rising power supply voltage. The time constant of the RC circuit sh

ould be clearly larger than the rise

time of the power supply (to make sure that the reset condition is always satisfied), even when

considering tolerance spreading. To avoid problems with a too slow discharging of the capacitor at

power-down, it may be helpful to add a diode from pin CRESET to VDDD.

should be noted that the internal ESD protection diode does not help here as it only conducts at

It

higher voltages. Under difficult power supply conditions (e.g. very slow or non-monotonic ramp-u

it is recommended to drive the reset line from a microcontroller port or the like.

p),

Page 23

TCL OVERSEAS HOLDINGS LIMITED Service Manual

escription of the DSPD

25

1. LEVEL SCALING

All input channels to

the digital crossbar switch are equipped with a level adjustment facility to

change the signal level in a range of 15 dB. Adjusting the signal levelǂ is intended to compensa

the different modulation parameters of the various TV standards. Under nominal conditions it is

recommended to scale all input channels to be 15 dB below full-scale. This will create sufficient

headroom to cope with overmodulation and avoids changes of the volume impression when switc

from FM to NICAM or vice versa.

te for

hing

2

.NICAM

The NICAM path

3

.NICAM

If NICAM is received,

PATH

has a switchable J17 de-emphasis.

AUTO-MUTE

the auto-mute is enabled and the signal quality becomes poor. The digital

crossbar switches automatically to FM, channel 1 or the analog mono input, as selected by bit AM

This automatic switching depends on the NICAM bit error rate. The auto-mute function can be

disabled via the I

4

.FM(AM)

A high-pass filter s

2

C-bus.

PATH

uppresses DC offsets from the FM demodulator that may occur due to carrier

frequency offsets, and supplies the FM monitor function with DC values, e.g. for the purpose of

microprocessor controlled carrier search or fine tuning functions.

A

n adaptive de-emphasis is available for Wegener-Panda 1 encoded satellite programs.

T

he de-emphasis stage offers a choice of settings for the supported TV standards.

T

he 2-channel decoder performs the dematrixing of ½(L + R), R to L and R signals of ½ (L + R) and

½(L ҟҏR) to L and R signals or of channel 1 and channel 2 to L and R signals, as demanded by the

different TV standards or user preferences.

SEL.

A

utomatic FM dematrixing is also supported.

Page 24

26

Service Manual TCL OVERSEAS HOLDINGS LIMITED

Using the high deviation mode, only channel 1 (mono) can be demodulated. The scaling is ҟ6 dB

compared to 2-channel decoding.

5

. MONITOR

This function p

rovides data words from the FM demodulator outputs and FM and NICAM signals for

external use, such as carrier search or fine tuning. The peak level of these signals can also be observed

Source selection and data read out are performed via the I

. DIGITAL CROSSBAR SWITCH

6

The input channels are derived from t

2

I

S-bus and the audio DACs to the analog crossbar switch. It should be noted that there is no

he FM and NICAM paths, while the output channels comprise

2

C-bus.

connection from the external analog audio inputs to the digital crossbar switch.

7

. DIGITAL AUDIO OUTPUT

The digital audio output interface

2

I

S-bus port is equipped with a level adjustment facility that can change the signal level in a 15 dBǂ

comprises an I

2

S-bus output port and a system clock output. The

range in 1 dB steps. Muting is possible, too, and outputs can be disabled to improve EMC

performance.

.

2

T

he I

S-bus output matrix provides the functions for forced mono, stereo, channel swap, channel 1 or

channel 2.

A

utomatic selection for TV applications is possible. In this case the microcontroller program only has

to provide a user controlled sound A or sound B selection.

8

. STEREO CHANNEL TO THE ANALOG CROSSBAR PATH

A level adjustment function is provided with control positions of 0

dB, +3 dB, +6 dB and +9 dB in

combination with the audio DACs. The Automatic Volume Level (AVL) function provides a constan

output level of ҟ20 dB (full-scale) for input levels between 0 dB (full-scale) and ҟ26 dB (full-scale).

There are some fixed decay time constants to choose from, i.e. 2, 4 or 8 seconds.

A

utomatic selection for TV applications is possible. In this case the microcontroller program only has

to provide a user controlled sound A or sound B selection.

9

. GENERAL

The level adjus

taken when using gain with large input signals, e.g., due to overmodulation, in order not to exceed

tment functions can provide signal gain at multiple locations. Great care has to be

the

maximum possible signal swing, which would cause severe signal distortion. The nominal signal level

of the various signal sources to the digital crossbar switch should be 15 dB below digital full-scale (ҟ15

dB full-scale).

Description of

1. ANALOG CROSSBAR SWITCH AND

The TDA9874A has one external analog stereo input, one mono i

single-channel output port. Analog source selector switches are employed to provide the desire

the analog audio section

ANALOG MATRIX

nput, one 2-channel and one

d

t

Page 25

TCL OVERSEAS HOLDINGS LIMITED Service Manual

27

analog signal routing capability, which is done by the analog crossbar switch section.

The basic signal routing philosophy of the TDA9874A is that each switch handles two signal channels

at the same time (e.g. left and right, language A and B) directly at the source.

E

ach source selector switch is followed by an analog matrix to perform further selection tasks, such as

putting a signal from one input channel, say language A, to both output channels or for swapping left

and right channels. The analog matrix provides the functions given in the follow table. Automatic

matrixing for TV applications is also supported.

A

ll switches and matrices are controlled via the I

A

nalog matrix functions

MODE

OUTPUTMATRIX

LO TUTPUT R OUTPU

1

L input R input

2 R input L input

3 L input L input

4 R input R input

2

C-bus.

2. EXTERNAL AND MONO INPUTS

The external and mono inputs accept sig

nal levels of up

to 1.4 V (RMS). By adding external series resistors to

provide suitable attenuation, the external input could be

used as a SCART input. Whenever the external or mono

input is selected, the output of the DAC is muted to

improve the crosstalk performance.

3. AUDIO DACS

The TDA9874A co

mprises a 2-channel audio DAC and an additional single-channel audio DAC for

feeding signals from the DSP section to the analog crossbar switch. These DACs have a resolution of

15 bits and employ four-times oversampling and noise shaping.

4

. AUDIO OUTPUT BUFFERS

The output buffers provide a gain

of 0 dB and offer a muting possibility. The post filter capacitors of

the audio DACs are connected to the buffer outputs.

5

. STANDBY MODE

Switchdiagramfortheanalogaudiosection

The standby mode disables most functions and reduces power dissipat

ion of the TDA9874A. It

Page 26

28

provides no other function.

Internal registers may lose their information in standby mode. Therefore, the device needs to be

initialized on returning to normal operation. This can be accomplished in the same way as after a

Power-on reset.

Service Manual TCL OVERSEAS HOLDINGS LIMITED

Audio signal flow.

4. TDA7057AQ 2u8 W stereo BTL audio output amplifier with DC volume

control

Pin

ning

SYMBO

OUT2+

PGND2 9 power ground 2

PGND1 12 power ground 1

L PIN DESCRIPTION

VC1 1 DC volume control 1

n.c. 2 not connected

l (1) 3 voltage input 1

V

VP 4 positive supply v

l (2) 5 voltage input 2

V

SGND 6 signal ground

VC2 7 DC volume con

8 positive output 2

OUT2ҟ 10 negative output 2

OUT1ҟ 11 negative output 1

OUT1ҙ 13 positive output 1

oltage

trol 2

UNCTIONAL DESCRIPTION

F

The TDA7057AQ is a stereo ou

volume control stages. The device is designed for TVs and

monitors, but is also suitable for battery-fed portable

recorders and radios.

In conventional DC vo

stage via external capacitors to keep the offset voltage low.

the TDA7057AQ the two DC volume control stages are integrated into the input stages so that no

In

lume control circuits the control or input stage is AC-coupled to the output

tput amplifier with two DC

Page 27

TCL OVERSEAS HOLDINGS LIMITED Service Manual

coupling capacitors are required and a low offset voltage is still maintained. The minimum supply

voltage also remains low.

The BTL principle offers the following advantages:

ҏLower peak value of the supply currentǂ

ҏThe frequency of the ripple on the supplǂ

C

onsequently, a reduced power supply with smaller capacitors can be used which results in cost

reductions.

F

or portable applications there is a trend to decrease the supply voltage, resulting in a reduction of

output power at conventional output stages. Using the BTL principle increases the output power.

T

he maximum gain of the amplifier is fixed at 40.5 dB. The DC volume control stages have a

logarithmic control characteristic. Therefore, the total gain can be controlled from +40.5 dB to

If the DC volume control voltage falls below 0.4 V, the device will switch to the mute mode.

y voltage is twice the signal frequency.

29

ҟ33 dB.

Block diagram.

5. TMPA

The TMPA8803CSN is an integrated NTSC

TV. It consists of two

Multi-Chip-Package (MCP) technology. One is a micro

8803CSN

circuit for a PAL/

pieces of IC chip in one package, using

T

he amplifier is a

short-circuit

protected to g

VP and acros

load. A thermal

protection circuit is

also implemented.

If the crystal

temperature rises

above +150

the gain will be

reduced, thereby

reducing the outp

power.

Special

g

iven to switch-on

and switch-off

clicks, low HF

radiation and a

good overall

stability.

round,

sthe

Cǂ

ut

attention is

Page 28

30

controller (MCU) and the other one is a signal processor (SP) for a color TV. The TV signal processor

contains PIF, SIF, Video, multi-standard chroma, Sync, RGB processors.

Service Manual TCL OVERSEAS HOLDINGS LIMITED

Page 29

TCL OVERSEAS HOLDINGS LIMITED Service Manual

PINNING

SYMBOL PIN DESCRIPTION SYMBOL PIN DESCRIPTION

BAND2 1 Band selector SIF in 33

TV/AV 2 TV/AV switch DC NF 34

KEY 3 Panel key input PIF PLL 35

GND 4 GND IF vcc(5V) 36

RESET 5 System clock reset output S-reg 37

X-TAL 6 Deepmph 38

X’tal connecting pins

X-TAL 7

TEST 8

5V 9 Vdd Supply 5V IF in 41

GND 10 GND for Slicer circuit IF in 42

GND 11 GND terminal for Analog block. RF AGC 43

FBP in

/SCP out

H out 13

H-AFC 14

V saw 15

V out 16

H vcc 17

N.C. 18 N.C. R out 50

Cb 19 Input terminal for Cb signal. G out 51

Test pin for out-going test. Be tied to

low.

12 Input terminal for FBP. Y/C 5V 44

Output terminal for Horizontal driving

pulse.

Terminal to be connected capacitor for

H AFC filter. This terminal voltage

controls H VCO frequency.

Terminal to be connected capacitor to

generate V saw signal. V saw

amplitude is kept constant by V AGC

function.

Output terminal for Vertical driving

pulse.

Vcc terminal for DEF circuit. Supply

9V.

IF AGC 39

IF GND 40 GND terminal for IF circuit.

AV out 45

BLACK

DET

APC FIL 47

IK in 48

RGB 9V 49

Input terminal for H correction and

2nd SIF.

Terminal to be connected capacitor

for DC Negative Feedback from SIF

Det output.

Terminal to be connected with loop

filter for PIF PLL. This terminal

voltage is controlled PIF VCO

frequency.

Vcc terminal for IF circuit. Supply

5V.

Terminal to be

connected capacitor for stabilizing

internal bias.

Terminal to be connected capacitor

for SIF Det De-Emphasis.

Terminal to be connected with IF

AGC filter.

Input terminals for IF signals. Pin41

and Pin42 are both input poles of

differential amplifier.

Output terminal for RF AGC control

level.

Vcc terminal for Y/C circuit. Supply

5V.

Output terminal for CVBS or Y signal

selected by BUS (Video SW).

Terminal to be connected with Black

46

Det filter for black stretch.

Terminal to be connected with APC

filter for Chroma demodulation. This

terminal voltage controls frequency of

VCXO

Input terminal to sense ACB cathode

current.

Vcc terminal for RGB circuit. Supply

9V.

Output terminals for R /G/B signal.

31

Page 30

32

Y in 20 Input terminal for Y signal. B out 52

Cr 21 Input terminal for Cr signal. GND 53 GND terminal for Analog block.

TV-GND 22 GND terminal for Digital block. GND 54 scillator circuit GND for O

C in 23 Input terminal for Chroma signal. 5V 55 Vdd for Oscillator circuit Supply 5V

EXT in 24 r Video signal. 50/60 Input terminal fo 56 PAL/NTSC selector

DIG 5V 25

TV in 26 Input terminal for Video signal. SCL 58 I2C bus serial clock input /output

ABCL in 27 Input terminal for ABL/ACL control. VOL 59 trol signal output Volume con

Audio out terminal for Audio signal.28 Output VT 60 Tune voltage controller

IF vcc(9V) 29 Vcc terminal for IF circuit. Supply 9V. BAND1 61 selector Band

TV out 30

SIF out 31

EXT audio 32

Service Manual TCL OVERSEAS HOLDINGS LIMITED

Vcc terminal for Digital block. This

terminal voltage is clipped about 3.3V

by regulator circuit.

Output terminal for detected PIF

signal.

Output terminal for detected SIF

signal.

Input terminal for E

signal.

xternal Audio

SDA 57 I2C bus serial data input /output

TV sync 62 Sync signal input

RMT in 63

POWER 64

input

LED output

signal preprocessor Remote control

SIGNA RO SSOR DESCRIPTIONS

L P CE

1. Tank-coil-less PIF VCO

PA8803 adopts a tank-coil-less PIF VCO circuit h has nt

TM , whic adva ages of cost, performance of

IF in an layout. The P L syst as

weak put d easy to design PCB IF PL em h

the micro controller needs only to order the PIF PLL system to start se the IIC

he se lig c.

bus. T lf-a nment finishes within 50 mse

2. Built-in Soun

A sound

d Band Pass Filter

band pass filter is integrated on the chip for multi frequency SIF systems. The 1st SIF

demodulator multiplies PIF input signal and regenerated PIF carrier fro

self-alignment circuit, so that

lf-alignment through

m VCO with 90-degree angle,

and gets multi-frequency SIF signal as 6.5MHz, 6.0MHz, 5.5MHz and 4.5MHz according to the SIF

system. A freque z-SIF signal by

g th nv bus. The buil sound BPF rejects undesired

frequency compo l. A narrow-band 1 MHz PLL FM demodulator with no

external tank-coil achieves to output sound signal with better S/N ratio

ncy converter converts one of those four SIF signals into 1 MH

erting frequency through the IICselectin e co t-in

nents of 1MHz-SIF signa

.

3. AFT

A recent IF syste a digital AFT circuit. But analog DC voltage is used as interface between

an IF system and ol loop. TMPA88

through IIC bus s s below.

m adopts

a micro controller in the AFT contr

hown a

03 adopts a digital interface

-stan d I nals

4. Non dar F sig

A8803 prepares ways for non-standard IF inputs. The OVE OD switch is available for

TMP R M

r-modulated PIF signals in the condition of more 7.5% du

ove than 8 mo lation at 100 IRE, which is the

mum ul d NTSC. ition, PA8803 has capability to

maxi mod ation Standard of PAL an In add TM

Page 31

TCL OVERSEAS HOLDINGS LIMITED Service Manual

modulate m th SIF sign out un ireore an 400% over-modulated al with des d voltage turning over also.

33

5. AV swit

The audio switch has one input for an external audio, and another for internal demodulated audio

signal. The sw hed aud o attenuat wh has control

g

ain from 0 dB to –80dB or less with near log curve characteristic.

The video switch has one in

TV video signal and the last for an external YCbCr signal, mainly coming form a DVD player. The

Cin terminal for the external S-VHS signal has capability to detect DC level of the input signal, and

the micro controller can read the result as ‘Cin DC’ through the IIC bus. This function may prepare

way for automatic switching, when inserting S-VH

A monitor output is available with t

and C signals are mixed for the monitor output. This output is useful for signal detecting by the

counting of the micro controller through an external LPF circuit for strict signal detecting

performance.

6. Asymmetric Sharpness

External analog circuits are likely to generate ‘over-shoot’ signal. The asymmetric sharpness circuit

provided to compensate this undesired signal. It is possible to get more g

o

ver-shoot by using the asymmetric sharpness, instead of that a conventional sharpness function

generate

ch

itc io signal goes into the audi or, ich lability of audio

put for an external CVBS or S-VHS signal, the other for the demodulated

S connection, by means of software control.

he selected video signal. In the case of selecting S-VHS input, Y

TC3

ain of pre-shoot than

s both pre-shoot and over-shoot symmetrically.

a

is

7. Scan Velocity Modulation (SVM)

The SVM output is available for a

a

t pin45 through the IIC bus. The SVM gain and timing is also selectable to match an external SVM

drive circuit.

8. Chroma demodulator

The multi-color chroma demodulator is integrated with the automatic color system detection. T

1H-delay line is integrated on the chip for PAL chroma demodulation. The 1H-delay line can acts a

large screen size TV. The SVM or the monitor output is selectable

he

sa

Page 32

34

chroma comb filter on NTSC chroma system.

9. Base Band Color System

TMPA8803 features a base band color system for a YCbCr inputs capability for a DVD and a SDTV

signals. Those signals are demodulated out side of TMPA8803, so that color signals (Cb, Cr) has

different color level, different demodulation angle and different relative amplitude from the color

signals demodulated by the internal chroma demodulator of TMPA8803. The base band color system

is required to have control functions of color saturation, TINT and relative amplitude, and TMPA8803

has all of these functions in it. Because of base band TINT function, TMPA8803 has capability to

control PAL TINT, which is basically hard to control on a conventional signal processor IC. Of course

the control software can inhibit the PAL TINT function.

YCbCr inputs are also available for PIP operation with Ys input at pin18. In case of no PIP application,

connecting the

10. AKB (Auto-Kine-Bias) system

TMPA8803 provides AKB capability with the software control, for

c

ontrol at the manufacture’s factory. TMPA8803 includes circuits below as hardware on the chip.

Service Manual TCL OVERSEAS HOLDINGS LIMITED

pin18 to GND via a 10k-ohm resister is recommended.

automatic dark and bright level

(1) AKB reference pulse generator

(2) IK feedback input

(3) comparaters to check feedback level

(4) read bus to know the result of comparison

The software can achieve AKB functionality by

(5) analyzing the comparison result

(6) controlling

11. Transparent OSD inte

TMPA8803 provides a transparent OSD capability. A conventional OSD system provides a half-to

function for OSD interface, by reducing the gain of a main picture signal during high period of ‘Ym’

signal from the micro controller. TMPA8803 h

cutoff and drive through the IIC bus.

rface

ne

as one more control line as ‘I’ for OSD from the micro

Page 33

TCL OVERSEAS HOLDINGS LIMITED Service Manual

controller, which enables to put a color on the same area of half-tone, so that software can achieve a

see-through color menu by u

12. Noise Level Detection

The Noise level detector is integrated. The result can be read through the IIC bus. According to the

result, the micro controller can adjust level of some controls in the signal processor. For example,

(1)When a noisy signal comes in, horizontal synchronization is influenced and the picture on the

screen looks bad. Selecting less H-AFC gain makes the picture looks better.

(2)When a noisy signal comes in, SECAM system causes

s

aturation level makes noisy impression better.

(3)When a very noisy signal comes in, the vertical frequency detector sometimes makes

miss-detection, and causes vertical jittering. Selecting the auto-50Hz m

a

ccording to the vertical frequency information just before, may solves the vertical jittering.

13. Signal Detection Flags

There are some flags on the READ BUS registers. They indicate that a certain signal is detected at

moment. But reliability of a detection result is not so accurate if checking only one flag, so that

confirming several flags, which means similar result by each other, at the same time is recommended.

sing the transparent OSD.

very strong color noise. Reducing color

ode or auto-60Hz mode,

35

the

14. Control the Signal Processor

The signal processor is connected with the micro controller by means of internal wiring. All functions

of the signal processor can be controlled through IIC bus, which is a part of the internal connections.

15. Color system: Automatic mode for Southern-America

The Automatic color identification system for “SA AUTO” mode may not work well. In order to

make sure automatic color system identification in South America are, design the control software

with following algorithm.

Page 34

36

Service Manual TCL OVERSEAS HOLDINGS LIMITED

6. HEF4066BP-Quadruple bilateral switches

D

ESCRIPTION

The HEF4066BP has four i

ndependent bilateral analogue s

has two input/output terminals (Y/Z) and an active HIGH enable input (E). When E is connected to

VDD a low impedance bidirectional path between Y and Z is established (ON condition). When E

onnected to VSS the switch is disabled and a high im

c

condition).

The HEF4066BP is pin compatible with the

HEF4016B but exhibits a much lower ON resist

ance.

In addition the ON resistance is relatively constant

over the full input signal range.

witches (transmission gates). Each switch

pedance between Y and Z is established (OFF

Pinning diagram.

is

. TC9028F-INFRARED REMOTE

7

CONTROL TRANS

MITTING CHIP

TC9028F is CMOS LSI for Infrared Remote

Control Transmitting suitable for Remote

Controlling TV, VCR, Video D

sing a 4bit Microcontroller, various transmittings

U

are structured by

PIN CONNECTION (TOP VIEW)

a programming.

isk, CD-Player etc.

PIN NAME PIN DESCRIPTION

Supply

Output for

Osc.

Input for Osc. 3

Reset Input

Input Port PO 5~8 4bit input port. Built-in pulldown

I/O Port P1 9~12

I/O Port P2 13~16

Output Port

P51

Output Port

P52

Output Port

P53

Functional diagram

E0 to E3 enable inputs

Y0 to Y3 input/output terminals

Z0 to Z3 input/output terminals

1Power

20

2

4

17 Pch open drain output port.

18 Hiah current output port. For drivina

19 High current output port. For driving

VDD=~.O-~.OV, 3V (Typ.)

Resonator connecting pins. Connects

ceramic resonator with capacitor. Built-in

feedback resistance.

RST for going reset. Be held to "L" ( ı 3

instruction cycles)

resistance.

4bit I/0 ports with latch. Built-in pulldown

resistance.

indication LED.

infrared LED.

Page 35

TCL OVERSEAS HOLDINGS LIMITED Service Manual

8. M24C08-8Kbit Serial I²C Bus EEPROM

Logic Diagram

NC

NC

E2

Vss

Pin Connections

37

Signal N

E2

SDA Serial Data/Address Input/Output

SCL Serial Clock

WC Write Control

Vcc Supply Voltage

Vss Ground

SIGNAL DESCRIPTION

Serial Clock (SCL)

The SCL input pin is used to strobe all data in and out of the memory. In applications where this line

used by slaves to synchronize the bus to a slower clock, the master must have an open drain output,

is

nd a pull-up resistor must be connected from the SCL line to VCC. In most applications, though, this

a

ethod of synchronization is not employed, and so the pull-up resistor is not necessary, provided that

m

the master has a push-pull (rather

Serial Data (SDA)

The SDA pin is bi-directional, and to transf data in o open drain

output that may be wire-OR’ed with other open drain or open collector signals on the bus. A pull up

resistor must be connected from th o VCC.

than open drain) output.

is used er r out of the memory. It is an

eSDAbust

ames

Chip Enable Inputs

Chip Enable (E2)

These chip enable inputs are used e t is to be

bits (b3, b2, b1) of the 7-bit device select code. These inputs ically or tied to

VCC or VSS to establish the devic

Write Control (

The hardware Write Control pin(WC

inadvertent erase/write. The Write Control signal is used to enable (

rite instructions to the entire memory area. When unconnected, the w input is internally read as

IL, and write operations are allowed.V

WC )

to set the valu hat looked for on the three least significant

may be driven dynam

e select code.

) is useful for protecting the entire contents of the memory from

WC WC

=VIL) or disable ( =VIH)

WC

Page 36

38

When WC =1, Device Select and Address bytes are acknowledged, Data bytes are not acknowledged.

Service Manual TCL OVERSEAS HOLDINGS LIMITED

9. LA7840 -Vertical Deflection Output Circuit

The LA7840 is a vertical deflection

output IC for TVs and CRT displays

with ex

BUS control system signal processing

IC. This IC can drive the direct (even

in

yoke with the

from the BUS control system

process

deflectio

LA7840 is

sc

cellent image quality that use a

cluding a DC component) deflection

sawtooth wave output

signal

ing IC. Because the maximum

n current is 1.8 Ap-p, the

suited for small and medium

reen sets.

Pin Name

1. GND

2. Ver OUTPUT

3. OUTPUT STAGE Vcc

4. NON INV.INPUT

5. INVERTING INPUT

6

. Vcc

7. PUMP UP OUT

Page 37

TCL OVERSEAS HOLDINGS LIMITED Service Manual

N

t

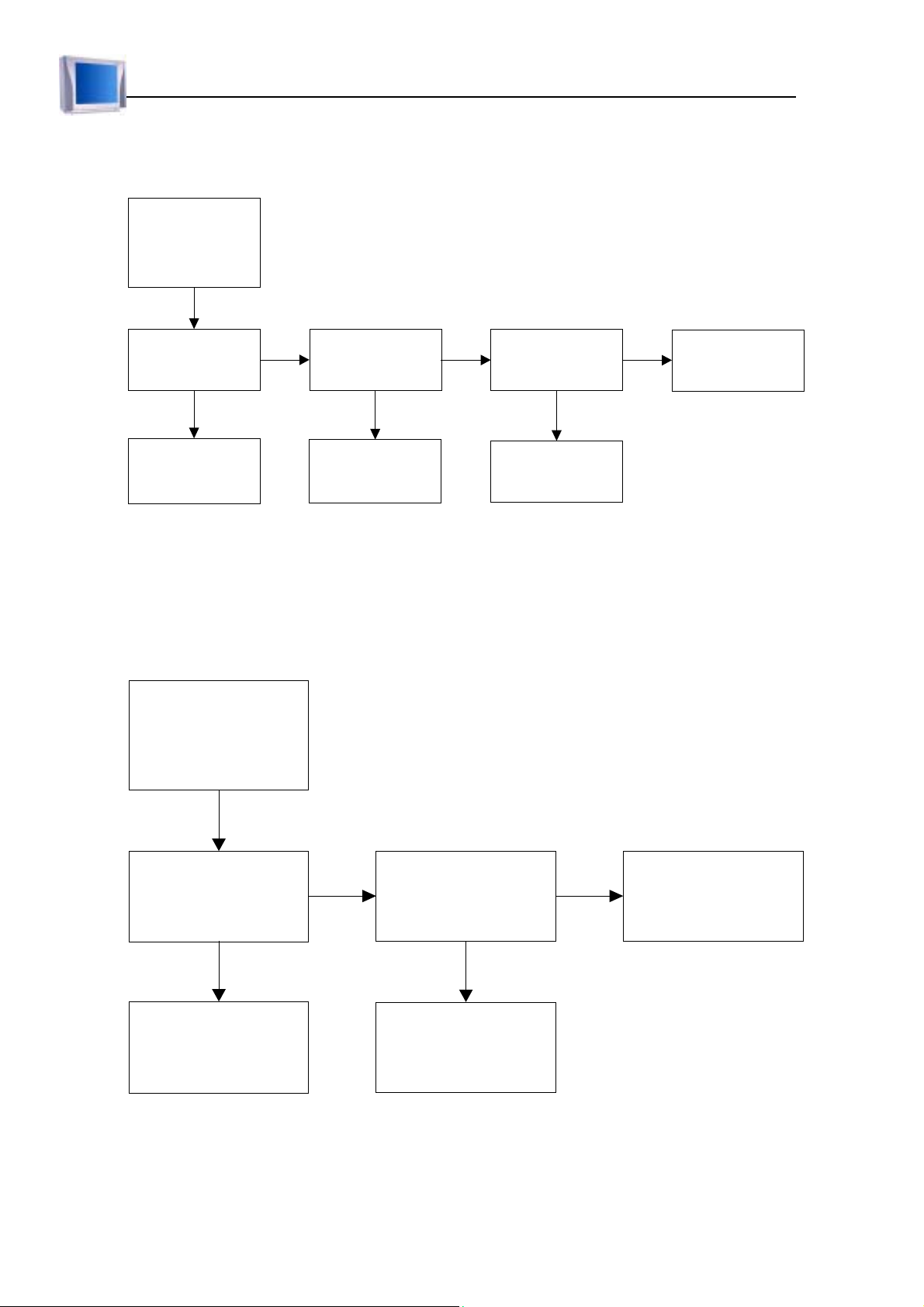

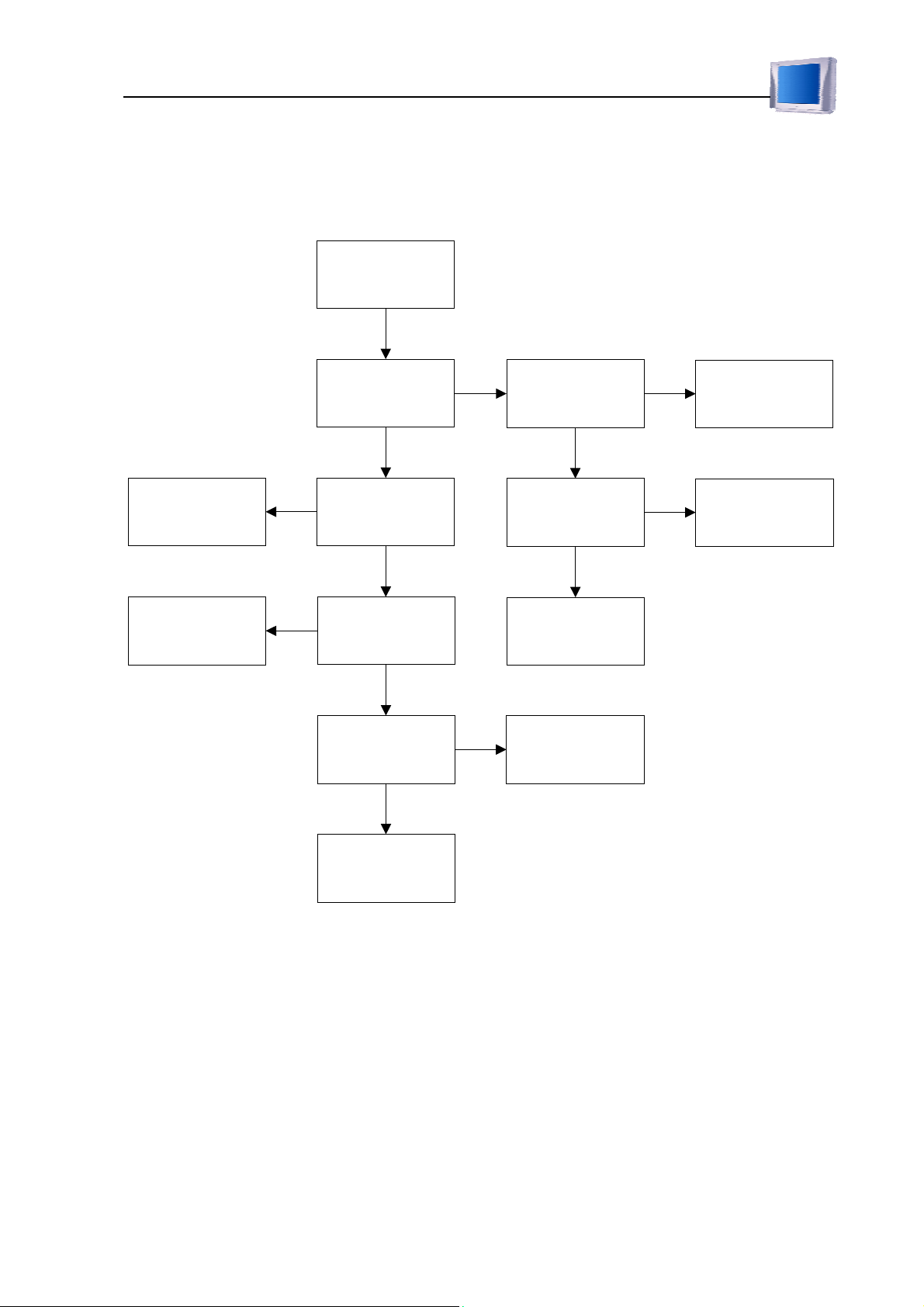

PART . Adjusting DescriptionV

lowchart chart of alignment procedure for M28 chassis:

F

39

B+

adjustment

Sub-brightnes

s Adjustment

Pincushion and screen

width

adjustment

ALIGNMENT PROCEDURE FOR M28 CHASSIS

ICAM

Adjustment

White balance

Adjustment

Screen center & size

adjustment (PAL)

Electricalproperties

checking for chass

Aging

Adjust

volt

Screen

adjustm

RF AGC

is adjustment

ment of screen

age and focus

center & size

ent (NTSC)

:

Sub-color & Sub-tin

adjustment

QC

Checking

I) Adjustment of +B Voltage

1. Apply 110-240VAC( 5V) to mains power inpuǂ t, and Philips standard testing pattern to RF

input.

2. Adjust VR830 in STANDARD mode until voltage at (B+) is 112V 0.25V.ǂ

II) NICAM

1. Apply a 38.9MH

2. Monitor the DC voltage

3. Adjust T1101 until th

4. Then check the wavefor

Adjustment (for NICAM model only)

z color bar with NICAM signal to the IF input.

at pin 15 of IC1101.

e voltage at pin 15 of IC1101 becomes 2.5 +/- 0.1V.

m at pin 4 and 6 of P1103 and it must show correct audio signal.

III The alignment o

) f RFAGC (choose A or B)

A)

1. Connect the detector shown below to collector of Q101.

2. Receive a grey scale signal with 70dB

V amplitude.

3. Adjust RFAGC item until the output of the detector becomes 0.8Vpp

B)

1. Receive a grey scale signal with 60dB

V amplitude.

2. Adjust RFAGC data until the noise of the picture just disappear.

V) Adjustment of Sub-contrast, Sub-tint and Sub-colour for NSTC and PAL signal.