Page 1

5

4

3

2

1

D D

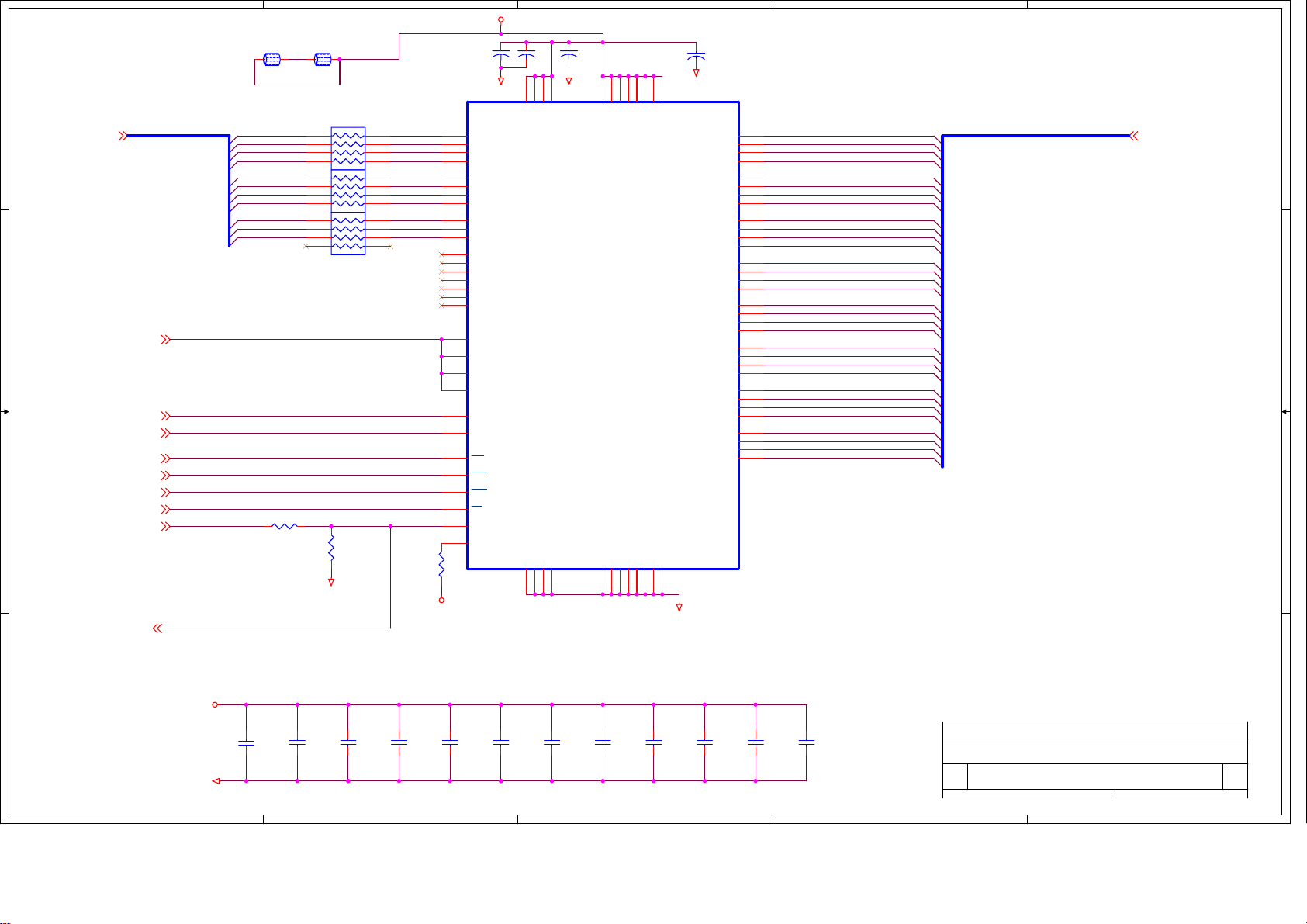

LCD TV LCD42B66--2300+Jagasm

VER:00 DATA:2005.07.27

C C

THIS SHEET

YPbPr INTERFACE

AD9883 INTERFACE

S2300 DEINTERLACE

S2300 SDRAM

VGA CONNECTOR

JAGUAR ANALOG INTERFACE

JAGUAR SDRAM SECTION

SDRAM BASED FRAME BUFFER

JAGUAR DIGITAL INTERFACE

JAGUAR PANEL INTERFACE

PANEL INTERFACE

B B

LVDS PANEL INTERFACE

DVI INTERFACE

MICROCONTROLLER 80C32

POWER SUPPLY AND DECAPS

DC-DC

SHEET NO.DESCRIPTION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

拟制:

审核:

A A

批准:

Title

LCD42B66

Size Document Number Rev

5

4

3

2

Date: Sheet

<Doc> 00

Custom

1

117Thursday, July 28, 2005

of

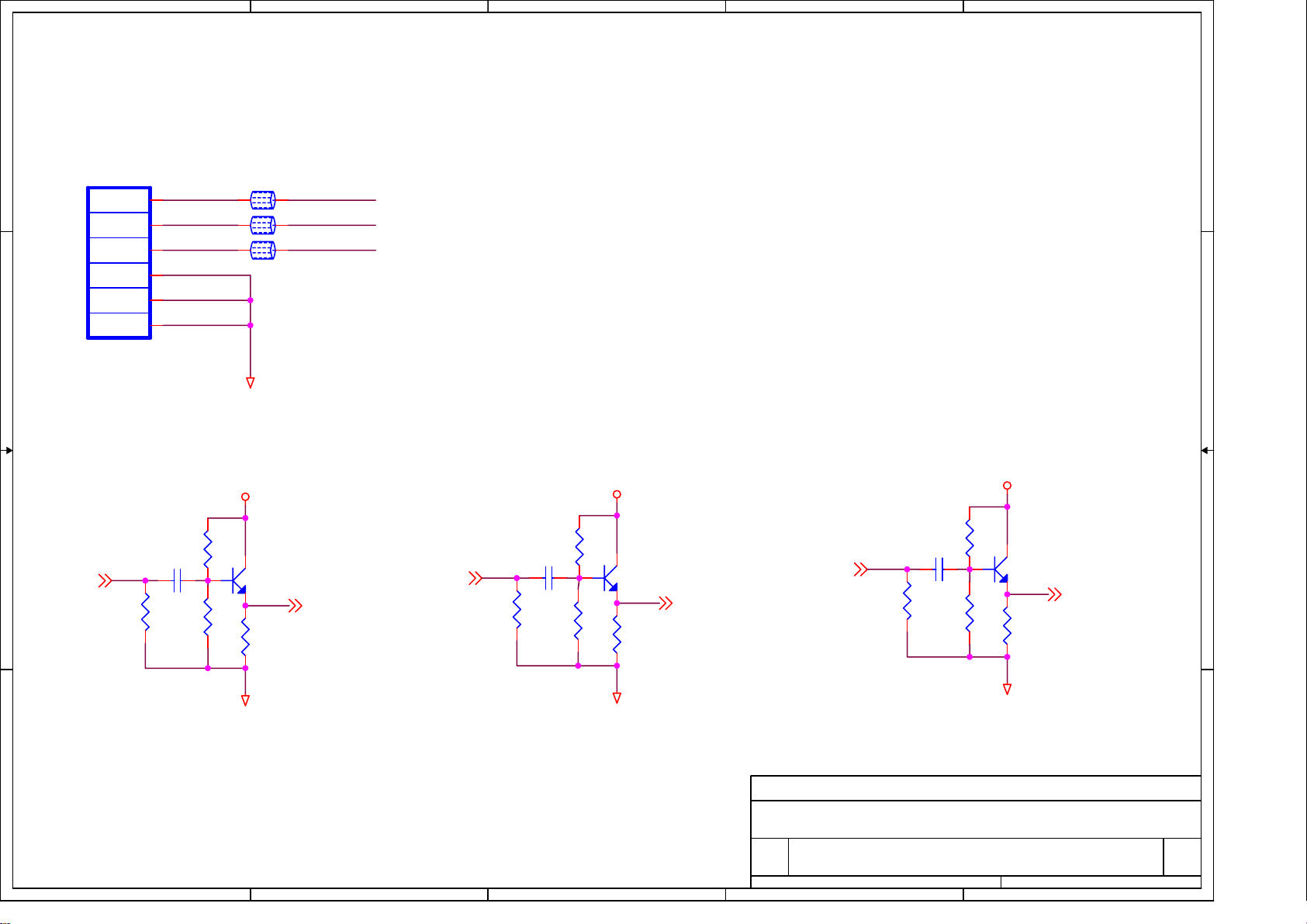

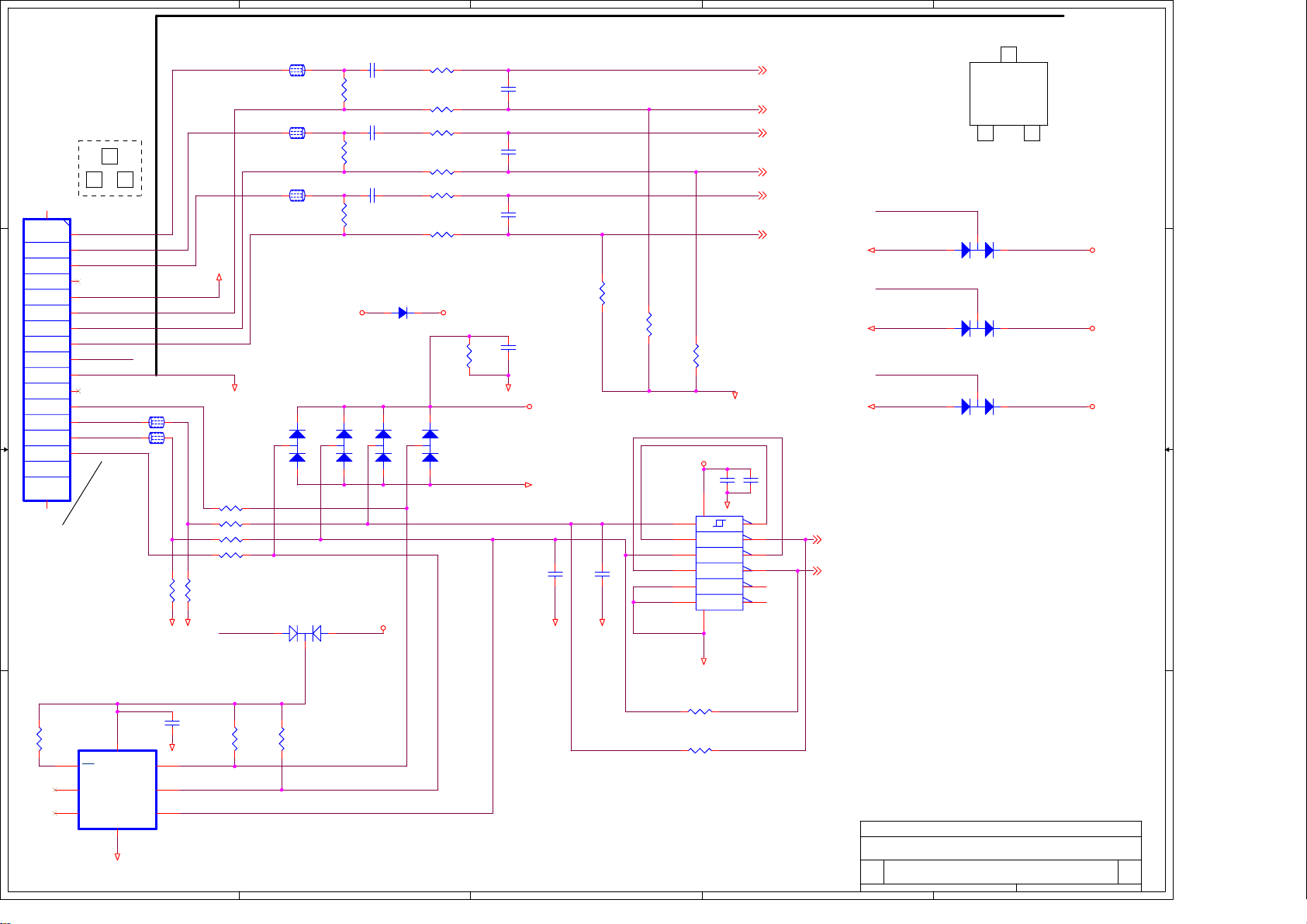

Page 2

5

D D

YCBCR

4

3

2

1

P17

1

Y

2

Cb

3

Cr

4

GND

5

GND

6

GND

C C

JST-S6B-PH-K

1 2

FB95

1 2

FB88

1 2

FB96

Y_in

Pb_in

Pr_in

GND

C539/C542/C545 $4,10u/10V

L+5V

R252

68k

B B

Y_in

Y_in

C539

R261

82

10u

R253

68k

1

3

Q10

MMBT2222ALT1

2

HD_Y 3

R254

1k

Pr_in

Pr_in

R262

82

R255

68k

C542

10u

R256

68k

GND

A A

使用无极性铝电解电容

L+5V

3

1

Q11

MMBT2222ALT1

2

R257

1k

GND

HD_V 3

Pb_in

Pb_in

R263

82

R249

68k

C545

10u

R250

68k

L+5V

3

1

Q14

MMBT2222ALT1

2

HD_U 3

R251

1k

GND

Title

LCD42B66 YPbPr_domestic

Size Document Number Rev

<Doc> 00

A

5

4

3

Date: Sheet

2

217Thursday, July 28, 2005

of

1

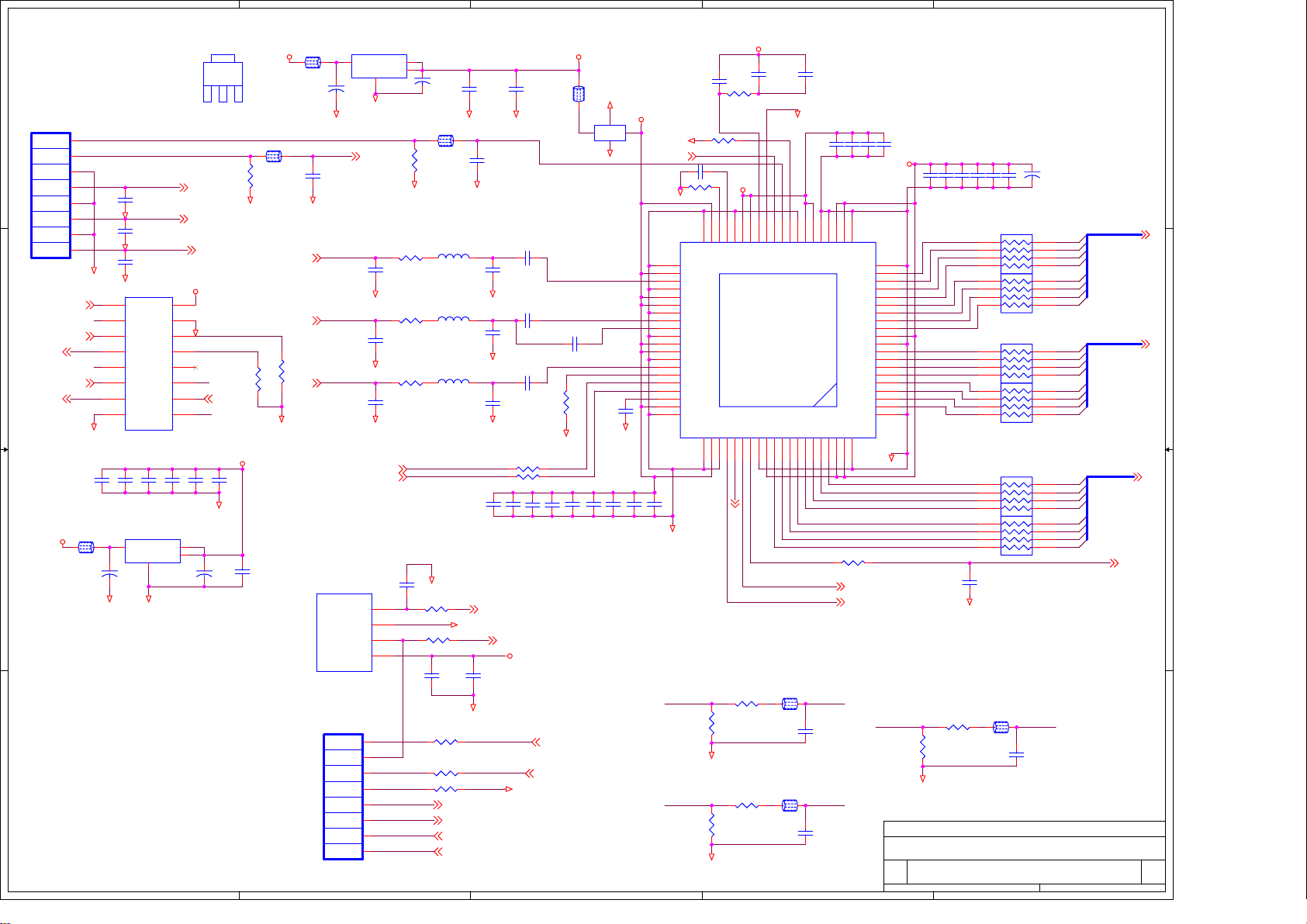

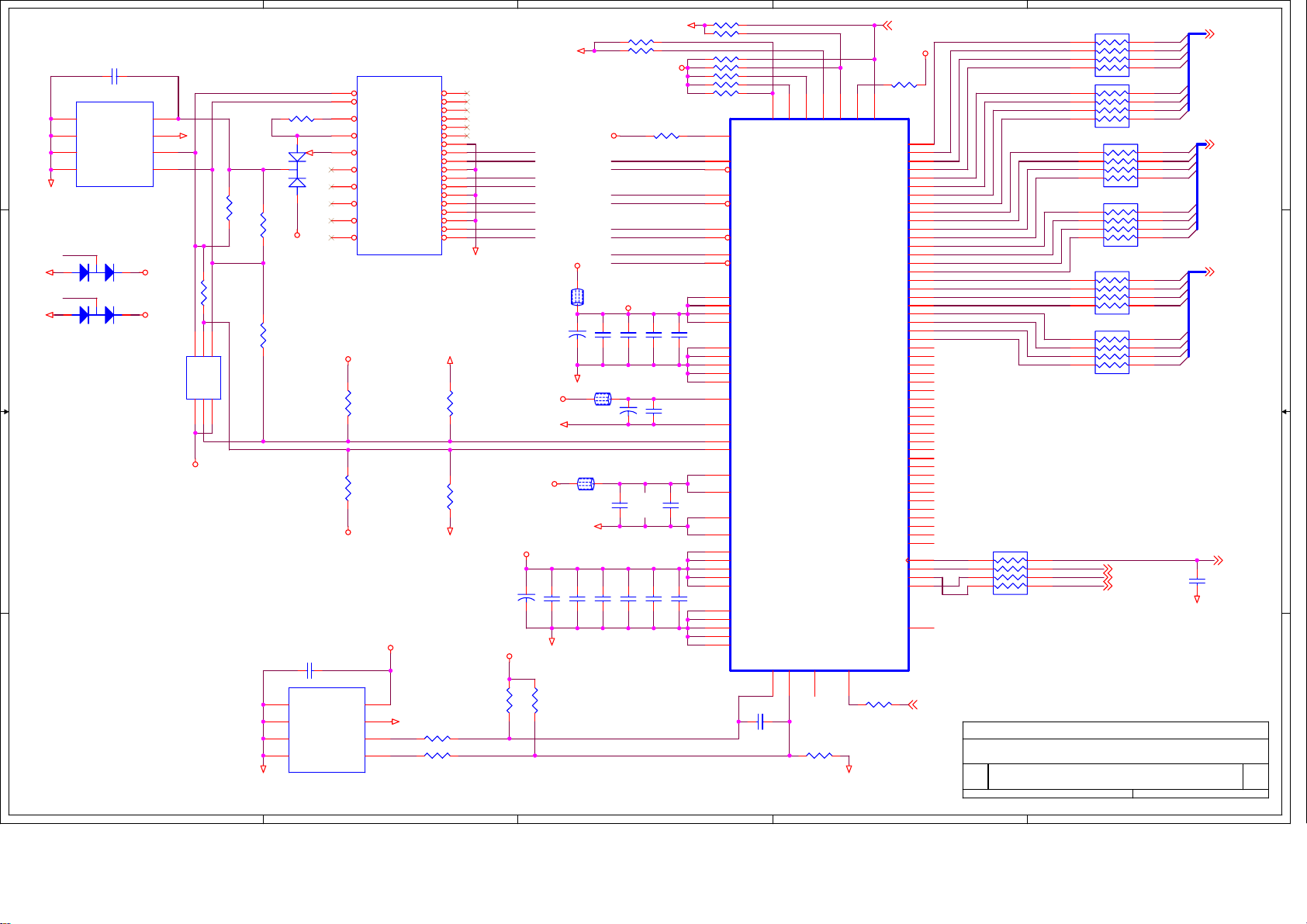

Page 3

5

4

3

2

1

C216

0.1uF

C28

0.1u

15,16

SCL_analog

SDA_analog

C29

100

AD_HS

C561

GND

C30

0.1u

PVDD

1nF

R10

4k7

1 2

GND

0.1u

15

C31

3

FB90

GND

CX5

CX

15

C26

0.1uF

C32

0.1u

GND

C6

3.9nF

3.3AN

GND

R3 10K

AD_VSAD_VS

C8 0.1uF

R610K

GND

40

41

GND

42

VD

43

BAIN

44

GND

45

VD

46

VD

47

GND

48

GAIN

49

SOGIN

50

GND

51

VD

52

VD

53

GND

54

RAIN

55

A0

56

SCA

57

SDA

58

REF BYP

59

VD

60

GND

61626364656667686970717273747576777879

C34

C33

0.1u

0.1u

GND

S1A S1AA

GND

S1B S1BB

GND

3 2

12

C4

GND

C35

47pF

U

Y

V

P25

4pin

Intr_main#

2596_on/light

P2

2596_ON_

GND

JST-S6B-PH-K

LM1117MPX-3.3

U1

IN OUT

1

GND

C23 4.7pF

GND

GND

GND

MC_SCLK4,10,15

MC_DATA4,10,15

1

2

GND

3

4

+3.3V

1

SCL

2

3

SDA

4

5

I/O1

6

INT

7

IO

8

IO

4

GND

C21

4.7pF

C25

4.7pF

C562

0.001u

TAB

R7 120

R11

4

12

C2

47uF/10V/5x5.4

1 2

R4

4.7K

GND

R8

150

150

MC_SCLK

MC_DATA

GND

R215

R201 0

R200

R5

GND

FB3

GND

L3

0

GND

0

L2

C93 open

GND

L4 0

GND

C19

0.1u

0

GND

C571

0.01u

GND

R199

470

SCL_analog

470

SDA_analog

0

REST_Analog 15

INTR_analog 15

P3.4

4,15

P1.4 15

C3

0.1uF

GND

C7

47pF

C92

open

C175

open

R12 100

R13

C27

0.1u

REMOT

2596_on

C572

1u

C22

10u/16v

C20

10u/16v

C24

10u/16v

0.1u

15

L+5V

GND

FB2

+5V

FB7

1 2

R14

4.7K

R272

R271

4k7

4k7

GND

C476

open

Com port with

Analog_board

定义

251

P1.6

P1.5

P1.3

INT0/P3.2

P1.4

1 2

47uF/10V/5x5.4

AD_VSVSYNC

GND

U

Y

V

4

123

LM1117MPX-3.3

9332-9883

D D

P1

GND

GND

GND

JST-S8B-PH-K

CTRL_SOURCE10

C C

Y

U

+12V

B B

A A

HS

VS

V

U

Y

HD_Y2

HD_U2

1

2

3

4

5

6

7

8

GND

Y

U

GND

FB75

1 2

HSYNC

C42

47pF

GND

C43

47pF

GND

C44

47pF

GND

U37

1

IN

S1AA

2

S1A

3

S2A

4

DA

S1BB

5

S1B

6

S2B

7

DB

8 9

GND DC

PIV

C547

C544

0.1u

0.1u

LM1117MPX-5

U38

3 2

IN OUT

12

C475

10uF/35V

GND

5

C541

0.1u

GND

S1C

S1B

S1A

VCC

S1D

S2D

DD

S1C

S2C

GND

1

SOT223

S1C

GND

S1B

S1A

L+5V

16

15

EN

GND

14

13

12

S1CC

11

10

HD_V 2

V

C543

0.1u

TAB

4

C546

0.1u

C540

0.1u

GND

12

C474

10uF/16V

L+5V

AD_VS

VD

GND

CLAMP

GNDVDGND

R21

R19

PVDD

GND

open

C179

GND

VD

GND

COAST

VSYNC

HSYNC

R2 3.3K

PVDD

PVD

GND

MIDSCV

PVD

39nF

C5

FILT

LQFP80

AD9883

VSOUT

SOGOUT

HSOUT

DATACK

GND

VDD

RED7

RED6

RED5

RED4

RED3

SOG

R20

R18

4

排版时应注意 下面的 层不走线!

L7

12

C46

L6

12

C45

C17

C16

C15

0.1uF

0.1uF

1nF

21222324252627282930313233343536373839

VD

VDD

VDD

GND

GND

GND

GND

BLUE0

BLUE1

BLUE2

BLUE3

BLUE4

BLUE5

BLUE6

BLUE7

VDD

GND

GREEN0

GREEN1

GREEN2

GREEN3

GREEN4

GREEN5

GREEN6

GREEN7

GND

RED2

RED1

RED0

VDD

VDD

GND

80

R15 22R

2300_HS

2300_VS

TDA9883 TOP

2

C18

3.3V

1nF

AD9883

U3

S1C S1CC

C9

0.1uF

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

GND

4

4

GND

Title

LCD42B66 AD9883 INTERFACE

Size Document Number Rev

<Doc> 00

Custom

Date: Sheet

R17

C12

C10

C11

C13

0.1uF

0.1uF

1nF

1nF

C37

open

GND

R16

C14

1nF

RP1 22Rx4

RP2 22Rx4

RP3 22Rx4

RP4 22Rx4

RP5 22Rx4

RP6 22Rx4

L5

12

C36

12

47uF/6V/5x5.4

C1

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

1

DU0

DU1

DU2

DU3

DU4

DU5

DU6

DU7

DY0

DY1

DY2

DY3

DY4

DY5

DY6

DY7

DV0

DV1

DV2

DV3

DV4

DV5

DV6

DV7

DU[0..7]

DU[0..7] 4

DY[0..7]

DY[0..7] 4

DV[0..7]

DV[0..7] 4

P_CLK

317Thursday, July 28, 2005

of

4

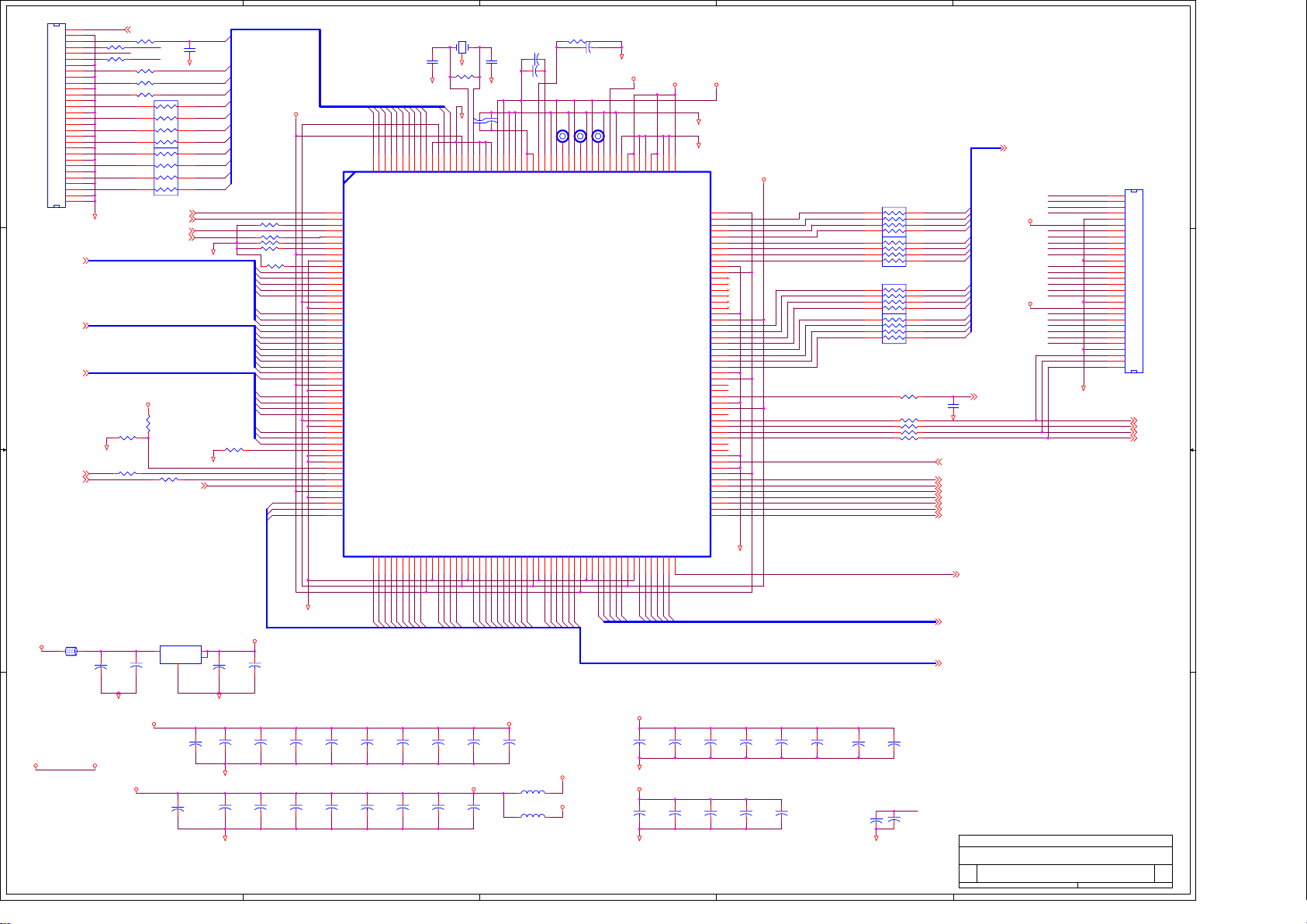

Page 4

GND

P_CLK2

R231 100

RES_2300#

R232 100

Hsync

Vsync

Field_ID

data_7

data_6

data_5

data_4

data_3

data_2

data_1

data_0

DU[0..7]

DV[0..7]

DY[0..7]

R242 4k7

GND

R244

5

100

P3.4 3,15

R229

MC_DATA

MC_SCLK

R233 22

R235 22

R236 22

4 5

3 6

2 7

1 8

4 5

3 6

2 7

1 8

3.3V

100

2300_HS3

2300_VS3

R238

open

R245 100

P2_CLK

12

C478

open

GND

P2_H

P2_V

P2_ID

22RX4RP36

P2_7

P2_6

P2_5

P2_4

P2_3

P2_2

P2_1

P2_0

22RX4RP37

P_CLK3

SOG3

GND

R275 open

GND

RES_2300#15

R224 4k7

R225 4k7

R226 4k7

R227 4k7

R228 4k7

SCL

SDA

DU0

DU1

DU2

DU3

DU4

DU5

DU6

DU7

DV0

DV1

DV2

DV3

DV4

DV5

DV6

DV7

DY0

DY1

DY2

DY3

DY4

DY5

DY6

DY7

DATA0

DATA1

DATA2

3.3V

P24A

30

30

29

29

28

28

27

27

26

26

25

25

24

24

23

23

22

22

21

21

20

20

19

19

18

18

17

17

16

16

D D

C C

15

15

14

14

13

13

12

12

11

11

10

10

9

9

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

DU[0..7]3

DV[0..7]3

DY[0..7]3

MC_SCLK3,10,15

MC_DATA3,10,15

1

HSYNC1_PORT1

2

VSYNC1_PORT1

3

FIELD ID1_PORT1

4

IN_CLK1_PORT1

5

HSYNC2_PORT1

6

VSYNC2_PORT1

7

FIELD ID2_PORT1

8

VDD1(3.3)

9

VSSio

10

IN_CLK2_PORT1

11

PORT1_A0

12

PORT1_A1

13

PORT1_A2

14

PORT1_A3

15

PORT1_A4

16

VDDcore1(1.8)

17

VSScore

18

PORT1_A5

19

PORT1_A6

20

PORT1_A7

21

PORT1_B0

22

PORT1_B1

23

PORT1_B2

24

PORT1_B3

25

PORT1_B4

26

PORT1_B5

27

PORT1_B6

28

PORT1_B7

29

PORT1_C0

30

VDD2(3.3)

31

VSSio

32

PORT1_C1

33

PORT1_C2

34

PORT1_C3

35

PORT1_C4

36

VDDcore2(1.8)

37

VSScore

38

PORT1_C5

39

PORT1_C6

40

PORT1_C7

41

IN_SEL

42

FILM SYNC_IN

43

DEV_ADDR1

44

DEV_ADDR0

45

SCLK

46

SDATA

47

RESET_N

48

VDD3(3.3)

49

VSSio

50

SDRAM DATA0

51

SDRAM DATA1

52

SDRM DT2

4

P2_ID

P2_V

P2_7

P2_H

208

207

206

205

FILDID_PRT2

VSYN_PORT2

HSYN_PORT2

P2_6

P2_5

204

203

PORT2_7

PORT2_6

PORT2_5

P2_3

P2_4

202

PORT2_4

P2_2

201

200

PORT2_3

PORT2_2

12

33pF/5%

GND

P2_1

199

198

PORT2_1

3

DAC_VREFOUT

180

179

DAC_RSET

R

probe

178

177

DAC_COMP

DAC_AVSSR

DAC_AVDDR(3.3)

187/1%

G

probe

1

176

175

174

DAC_ROUT

DAC_AVSSG

R230

1

173

DAC_GOUT

DAC_AVDDG(3.3)

C477

.1uF/50V

B

probe

1

172

171

170

169

DAC_BOUT

DAC_AVSSB

DAC_AVDDB(3.3)

168

DAC_VSS

GND

DAC1.8V

167

DAC_PVSS

DAC_VDD(1.8)

ANALOG GND

166

165

164

163

162

AVSS_PLL_FE

AVSS_PLL_SDI

AVSS_PLL_BE2

AVDD_PLL_FE(1.8)

AVDD_PLL_SDI(1.8)

PLL1.8V

161

160

159

158

157

PLL_PVSS

PLL_PVDD(1.8)

AVSS_PLL_BE1

VID_OUT7

AVDD_PLL_BE2(1.8)

AVDD_PLL_BE1(1.8)

VID_OUT6

VID_OUT5

VID_OUT4

VID_OUT3

VID_OUT2

VID_OUT1

VID_OUT0

VDD8(3.3)

VID_OUT15

VID_OUT14

VID_OUT13

VID_OUT12

VID_OUT11

VID_OUT10

VDDcore7(1.8)

VID_OUT9

VID_OUT8

VID_OUT23

VID_OUT22

VID_OUT21

VID_OUT20

VID_OUT19

VID_OUT18

VDD7(3.3)

VID_OUT17

VID_OUT16

VDDcore6(1.8)

CTLOUT4

CTLOUT3

CTLOUT2

CTLOUT1

CTLOUT0

TEST OUT1

TEST OUT0

SDRAM CLKIN

VDD6(3.3)

SDRAM CLKOUT

GND

GND

VSSio

VSScore

VSSio

CLKOUT

VSScore

TEST3

VSSio

CASN

RASN

DAC3.3V

+1.8VD

156

OE

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

DQM

109

CSN

108

BA0

107

BA1

106

105

X1

13.5MHz

1 2

C480

3

GND

R234

47K,5%

C483

GND

10UF/16V

P2_CLK

P2_0

197

196

195

194

193

192

191

190

VSSio

XTAL IN

VSScore

PORT2_0

VDD9(3.3)

XTAL OUT

VDDcore8(1.8)

IN_CLK_PORT2

GND

+

189

TEST2

12

188

TEST1

C481

33pF/5%

C484

187

TEST0

DAC_PVDD(3.3)

0.1uF/50V

186

185

184

DAC_AVSS

DAC_GR_AVSS

DAC_GR_AVDD(3.3)

C479

10UF/16V

C482

.1uF/50V

183

182

DAC_VREFIN

DAC_AVDD(3.3)

U39

+

181

s2300

SDRAM_CLKIN

SDRAM_CLK

DQM

CSN

BA0

BA1

CASN

RASN

2

PC[15..0] 10

RP38 22Rx4

G/Y6

G/Y5

G/Y4

G/Y3

G/Y2

G/Y1

G/Y0

B/U/C7

B/U/C6

B/U/C5

B/U/C4

B/U/C3

B/U/C2

B/U/C1

B/U/C0

G/Y7

RP39 22Rx4

RP40 22Rx4

RP41 22Rx4

R237 22

R239 22

R240 22

R241 22

R243 22

45

36

27

18

45

36

27

18

45

36

27

18

45

36

27

18

PC15

PC14

PC13

PC12

PC11

PC10

PC9

PC8

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

C560

open

SDRAM_CLKIN 5

SDRAM_CLK 5

DQM 5

CSN 5

BA0 5

BA1 5

CASN 5

RASN 5

DI_YCLK

GND

2.5V

3.3V

10

P3.4

RES_2300#

MC_DATA

MC_SCLK

DI_YCLK

PC15

PC14

PC13

PC12

PC11

PC10

PC9

PC8

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

1

P28A

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

GND

DI_HREF 10

DI_VREF 10

DI_VSYNC 10

DI_HSYNC 10

SDRAM DATA3

SDRAM DATA4

SDRAM DATA5

SDRAM DATA6

SDRAM DATA7

SDRAM DATA8

SDRAM DATA9

SDRAM DATA10

SDRAM DATA11

VDD4(3.3)

VSSio

SDRAM DATA12

SDRAM DATA13

SDRAM DATA14

SDRAM DATA15

VDDcore3(1.8)

VSScore

SDRAM DATA16

SDRAM DATA17

SDRAM DATA18

SDRAM DATA19

SDRAM DATA20

SDRAM DATA21

SDRAM DATA22

SDRAM DATA23

SDRAM DATA24

SDRAM DATA25

VDDcore4(1.8)

VSScore

SDRAM DATA26

SDRAM DATA27

SDRAM DATA28

SDRAM DATA29

SDRAM DATA30

SDRAM DATA31

VDD5(3.3)

VSSio

TEST IN

SDRAM ADDR10

SDRAM ADDR9

SDRAM ADDR8

SDRAM ADDR7

SDRAM ADDR6

VDDcore5(1.8)

VSScore

SDRAM ADDR5

SDRAM ADDR4

SDRAM ADDR3

SDRAM ADDR2

SDRAM ADDR1

SDRAM ADDR0

B B

GND

4

+

C489

100uF/16V

+

100UF/16V

GND

GND

GND

C487

+1.8VD

C490

.1uF/50V

C508

.1uF/50V

12

C488

.1uF/50V

C491

.1uF/50V

C509

.1uF/50V

C492

.1uF/50V

C510

.1uF/50V

GND

+1.8VD

5

LM1117MPX-1.8

U40

3 2

IN OUT

12

C486

.1uF/50V

+3.3VD

GND

1

+

100uF/16V

TAB

C507

FB76

3.3V

1 2

+

C485

100UF/16V

+3.3VDDAC3.3V

A A

5354555657585960616263646566676869707172737475767778798081828384858687888990919293949596979899

DATA26

DATA29

DATA31

DATA30

DATA28

DATA23

DATA22

12

.1uF/50V

DATA24

C498

L8

L9

DATA27

DATA25

DAC1.8V

5.6uH

PLL1.8V

5.6uH

C493

.1uF/50V

C511

.1uF/50V

DATA7

DATA4

DATA3

DATA6

DATA9

DATA8

DATA5

DATA10

DATA11

C494

C495

.1uF/50V

.1uF/50V

C513

C512

.1uF/50V

.1uF/50V

4

DATA18

DATA16

DATA13

DATA14

DATA15

C496

.1uF/50V

+1.8V

C514

.1uF/50V

DATA17

DATA19

C497

.1uF/50V

C515

.1uF/50V

DATA21

DATA20

3.3V

DATA12

ADDR10

3

ADDR9

ADDR8

ADDR7

ADDR6

DAC3.3V

PLL1.8V

100

101

ADDR4

ADDR5

ADDR2

ADDR3

C499

.1uF/50V

GND_ANALOG

C516

.1uF/50V

GND_PLL

102

ADDR1

103

ADDR0

WEN

104

C500

.1uF/50V

C517

.1uF/50V

ADDR[0..10]

C501

.1uF/50V

C518

.1uF/50V

GND

C502

.1uF/50V

C519

.1uF/50V

WEN

C503

.1uF/50V

C520

.1uF/50V

DATA[0..31]

C504

.1uF/50V

2

C521

10UF/16V

+

C505

47UF/16V

+

C506

47UF/16V

DAC1.8V

+

C522

.1uF/50V

GND

WEN 5

ADDR[0..10] 5

SDRAM_DATA[0..31] 5

Title

LCD42B66 S2300 DEINTERLACE

Size Document Number Rev

03 00

C

Date: Sheet

417Thursday, July 28, 2005

1

of

Page 5

5

4

3.3V

3

2

1

FB93

D D

ADDR[0..10]

4

C C

DQM4

BA04

BA14

WEN4

CASN4

RASN4

B B

4

SDRAM_CLK4

SDRAM_CLKIN

CSN4

SDRAM_CLK

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4 DATA4

ADDR5

ADDR6

ADDR7

ADDR8 DATA8

ADDR9

ADDR10

DQM

BA0

BA1

WEN

CASN

RASN

CSN

R246 100/5%

SDRAM_CLKIN

FB94

R247

NL

GND

12

RP42 22Rx4

45

36

27

18

RP43 22Rx4

45

36

27

18

RP44 22Rx4

45

36

27

18

3.3V

12

25

26

27

60

61

62

63

64

65

66

24

14

21

30

57

69

70

73

16

71

28

59

22

23

17

18

19

20

68

67

R248

4k7/5%

C523

.1uF/50V

U35

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

NC

NC

NC

NC

NC

NC

NC

DQM0

DQM1

DQM2

DQM3

BA0

BA1

WE

CAS

RAS

CS

CLK

CKE

GND

C524

.1uF/50V

186

VDDVSS

C525

.1uF/50V

GND

15

29

43

VDD

VDD

VDD

KM432S2030C

86 PIN TSOP

KM432S2030C

VSS

VSS

VSS

72

58

44

3935414946

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

63212

38

557581

VDDQ

VDDQVSSQ

VSSQ

527884

VDDQ

VSSQ

VDDQ

VSSQ

GND

GND

C526

+

2.2uF/25V

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

2

4

5

7

8

10

11

13

74

76

77

79

80

82

83

85

31

33

34

36

37

39

40

42

45

47

48

50

51

53

54

56

DATA0

DATA1

DATA2

DATA3

DATA5

DATA6

DATA7

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

DATA16

DATA17

DATA18

DATA19

DATA20

DATA21

DATA22

DATA23

DATA24

DATA25

DATA26

DATA27

DATA28

DATA29

DATA30

DATA31

DATA[0..31]

SDRAM_DATA[0..31] 4

3.3V

A A

C527

0.1uF

GND

5

C528

0.1uF

C529

0.1uF

DECOUPLING FOR SDRAM

C530

0.1uF

4

C531

0.1uF

C532

0.1uF

C533

0.1uF

C534

0.1uF

C535

0.1uF

3

C536

0.1uF

C537

0.1uF

C538

0.1uF

Title

LCD42B66 S2300 SDRAM

Size Document Number Rev

04 00

B

Date: Sheet

2

517Thursday, July 28, 2005

of

1

Page 6

5

4

3

2

1

AGREEN1P 7

ABLUE1P 7

ABLUE1N 7

TO JAGASM ADC

RED1

GND

GREEN1

GND

BLUE1

GND

VGA_HSYNC 10

VGA_VSYNC 10

1

3

D10

1 2

BAV99

3

D11

1 2

BAV99

3

D12

1 2

BAV99

3

2

A+5V

A+5V

A+5V

RED1

D D

3

21

1617

RED

MH1MH2

GREEN

BLUE

GND

RGND

GGND

BGND

VCC

GND

HSYNC

VSYNC

ID2

ID0

BAV99 FOOTPRINT

RED1

1

GREEN1

2

BLUE1

3

4

5

6

7

8

VGA_+5V

9

10

11

DDDA

12

PHSI1

13

PVSI1

14

DDCK

15

FB12

12

12

FB13

R48

1K

GND GND GND GND

VGA

P11

C C

DDDA(ID1)

DDCK(ID3)

ASTRON HDB600-15

CUT IN GND

PLANE AND JOIN

B B

NEAR JAG

RED-GND

GREEN1

BLUE1

GND

GND

R44 100R

R45 100R

100R

R46

100R

R47

R49

1K

VGA_+5V +5V

FB55

1 2

FB56

1 2

FB57

1 2

3

1 2

D7

BAT54C/BAV70

1

SOT23

D1

3

3

+5V

1 2

2

C75

R29

1u

75 1%

C77

R33

1u

75 1%

GREEN-GND

C79

R37

1u

75 1%

BLUE-GND

D2

3

+5V

R30

R34

R38 0R

D21

DIODE

D3

1 2

R28 75 1%

0R

R32 75

0R 1%

R36 75 1%

A+5V

D4

3

BAV99

1 2

C76

2.2pf

C78

2.2pf

C80

2.2pf

R286

C573

100R

1u

GND

A+5V

CUT IN GND PLANE AND

JOIN NEAR ANALOG

POWER SUPPLY

GND

C85

100pf

C86

100pf

R211

0

ARED1N

AGREEN1N

R210

0

1

3

5

9

11

13

3.3V

GND

C558

0.01u

147

U41

7414

R209

0

GND

ARED1P 7

ARED1N 7

AGREEN1N 7

GND

C559

1u

2

4

6

8

10

12

R285

open

SDA

SCL

5

6

7

GND

C87

0.1uF

R51

10K

R52

10K

R284

open

Title

LCD42B66 VGA CONNECTOR

Size Document Number Rev

<Doc> 00

Custom

4

3

Date: Sheet

2

617Thursday, July 28, 2005

of

1

R50

10K

3

A A

1

2

EDID

DATA

8

U8

WC

VCC

DDC

NC1

GND

GND

4

5

VCLK

ST24FW21

NC2

Page 7

5

C454

10pF

C89

1 2

GND

D D

GND

UNDER THESE LINES GND PLANE MUST

BE CUT FROM VGA AS SHOWN ON VGA

SHEET.

C C

ARED1N

6

6

ARED1P

AGREEN1N6

AGREEN1P

6

ABLUE1N6

6

ABLUE1P

B B

A A

5

U10

1

N

2

OVDG

14.318MHz OSC

1nF

4

3

FB16

GND

GND

2.5V

4

3.3V

R5322R

C94

10pF

GND

U11D

A10

R2N

A11

R2P

A14

G2N

A15

G2P

A18

B2N

A19

B2P

A12

R1N

A13

R1P

A16

G1N

A17

G1P

A20

B1N

A21

B1P

A8

I1

A9

I2

C15

RREFH

C14

RREFL

C17

GREFH

C16

GREFL

C19

BREFH

C18

BREFL

C13

IREFH

C12

IREFL

JAGUAR

VDDP1

VDDP2

B22

C22

A22

FB21

12

C117

GND GND

C118

1nF

0.1uF

GND

DIGITAL PLL GND

4

A6

XIN

VSSP1

VSSP2

D22

GND

PVSS1

B20

A7

JAGUAR - ANALOG

B21

XOUT

GPVSS

R217

open

C119

0.1uF

D20

PVDD1

C120

0.1uF

C21

IVDD2

IVDD1

RVDD2

RVDD1

GVDD2

GVDD1

BVDD2

BVDD1

IVSS2

IVSS1

RVSS2

RVSS1

GVSS2

GVSS1

BVSS2

BVSS1

SVSS

SVDD

AVSS1

AVDD1

AVDD2

AVSS2

CVSS2

CVSS1

CVDD2

CVDD1

AVDD3

AVDD4

DVDD

DVSS

XVSS

XVDD

GPVDD

C121

1u

FB22

D11

D12

D13

D14

D15

D16

D17

D18

B11

B12

B13

B14

B15

B16

B17

B18

B19

D19

C20

C10

C11

C7

B8

B9

D8

D9

C8

C9

D10

B10

B7

D7

3

QUIET

ANALOG

GND

C103

C105

C107

0.1uF

C108

0.1uF

C111

0.1uF

GND

12

2.5V

3

GND

GND

1nF

GND

1nF

GND GND

GND

CAPTURE PLL GND

GND

C113

0.1uF

GND

C115

0.1uF

GND

GND

C109

C96

1nF

1u

GND

+5V

C104

10uF/16V

C106

1uF/25V

R212

C110

1u

C112

C114

10uF/16V

C116

10uF/16V

GND

GND

1u

1 2

R54

10R

R55

10R

47

R56

47

R57

10

FB19

FB20

FB15

C98

0.1uF

12

12

C90

10uF/16V

C99

0.1uF

GND

C100

0.1uF

JA2.5V1

JA2.5V1

JA2.5V2

JA2.5V2

JA2.5V1

3.3V

2

LM1117MPX-2.5

U9

3 2

IN OUT

TAB

GND

1

GND

JA2.5V1

C101

C102

0.1uF

1nF

2

1

2.5V ANALOG POWER

4

C91

10uF/16V

Title

LCD42B66 JAGUAR ANALOG INTERFACE

Size Document Number Rev

<Doc> 00

Custom

Date: Sheet

1

FB14

1 2

FB17

1 2

717Thursday, July 28, 2005

JA2.5V1

JA2.5V2

of

Page 8

5

3.3V

C122

C123

0.1uF

0.1uF

D D

C124

0.1uF

C125

0.1uF

C126

0.1uF

GND

C C

TSA1

TSA0

TSA2

TSA3

SA1

18

SA0

27

SA2

36

SA3

45

RP11

TSA5

TSA6

SA5 SA5

18

SA4

27

36

45

22RX4

RP13

B B

TSA8

TSA7

TSA10

TSA9

22RX4

RP15

SA8

18

SA7

27

SA10

36

SA9

45

C127

0.1uF

4

A26

J26

N26

U11B

SD0

AD22

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

SD16

SD17

SD18

SD19

SD20

SD21

SD22

SD23

SD24

SD25

SD26

SD27

SD28

SD29

SD30 TSDQM

SD31

SA0

SA1

SA2

SA3

SA4

SA6

SA7

SA8

SA9

SA10

SDD00

AE22

SDD01

AC23

SDD02

AD23

SDD03

AE23

SDD04

AC24

SDD05

AD24

SDD06

AE24

SDD07

AF24

SDD08

AC25

SDD09

AD25

SDD10

AE25

SDD11

AF25

SDD12

AD26

SDD13

AE26

SDD14

AB24

SDD15

AB25

SDD16

AB26

SDD17

AA23

SDD18

AA24

SDD19

AA25

SDD20

AA26

SDD21

Y23

SDD22

Y24

SDD23

Y25

SDD24

W24

SDD25

W25

SDD26

W26

SDD27

L23

SDD28

L24

SDD29

L25

SDD30

K24 K25

SDD31 SDD32

V23

SDA0

V24

SDA1

V25

SDA2

V26

SDA3

U23

SDA4

U24

SDA5

U25

SDA6

P25

SDA7

P26

SDA8

N24

SDA9

N25

SDA10

JAGUAR

U26

VDD

VDD

VDD

VDD

VSS

VSS

VSS

A23

F26

L26

R26

VSS

3

Y26

AF26

D23

K23

T23

AB23

D21

SD63

A25

N23

VDDC

VSSC

VDDC

VSSC

W23

SDD63

VDDC

SDD62

SDD61

SDD60

SDD59

SDD58

SDD57

SDD56

SDD55

SDD54

SDD53

SDD52

SDD51

SDD50

SDD49

SDD48

SDD47

SDD46

SDD45

SDD44

SDD43

SDD42

SDD41

SDD40

SDD39

SDD38

SDD37

SDD36

SDD35

SDD34

SDD33

BANK

DQM

SDCS0

SDCKN

SDRAS#

SDWE#

SDCKE

SDCAS#

SDCKP

SDCKFB

MEMCLK

DQS

A24

B26

B25

B24

B23

C26

C25

C24

C23

D26

D25

D24

E26

E25

E24

E23

F25

F24

F23

G26

G25

G24

H26

H25

H24

H23

J25

J24

J23

K26

M25

M24

M23

M26

P23

P24

R25

R24

T26

R23

T25

T24

SBA#

SDQM

SCS#

SRAS#

SWE#

SCKE

SCAS#

SCLK

SD62

SD61

SD60

SD59

SD58

SD57

SD56

SD55

SD54

SD53

SD52

SD51

SD50

SD49

SD48

SD47

SD46

SD45

SD44

SD43

SD42

SD41

SD40

SD39

SD38

SD37

SD36

SD35

SD34

SD33

SD32

R190

100

VDD

VDD

VDDC

VDDC

JAGUAR - SDRAM

VSS

VSS

VSSC

AC26

AF23

G23

SD[63..0]

C128

0.1uF

2

C129

0.1uF

SD[63..0]

C130

0.1uF

9

GND

SDQM

SBA#

SCS#

22RX4

RP12

SRAS#

SWE#

SCKE#

SCAS#

22RX4

RP14

R60

22R

GND

GND

X1

15

C131

0.1uF

18

TSBA0

27

R58 0R

36

R59 0R22RX4

45

OR6 open

TSRAS#TSA4

18

TSWE#SA6

27

36

TSCAS#

45

TSCLK

FB23

1 2

1

2.5V

TSDQM 9

TSBA0

TSRAS# 9

TSWE# 9

TSCKE 9

TSCAS# 9

TSCLK 9

9

TSCS#

TSBA1

9

9

TSA[10..0]

A A

5

4

TSA[10..0] 9

Title

LCD42B66 JAG SARAM INTERFACE

Size Document Number Rev

<Doc> 00

Custom

3

2

Date: Sheet

817Thursday, July 28, 2005

1

of

Page 9

5

SD[63..0]

8

TSA[10..0]8

SD[63..0]

TSA[10..0]

4

3

2

1

3.3V 3.3V

3935

D D

TSA0

TSA1

TSA2

TSA3

TSA4

TSA5

TSA6

TSA7

TSA8

TSA9

TSA10

C C

R61

10k

GND

U12

25

A0

26

A1

27

A2

60

A3

61

A4

62

A5

63

A6

64

A7

65

A8

66

A9

24

A10/AP

14

NC1

21

NC2

30

NC3

57

NC4

69

NC5

70

NC6

73

NC7

22

BA0

23

BA1

20

CS

67

CKE

68

CLK

19

RAS

18

CAS

17

WE

16

DQM0

71

DQM1

28

DQM2

59

DQM3

41

VCCQ

VCCQ

VCCQ

K4S643232C

VSSQ

VSSQ

VSSQ

61232

38

49

VCCQ

VSSQ

46

VCCQ

VSSQ

52 55

VSSQ VCCQ

75

78

81

VCCQ

VSSQ

84

VCCQ

VSSQ

1

15

29

VCC

VCC

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VSS

VSS

44

58

72

VCC

2

4

5

7

8

10

11

13

74

76

77

79

80

82

83

85

31

33

34

36

37

39

40

42

45

47

48

50

51

53

54

56

VSS

VSS VCC

K4S643232C-TC/L70

86 43

3935

U13

SD0

SD1

SD3

SD4

SD5

SD6 SD38

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

SD16

SD17

SD18

SD19

SD20

SD21

SD22

SD23

SD24

SD25

SD26

SD27

SD28

SD29

SD30

SD31

TSA0

TSA1

TSA2

TSA3

TSA4

TSA5

TSA6

TSA7

TSA8

TSA9

TSA10

25

A0

26

A1

27

A2

60

A3

61

A4

62

A5

63

A6

64

A7

65

A8

66

A9

24

A10/AP

14

NC1

21

NC2

30

NC3

57

NC4

69

NC5

70

NC6

73

NC7

22

BA0

23

BA1

20

CS

67

CKE

68

CLK

19

RAS

18

CAS

17

WE

16

DQM0

71

DQM1

28

DQM2

59

DQM3

41

VCCQ

VCCQ

VCCQ

K4S643232C

VSSQ

VSSQ

VSSQ

61232

38

49

VCCQ

VSSQ

46

VCCQ

VSSQ

52 55

VSSQ VCCQ

75

VCCQ

VSSQ

78

81

84

VCCQ

VSSQ

1

15

VCC

VCC

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VSS

VSS

44

58

29

VCC

2

4

5

7

8

10

11

13

74

76

77

79

80

82

83

85

31

33

34

36

37

39

40

42

45

47

48

50

51

53

54

56

VSS

VSS VCC

K4S643232C-TC/L70

72

86 43

SD32

SD33

SD34SD2

SD35

SD36

SD37

SD39

SD40

SD41

SD42

SD43

SD44

SD45

SD46

SD47

SD48

SD49

SD50

SD51

SD52

SD53

SD54

SD55

SD56

SD57

SD58

SD59

SD60

SD61

SD62

SD63

GND

B B

GND

TSBA0 8

TSBA1 8

TSCS# 8

TSCKE 8

TSCLK 8

TSRAS# 8

TSCAS# 8

TSWE# 8

TSDQM 8

3.3V

C133

C132

0.1uF

0.1uF

GND

A A

3.3V

C147

C146

0.1uF

0.1uF

C134

0.1uF

C148

0.1uF

GND

5

DECOUPLING FOR SDRAMS

C135

0.1uF

C149

0.1uF

C136

0.1uF

C150

0.1uF

C137

0.1uF

C151

0.1uF

C138

0.1uF

C152

0.1uF

4

C139

0.1uF

C153

0.1uF

C140

0.1uF

C154

0.1uF

C141

0.1uF

C155

0.1uF

C142

0.1uF

C156

0.1uF

3

C143

0.1uF

C157

0.1uF

3.3V

GND

C144

22uF/16V

3.3V

GND

C145

22uF/16V

2

FB8012FB81

3.3V

Title

LCD42B66 SDRAM BASED FRAM BUFFER

Size Document Number Rev

<Doc> 00

Custom

FB8212FB83

Date: Sheet

12

12

917Thursday, July 28, 2005

1

of

Page 10

5

3.3V

PAB[7..0]14

D D

PAG[7..0]

14

PAR[7..0]14

DVICK14

DVIDE14

C C

B B

DVI_HSYNC14

DVI_VSYNC14

14

PD_DVI

VGA_HSYNC6

VGA_VSYNC6

DVICK

DDE

DVI_HSYNC

DVI_VSYNC

VGA_HSYNC

VGA_VSYNC

3.3V

GND

R218

4k7

C161

0.1uF

GND

GND

R73 4.7k

R75 4.7k

PAB0

PAB1

PAB2

PAB3

PAB4

PAB5

PAB6

PAB7

PAG0

PAG1

PAG2

PAG3

PAG4

PAG5

PAG6

PAG7

PAR0

PAR1

PAR2

PAR3

PAR4

PAR5

PAR6

PAR7

4

GND

AA2

AA3

P1

P2

N2

N3

M1

M2

M3

M4

L1

L2

L3

L4

K2

K3

K4

J1

J2

J3

J4

H1

H2

H3

G1

G2

G4

F1

F2

G3

E2

Y1

Y2

Y3

W1

W2

W3

W4

V1

V2

V3

V4

U1

U2

U3

U4

T1

T2

T3

T4

R1

R2

R3

P4

D6

C6

P3

C163

0.1uF

U11A

PA00

PA01

PA02

PA03

PA04

PA05

PA06

PA07

PA08

PA09

PA10

PA11

PA12

PA13

PA14

PA15

PA16

PA17

PA18

PA19

PA20

PA21

PA22

PA23

PCLKA

DEIN

HSYNC0

DVSYNC

PWM1/GPIO0

PB00

PB01

PB02

PB03

PB04

PB05

PB06

PB07

PB08

PB09

PB10

PB11

PB12

PB13

PB14

PB15

PB16

PB17

PB18

PB19

PB20

PB21

PB22

PB23

PCLKB

HSYNC1

HSYNC2

PBVSYNC

JAGUAR

A5H4K1

VDD

VDD

PORT APORT B

VSS

C1

AA1

N1

VDD

VSS

JAGUAR - DIGITAL

VSS

D4N4Y4

AC5

C162

0.1uF

VDDC

VSSC

R4

VDDC

VSSC

3

GND

AB4

VDDC

CLAMPOUT

HSYNCOUT

PORT C CPU

PCFIELD/GPIO3

PCVREF/GPIO2

VSSC

C158

0.1uF

MCAD0

MCAD1

MCAD2

MCAD3

MCAD4

MCAD5

MCAD6

MCAD7

MCA8

MCA9

MCCS#

MCALE

MCRD#

MCWR#

INTR#

SYSRST#

TEST

SDA

SCL

GPIO4

PC00

PC01

PC02

PC03

PC04

PC05

PC06

PC07

PC08

PC09

PC10

PC11

PC12

PC13

PC14

PC15

PCLKC

PCHREF

PCHSYNC

PCVSYNC

C159

0.1uF

MCAD0

B6

MCAD1

B5

MCAD2

C5

MCAD3

D5

MCAD4

A4

MCAD5

B4

MCAD6

A3

MCAD7

B3

MCA8

C3

MCA9

A2

C4

MCALE

D3

JRD#

E3

JWR#

E4

INTR_ASM#

D2

RESET#

E1

D1

R64 1k

F4

R65 1k

F3

A1

C2

B2

AF1

AF2

AF3

AF4

AE1

AE2

AE3

AE4

AD1

AD2

AD3

AD4

AC1

AC2

AC3

AC4

R72

AE5

AD5

AA4

AB2

AB3

AB1

FB25

1 2

C160

0.1uF

R63 10K

GPIO4:internal

PLL clock

output

R70 open

PC0

PC1

PC2

PC3

PC4

PC5

PC6

PC7

PC8

PC9

PC10

PC11

PC12

PC13

PC14

PC15

220

2.5V

MCAD[7..0]

MCA8 15

MCA9 15

GND

MCALE 15

JRD# 15

JWR# 15

GND

DI_VREF

DI_YCLK

DI_HREF

DI_HSYNC

DI_VSYNC

2

3.3V

R62

MCAD[7..0] 15

10K

INTR_ASM# 15

RESET# 15

MC_DATA 3,4,15

MC_SCLK 3,4,15

CTRL_SOURCE 3

PC[15..0] 4

DVI_RESET# 14

DI_VREF 4

DI_YCLK 4

DI_HREF 4

DI_HSYNC 4

DI_VSYNC 4

1

SAME COPPER ISLAND ON L4

A A

5

4

GND

GND

Title

LCD42B66 JAG DIGITAL INTERFACE

Size Document Number Rev

<Doc> 00

Custom

3

2

Date: Sheet

10 17Thursday, July 28, 2005

1

of

Page 11

5

FB26

2.5V

1 2

D D

C C

B B

C164

0.1uF

GND

C165

0.1uF

4

L11

L12

L13

L14

L15

L16

M11

M12

M13

M14

M15

M16

N11

N12

N13

N14

N15

N16

P11

P12

P13

P14

P15

P16

R11

R12

R13

R14

R15

R16

T11

T12

T13

T14

T15

T16

JAGUAR

C166

0.1uF

U11C

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSC

AC22

AC20

VDDC

VSSC

AC17

AC14

VDDC

VSSC

AC11

3

2

1

3.3V

PNLCLK

PENVDD

PENBKL

GND

P0

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

P21

P22

P23

P24

P25

P26

P27

P28

P29

P30

P31

P32

P33

P34

P35

P36

P37

P38

P39

P40

P41

P42

P43

P44

P45

P46

P47

C168

0.1uF

C167

0.1uF

AF10

AF16

AF21

AC8

AF5

PD00

VDD

VDD

VDD

VDDC

JAGUAR - PANEL

VSS

VSS

AF13

AF19

PVSYNC

PHSYNC

PSHFCLK

PNLCLK

PWM1

ENVDD

ENBKL

VSS

AF8

PD01

PD02

PD03

PD04

PD05

PD06

PD07

PD08

PD09

PD10

PD11

PD12

PD13

PD14

PD15

PD16

PD17

PD18

PD19

PD20

PD21

PD22

PD23

PD24

PD25

PD26

PD27

PD28

PD29

PD30

PD31

PD32

PD33

PD34

PD35

PD36

PD37

PD38

PD39

PD40

PD41

PD42

PD43

PD44

PD45

PD46

PD47

PDE

AC6

AD6

AE6

AF6

AC7

AD7

AE7

AF7

AD8

AE8

AC9

AD9

AE9

AF9

AC10

AD10

AE10

AD11

AE11

AF11

AC12

AD12

AE12

AD13

AE13

AD14

AE14

AF14

AC15

AD15

AE15

AF15

AC16

AD16

AE16

AD17

AE17

AF17

AC18

AD18

AE18

AF18

AC19

AD19

AE19

AD20

AE20

AC21

AE21

AF20

AC13

AF12

B1

AD21

AF22

PENVDD

PENBKL

C169

0.1uF

1 8

2 7

3 6

4 5

100RX4

R87 22R

12,13

12

RP28

P[23..0] 12

P[47..24] 12

PVSYNC

PHSYNC

PDE

PVSYNC 12,13

PHSYNC 13

PDE 12,13

PSHFCLK 12,13

R11_1

open

GND

PWM1 12

GNDGND

A A

Title

LCD42B66 JAG PANEL INTERFACE

Size Document Number Rev

<Doc> 00

Custom

5

4

3

2

Date: Sheet

11 17Thursday, July 28, 2005

of

1

Page 12

5

4

3

2

1

P[23..0]11

RP17

P0

P1

D D

C C

P3

100RX4

RP19

P4

4 5

P5

3 6

P6

2 7

P7

1 8

100RX4

RP21

P8

4 5

P9

3 6

P10

2 7

P11

1 8

100RX4

RP23

P12

4 5

P13

3 6

P14

2 7

P15

1 8

100RX4

RP25

P16

4 5

P17

3 6

P18

2 7

P19

1 8

100RX4

RP27

P20

4 5

P21

3 6

P22

2 7

P23

1 8

100RX4

FP0

18

FP1

27

FP2

36

FP3

45

FP4

FP5

FP6

FP7

FP8

FP9

FP10

FP11

FP12

FP13

FP14

FP15

FP16

FP17

FP18

FP19

FP20

FP21

FP22

FP23

11

FP[23..0]

P[47..24]

FP[23..0] 13

RP16

P24

4 5

P25

3 6

P27P2

2 7

P26

1 8

100RX4

RP18

P28

4 5

P31

3 6

P29

2 7

P30

1 8

100RX4

RP20

P32

4 5

P33

3 6

P34

2 7

P35

1 8

100RX4

RP22

P36

4 5

P37

3 6

P38

2 7

P39

1 8

100RX4

RP24

P40

4 5

P41

3 6

P42

2 7

P43

1 8

100RX4

RP26

P44

4 5

P45

3 6

P46

2 7

P47

1 8

100RX4

FP24

FP25

FP27

FP26

FP28

FP31

FP29

FP30

FP32

FP33

FP34

FP35

FP36

FP37

FP38

FP39

FP40

FP41

FP42

FP43

FP44

FP45

FP46

FP47

FP[47..24]

FP[47..24]

13

OUTPUT IS 24BIT :

P0-P7(B0-B7)

P8-P15(G0-G7)

P16-P23(R0-R7)

OUTPUT IS 48BIT :

P0-P7(FB0-FB7)

P8-P15(SB0-SB7)

P16-P23(FG0-FG7)

P24-P31(SG0-SG7)

P32-P39(FRO-FR7)

P40-P47(SRO-SR7)

C422

0.1uF

GND

1

1

Q5

DTC144EKA open

FSHFCLK

C423

0.1uF

Q3

DTC144EKA

5

+5V

GND

2 3

GND

R78

6.8k

2 3

R79 4.7K

R82 5.1K open

GND

PENVDD

FSHFCLK 11,13

FHSYNC

BACKLIGHT

C171

C170

10uF/35V

GND

C172

0.1uF

R77 0

OR8 0

+5V

OR9 open

GND

0.1uF

1

R69

open

GND

+5V

INV-12V

3

Q7

open

2

FB67

1 2

FB68

1 2

FB69

1 2

GND

C173

R270

1uF

6.8k

GND

GND

4

1

2

3

4

5

6

7

PENVDD

P7

+15V

GND

BRT

NC

ON/OFF

GND

+15V

JST-S7B-PH-K

1

Q4

DTC144EKA

INV-12V

C554

0.1uF

GND

C555

0.1uF

R268

open

GND

3.3V

2 3

R269

open

GND

PNLPWR

R80

47k

C556

0.1uF

3

4

2

Use Pin Compatible

Si9934DY for 3.3V

Panels

C557

0.1uF

P-MOS

3

S2

G2

G

D

8

排板时公共端重叠

R12_1 0 or open

R12_2 0 or open

R12_3 0 or open

1

U14A

S

Si9953DY

D

D2

D2

7

5

6

VDDSWON/OFF

3.3V

+5V

pannle_12V

F2

1 2

FUSE-3A

速熔

FDE

VDDSAFE 13

Title

LCD42B66 PANEL INTERFACE

Size Document Number Rev

<Doc> 00

Custom

Date: Sheet

2

11,13

FHSYNC

FDE 11,13

DTC144EKA

FOOTPRINT

B

12 17Thursday, July 28, 2005

C

3

21

E

of

1

B B

A A

PVSYNC11,13 FVSYNC

PHSYNC11,13

PDE11,13

PWM1

11

PENBKL11

PENVDD

11,13

PSHFCLK

11,13

Page 13

5

FP[47..24]12

D D

0 for 15~23 inch pannel,open for 30inch pannel

12

R185 0 or open

R186 0 or open

R188 0 or open

R189 0 or open

FP[23..0]

PHSYNC11,12

C C

PVSYNC11,12

PDE11,12

PSHFCLK11,12

B B

布板时此处电阻尽量靠近

open for 15~23 inch pannel,0 for 30inch pannel

A A

PHSYNC11

11,12

PVSYNC

PSHFCLK11,12

R13_5 0 or open

R13_6 0 or open

R13_7 0 or open

PDE11,12

R13_8 0 or open

FP[47..24]

5

FP10

FP13

FP12

FP11

FP31

FP30

FP29

FP28

FP27

FP26

FP25

FP24

FP47

FP46

FP45

FP44

FP43

FP42

FP41

FP40

FP5

FP4

FP3

FP2

FP1

FP0

FP7

FP6

FP9

FP8

FP15

FP14

FP39

FP38

FP37

FP36

FP35

FP34

FP33

FP32

3.3V

FP21

FP20

FP19

FP18

FP17

FP16

FP23

FP22

R106 47

R96 47

PHS

PVS

PENAB

PCLK

C196

open

GND

R182 47

R183 47

3.3V

PENVDD11,12

PENVDD11,12

PHS1

PVS1

PENAB1

4

R97

open

GND

R184

open

GND

4

3.3V

C177

PLLGND

PLLGND

333432

GND

PLLGND

PLLGND

333432

0.01uF

PLLVCC

LVDSVCC

CLKOUTM

LVDSGND

LVDSGND

LVDSGND

C13_7

0.01uF

PLLVCC

LVDSVCC

CLKOUTM

LVDSGND

LVDSGND

LVDSGND

C178

0.01uF

44

48

Y0M

47

Y0P

46

Y1M

45

Y1P

41

Y2P

38

Y3M

37

Y3P

40

49

43

36

C13_8

0.01uF

44

48

Y0M

47

Y0P

46

Y1M

45

Y1P

41

Y2P

38

Y3M

37

Y3P

40

49

43

36

C176

C174

0.1uF

22UF

GND

U15

26

VCC

9

VCC

1

VCC

15

D15

19

D18

20

D19

22

D20

23

D21

24

D22

16

D16

18

D17

4

D7

6

D8

7

D9

11111111

D12D12D12D12

12 42

D13 Y2M

14

D14

8

D10

10

D11

51

D0

52

D1

54

D2

55

D3

56

D4

3

D6

50

D27

2

D5

27

D24

28

D25

30

D26

25

D23

31

CLKIN

17 39

CLKSEL CLKOUTP

5

GND

13

GND

21

GND

53

GND

29

GND

/SHTDN

SN75LVDS83

GND

3.3V

GND

C446

open

GND

35

C13_6

C13_5

0.1uF

22UF/16v

GND

U13_1

SN75LVDS83

26

VCC

9

VCC

1

VCC

15

D15

19

D18

20

D19

22

D20

23

D21

24

D22

16

D16

18

D17

4

D7

6

D8

7

D9

11111111

D12D12D12D12

12 42

D13 Y2M

14

D14

8

D10

10

D11

51

D0

52

D1

54

D2

55

D3

56

D4

3

D6

50

D27

2

D5

27

D24

28

D25

30

D26

25

D23

31

CLKIN

17 39

CLKSEL CLKOUTP

5

GND

13

GND

21

GND

53

GND

29

GND

/SHTDN

35

GND

GND

GND

RxE0-

RxE0+

RxE1-

RxE1+

RxE2-

RxE2+

RxE3-

RxE3+

R187 47

R8347

3

RxEC-

RxEC+

3

PLLVCC

LVDSVCC

RxO0-

RxO0+

RxO1-

RxO1+

RxO2-

RxO2+

RxO3-

RxO3+

RxOC-

RxOC+

PENVDD 11,12

PLLVCC

LVDSVCC

PENVDD 11,12

2

CN1 LVDS LVDS LVDS PIN11~PIN30 LVDS PI

为单 接口与双 接口共用插排,单 接口用 ;双 接口用

VDDSAFE12

1u

1u

C576

VDDSAFE12

C577

GND

C470

C223

10uF/35V

10pF

1u

C575

GND

1u

C578

R84_1

R85_1

0

0

2

GND

RxO0RxO0+

RxO1RxO1+

RxO2RxO2+

RxOCRxOC+

RxO3RxO3+

R85

R84

0

0

RxE0RxE0+

RxE1RxE1+

RxE2RxE2+

RxECRxEC+

RxE3RxE3+

GND

CN14 15'20'

删除,

23'

CN1

CON30

30

VDD

29

VDD

28

VDD

27

VDD

26

RXO0-

25

RXO0+

24

GND

23

RXO1-

22

RXO1+

21

GND

20

RXO2-

19

RXO2+

18

GND

17

RXOC-

16

RXOC+

15

GND

14

RXO3-

13

RXO3+

12

GND

11

GND

10

RXE0-

9

RXE0+

8

RXE1-

7

RXE1+

6

RXE2-

5

RXE2+

4

RXEC-

3

RXEC+

2

RXE3-

1

RXE3+

3.3V

C183

0.1uF

FB29

3.3V

BEAD POWER

3.3V

C464

0.1uF

FB60

3.3V

BEAD POWER

Title

Size Document Number Rev

C

Date: Sheet

PLLVCC

FB28

BEAD POWER

LVDSVCC

FB61

BEAD POWER

LCD42B66 LVDS PANEL

<Doc> 00

C189

22uF

LVDSVCC

PLLVCC

GND

C463

22uF/16v

GND

C184

22uF

C190

220PF

C465

22uF/16v

N1~PIN30

GND

C461

220PF

1

。

C185

220PF

C191

0.01UF

C466

220PF

C462

0.01UF

GND

of

13 17Thursday, July 28, 2005

1

Page 14

5

C404

0.1uF

DVI_SCL

R175

100

R177

4.7K

DVI_SDA

R179

4.7K

R165 22R

3

+5V

R176

100

D D

C C

1

2

3

4 5

GND

DVI_SCL

1 2

GND

DVI_SDA

1 2

GND

A0

A1

A2

VCC

TEST

SCL

GND SDA

U29

X24C04S8

3

D18

BAV99

3

D19

BAV99

8

7

6

+5V

+5V

U49

NDC7002N

GND

5

6

S1

D1

DVI CONNECTOR

16

14

12

GND

15

28

BAT54C/BAV70

SOT23

25

D6

26

27

3.3V GND

G1S2G2 D2

123 4

3.3V

B B

第一版用插件,

HDCP

以后要注意 的要求

C549 open

U42

1

A A

5

A0

2

A1

3

A2

4 5

GND SDA

GND

X24C04S8(open)

TEST

6

7

8

open

VCC

SCL

R178

DDC_CLK

DDC_DAT

HPD

+5V

GND

AHSYNC

AVSYNC

ARED

AGREEN

ABLUE

R191

open

3.3V

8

7

6

4

P10

SHLD2/4

SHLD1/3

SHLD0/5

GND

4

21

RX5+

20

RX5-

5

RX4+

4

RX4-

13

RX3+

12

RX3-

3

2

RX2+

1

RX2-

11

10

RX1+

9

RX1-

19

18

RX0+

17

RX0-

22

SHLDC

23

RXC+

24

RXC-

GND3.3V

4k7(EP169) 0(sil169)

R195 open

R196 open

R180

open

GND

R192

open

R193

RX2+

RX2-

RX1+

RX1-

RX0+

RX0-

RXC+

RXC-

10uF/16V

3.3V

3.3V

C424

10uF/16V

3.3V

12

C434

GND

DAVCC1

3.3V

12

C425

100pF

DAVCC1

FB50

12

GND

FB51

1 2

3.3V

C429

GND

10uF/16V

FB52

1 2

C431

0.1uF

GND

C436

10nF

C437

10nF

C435

0.1uF

GND

R194

4k7(EP169) open(sil169)

3

4.7k

GND

R168

OR13

4k7

3.3V

390

R174

RX2+

RX2-

RX1+

RX1-

RX0+

RX0-

RXC+

RXC-

C427

100pF

C426

100pF

C438

10nF

C428

100pF

C430

12

100pF

C433

0.1uF

C439

10nF

C440

10nF

open(EP169) 0.1u(sil169)

3

R166 open

R167 4k7

R169 open

R170 open

R171 4.7K

R172 4.7K

R173 open

U28

96

EXT_RES

80

RX2+

81

RX2-

85

RX1+

86

RX1-

90

RX0+

91

RX0-

93

RXC+

94

RXC-

82

AVCC

84

AVCC

88

AVCC

95

AVCC

79

AGND

83

AGND

87

AGND

89

AGND

92

AGND

97

PVCC

98

PGND

3

SDA(ST)

100

SCL(OCK_INV)

6

CVCC

67

CVCC

68

GND

5

GND

18

OVCC

29

OVCC

43

OVCC

57

OVCC

78

OVCC

76

OGND

58

OGND

45

OGND

28

OGND

19

OGND

Sil161

41

99

RESERVED

(CTL2)OCK_INV

40

2

4

7

PD

PIXS

STAG_OUT

(CTL1)HS_DJTR

TMDS RECEIVER

CVCC/SCL2

GND/SDA2

38

39

C432

open(EP169) 0(Sil169/161)

R197

8

SCDT

PDO

9

R181 4k7

GND

2

DVI_RESET# 10

R289

1k

1

QE0

QE1

QE2

QE3

QE4

QE5

(HS_DJTR)RESET#

QE6

QE7

QE8

QE9

QE10

QE11

QE12

QE13

QE14

QE15

QE16

QE17

QE18

QE19

QE20

QE21

QE22

QE23

QO0

QO1

QO2

QO3

QO4

QO5

QO6

QO7

QO8

QO9

QO10

QO11

QO12

QO13

QO14

QO15

QO16

QO17

QO18

QO19

QO20

QO21

QO22

QO23

ODCK

DE

VSYNC

HSYNC

CTL3

2

3.3V

10

11

12

13

14

15

16

17

20

21

22

23

24

25

26

27

30

31

32

33

34

35

36

37

49

50

51

52

53

54

55

56

59

60

61

62

63

64

65

66

69

70

71

72

73

74

75

77

44

46

47

48

42

PD_DVI 10

1

4 5

3 6

2 7

1 8

4 5

3 6

2 7

1 8

4 5

3 6

2 7

1 8

4 5

3 6

2 7

1 8

22RX4

4 5

3 6

2 7

1 8

RP30

RP31

22Rx4

RP32

22RX4

RP33

22RX4

22RX4

RP34

RP35

PAB0

18

PAB1

27

PAB2

36

PAB3

45

PAB4

PAB5

PAB6

PAB7

PAG0

PAG1

PAG2

PAG3

PAG4

PAG5

PAG6

PAG7

PAR0

PAR1

PAR2

PAR3

PAR4

PAR5

PAR6

PAR7

PAB[7..0] 10

PAG[7..0] 10

PAR[7..0] 10

22RX4

RP29

18

DVIDE

27

DVI_HSYNC

36

DVI_VSYNC

45

22Rx4

Title

LCD42B66 DVI INTERFACE

Size Document Number Rev

<Doc> 00

B

PLACE TERMINATION

RESISTANCE AT OUTPUTS

BASED ON ROUTE LENGTH

DVIDE 10

DVI_HSYNC 10

DVI_VSYNC 10

Date: Sheet

DVICK

DVICK 10

C548

open

GND

14 17Thursday, July 28, 2005

of

1

Page 15

5

+3.3V_MCU

GND

1

2

3

4

5

3,4,10

3,4,10

10

3

3,4

4

3

C453

0.1UF

+3.3V_MCU

RXD

TXD

EA#

GND

RES_2300#

GND

INTR_ASM#

INTR_analog

RES_2300#

3

MC_SCLK

MC_DATA

2596_ON3,16

REST_Analog3

SDA_analog3

SCL_analog3

1 2

P1.4

5

P3.4

C47

REMOT

D20

1N5818

C570

100uF/16V

Solid Tantalum

R9

MC_SCLK

MC_DATA

REST

MCA16

MCA17

DEBUG PORT

P8

+3.3V_MCU

RXD

D D

C C

B B

A A

TXD

EA#

GND

JST-S5B-PH-K

SW1

PB

INTR_analog

REMOT

INTR_ASM#

REMOT

2596_ON

R103

47K

34

1 2

OR14

OR41

open

100

OR22

OR23

SCL_analog

OPEN

OPEN

OR24

OPEN

+3.3V_MCU

R94

4.7K

GND

OR25

OPEN

12

GND

RESET#

C224

0.1UF

C225

1UF

RESET#

OR16 OPEN

RST_2300#

R93

4.7K

OR15

OR17 0

RESET

U27

4

PBRST_

5

VCC

DS1819C for 3.3V DS1814C for 5V

10

R1

OPEN

R14_1

+3.3V_MCU

EA#

RESET

C60

0.1uF

MC_DATA 3,4,10

MC_SCLK 3,4,10

4

3

RST

2

GND

1

RST-

8

RXD

TXD

0

OR10

OPEN

OR11

4k7

GND

RESET

GND

C198

12pF

X1

U19

11

P3.0/RXD

13

P3.1/TXD

14

P3.2/INT0

15

P3.3/INT1

16

P3.4/T0

17

P3.5/T1

34

NMI

12

AWAIT

P1.7/CEX4/SDA/MOSI/A17/WCLK

2

P1.0/T2

3

P1.1/T2EX

4

P1.2/ECI

5

P1.3/CEX0

6

P1.4/CEX1/SS#

7

P1.5/CEX2/MISO

8

P1.6/CEX3/SCL/SCK/WAIT

80C32PLCC

35

EA/VPP

10

RESET

80C251SA/LCC

4

GND

1 2

27MHZ

21

X1

GND

22

Y2

VSS1

1

U50

4

Y

5

VCC

D8

74LV104

809

C199

12pF

3

44

20

X2

VCC

P3.6/WR

ALE/PROG

PSEN

P3.7/RD/A16

P2.0/A8

P2.1/A9

P2.2/A10

P2.3/A11

P2.4/A12

P2.5/A13

P2.6/A14

P2.7/A15

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

VSS2

23

C211

0.1uF

GND GND

3

GND

2

A

1

NC

3

VCC

2

RST

1

GND

R202 open

R203 open

R204 open

C213

0.1uF

18

33

32

19

9

24

25

26

27

28

29

30

31

43

42

41

40

39

38

37

36

RESET

GND

3.3V

+3.3V_MCU

GND

MCWR#

MCALE

MCA8

MCA9

MCA10

MCA11

MCA12

MCA13

MCA14

MCA15

MCAD0

MCAD1

MCAD2 MCA2

MCAD4

MCAD5

MCAD6

MCAD7

+3.3V_MCU

C215

0.1uF

3

CONFIGURATION

DATA

GND

U22

1

A0

2

A1

3

A2

4 5

GND SDA

AT24C16

GND

OPEN

OR18

OR19

OPEN

OR20

OPEN

OPEN

OR21

MCALE 10

MCRD#

MCA16

MCA17

SDA_analog

MCAD0

MCAD1

MCAD2

MCAD3

MCAD4

MCAD5

MCAD6

MCAD7

MCALE

MCAD0

13

MCAD1

14

MCAD2

15

MCAD3

17

MCAD4

18

MCAD5

19

MCAD6

20

MCAD7

21

SOCKET-DIP32

3

SEEPROM

3

4

7

8

13

14

17

18

MCA17

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

+3.3V_MCU

8

VCC

7

TEST

SCL

U21

D0

D1

D2

D3

D4

D5

D6

D7

MC_SCLK

6

MC_DATA

D13

809

MCA[15..0]

+3.3V_MCU

2010

2

Q0

5

VCCGND

Q1

6

Q2

9

Q3

12

Q4

15

Q5

16

Q6

19

Q7

111

OCG

SN74LV373A

GND

U23

A17

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

W27C020/SST29E020

A16

OE

WE

CE

GND VCC

NC

16 32301

29EE010-DIP32

GND

BIOS

VCC

RST

GND

MCA0

MCA1

MCA3MCAD3

MCA4

MCA5

MCA6

MCA7

12

11

10

9

8

7

6

5

27

26

23

25

4

28

29

3

2

24

31

22

C449

0.1u

GND

3

2

1

GND

MCA0

MCA1

MCA2

MCA3

MCA4

MCA5

MCA6

MCA7

MCA8

MCA9

MCA10

MCA11

MCA12

MCA13

MCA14

MCA15

MCA16

PSEN#

FLASHWE#

FLASHCE#

MCAD[7..0] 10

C450

0.1u

3.3V

FLASHCE#

OR12

OPEN

R95

open

MCA8

MCA9

GND

2

C451

0.1u

RESET#

+3.3V_MCU

MCA8 10

MCA9 10

OR43

OPEN

2

R279 0

MCA14

MCA12

MCA13

MCA15

MCWR#

MCA14

MCWR#

PSEN#

MCA15

JAGUAR#

MCRD#

+3.3V_MCU

C452

0.1u

MCA0

GND

+3.3V_MCU

R280

open

PSEN#

FLASHWE#

U48

MCA17

1

1A

MCA16

2

1B

3

1Y

4

2A

5

2B

6

2Y

7 8

GND 3Y

74LV32

GND GND

OR26 OPEN

OR27 OPEN

OR29 OPEN

OR30 OPEN

OR33 OPEN

OR34 OPEN

OR36 OPEN

OR38 OPEN

OR40 OPEN

OR42 OPEN

MCA1

MCA2

MCA3

MCA4

MCA5

MCA6

MCA7

MCA8

MCA9

MCA10

MCA11

MCA12

MCA13

MCA14

MCA15

MCA16

MCA17

GND GND

+3.3V_MCU

14

VCC

13

4B

12

4A

11

4Y

10

3A

9

3B

R267 22

+3.3V_MCU

OR31

OR32 OPEN

OPEN

+3.3V_MCU

Title

LCD42B66 MICROCONTROLLER 80C251

Size Document Number Rev

<Doc> 00

A3

Date: Sheet

AM27C020/SO

MCWR#

FLASHWE#

MCA14

MCA15

14

13

15

C551

0.01u

2

3

1

U31

20

19

18

17

16

15

14

13

31

12

11

10

30

32

168

168

3

2

1

4

5

6

7

9

GND

GND

U20B

A

VCCGND

B

G

U20A

A

VCCGND

B

G

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

CE

OE

PGM

VPP

C552

1u

1

2

3

Y0

Y1

Y2

Y3

Y0

Y1

Y2

Y3

824

VCCGND

U24

74LV104

NC

A

GND

12

11

10

9

4

5

6

7

74lv139

1

21

D0

22

D1

23

D2

25

D3

26

D4

27

D5

28

D6

29

D7

C553

1u

R205

3

Q8

2

BC847AL

VCC

Y

JAGUAR#

2000-2FFF

3000-3FFF

74lv139

OR35 OPEN

OR37 OPEN

OR39 OPEN

1

4.7k

1

5

4

OR28

OPEN

MCAD0

MCAD1

MCAD2

MCAD3

MCAD4

MCAD5

MCAD6

MCAD7

R206

220

+3.3V_MCU

FLASHCE#

15 17Thursday, July 28, 2005

of

EA#

JWR# 10

JRD#

10

Page 16

5

4

3

2

1

12V IN

P22

GND

CON4

P26

1

2

CN2

1