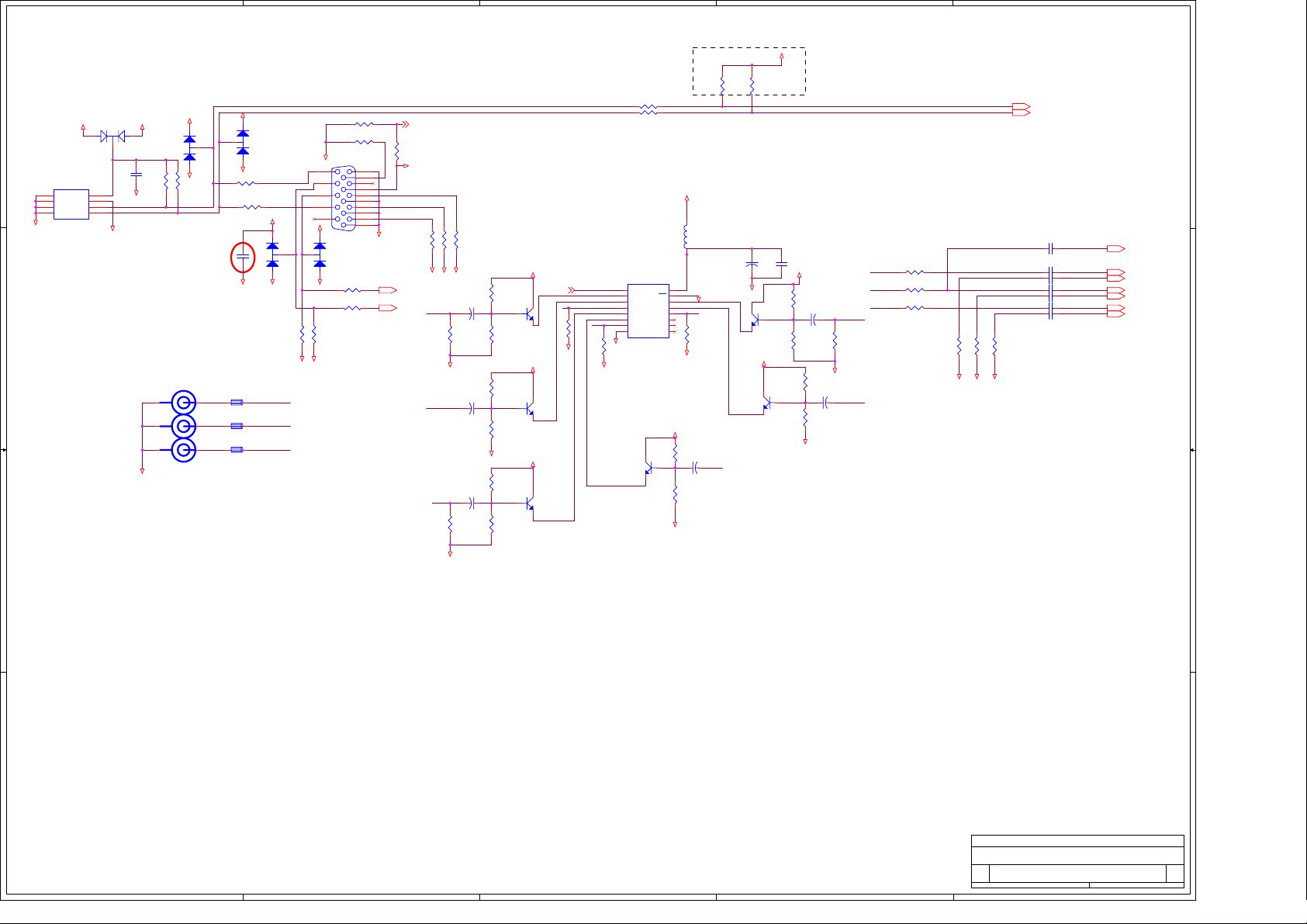

Page 1

5

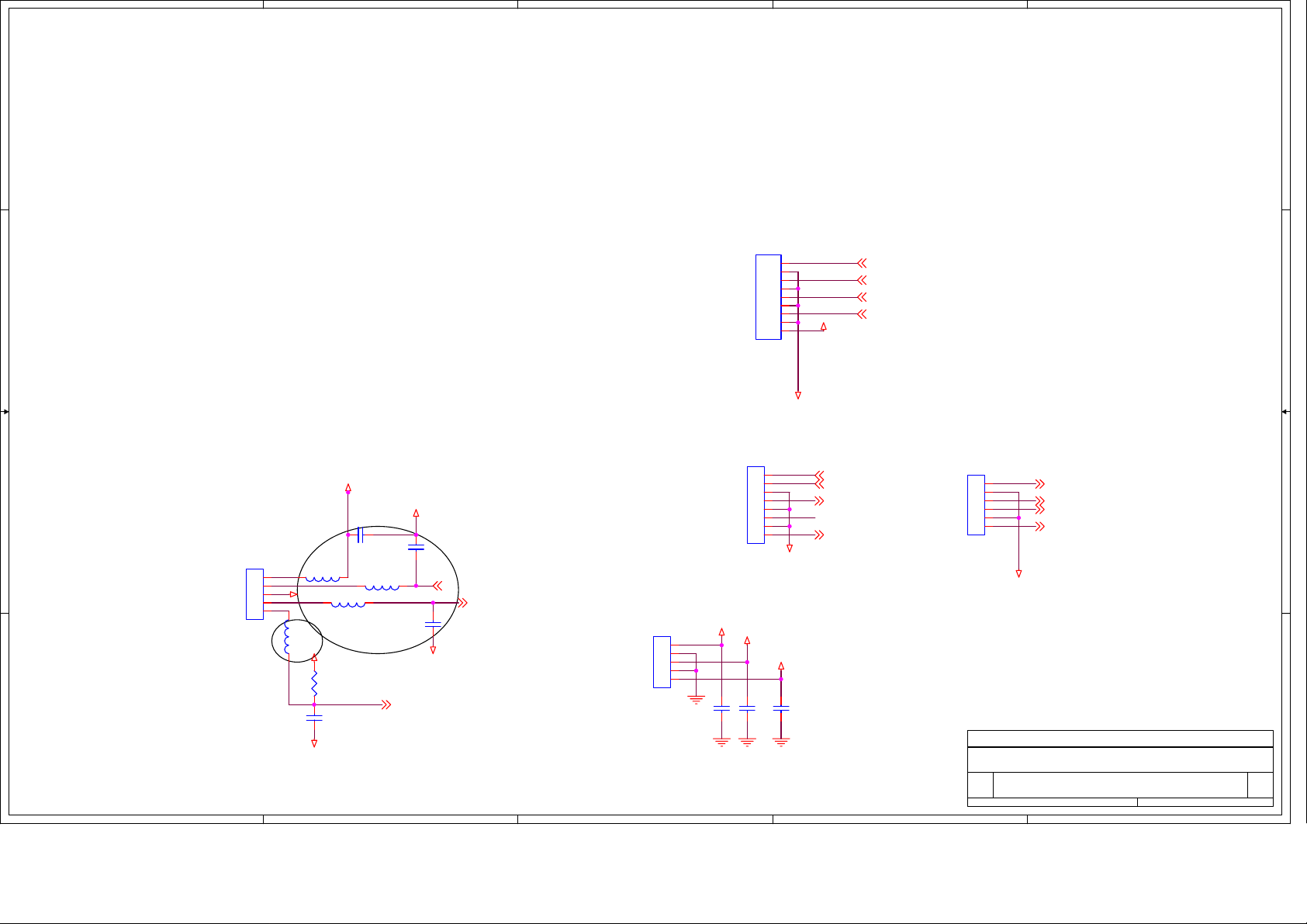

GM21 LCD TV

4

3

2

1

D D

C C

B B

CONTENTS

SCHEMATIC

01. Contents

02. Input

03. GM2221

04.SPI/RESET/KEYPAD

05. LVDS_ Out

05. TTL_ Out

06. Power

07. VIDEO DECODER

08.AUDIO

09 AV Board

10 Front Control Board

11 Interface

12 Nicam Board

13 Power_New

14 Receiver

SHEET

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Approval

A A

SignatureOrganization

Date

CHY 04-05-17

Wangdc 05-05-17

5

4

3

2

Title

GM21

Size Document Number Rev

040108 chy

B

of

Date: Sheet

114Friday, August 19, 2005

1

Page 2

5

VGASCL

VGASDA

D6

3

BAV99

65

+5V

D4

3

BAV99

1 2

GND

R17 100R

R18 100R

C220

0.1UF

GND

FB1

21

FB2

21

FB3

21

VGA_SCL

VGA_SDA

+5V

D7

3

3

BAV99

1 2

GND GND

A-VS

R30

10K

GNDGND

A-PB

A-PR

A-Y

+5V

DNP

R15

47K

P1

3 4

GND2 SIG2

1 2

GND1 SIG1

COMPONENT

+5V

1 2

GND

R16

2K7

SIG3GND3

D D

EDID VGA

U2

2

A1A2WP

3

4

GND

24AA02

GND

ANALOG DDC

C C

VGA_5V

VCCA0

SCL

SDA

BAT54C

+5V

D5

A1

A2

C

5V_VGA

C2

0.1uF

81

GND

7

6

5

GND

GND

YPrPB Video In

B B

R12 10K

CN2

GND

15

14

13

12

11

DB15 HD

D8

BAV99

1 2

R23 20R

R31

10K

4

R13 0R

5

10

4

9

3

8

2

7

1

6

GND

Near VGA pins

1%

1%

3

+5V

R8

R9

10K

R10 100R

R37

Pb/B

1k

GND

R11 100R

1

IN

2

SA1

3

SA2

4

DA

5

SB1

6

SB2

7

DB

8

GND

13-PI5V33-0QB

GND

U3

PI5V330

2 3

BC847c

3.3V

L1

16

VCC

15

EN

14

SD1

GND

13

SD2

Pr/R

12

DD

11

SC1

10

SC2

R34

9

DC

1k

GND

+5V_MUX

R46

22k

A-BLUE

1

1 2

Q5

C16

10uF/16V

10k

R48

GND

VGACON

R14

10K

VGA_5V

VGA RGB In

A-BLUE

A-GREEN

A-RED

R1982

R2082

R2182

HSYNC 5

VSYNC 5 BLUE+ 5

A-Y

A-GREEN

A-PB

C11

12

10uF/16V

82

R36

GND

C15

12

10uF/16V

C17

12

10uF/16V

82

R32

GND

GND

GND

GND

+5V_MUX

SEL_RGB3

R24

Q2

22k

BC847c

1

R33

10k

R42

Q4

22k

BC847c

1

R45

10k

GND

R47

Q1

22k

BC847c

1

R50

10k

2 3

+5V_MUX

2 3

+5V_MUX

2 3

Y/G

R29

1k

GND

10K

+

C4

10uF

GND

Q6

BC847c

1

2 3

R35

10k

+5V_MUX

R41

Q3

22k

BC847c

1

R43

2 3

10k

C5 0.01uF

+5V_MUX

R26

22k

GND

1 2

10uF/16V

2

NOT TO BE MOUNTED

C13

A-PR

82

R49

GND

C14

A-RED

1 2

10uF/16V

Pr/R

R22 47R 1%

Y/G

R25 47R 1%

Pb/B

R28 47R 1%

R3884.5 1%

R3984.5 1%

GND GND GND

R4084.5 1%

DDC_SCL_VGA 5

DDC_SDA_VGA 5

C3 0.01uF

C6 0.01uF

C7 0.01uF

C8 0.01uF

C9 0.01uF

C10 0.01uFR27 20R

C12 0.01uF

1

MUXED RGB

TO 5221ADC

INPUT

SOG_MCSS 5

RED+ 5

RED- 5

GREEN+ 5

GREEN- 5

BLUE- 5

A A

Title

40-LD2010-DIC4X(40-LD2010-DIC4X)

Size Document Number Rev

040108 chy

C

5

4

3

2

Date: Sheet

1

of

214Friday, August 19, 2005

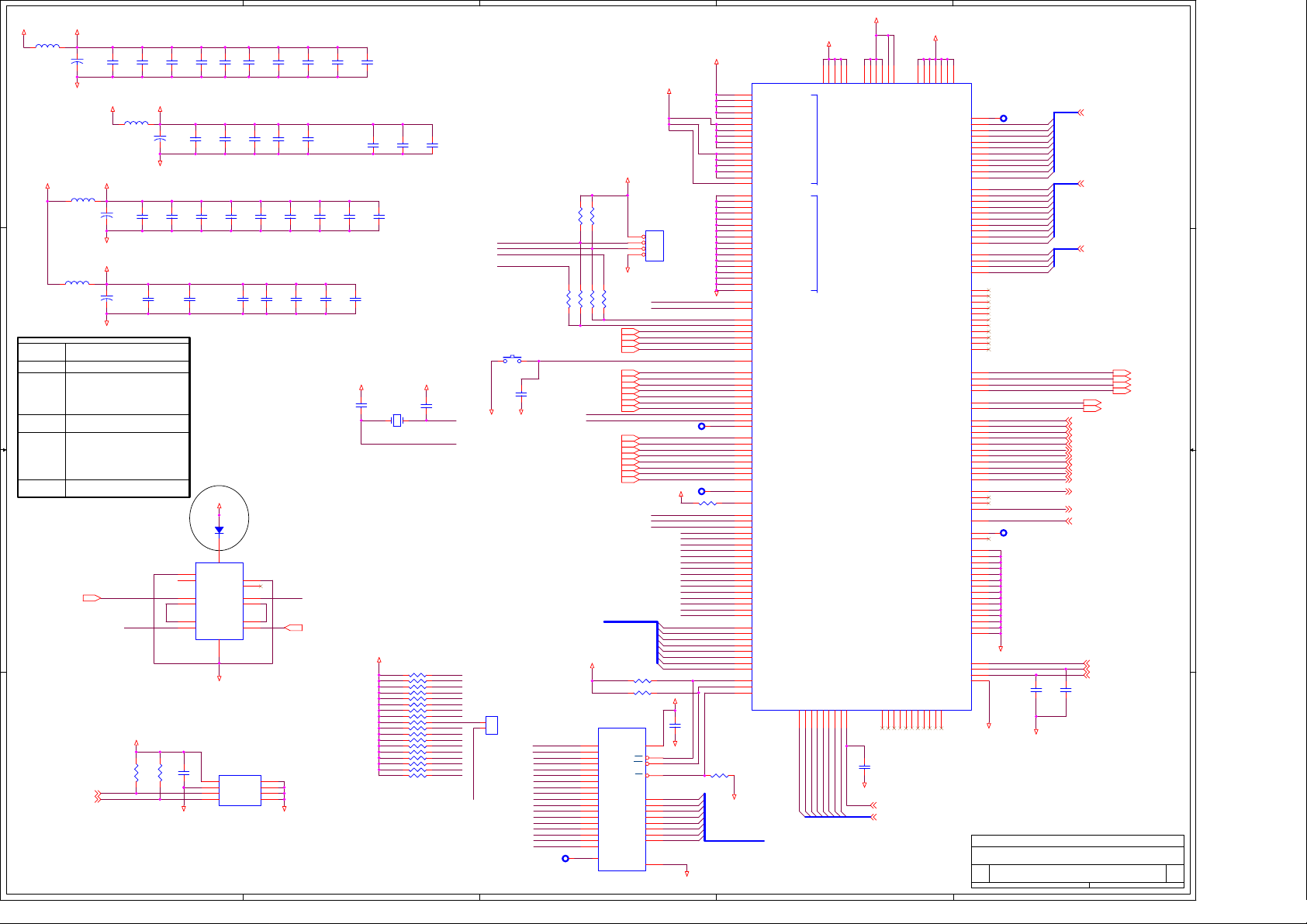

Page 3

5

+3.3V_AVDD

D D

C C

B B

A A

L2

33R FB

+1.8V_DVDD

RMADDR[6:0]

RMADDR[12:7]

RMADDR[14:13]

RMADDR15

RMADDR16

RMADDR17

3.3V_AVDD

C18

C19

22uF/16V

0.1uF

GND

+3.3V_DVDD 3.3V_DVDD

L3

33R FB

CVDD_1.8

L4

33R FB

L5

33R FB

BootStrap Signals

HSYNC3

C38

22uF/16V

GND

AVDD_1.8

C48

22uF/16V

GND

For I2C address [6:0] to JTAG bridge

Host I/F, to determine device address.

User_Bits[5:0] for configuration setting

OP_MODE[1:0]:

00 = Normal op. UART in 186 on system pins.

01 = I2C to JTAG bridge.

10 = JTAG port, 5 wires

11 = External parallel control bus using

ROM Addr/Data

SPI_EN: 0 = parallel ROM I/F. 1 = SPI

serial ROM and Cache control

Initial state of OCM ROM:

0 = internal ROM on, and mapped to top 32K

of OCM and OCM boot will be from internal

ROM codes.

1 = Internal ROM off. The external ROM

mapped to entire upper 512K of OCM address.

OCM boot from external ROM code.

OSC_SEL: 0 = Xtal and internal oscillator.

1 = TTL oscillator (on TCLK pin)

VGAHS

+5V

GPIO9/SCL

MCSCL

GPIO10/SDA

MCSDA

5

Close to respective power Pins

C20

0.1uF

C21

0.1uF

C22

0.1uF

Close to respective power Pins

C30

C29

0.1uF

22uF/16V

GND

Close to respective power Pins

C40

C39

0.1uF

C49

0.1uF

R76

10K

C41

0.1uF

0.1uF

C50

0.1uF

5.5V

14

U5

1

1

2

2

3

3

4

4

11

11

10

10

7

74LCX14

GND

R77

C65

10K

0.1uF

8

7

6

GND GND

C23

0.1uF

C31

0.1uF

1N4148

14

7

U7

VCC

WP

SCK

24LC16B

C24

0.1uF

C32

0.1uF

C42

C43

0.1uF

0.1uF

C52

C51

0.1uF

0.1uF

13

13

12

12

8

8

9

9

6

6

5

5

1

A0

2

A1

3

A2

45

VSSSI

C26

C25

0.1uF

0.1uF

C33

C34

0.1uF

0.1uF

C44

0.1uF

Close to respective power Pins

C53

0.1uF

VGAVS

VSYNC

3

4

C28

C27

0.1uF

0.1uF

Close to respective power Pins

C35

0.1uF

C45

C46

0.1uF

220pF

C55

C54

220pF

0.1uF

3.3V_AVDD

C58

5pF

BOOTSTRAP OPTIONS SELECT

(NOT POPULATED SHOULD BE

HARD WIRED)

+5V

4

C47

220pF

X1

14.318MHz

C36

0.1uF

3.3V_AVDD

C37

0.1uF

JTAG

DEBUG

I2C SEL

C59

5pF

TCLK

XTAL

10KR54

RMADDR0

10KR55

RMADDR1

10KR57

RMADDR2

10KR58

RMADDR3

10KR60

RMADDR4

10KR61

RMADDR5

10KR62

RMADDR6

10KR63

RMADDR7

10KR64

10KR65

RMADDR9

10KR66

RMADDR10

10KR67

RMADDR11

10KR68

RMADDR12

10KR69

RMADDR13

10KR70

RMADDR14

10KR71

RMADDR15

10KR72

RMADDR16

10KR73

RMADDR17

GND GND

T2

1

2

RMADDR8

HOST_SDA/UART_DO

HOST_SCL/UART_DI

DDC_SCL_VGA

DDC_SDA_VGA

SW1

SW PUSHBUTTON

For_Update

C57

0.1uF

RMADDR17

RMADDR16

RMADDR15

RMADDR14

RMADDR13

RMADDR12

RMADDR11

RMADDR10

RMADDR9

RMADDR8

RMADDR7

RMADDR6

RMADDR5

RMADDR4

RMADDR3

RMADDR2

RMADDR1

RMADDR0

TP14 VP

R5110K

R5210K

OR30R

OR20R

OR10R

DDC_SCL_VGA3

DDC_SDA_VGA3

DDC_SCL_DVI3

DDC_SDA_DVI3

BLUE+3

BLUE-3

SOG_MCSS3

GREEN+3

GREEN-3

RED+3

RED-3

VGAHS

VGAVS

RX2+3

RX2-3

RX1+3

RX1-3

RX0+3

RX0-3

RXC+3

RXC-3

+5V

U6

30

2

3

29

28

4

25

23

26

27

5

6

7

8

9

10

11

12

1

AT49HF/F010-45JC

32-Pin PLCC Socket

3

NC/A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

NC

3

OR40R

+5V

GND

RMDATA[0..7]

R56 10K

R59 10K

VCC

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

GND

J1

1

2

3

4

RS232

DDC_SCL_VGA

DDC_SDA_VGA

DDC_SCL_DVI

DDC_SDA_DVI

OE

WE

CE

3.3V_AVDD

GPROBE

DEBUG

PORT

TCLK

XTAL

RESET

ADC_TEST

RX2+

RX2RX1+

RX1RX0+

RX0RXC+

RXC-

3.3V_AVDD

+5V

32

GND

24

31

22

RMDATA7

21

RMDATA6

20

RMDATA5

19

RMDATA4

18

RMDATA3

17

RMDATA2

15

RMDATA1

14

RMDATA0

13

16

RMADDR17

RMADDR16

RMADDR15

RMADDR14

RMADDR13

RMADDR12

RMADDR11

RMADDR10

RMADDR9

RMADDR8

RMADDR7

RMADDR6

RMADDR5

RMADDR4

RMADDR3

RMADDR2

RMADDR1

RMADDR0

RMDATA7

RMDATA6

RMDATA5

RMDATA4

RMDATA3

RMDATA2

RMDATA1

RMDATA0

C62

0.1uF

GND

3.3V_DVDD

TP10

TP11

R53 250/1%

ROM_OEn

ROM_WEn

ROM_CSn

2

3.3V_DVDD

5073190

3.3V_A

AGND

VDATA7/GPIO16

VDATA6/GPIO17

VDATA5/GPIO18

VDATA4/GPIO19

102

103

106

107

108

YUV6

YUV7

YUV5

YUV4

YUV3

95

RVDD_33

RVDD_33

VDATA3/GPIO20

VDATA2/GPIO21

109

110

YUV2

YUV1

2

U4

AVDD_OUT_LV_E_33

24

AVDD_OUT_LV_E_33

26

AVDD_LV_33

27

AVDD_OUT_LV_O_33

40

AVDD_OUT_LV_O_33

113

AVDD_IMB_33

120

AVDD_RX2_33

125

AVDD_RX1_33

130

AVDD_RX0_33

134

AVDD_RXC_33

141

AVDD_BLUE_33

145

AVDD_GREEN_33

150

AVDD_RED_33

154

AVDD_ADC_33

172

LBADC_VDD_33

171

AVDD_RPLL_33

12

AVSS_OUT_LV_E

23

AVSS_OUT_LV_E

AVSS_LV

28

AVSS_OUT_LV_O

39

AVSS_OUT_LV_O

115

AGND_IMB

117

AGND_RX2

122

AGND_RX1

127

AGND_RX0

131

AGND_RXC

144

AGND_BLUE

149

AGND_GREEN

153

AGND_RED

156

AGND_ADC

168

AGND_RPLL

177

LBADC_GND

136

GND_RXPLL

GND

170

TCLK

169

XTAL

71

HOST_SCL/UART_DI

72

HOST_SDA/UART_DO

77

DDC_SCL_VGA

78

DDC_SDA_VGA

79

DDC_SCL_DVI

80

DDC_SDA_DVI

178

RESETn

142

BLUE+

143

BLUE-

146

SOG_MCSS

147

GREEN+

148

GREEN-

151

RED+

152

RED-

181

HSYNC

182

VSYNC

155

ADC_TEST

118

RX2+

119

RX2-

123

RX1+

124

RX1-

128

RX0+

129

RX0-

132

RXC+

133

RXC-

138

CLKOUT

114

REXT

183

ROM_ADDR17

184

ROM_ADDR16

185

ROM_ADDR15

186

ROM_ADDR14

187

ROM_ADDR13

188

ROM_ADDR12

189

ROM_ADDR11

192

ROM_ADDR10

193

ROM_ADDR9

194

ROM_ADDR8

195

ROM_ADDR7

196

ROM_ADDR6

197

ROM_ADDR5

198

ROM_ADDR4

199

ROM_ADDR3

200

ROM_ADDR2

201

ROM_ADDR1

202

ROM_ADDR0

203

ROM_DATA7

204

ROM_DATA6

207

ROM_DATA5

208

ROM_DATA4

1

ROM_DATA3

2

ROM_DATA2

3

ROM_DATA1

4

ROM_DATA0

5

ROM_OEn

6

ROM_WEn

7

ROM_CSn

gm5221

PQFP-208

SOCKET:

IC51-2084-1052

R74

10K

GND

RMDATA[0..7]

Route (LBADC_IN1, LBADC_RET) and

(LBADC_IN2, LBADC_RET) as differential

tracks close to each other and ground the

return track of each pair very close to the

5221 and ground pin

AVDD_1.8

205

RVDD_33

RVDD_33

VDATA1/GPIO22

VDATA0/GPIO23

111

112

YUV0

YUV[0..7]

1669417596

116

12125126

13711164

RVDD_33

VDD_RX2_18

VDD_RX1_18

VDD_RX0_18

VDD_RPLL_18

VDD1_ADC_18

VDD_RXPLL_18

CH3P_LV_E(PD0/ER0)

CH3N_LV_E(PD1/ER1)

CLKP_LV_E(PD2/ER2)

CLKN_LV_E(PD3/ER3)

CH2P_LV_E(PD4/ER4)

CH2N_LV_E(PD5/ER5)

CH1P_LV_E(PD6/ER6)

CH1N_LV_E(PD7/ER7)

CH0P_LV_E(PD8/EG0)

CH0N_LV_E(PD9/EG1)

CH3P_LV_O(PD10/EG2)

CH3N_LV_O(PD11/EG3)

CLKP_LV_O(PD12/EG4)

CLKN_LV_O(PD13/EG5)

CH2P_LV_O(PD14/EG6)

CH2N_LV_O(PD15/EG7)

CH1P_LV_O(PD16/EB0)

CH1N_LV_O(PD17/EB1)

CH0P_LV_O(PD18/EB2)

CH0N_LV_O(PD19/EB3)

GND

DECCLK

C63

8P2

5253104

DECCLK

YUV[0..7]

NC

54

105

157

VCLKNCNCNCNCNCNCNCNCNCNC

CVDD_1.8

CVDD_1.8

86

CVDD_18

CVDD_18

CVDD_18

CVDD_18

GPIO7/IRQin

GPIO8/IRQout

GPIO10/SDA

PWM0/GPIO11

PWM1/GPIO12

PWM2/GPIO13

PWM3/GPIO14

STI_TM1/GPIO15

VBUFC_RPLL

VBUFC_DVI

LBADC_RETURN

158

159

160

161

1

139

179

CVDD_18

CVDD_18

CVDD_18

VCO_LV

PD20/EB4

PD21/EB5

PD22/EB6

PD23/EB7

PD24/OR0

PD25/OR1

PD26/OR2

PD27/OR3

PD28/OR4

PD29/OR5

PD30/OR6

PD31/OR7

PD32/OG0

PD33/OG1

PD37/OG5

DEN

DHS

DVS

DCLK

PPWR

PBIAS

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO9/SCL

STI_TM2

CRVSS

CRVSS

CRVSS

CRVSS

CRVSS

CRVSS

CRVSS

CRVSS

CRVSS

CRVSS

CRVSS

CRVSS

GND_RPLL

GND1_ADC

LBADC_IN1

LBADC_IN2

LBADC_IN3

162

Title

Size Document Number Rev

Date: Sheet

LV_E9

13

LV_E8

14

LV_E7

15

LV_E6

16

LV_E5

17

LV_E4

18

LV_E3

19

LV_E2

20

LV_E1

21

LV_E0

22

LV_O9

29

LV_O8

30

LV_O7

31

LV_O6

32

LV_O5

33

LV_O4

34

LV_O3

35

LV_O2

36

LV_O1

37

LV_O0

38

PD20

43

PD21

44

PD22

45

PD23

46

56

57

58

59

60

61

62

63

64

65

66

47

48

49

55

67

68

81

82

83

84

85

88

89

90

91

92

93

98

99

100

101

69

167

135

70

206

191

180

140

97

94

76

74

51

42

8

87

165

163

173

174

175

176

LBADC_RET

GND

PPWR

PBIAS

GPIO0

GPIO1

GPIO2

GPIO3

GPIO5

GPIO6

MCSCL

MCSDA

TP12

GND

GND

40-LD2010-DIB4X(40-LD2010-DIC4X)

040108 chy

C

TP9

10

DEN

DHS

DVS

DCLK

SEL_RGB

VGACON

VBI_INTR

LED

DEC_PWN

RET_OTHER

POWER

IR_IN

SWS1

MCSCL

MCSDA

PWM0

AMP_MUTE

SWS0

KEYBOARD

INPUT TO

LBW ADC

C60

C61

0.1uF

0.1uF

1

LV_E[0..9] 7,8

LV_O[0..9] 7,8

PD[20..23] 8

ADC_IN1

SCART_FB1

SCART_FB2

DEN

DHS

DVS

DCLK

PPWR 7,8

PBIAS 7

MUX SEL,VGA

CONNECTOR

SIGNAL,VBI

INTR, LED, AMP

AND AUDIO

DISABLE

I2C

PWM

OUPUT

FOR AMP

VOLUME,

BL

BRITNESS

of

314Friday, August 19, 2005

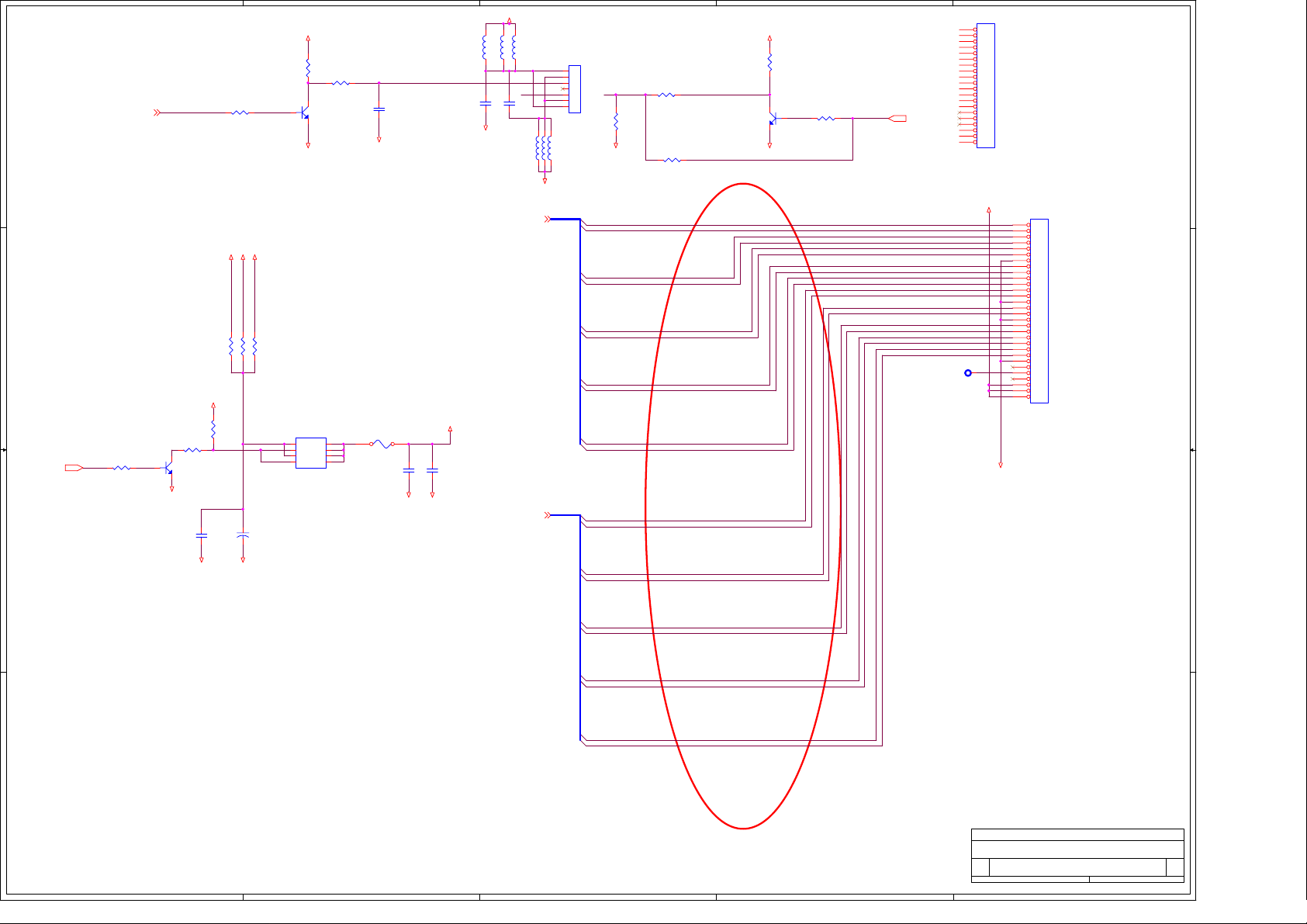

Page 4

5

+5V

R80 470R

3

Q7

1

MMBT3904L

2

GND

U8

1

S1

2

G1

3

S2

4

G2

SI9953ADY

Panel Power Switch

3

Q9

MMBT3904L

2

R82 1K

+12V

+5V+3.3V_DVDD

R86

R88

R87 0

+5V

R89

47K

R90

1K

C75

C74

22uF/16V

0.1uF

GND

GND

D D

C C

B B

Panel Power Voltage Selection

PPWR5

PWM0

PPWR

R91 4K7 C223

1

GND

4

R79

100R

100

D1

D1

D2

D2

0R

GND

F1

8

7

33R FB

6

5

C72

0.1uF

C56

0.1uF

GND GND

BKLT_ADJ

PANEL_POWER

0.1uF

0.1uF

+12V

L6

31R FBL831R FBL731R FB

C71

C70

0.1uF

GND

LV_O[0..9]

LV_E[0..9]

L10

L11

31R FB

GND

31R FBL931R FB

Backlight

Inverter

Connector

J9

1

2

3

4

5

6

7

CON7

3

+5V

R78

10K

BKLT_ENBKLT_EN

R81 0R

4k7

GND

R85 0R

3

1

2

Q8

MMBT3904L

GND

LVDS test points right on the trace to avoid extra length

TXO0-

LV_O0 TXO0-EB3

LV_O2

LV_O3 EB0

LV_O4 EG7

LV_O5 EG6

LV_O6 EG5

LV_O7 EG4

LV_O8 EG3

LV_O9 EG2

TXE0+

TXE1-

TXE1+

EB2

EB1

LV_E0 EG1

LV_E1 EG0

LV_E2 ER7

LV_E3 ER6

TXO0+

TXO1-

TXO1+

TXO2-

TXO2+

TXOC-

TXOC+

TXO3-

TXO3+

2

20

19

18

17

16

15

14

13

12

11

10

9

8

7

TXO0+LV_O1

TXO1TXO1+

TXO2TXO2+

TXOCTXOC+

TXO3TXO3+

TXE0TXE0+

TXE1TXE1+

TXE2TXE2+

TXECTXEC+

TXE3TXE3+

6

5

4

3

2

1

PANEL_POWER

DF14A-20P-1.25H

TP15

LVDS Output

Connector

GND

R84 1KR83

PBIAS

PBIAS 5

CN3

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

DF14A-30P-1.25H

1

15"SAMSUNG

连接到 屏

TXE2-

TXE2+

TXEC-

TXEC+

TXE3-

TXE3+

A A

5

4

3

LV_E4 ER5

LV_E5 ER4

LV_E6 ER3

LV_E7 ER2

LV_E8 ER1

LV_E9 ER0

Title

40-LD2010-DIB4X(40-LD2010-DIC4X)

Size Document Number Rev

040108 chy

C

Date: Sheet

2

1

of

414Friday, August 19, 2005

Page 5

5

D D

4

3

2

1

PANEL_POWER PANEL_POWER

LV_E[0..9]

C C

LV_O[0..9]

PD[20..23]

LV_E9

LV_E8

LV_E7

LV_E6 ER3

LV_E5

LV_E4

LV_E3

LV_E2

LV_E1

LV_E0

LV_O9

LV_O8

LV_O7

LV_O6

LV_O5

LV_O4

LV_O3

LV_O2

LV_O1

LV_O0

PD20

PD21

PD22

PD23

22Rx4

22Rx4

22Rx4

8

7

6

5 4

8

7

RN1

6

5 4

8

7

6

5 4

8

7

6

5 4

8

7

6

5 4

8

7

6

5 4

ER0

1

ER1

2

ER2

3

ER4

RN222Rx4

1

ER5

2

ER6

3

ER7

EG0

1

EG1

2

EG2

3

EG3

EG4

RN3

1

EG5

2

EG6

3

EG7

RN422Rx4

EB0

1

EB1

2

EB2

3

EB3

EB4

RN5

1

EB5

2

EB6

3

EB7

RN622Rx4

ER[0..7] SHT-6

EG[0..7] SHT-6

EB[0..7] SHT-6

CLK

VS

EB6

EB2

EB0 EB1

EG6

EG4

EG2

EG0

ER6

ER4

ER2

ER0

J10

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

87089-40

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

DE

HS

EB7

EB5EB4

EB3

EG7

EG5

EG3

EG1

ER7

ER5

ER3

ER1

GNDGND

B B

DENSHT-5,6

DHSSHT-5,6

DVSSHT-5,6

DCLKSHT-5,6

DEN

DHS

DVS

DCLK

R92 22R

R93 22R

R94 22R

R95 22R

C76

47PF

DE

HS

VS

CLK

GND

A A

Title

GM21-TTL out

Size Document Number Rev

040108 chy

B

of

Date: Sheet

5

4

3

2

514Friday, August 19, 2005

1

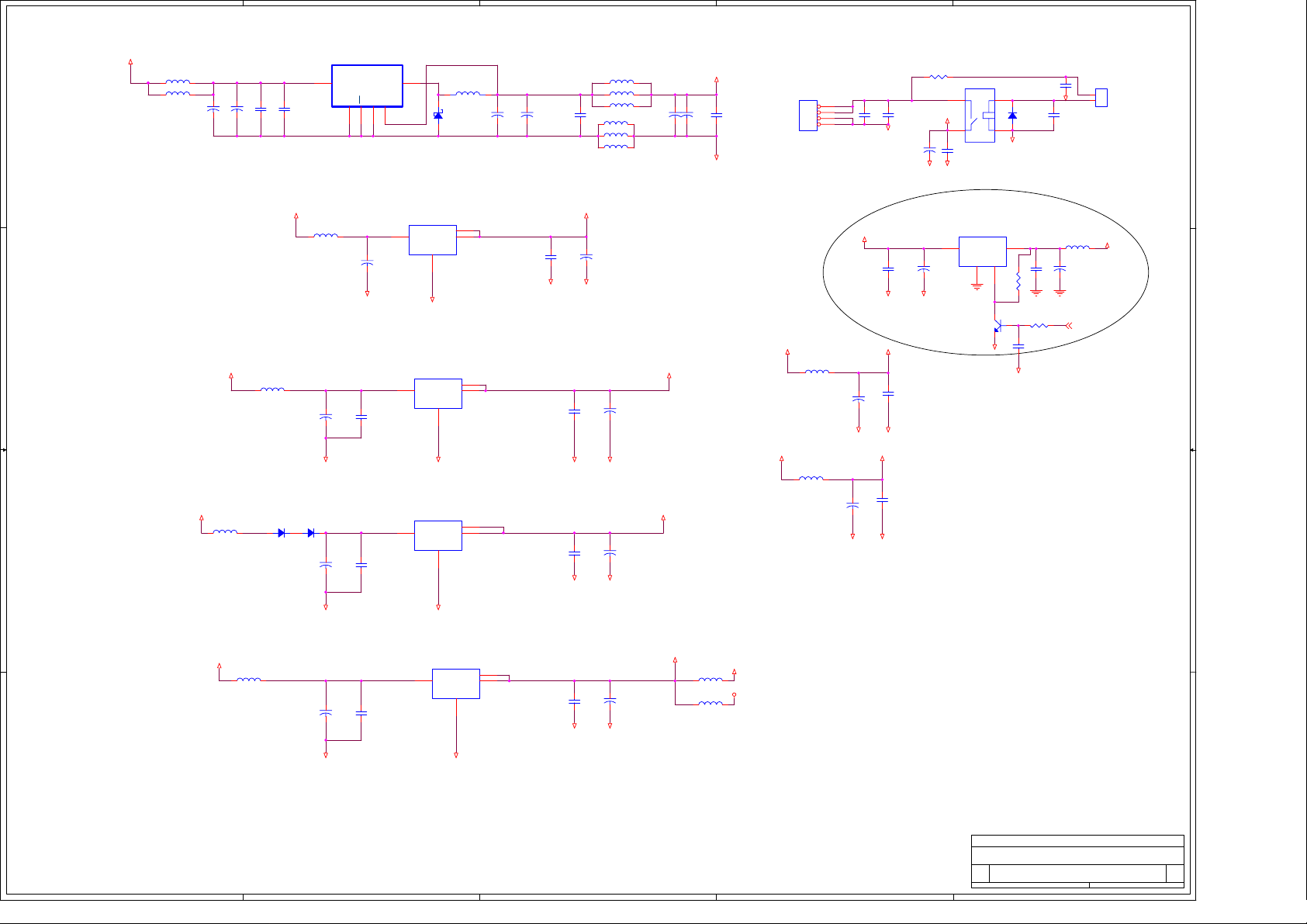

Page 6

5

4

3

2

1

+12V

L12 33R FB

L14 33R FB

D D

C C

C78

100uF/16V

+5V

C79

470uF/25V

C80

0.1uF

L24

33R FB

+5V

L26

D11

1N4001

33R FB

B B

U9

LM2596S-5.0

1

VIN

C81

0.1uF

GND

3

+5V +3.3V_DVDD

L21

33R FB

C105

100uF/16V

GND

D12

1N4001

C111

GND

C106

0.1uF

C112

0.1uF

VOUT

456

C95

100uF/16V

ADJONTAB

2

D9

IN5820

1 2

lt1084-3.3V

U10

TAB

3 2

VIN VOUT

GND/ADJ

1

GND

LT1117-3.3V

U12

TAB

3 2

VIN VOUT

GND/ADJ

Sot223

1

GND

U13

LT1117-1.8V

TAB

3 2

VIN VOUT

GND/ADJ

Sot223

1

L15

33uH

C82

C83

330uF/16V

330uF/16V

4

4

4

100uF/16V

GND

GND

31ohm at 100Mhz Rated Currrent

>=2A

C84

L18 33R FB

0.1uF

L19 33R FB

L20 33R FB

40mA

C94

C93

100uF/16V

0.1uF

10V

GND

GND

C103

0.1uF

GND

C109

0.1uF

GND GND

L13 33R FB

L16 33R FB

L17 33R FB

C104

100uF/16V

GND

C110

100uF/16V

C85

100uF/16V

+3.3V_AVDD

+1.8V_DVDD

330uF/16V

200mA

CVDD:300mA

AVDD:60mA

R96

C91

GNDGND

+12V

GNDGND

C97

100uF/16V

10V

U11

100

C92

0.1u

KIA278R09

VOUT

To-223

RELA1

4

Jidian1

GND

324

BC847c

C77

0.1u

D10

C90

1N4148

123

0.1u

J11

1

2

GND

CONTROL

GND

+12V

C100

0.1uF

L22

33R FB

C98

C99

0.1uF

100uF/16V

10V

R98

2k2

POWER

1

Vin

SW

R97

10k

Q10

1

2 3

GND

GND

+5V

JP1

C87

C86

0.1uF

4

3

2

1

POWER IN

C88

C89

0.1u

100P

GND

470uF/25V

GND

+9V

C96

0.1uF

+5V

+5V_MUX

L23

33R FB

C101

C102

0.1uF

22uF/16V

GND

GND

+3.3V_AVDD +3.3V_LBADC

L25

33R FB

C108

22uF/16V

C107

0.1uF

GND GND

+3.3V_AVDD

L27

33R FB

C115

C116

0.1uF

100uF/16V

GND

A A

5

4

U14

LT1117-1.8V

TAB

3 2

VIN VOUT

GND/ADJ

Sot223

1

GND

4

C114

C113

100uF/16V

0.1uF

GND

GND

3

+1.8V_DEC

A_1.8V

L28

33R FB

D_1.8V

L29

33R FB

Title

40-LD2010-DIB4X(40-LD2010-DIC4X)

Size Document Number Rev

040108 chy

C

2

Date: Sheet

1

of

614Friday, August 19, 2005

Page 7

5

4

3

2

1

5.5V

L49 2.7uH

SCART_R

L47 2.7uH

L51 2.7uH

SCART_G

L50 2.7uH

SCART_B

R44

NC

R191

22k

R192

10k

R107

0

SCART_R

SCART_G

SCART_B

SCART_CVBS/Y

GND

GND

GND

C123 0.1uF

C225 0.1uF

C128 0.1uF

C130 0.1uF

C142

330pF

C144 0.1uF

C145 0.1uF

C146 0.1uF

C149

330pF

C154 0.1uF

C155 0.1uF

C156

330pF

C163 0.1uF

C164

330pF

GND

DECODER_VS

DECODER_HS

C117

14.318Mhz

12

33pF

A_3.3V

A_1.8V

C121

C122

0.1uF

GND

0.1uF

GND

C224

330pF

GND

C228

330pF

GND

C226

330pF

GND

C227

330pF

GND

C229

330pF

GND

GND

C118

33pF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

X2

R101 100K

80

XTAL1

XTAL2

VI_1_A

PLL_A18VDD

PLL_A18GND

CH1_A18VDD

CH1_A18GND

CH4_A33VDD

CH4_A33GND

VS/VBLK/GPIO

TVP5146PFP

VI_4_A

CH4_A18GND

VI_1_B

VI_1_C

CH1_A33GND

CH1_A33VDD

CH2_A33VDD

CH2_A33GND

VI_2_A

VI_2_B

VI_2_C

CH2_A18GND

CH2_A18VDD

A18VDD_REF

A18GND_REF

CH3_A18VDD

CH3_A18GND

VI_3_A

VI_3_B

VI_3_C

CH4_A33GND

CH4_A33VDD

21222324252627282930313233343536373839

R102 10K

GND

D_3.3V

61626364656667686970717273747576777879

D_1.8V

DVDD

DGND

IOVDD

IOGND

C-2/GPIO

FID/GPIO

C_5/GPIO

C_4/GPIO

C_3/GPIO

C_1/GPIO

C_0/GPIO

HS/CS/GPIO

C_6/GPIO/RED

C_7/GPIO/GREEN

C_8/GPIO/BLUE

C_9/GPIO/FSO

DGND

PWDN

RESETB

FSS/GPIO

AVID/GPIO

GLCO/I2CA

IOVDD

DGND

DVDD

IOGND

IOVDD

DGND

DVDD

IOGND

Y_0

Y_1

Y_2

Y_3

Y_4

Y_5

Y_6

Y_7

Y_8

Y_9

DATACLK

U15

CH4_A18VDD

NSUB

TMS

SCL

SDA

INTREQ

DVDD

C131 0.1uF

59

C132 0.1uF

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

GND

C129 0.1uF

60

40

R120

100R

R115

10K

C143

10P

RN7

22Rx4

1

2

3

4 5

RN8

1

2

3

4 5

22Rx4

R114 22R

DECBIN

DECGIN

DECRIN

DEC_FB

YUV0

8

YUV1

7

YUV2

6

YUV3

YUV4

8

YUV5

7

YUV6

6

YUV7

L56 17 OHM

GND

R118 100R

+3.3V_DVDD

L32

33R FB

C124

0.1uF

GND GND

D_3.3V A_3.3V

C133

0.1uF

0.1uF

0.1uF

C135

C134

GNDGND

YUV[0..7]

DECCLK

0.1uF

C63

GND

R116 100R

R117 100R

MCSDA

MCSCL

RET_OTHER

L31 33R FB

L33 33R FB

C125

100uF/16V

10V

C137

C136

0.1uF

0.1uF

A_1.8V

C151

C150

0.1uF

0.1uF

GND

D_1.8V

C159

C160

0.1uF

0.1uF

GND

C138

A_3.3VD_3.3V

0.1uF

C152

0.1uF

C161

0.1uF

C139

0.1uF

C153

C162

0.1uF

0.1uF

TP16

TP17

TP18

Q915

CVBS_OUT

D D

R103

120

CVBS2

CVBS2

R104 NC

GND

GND

CVBS1

CVBS1

R106 NC

GND

GND

TV_IN

SVIDEO_C

SVIDEO_Y

TV_IN

R109 NC

GND GND

GND

R111 75R 1%

GND

R113 NC

GND GND

GND

SVIDEO_C

C C

B B

SVIDEO_Y

C119

4.7pF

C126

4.7pF

R105

C140

4.7pF

C147

4.7pF

C157

4.7pF

R112

120

R108

R110

120

120

120

L30 2.7uH

L34 2.7uH

L35 2.7uH

L36 2.7uH

L37 2.7uH

GND

GND

BC847c

1

2 3

R194

1k

L46 2.7uH

C120

330pF

C127

330pF

C141

330pF

C148

330pF

GNDGND

C158

330pF

A A

Title

40-LD2010-DIB4X(40-LD2010-DIC4X)

Size Document Number Rev

040108 chy

C

5

4

3

2

Date: Sheet

1

of

714Friday, August 19, 2005

Page 8

5

4

3

2

1

+9V

D D

PC_L

R180

C233

22uF/NS

+

10k

R181

R182

22k

10k

Q917

1

2 3

BC847c

R183

1k

R184

75

PC_L

+9V

R176

PC_R

R174

C232

22uF/NS

+

10k

R175

22k

10k

Q916

1

2 3

BC847c

R179

1k

R178

PC_R

75

YPbPr_R

YPbPr_L

PC_R

PC_L

J5A

1

2

3

4

5

6

+9V

R192

R191

22k

10k

Q915

1

2 3

BC847c

R194

1k

R193

75

YPbPr_L

C C

YPrPb_L

R190

C231

22uF/NS

+

10k

+9V

YPrPb_R

R164

C230

22uF/NS

+

10k

R187

R186

22k

10k

Q914

1

2 3

R189

BC847c

1k

R188

75

YPbPr_R

B B

A A

Title

40-LD2010-DIB4X(40-LD2010-DIC4X)

Size Document Number Rev

040108 chy

C

5

4

3

2

Date: Sheet

1

of

814Friday, August 19, 2005

Page 9

5

D D

J6

1

2

3

4

5

6

CON6

J2

1

2

CVBS1

3

4

SVIDEO_Y

5

6

SVIDEO_C

7

+9V

8

9

4

3

2

1

CON9

C C

B B

GND

C908

22U/16V

R925

+9V

c19

0.1u

R929

22K

Q906

2

1 3

BCB47

R930

10K

R931

1k

82

R919

R920

3K3

C905

22U/16V

1

AV1-V

AR

2

R922

6K8

R918

100K

R923

3K3

6K8

C906

22U/16V

1

R921

100K

AV1-V

AL

2

+9V +9V

+

C18

R905

C902

+

22U/16V

R906

22K

Q902

2

1 3

C1815

10K

BCB47

Q905

1 3

R904

22U/16V

82

1

AV1-V

AV

2

R907

1k

R928

R926

22K

2

R927

10K

1k

+

C907

103

R924

82

1

3 4

YC

2

SZ1

A A

Title

40-LD15V2-SVB2X

Size Document Number Rev

<Doc> <RevCode>

C

Date: Sheet

5

4

3

2

914Friday, August 19, 2005

of

1

Page 10

5

4

3

2

1

J1

CON5

D D

12345

J2

CON4

123

J7

J8

J6

4

1

234

1

2

1

2

VCC

LED

GND

IR

R6

330

C C

R4

1k2

R5

1k8

ch-ch+

R3

2k7

vol+

R1

3k3

vol-

R2

5k6

menu

ON/OFF

JP1

8

1

2

3

23

1

9

789

456

CIRDIN_8-P

7

6

5

4

R7

B B

330

SW1

J4

1

8

3

1

2

3

SW KEY-Y1011

A A

Title

40-L1526A-FBC1X

Size Document Number Rev

<Doc>

A

Date: Sheet

5

4

3

2

10 14Friday, August 19, 2005

of

1

Page 11

5

4

3

2

1

D D

Keypad

INTERFACE

NV RAM

INTERFACE

J3

1

2

3

4

5

J5

CON8

+5V

CON15

1

2

3

4

5

6

7

8

C68

0.1uF

6

7

8

9

+12V

C C

IR REMOTE SENSOR

INTERFACE

B B

J7

1

2

3

4

5

CON5

A A

5

L38 1k OHM

GND

L55

1k OHM

+5V

GND

R75

10K

C64

220pF

+5V

L54

1k OHM

C66

220pF

L39 1k OHM

GND

C66

220pF

ADC_IN1

4

C66

220pF

GND

LED

IR_IN

CON5

3

1x5x2.0mm

J8

1

2

3

4

5

+9V

C67

0.1uF

CVBS2

CVBS2

CVBS1

CVBS1

SVIDEO_Y

SVIDEO_C

MCSCL

MCSDA Y-L

MUTE#

TV_IN

2

GND

GND

C69

0.1uF

SVIDEO_Y

SVIDEO_C

+9V

J5A

1

CON8

Title

2

3

4

5

6

GND

Y-R

P-R

P-L

40-LD2010-DIB4X(40-LD2010-DIC4X)

Size Document Number Rev

040108 chy

B

of

Date: Sheet

11 14Friday, August 19, 2005

1

Page 12

5

AV1-L

AV1-R

R11

R10

C30

C29

1n

0

0

C9

C10

10u 25V

D D

C C

+5V

L4

0

100uH

C23

10n

10u 25v

C22

0

47U 25V

C11

56P

C15

10n

0

C16

0

3.3P

C41

0

C11

3.3P

0

10K

+5V

R5

MCSCL

MCSDA

+5V

10u 25v

0

100n PE

C18

IC502

MSP34*0G

49

AVSUP

50

ANA-IN+

51

ANA-IN-

56P

52

ANA-IN2+

53

TESTEN

54

XTAL-IN

55

XTAL-OUT

56

TP

57

AUD-CL-OUT

58

NC

59

NC

60

D-CTR-I/O1

61

D-CTR-I/O0

62

ADR-SEL

63

STANDBYQ

64

NC

R28

100 2.2uF

R22

100

L6

Y_R

C32

R12

R

C42

C554

1n

1n

0

C10

10u 25v

10u 25v

C7

0

4847464544424139383433

12345678910111213

43

AVSS

SC1-IN-L

SC1-IN-R

MONO-IN

VREFTOP

IC204 DIP2 MSP34*5G

I2C-CL

I2C-DA

I2S-CL

I2S-WS

I2S-DA-OUT

C33

103

ASG

SC2-IN-R

I2S-DA-IN1

ADR-DA

C32

40

ASG

SC2-IN-L

ADR-WS

ADR-CL

47u 25v

0

+5V

PC_RY_L

R

C31

1n

0

C34

C35

3u3 25v

ASG

SC3-IN-L

SC3-IN-R

DVSUP

DVSS

I2S-DA-IN2NCRESETQ

0

C39

103

C37

353637

SC4_IN_R

14

R13

R

C550

1n

0

AGNDC

SC4_IN_L

SC1-OUT-L

SC1-OUT-R

SC2-OUT-L

SC2-OUT-R

DACM-SUB

NC

NC

16

15

0

PC_L

0

CAPL-M

AHVSS

AHVSUP

CAPL-A

DACM-L

DACM-R

DACA-L

DACA-R

10U 25v

1n

C35

100n PE

C19

VREF1

VREF2

R33

C38

R15

R

C26

1n

32

31

30

29

28

27

26

25

24

NC

23

22

NC

21

20

19

18

17

R20

C25

R25

0

C24

C3

C3

SIF

B B

R24

R31

L3

0

0

+5V

L603

L612

L604

L602

R630

C631

5

C631

C632

L612

Q612

C603

A A

C637

C633

BAV99

D613

C634

R631

C635

L606

D614

4

Y_L

Y_R

C40

1n

0

PC_R

PC_L

SVC

SVY

AV1

P4

1

2

3

4

5

6

7

8

9

10

11

12

+5V

0

1n5

C20

C28

47u 25v

C27

470p

0

C36

C21

0

+5V

R16

1K

R19

47u 25v

47u 25v

R7

100

C13

1000p

10K

D1

1N4148

0

100

C14

0

+9V

L5

22uH

1K

R36

L

R

1000p

R6

R30

1K

0

R37

C4

C44

RS

2n/ns

2n/ns

3

IC1

7805

3

O

C45

C46

47U 16V

10n

0

C5

OUT_L

2.2uF

C43

OUT_R

C2

47u 25v

1

I

G

2

L1

C1

10n

SDA

TV_IN

0

J5

1K

R3C6

EAR_L

SPK_L

SPK_R

EAR_R

R4

1K

4

3

2

1

456

3

EAR

2

1

6

5

0

IN_L

IN_R

2

C57

J1

1

2

3

4

5

6

7

8

Q7

J2

1

2

3

4

5

6

IN_RSCL

OUT_R

OUT_L

+9V

C58

SVY

R43

Q6

SVC

+9V

C59

C60

AV1

Q8

R54

AV1-L

R42

R44

R50

C67

R46

LIN_L+9V

R

R35

R41

R34

R38

C66

R60

1

J3

1

2

3

4

C63

SVY

R53

SVC

R52

AV1

Audio R

P8

PN

R56

C47

R17

C638

C604

C636

TV_IN

R604

MCSDA

MCSCL

Q610

0

TDA9886T

R615

C611

R618

SCL

SIOUT/MAD

NC

TAGC

131415

C48

101211

SDA

REF

C613

Z601

C612

C619

R619

AGC TOP

IF AGC

16

AUDIO OUT

CVBS OUT

17

C621

C620

R617

C617

C615

AFD

D GND

AGND

18192021222423

DEEMP

VPLLVPAFC OUT

C622

C610

C614

R612

OUTP1

FM PLL

OUTPUT2

C609

R611

C618

VIF IN2

SIF1

123456789

VIF IN1

SIF2

IC601

R606

Z611

M9370M

12345

12345

M3953M

R606

Z610

D611

12345

12345

C632

MCSDA

MCSCL

L601

R1

R608

IF1

IF2

VT

C602

ADC

VS

NC

SDA

SCL

AS

TU

110 2356789411

AGC

AV1-R

R601

R613

R616

D601

C601

R614

4

3

2

Title

Size Document Number Rev

C

Date: Sheet

R45

40-LD2010-NIC2X

<Doc>

Audio L

R55

12 14Friday, August 19, 2005

of

1

Page 13

5

4

3

2

1

C81

0.1uF

U9

LM2596S-5.0

1

VIN

GND

3

4

TAB

C105

100uF/16V

GND

D12

1N4001

C111

C106

0.1uF

C112

0.1uF

2

VOUT

ADJONTAB

456

C93

0.1uF

GND

U12

3 2

U13

3 2

1 2

+3.3V_DVDD

GND

LT1117-3.3V

VIN VOUT

GND/ADJ

Sot223

1

LT1117-1.8V

VIN VOUT

GND/ADJ

Sot223

1

D9

IN5820

40mA

C94

100uF/16V

10V

TAB

GND

TAB

L15

33uH

C83

C82

330uF/16V

330uF/16V

4

4

100uF/16V

GND

C115

C116

0.1uF

GND

U14

LT1117-1.8V

3 2

VIN VOUT

GND/ADJ

Sot223

1

4

TAB

100uF/16V

GND

GND

31ohm at 100Mhz Rated Currrent

>=2A

L13 33R FB

L16 33R FB

L17 33R FB

C84

L18 33R FB

0.1uF

L19 33R FB

L20 33R FB

+5V

L23

33R FB

GND

C103

C104

0.1uF

100uF/16V

GND

GND

C110

C109

100uF/16V

0.1uF

GND

GND

C114

C113

100uF/16V

0.1uF

GND

GND

C85

100uF/16V

+5V_MUX

C102

22uF/16V

+3.3V_AVDD

+1.8V_DVDD

330uF/16V

C101

0.1uF

GND

200mA

CVDD:300mA

AVDD:60mA

+1.8V_DEC

R96

C91

GND

GND

C97

100uF/16V

10V

+12V

GND

U11

100

C92

0.1u

KIA278R09

VOUT

To-223

RELA1

4

Jidian1

GND

324

BC847c

C77

0.1u

D10

C90

1N4148

123

0.1u

J11

1

2

GND

CONTROL

GND

+12_nV

C100

0.1uF

L22

33R FB

C99

C98

100uF/16V

0.1uF

10V

R98

2k2

POWER

1

Vin

SW

R97

10k

Q10

1

2 3

GND

+5V

JP1

C87

C86

0.1uF

4

3

2

1

POWER IN

C89

C88

100P

0.1u

GND

470uF/25V

GND

+9V

C96

0.1uF

GND

GND

+3.3V_AVDD

+3.3V_LBADC

L25

33R FB

+12V

C95

100uF/16V

GND GND

A_1.8V

L28

33R FB

D_1.8V

L29

33R FB

POWER

R98

2k2

C107

C108

0.1uF

22uF/16V

GND

GND

2SJ449/STD30PF03L

Vin Vout

3 2

Source Drain

GATE

R98

1

10K

Q10

1

BC847c

2 3

C100

0.1uF

GND

GND

C95

100uF/16V

+12_nV

+12_nV

GND

C95

100uF/16V

L7809C

Vin Vout

1 3

Vin Vout

GND

2

GND

C95

100uF/16V

+9V

GND

+12V

L12 33R FB

L14 33R FB

D D

+5V

L21

33R FB

C C

C78

100uF/16V

C95

100uF/16V

GND

+5V

C79

470uF/25V

lt1084-3.3V

3 2

VIN VOUT

L24

C80

0.1uF

U10

GND/ADJ

1

GND

33R FB

+5V

L26

D11

1N4001

33R FB

B B

+3.3V_AVDD

L27

33R FB

A A

Title

40-LD2010-DIC4X

Size Document Number Rev

040108 chy

C

Date: Sheet

5

4

3

2

13 14Friday, August 19, 2005

of

1

Page 14

5

4

3

2

1

D D

DS1

IR01

123

R12

VCC +5V

10

C1

10U/10V

C C

VCC +5V

VCC +5V

R8

12

D1

LN117

B B

R10

10k

Q1

C1815

10k

IR

GND

+5V

LED1

J3

1

2

3

4

CON5

A A

Title

40-LD2026-IRA1X

Size Document Number Rev

<Doc> <RevCode>

A

Date: Sheet

5

4

3

2

14 14Friday, August 19, 2005

of

1

Loading...

Loading...