TE

C

H

tm

VSS→

Vcc

→

CS

WE

OE

T14L256A

SRAM

FEATURES

•

High speed access time: 8/10/12/15ns(max.)

• Low power consumption : Active 300 mW (typ.)

•

Single + 3.3 power supply

•

Fully static operation – No clock or refreshing

required

•

All inputs and outputs directly LVTTL compatible

•

Comm on I/O capability

•

Available packages :28-pin 300 mil, SOJ and

TSOP-I (forward type).

•

Output enable (OE) available for very fast

access

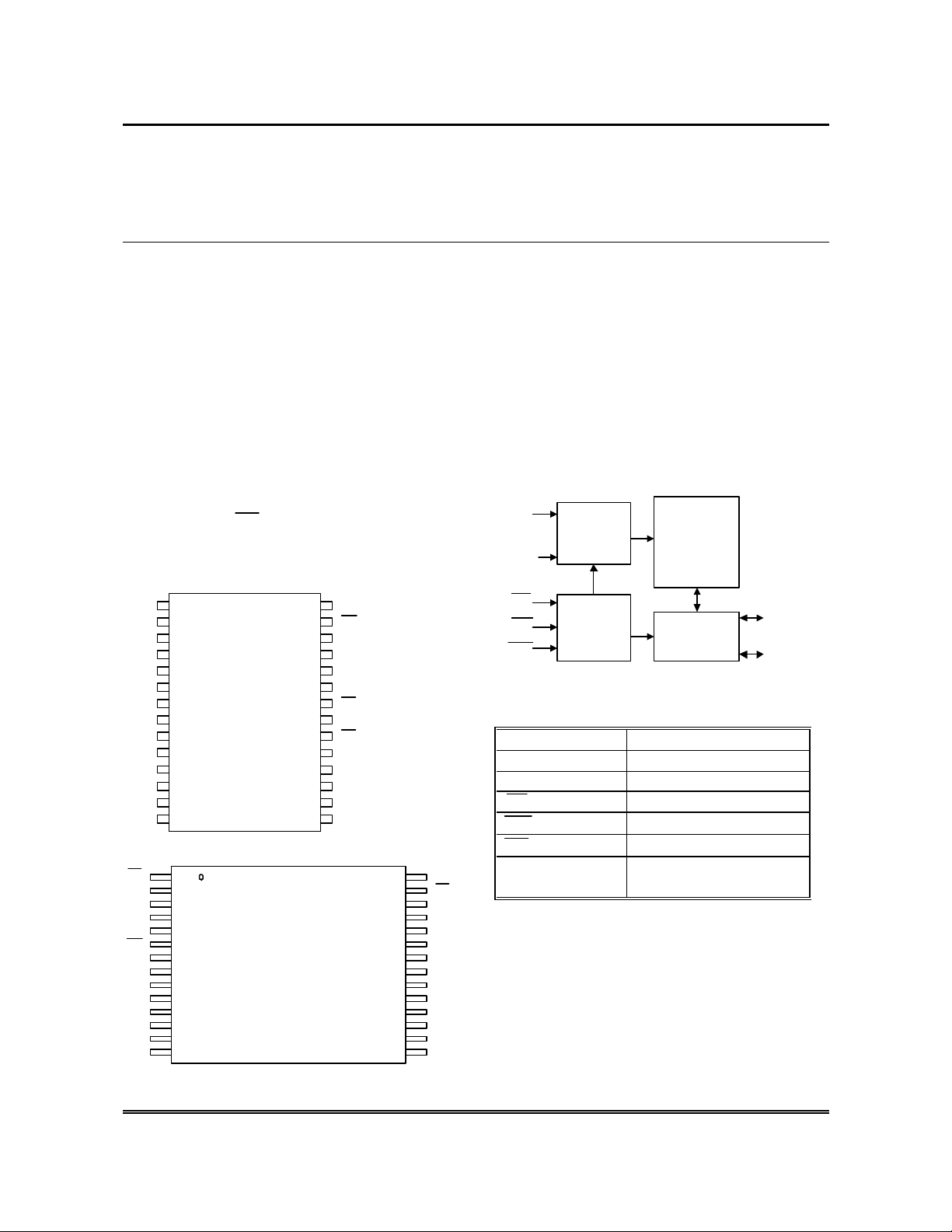

PIN CONFIGURATION

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O1

I/O2

I/O3

Vss

OE

A11

A9

A8

A13

WE

VCC

A14

A12

A7

A6

A5

A4

A3

1

2

3

4

5

6

7

SOJ

8

9

10

11

12

13

14

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

TSOP-I

Vcc

WE

A13

A8

A9

A11

OE

A10

CS

I/O8

I/O7

I/O6

I/O5

I/O4

28

27

26

25

24

23

22

21

20

19

18

17

16

15

A10

CS

I/O8

I/O7

I/O6

I/O5

I/O4

VSS

I/O3

I/O2

I/O1

A0

A1

A2

32K X 8 HIGH SPEED

CMOS STATIC RAM

GENERAL DESCRIPTION

The T14L256A is a high speed, low power

CMOS static RAM organized as 32,768 x 8 bits

that operates on a single 3.3-volt power supply.

This device is packaged in a standard 28-pin 300

mil SOJ or TSOP-I forward.

BLOCK DIAGRAM

A 0

.

DECODER

.

.

A 14

CS

OE

WE

CONTROL

PIN DESCRIPTION

SYMBOL DESCRIPTION

A0 - A14 Address Inputs

I/O1 - I/O8 Data Inputs/Outputs

Vcc Power Supply

Vss Ground

PART NUMBER EXAMPLES

PACKAGE SPEED

T14L256A-8J SOJ 8ns

T14L256A-8P TSOP-I

CORE

ARRAY

DATA I/O

Chip Select Inputs

Write Enable

Output Enable

8ns

I/O 1

.

.

.

I/O 8

Taiwan Memory Technology, Inc. reserves the right P. 1 Publication Date: APR. 2001

to change products or specifications without notice. Revision: E

TE

C

H

tm

V

IL

IH

A

I

I

SB1

I

LI

LO

CS

IH

OE

V

IH

WE

V

IL

OL

OL

OH

OH

2.4

CS

V

IL

SB

CS

IH

SB1

CS

cc

T14L256A

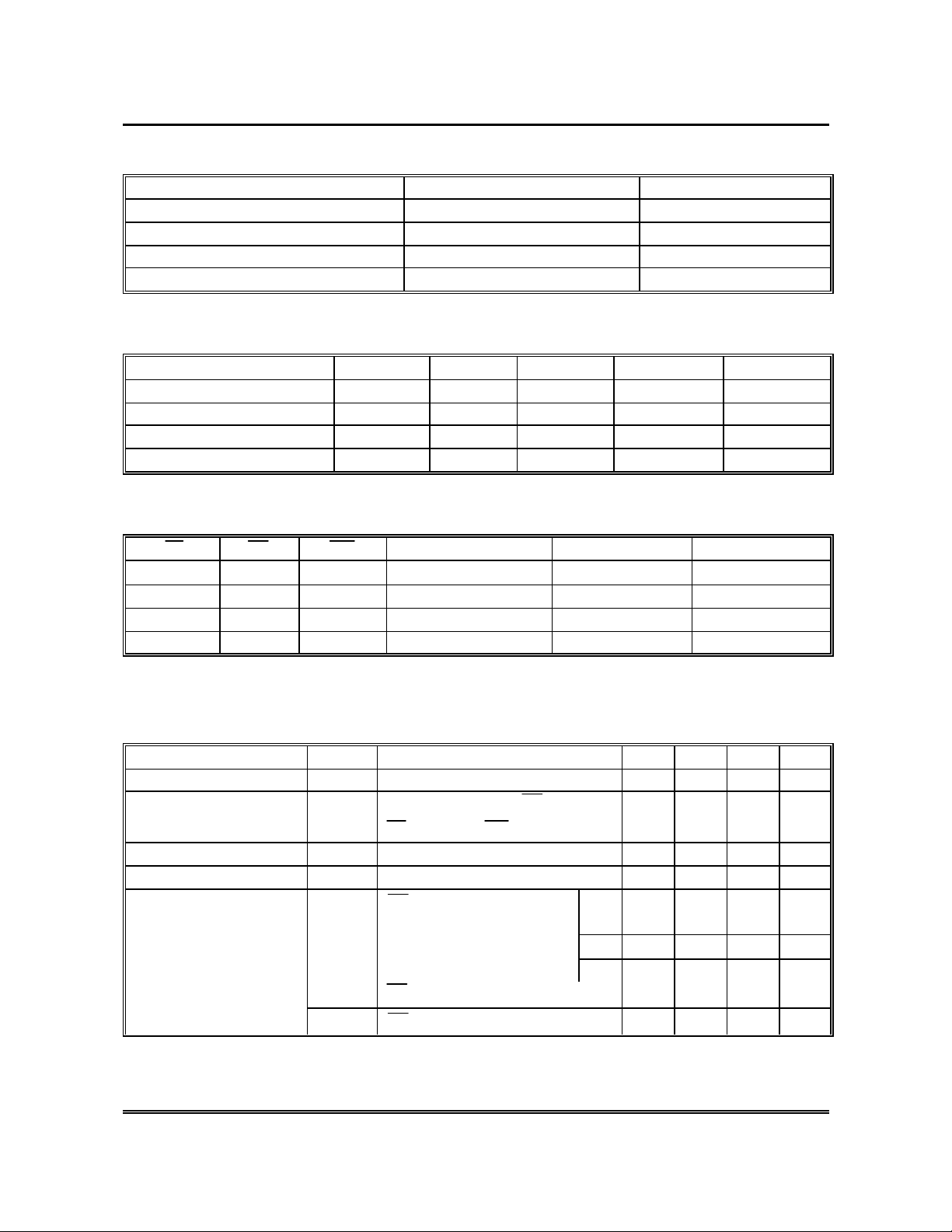

DC CHARACTERISTICS ABSOLUTE MAXIMUM RATINGS

PARAMETER RATING UNIT

Supply Voltage to Vss Potential -0.5 to + 4.6 V

Inputs to Vss Potential -0.5 to Vcc +0.5 V

Power Dissipation 1.0 W

Storage Temperature -60 to +150

RECOMMENDED OPERATING CONDITIONS

PARAMETER SYM MIN TYP MAX UNIT

Supply Voltage Vcc Typ-5% 3.3 Typ+ 5% V

V

T

-0.3 - 0.8 V

2.1 - Vcc+0.3 V

0 - 70 °C

Input Voltage, low

Input Voltage, high

Ambient Temperature

TRUTH TABLE

°

C

CS

OE

WE

MODE I/O1- I/O8 Vcc

H X X Not Selected High -Z

L H H Output Disable High-Z Icc

L L H Read Data Out Icc

L X L Write Data In Icc

OPERATING CHARACTERISTICS

(Vcc = 3.3V ± 5%, Vss = 0V, Ta = 0 to 70°C)

PARAMETER SYM. TEST CONDITIONS MIN. TYP. MAX. UNIT

Input Leakage Current

Output Leakage Current

Output Low Voltage

Output High Voltage

Operating Power

Supply Current

Standby Power

Supply Current I

Vin=Vss to Vcc -10 - +10 uA

V

V

I

Icc

V

I/O

=

I

= + 8.0mA

I

= - 4.0mA

Cycle = MIN.

Duty = 100%

=Vss to Vcc ,

or

=

, I/O=0mA

=

=

V

or

-10 - +10 uA

- - 0.4 V

- - V

8 - - 110 mA

10 - - 100 mA

12 - - 90 mA

15 - - 80 mA

I

V

=

, Cycle=MIN, Duty=100%

V

≥

-0.2V

- - 15 mA

- - 2 mA

SB,

Note: Typical characteristics are at Vcc = 3.3V, Ta = 25°C

Taiwan Memory Technology, Inc. reserves the right P. 2 Publication Date: APR. 2001

to change products or specifications without notice. Revision: E

TE

C

H

tm

IN

IN

I/O

OUT

C

L

I

OH

I

OL

T14L256A

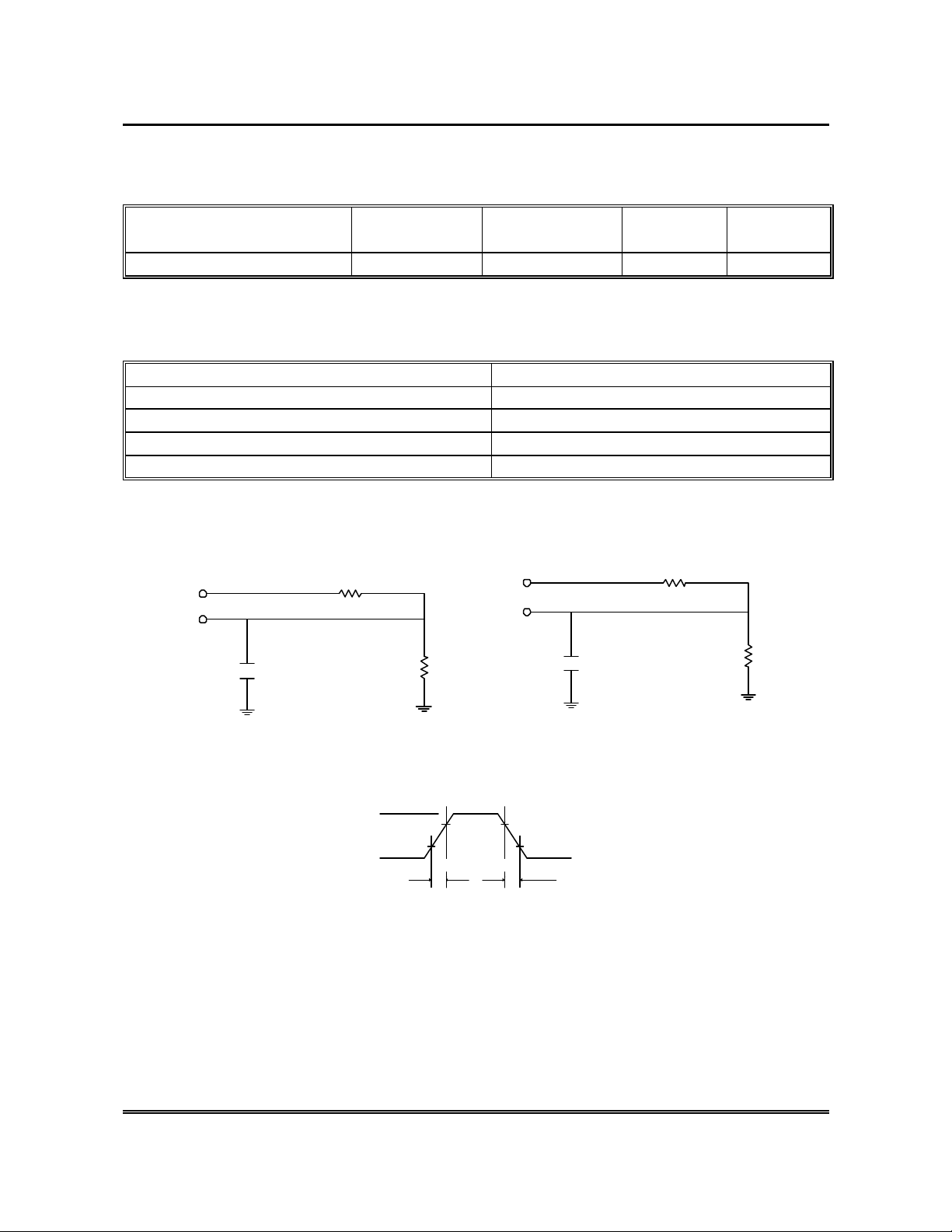

CAPACITANCE

(Vcc = 3.3V, Ta = 25°C, f = 1 MHz)

PARAMETER SYMBOL CONDITION MAX. UNIT

C

Input Capacitance

Input/ Output Capacitance

Note: These parameters are sampled but not 100% tested.

C

AC TEST CONDITIONS

PARAMETER CONDITIONS

Input Pulse Levels 0V to 3V

Input Rise and Fall Times 3 ns

Input and Output Timing Reference Level 1.5V

Output Load

AC TEST LOADS AND WAVEFORM

3.3V

OUTPUT

R1 320 ohm

30pF

Including

Jig and

Scope

OUTPUT

R2

350 ohm

V

V

=30pF,

3.3V

= 0V

= 0V

/

= -4mA/8mA

R1 320 ohm

5pF

Including

Jig and

Scope

6 pF

8 pF

R2

350 ohm

(For TCLZ, TOLZ, TCHZ, TOHZ, TWHZ, TOW )

3.0V

0 V

3ns

Taiwan Memory Technology, Inc. reserves the right P. 3 Publication Date: APR. 2001

to change products or specifications without notice. Revision: E

90%

10% 10%

90%

3ns

Loading...

Loading...