Page 1

Series

3

Technical Reference Manual

980327-02

Page 2

Trademarks

I

P

All rights reserved. This product or document is protected by copyright and distributed under licenses restricting its

use, copying, distribution and decompilation. No part of this product or document may be reproduced in any form

by any means without prior written authorization of Sun and its licensors, if any. This product or the products

depicted herein may be protected by one or more U.S. or international patents or pending patents. Portions of this

product may be derived from the UNIX® and Berkeley 4.3 BSD systems, licensed from UNIX Systems

Laboratories, Inc. and the University of California, respectively. Third party font software in this product is

protected by copyright and licensed from Sun’s Font Suppliers.

RESTRICTED RIGHTS LEGEND: Use, duplication, or disclosure by the government is subject to restrictions as

set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS

252.227-7013 and FAR 52.227-19.

Sun, Sun Microsystems, the Sun Logo, OpenWindows, SunView, SunOS, DeskSet, NFS and NEWS are trademarks

or registered trademarks of Sun Microsystems, Inc. UNIX and OPEN LOOK are registered trademarks of UNIX

Systems Laboratories, Inc. All other product names mentioned herein are the trademarks of their respective owners.

All SPARC trademarks, including the SCD Compliant Logo, are trademarks or registered trademarks of SPARC

International, Inc. The SPARCbook trademark is licensed exclusively to Tadpole Technology, Inc. Products bearing

SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK® and Sun™ Graphical User Interfaces were developed by Sun Microsystems, Inc. for its users

and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of

visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the

Xerox Graphical User Interface, which license also covers Sun’s licensees who implement OPEN LOOK GUI’s and

otherwise comply with Sun’s written license agreements.

The X Window System is a product of the Massachusetts Institute of Technology.

UNIX and OPEN LOOK are registered trademarks of UNIX System Laboratories

PostScript is a trademark of Adobe Systems, Inc

Solaris is a product of Sun Microsystems, Inc

Notebook Computing Environment and NCE are trademarks of Tadpole Technology, Inc.

ssue 2.2 (Draft) of February 10, 1997 © 1996, 1997 by Tadpole Technology

art number 980327-02 Printed in the UK

Page 3

Contents

About This Guide ix

Document Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .x

Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

Logic states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

Data entities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

Typographical conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

Key presses, buttons, and field names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

Solaris commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xii

Notes, cautions and warnings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xii

Chapter 1 Architecture Overview

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2 Main Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2.1 Base board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2.2 CPU module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2.3 Microcontroller module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2.4 Main display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

1.2.5 Other components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.3 System Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.4 Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.5 Main System Buses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.5.1 Memory bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.5.2 SBus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.5.3 Ebus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-7

1.6 DRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.7 Slow I/O Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.7.1 Serial Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.7.2 Counter-Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.7.3 Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.7.4 EBus Interface and Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.8 Fast I/O Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.8.1 SCSI Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.8.2 Ethernet Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.8.3 Parallel Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.8.4 FIFOs and DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.9 Graphics and Video Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.9.1 Graphics Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.9.2 VRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-12

1.9.3 RAMDAC, Panel Driver and Video Clock Generator . . . . . . . . . . . . . . . 1-12

1.10 MK48T08 RTCRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.11 ISDN and 16-Bit Audio Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.12 PCMCIA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

iii

Page 4

1.13 Modem Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.14 Microcontroller Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

Chapter 2 The SPARC CPU

2.1 SPARC Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.2 Integer Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2.1 Pipeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2.2 Instruction set overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2.3 Traps and interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.2.4 Memory protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.2.5 IU internal registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.2.6 IU control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.3 Floating Point Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.3.1 Floating Point Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.4 Cache Controller and Memory Management Unit . . . . . . . . . . . . . . . . . . . . . . 2-8

2.4.1 Translation lookaside buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.4.2 Address translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.5 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.6 Instruction Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.7 Data Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.8 SBus Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.8.1 Programmed I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.8.2 DVMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Chapter 3 Memory Map and Interrupts

3.1 Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.1 MACIO and SLAVIO Space (SBus Slot 4) . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.2 DRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.2.1 Interrupt Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.3 NCR89C105 SLAVIO Configuration Control . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.3.1 SLAVIO Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.3.2 Diagnostic Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.3.3 Miscellaneous System Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Chapter 4 Serial Interface

4.1 Serial Channel Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.1.1 Serial Interface Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2 SCC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.2.1 Register functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.3 Baud Rate Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

4.4 Handshakes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

iv

Page 5

Chapter 5 SCSI Controller

5.1 Connecting SCSI Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.2 NCR53C9X SCSI Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.2.1 53C9X register set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.3 DMA Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.3.1 DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.3.2 DMA Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.3.3 SCSI Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Chapter 6 Ethernet Interface

6.1 NCR92C990 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.1.1 Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.1.2 LAN Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.1.3 Descriptor Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.2 LAN Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2.1 Register Indexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2.2 Control and Status Register 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2.3 Control and Status Register 1 and 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.4 Control and Status Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.3 DMA Support for Network Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

Chapter 7 PCMCIA Interface

7.1 TS102 Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.1.1 SBus interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.1.2 PCMCIA interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.1.3 Microcontroller interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.2 TS102 Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.2.1 Acceses to PCMCIA Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.2.2 Byte Swapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.2.3 SLAVIO expansion interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.3 TS102 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.3.1 Card A and B interrupt registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

7.3.2 Card status register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.3.3 Card Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.3.4 Microcontroller Interrupt Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.3.5 Microcontroller data register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.3.6 Microcontroller status register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.4 Microcontroller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

Chapter 8 ISDN and 16-bit Audio

8.1 ISDN Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

8.2 DBRI Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

8.2.1 TE and NT Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.2.2 CHI Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

v

Page 6

8.2.3 SBus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.2.4 DBRI Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

8.2.5 DBRI Internal Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.2.6 DBRI Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

8.2.7 Data structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-13

8.3 Audio CODEC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-14

8.3.1 Clocking and Data Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-14

8.3.2 Control Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-17

8.3.3 Data Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-20

Chapter 9 MODEM

9.1 Internal Modem Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.2 Interface Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.3 Modem Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.3.1 Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.3.2 Interrupt Identification Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.3.3 Line Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

9.4 AT Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

9.5 S Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-11

9.6 Class 2 Fax Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-27

Chapter 10 Parallel Interface

10.1 Parallel Port Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.1.1 Parallel Port DMA Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.2 Parallel Port Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

Chapter 11 Display Interface

11.1 Display Interface Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

11.1.1 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

11.1.2 Display Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

11.1.3 LCD Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4

11.2 Power 9100 User Interface Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

11.2.1 Parameter engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-6

11.2.2 Drawing engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-6

11.2.3 Frame buffer controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-6

11.2.4 SVGA unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7

11.2.5 Power 9100 host interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7

11.2.6 System Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-9

11.2.7 Video Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-12

11.2.8 VRAM control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-15

11.2.9 Parameter engine registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-15

11.2.10Drawing engine registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-18

11.2.11RAMDAC register accesses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-20

11.3 Direct frame buffer access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-20

vi

Page 7

11.4 RAMDAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

11.4.1 RAMDAC host interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-22

11.4.2 Control register accesses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-22

11.4.3 Color palette accesses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-28

11.4.4 Pixel Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-29

Chapter 12 Microcontroller Subsystem

12.1 Microcontroller subsystem overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-2

12.1.1 Normal operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-3

12.1.2 Internal keyboard scanning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

12.1.3 External keyboard and mouse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

12.1.4 Pointing stick . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

12.1.5 Real time clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

12.1.6 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

12.1.7 LCD status display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-5

12.2 Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-6

12.2.1 Command synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-6

12.2.2 System Information Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-6

12.2.3 Read/Write/Modify Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-11

12.2.4 Commands Returning no Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-14

12.2.5 Block Transfer Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-15

12.2.6 Generic Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-16

12.2.7 Generic Commands with Optional Status . . . . . . . . . . . . . . . . . . . . . . . . 12-17

12.2.8 Administration Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-18

Appendix A Further Information

Appendix B Connector Information

B.1 I/O Panel Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-2

B.1.1 DCIn . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-2

B.1.2 Parallel (S3XP, S3GX and S3TX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-2

B.1.3 Parallel (S3 and S3LC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-3

B.1.4 Ethernet (S3XP, S3GX and S3TX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-3

B.1.5 Ethernet (S3 and S3LC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-4

B.1.6 Video . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-4

B.1.7 SCSI (S3XP, S3GX and S3TX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-5

B.1.8 SCSI (S3 and S3LC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-6

B.1.9 Keyboard/Mouse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-6

B.1.10Serial (x2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-6

B.1.11ISDN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-7

B.2 Cable Adapter Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-8

B.2.1 Parallel Cable Adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-8

B.3 Removable Hard Drive SCSI Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-9

vii

Page 8

viii

Page 9

Note

About This Guide

The SPARCbook 3 Technical Reference Manual is

written for the hardware engineer wishing to carry

out service or repairs, and at the software engineer

wishing to implement hardware drivers. It is

assumed that you are familiar with the operation of

SPARCbook 3, as detailed in the SPARCbook 3

User Guide, and that you have an understanding of

computer hardware.

The SPARCbook 3 Technical Reference Manual covers all

models of SPARCbook 3. Where information for one model

differs to information for another model, this is indicated in the

text.

Page 10

Document Summary

The SPARCbook 3 Technical Reference Manual comprises the following

chapters:

• Chapter 1 ,

SPARCbook 3 and introduces the main hardware devices that provide

control over the SPARCbook 3’s operations. The internal architecture

of SPARCbook 3 is described, showing how the major devices are

connected together.

• Chapter 2,

processor.

• Chapter 3,

architecture and the interrupt architecture of the SPARCbook 3.

• Chapter 4 ,

SPARCbook 3.

• Chapter 5,

• Chapter 6,

SPARCbook 3.

• Chapter 7,

the SPARCbook 3.

• Chapter 8,

16-bit audio controller.

• Chapter 9,

3.

Architecture Overview,

Microprocessor

Memory Map and Interrupts

Serial Interface

SCSI Communications,

Ethernet Interfac

PCMCIA

ISDN and 16-Bit Audio Controller

Modem

, discusses the internal modem on the SPARCbook

, provides an overview of the SPARC

, discusses the serial interface of the

, discusses the PCMCIA interface implemented in

discusses the main features of the

, describes the addressing

discusses the SCSI controller.

e, discusses the Ethernet interface of the

, discusses the ISDN and

• Chapter 10,

SPARCbook 3.

• Chapter 11,

implemented in the SPARCbook 3. The discussion is centered on the

Brooktree Bt445 RAMDAC, on which the interface is based.

• Chapter 12,

subsystem. This is used to provide internal control over such things as

the display brightness, keyboard and mouse scanning and power

management.

x

Parallel Interface

Display Interface

Microcontroller Subsystem

, discusses the parallel interface on the

, discusses the display interface

, discusses the microcontroller

Page 11

Definitions

Logic states

The following conventions are used in the SPARCbook 3 Technical

Reference Manual:

The terms

level ‘0’.

The terms

level ‘1’.

The term

regardless of whether that state is high or low.

The term

regardless of whether that state is high or low.

clear

or

set

or

asserted

negated

low

high

indicates that a signal is in its true or active state

indicates that a signal is in its false or inactive state

Data entities

A

halfword

A

word

A

doubleword

is taken to contain 16 bits.

is taken to contain 32 bits.

is taken to contain 64 bits

Typographical conventions

Different typography is used in this guide to distinguish between normal

text, examples of SPARCbook responses, and cases where you are required

to provide input using the keyboard or mouse.

Key presses, buttons, and field names

Key presses are shown in

you need to press two or more keys; for example:

To switch off your SPARCbook, press

indicate that the signal being discussed is at the logic

indicate that the signal being discussed is at the logic

Helvetica bold

. In order to perform certain tasks,

Pause-O.

In this case, you should press the

holding the

Buttons and field names are also shown in

Click the

Type the name of the file that you want to send in the

key down, press the O key.

Pause

Transmit

button.

key down first, and then, while

Pause

Helvetica bold

. For example:

File Name

field.

xi

Page 12

Solaris commands

Information displayed on your SPARCbook screen by the Solaris

Operating System is shown in

Courier

font.

Courier

is also used to

describe system utilities and commands. For example:

The

mail

system will inform you when there is incoming mail from

another user.

you have mail

Bold Courier

perform a specific task. For example:

To report the current time and date you should use the

command:

%

Notes, cautions and warnings

Notes are used throughout this manual to explain items of related interest

to the topic under discussion, and are used to refer the reader to another part

of the manual, or to other documentation.

Note

This is an example of a note, used as to provide additional information.

Cautions are used to advise the reader of actions that if carried out may

cause damage to the SPARCbook 3.

Caution

This is an example of a caution

Warnings are used to draw your attention to actions that could cause

personal injury or pose a hazard to life. For example:

WARNING!

THE AC ADAPTER SUPPLIED WITH YOUR SPARCBOOK 3 CONTAINS

HAZARDOUS VOLTAGES. IT CONTAINS NO USER SERVICEABLE

PARTS. DO NOT REMOVE THE COVERS.

is used in examples to show what you must type in order to

date

date

xii

Page 13

Architecture Overview

This chapter discusses the architecture of the

SPARCbook 3. It describes the main system

components and how they are packaged together to

deliver workstation-class performance in a compact

notebook form factor.

1

1

Page 14

1.1 Introduction

At the heart of the SPARCbook 3 design concept is the Tadpole Advanced

Notebook Architecture (ANA). This defines a set of goals and guidelines to

which the SPARCbook 3 range of systems are designed. It is a modular

approach which results in a system that implements highly integrated

components to provide the performance and I/O facilities normally

associated with desktop workstations. It also results in a system that can be

readily upgraded by the user with larger memory (up to 128 MB) or disk

capacities or returned to the factory for upgrades with the fastest CPUs

available for notebook implementation.

1.2 Main Components

The SPARCbook 3 contains three printed circuit boards. These are the

S3-XP Base board, the S3-XP or the S3TX CPU module, and the

microcontroller board.

1.2.1 Base board

The S3-XP Base board carries all of the I/O components together with the

display controller, RAMDAC and 2MB of Video RAM, and the battery

management hardware. It is populated on both sides using mainly surface

mount devices in order to keep its physical dimensions to a minimum. The

Base board also carries two PCMCIA sockets and the I/O panel which is

visible at the rear of the assembled system.

Introduction

1.2.2 CPU module

1-2

Architecture Overview

The Base board provides mounting points and sockets to accommodate the

CPU module.

The CPU module carries the main SPARC CPU. The CPU module is

extended to carry the main memory SIMMS. This physical arrangement

has the advantage of making the SIMMs very easy to fit to or remove from

a fully assembled system through the battery tray without the use of tools.

The CPU module is mounted onto the base board such that the CPU itself

is sandwiched between the CPU module and Base board. However, an

interesting feature of the Base board is a large hole through which a

heatsink fitted to the main CPU is allowed to protrude when the two boards

Page 15

Main Components

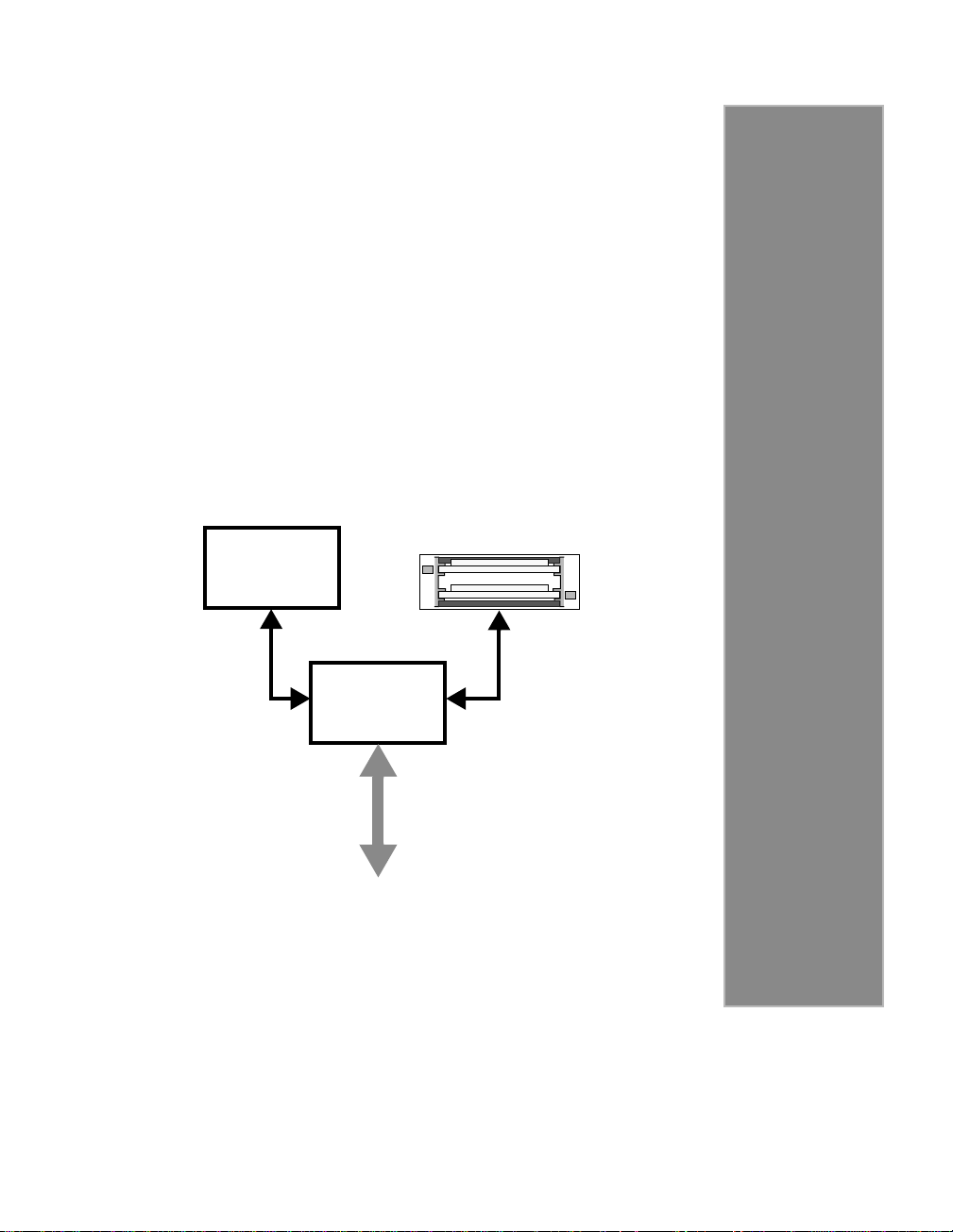

are fixed together. When the two boards are correctly assembled, the CPU

heatsink is brought into contact with the system’s magnesium base casting

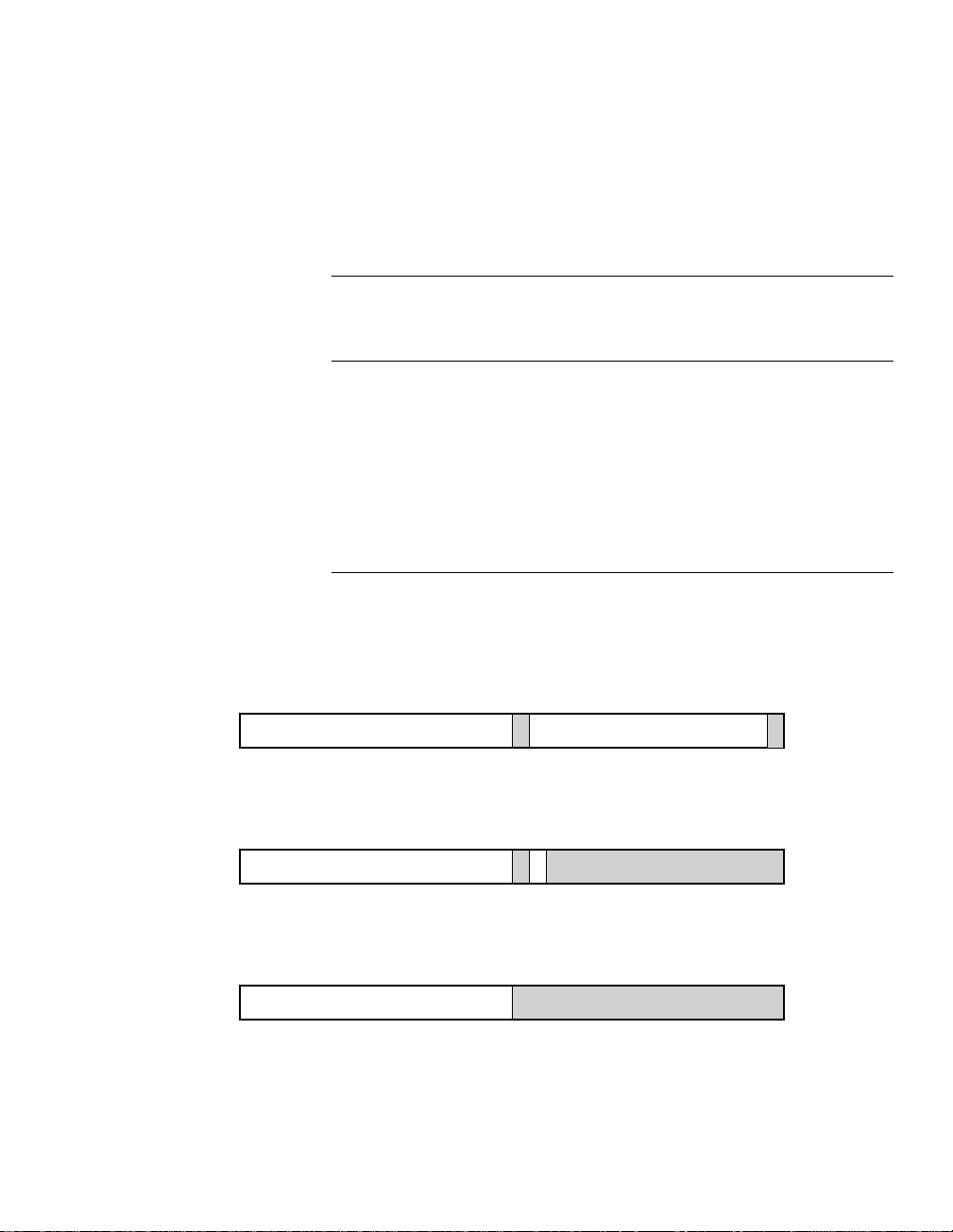

to provide effective heat dissipation, as shown in Figure 1-1.

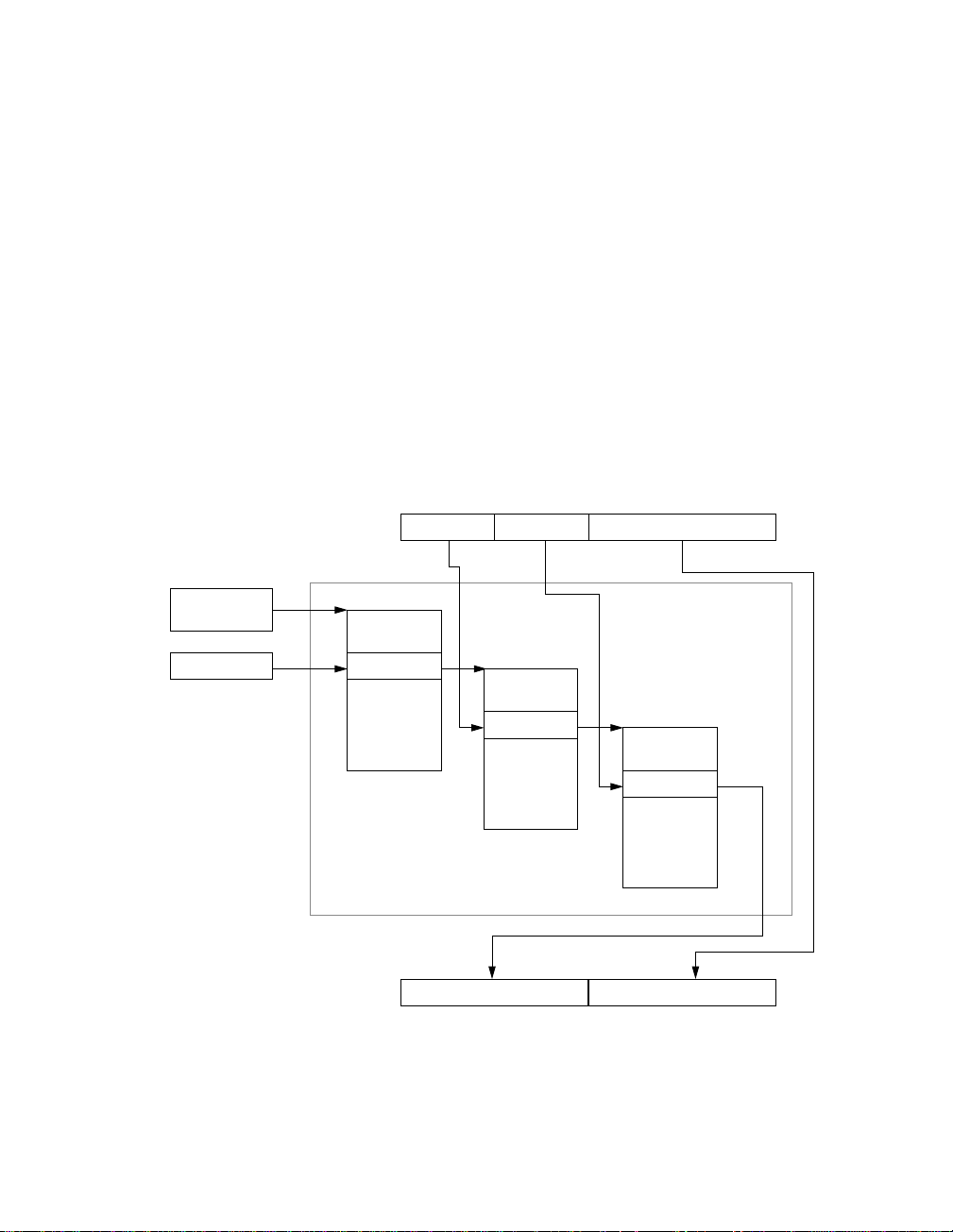

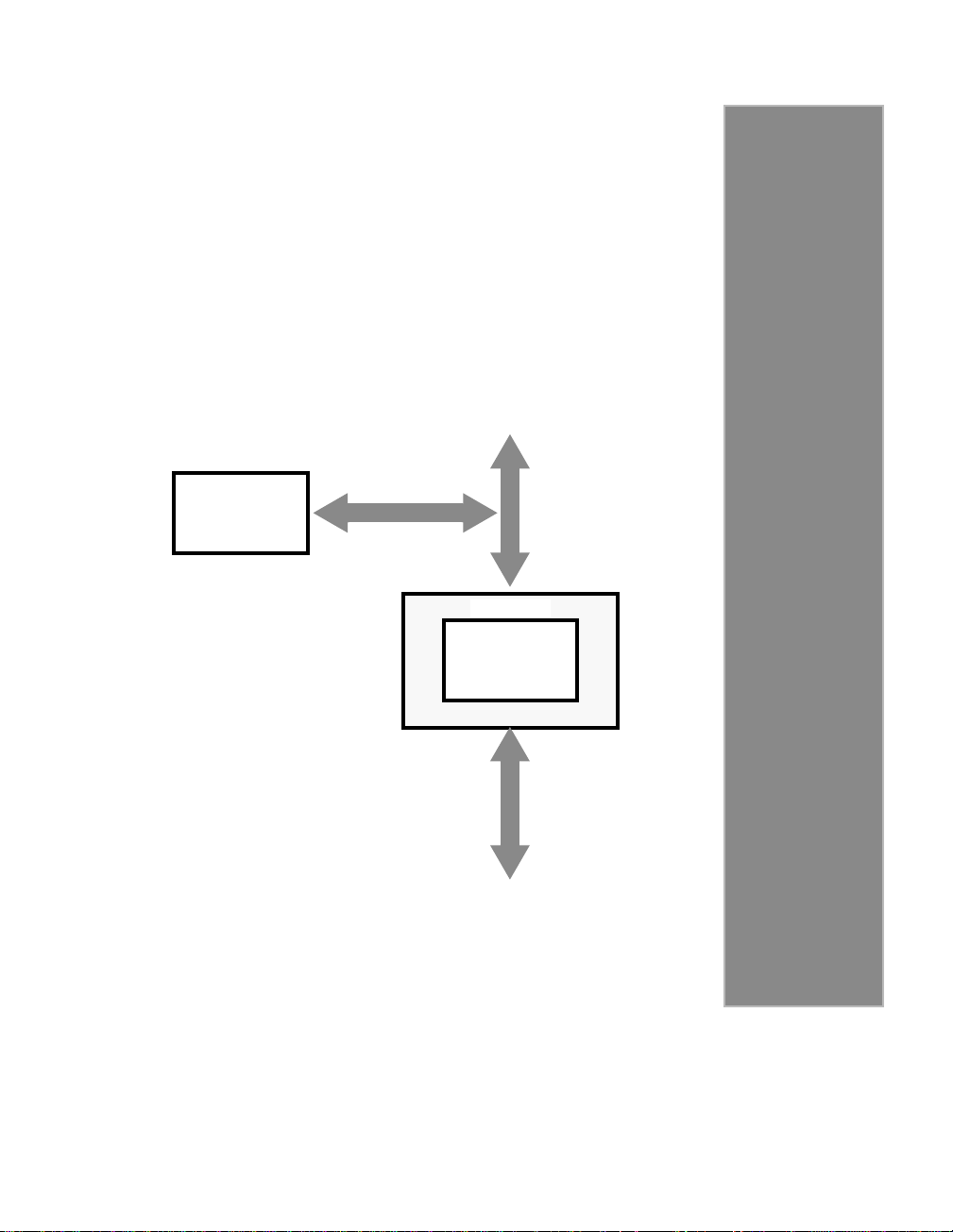

Figure 1-1 CPU Heat Dissipation

1.2.3 Microcontroller module

The microcontroller module is a small board which carries an Hitachi H8

microcontroller, the status display which is visible from the outside of the

assembled system, and a number of programmable memory devices. It

provides connections for the keyboard and pointing stick for which it

provides control and for the Base board for which it provides system

control and status monitoring functions.

Inter-Board Connectors

Heatsink

CPU

CPU Module

Base Board

System’s Magnesium

Base

1.2.4 Main display

The main display is housed within the system’s lid along with an inverter

board required to drive the display’s backlight. Systems use either 9.4 inch

640 x 480 or 10.4 inch 800 x 600 color TFT display to provide a sharp

image in a wide range of lighting conditions. The brightness of the

backlight is controlled by the microcontroller and can be varied to suit the

lighting conditions or can be dimmed or turned off when required to

conserve battery power.

1.2.5 Other components

In addition to the main boards and display, the SPARCbook 3 system

contains is a 2.5 inch 1.2 GB (or larger when available) SCSI hard disk

drive assembled within a removable module. The drive can be removed

from the SPARCbook 3 while the system is fully assembled, see your

SPARCbook 3 User Guide

.

Architecture Overview

1-3

Page 16

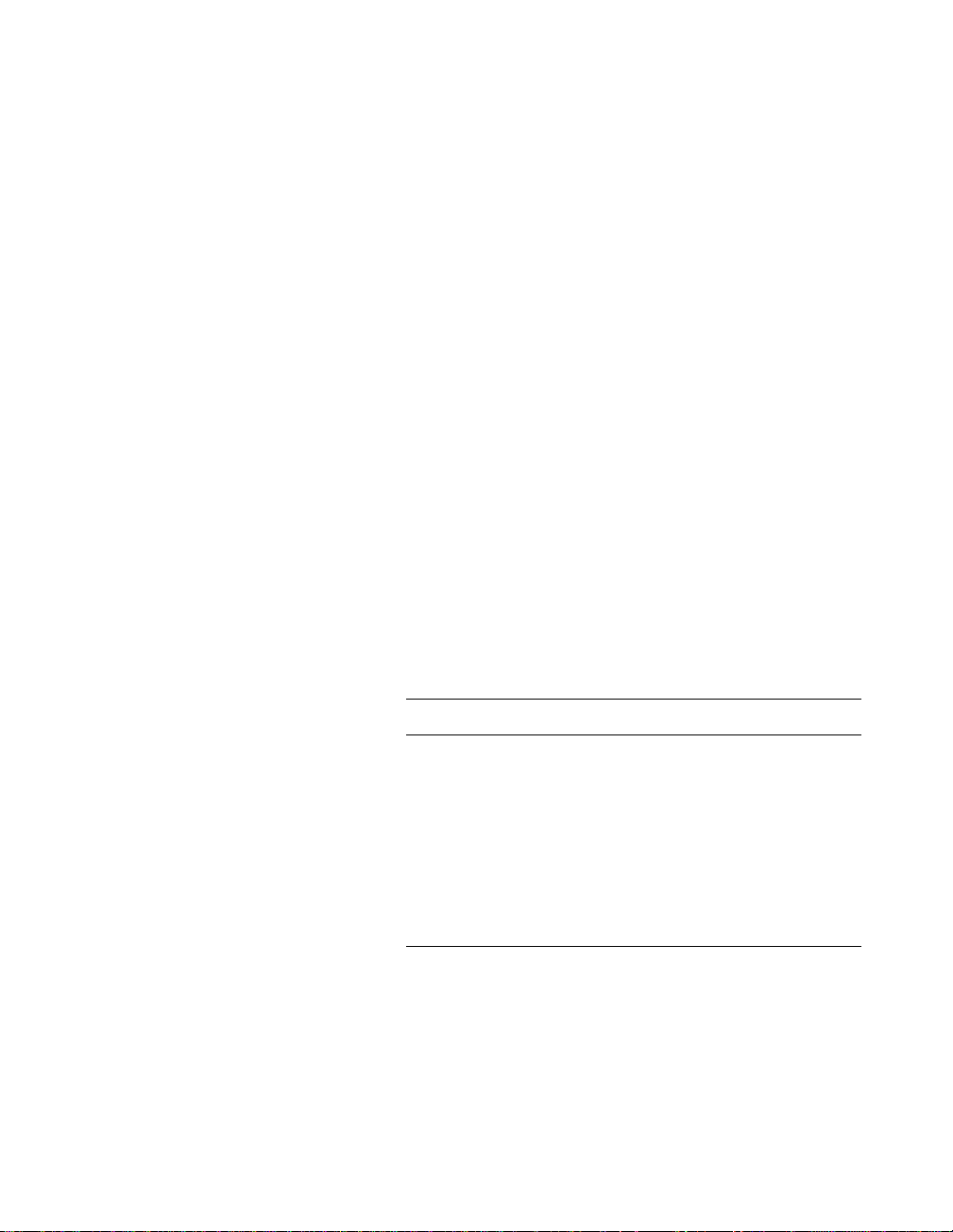

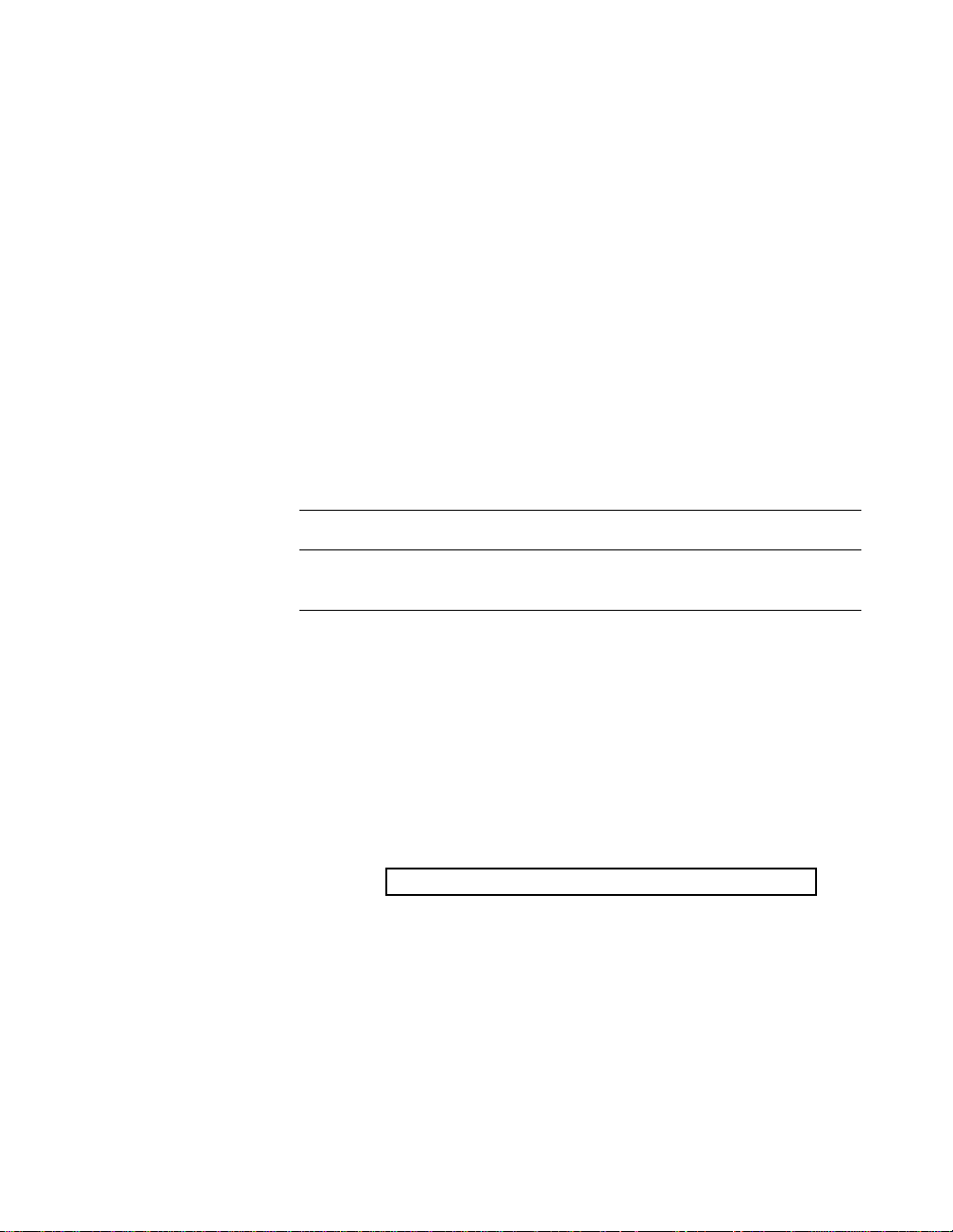

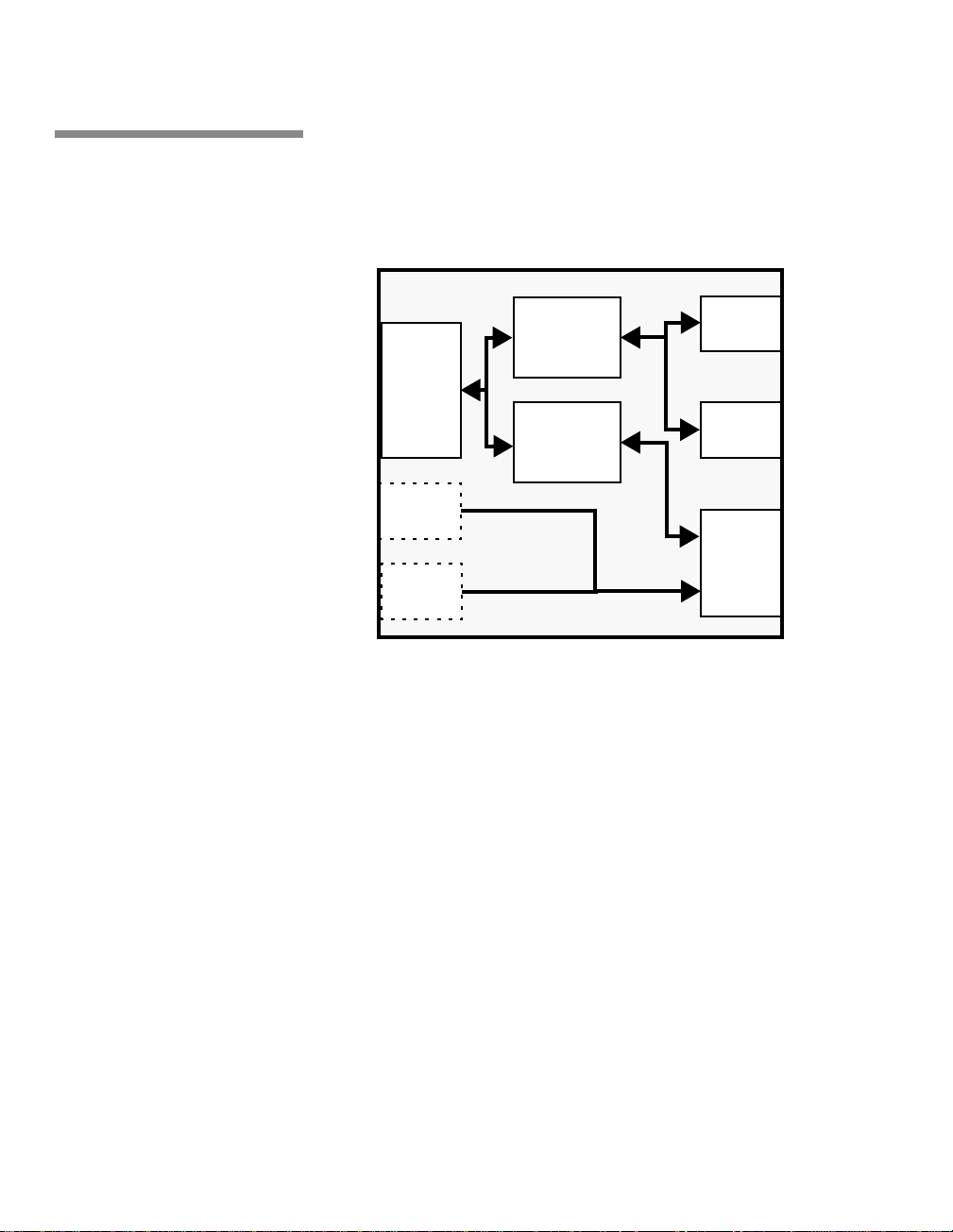

1.3 System Architecture

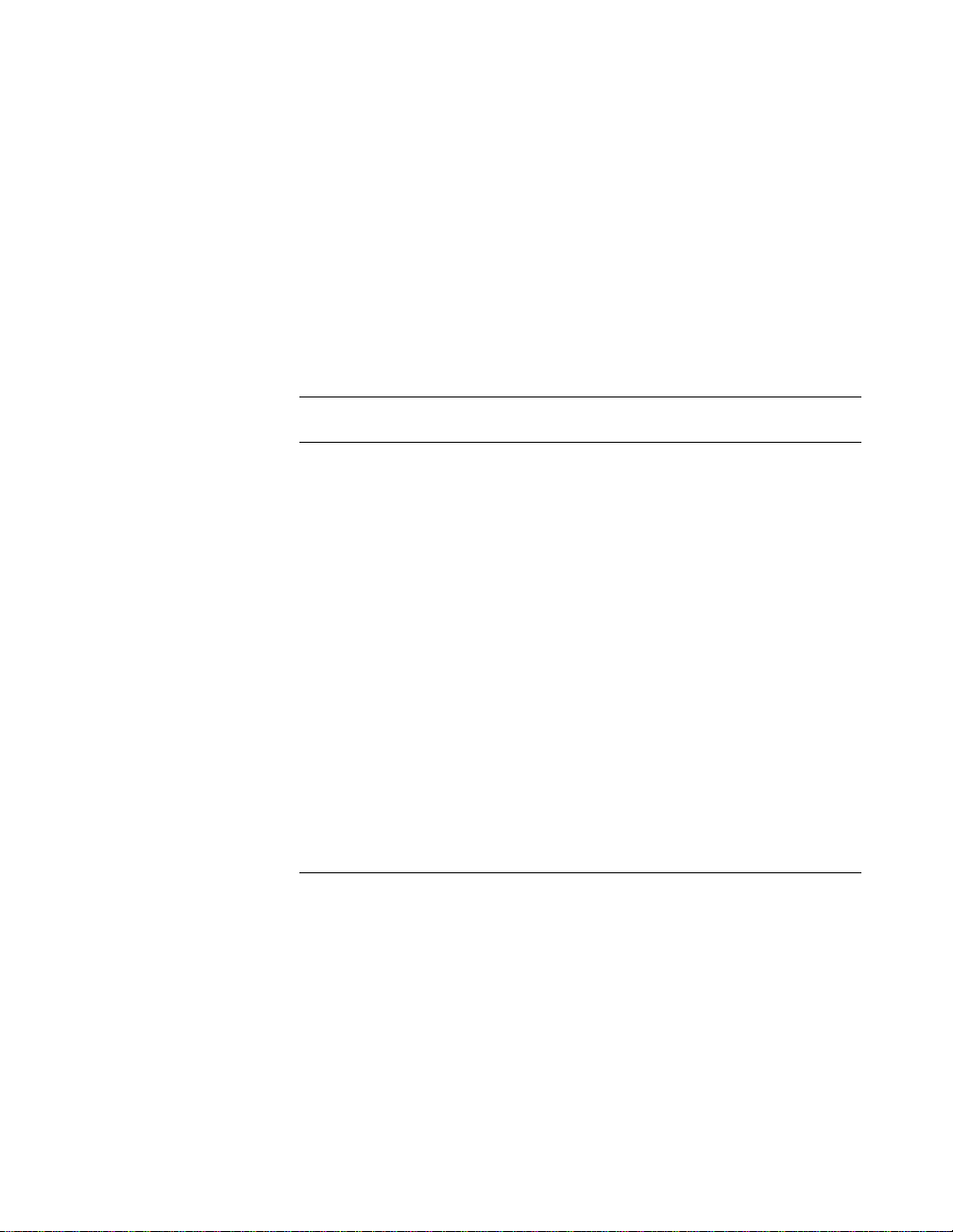

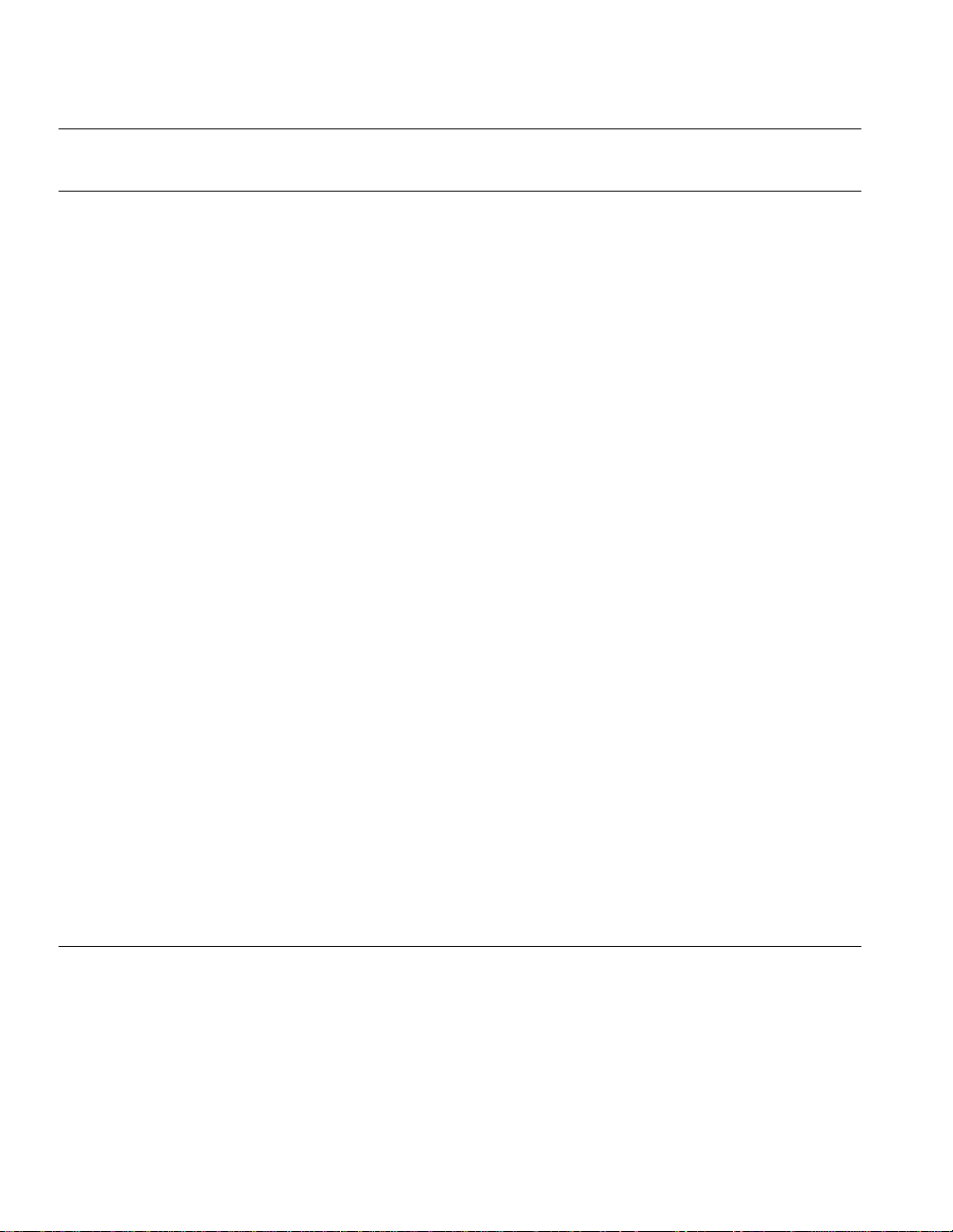

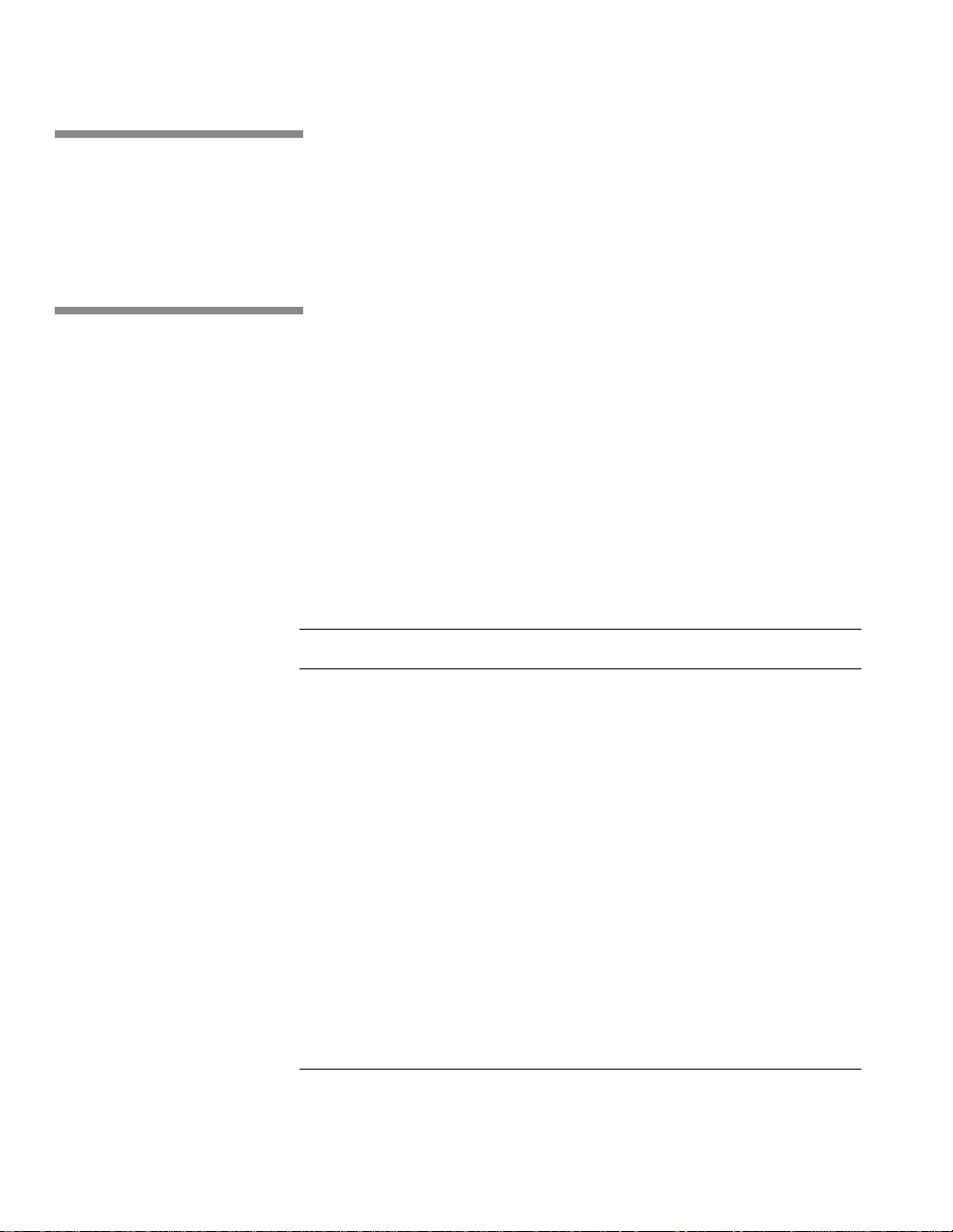

The SPARCbook 3 system architecture is illustrated in Figure 1-2.

System Architecture

TFT

Display

Ext.

Display

RAMDAC

Graphics

Controller

Microcontroller

Subsystem

Module

Modem

Modem

CPU

Base

Board

Ext.

Keyboard/Mouse

Serial

SLAVIO

SPARC CPU

SCSI

SBus

TS102

ASIC

Ethernet

Parallel

MACIO

Audio

ISDN

ISDN/

Audio

32

2x

PCMCIA

Sockets

Figure 1-2 SPARCbook 3 Architecture

1-4

Architecture Overview

Memory

Bus

DRAM (2 x SIMMs)

64

Page 17

Processor

1.4 Processor

The CPU used in the S3TX is the TurboSPARC and the CPU used in the

S3XPand S3GX is the microSPARC II.

The TurboSPARC CPU provides the following key features:

• SPARC compliant V8 Integer Unit core

• SPARC Reference Memory Management Unit

• Floating Point ALU

• FP-Muliply Unit

• FP Divide/Square Root Unit

• 16 Kbyte Instruction Cache

• 16 Kbyte Data Cache

• Secondary Cache Controller

• DRAM Controller

• SBus Controller, Master and Slave Interface.

The TurboSPARC implemented in the S3TX operates at 170 MHz and

provides performance figures of 3.5 SPECint95 and 3.0 SPECfp95.

The microSPARC II CPU provides the following key features:

• SPARC-II compliant V8 Integer Unit (IU) core

• SPARC Reference Memory Management Unit (MMU)

• MEIKO Floating Point Unit (FPU)

• 16 Kbyte Instruction Cache

• 8 Kbyte Data Cache

• Memory Controller

• SBus Controller, Master & Slave Interface.

The microSPARC II implemented in the SPARCbook 3XP processor

operates at 85 MHz and provides performance figures of 64 SPECint92 and

54.6 SPECfp92.

The microSPARC II implemented in the SPARCbook 3GX processor

operates at 105 MHz and provides performance figures of 64 SPECint92

and 54.6 SPECfp92.

Architecture Overview

1-5

Page 18

1.5 Main System Buses

The SPARCbook 3 architecture is based around three main buses

conventional for SPARC-based workstations. These are the Memory bus

which connects the CPU to the main memory; the SBus which connects the

CPU to the major I/O devices; and the EBus.

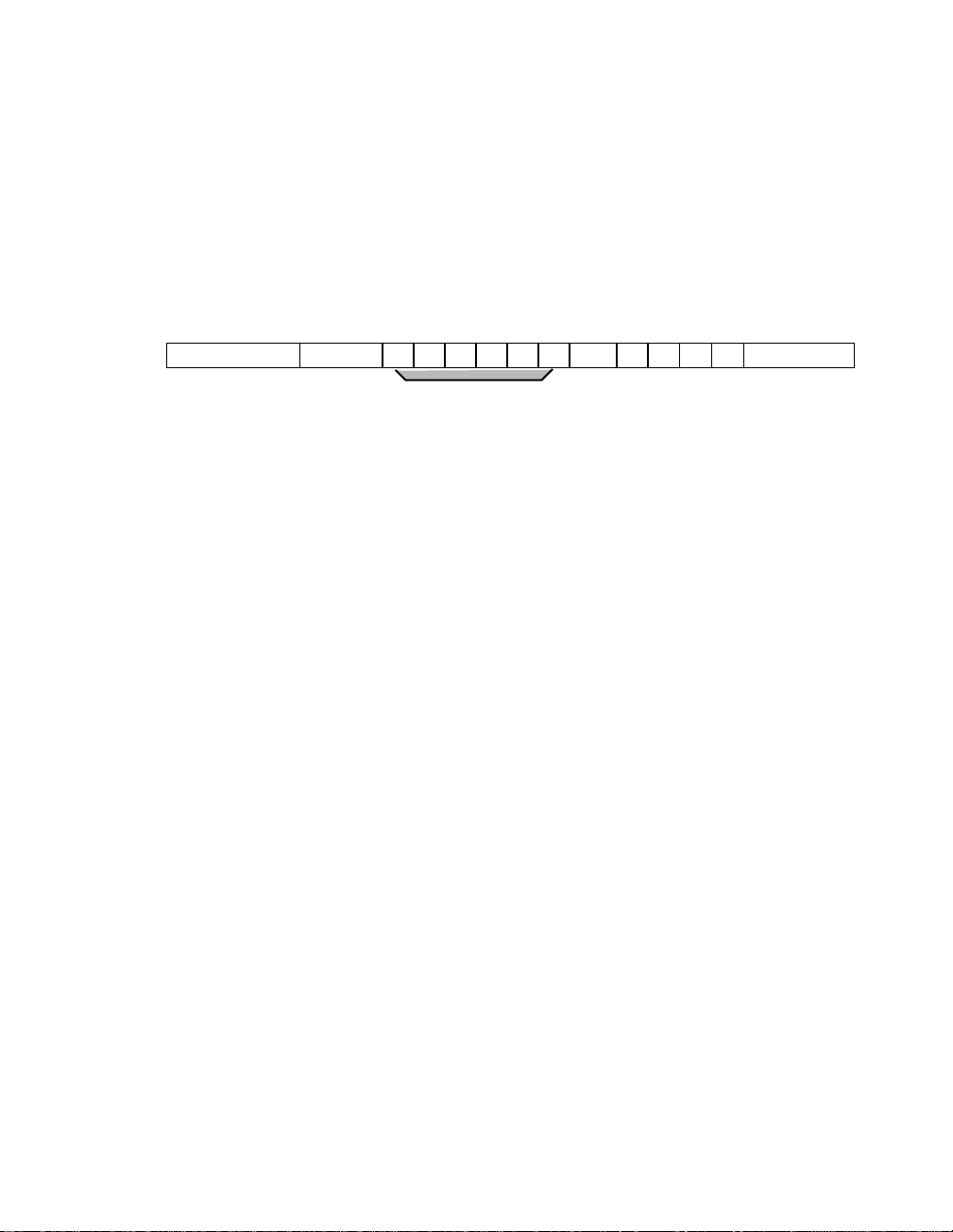

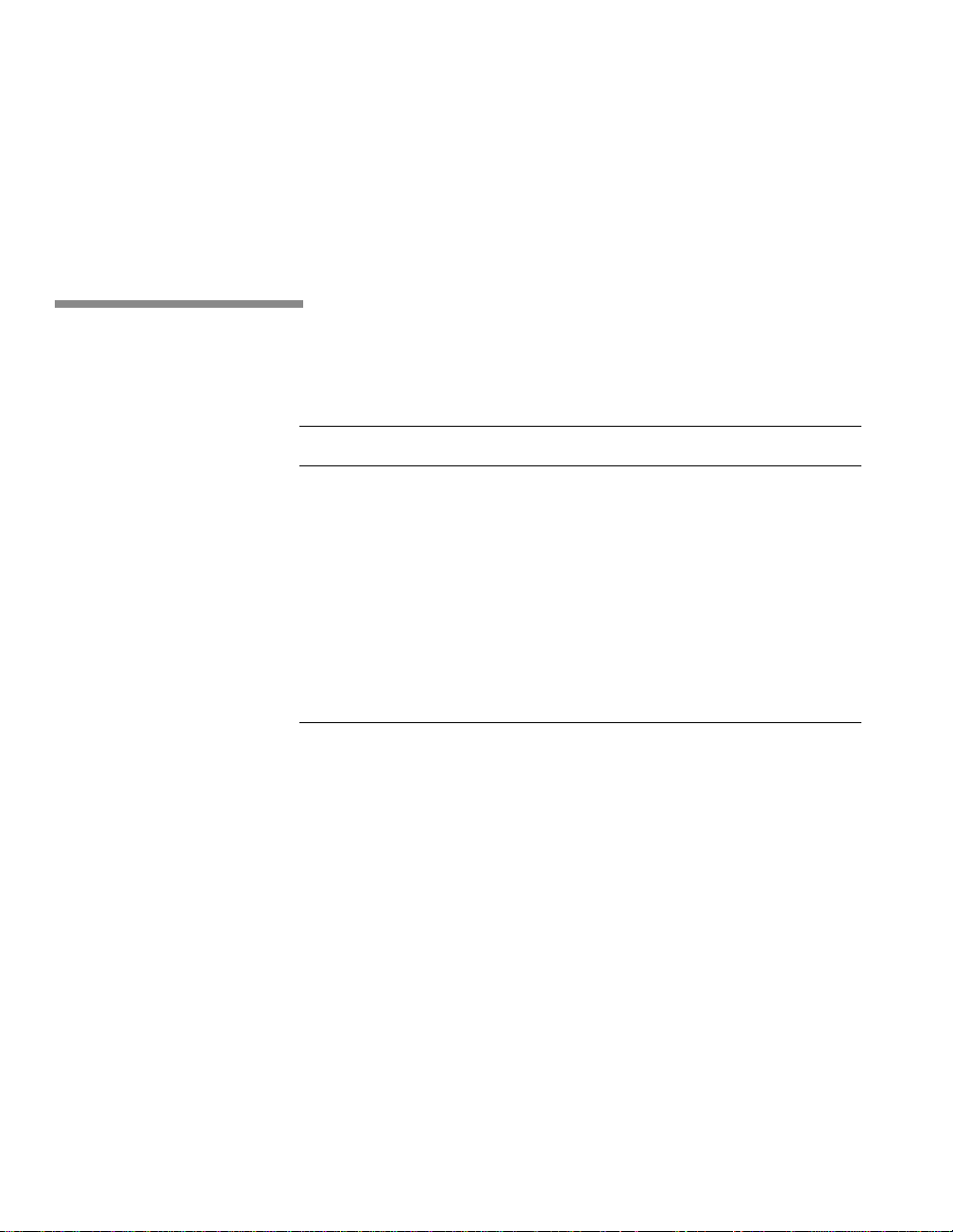

1.5.1 Memory bus

The microSPARC II’s integral memory controller is connected to the

system DRAM directly via a 64 bit high speed memory bus. The

microSPARC II provides direct addressing and control for the main

memory, illustrated in Figure 1-3, providing the write enable signal and

RAS and CAS lines. The smallest data movement is 64 bits; smaller

transfers are carried out by using read-modify-write operations. Parity

protection is provided by the CPU as 1 bit per word (32 bits) of data. SBus

based master I/O devices are able to access the memory bus via the

processor’s SBus interface.

Main System Buses

STSX1012

microSPARC II

Figure 1-3 Main Memory/CPU Interface

1.5.2 SBus

The microSPARC II incorporates a complete SBus controller. The SBus

connects the microSPARC II to the Weitek P9100 graphics controller,

NCR89C105 SLAVIO, NCR89C100 MACIO and T725FC ISDN

controller. See Figure 1-4.

1-6 Architecture Overview

64

12

Data

Address

Control

DRAM

Page 19

Main System Buses

Weitek P9100

Graphics Controller

32 32 32 16

STSX1012

microSPARC II

Figure 1-4 SBus Connected Devices

The microSPARC II provides an SBus Master and Slave interface which

enables the I/O devices with integrated DMA capability to gain access to

the main memory without encroaching unduly on processor bandwidth.

SBus master and slave operations can be single cycle or bursts, and

dynamic bus sizing is supported (for single-cycle transfers). Master

accesses by the microSPARC II to the SBus cannot be cached, and only

double burst accesses are supported.

1.5.3 Ebus

NCR89C105

SLAVIO

NCR89C100

MACIO

TS102

PCMCIA Controller

Data

Address

T725FC

ISDN Controller

32

The third system bus within the SPARCbook 3 is the Ebus. This is an 8-bit

data bus driven by the SLAVIO. The SLAVIO divides the EBus address

space into a number of regions by providing address generated EPROM,

RTC/RAM and Generic chip select signals. The EBus interface of the

SLAVIO is limited to a data bus and the chip select signals. The EBus

address bus is driven by the TS102 ASIC to enable the CPU to gain access

to the internal registers of devices on the EBus. Figure 1-5 provides a

simplified illustration of the EBus architecture.

Architecture Overview 1-7

Page 20

Chip Selects

DRAM

NCR89C105

SLAVIO

Figure 1-5 EBus Architecture

1.6 DRAM

Data

MK48T08

TRC/RAM

Address

Boot

EPROM

Modem

8

19

TS102

MBus

Address

The SPARCbook 3 provides two SIMM sites which support a range of

different capacity modules. The SIMM sites accommodate 72-pin units,

which must be fitted in matched pairs to provide a full width 64-bit data

interface for the microSPARC II.

The SIMMs are each 33-bits wide (32 bits data and 1 bit parity), and are

available in sizes of 8Mbytes x 33, 16Mbytes x 33, 32Mbytes x 33, and

64Mbytesx33. This gives a usable memory capacity of up to of 128. The

fast processor clock speed used in SPARCbook 3 series computers requires

the use of 60ns SIMMS.

1-8 Architecture Overview

Page 21

Slow I/O Subsystem

1.7 Slow I/O Subsystem

The Slow I/O subsystem is managed by an NCR89C105 SLAVIO. The

SLAVIO is an application specific integrated circuit (ASIC), designed as

part of a two-chip set with the NCR89C100 MACIO, which provides two

serial channels, keyboard and mouse ports, an interrupt controller and two

counter-timers. The key features of the SLAVIO include:

• Two synchronous/asynchronous serial ports (85C30 SCC compatible)

• Keyboard/mouse ports (85C30 SCC sub-set)

• Two programmable counter-timers (500ns period)

• Interrupt controller

• 8-bit expansion bus (EBus) interface/controller for EPROM and 8-bit

I/O devices

• Internal 82077 style floppy disk controller

• Miscellaneous I/O functions.

1.7.1 Serial Channels

The two serial ports are used to provide general purpose synchronous or

asynchronous RS232 interfaces. The SCC channels A and B are connected

to two 8-way mini-DIN connectors, which are marked as Serial Channel A

and Serial Channel B on the I/O panel at the rear of the SPARCbook 3

system unit.

1.7.2 Counter-Timers

The two remaining serial channels provide the keyboard and mouse

interfaces. These use transmit and receive data only. The TTL-level output

signals connect directly to the combined Keyboard/Mouse mini-DIN

connector on the I/O panel at the rear of the SPARCbook 3 unit.

For more information about these channels, refer to Chapter 4, “Serial

Interface”. For information about the connections of these channels, refer

to Appendix B, “Connector Information”.

The SLAVIO contains two counter timers. These are the System Counter

and the Processor Counter/User Timer which are clocked at 2MHz and can

provide counter-timer functions or periodic interrupts. The System Counter

is 22 bits wide, and increments every 500ns.

The Processor Counter/User Timer can be used in either the same mode as

the System Counter, or as a free running 54-bit timer. OpenBoot uses the

Processor Counter as a system watchdog timer.

Architecture Overview 1-9

Page 22

1.7.3 Interrupt Controller

The interrupt controller co-ordinates all on-board interrupt functions. These

include all internal sources and a number of signals from elsewhere within

the system. The microSPARC II uses a 4-bit priority encoded interrupt

mechanism. The SLAVIO provides control and priority encoding for all of

the system interrupt sources. For more information about the SPARCbook

3 interrupts system, see Section 3.2, “Interrupts”, on page 3-5.

1.7.4 EBus Interface and Controller

The SLAVIO provides an 8-bit bus called the EBus for a number of slower

auxiliary devices. The EBus interface of the SLAVIO supports the Boot

ROM; the real time clock and SRAM; and the system clock control port.

This is illustrated in Figure 1-5.

1.8 Fast I/O Subsystem

The Fast I/O Subsystem includes the SCSI, parallel and network interfaces.

These are controlled by the NCR89C105 MACIO. This device is a custom

ASIC designed to be operated with the NCR89C100 SLAVIO as a

two-chip set. The key features of the MACIO include:

Fast I/O Subsystem

1.8.1 SCSI Controller

1-10 Architecture Overview

• 53C90 style SCSI controller (Emulex FAS100A compatible)

• 7990 style Ethernet controller

• Parallel port interface

• Dual 64 byte FIFOs

• IEEE-1496 SBus DMA controller

This section describes each of these features.

The SCSI controller provides a 10Mbyte/sec 8-bit interface able to support

up to eight SCSI devices. The SPARCbook 3 counts as one device, and the

hard disk counts as a second, making it possible to add six external devices.

The SPARCbook 3 is fitted with a 50-pin high density SCSI-2 connector.

For more information, refer to Chapter 5, “SCSI Controller”. For

information about the connections, refer to Appendix B, “Connector

Information”.

Page 23

Fast I/O Subsystem

1.8.2 Ethernet Controller

The Ethernet controller provides a 10Mbit/sec networking interface. The

design features an AT&T serial interface encoder to provide the standard

AUI interface through a 26-way high density connector. An AUI cable and

an Ethernet transceiver can be used to provide access to other physical

Ethernet media, including Thick, Thin and Fiber-optic networks.

Note

The AUI interface is DC coupled, and any attachment units used with SPARCbook 3

must feature the network isolation function.

Ethernet data transfers are supported with the MACIO DMA function.

For more information, refer to Chapter 6, “Ethernet Interface”. For

information about the connections, refer to Appendix B, “Connector

Information”.

1.8.3 Parallel Port

The parallel port breakout cable supplied with the SPARCbook enables

connection to a bi-directional Centronics style interface on a standard

25-way D-Type connector. Parallel port data transfers are supported with

the MACIO DMA function.

For more information, refer to Chapter 10, “Parallel Interface”. For

information about the connections, refer to to Appendix B, “Connector

Information”.

1.8.4 FIFOs and DMA Controller

The FIFO and DMAC arrangement provided by the MACIO supports the

SCSI, Ethernet and parallel interfaces. The DMAC performs burst transfers

on the SBus whenever possible, supported by the FIFO circuitry, to

minimize the I/O bandwidth consumed by simultaneous operation of these

interfaces.

Architecture Overview 1-11

Page 24

1.9 Graphics and Video Subsystem

The Graphics and Video Subsystem comprises the Weitek P9100 User

Interface Controller, an IBM RGB528 palette DAC (RAMDAC), and a

framebuffer provided by a 2MByte array of video RAM (VRAM) devices.

All display interface configuration is carried out in software. There are no

link adjustments.

The display interface supports the following display resolutions:

• 640 x 480 at 8, 16 or 24 bits per pixel

• 1024 x 768 at 8 or 16 bits per pixel

• 1152 x 900 at 8 bits per pixel

• 1280 x 1024 at 8 bits per pixel

1.9.1 Graphics Controller

The P9100 User Interface Controller provides the graphics control

function. This device provides a 32-bit host interface and the following

features:

• 32-bit VRAM interface and control signals

• RAMDAC interface and control signals

• Video timing control (up to 165MHz)

• 2D Graphics Accelerator

• Supports X window drawing mode

• Powerful graphics primitives

Graphics and Video Subsystem

The Weitek Power 9100 User Interface Controller provides programmable

display resolutions, supporting displays from 640 x 480 up to 1280 x 1024

pixels.

1.9.2 VRAM

The SPARCbook 3 has a 2Mbyte framebuffer comprising eight 256K x 8

devices. The VRAM is dual ported to provide a random access port for

P9100 and a serial read-only port for the RAMDAC. The random access

port is used by the P9100 and host to read and write picture information.

The serial port is used to output pixel information to the RAMDAC. The

RAMDAC provides timing signals for the serial data port of the

framebuffer.

1.9.3 RAMDAC, Panel Driver and Video Clock Generator

The RGB528 combines a video clock generator, RAMDAC and flat panel

control circuitry. The primary mode of operation supports the internal TFT

panel and provides a display of 800 x 600 pixels (640x480 on some models)

1-12 Architecture Overview

Page 25

MK48T08 RTCRAM

in 256 colors from a palette of 262144. The RAMDAC can be software

configured to support display resolutions of up to 1280 x 1024 in 256 colors

(from a choice of 16M) on external monitors. 16 bit and 24 bit true color

imaging modes are also supported on some configurations. The RAMDAC

also provides numerous power-down features.

1.10 MK48T08 RTCRAM

The MK48T18 provides time-keeping facilities and incorporates 8 Kbytes

of battery-backed non-volatile RAM. The device appears to software as an

ordinary 8K x 8 RAM array. However, the uppermost 8 bytes provides an

accurately updated real-time clock. The battery-backed RAM is used to

store system configuration information, such as manufacturing data and

Ethernet ID, via Tadpole’s implementation of the OpenBoot firmware. The

real time clock provides second, minute, hour, day, date, month and year

information and a calibration register which allows adjustment of the RTC

function in 2ppm steps. The device is accessed via the EBus port of the

SLAVIO device.

1.11 ISDN and 16-Bit Audio Controller

The ISDN and Audio interface consists of two major components: the

AT&T T7259 Dual Basic Rate ISDN Controller; and the Crystal

Semiconductor Corporation CS4215 Multimedia Audio CODEC.

The T7259 has the following major features:

• Simultaneous terminal endpoint (TE) and network termination (NT)

• CCITT I.430/ANSI T1.605 support for 4 wire ISDN 2B+D basic

access at the S/T reference point

• Multiframing support: S&Q channel operation

• Automatic synchronization of ISDN interfaces

• On-chip HDLC formatter

• On-chip 16-channel DMA address generator and linked list buffer

manager

• Supports AT&T Concentration Highway Interface (CHI)

• Sbus master and slave interface

The ISDN controller combines a DMAC and data format converter

(Parallel/Serial, Serial/Parallel and Time-Division-Multiplex). It has a

number of DMA channels that can be allocated to support the ISDN or

audio functions. The DMACs provide linked-list command support, and

Architecture Overview 1-13

Page 26

PCMCIA Controller

FIFOs allow burst data transfers to be performed on the Sbus. Large

amounts of ISDN or audio information can be moved to and from the Sbus

with a minimum of processor overhead. The data is formatted by the ISDN

controller into a composite digital serial stream (the Concentration

Highway Interface). This connects to additional on-chip ISDN support

circuitry, and to the external audio CODEC. The ISDN interface is

implemented as a 2B+D Terminal Endpoint.

The Concentration Highway Interface of the ISDN circuitry provides a

variety of different serial digital framing standards and data rates to the

Audio CODEC. This supports a majority of the world standard Digital

Audio formats. Typical configurations include high-quality stereo 16-bit

44.1KHz (CD), and telephony quality mono 8-bit 8KHz (ISDN).

The CS4215 Audio CODEC has the following major features:

• Stereo analog-to-digital and digital-to-analog conversion

• 4KHz to 48KHz sample rates

• 16-bit linear and 8-bit u-law or A-law coding

• Serial digital interface, compatible with AT&T CHI Concentration

Highway Interface

• Microphone and line analog outputs

1.12 PCMCIA Controller

The PCMCIA controller is the Tadpole TS102. This device provides an

interface between the SBus and the PCMCIA bus. It performs the

additional function of providing a serial link between the CPU and

microcontroller. The TS102 supports two PCMCIA Type I, II, and III cards

or devices at a time. However, due to space constraints, the SPARCbook 3

unit is able to support one or two Type I and II cards, but only one Type III

device.

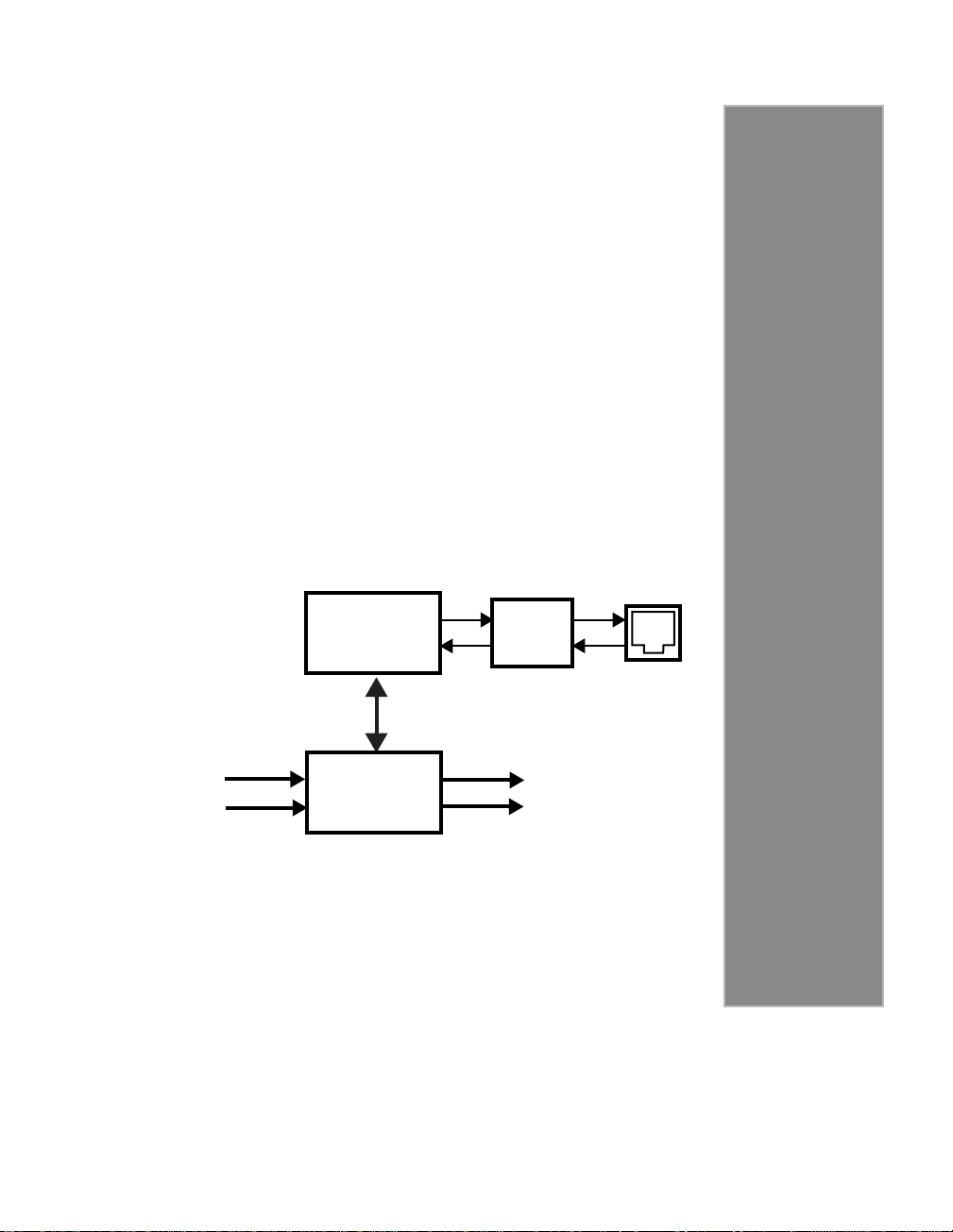

1.13 Modem Interface

The modem interface consists of a microcontroller, a DSP device and a

DAA. The microcontroller is the high-level controlling element and

interfaces to the system bus. The DSP device performs all of the high speed

data manipulation and data conversion. The DAA provides the line

interconnect to the telephone network.

1-14 Architecture Overview

Page 27

Microcontroller Subsystem

The modem supports a number of high level functions. It implements

DTMF dialing, call progression, and is controlled via an enhanced “AT”

command set. The data standards supported include V.22 bis, V.23, V.32,

V.32 bis, V.42, and V.42 bis. In addition, the modem provides send and

receive Fax capabilities to Group 3 standards (at up to 14,400bps).

1.14 Microcontroller Subsystem

The microcontroller subsystem provides system housekeeping support,

freeing the main CPU. A Hitachi H8/337 microcontroller is used, offering

the following features:

The microcontroller subsystem performs the following functions:

• Internal keyboard and pointing device control

• External keyboard and mouse control

• Serial communication channels to SLAVIO keyboard and mouse ports

• PSU and battery energy management

• System non-volatile storage (RTC and serial EEPROM)

• Environmental parameter control (display brightness and audio

volume)

• LCD status display (2 x 16 character) control

• System reset control

• Power management control

Architecture Overview 1-15

Page 28

Microcontroller Subsystem

1-16 Architecture Overview

Page 29

The SPARC CPU 2

Processing power for all SPARCbook 3 models is

provided by SPARC processors. In the case of he

S3XP and S3GX microSPARC II is used; in the

case of the S3TX TurboSPARC is used.

This chapter provides a general overview of

SPARC CPU. For further information, please refer

to Appendix A, “Further Information”.

22

Page 30

2.1 SPARC Architecture Overview

The SPARC processor is a highly integrated device which provides the

following features:

• SPARC compliant V8 Integer Unit core

• SPARC Reference Memory Management Unit

• MEIKO Floating Point Unit

• 16 Kbyte Instruction Cache

• 8 or 16 Kbyte Data Cache

• Memory Controller

• SBus Controller, Master and Slave Interface

inst[31:0]

Integer

Unit

Instr

dpc[31:2]

fp_dout_e[63:0]

iu_dout[63:0]

Floating Point

Unit

SPARC Architecture Overview

d_va[31:0]

i_va{31:0]

Instruction

Cache

64 bit Cache Fill Bus

Memory

Interface

memdata<63:0>

Main Memory

Figure 2-1 MicroSPARC-II Architecture

2-2 The SPARC CPU

Data

Cache

Write Buffer

4 Entry

SBC

32 bit SBus

MMU

64 entry

Phy_addr[27:0]

Misc_Bus[31:0]

Page 31

Integer Unit

2.2 Integer Unit

2.2.1 Pipeline

The SPARC CPU is a RISC (reduced instruction set computer) based

processor which uses a simplified command set to carry out operations. It

is able to execute most instructions within a single clock cycle.

The high performance of the SPARC CPU is enhanced by the ability of the

floating point unit (FPU) to execute instructions simultaneously with the

integer unit (IU), and by the provision of cache memory. The cache

memory is a specialized area of fast (zero wait state) memory which allows

many instructions and operands to be fetched locally by the CPU without it

having to access the (comparatively slow) main memory.

The IU is the main processing engine, executing all instruction groups

except for floating point operations.

The SPA IU has a five-stage pipeline, receiving instructions which

complete five cycles later. The five stages are fetch, decode, execute, cache

access and write back. These stages are overlapped to allow a peak

execution rate of one instruction per cycle.

The one instruction per cycle performance is supported by the IU’s 32-bit

data bus which interfaces directly with the instruction cache. If an

instruction is in the cache, it is returned in the same cycle in which it was

requested.

2.2.2 Instruction set overview

The integer instructions supported by the micro SPARC processor fall into

the following basic categories:

• Load and Store Instructions

• Arithmetic, Logical and Shift Instructions

• Control Transfer Instructions

• Read/Write Control Registers Instructions.

The load and store instructions are the only instructions that cause the

movement of data on the memory interface. They use two registers or a

register and a constant to calculate the memory address involved. Halfword

accesses must be aligned on 2-byte boundaries, word accesses on 4-byte

boundaries, and doubleword accesses on 8-byte boundaries. These

alignment restrictions greatly speed up memory access.

The SPARC CPU 2-3

Page 32

Integer Unit

The arithmetic, logical and shift instructions compute a result that is a

function of one or two source operands and then place the result

non-destructively in a register.

The control transfer instruction category includes jumps, calls, traps, and

branches. Control transfers are usually delayed until after execution of the

next instructions so that the pipeline is not emptied every time a control

transfer occurs, allowing compilers to optimize for delayed branching.

The read/write control register instructions include instructions to read and

write the contents of various control registers. Generally, the source or

destination is implied by the instruction.

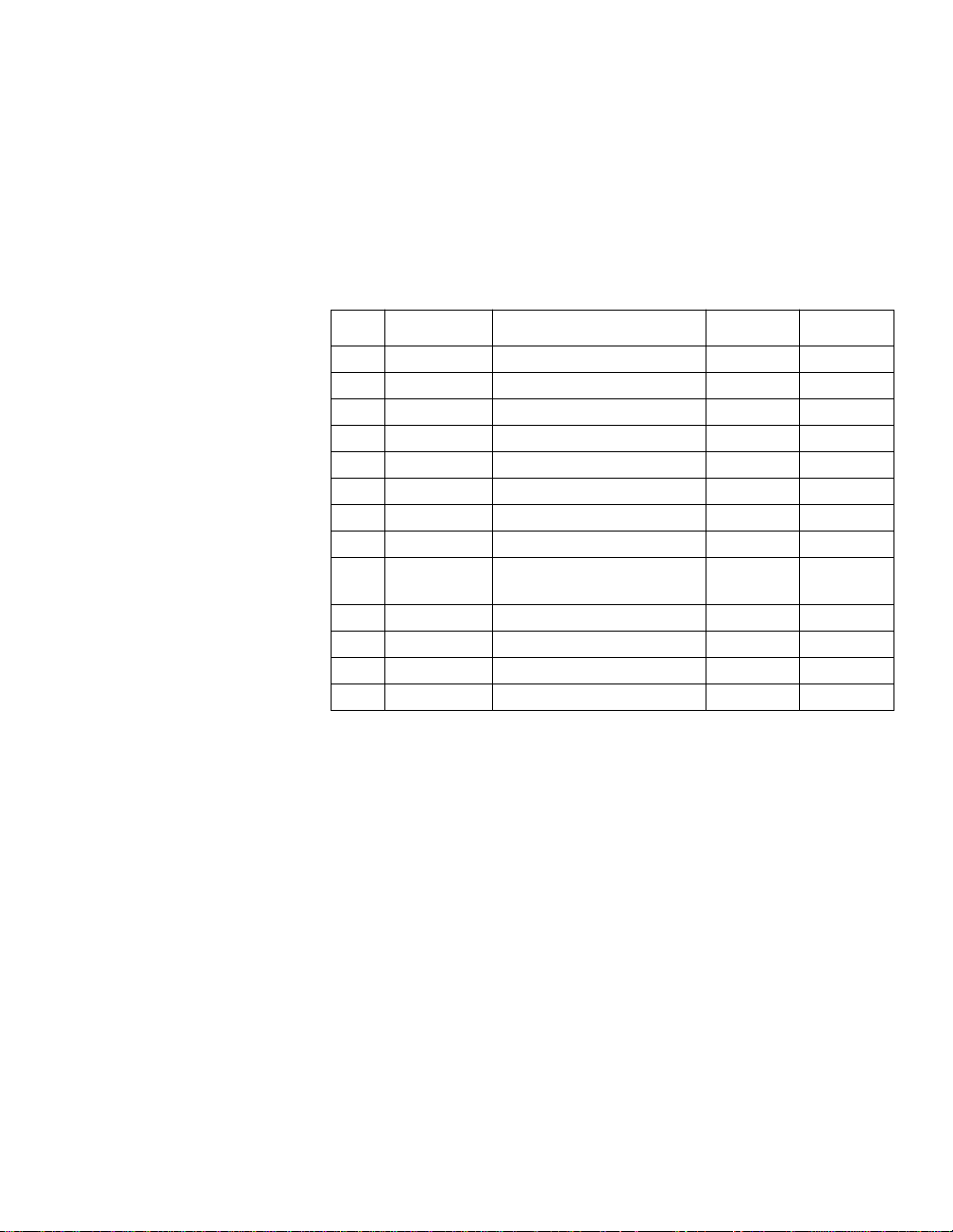

INSTRUCTION CYCLES

Call 1

Single Loads 1

Jump/Return 2

Double Loads 2

Single Stores 1

Double Stores 2

Taken Trap 3

Atomic Load/Store 2

SWAP 2

Integer Multiply 19

Integer Divide 39

All Others 1

2.2.3 Traps and interrupts

The SPARC design supports a full set of traps and interrupts. They are

handled by a table that supports 128 hardware and 128 software traps. Even

though floating-point instructions can execute concurrently with integer

instructions, floating-point traps are precise because the FPU supplies

(from the table) the address of the instruction that failed.

2-4 The SPARC CPU

Table 2-1 IU Cycles per Instruction

Page 33

Integer Unit

The IU supports both asynchronous traps (interrupts) and synchronous

traps (error conditions and trap instructions). Traps transfer control to an

offset within the trap table. The base address of the table is specified by the

Trap Base Register and the offset is a function of the trap type. Traps are

taken before the current instruction causes any changes visible to the

programmer and can therefore be considered to occur between instructions.

Interrupts from the peripheral devices in SPARCbook 3 are controlled and

prioritized by the SLAVIO.

2.2.4 Memory protection

The SPARC design provides memory protection, essential for smooth

multi-tasking operation. Memory protection prevents user programs from

corrupting the system, other user programs, or themselves.

The IU supports a multi-tasking operating system by providing user and

supervisor modes. Some instructions are privileged and can only be

executed while the processor is in supervisor mode. Changing from user to

supervisor mode requires taking a hardware interrupt or executing a trap

instruction. This instruction execution protection ensures that user

programs cannot accidentally alter the state of the machine with respect to

its peripherals.

2.2.5 IU internal registers

The IU contains working registers (or r registers) and control registers. The

r registers are used for storage by processes, and the control registers are

used to track and control the state of the IU. The r registers are within a

large register file containing one hundred and twenty 32-bit registers. Eight

of these are global registers and are always accessible to a program, while

the remaining registers are accessed through register windows. The way in

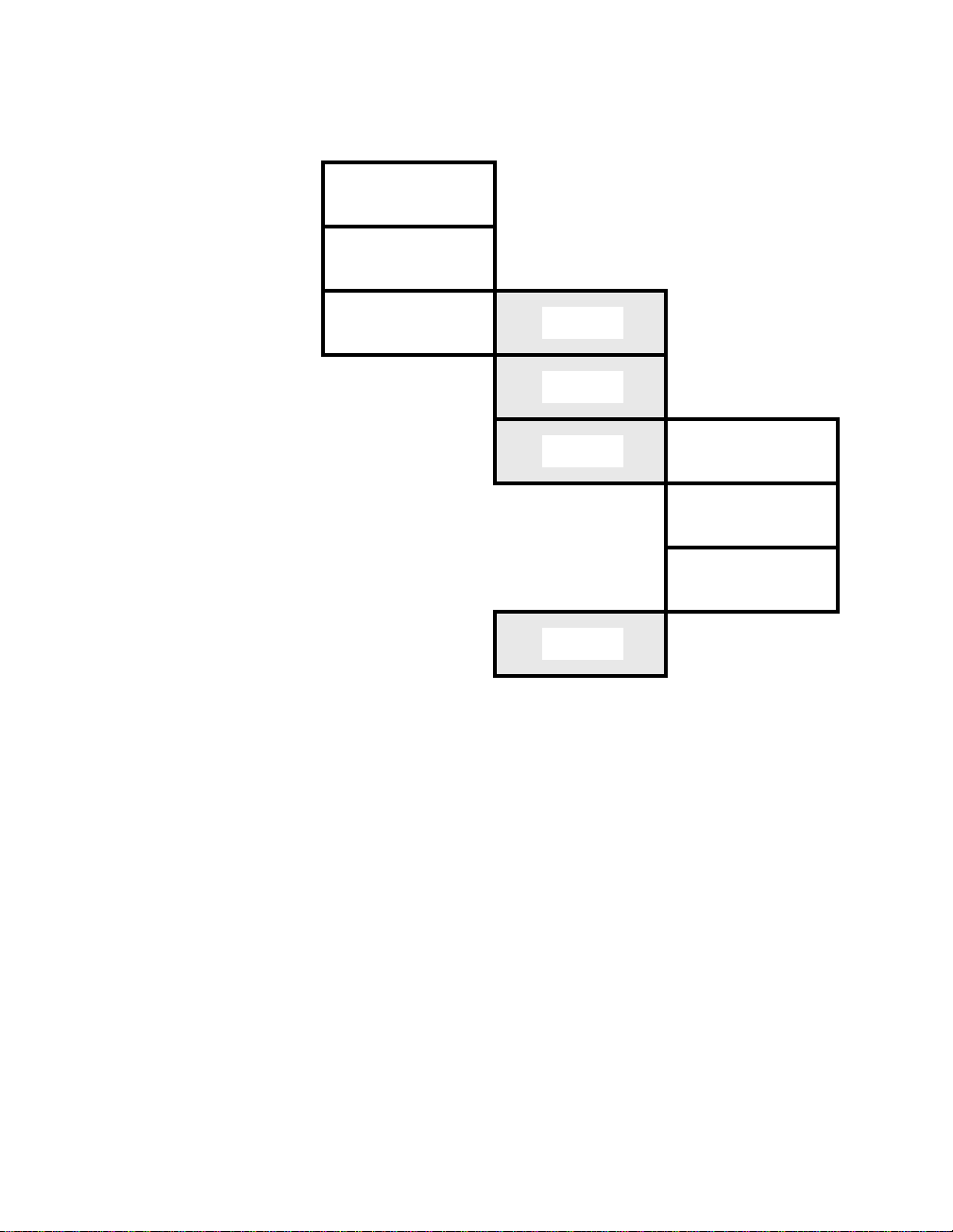

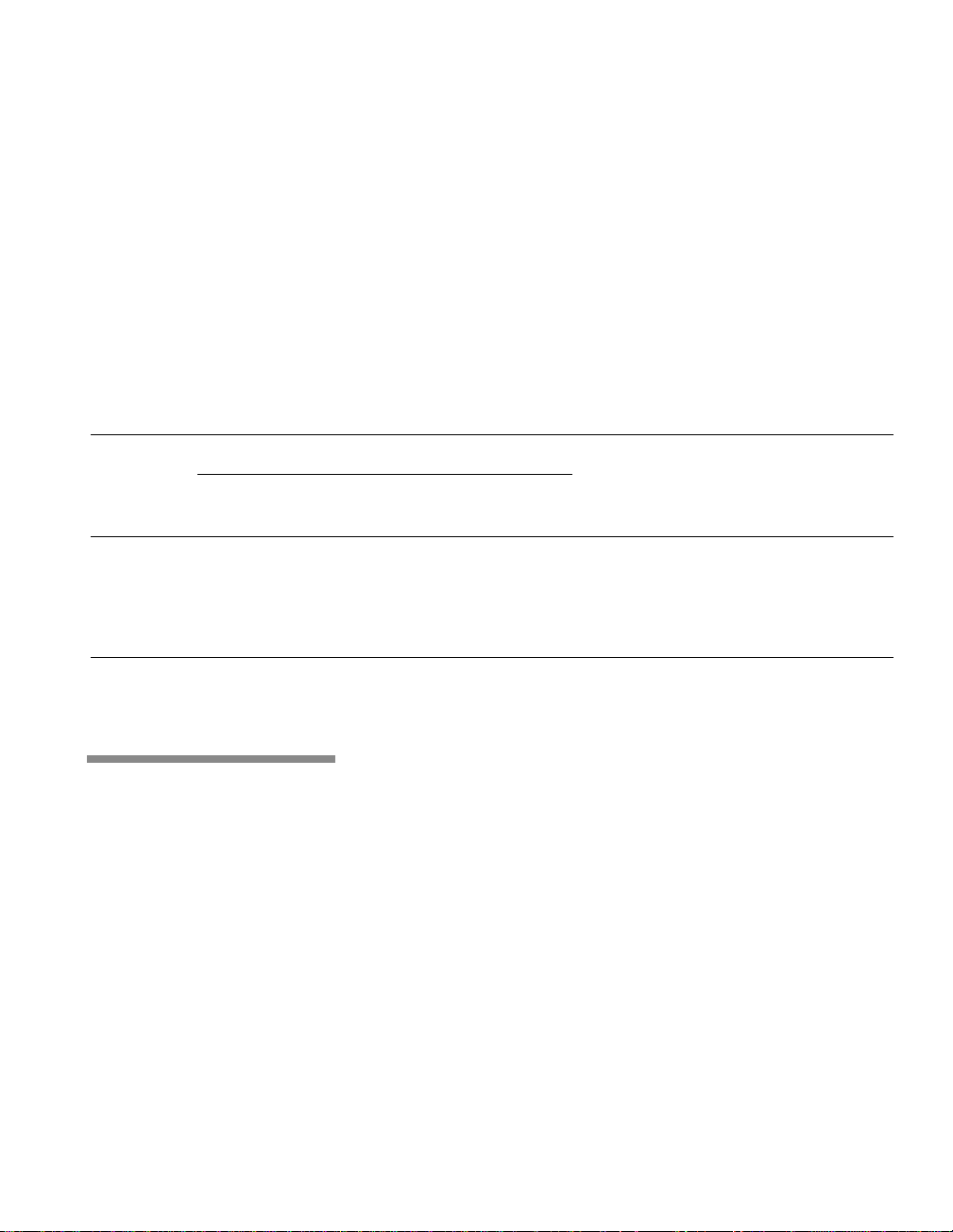

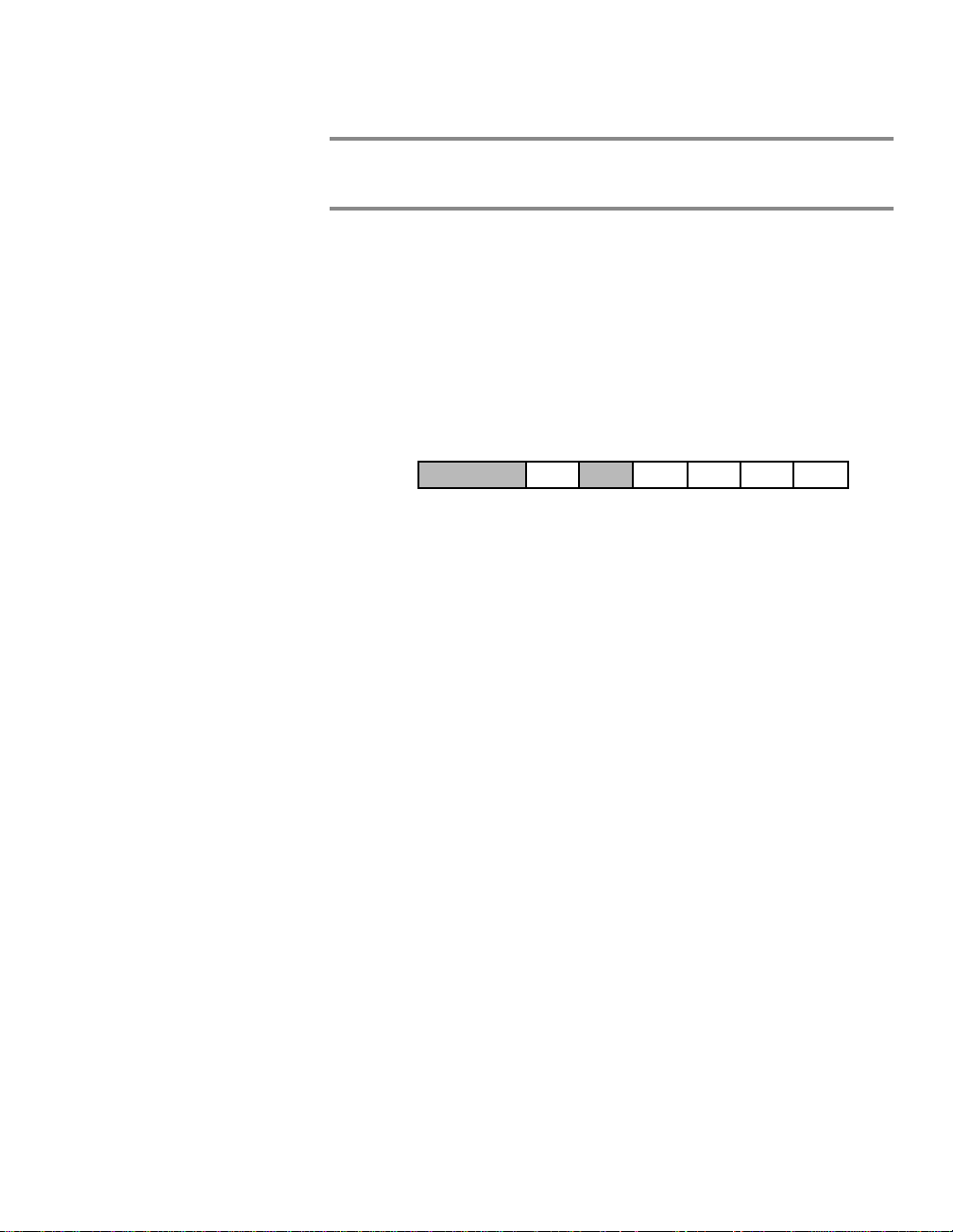

which register windows are organized is shown in Figure 2-2.

The register file contains seven register windows, and each window

contains twenty-four working registers. Each register window is divided

into three sections called ins, outs, and locals, with eight registers in each

section. Windows share ins and outs with adjacent windows. The outs of

the previous window are the ins of the current window, and the outs of the

current window are the ins of the next window. The windows form a

circular stack where the outs of the last window are the ins of the first

window.

A current window pointer (CWP) in the processor state register keeps track

of the currently active window. The CWP is decremented when a program

calls a subroutine that causes the processor to make accesses to the next

The SPARC CPU 2-5

Page 34

r31

:

r24

r23

:

r16

r15

:

r8

INS

LOCALS

OUTS

r31

:

r24

r23

r

:

r16

r15

:

r8

r7

:r0GLOBALS

INS

LOCALS

OUTS

r31

:

r24

r23

:

r16

r15

:

r8

Integer Unit

INS

LOCALS

OUTS

Figure 2-2 Window Register Organization

window, and is incremented when the processor returns to the previous

window. Register windows can be marked as invalid in the WIM register,

and interrupts can be enabled to signal when movement into an invalid

window is caused by an instruction.

2.2.6 IU control registers

These include the Processor Status Register, the Window Invalid Mask

Register, the Trap Base Register, the Y Register, and the Program Counter.

2-6 The SPARC CPU

Page 35

Floating Point Unit

2.3 Floating Point Unit

The SPARC FPU is designed to execute all single- and double-precision

SPARC Version 8 floating point instructions except fsmuld. All other FP

instructions cause an unimplemented floating point operation trap. The

FPU contains a 32x32-bit register file.

INSTRUCTION MIN TYP MAX

fads 4 4 17

faddd 4 4 17

fsubs 4 4 17

fsubd 4 4 17

fmuls 5 5 25

fmuld 7 9 32

fdivs 6 20 38

fdivd 6 35 56

fsqrts 6 37 51

fsqrtd 6 65 80

fnegs 2 2 2

fmovs 2 2 2

fabss 2 2 2

fstod 2 2 14

fdtos 3 3 16

fitos 5 6 13

fitod 4 6 13

fstoi 6 6 13

fdtoi 7 7 14

fcmps 4 4 15

fcmpd 4 4 15

fcomes 4 4 15

fcmped 4 4 15

unimplemented 3 3 3

Table 2-2 FPU Execution Timing

The SPARC CPU 2-7

Page 36

2.3.1 Floating Point Registers

The FPU contains thirty-two 32-bit floating-point f registers, as illustrated

in Figure 3-8. These form a 32x32-bit register file. The contents of these

registers are transferred to and from external memory under control of the

IU using floating-point load/store instructions. Addresses and control

signals for data accesses during a floating-point load or store are supplied

by the IU, while the FPU supplies or receives the data.

f31

f30

•

•

•

•

•

•

•

f01

f00

Cache Controller and Memory Management Unit

Figure 2-3 f Registers

Although the FPU operates concurrently with the IU, a program containing

floating-point computations generates results as if the instructions were

being executed sequentially.

A single f register is able to store one single-precision operand. Two

registers are required to hold a double precision operand.

2.4 Cache Controller and Memory Management Unit

The SPARC’s integral Memory Management Unit (MMU) provides virtual

to physical address translation, memory protection and arbitration between

I/O, data cache and TLB references to physical memory.

2-8 The SPARC CPU

Page 37

Cache Controller and Memory Management Unit

2.4.1 Translation lookaside buffer

The Memory Management Unit (MMU) conforms to the standard SPARC

architecture definition for memory management.

The MMU provides virtual to physical address translation using a

translation lookaside buffer (TLB). An entry in the TLB has the fields

shown in Figure 2-4.

Virtual Address Tag Context Tag Level S IO PTP Page Table FieldMUW SR SWUR SEUE

Prot

Figure 2-4 TLB Entry

TLB Entry Fields Virtual Address Tag

represents the most significant 20 bits, VA(31:12), of the

virtual address.

Context Tag

is compared with the 6-bit context number in the context

register written by memory management software.

Prot Six protection bits in each TLB entry represent the decoded

ACC bits from the matching PTE. These are: User Rd, Wr,

Ex, and Supervisor Rd, Wr, Ex.

Level This 3-bit field is used to allow the proper tag match of

region and segment PTEs. I/O PTEs and PTPs 1 will have

this field set to use index 1, 2, and 3. The most significant bit

also serves as the TLB Valid Bit because it is set for any

valid PTE, I/OPTE or PTP.

000 = none

100 = Index 1 –VA(31:24)

110 = Index 1,2 – VA(31:18)

111 = index 1,2,3 – VA(31:12)

S Supervisor – This bit disables matching of the context field

of a page in supervisor level.

M This is set to 1 if page is written.

I/O PTE This bit, when ‘0’, indicates that an I/O PTE is contained in

this entry.

The SPARC CPU 2-9

Page 38

Cache Controller and Memory Management Unit

PTP This bit, when set, indicates that a page table pointer is

contained in this entry

Page Table Field

This field can contain a PTE, PTP or I/O PTE. It can be read

and written using ASI 0x06 (25 bits).

Page Table Entry The PTE defines the physical address of a page and its access permission.

It contains the following information:

Bits 31:27 Reserved - always write 0.

Bits 26:8 PPN – Physical Page Number, which provides the upper 19

bits (30:12) of the 31-bit physical address of the page.

Bit 7 Cacheable. This bit when set indicates that a page is

cacheable.

Bit 6 Modified. This bit is set when the page is written to.

Bit 5 Always 1 for a PTE in the TLB. For a PTE in physical

memory, this bit is set when the page is accessed.

Bits 4:2 ACC – Access Permissions. This field indicates whether

access is permitted for the transaction being attempted. The

Address Space Identifier (ASI) determines whether the an

access is an instruction or data access, and whether it is a

user or supervisor access.

2-10 The SPARC CPU

ACC User Supervisor

000 Read Only Read Only

001 Read/Write Read/Write

010 Read/Execute Read/Execute

011 Read/Write/Execute Read/Write/Execute

100 Execute Only Execute Only

101 Read Only Execute Only

110 No Access Read/Execute

111 No Access Read/Write/Execute

Table 2-3 Page Table Access Permissions

Bits 1:0 ET – These are set to 10 indicate an entry type of PTE.

00 = Invalid

01 = Page Table Pointer

10 = Page Table Entry

11 = Reserved in Page Tables

Page 39

Cache Controller and Memory Management Unit

Page Table Pointer The PTP contains the physical address of a page table in memory, and can

be found in the context table, or in a level 1 or 2 page table. Page tables are

loaded into the TLB during tablewalks, and are removed by tablewalks or

flushing.

Bits 31:27 Reserved – always write 0

Bits 26:4 PTP – Physical address of the next page table.

Bits 3:2 Reserved – always 00.

Bits 1:0 ET – Entry type, contains 01 to denote a PTP.

I/O Page Table Entry The I/O PTE defines the physical address of a page and its access

permission.

Bits 31:27 Reserved – always write 0

Bits 26:8 PPN – Physical Page Number, which provides the upper 19

bits (30:12) of the 31-bit physical address of the page.

Bits 7:3 Reserved – always contains 0000

Bit 2 Writeable

0 = read only

1 = read/write

Bit 1 This bit is set to 1 when the I/OPTE is valid

Bit 0 This bit is to be written as zero (WAZ) in the Memory I/O

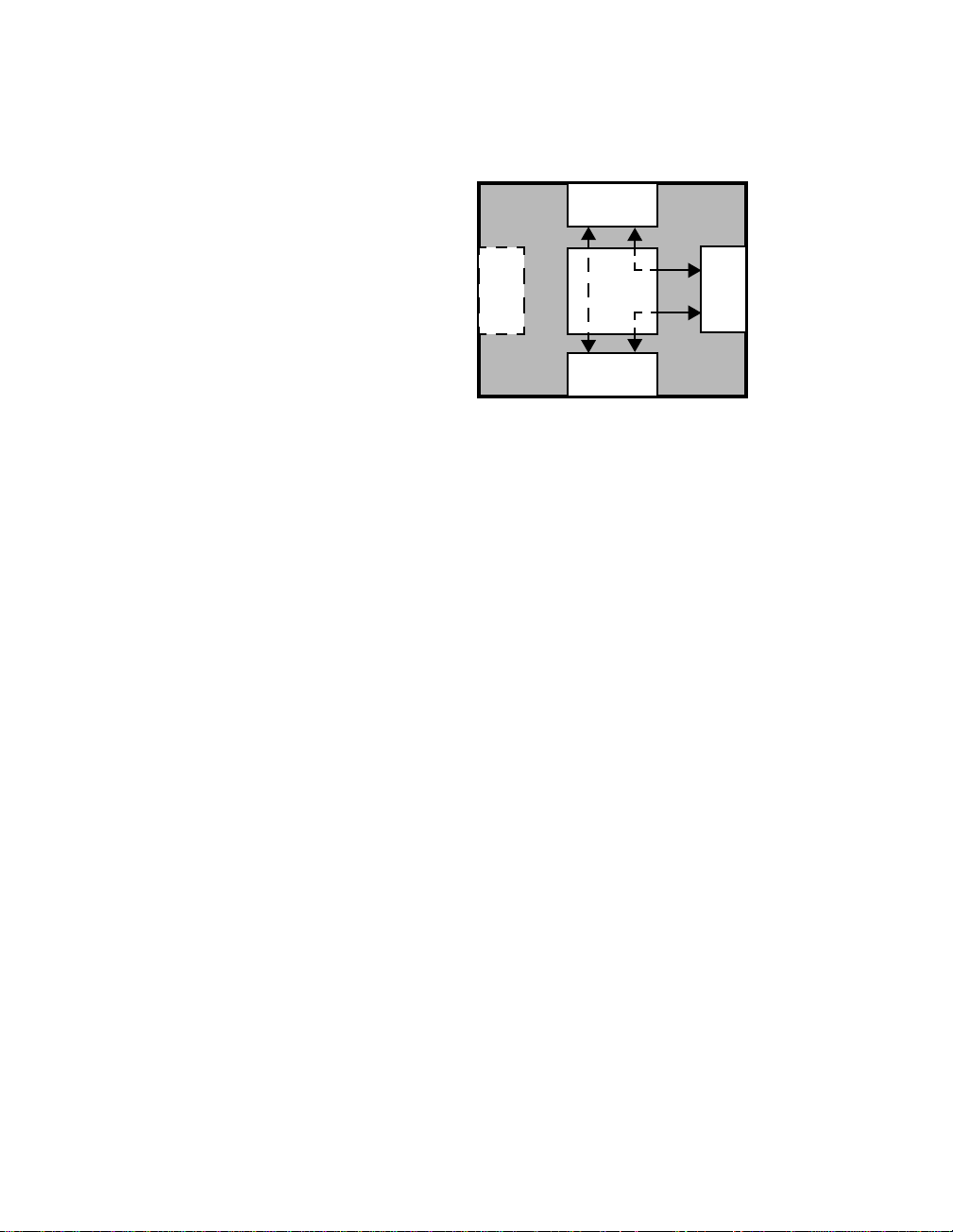

2.4.2 Address translation

During an access by the IU, the virtual address supplied by the IU and the

contents of the context register are compared with the virtual section of all

TLB entries. When a match is found (or a “hit” occurs), the Physical section

supplies the address of a page in memory, or a pointer to a page table in

physical memory. Virtual address bits A(11:00) from the IU are passed

through unchanged to supply a byte offset. Each hit TLB entry is

automatically checked for memory protection attributes and violations are

reported to the IU as memory exceptions.

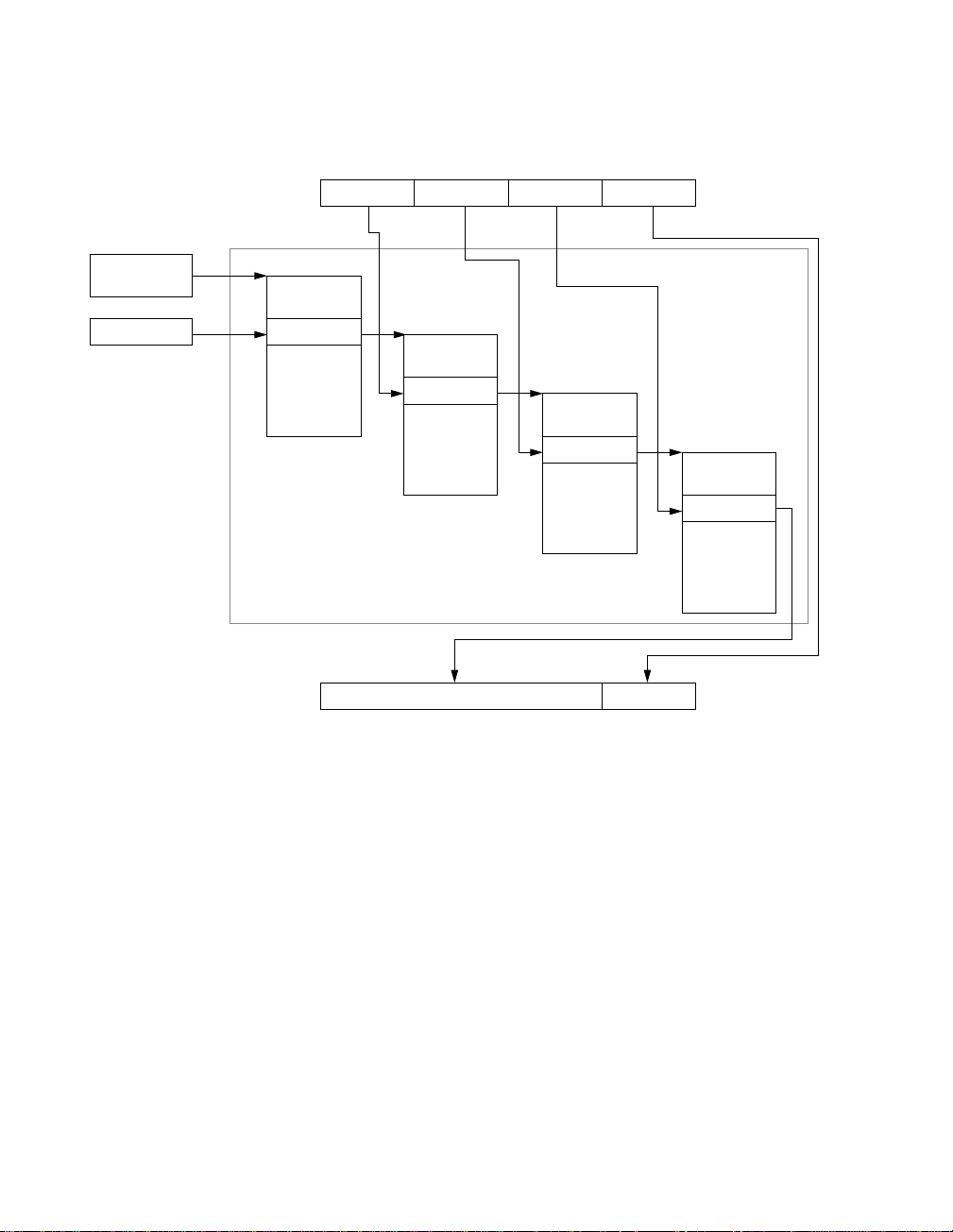

If the virtual address from the IU does not match an entry in the TLB, the

MMU automatically performs a search (or table walk) through a translation

table in main memory to obtain an address translation. The translation table

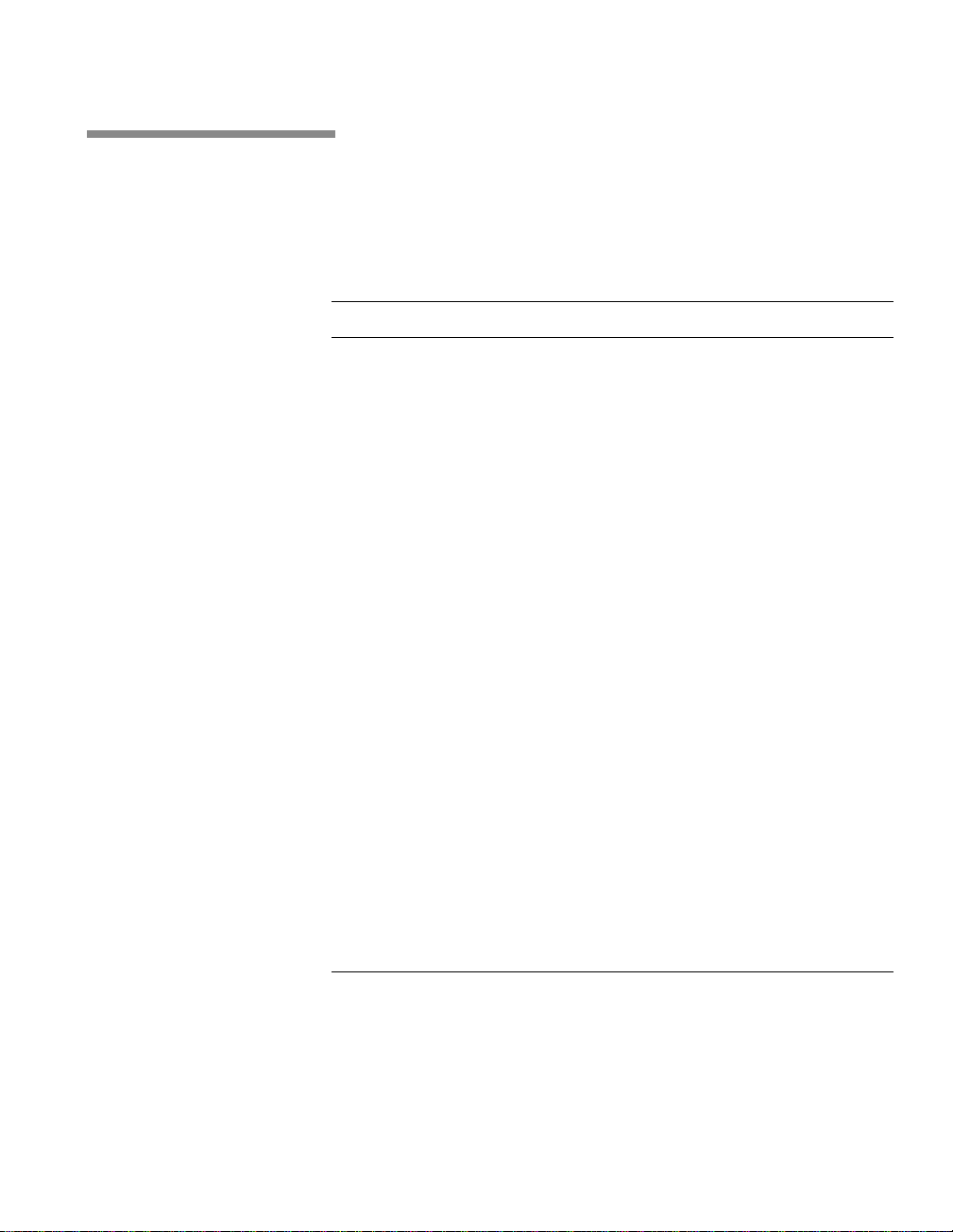

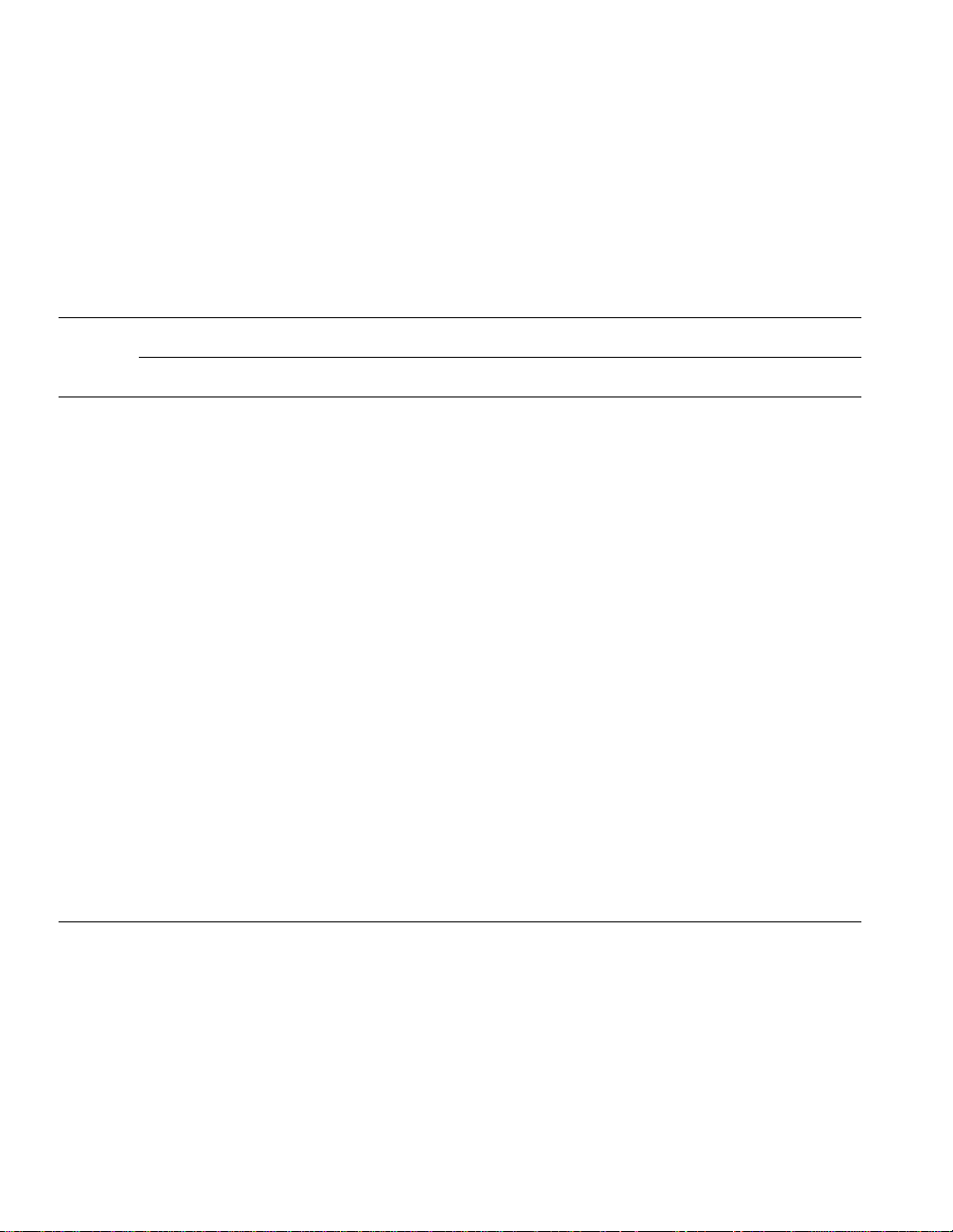

forms a tree structure in the main memory. An example of this is illustrated

in Figure 2-5.

Page Table by software.

The SPARC CPU 2-11

Page 40

Cache Controller and Memory Management Unit

31 24 23 18 17 12 11 0

Virtual Address Index 1 Index 2 Index 3 Page Offset

Context Table

Pointer

Register

Context Register

Context Table

Level 1 Page

Root Pointer

35 12 11 0

Physical Page NumberPhysical Address

Figure 2-5 A Three Level Table Walk In Memory

The Context Table Pointer register provides a pointer to the context table,

and the context register provides an index to the Root Pointer, which in turn

points to a level 1 page table. Index 1 from the virtual address selects an

entry within Level 1 pointing to a level 2 page table, where Index 2 selects

a pointer to a level 3 table. Index 3 then selects one of the entries in the level

3 table which should point to a 4Kbyte memory page. When a page table

pointer (PTP) is encountered within the tables, the search continues to the

next lower level. If a page table entry (PTE) is found, the search is

terminated and the entry is stored in the TLB. If no PTE is found at all, a

synchronous fault exception is signalled to the IU. The PTE provides a

pointer to a physical page while, in the case of a three level table walk, the

lower 12 bits of the virtual address provides an offset.

Table

PTP

Level 2 Page

Table

PTP

Page Offset

Level 3 Page

Table

PTE

2-12 The SPARC CPU

Page 41

Cache Controller and Memory Management Unit

The level at which a table walk terminates (that is, a PTE is found) is related

to the size of addressing region associated with the entry. A table walk

which finds a PTE in the context table corresponds to a region of 4Gbytes.

A PTE corresponds to: a 16Mbyte region in level 1; a 256Kbyte region in

level 2; or a 4Kbyte region in level 3. The virtual address bits not used to

index table entries are used to supply the offset address within the page.

A table walk which uses three page table levels is shown in the illustration

in Figure 2-5. In this example A(31:12) from the virtual address are used to

index the page tables, and A(11:0) supply an offset address into the selected

memory page.

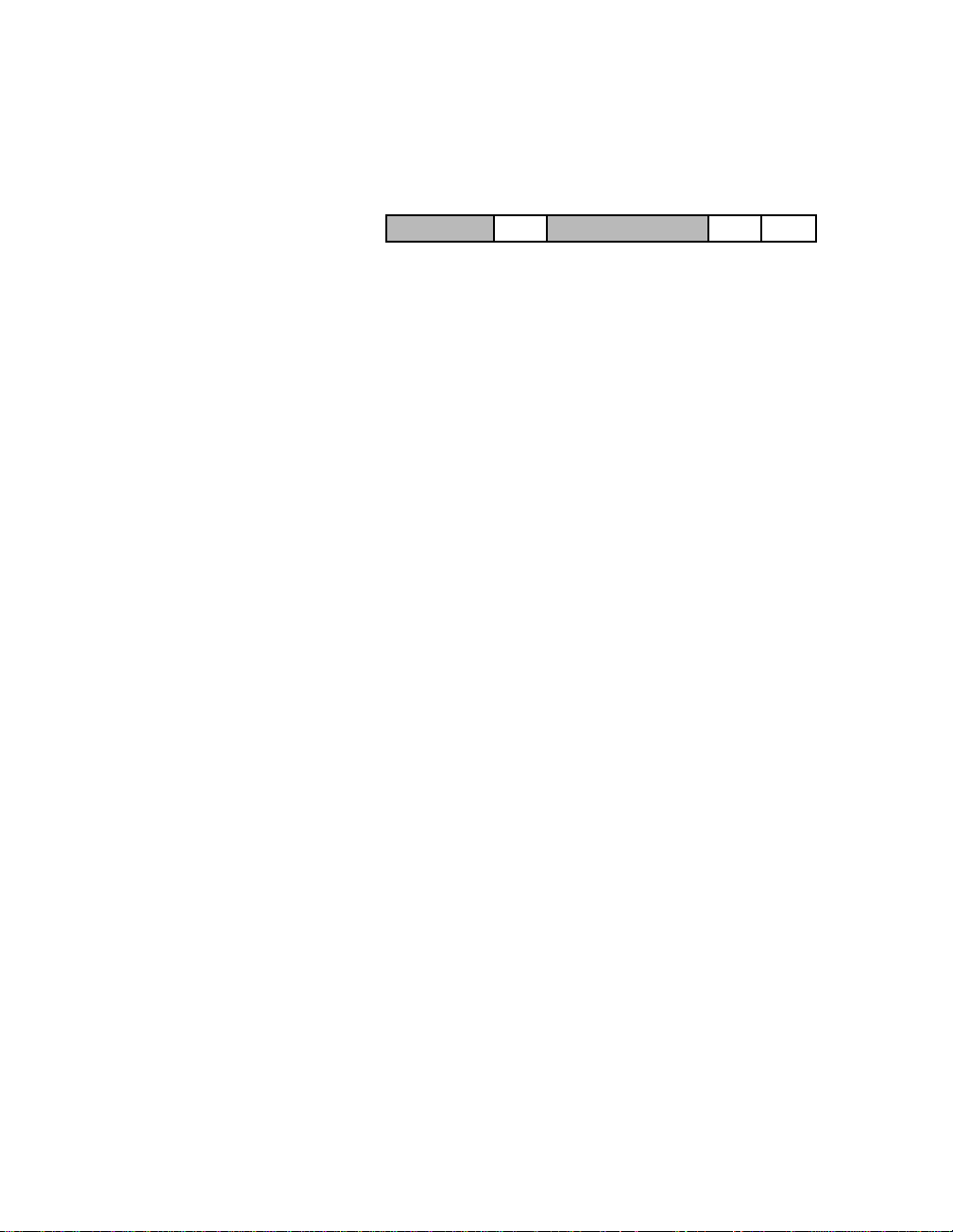

Figure 2-6 shows a table walk which terminates at level 2. In this case

A(31:18) are used as index bits, and A(17:0) provide an offset address into

the selected 256 Kbyte page.

31 24 23 18 17 0

Virtual Address Index 1 Index 2 Offset

Context Table

Register

Pointer

Context Register

Context Table

Root Pointer

35 18 17 0

Physical Page NumberPhysical Address

Figure 2-6 A Two Level TableWalk In Memory

Level 1 Page

Table

PTP

Level 2 Page

Table

PTE

Byte Offset

The SPARC CPU 2-13

Page 42

2.5 Memory Interface

The SPARC provides a 64-bit memory interface which supports up to

128Mbytes of system memory. The memory is composed of four banks of

up to 32Mbytes each. Different density devices are supported, allowing the

SPARCbook 3 to be fitted with a range of memory size options.

The SPARC’s memory interface provides a 64-bit data bus with 2-bit parity

(1 bit parity for each 32 bit word). The memory interface incorporates a

DRAM refresh controller.

The minimum memory access width is 32 bits; 8-bit and 16-bit write

accesses require read-modify-write operation and correct 32-bit boundary

alignment.

2.6 Instruction Cache

The integral instruction cache is a 16Kbyte physically tagged cache. The

instruction cache is organized as 512 lines of 32 bytes each.

2.7 Data Cache

Memory Interface

The data cache is a 8Kbyte direct mapped physically tagged write through

cache with no write allocate. It is organized as 512 lines of 16 bytes each.

Data cache read and write hits take no extra pipe cycles, except for

doubleword operations. There are two store buffers which hold data being

stored from the IU or FPU to memory or other physical devices. The store

buffers are 32-bit registers.

2.8 SBus Controller

The SPARC incorporates an SBus Controller which provides a master and

slave interface used to access I/O devices. It connects the CPU core directly

to the SBus and allows DMA devices to access the main DRAM located on

the SPARC’s memory bus. The SBus controller provides 32-bit data,

SBD(31:00), and 28-bit physical address, SBA(27:00), interface to other

devices in SPARCbook 3. The SBus controller also provides five SBus

Slave Select lines, SBSEL(4:0).

2-14 The SPARC CPU

Page 43

SBus Controller

2.8.1 Programmed I/O

Programmed I/O transactions consist of an SBus slave cycle only, with

address translations being carried out before bus acquisition. The processor

executes loads and stores to transfer data between it and devices on the

SBus (in I/O Space). The SBus Controller performs write posting during

processor writes, allowing processing to continue while the SBus

transaction is completed. During reads, processing is stalled until the data

becomes valid at the end of the SBus transaction.

2.8.2 DVMA

A direct virtual memory access consists of a translation cycle followed by

a slave cycle. During the translation cycle, a master places a virtual address

on the SBus data bus. The SPARC’s MMU provides a translated physical

address on the SBus.

The SPARC CPU 2-15

Page 44

SBus Controller

2-16 The SPARC CPU

Page 45

Memory Map and Interrupts 3

This chapter describes the addressing architecture

and interrupt architecture of SPARCbook 3.

The SLAVIO incorporates an interrupt controller

and is used to coordinate all on-board interrupts.

These include interrupts from devices on the board

and interrupts from SLAVIO internal source.

33

Page 46

3.1 Address Map

Address Map

The SBus controller contained in the MicroSPARC partitions the

SPARCbook 3’s memory map into a region for the main memory plus five

physical address regions of 256Mbytes each for the SBus. The resulting

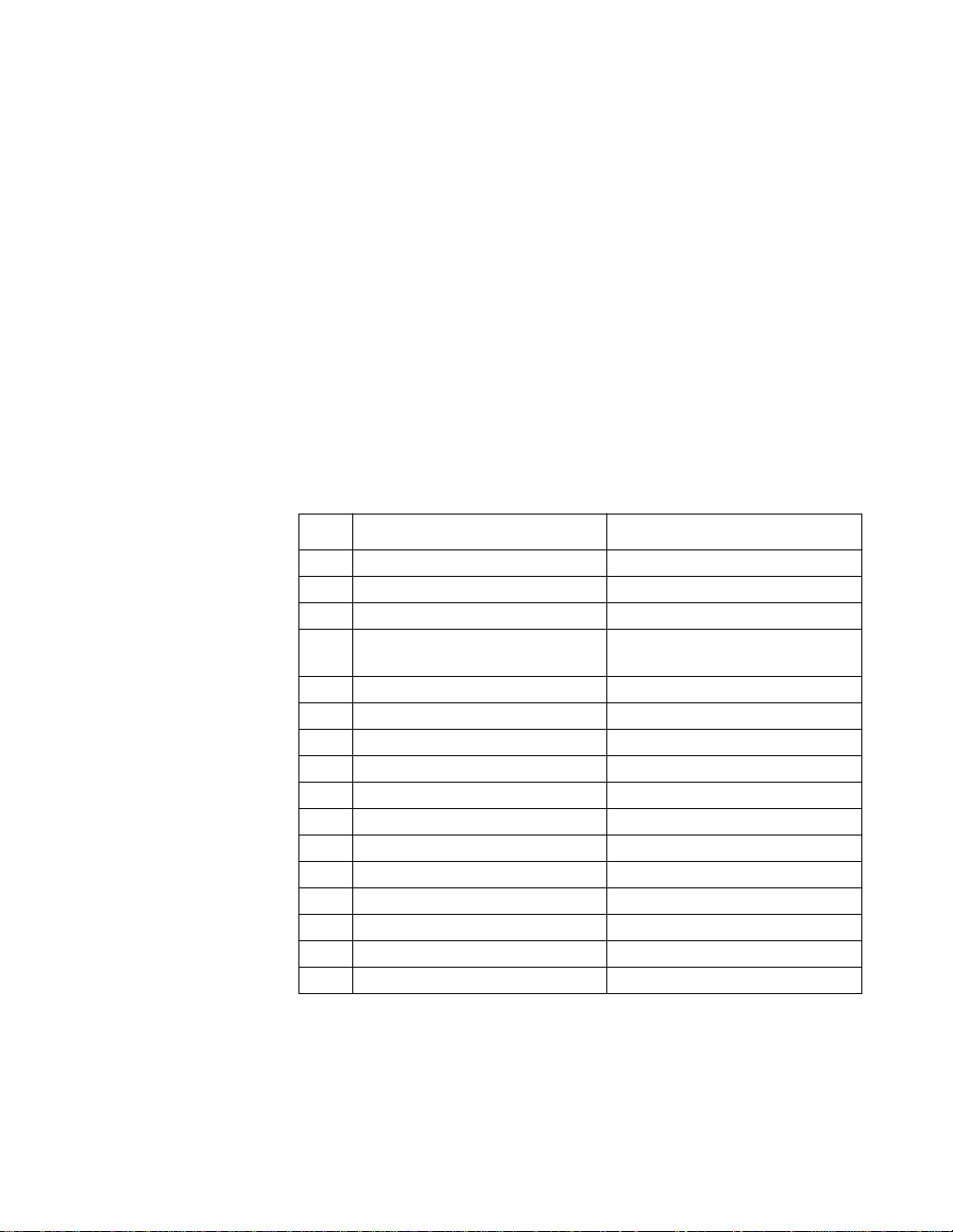

memory map of the SPARCbook is shown in Table 3-1.

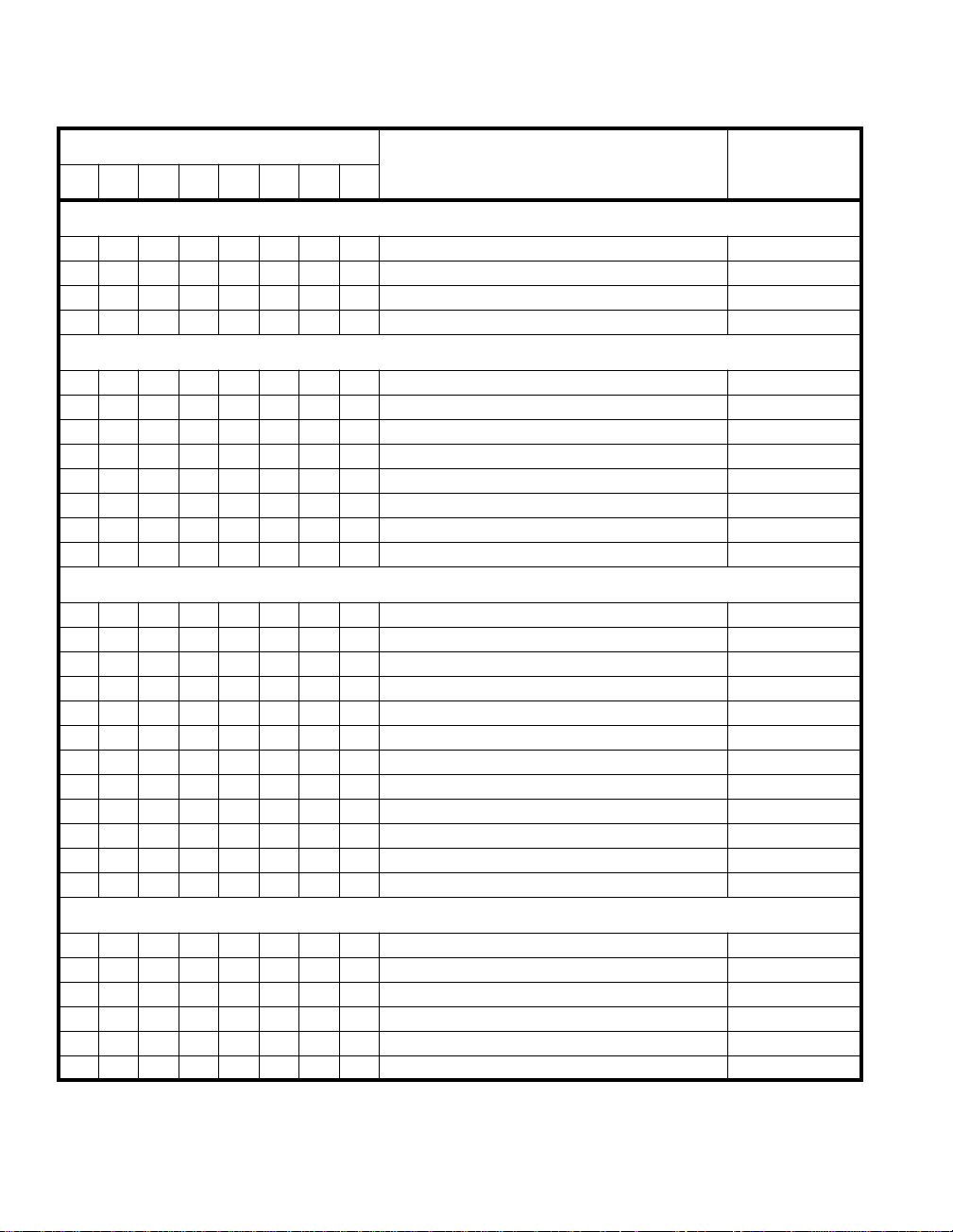

Address Range

(Hexadecimal)

70000000 7FFFFFFF SBus Slot 4 MACIO/SLAVIO 256

60000000 6FFFFFFF SBus Slot 3 Not allocated 256

50000000 5FFFFFFF SBus Slot 2 ISDN Controller 256

40000000 4FFFFFFF SBus Slot 1 TS102 PCMCIA Controller 256

30000000 3FFFFFFF SBus Slot 0 P9100 Graphics Controller 256

20000000 2FFFFFFF Unmapped - 256

10000000 1FFFFFFF I/O MMU Control Space - 256

08000000 0FFFFFFF Unmapped - 128

06000000 07FFFFFF DRAM Bank 3 - 32

04000000 05FFFFFF DRAM bank 2 - 32

02000000 03FFFFFF DRAM Bank 1 - 32

00000000 01FFFFFF DRAM Bank 0 - 32

Region SBus Rsource

Table 3-1 Main Memory Map

3.1.1 MACIO and SLAVIO Space (SBus Slot 4)

SBus slot 4 is sub-divided to provide access to the MACIO and SLAVIO.