SYNERGY SEMICONDUCTOR SY10E167, SY100E167 Technical data

查询SY100E167JC供应商

SY NERGY

SEMICONDUCTOR

6-BIT 2:1 MUX-REGISTER

SY10E167

SY100E167

SY10E167

SY100E167

FEATURES

■ 1000MHz min. operating frequency

■ Extended 100E VEE range of –4.2V to –5.5V

■ 800ps max. clock to output

■ Single-ended outputs

■ Asynchronous Master Reset

■ Dual clocks

■ Fully compatible with industry standard 10KH,

100K ECL levels

■ Internal 75KΩ input pulldown resistors

■ ESD protection of 2000V

■ Fully compatible with Motorola MC10E/100E167

■ Available in 28-pin PLCC package

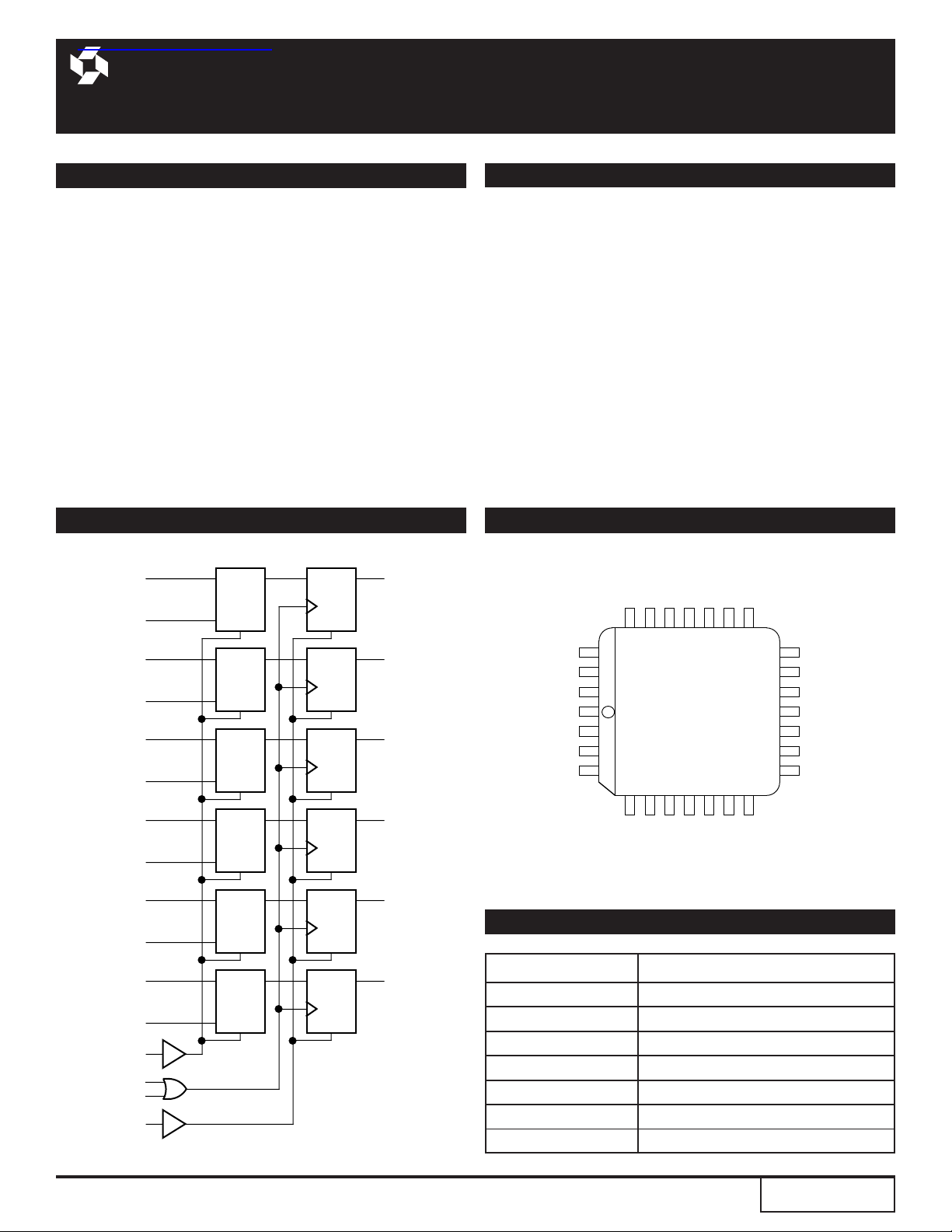

BLOCK DIAGRAM

D

D

D1a

D1b

D2a

D2b

0a

MUX

0b

SEL

MUX

SEL

MUX

SEL

Q

D

R

Q

D

R

Q

D

R

Q

Q1

Q2

0

DESCRIPTION

The SY10/100E167 offer six 2:1 multiplexers followed

by D flip-flops with single-ended outputs, designed for use

in new, high-performance ECL systems. The Select (SEL)

control allows one of the two data inputs to the multiplexer

to pass through. The two external clock signals (CLK1,

CLK2) are gated through a logical OR operation before use

as control for the six flip-flops. The selected data are

transferred to the flip-flops on the rising edge of CLK1 or

CLK2 (or both).

The multiplexer operation is controlled by the Select

(SEL) signal which selects one of the two bits of input data

at each mux to be passed through.

When a logic HIGH is applied to the Master Reset (MR)

signal, it operates asychronously to take all outputs Q to a

logic LOW.

PIN CONFIGURATION

3a

4a

D

CLK

CLK

V

MR

SEL

D

EE

5a

D

25 24 23 22 21 20 19

5b

26

1

27

2

28

1

2

3

0a

4

5 6 7 8 9 10 11

3b

4b

D

D

D

TOP VIEW

PLCC

J28-1

CCO

D

NC

V

Q

Q

V

Q

Q

V

Q

5

4

CC

3

2

CCO

1

18

17

16

15

14

13

12

D3a

D3b

D4a

D4b

D5a

D5b

SEL

CLK1

CLK2

MR

© 1999 Micrel-Synergy

MUX

SEL

MUX

SEL

MUX

SEL

Q

D

Q3

1b

0b

D

2a

1a

D

D

D

0

2b

Q

D

CCO

V

R

Q

D

Q4

PIN NAMES

R

Q

D

Q5

R

5-127

Pin Function

D0a–D5a Input Data a

D0b–D5b Input Data b

SEL Select Input

CLK1, CLK2 Clock Inputs

MR Master Reset

Q0–Q5 Data Outputs

CCO VCC to Output

V

Rev.: C Amendment: /1

Issue Date: February, 1998

SYNERGY

SEMICONDUCTOR

SY100E167

TRUTH TABLE

SY10E167

SEL Data

Ha

Lb

DC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit Condition

IIH Input HIGH Current — — 150 — — 150 — — 150 µA—

EE Power Supply Current mA —

I

10E — 94 113 — 94 113 — 94 113

100E — 94 113 — 94 113 — 108 130

AC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit Condition

fMAX Max. Toggle Frequency 1000 1400 — 1000 1400 — 1000 1400 — MHz —

t

PLH Propagation Delay to Output ps —

tPHL CLK 450 650 800 450 650 800 450 650 800

MR 450 650 850 450 650 850 450 650 850

S Set-up Time ps —

t

D 100 –50 — 100 –50 — 100 –50 —

SEL 275 125 — 275 125 — 275 125 —

H Hold Time ps —

t

D 300 50 — 300 50 — 300 50 —

SEL 75 –125 — 75 –125 — 75 –125 —

tRR Reset Recovery Time 750 550 — 750 550 — 750 550 — ps —

t

PW Minimum Pulse Width 400 — — 400 — — 400 — — ps —

CLK, MR

tskew Within-Device Skew — 75 — — 75 — — 75 — ps 1

r Rise/Fall Time 300 450 800 300 450 800 300 450 800 ps —

t

tf 20% to 80%

NOTE:

1. Within-device skew is defined as identical transitions on similar paths through a device.

PRODUCT ORDERING CODE

Ordering Package Operating

Code Type Range

SY10E167JC J28-1 Commercial

SY10E167JCTR J28-1 Commercial

SY100E167JC J28-1 Commercial

SY100E167JCTR J28-1 Commercial

5-128

Loading...

Loading...