Page 1

PRELIMINARY PRODUCT SPECIFICATION

nRF24Z1

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

2.4GHz wireless audio streamer

FEATURES APPLICATIONS

• Low cost 0.18u CMOS process, 36 pin 6x6mm

QFN package

• Single chip 2.4GHz RF transceiver • MP3 / Mini Disk headset

• 4Mbit/sec RF link • Speakers

• Input sample rate up to 96kHz, 24bits • Surround speakers

• Output sample rate up to 48kHz, 16bits • Microphone

• Programmable latency • Musical instruments

• Quality of Service engine supporting up to

1.536 Mbit/s LPCM audio

• S/PDIF interface for direct connection to PC

soundcard and surround receivers

• I2S interface for glueless audio support • Compressed video streaming

• SPI or 2-wire interface for up to 12 kbit/sec peak bi-

directional digital control/AUX data

• On chip optional 2:1 compression

• On chip voltage regulators

• Few external components

• Uses global 2.4GHz band

• Compact Disk, CD quality

headset

• Audio streaming from PC

soundcard to HiFi system

• Download MP3 files from PC

to MP3 player

GENERAL DESCRIPTION

nRF24Z1 gives you a true single chip system for CD quality audio streaming of up to16 bit

48 kHz audio with support of up to 24 bit 96 kHz input. I2S and S/PDIF interfaces are

supported for audio I/O. Seamless interfacing of low cost A/D and D/A for analog audio

input and output. SPI or 2-wire (I2C compatible) serial interfaces for control. The circuit

has embedded voltage regulators, giving maximum noise immuni ty and operation from a

single 2.0V to 3.6V supply.

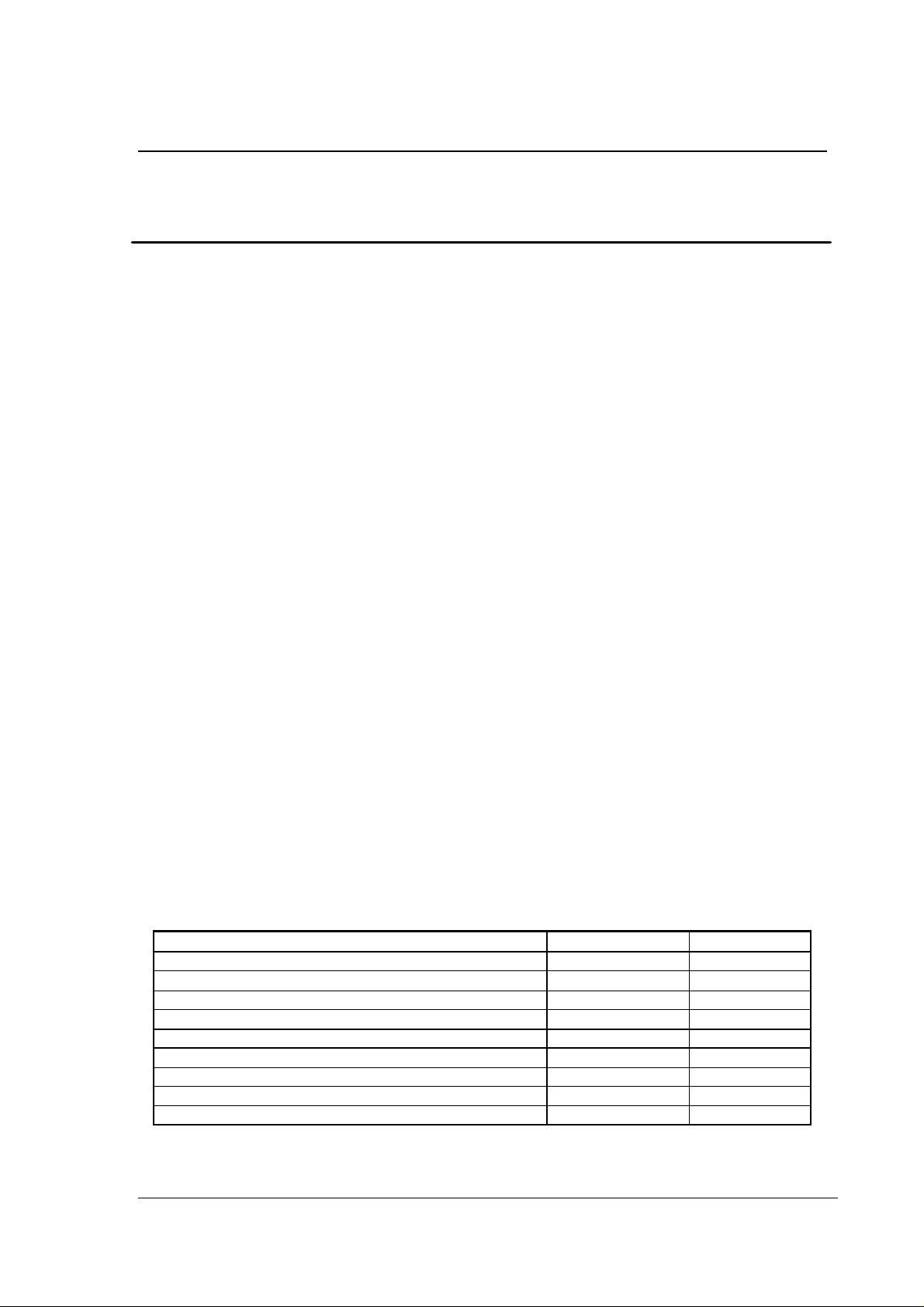

QUICK REFERENCE DATA

Parameter Value Unit

Minimum supply voltage 2.0 V

Temperature range -20 to +80

Peak supply current in transmit @ -5dBm output power 15 mA

Peak supply current in receive mode 32 mA

Supply current in power down mode 4 µA

Maximum transmit output power 0 dBm

Audio sample rate 32, 44.1 or 48 kbps

Audio resolution 16 bit

Receiver sensitivity -80 dBm

Table 1-1 nRF24Z1 quick reference data.

°C

Page 2

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

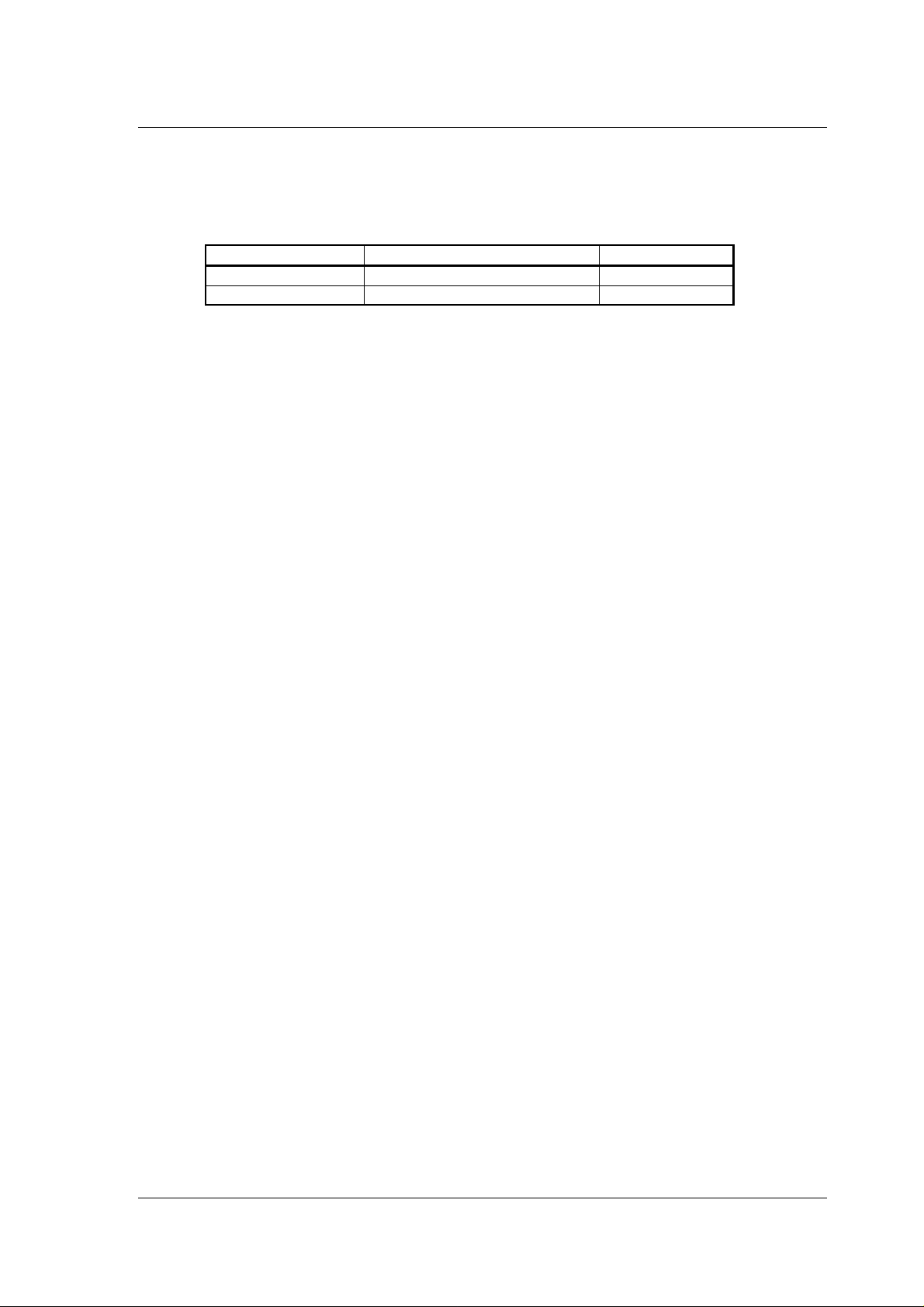

ORDERING INFORMATION

Type number Description Version

nRF24Z1 36L QFN 6x6 mm A

nRF24Z1-EVKIT Evaluation kit 1.0

Table 1-2 nRF24Z1 ordering information.

Page 3

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

TABLE OF CONTENTS

FEATURES ............................................................................................................................1

APPLICATIONS ....................................................................................................................1

GENERAL DESCRIPTION...................................................................................................1

QUICK REFERENCE DATA................................................................................................1

ORDERING INFORMATION...............................................................................................2

TABLE OF CONTENTS........................................................................................................3

1 Pin Assignment ...............................................................................................................6

2 Pin Function....................................................................................................................7

3 Glossary of terms ............................................................................................................8

4 Architectural Overview...................................................................................................9

4.1 Audio transmitter ..................................................................................................11

4.1.1 I2S audio input..............................................................................................11

4.1.2 S/PDIF audio input .......................................................................................12

4.1.3 Serial control (slave) interfaces.....................................................................12

4.1.4 Master interfaces...........................................................................................12

4.1.5 Direct data input pins ....................................................................................13

4.1.6 Interrupt output .............................................................................................13

4.2 Audio Receiver .....................................................................................................13

4.2.1 I2S audio output............................................................................................14

4.2.2 S/PDIF audio output.....................................................................................15

4.2.3 Master interfaces...........................................................................................15

4.2.4 Serial control (slave) interfaces.....................................................................15

4.2.5 Parallel port and PWM..................................................................................15

4.3 Blocks common to audio transmitter and receiver................................................16

4.3.1 XTAL Oscillator ...........................................................................................16

4.3.2 Radio Transceiver.........................................................................................16

4.3.3 Quality of Service engine..............................................................................16

4.3.4 Audio compression / Decompression...........................................................17

4.3.5 Power............................................................................................................17

4.3.6 IREF / RESET...............................................................................................17

5 Operation overview.......................................................................................................18

5.1 Power on / RESET sequence ................................................................................18

5.2 RF Link initialization............................................................................................18

5.2.1 Idle state ........................................................................................................18

5.2.2 Link-locate state............................................................................................19

5.2.3 Synchronization state ....................................................................................19

5.3 Audio streaming....................................................................................................19

5.4 Audio receiver clock rate recovery.......................................................................20

5.5 Data link................................................................................................................20

5.6 Power down mode.................................................................................................21

6 nRF24Z1 register MAP.................................................................................................22

6.1 Access from audio transmitter side.......................................................................22

6.2 Access from audio receiver side ...........................................................................22

7 Digital I/O.....................................................................................................................25

7.1 Digital I/O behaviour during RESET....................................................................25

Page 4

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

7.2 Audio interfaces....................................................................................................25

7.3 I2S Audio Interface...............................................................................................25

7.4 S/PDIF Audio Interface ........................................................................................26

7.5 Audio interface functionality ................................................................................27

7.5.1 ATX audio interface control.........................................................................27

7.5.2 ARX audio interface control.........................................................................30

7.5.3 I2S Audio interface timing............................................................................32

7.6 Serial master interfaces.........................................................................................33

7.6.1 Timing serial master interfaces....................................................................36

7.7 Control and GPIO interfaces.................................................................................37

7.7.1 ATX control and GPIO pins .........................................................................37

7.7.2 SPI slave interface.........................................................................................38

7.7.3 2-wire slave interface....................................................................................38

7.7.4 General purpose input pins D[2:0]................................................................40

7.7.5 ATX Control interface timing.......................................................................41

7.7.6 ARX control interface options ......................................................................42

7.7.7 ARX GPIO pins ............................................................................................43

7.8 Data Channel Timing............................................................................................45

7.8.1 Forward data channel, data transfer from ATX to ARX...............................45

7.8.2 Return data channel, data transfer from ARX to ATX .................................46

8 Quality of service (Qos) and RF...................................................................................48

8.1 Link algorithm.......................................................................................................48

8.2 RF protocol ...........................................................................................................48

8.3 Adaptive frequency hopping.................................................................................48

8.3.1 Adapting to the RF environment...................................................................50

8.4 Link registers.........................................................................................................50

8.4.1 RF link latency..............................................................................................52

8.5 RF output power ...................................................................................................53

9 Interrupts .......................................................................................................................54

10 RESET outputs..........................................................................................................55

11 Power down control..................................................................................................56

11.1 Enter power down.................................................................................................56

11.2 Wake up from power down...................................................................................56

11.2.1 External pin change.......................................................................................57

11.2.2 Timer controlled wake up .............................................................................57

11.3 nRF24Z1 power saving example ..........................................................................58

12 Register update over the data link.............................................................................60

13 Eletrical Specification...............................................................................................61

14 Absolute maximum ratings .......................................................................................63

15 Package outline .........................................................................................................64

16 Application Information............................................................................................65

16.1 Antenna I/O...........................................................................................................65

16.2 Crystal Specification.............................................................................................65

16.3 Bias reference resistor...........................................................................................65

16.4 Internal digital supply de-coupling .......................................................................65

16.5 PCB layout and de-coupling guidelines................................................................66

17 Application example.................................................................................................67

17.1 nRF24Z1 schematics.............................................................................................67

Page 5

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

17.2 nRF24Z1 layout....................................................................................................69

17.3 nRF24Z1 Bill of Material .....................................................................................71

18 References.................................................................................................................73

19 Definitions.................................................................................................................74

20 Your notes .................................................................................................................75

Page 6

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

1 PIN ASSIGNMENT

DO[3]/

IRQ/

MSCK

VSS

VDD

PWM

MMOSI

VSS

MMISO

MCSN

MSCL

SSEL/DO[2]

SMISO/SSDA/DO[1]

SSCK/SSCL/DO[0]

SCSN/SADR/DI[3]

VDD

SMOSI/DD[2]/DI[2]

DD[1]/DI[1]

DD[0]/DI[0]

REQ

32

1

2

3

nRF24Z1

2829303136 35 34 33

27

MSDA

26

MODE

25

VSS

QFN36 6x6

IREF

4

5

6

7

8

9

1817161510 11 12 13 14

XC1

XC2

VSS

CLK

WS

DATA

SPDIO

MCLK

DVDD

24

23

VSS_PA

ANT2

22

21

ANT1

VDD_PA

20

19

VDD

Figure 1-1: Pin assignment nRF24Z1

Page 7

PRELIMINARY PRODUCT SPECIFICATION

Pin function

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

2 PIN FUNCTION

Name

Description Pin

Slave

IF

1 SSEL DO[2] Dig. In Dig. Out Slave interface select

2 SMISO

/SSDA

3 SSCK

/SSCL

4 SCSN

/SADR

5 VDD Power Power Supply (2.0-3.6 V DC)

6 SMOSI

/DD[2]

7 DD[1] DI1 Digital Input Direct data in bit #1 GPIO in bit #1

8 DD[0] DI0 Digital Input Direct data in bit #0 GPIO in bit #0

9 REQ Dig. Out Dig. In I2S data request (programmable polarity)

10 CLK Dig. In Dig. Out I2S bit clock

11 WS Dig. In Dig. Out I2S word clock

12 DATA Dig. In Dig. Out I2S data signal

13 SPDIO Dig. In Dig. Out S/PDIF interface

14 MCLK Dig. Out 256X sample rate clock to ADC or DAC

15 DVDD Regulator output Digital voltage regulator output for decoupling

16 VSS Power Ground (0V)

17 XC2 Analog output Crystal Pin 2

18 XC1 Analog input Crystal Pin 1

19 VDD Power Power Supply (2.0-3.6 V DC)

20 VDD_PA Regulator output DC output (+1.8V) for RF interface (ANT1, ANT2)

21 ANT1 RF Antenna interface 1

22 ANT2 RF Antenna interface 2

23 VSS_PA Power Ground (0V)

24 IREF Analog input Connection to external Bias reference resistor, or RESET

25 VSS Power Ground (0V)

26 MODE Digital Input nRF24Z1 function

27 MSDA Digital IO Master 2-wire bi-directional data

28 MSCL Digital IO Master 2-wire bi-directional clock

29 MCSN Digital Output Master SPI primary slave select (active low)

30 MMISO Digital Input Master SPI serial input

31 MMOSI Digital Output Master SPI serial output

32 VSS Power Ground (0V)

33 VDD Power Power Supply (2.0-3.6 V DC)

34 VSS Power Ground (0V)

35 MSCK Digital Output Master SPI clock

36 IRQ DO[3]

ARX

GPIO Slave IF

DO[1] Digital Output

/ Digital IO

DO[0] Dig. In Dig. Out Slave SPI clock

DI3 Digital Input Slave SPI slave select

DI2 Digital Input Slave SPI serial in

Digital Output Interrupt request GPIO out bit #3

/ PWM

ARX

GPIO IF ATX/ARX with slave IF

1: 2-wire, 0: SPI

Slave SPI serial out

/ Slave 2-wire data (bidir)

/ Slave 2-wire clock

/ Address select 2-wire slave

/ Direct data in bit #2

if pulled to VDD

1 : audio transmitter, 0: audio receiver

ARX with GPIO IF

GPIO out bit #2

GPIO out bit #1

GPIO out bit #0

GPIO in bit #2

GPIO in bit #3

/ PWM output

Table 2-1 nRF24Z1 pin function

Page 8

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

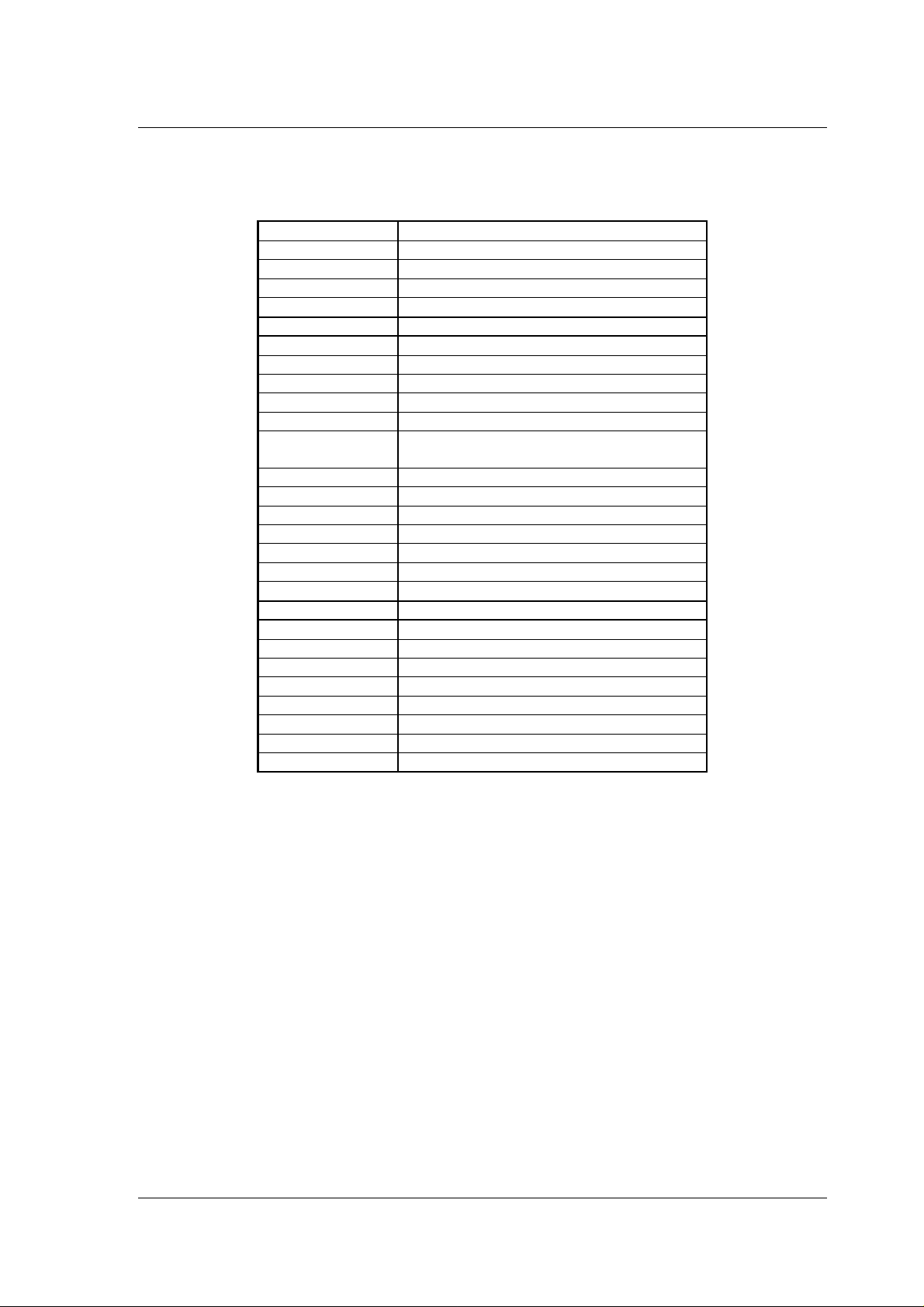

3 GLOSSARY OF TERMS

Term Description

ADC Analog to Digital Converter

ARX audio receiver

ATX audio transmitter

CD Carrier Detect

CHPA SPI clock phase

CLK Clock

CPOL SPI clock polarity

CRC Cyclic Redundancy Check

DAC Digital to Analog Converter

DSP Digital Signal Processor

EEPROM electrical erasable programmable read only

memory

Flash Flash memory

GFSK Gaussian Frequency Shift Keying

GPIO General Purpose In Out

I2S 3 wire audio serial interface

ISM Industrial-Scientific-Medical

LPCM linear PCM (pulse code modulation)

MBZ Must Be Zero (reserved for future extensions)

MCU Micro Controller Unit

MP3 a popular compressed audio format

PWM Pulse Width Modulation

QOS Quality Of Service

RX Receive

S/PDIF one wire serial digital audio format

SPI Serial Peripheral Interface

TX Transmit

2-wire 2-wire serial interface compatible with I2C

Table 3-1 Glossary of terms nRF24Z1.

Page 9

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

4 ARCHITECTURAL OVERVIEW

nRF24Z1 is a 4 MBit/s single chip RF transceiver that operates in the world wide 2.4 GHz

licencee free ISM band. The nR24Z1 is based on the proven nRF24xx radio and

ShockBurst™ platforms from Nordic Semiconductor.

The device offers a wireless channel for seamless streaming of LPCM or compressed audio

in parallel with a low data rate control channel. To enable this, the device offers the

following features in addition to the nRF24xx RF platform:

• Standard digital audio interfaces (I2S, S/PDIF)

• Fully embedded Quality of Service engine that handles all RF protocol and

RF link tasks.

• SPI and 2-wire master and slave control interfaces

• GPIO pins

As all processing related to audio I/O, RF protocol and RF link management is embedded,

the device offers the end application an up to 1.54 MBit/s transparent audio channel

without any true time processing needed. nRF24Z1 can be utilized in systems without

external microcontroller or by a simple microcontroller that only need to handle low speed

tasks over the serial or parallel ports (ex: volume up/down).

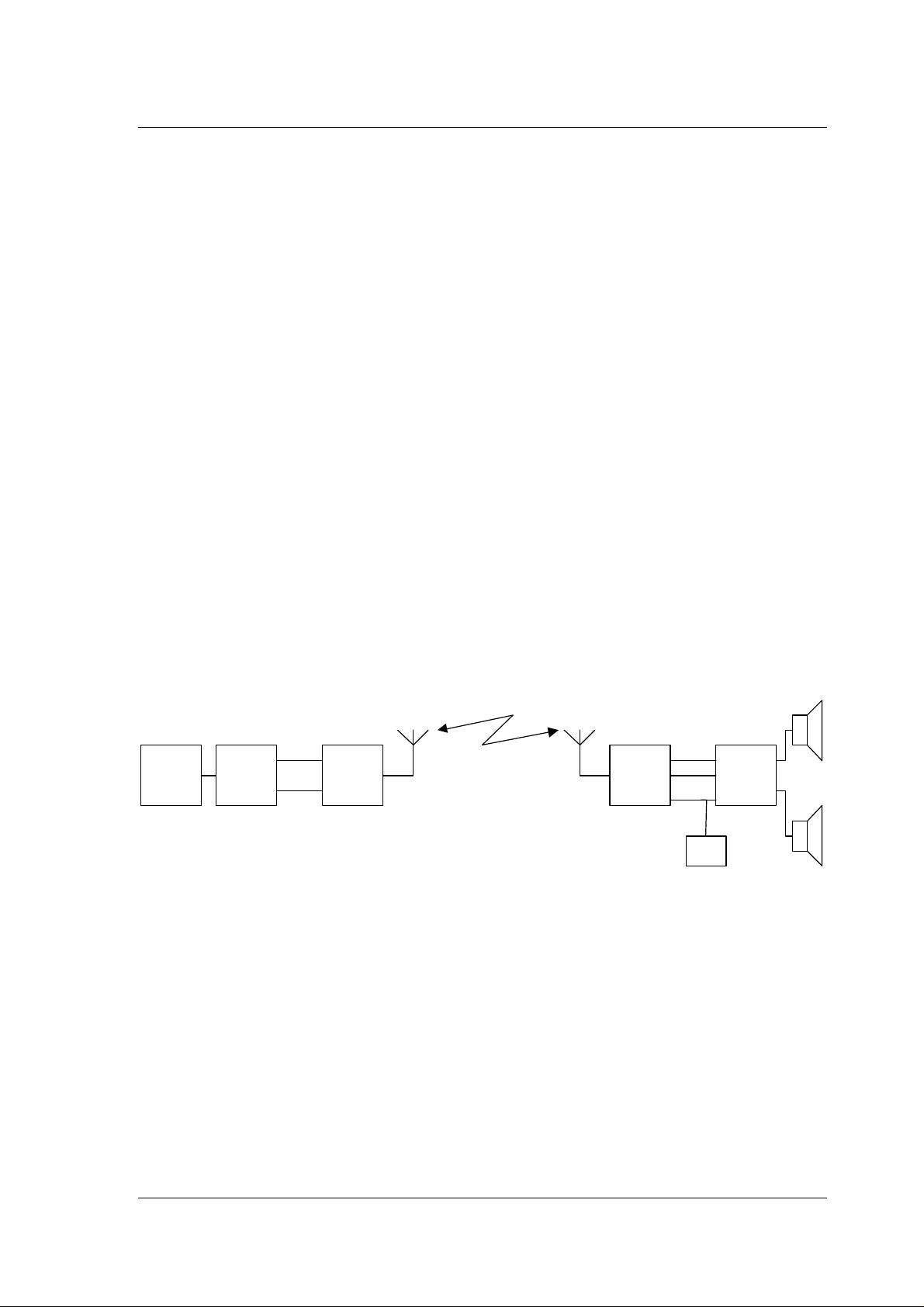

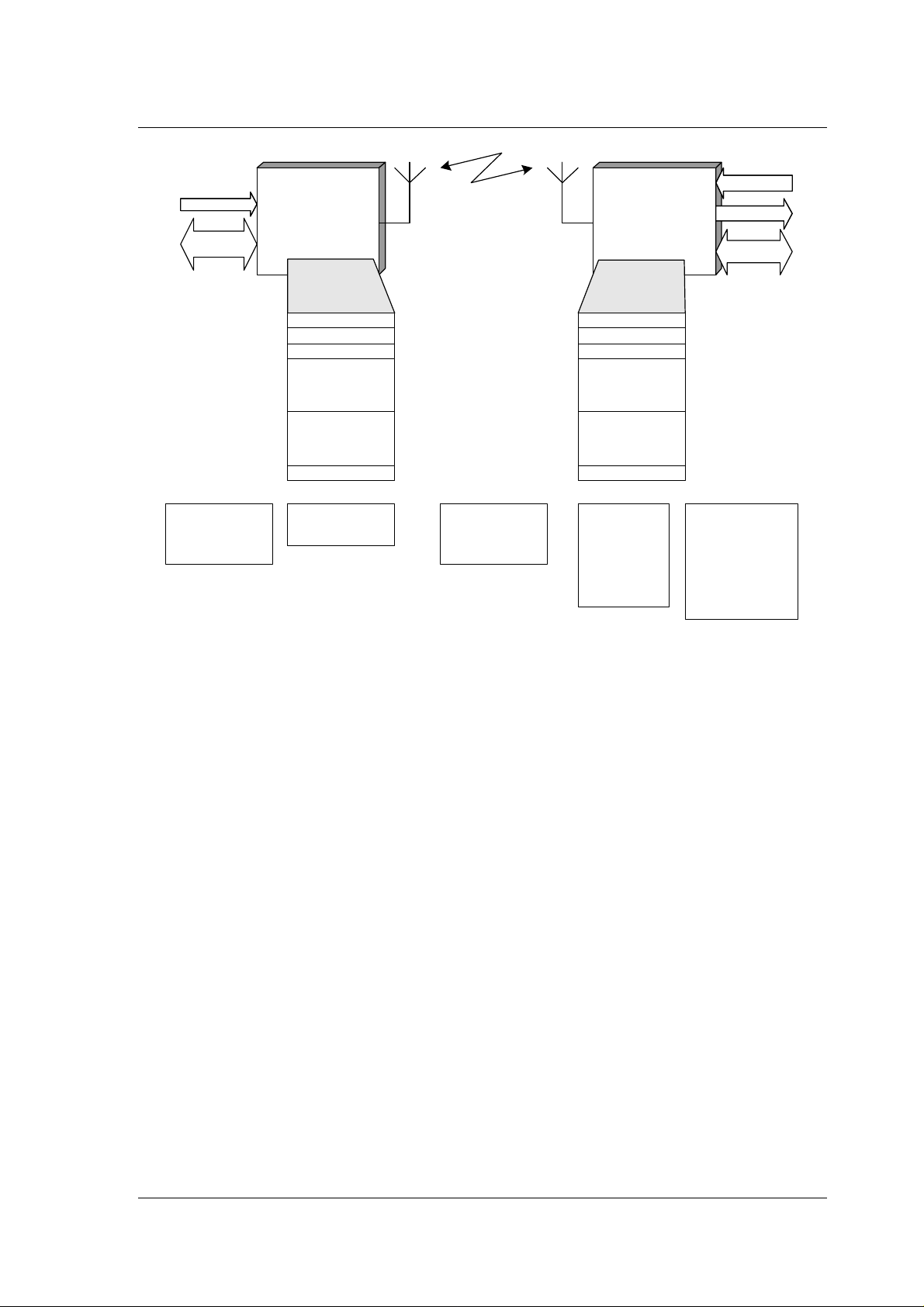

A typical system using nRF24Z1 can be seen in Figure 4-1

Audio Source Destination

DAC

and

audio

amplifier

E2

Storage

DSP /

uP

nRF24Z1 nRF24Z1

I2S

Audio

transmitter

MCLKSPI

I2S

SPI

Audio

receiver

Figure 4-1 Typical audio application using nRF24Z1

In this system a DSP or micro controller feeds data from storage to nRF24Z1 using

standard audio format (I2S). A nRF24Z1 pair transfers the audio data and presents it to a

stereo DAC on the other side. For other parts of the application, the nRF24Z1 link will in

other words look like an open channel (like a cable).

Initial configuration of nRF24Z1 is done by the micro controller through a SPI or 2-wire

control interface. On the destination side, peripherals like a DAC can be controlled from

the audio source side through the control channel offered by nRF24Z1. In designs without

an external micro controller, configuration data can be loaded by nRF24Z1 from an

optional EEPROM/FLASH memory, enabling it to operate stand alone with limited feature

set.

Page 10

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

A wireless system that is streaming audio will have a very asymmetrical load on the RF

link since audio data is fed from an audio source (CD player) to a destination (loud

speakers). From the destination back to the audio source only service and control

communication is needed.

nRF24Z1 are used both on the audio source side (ex. in a CD player) transmitting audio

data, and in the 'destination' (loud speaker) side receiving audio data. Due to the

asymmetry, nRF24Z1 has two main modes set by external pin MODE, depending on which

side of the link it is put. The two modes have significant differences both in internal and

I/O functionality.

To ease understanding of nRF24Z1 operation, the following notation is introduced:

• Audio transmitter (ATX) – nRF24Z1 on the audio source side, transmitting audio data

• Audio receiver (ARX ) – nRF24Z1 on the destination side, receiving audio data

Transmitter and receiver are here referring to the flow of the audio; the nRF24Z1 RF front

end always runs a full two way link.

The nRF24Z1 control and data channel is a two way low data rate channel superimposed on

the audio and service communication. The audio transmitter is designated master meaning

that when a RF link is present 2-wire, SPI, GPIO and internal registers in the audio receiver

can be seen and controlled as a virtual extension of the audio transmitters own I/O and

registers. The implications of this is that external devices like audio DAC or volume control

components connected to the audio receiver effectively can be controlled by input to the

audio transmitter. User actions (ex: push of a button) on the audio receiver side are

similarly fed back to and can be processed on the audio transmitter side.

The following sections will give an overview of the I/O, main modules and functionality of

nRF24Z1. Due to the differences in ATX and ARX, the overview will present the modes

separately.

Page 11

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

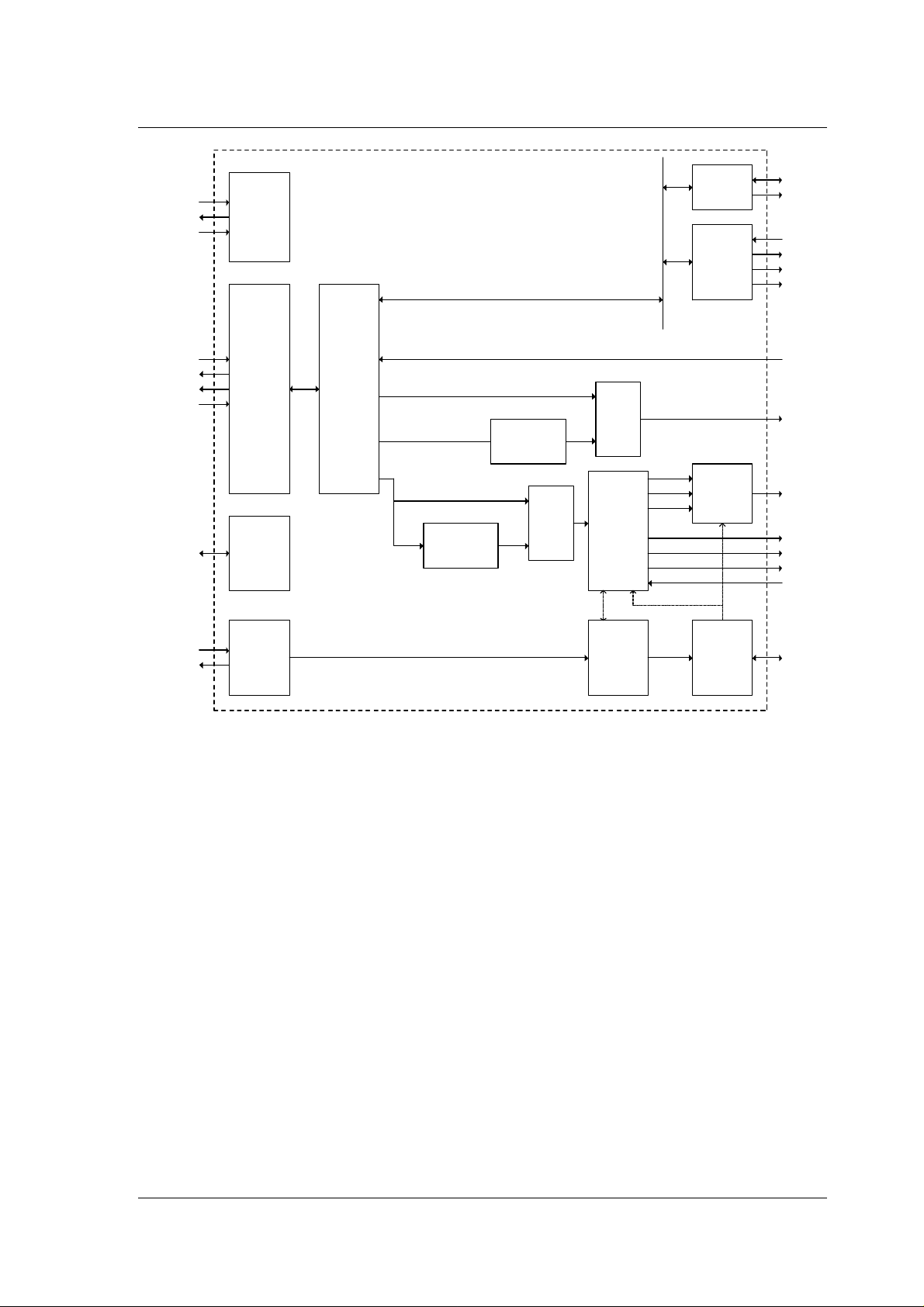

4.1 Audio transmitter

When nRF24Z1 is put at the audio source side of the RF link, MODE must be high and

nRF24Z1 becomes an audio transmitter (ATX). The block schematic of nRF24Z1 in ATX

mode can be seen in Figure 4-2.

VDD

DVDD

VSS

SADR/

SCSN

SSCL/

SSCK

SSDA/

SMISO

SMOSI/

DD[2]

SSEL

DD[1:0]

IRQ

SPDIO

CLK

DATA

WS

REQ

POWER

Slave

IF

MUX

S/PDIF

to

I2S

2-wire

slave

SPI

slave

parallel

Serial

to

Local

Status

Local

Config

Remote

Status

Remote

Config

Remote

Data

Audio

compress

MUX

TDM

QOS

2-wire

master

SPI

master

nRF

24xx

radio

BIAS /

RESET

MSDA

MSCL

MMISO

MSCK

MMOSI

MCSN

VSS_PA

ANT1

ANT2

VDD_PA

IREF

PLLMCLK

Clock

Control

XTAL

oscillator

XC2

XC1

Figure 4-2 nRF24Z1 ATX mode block diagram

The I2S or S/PDIF interfaces can be used for audio data input or alternatively the device

may stream other real-time data from a DSP over the I2S interface.

4.1.1 I2S audio input

For seamless input from audio sources physically close to nRF24Z1, I2S is the preferred

interface. The I2S interface consists of pins CLK, DATA and WS. The interface supports

Page 12

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

sample rates of 32, 44.1, 48 and 96 kHz. Data may be in 16, 20 or 24 bit format.1 The data

rate is automatically detected.

I2S may also be used with an external stereo ADC for analog audio sources. The nRF24Z1

offers a 256 times audio sampling rate clock (fS) on the MCLK pin to be used as system

clock for the ADC.

A REQ output is available for pacing the data-flow when streaming MP3 and other “data”

streams over the I2S interface.

4.1.2 S/PDIF audio input

For audio sources physically more remote , the ATX offers a (CMOS level) S/PDIF input

on pin SPDIO. This interface supports 32, 44.1 or 48 kHz sampling rates with resolution of

16, 20 or 24 bit. It supports both linear and nonlinear audio according to IEC standards, see

ch. 7.4 for details.

4.1.3 Serial control (slave) interfaces

When ATX is controlled by an external MCU, configuration and control data both for the

audio transmitter itself and a linked audio receiver may be entered via a 2-wire or SPI slave

serial interface. The same interface is used for reading back status information. The register

map is identical for both interfaces, but only one of the interfaces, selected by SSEL pin,

may be used in a given application.

The two interfaces are :

SSEL = 0; SPI (pins SCSN, SSCK, SMISO, SMOSI).

SSEL = 1; 2-wire (pins SADR, SSCL and SSDA)

Pin SADR is not part of a standard 2-wire interface but selects one of two possible bus

addresses for the nRF24Z1.

4.1.4 Master interfaces

For standalone operation of nRF24Z1, a serial EEPROM or FLASH memory may be

connected to a SPI or 2-wire master interface. If a memory is present at any of these

interfaces during power up or reset, the device will read default configuration data from the

memory.

The SPI master is found on pins MCSN, MMISO, MMOSI and MSCK and 2-wire master

on pins MSDA and MSCL.

1

This specification item is for the I2S input interface. Not all of these formats can be

transferred within the available 1.54 Mbit/s data rate.

Page 13

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

4.1.5 Direct data input pins

The ATX has 2 general purpose input pins, DD[1:0], that may be transmitted directly to

and hence mirrored on the audio receiver. When SSEL is set high (2-wire interface

selected), one additional direct data pin (DD[2]) is available. If the logic level on pins

DD[2:0] are mirrored (copied) over the control link, pins DO[2:0] on the audio receiver

will carry the mirrored signal.

These pins may hence be used to switch on/off audio receiver peripherals without

microprocessor activity.

4.1.6 Interrupt output

The nRF24Z1 can interrupt the external application through pin IRQ based on a number of

sources such as no audio input detected, loss of RF communication etc.

Once IRQ has triggered external MCU, interrupt status can be read, through the serial

control interface.

4.2 Audio Receiver

When nRF24Z1 is put at the destination side of the RF link, MODE must be low and

nRF24Z1 becomes the audio receiver (ARX). The block schematic of nRF24Z1 in ARX

mode can be seen in Figure 4-3. I2S or S/PDIF are now used for audio or other real time

data output.

Page 14

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

VDD

DVDD

VSS

VSS_PA

ANT1

ANT2

VDD_PA

IREF

POWER

nRF

24xx

radio

BIAS /

RESET

TDM

QOS

Audio de-

compress

PWM

MUX

MUX

Parallel

to

serial

2-wire

master

SPI

master

I2S

to

SPDIF

MSDA

MSCL

MMISO

MSCK

MMOSI

MCSN

DI[3:0]

DO[3:0]

SPDIO

CLK

DATA

WS

REQ

XC2

XC1

XTAL

oscillator

Clock

Control

PLL /

MUX

MCLK

Figure 4-3 nRF24Z1 ARX mode block diagram

After a link is established the user can control the SPI and 2 wire master from the audio

transmitter. In this way the audio transmitter is able to control audio receiver serial

peripherals like audio DACs and amplifiers.

4.2.1 I2S audio output

Audio output to devices physically close to nRF24Z1 (typically a stereo DAC) are normally

driven by the I2S output (pins CLK, DATA and WS). The inte rface supports sample rates

of 32, 44.1 and 48 kHz. Data are in 16 bit format.

In audio receiver mode the MCLK pin provides 256 times fS clock for an external DAC.

A REQ input is available for pacing the data-flow when streaming MP3 or other “data”

streams over the I2S.

Page 15

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

4.2.2 S/PDIF audio output

For physically more remote audio devices, the audio receiver provides an S/PDIF (full

swing CMOS) output on pin SPDIO. This interface supports 32, 44.1 and 48 kHz, 16 or 24

bit data. It supports both linear and nonlinear audio according to IEC standards, see ch. 7.4

for details.

4.2.3 Master interfaces

A serial EEPROM or FLASH memory may be connected to a SPI or 2-wire master

interface. If a memory is present at any of these interfaces during power up or reset, the

device will read default configuration data from that memory; otherwise hard coded default

values will be used.

During audio receiver configuration, the SPI master (pins MMSCK, MMISO, MMOSI,

MCSN) is operated at 1MHz or 0.5MHz with the SPI format set to CPOL=0,CHPA=0 for

EEPROM/FLASH compatibility. After a link is established, the user may control the SPI

master from the audio transmitter. The available clock speed is up to 8 MHz over the full

operation range of the device.

During start-up, the audio receiver operates the 2-wire master (MSDA, MSCL) interface at

100 kHz. After a link is established, the user may control the 2-wire master from the audio

transmitter to 100kHz, 400kHz or 1MHz.

4.2.4 Serial control (slave) interfaces

When ARX is controlled by an external MCU, configuration and control data for the audio

receiver may be entered via a 2-wire or SPI slave serial interface. The same interface is

used for reading back status information. The register map is identical for both interfaces,

but only one of the interfaces, selected by SSEL pin, may be used in a given application.

The two interfaces are :

SSEL = 0; SPI (pins SCSN, SSCK, SMISO, SMOSI).

SSEL = 1; 2-wire (pins SADR, SSCL and SSDA)

Pin SADR is not part of a standard 2-wire interface but selects one of two possible bus

addresses for the nRF24Z1.

4.2.5 Parallel port and PWM

Alternatively to the serial slave interfaces, ARX can be configured with an 8 bit parallel

port, which can be controlled and read from the audio transmitter. There are 4 input pins

DI[3:0] that are continuously monitored when a link is up. Changes on any of these inputs

will be sent back to the audio transmitter where it can be accessed in a register (via the

serial control interface). The audio receiver can also be programmed to wake up from

power down mode on a change on one of these pins.

Page 16

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

There are 4 outputs DO[3:0] that are controlled from the audio transmitter. Any of these

may be programmed for high current in order to drive LEDs or for standard CMOS to

control of other devices on the audio receiver board.

DO3 may be programmed to output a PWM signal, where the output duty cycle is

programmable with 8-bit resolution from the audio transmitter. Note that this PWM cannot

be used as audio DAC

The output pins DO[3:0] may also function as slave select signals if multiple slaves are

present on the ARX SPI master bus.

4.3 Blocks common to audio transmitter and receiver

4.3.1 XTAL Oscillator

The crystal oscillator will provide a stable reference frequency with low phase noise for the

radio and audio functions. See section 16.2 for full Crystal Specification.

4.3.2 Radio Transceiver

The RF transceiver part of the circuit is a member of nRF24xx family of low power highly

integrated 2.4GHz ShockBurst™ transceivers. The transceiver interface is optimized for

high speed streaming of up to 4 Mbps. Output power and some protocol parameters can be

controlled by the user via the QoS module.

4.3.3 Quality of Service engine

The primary function of the quality of service engine is to deliver a robust communication

channel between the audio transmitter and audio receiver in an audio streaming application.

Several data streams with different properties are handled. The available bandwidth is

shared between audio data, service data and remote data.

Data integrity is ensured through a number of RF protocol features:

1. Packets of data are sent in frames and integrity of each packet is ensured as every

packet has a complete build of RF address, payload and CRC.

2. Packets that are lost or received with errors are handled by the error correction level

of the quality of service engine; a two way, acknowledge protocol:

When a packet is received by ARX, it’s registered and CRC is checked.

After ARX has received a frame it sends a packet back to ATX

acknowledging the packets that where successfully transferred. Packets lost

or received with errors will be re-sent from ATX in the next frame.

3. Finally the information (audio data ) is spread over the 2.4 GHz band by use of an

adaptive frequency hopping algorithm. Through this a nRF24Z1 link can handle RF

propagation challenges like reflections and multi-path fading and not least avoid

Page 17

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

heavily trafficked areas of the 2.4 GHz band. The 2.4 GHz band is a world wide

open RF band and co-existence with RF systems such as Bluetooth, ZigBee,

WLAN/WiFi as well as other nRF applications, is increasingly important.

nRF24Z1 constantly monitors the quality of the RF link and numbers indicating total link

quality are available for external control devices in registers. nRF24Z1 can also be set to

interrupt external controller devices upon poor link quality before RF link is lost. An

external controller device can hence take further actions to improve link quality or warn

end user if RF link margins are poor.

The secondary function of the QoS module is to run a link initialization algorithm which

manages initial connect and re-connect if link is lost (ex: out of range) between paired

nRF24Z1’s. Several schemes are available to enable nRF24Z1 connection without end user

involvement.

4.3.4 Audio compression / Decompression

Default operation for nRF24Z1 is streaming of uncompressed audio, however there is some

optional low delay audio compression options available. This function can be enabled by

the user to conserve power or to increase the dynamic range with a constant signal to noise

ratio for 24-bit input signals.

4.3.5 Power

The power section of nRF24Z1 offers linear regulated supply to all internal parts of the

device. This makes the device very robust towards external voltage supply noise and

isolates (audio) devices in an application from noise generated the nRF24Z1.

4.3.6 IREF / RESET

The IREF pin sets up the bias reference for the nRF24Z1 by use of an external resistor.

Pulling IREF to VDD will reset the device. When IREF pin is released, nRF24Z1 runs a

full configuration procedure.

Page 18

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

5 OPERATION OVERVIEW

5.1 Power on / RESET sequence

When supply is applied, nRF24Z1 goes into power on reset. The reset is held until supply

voltage is kept above minimum supply voltage for a few milliseconds. Pulling IREF to

VDD will also put the device into reset.

When reset (power on or IREF high) is released the device needs to be configured. There

are 2 ways nRF24Z1 can be configured:

1. After reset nRF24Z1 will look for an external EEPROM/FLASH memory on the SPI

master interface. If such a memory is present, configuration data is loaded, which

means that all registers values are read from the external memory. If no memory is

present on the SPI master interface, the procedure is repeated on the 2-wire master

interface. These data will override any initial content of nRF24Z1 registers.

2. If no external memory is present:

For both ATX and ARX an external micro processor must configure the nRF24Z1

through the slave SPI or 2-wire serial interface, otherwise hard coded initial register

content is used.

NOTE:

A combination of the two power-up sequences may well be used. One likely

scenario is that ATX is configured by external MCU and ARX is configured from

an external EEPROM/FLASH memory.

nRF24Z1 will now start a link initialization procedure based on the link configuration data.

The value of the MODE pin determines whether it will be in ATX or ARX mode.

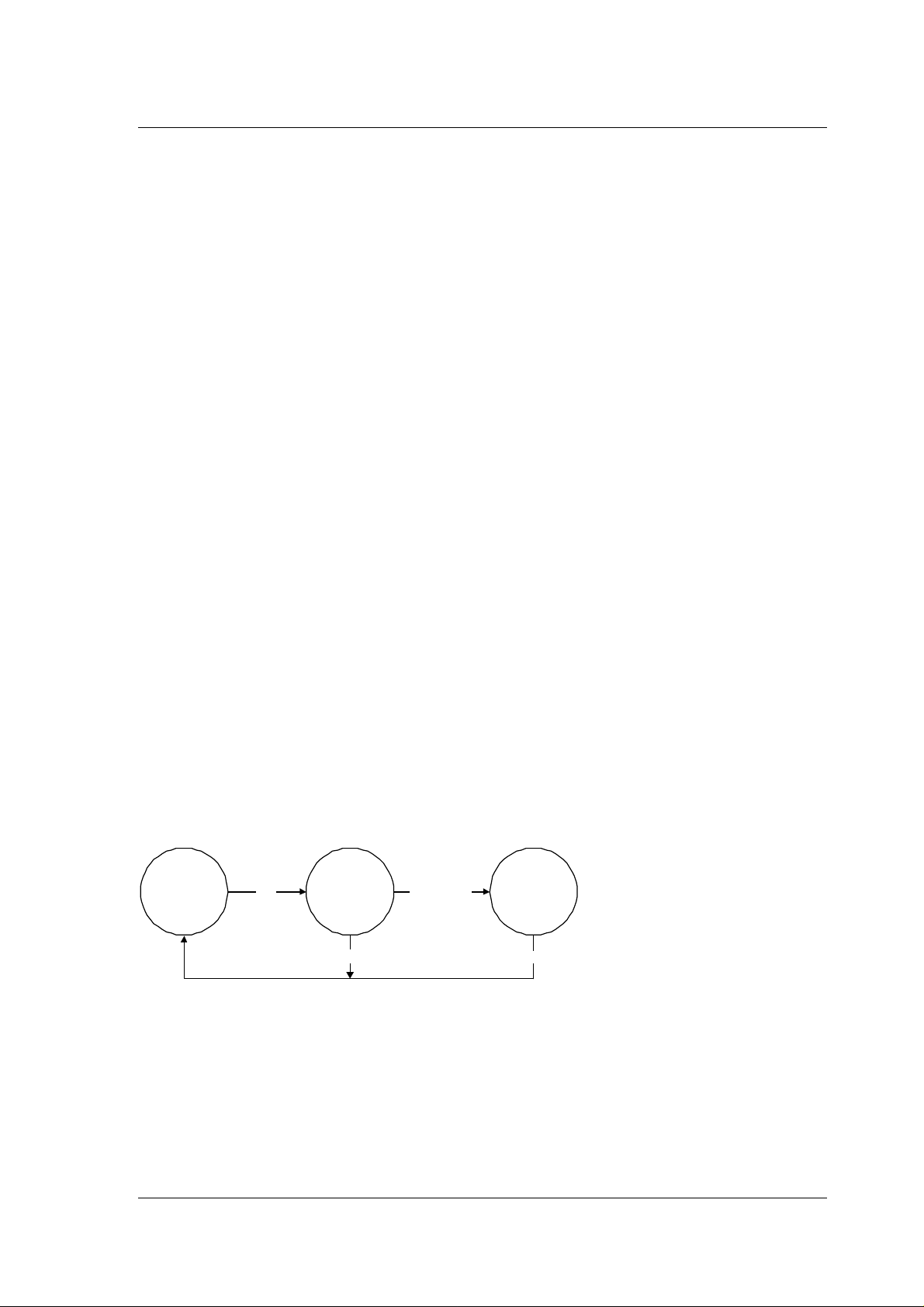

5.2 RF Link initialization

Link-locate Synchronization IdleLink Synchronized

Link -lost Link-lost

Figure 5-1 : link initialisation algorithm

5.2.1 Idle state

The nRF24Z1 link initialsation algorithm will be in its idle state when a link is established,

and the channel hopping engine is initiated and synchronized.

Page 19

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

5.2.2 Link-locate state

When the link between ATX and ARX is broken, a special link-locate routine is initiated

on both sides to establish a new link, see Figure 5-1. During initialization nRF24Z1

derives a set of channels from register CHP1, CHP2 and CHP3, which will be used during

channel hopping in idle state. These channels are also utilized by the link-locate routine

when acquiring a feasible startup channel for the new link.

- Link-locate on ATX

ATX tries to establish a link with ARX by iteratively sending short search packages on all

available channels until acknowledge is received from ARX. ATX will send one package

on each channel and wait for acknowledge for a specific time which is long enough to

secure that ARX has time to respond. The accumulated time used by ATX while looping

through all available channels is here defined as the ATX-loop-time. After receiving an

acknowledge package from ARX, ATX will enter the synchronization state as described in

Figure 5-1.

- Link-locate on ARX

ARX tries to establish a link with ATX by listening for incoming search packages on all

available channels until such is received. When a search package is received, ARX will

proceed by sending one acknowledge package to confirm a feasible link. ARX will listen

for incoming search packages on each channel for a fixed time which is larger than the

ATX-loop-time, which will guarantee at least one search package to get through on each

available channel used by ARX, as long as this channel is not being occupied by another

radio device. After sending the acknowledge package, ARX will enter the synchronization

state.

5.2.3 Synchronization state

This state takes care of synchronizing the channel hopping engine on ATX and ARX, to

secure that both parts follows the same hopping sequence. ATX takes initiative for starting

the channel hopping engine, by sending a start condition to ARX about when to start

hopping. Which channel to start from is implicitly found during the link-locate state.

5.3 Audio streaming

The audio data fed to the audio interfaces on a nRF24Z1 in ATX mode can be of a number

of common digital audio stream formats :

I2S (audio serial) interface:

• left justified, I2S and right justified

S/PDIF interface:

• Consumer Linear PCM Audio described in IEC 60958-3. nRF24Z1 has a single

ended CMOS interface, so to fulfil the electrical requirements external adaptation

circuitry is needed.

Page 20

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

• Non-Linear PCM Audio. As described in IEC 61937-1 (General) and IEC 61937-2

(Burst-info). The nRF24Z1 is transparent to the specific audio compression

algorithms used, so it covers all the described formats in IEC 61937-3 to 61937-7.

In ATX the audio stream formats are converted to the nRF24Z1 RF protocol and

transferred over the air.

In the ARX the data are validated and converted back to audio stream format and fed to the

corresponding audio output interface.

5.4 Audio receiver clock rate recovery

In all RF systems streaming ‘true time’ data, maintaining equal datarates on both sides of

RF link, is a big challenge. In other words; keeping the master clock (MCLK) for the DAC

on the receiving side, equal to the clock used to feed data into the RF device on the

transmitter side.

If these two clocks are not equal the receiving end will either run out of samples for the

DAC or overflow hence need to skip some.

Usually this problem is solved by use of very thigh tolerance crystals (expensive) or

extensive digital filtering (high current consumption) only masking or interpolating the bits

missing in the stream.

nRF24Z1 solves this problem without tight tolerance crystal or extensive digital filtering.

As long as the nRF24Z1 quality of service engine is able to maintain a RF link, the ARX

(audio receiver) locks its master clock output (MCLK) to the speed the audio stream

actually is fed into the ATX on. The MCLK signal on the ARX side is hence locked to the

reference (crystal) of the device (DSP, MCU, DECODER) feeding the audio data to the

ATX and not the crystal of the nRF24Z1 devices (ATX or ARX) themselves.

One exception; if the MCLK output option is used in audio transmitter (clocking an

external ADC for instance) the crystal on the nRF24Z1 in ATX mode is the reference for

the audio speed on the entire nRF24Z1 link.

This offers the end application a true loss less audio channel.

5.5 Data link

There is a 2-way, low bit rate, robust, control and data link running in parallel with the

audio stream. This data link is a part of the quality of service overhead, i.e. difference

between on the air data rate (4 MBit/s) and audio data rate 1.5 MBit/s. Data link rate can

hence not be traded for higher audio data rate. The functionality of the control and data link

is illustrated in Figure 5-2.

Page 21

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

DD[2:0]

SPI / 2-wire

slave

nRF24Z1

ATX mode

nRF24Z1

ARX mode

DI[3:0]

DO[3:0]

SPI / 2-wire

master

1: Data for the ARX are

fed to the ATX via

general purpose inputs or

one of the serial slave

interfaces

RXDCMD

RXWCNT

RXRCNT

RXWBUF

RXRBUF

RXEXEC

2: The ATX serial slave

interfaces gives access

to all ATX registers.

3: A sub set of the ATX

registers and the input

pin status are transferred

by RF between two

linked nRF24Z1

RXDCMD

RXWCNT

RXRCNT

RXWBUF

RXRBUF

RXEXEC

4: Resulting in a

mirror of these ATX

registers on the ARX

side. The mirrored

registers access all

ARX RF and audio

config plus digital I/O

controls and I/O

data.

5: Command register

contents (like in RXDCMD)

dictates the actions to take

place on the ARX GPIO

pins and serial master

interfaces.

Input status of general

purpose input pins (DI[3:0])

are similarly fed back to

ATX.

Figure 5-2 nRF24Z1 control and data link

Through the control and data link the ATX has full control over all registers related to ARX

configuration and can access ARX GPIO (for LED’s etc.) and the ARX 2-wire and SPI

master interface for configuring of DAC’s, volume control and other peripheral functions.

5.6 Power down mode

nRF24Z1 has a power saving mode called “Power down”. In this mode, the quality of

service engine is shut down, and only a low frequency oscillator and some timers are

running. The power down mode can be left upon sleep timer time out or on external pin

event. The ATX and ARX will now go up and start the link initialization routine as

described in section 5.2. The sleep timers also enable the nRF24Z1 to shut down again if

no counterpart is found on the air or no audio input is detected. ARX may also be put in

and out of power down mode by toggling a pin.

Page 22

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

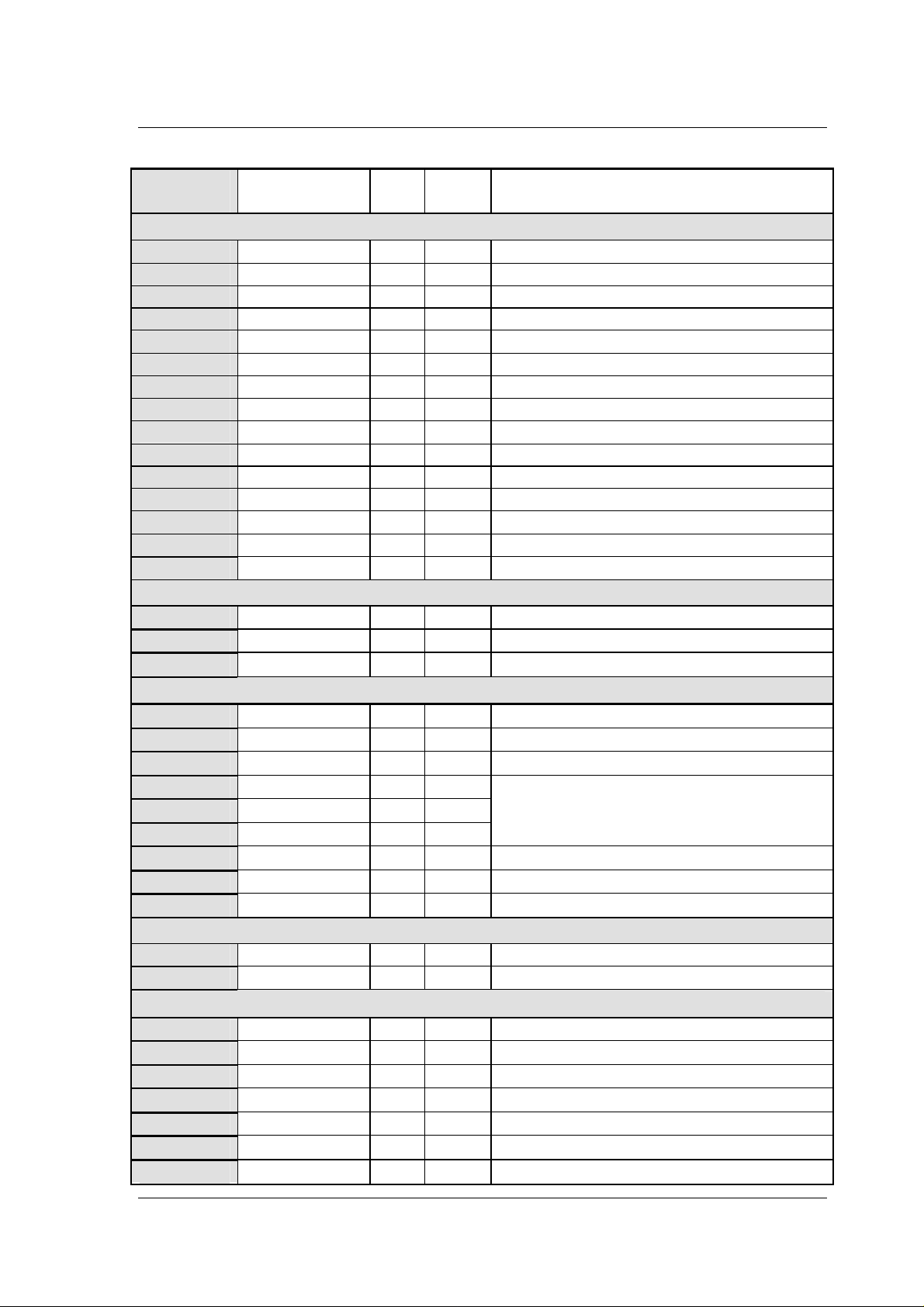

6 NRF24Z1 REGISTER MAP

nRF24Z1 contains several control and status registers, which are listed in the table below.

The registers may be accessed by an external MCU via the (SPI or 2-wire) slave interface.

The registers are organized functinally into 6 groups; ATX , Link and ARX control and

tatus, and Data link. All registers are present both in audio transmitter and audio receiver.

The intial value of all registers is read from EEPROM (if present) immediately after reset,

othervise the initial values in Table 6-1 applies.

6.1 Access from audio transmitter side

If a MCU on the audio transmitter side writes to a register, the audio transmitter version of

the register is written, and registers TXCSTATE, LNKCSTATE, RXCSTAT, RXEXEC

controls whether also the audio receiver version of the register is written via the data link.

• If it is a ATX control register, register TXCSTATE controls if also the audio

receiver version of the register is written via the data link

• If it is a Link control register, register LNKCSTATE controls if also the

audio receiver version of the register is written via the data link

• If it is a ARX control register, register RXCSTATE controls if also the

audio receiver version of the register is written via the data link

See ch. 12 for details about how control registers are updated via the data link, and Table

7-10 about data link registers.

A MCU on the audio transmitter side can read all registers on its side, plus the Link status,

ARX status and data link registers, which are read from audio receiver via the data link.

6.2 Access from audio receiver side

If a MCU on the audio receiver side writes to a register, only the audio receiver version of

the register is written, and it is not sent via the data link to the audio transmitter. Which

implies that a MCU on audio transmitter will not know about it, but as mentioned above,

ATX MCU may read status registers via the link anytime. A MCU on the audio receiver

side can read all registers on its side, but it cannot read anything via the link. In brief ARX

MCU only has local access, while ATX MCU controls the data link.

Page 23

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

Address

Hex

Register R/W Initial

Hex

Description

ATX registers

0x01 TXSTA R 0x40 Table 7-4, page 28

0x20 TXDD R 0x00 Table 7-15, page 40

0x02 INTSTA R 0x00 Table 9-1, page 54

0x1A TXMOD R/W 0x01 Table 7-6, page 29

0x11 TXFMT R/W 0x00 Table 7-5, page 28

0x12 TXLAT R/W 0x00 Table 8-6, page 53

0x13 INTCF R/W 0x00 Table 9-1, page 54

0x14 I2SCNF_IN R/W 0x00 Table 7-6, page 29

0x15 I2SRAT R/W 0x00 Table 7-7, page 30

0x16 TXPWR R/W 0x03 page 53

0x17 TXSTI[0] R/W 0x00 page 58

0x18 TXSTI[1] R/W 0x00 page 58

0x19 TXWTI R/W 0x00 page 58

0x10 TXRESO R/W 0x00 page 55

0x1B TXCSTATE R/W 0x00 page 60

LINK status registers

0x03 LNKSTA R 0x00 page 52

0x04 LNKQ R 0x00 page 51

0x05 LNKERR R 0x00 page 51

LINK control registers

0x30 LNKMOD R/W 0x00 page 52

0x31 LNKWTH R/W 0xff page 51

0x32 LNKETH R/W 0xff page 51

0x35 CHP1 R/W 0x01

0x36 CHP2 R/W 0x12

0x37 CHP3 R/W 0x05

0x38 ALEN R/W 0x05 page 48

0x39 -0x3D ADDR[0:4] R/W 0x01 page 49

0x3E LNKCSTATE R/W 0x00 page 60

page 49

ARX status registers

0x06 RXSTA R 0x00 page 42

0x07 RXPIN R 0x00 Table 7-22, page 45

ARX control registers

0x4A RXMOD R/W 0x00 Table 7-8, page 31

0x41 RXPIO R/W 0x00 Table 7-20, page 44

0x42 RXPWME R/W 0x00 Table 7-21, page 44

0x43 RXPWMD R/W 0x00 Table 7-21, page 44

0x44 I2SCNF_OUT R/W 0x00 Table 7-8, page 31

0x45 RXWAKE R/W 0x28 page 57

0x49 RXPWR R/W 0x00 page 53

Page 24

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

0x46 RXSTI[0] R/W 0x00 page 58

0x47 RXSTI[1] R/W 0x00 page 58

0x48 RXWTI R/W 0x00 page 58

0x40 RXRESO R/W 0x00 page 55

0x4B RXCSTATE R/W 0x00 page 60

Data link registers

0x70 RXDCMD R/W 0x82 Table 7-10, page 34

0x71 RXWCNT R/W 0x00

0x72 RXRCNT R/W 0x00

0x50-0x5f RXWBUF W 0x00

0x60-0x6f RXRBUF R 0x00

0x74 RXEXEC W/R 0x00

Table 6-1 nRF24Z1 register listing

In the following chapters, the nRF24Z1 registers are described sorted by function.

Table 7-11, page 35

Page 25

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

7 DIGITAL I/O

This section describes the digital I/O pins, control registers and important interface timing

of the nRF24Z1.

The digital I/O pins of the nRF24Z1 are divided into three groups:

1. Audio interfaces

2. Serial master interfaces

3. Control and GPIO interfaces

7.1 Digital I/O behaviour during RESET

During reset all digital pins, except the master SPI interface output pins, are set as inputs to

avoid driving conflicts. The master SPI pins MCSN, MSCK and MMOSI are set to output

high, that is, in inactive SPI state, ready to read EEPROM configuration data, which is the

first thing to happen after reset. All pins will remain in their respective direction until one

of the configuration read routines described in section 5.1 is finished, and thereafter I/O

pins are set according to new configuration data.

7.2 Audio interfaces

The audio interface group are defined as the I2S and S/PDIF interfaces plus the MCLK and

REQ pins.

Pin name Function

CLK bit clock

WS word sync clock

DATA audio data

MCLK 256 * audio fundamental sample rate output, see Table 7-4 .

REQ data request, used for burst type data, see Table 7-7.

SPDIO S/PDIF serial in- or output, see ch. 7.4.

Table 7-1 serial audio port pins

7.3 I2S Audio Interface

nRF24Z1 has a three-wire serial audio port which can be configured to be compatible with

different serial audio formats. In ATX mode, the audio port is in slave (receive) mode. In

ARX mode, the audio port is in master (transmit) mode. The audio port consists altogether

of 6 pins, see Table 7-1.

Page 26

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

Figure 7-1 : some serial audio formats

audio format I2SCNF[3:0] value

Left justified 0xA

I2S 0x0

Right Justified 0xB

Table 7-2 : Example of I2SCNF setting for some common serial audio formats , applies to

both I2SCNF_IN and I2SCNF_OUT registers.

See also Table 7-7 and Table 7-8.

7.4 S/PDIF Audio Interface

nRF24Z1 supports the following formats of the S/PDIF interface:

• Consumer Linear PCM Audio described in IEC 60958-3. nRF24Z1 has a single

ended CMOS interface, so to fulfil the electrical requirements external adaptation

circuitry is needed.

• Non-Linear PCM Audio, as described in IEC 61937-1 (General) and IEC 61937-2

(Burst-info). nRF24Z1 is transparent to the specific audio compression algorithms

used, it just transfers what comes in on the input side to the receiver side. Except

that only the 32 first bits of channel status information bits are transferred, and no

user data bits.

Page 27

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

Only one of the audio interfaces can be active at one time. The active audio interface for

ATX is chosen by bit 2 in register TXMOD (0= I2S is default, see Table 7-16), and for

ARX by bit 2 in register RXMOD.

7.5 Audio interface functionality

The functionality and direction of the pins in the audio interfaces are listed in Table 7-3.

MODE=0 (ARX) MODE =1 (ATX) nRF24Z1 Audio

interfaces

Pin # Pin

name

9 REQ REQ IN X IN REQ OUT X OUT

10 CLK CLK OUT X IN CLK IN X IN

11 WS WS OUT X IN WS IN X IN

12 DATA DATA OUT X IN DATA IN X IN

13 SPDIO

14 MCLK MCLK OUT X OUT MCLK OUT X OUT

TXMOD[2]=0

(I2S)

Function Direction Function Direction Function Direction Function Direction

X IN X IN

RESET* OUT

TXMOD[2]=1

(S/PDIF)

SPDIO OUT

TXMOD[2]=0

(I2S)

RESET* OUT

TXMOD[2]=1

(S/PDIF)

SPDIO IN

Table 7-3 Audio interface pin functions

* If S/PDIF is not used for audio, the SPDIO pin can be used as RESET (output) to external devices. Please see chapter 10 for further

details.

7.5.1 ATX audio interface control

The nRF24Z1 in ATX mode automatically detects the rate of a digital audio stream from an

external master both on the I2S and S/PDIF interface. Register 0x01 holds the status of this

detection for optional read back to an external MCU.

Page 28

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

Address

Hex

Register R/W Initial

Hex

Description

0x01 TXSTA R 0x40 Audio transmitter status register

Bit Interpretation

7 Reserved

6:5

Detected audio scale factor (I2S only)

00 0.25

01 0.5

10 1

11 2 1

4:3

Detected audio fundamental rate

00 48 kHz

01 44.1 kHz

10 32 kHz

11 Illegal or no input detected

2:0 Audio transmitter state (TBD)

Table 7-4 Audio input status

Default nRF24Z1 transfers uncompressed audio, but it has some options to transfer

companded audio data. This can be used to save power, or to accommodate transfer of 24

bit audio, which uncompanded would exceed the radio bandwidth. This is a lossy

compression/decompresion in the way that superfluous LSB's are lost. Here is an example

of how 24 to 16 bit compand works:

If the sample values within an audio frame are within +/- 200000, 3 LSB are cut, and if

sample values of the next frame is within +/- 60000, only 1 LSB is lost. So the number of

LSB lost varies dynamically with maximum sample value for each frame, and this limits

the relative error.

Address

Hex

Register R/W Initial

Hex

Description

0x11 TXFMT R/W 0x00 Transmit data format

Value Interpretation

0 16 bit linear PCM

1 24 bit linear companded to 16 bit

2 Reserved

4 16 bit linear companded to 8 bit

Table 7-5 : register TXFMT.

1

For 2x rate (96 kHz) every second sample is discarded in ATX, and in ARX the remaining samples are

output at 1x rate.

Page 29

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

The Audio interfaces in ATX mode are controlled by registers 0x1A (Bit[4], Bit[2:0]) and

0X14 listed in Table 7-5.

Address

Hex

0x1A TXMOD R/W 0x00 Operation modes for audio transmitter

0x14 I2SCNF_IN R/W 0x00 I2S interface configuration (on ATX side), see

Table 7-6 ATX audio input control

Register R/W Initial

Hex

Description

7 RF transmitter enable

6 Audio transmitter power down

5 Enable wakeup on changing DD[1]

4 REQ pin polarity (0 for active low)

3 Enable direct data from pins

DD[2:0].

DD[2] is only available if SSEL=1

2 S/PDIF enable (default input is I2S)

1:0

MCLK output control**

00 MCLK off (logic 0)

01 Output 256 x 48 kHz

10 Output 256 x 44.1 kHz

11 Output 256 x 32 kHz

also Table 7-2

7 Data enable

0 I2S carries sound

1 I2S carries data

6 Reserved, MBZ

3 WS Polarity

0 WS=0: Left sample (std)

1 WS=1: Left sample

2 Data to Bit Clock relation

(data valid at clock edge)

0 Rising Edge (standard)

1 Illegal

1 WS to MSB delay

0 1 clock cycle (standard)

1 0 clock cycles

0 Audio word justification

0 Left justified

1 Right justified

**IMPORTANT NOTE!

For S/PDIF audio input, MCLK output is disabled, but the MCLK control value TXMOD[1:0] should

generally be set to the expected sampling rate. This is mandatory if 32 kHz sampling rate is expected, and

recommended otherwise. Setting MCLK to the expected sampling rate gives the best phase margin and hence

sampling quality when the input S/PDIF signal has much jitter.

Page 30

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

To pace I2S data a REQ output signal is used. Polarity is set in TXMOD[4]. In I2S data

mode (I2SCNF_IN7=1) I2S DATA and CLK input must be stopped within 32 CLK cycles

when REQ goes inactive, and must start again when REQ goes active.

For analog audio sources, the nRF24Z1 offers a 256x clock output on pin MCLK

(TXMOD[1:0]). This clock can be used as system clock for an external stereo ADC.

If I2S is used for data transfers (I2SCNF_IN[7] = 1), average data rate is set in register

0x15

Address

Hex

0x15 I2SRAT R/W 0x00 I2S interface speed for digital input streams that

Register R/W Initial

Hex

Description

are not interpreted as audio by nRF24Z1.

n (dec) Digital stream

0 8 kbit/s

1 16 kbit/s

2-190 (n+1)*8 kbit/s

191 1536kbit/s

>191 Illegal

Table 7-7 ATX I2S data transfer control

7.5.2 ARX audio interface control

In ARX mode the audio interfaces are controlled by the registers 0x4A and 0x44 listed in

Table 7-8.

Page 31

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

Address

Hex

0x4A RXMOD R/W 0x00 Set operation modes for audio receiver

0x44 I2SCNF_OUT R/W 0x00 I2S interface configuration for audio output (on

Register R/W Initial

Hex

Description

Bit Interpretation

7 Receiver power down

6 Reserved, MBZ

5 RF receiver enable

4 REQ pin polarity

3 Reserved, MBZ

2 S/PDIF enable

1:0 Reserved, MBZ

ARX side), see also Table 7-2

Bit Interpretation

7 Reserved, MBZ

6 Mute sound output

5:4 Sample length

00 16-bit samples

01 reserved

10 24-bit samples

11 reserved

3 WS Polarity

0 WS=0: Left sample (std)

1 WS=1: Left sample

2 Data to Bit Clock relation

(data valid at clock edge)

0 Rising edge (standard)

1 Falling edge

1 WS to MSB delay

0 1 clock cycle (standard)

1 0 clock cycles

0 Audio word justification

0 Left justified

1 Right justified

Table 7-8 ARX audio interface control registers

In I2S data mode (I2SCNF_IN7=1) I2S DATA and CLK out will be stopped within 32

CLK cycles when REQ input goes inactive, and will start again when REQ goes active.

NOTE:

After reset, the ARX registers can be accessed by the audio transmitter (nRF24Z1 in

ATX mode) through the control and data channel set up between two linked

nRF24Z1.

Page 32

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

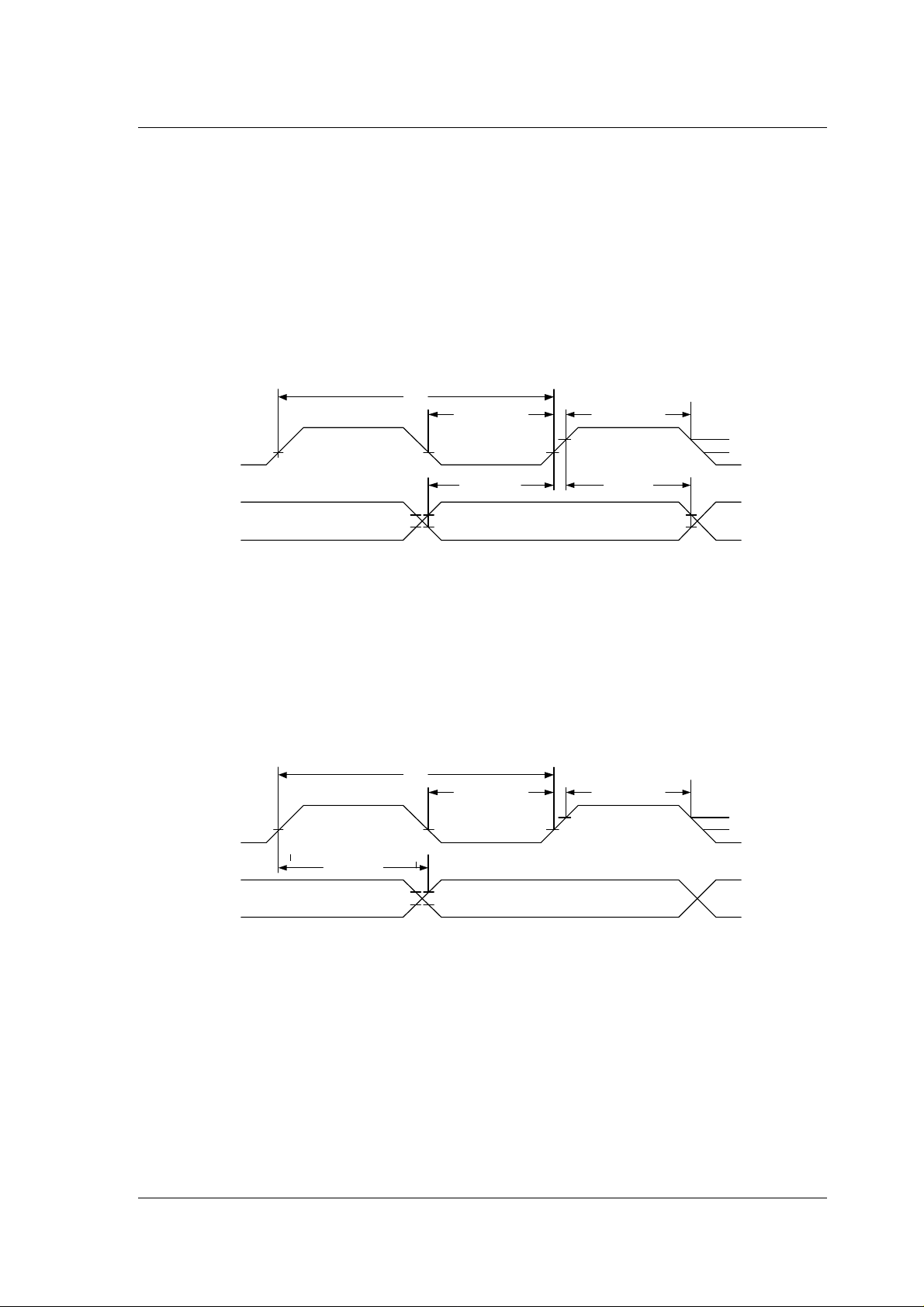

7.5.3 I2S Audio interface timing

I2S input (ATX) timing

The I2S input protocol is configurable to handle several I2S formats. In addition, the

interface will automatically detect sample size and word length for the most common

formats. This section shows the detailed bit, clock and word timing requirements.

T

I2S

CLK

DATA

and

WS

T

I2S

= clock period

t

hI2S

= hold time I2S receiver

t

sI2S

= setup time I2S receiver

Figure 7-2. Timing for I2S input on nRF24Z1, for values see Table 13-1

I2S output (ARX) timing

I2S output is protocol compatible with most I2S DACs and CODECs.

T

I2S

CLK

>= 0.35T

t

sI2S

>= 0.35T

I2S

I2S

>= 0.35T

t

hI2S

>= 0.35T

I2S

VH = 2.0V

VL = 0.8V

I2S

VH = 2.0V

VL = 0.8V

t

dI2S

DATA

and

WS

T

I2S

= clock perod

t

dI2S

= delay I2S transmitter

Figure 7-3. Timing for I2S output of nRF24Z1, for values see Table 13-1

Page 33

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

7.6 Serial master interfaces

The nRF24Z1 serial master interfaces group contains a SPI and a 2-wire master interface

available at all times.

After RESET the nRF24Z1 will look for a serial memory on the SPI master interface. If no

memory is present, the process is repeated on the 2-wire interface. If no memories is found

an nRF24Z1 assumes an external microcontroller will configure it over one of the slave

control interfaces and will hence be idle until that happens. Link initialization will start as

soon as the necessary control register bits are set.

During the configuration the SPI master is operated at 1MHz or 0.5MHz. SPI format is

CPOL=0, CHPA=0 as used by industry standard EEPROM/FLASH memories.

The nRF24Z1 is protocol comp atible with SPI memory with sizes ranging from 1 Kbyte to

64 Kbytes with 16-bit sub-address used.

The slave(s) that are connected determines the protocol on the 2-wire master interface. For

the case of configuration, nRF24Z1 is protocol compatible with “industry standard” 2-wire

memory with sizes ranging from 128 bytes to 4 Kbytes (with 3 address pins and one byte

sub-address used). During configuration this interface is operated at 100 kHz for

compatibility with most serial 2-wire memories.

The pin out and functionality of the serial master I/O pins are shown in Table 7-9.

ARX mode ATX mode nRF24Z1

I/O:

serial

masters

pin name

27 MSDA MSDA IN/OUT

28 MSCL MSCL OUT X IN X IN MSCL OUT

29 MSCN X IN MSCN OUT MSCN OUT X IN

30 MMISO X IN MMISO IN MMISO IN X IN

31 MMOSI

35 MSCK X IN MSCK OUT MSCK OUT X IN

MODE=0

RXDCMD[7] = 0

Functio

n Direction Function Direction Function Direction Function Direction

X IN X IN

RESET

* OUT MMOSI OUT MMOSI OUT RESET* OUT

MODE=0

RXDCMD[7] = 1

X IN X IN

RESET* OUT RESET* OUT

MODE=1

and EEPROM

connected to SPI

MODE =1

and EEPROM

connected to 2 wire

MSDA IN/OUT

Table 7-9 Serial masters functionality

* A pin in the serial interface that is NOT used for external memory and/or controlling external circuitry can be

configured to act as reset for external devices such an ADC or DAC. Please refer to chapter 10 for further details.

After configuration, the master interfaces in ATX go idle with pins still active, while the

interfaces in ARX become an extended arm of a linked ATX through the control channel

between two nRF24Z1.

The set-up of the serial master interfaces of the ARX after configuration is loaded is

controlled by register RXDCMD (0x70) as shown in Table 7-10.

Page 34

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

Address

Hex

0x70 RXDCMD R/W 0x82 Data “command”. Specifies interface and speed

Register R/W Initial

Hex

Description

Bit Interpretation

7 Interface select

0 Use ARX 2-wire interface

1 Use ARX SPI interface

6:4 SPI slave select control. Set which

signal to be used as slave select, and

associated polarity. Or 2-wire access

type.

Value SPI interpretation

000 CSN, active low2

001 DO[0], active low1

010 DO[1], active low1

011 DO[2], active low1

100 CSN, active low2

101 DO[0], active high1

110 DO[1], active high1

111 DO[2], active high1

Value 2-wire interpretation

000 start stop access

001 start only access (a start

only access followed by a

start-stop access will be a

start-start-stop access)

Notes:

1. In order to use any of DO[2:0] as SPI slave

selects, the corresponding bit in RXPIO

should be set to the SPI slave select

inactive state. I.e. if DO[0] is to be used as

active low slave select, RXPIO[0] must be

set to 1.

2. MCSN is always active low

3:1 Speed select

Value

(bin)

SPI

Interpretation

2-wire

Interpretation

000 8 Mbit/s Illegal

001 8 Mbit/s 100 kbit/s

010 4 Mbit/s 400 kbit/s

011 2 Mbit/s 1 Mbit/s

100 1 Mbit/s Illegal

101 500 kbit/s Illegal

110 250 kbit/s Illegal

111 Reserved Reserved

0 Reserved, MBZ.

Table 7-10 RXDCMD register

Page 35

PRELIMINARY PRODUCT SPECIFICATION

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

Number of bytes data to read/write is set in ‘write and read count’ registers RXWCNT

(0x71) and RXRCNT (0x72) and the actual data are transferred through the data buffers

RXWBUF and RXRBUF. Once the above registers are set, writing to RXEXEC will

initiate a SPI or 2-wire operation on the ARX serial master interfaces. Operation finished is

also reported in RXEXEC and can be coupled to an interrupt in the ATX. See also Figure

5-2 nRF24Z1 control and data link

Remember that all interaction with these registers is done through the slave interfaces on

the ATX. The data in RXWBUF are transferred to the ARX via RF and the interactions are

carried out on the ARX side as configured in RXDCMD. Once it is completed and data

read by the ARX is transferred back to the ATX, the ‘operation finished’ interrupt (flag

INTSTA.4) is set and data read on the ARX side are available in RXRBUF.

Address

Hex

0x71 RXWCNT R/W 0x00 Number of bytes to write (max 16)

0x72 RXRCNT R/W 0x00 Number of bytes to read (max 16)

0x500x5f

0x600x6f

0x74 RXEXEC W/R 0x00 Write to this register will execute a command on

Register R/W Initial

Hex

Description

RXWBUF W 0x00 Data to be written to the interface specified by

RXDCMD

RXRBUF R 0x00 Data read from audio receiver on the interface

specified by RXDCMD

the audio receiver. The interface and speed are

specified by RXDCMD. The audio receiver will

first write RXWCNT bytes from RXWBUF to

the selected interface, then read RXRCNT bytes

and transmit back to be stored in RXRBUF. An

interrupt may be delivered upon successful

completion of the command.

0= idle; 1=write or read

MCU must set RXEXEC=1 to perform

command, and can thereafter read RXEXEC to

find if command is finished (idle)

Table 7-11 ARX master data registers

Page 36

PRELIMINARY PRODUCT SPECIFICATION

1-789

1-789

8

9

SUNSTAR单片机专用电路 http://www.icasic.com/ TEL: 0755-83387030 FAX:0755-83376182 E-MAIL:szss20@163.com

SUNSTAR半导体集成电路 http://www.icasic.com/ TEL: 0755-83387016 FAX:0755-83376182 E-MAIL:szss20@163.com

nRF24Z1 wireless audio streamer

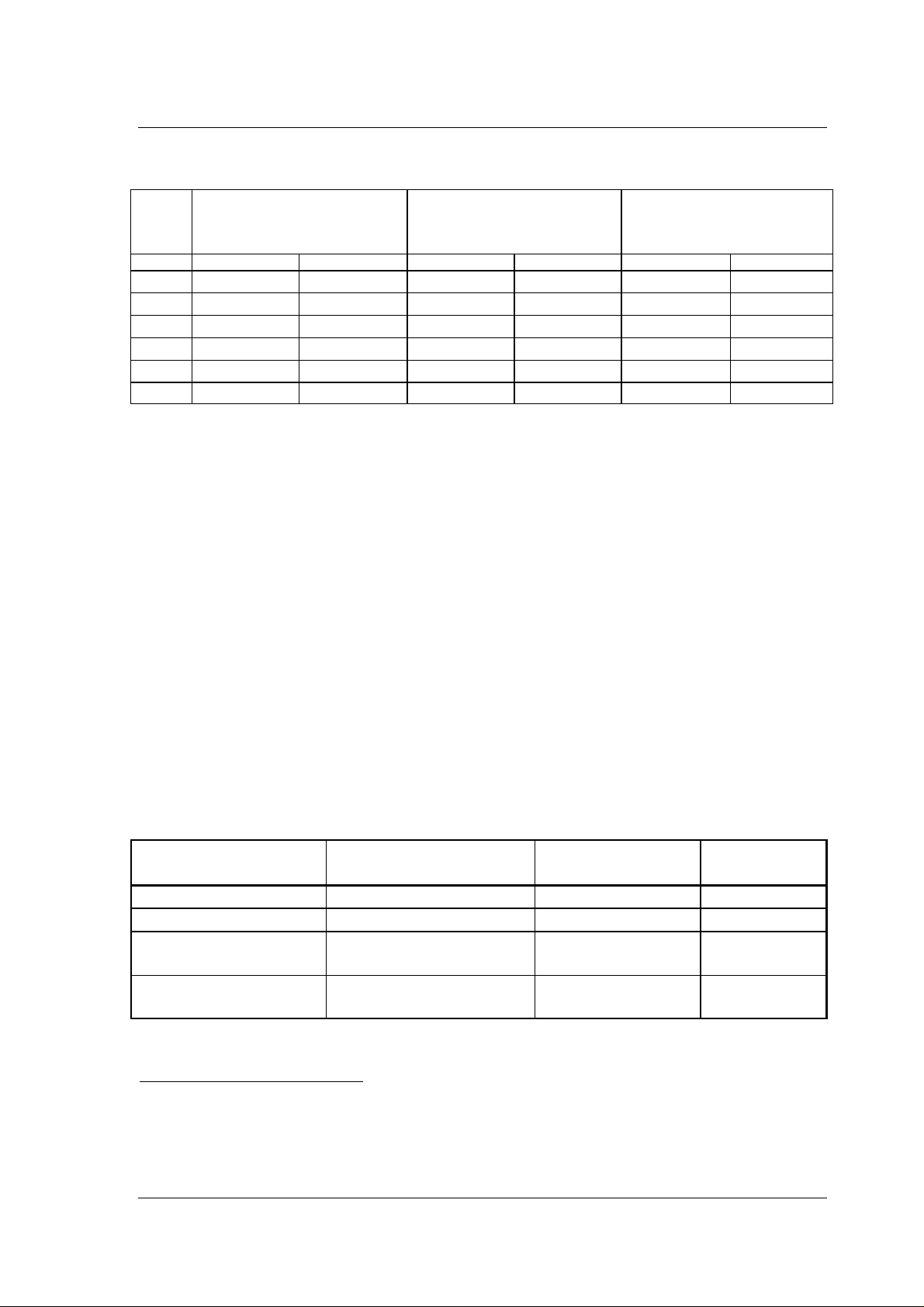

7.6.1 Timing serial master interfaces

SPI master timing

t

MCSN

MSCK

MMOSI

dMSCK

t

dMSPI

MSB LSB

T

MSCK

t

hdMSPI

MMISO

t

suMSPI

MSB LSB

Figure 7-4 : SPI master interface timing, here is shown a one byte transaction.

T

t

t

: MSCK cycle time, as defined by RXDCMD register.

MSCK

: time from MCSN active to first SCK pulse, t

dMSCK

: delay from negedge MSCK to new MMOSI output data

dMSPI

t

: MMISO setup time to posedge MSCK.

suMSPI

t

: MMISO hold time to posedge MSCK.

hdMSPI

dSCK

= T

MSCK

/ 2

for values see Table 13-1

2-wire master timing

START

Condition

SDA

STOP

Condition

SCL

ADDRESS

ACK DATA ACK DATA ACK

R/W

1-7

Figure 7-5 : 2-wire data transfer

Page 37

PRELIMINARY PRODUCT SPECIFICATION

T