Page 1

September 2015 DocID027351 Rev 3 1/100

1

UM1855

User manual

Evaluation board with STM32L476ZGT6 MCU

Introduction

The STM32L476G-EVAL evaluation board is designed as complete demonstration and

development platform for STMicroelectronics ARM

®

Cortex®-M4-core-based

STM32L476ZGT6 microcontroller with three I²C buses, three SPI and six USART ports,

CAN port, SWPMI, two SAI ports, 12-bit ADC, 12-bit DAC, LCD driver, internal 128-Kbyte

SRAM and 1-Mbyte Flash memory, Quad-SPI port, touch sensing capability, USB OTG FS

port, LCD controller, flexible memory controller (FMC), JTAG debug port.

STM32L476G-EVAL, shown in Figure 1

(1)

, can be used as reference design for user

application development, although it is not considered as final application.

A full range of hardware features on the board helps users evaluate all on-board peripherals

such as USB, USART, digital microphones, ADC and DAC, dot-matrix TFT LCD, LCD glass

module, IrDA, LDR, SRAM, NOR Flash memory device, Quad-SPI Flash memory device,

microSD card, sigma-delta modulators, smartcard with SWP, CAN transceiver, EEPROM,

RF-EEPROM. Extension headers allow connecting daughterboards or wrapping boards.

ST-LINK/V2-1 in-circuit debugger and flashing facility is integrated on the mainboard.

Figure 1. STM32L476G-EVAL evaluation board

1. Picture not contractual.

www.st.com

Page 2

Contents UM1855

2/100 DocID027351 Rev 3

Contents

1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.2 Demonstration software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.3 Order code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.4 Unpacking recommendations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2 Hardware layout and configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 ST-LINK/V2-1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.1.1 Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.1.2 ST-LINK/V2-1 firmware upgrade . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.2 ETM Trace . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3 Power supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.1 Supplying the board through ST-LINK/V2-1 USB port . . . . . . . . . . . . . . 15

2.3.2 Using ST-LINK/2-1 along with powering through CN22 power jack . . . 16

2.4 Clock references . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.5 Reset sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.6 Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.6.1 Boot options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.6.2 Bootloader limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.7 Audio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.7.1 Digital microphones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.7.2 Headphones outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.7.3 Limitations in using audio features . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.8 USB OTG FS port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.8.1 STM32L476G-EVAL used as USB device . . . . . . . . . . . . . . . . . . . . . . . 23

2.8.2 STM32L476G-EVAL used as USB host . . . . . . . . . . . . . . . . . . . . . . . . 24

2.8.3 Configuration elements related with USB OTG FS port . . . . . . . . . . . . 24

2.8.4 Limitations in using USB OTG FS port . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.8.5 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.9 RS-232 and IrDA ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.9.1 RS-232 port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.9.2 IrDA port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.9.3 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Page 3

DocID027351 Rev 3 3/100

UM1855 Contents

5

2.9.4 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.10 LPUART port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.11 microSD card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.11.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.11.2 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.12 Motor control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.12.1 Board modifications to enable motor control . . . . . . . . . . . . . . . . . . . . 29

2.12.2 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.13 CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.13.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.13.2 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.14 Extension connectors CN6 and CN7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.15 LCD glass module daughterboard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.15.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.16 TFT LCD panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.17 User LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.18 Physical input devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.18.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.19 Operational amplifier and comparator . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.19.1 Operational amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.19.2 Comparator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.20 Analog input, output, VREF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.21 SRAM device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.21.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.21.2 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.22 NOR Flash memory device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.22.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.22.2 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.23 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.23.1 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.24 RF-EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.25 Quad-SPI Flash memory device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

2.25.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.25.2 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.26 Touch-sensing button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Page 4

Contents UM1855

4/100 DocID027351 Rev 3

2.26.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.27 Smartcard, SWP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.27.1 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.27.2 Operating voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.28 Near-field communication (NFC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.29 Dual-channel sigma-delta modulators STPMS2L . . . . . . . . . . . . . . . . . . 51

2.29.1 STPMS2L presentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.29.2 STPMS2L settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

2.29.3 STPMS2L power metering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

2.29.4 STPMS2L for PT100 measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

2.29.5 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

2.30 STM32L476ZGT6 current consumption measurement . . . . . . . . . . . . . . 54

2.30.1 IDD measurement principle - analog part . . . . . . . . . . . . . . . . . . . . . . . 55

2.30.2 Low-power-mode IDD measurement principle - logic part . . . . . . . . . . . 56

2.30.3 IDD measurement in dynamic run mode . . . . . . . . . . . . . . . . . . . . . . . . 58

2.30.4 Calibration procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

3 Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.1 RS-232 D-sub male connector CN9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.2 Power connector CN22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.3 LCD daughterboard connectors CN11 and CN14 . . . . . . . . . . . . . . . . . . 61

3.4 Extension connectors CN6 and CN7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

3.5 ST-LINK/V2-1 programming connector CN16 . . . . . . . . . . . . . . . . . . . . . 65

3.6 ST-LINK/V2-1 Standard-B USB connector CN17 . . . . . . . . . . . . . . . . . . . 65

3.7 JTAG connector CN15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

3.8 ETM trace debugging connector CN12 . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3.9 microSD card connector CN18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.10 ADC/DAC connector CN8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.11 RF-EEPROM daughterboard connector CN3 . . . . . . . . . . . . . . . . . . . . . 69

3.12 Motor control connector CN2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.13 USB OTG FS Micro-AB connector CN1 . . . . . . . . . . . . . . . . . . . . . . . . . . 70

3.14 CAN D-sub male connector CN5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

3.15 NFC connector CN13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Appendix A Schematic diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Page 5

DocID027351 Rev 3 5/100

UM1855 Contents

5

Appendix B Federal Communications Commission (FCC)

and Industry Canada (IC) Compliance Statements . . . . . . . . . . . . 98

B.1 FCC Compliance Statement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

B.1.1 Part 15.19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

B.1.2 Part 15.105 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

B.1.3 Part 15.21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

B.2 IC Compliance Statement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

B.2.1 Compliance Statement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

B.2.2 Déclaration de conformité. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Page 6

List of tables UM1855

6/100 DocID027351 Rev 3

List of tables

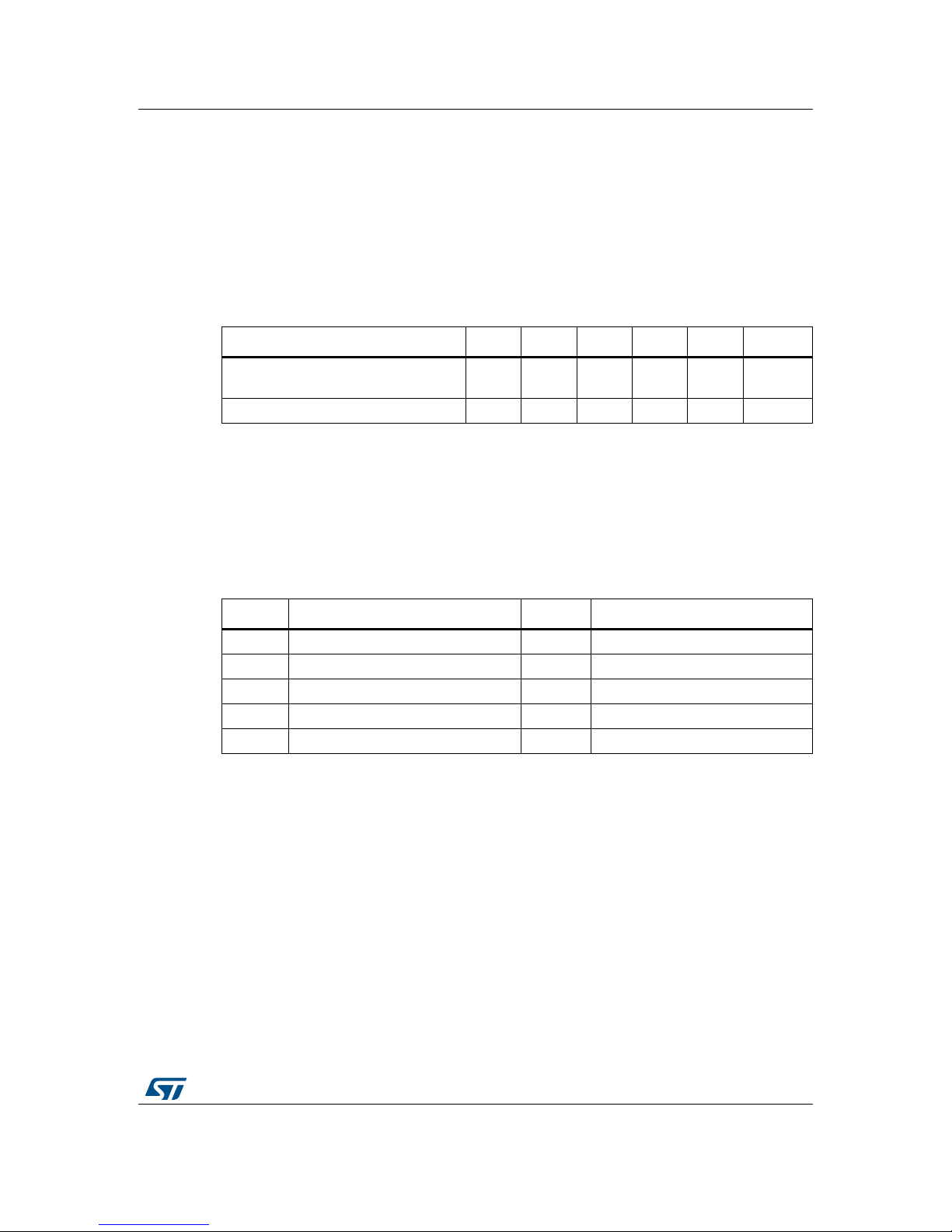

Table 1. Setting of configuration elements for trace connector CN12 . . . . . . . . . . . . . . . . . . . . . . . 14

Table 2. Power-supply-related jumper settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 3. X1-crystal-related solder bridge settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 4. X2-crystal-related solder bridge settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 5. Boot selection switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 6. Bootloader-related jumper setting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 7. Digital microphone-related jumper settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 8. Configuration elements related with USB OTG FS port . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 9. Settings of configuration elements for RS-232 and IrDA ports . . . . . . . . . . . . . . . . . . . . . . 26

Table 10. Hardware settings for LPUART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 11. Terminals of CN18 microSD slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 12. Motor control terminal and function assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 13. CAN related jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 14. LCD-daughterboard-related configuration elements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 15. LCD glass element mapping - segments 0 to 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 16. LCD glass element mapping - segments 10 to 19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 17. LCD glass element mapping - segments 20 to 29 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 18. LCD glass element mapping - segments 30 to 39 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 19. Access to TFT LCD resources with FMC address lines A0 and A1 . . . . . . . . . . . . . . . . . . 39

Table 20. Assignment of CN19 connector terminals of TFT LCD panel. . . . . . . . . . . . . . . . . . . . . . . 39

Table 21. Port assignment for control of LED indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 22. Port assignment for control of physical input devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 23. Setting of jumpers related with potentiometer and LDR . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 24. SRAM chip select configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 25. NOR Flash memory-related configuration elements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 26. Configuration elements related with Quad-SPI device . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 27. Touch-sensing-related configuration elements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 28. Assignment of ports for ST8024CDR control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 29. Configuration elements related with smartcard and SWP . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 30. CN13 NFC connector terminal assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 31. JP11 jumper settings during IDD measurement with calibration . . . . . . . . . . . . . . . . . . . . 59

Table 32. RS-232 D-sub (DE-9M) connector CN9 with HW flow control and ISP support . . . . . . . . . 60

Table 33. CN11 and CN14 daughterboard connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 34. Daughterboard extension connector CN6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 35. Daughterboard extension connector CN7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 36. USB Standard-B connector CN17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 37. JATG debugging connector CN15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 38. Trace debugging connector CN12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 39. microSD card connector CN18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 40. Analog input-output connector CN8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 41. RF-EEPROM daughterboard connector CN3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 42. Motor control connector CN2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 43. USB OTG FS Micro-AB connector CN1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 44. CAN D-sub (DE-9M) 9-pins male connector CN5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 45. NFC CN13 terminal assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 46. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Page 7

DocID027351 Rev 3 7/100

UM1855 List of figures

8

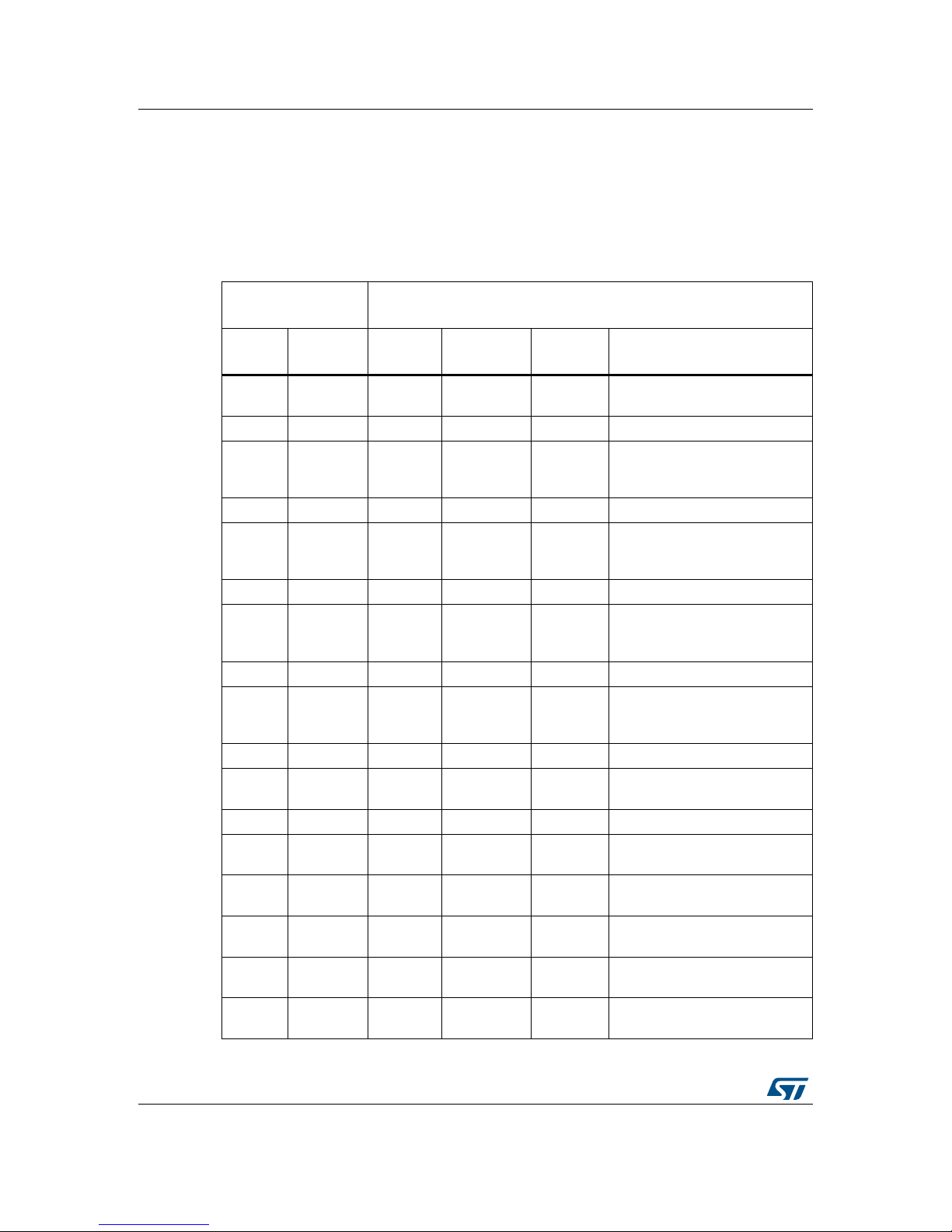

List of figures

Figure 1. STM32L476G-EVAL evaluation board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 2. STM32L476G-EVAL hardware block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 3. STM32L476G-EVAL main component layout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 4. USB Composite device. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 5. CN22 power jack polarity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

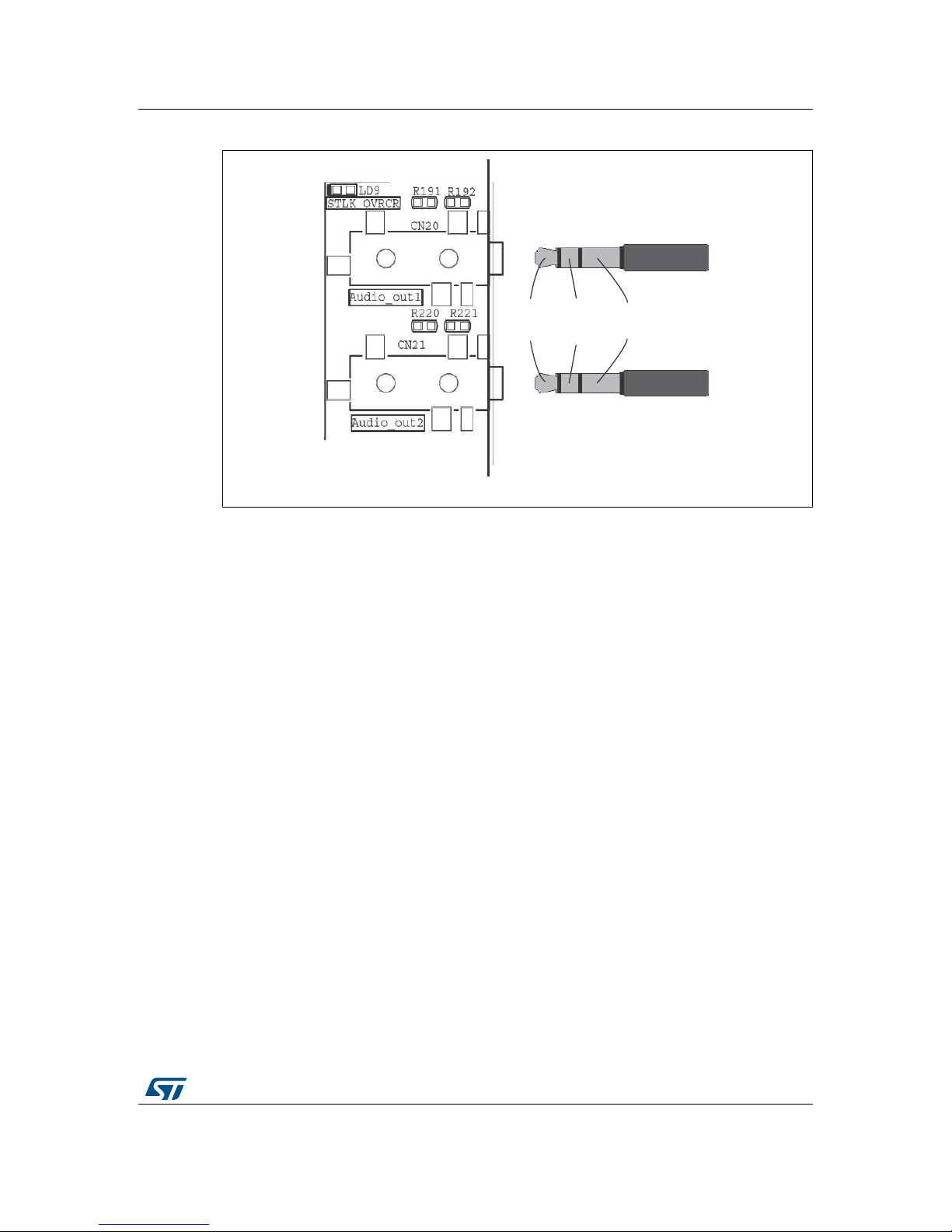

Figure 6. CN20, CN21 top view . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 7. PCB top-side rework for motor control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 8. PCB underside rework for motor control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 9. LCD glass module daughterboard in display position. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 10. LCD glass module daughterboard in I/O-bridge position . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 11. LCD glass display element mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 12. NFC board plugged into STM32L476G-EVAL board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 13. Routing of STPMS2L dual-channel sigma-delta modulators . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 14. Power measurement principle schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 15. STPMS2L power metering schematic diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 16. Temperature measurement principle schematic diagram. . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 17. Schematic diagram of the analog part of IDD measurement . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 18. Schematic diagram of logic part of low-power-mode IDD measurement . . . . . . . . . . . . . . 57

Figure 19. Low power mode IDD measurement timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 20. RS-232 D-sub (DE-9M) 9-pole connector (front view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 21. Power supply connector CN22 (front view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 22. USB type B connector CN17 (front view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 23. JTAG debugging connector CN15 (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 24. Trace debugging connector CN12 (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 25. microSD card connector CN18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 26. Analog input-output connector CN8 (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 27. RF EEPROM daughterboard connector CN3 (front view) . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 28. Motor control connector CN2 (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 29. USB OTG FS Micro-AB connector CN1 (front view). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 30. CAN D-sub (DE-9M) 9-pole male connector CN5 (front view) . . . . . . . . . . . . . . . . . . . . . . 71

Figure 31. NFC female connector CN13 (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 32. STM32L476G-EVAL top schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 33. MCU, LCD daughterboard and I/O expander interfaces - schematic diagram . . . . . . . . . 74

Figure 34. STM32L476G-EVAL MCU part 1 - schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 35. STM32L476G-EVAL MCU part 2 - schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 36. LCD glass module daughterboard connectors - schematic diagram . . . . . . . . . . . . . . . . . 77

Figure 37. I/O expander schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 38. Power supply schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 39. Smartcard, SWP and NFC - schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 40. USART and IrDA - schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 41. SRAM and NOR Flash memory devices - schematic diagram . . . . . . . . . . . . . . . . . . . . . . 82

Figure 42. TFT LCD schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 43. Extension connector schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 44. Quad-SPI Flash memory device schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 45. microSD card schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 46. Physical control peripherals - schematic diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 47. CAN transceiver schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Figure 48. Touch-sensing device schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Page 8

List of figures UM1855

8/100 DocID027351 Rev 3

Figure 49. USB_OTG_FS port schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Figure 50. IDD measurement schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 51. Audio codec device schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 52. STPMS2L and PT100 schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Figure 53. RF-EEPROM and EEPROM schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 54. Motor control connector schematic diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 55. JTAG and trace debug connectors - schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 56. ST-LINK/V2-1 schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Page 9

DocID027351 Rev 3 9/100

UM1855 Overview

99

1 Overview

1.1 Features

• STM32L476ZGT6 microcontroller with 1-Mbyte Flash memory and 128-Kbyte RAM

• four power supply options: power jack, ST-LINK/V2-1 USB connector, USB OTG FS

connector, daughterboard

• microcontroller supply voltage: 3.3 V or range from 1.71 V to 3.6 V

• two MEMS digital microphones

• two stereo audio headphones jack outputs with independent audio content

• slot for microSD card supporting SD, SDHC, SDXC

• 4-Gbyte microSD card bundled

• 16-Mbit (1M x 16 bit) SRAM device

• 128-Mbit (8M x 16 bit) NOR Flash memory device

• 256-Mbit Quad-SPI Flash memory device with double transfer rate (DTR) support

• RF-EEPROM with I²C bus

• EEPROM supporting 1 MHz I²C-bus communication speed

• RS-232 port configurable for communication or MCU flashing

• IrDA transceiver

• USB OTG FS Micro-AB port

• CAN 2.0A/B-compliant port

• joystick with four-way controller and selector

• reset and wake-up / tamper buttons

• touch-sensing button

• light-dependent resistor (LDR)

• potentiometer

• coin battery cell for power backup

• LCD glass module daughterboard (MB979) with 40x8-segment LCD driven directly by

STM32L476ZGT6

• 2.8-inch 320x240 dot-matrix color TFT LCD panel with resistive touchscreen

• smartcard connector and SWP support

• NFC transceiver connector

• connector for ADC input and DAC output

• power-metering demonstration with dual-channel sigma-delta modulator

• PT100 thermal sensor with dual-channel sigma-delta modulator

• MCU current consumption measurement circuit

• access to comparator and operational amplifier of STM32L476ZGT6

• extension connector for motor control module

• JTAG/SWD, ETM trace debug support, user interface through USB virtual COM port,

embedded ST-LINK/V2-1 debug and flashing facility

• extension connector for daughterboard

Page 10

Overview UM1855

10/100 DocID027351 Rev 3

1.2 Demonstration software

Demonstration software is preloaded in the STM32L476ZGT6 Flash memory, for easy

demonstration of the device peripherals in stand-alone mode. For more information and to

download the latest available version, refer to the STM32L476G-EVAL demonstration

software available on www.st.com.

1.3 Order code

To order the evaluation board based on the STM32L476ZGT6 MCU, use the order code

STM32L476G-EVAL.

1.4 Unpacking recommendations

Before the first use, make sure that, no damage occurred to the board during shipment and

no socketed components are loosen in their sockets or fallen into the plastic bag.

In particular, pay attention to the following components:

1. quartz crystal (X2 position)

2. microSD card in its CN18 receptacle

3. RF-EEPROM board (ANT7-M24LR-A) in its CN3 connector

For product information related with STM32L476ZGT6 microcontroller, visit www.st.com.

Page 11

DocID027351 Rev 3 11/100

UM1855 Hardware layout and configuration

99

2 Hardware layout and configuration

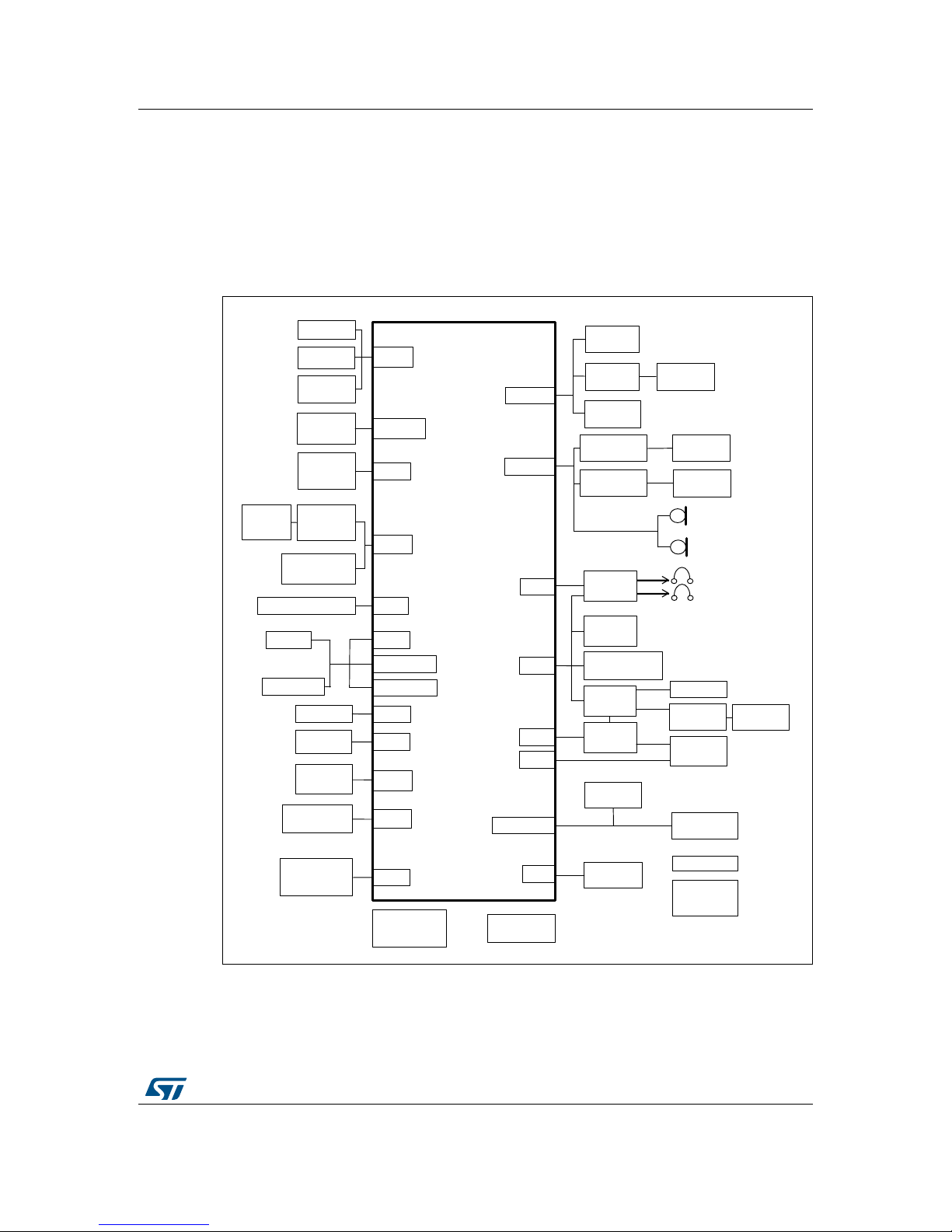

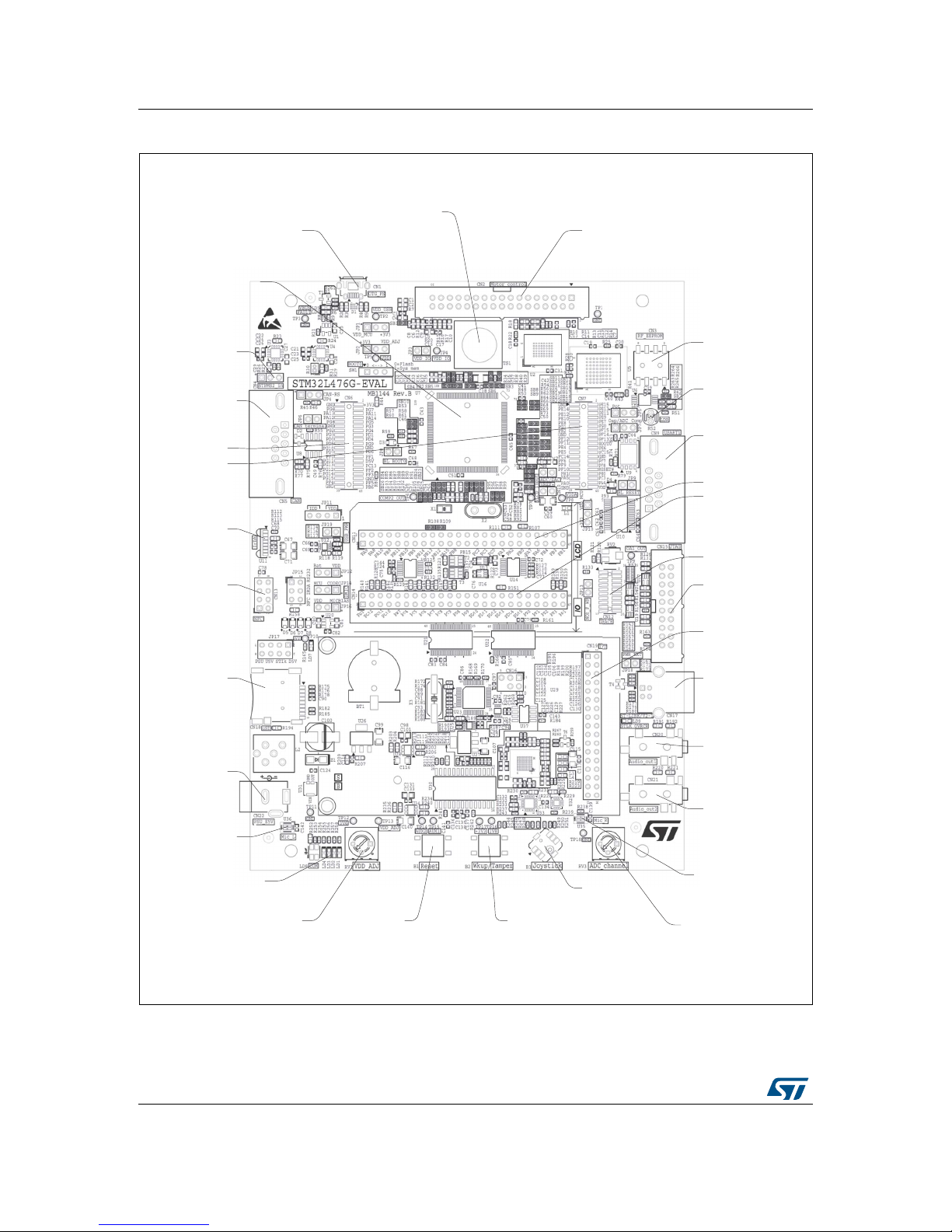

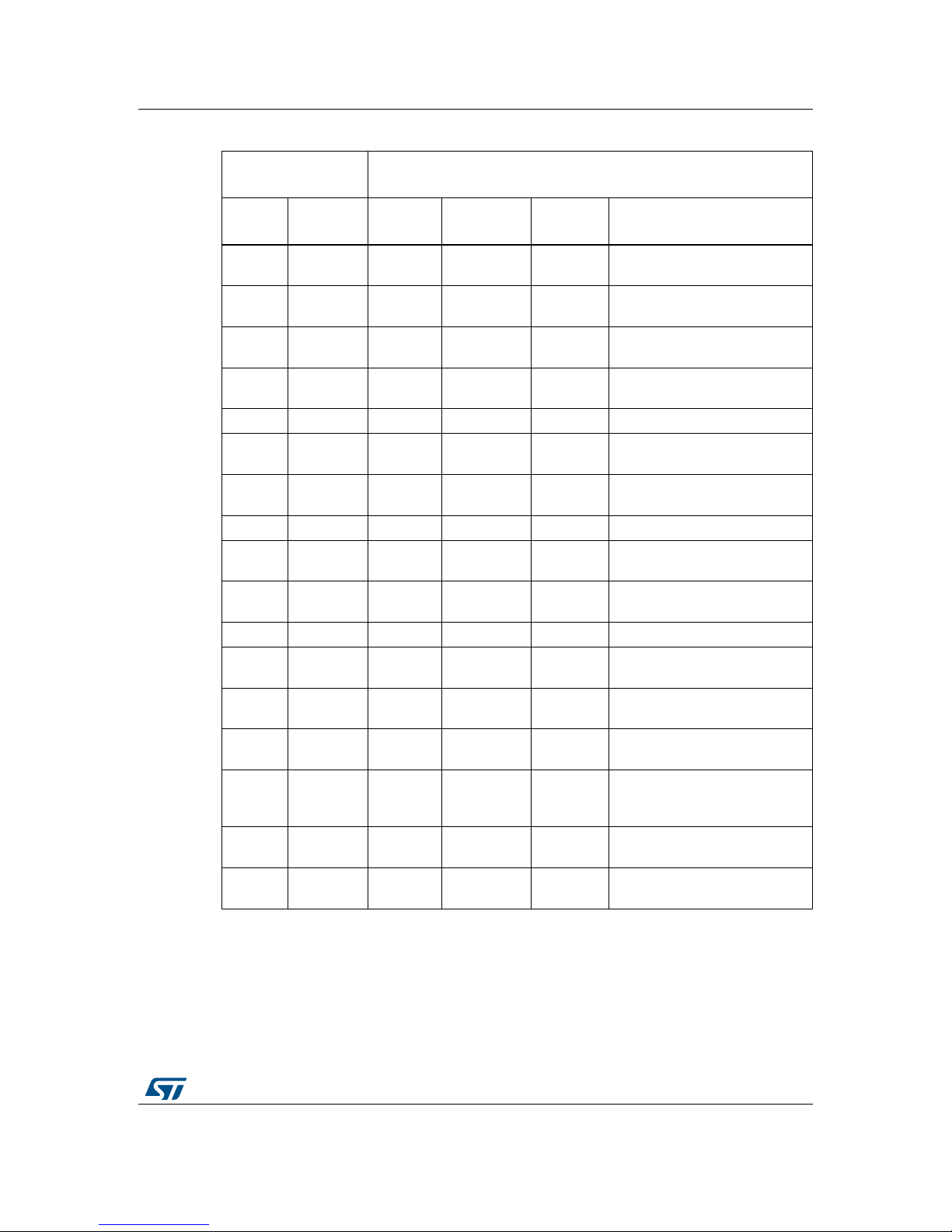

The STM32L476G-EVAL evaluation board is designed around STM32L476ZGT6 target

microcontroller in LQFP 144-pin package. Figure 2 illustrates STM32L476ZGT6

connections with peripheral components. Figure 3 shows the location of main components

on the evaluation board.

Figure 2. STM32L476G-EVAL hardware block diagram

06Y9

*3,2

,&

86$57

-7$*

3RWHQWLRPHWHU

-R\VWLFN

/('

.H\

EXWWRQ

5)((3520

FRQQHFWRU

56

WUDQVFHLYHU

,U'$

WUDQVFHLYHU

56

FRQQHFWRU

6$,

$XGLR

FRGHF

67/,1.9

6WDQGDUG%

86%

FRQQHFWRU

-7$*WUDFHDQG

6:'FRQQHFWRUV

([WHQVLRQ

FRQQHFWRUVIRU

*3,2V

WZRVWHUHR

KHDGSKRQH

RXWSXWV

670/=*7

&$1WUDQVFHLYHU

DQGFRQQHFWRU

&$1

0RWRUFRQWURO

FRQQHFWRU

&RPSDUDWRU

6',2

PLFUR6'

FDUG

)0&

57&

%DWWHU\

*3,2

,2

([SDQGHU

65$0

125)ODVK

PHPRU\

86%27*)6

86%0LFUR$%

FRQQHFWRU

86%SRZHU

VZLWFK

¶¶FRORU

7)7/&'

/&'

0LIDUH

FRQQHFWRU

6PDUWFDUG

ZLWK6:3

6:3

*3,2

6PDUWFDUG

LQWHUIDFH

/'5

2S$PS

$'&

((3520

/&'J/DVV

PRGXOH

[

7)7/&'

FRQWUROOHU

')6'0

WZRGLJLWDO0(06

PLFURSKRQHV

4XDG63,

)ODVKP(PRU\

GHYLFH

48$'63,

76&

7RXFKVHQVLQJEXWWRQ

6LJPDGHOWD

PRGXODWRU

37

VHQVRU

3RZHUPHWHU

0&8

VXSSO\FXUUHQW

PHDVXUHPHQW

9UHJXODWRU

WR9

DGMXVWDEOH

UHJXODWRU

6LJPDGHOWD

PRGXODWRU

7)7/&'

WRXFKVFUHHQ

*3,2

Page 12

Hardware layout and configuration UM1855

12/100 DocID027351 Rev 3

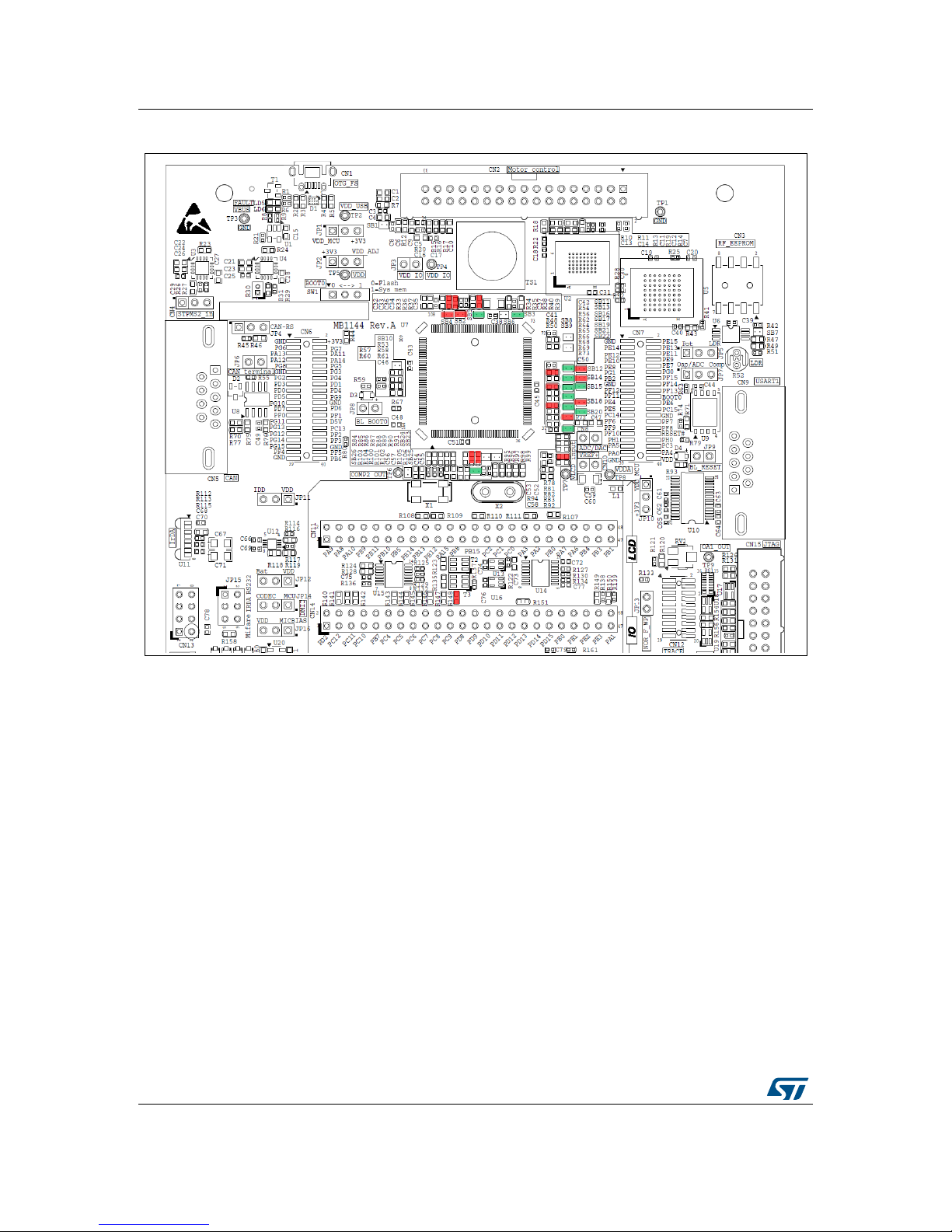

Figure 3. STM32L476G-EVAL main component layout

06Y9

59

3RWHQWLRPHWHU

8ULJKW

PLFURSKRQH

&1

+HDGSKRQHV

MDFN

&1

+HDGSKRQHV

MDFN

6WDQGDUG%

86%SRUWRI

67/,1.9

&1

-7$*

&17UDFH

&1

&1

/&'JODVVPRGXOH

GDXJKWHUERDUG

'%

&1

86$57

5

/'5

&1

5)((3520

&1

0RWRUFRQWURO

76

7RXFKVHQVLQJ

EXWWRQ

&1

86%27*SRUW

8

670/=*7

&1

6LJPDGHOWDLQ

&1

&$1

&1

&1

([WHQVLRQ

FRQQHFWRUV

8

,U'$

&1

1)&

&1

7)7/&'

&1

PLFUR6'FDUG

&1

3RZHUMDFN

8OHIW

PLFURSKRQH

)RXU/('V

59

9''VHWWLQJ

%

5HVHWEXWWRQ

%

:DNHXSWDPSHU

EXWWRQ

%

-R\VWLFN

Page 13

DocID027351 Rev 3 13/100

UM1855 Hardware layout and configuration

99

2.1 ST-LINK/V2-1

ST-LINK/V2-1 facility for debug and flashing of STM32L476ZGT6, is integrated on the

STM32L476G-EVAL evaluation board.

Compared to ST-LINK/V2 stand-alone tool available from STMicroelectronics, ST-LINK/V21 offers new features and drops some others.

New features:

• USB software re-enumeration

• Virtual COM port interface on USB

• Mass storage interface on USB

• USB power management request for more than 100mA power on USB

Features dropped:

• SWIM interface

The USB connector CN17 can be used to power STM32L476G-EVAL regardless of

ST-LINK/V2-1 facility use for debugging or for flashing STM32L476ZGT6. This holds also

when ST-LINK/V2 stand-alone tool is connected to CN12 or CN15 connector and used for

debugging or flashing STM32L476ZGT6. Section 2.3 provides more detail on powering

STM32L476G-EVAL.

For full detail on both versions of the debug and flashing tool, the stand-alone ST-LINK/V2

and the embedded ST-LINK/V2-1, refer to www.st.com.

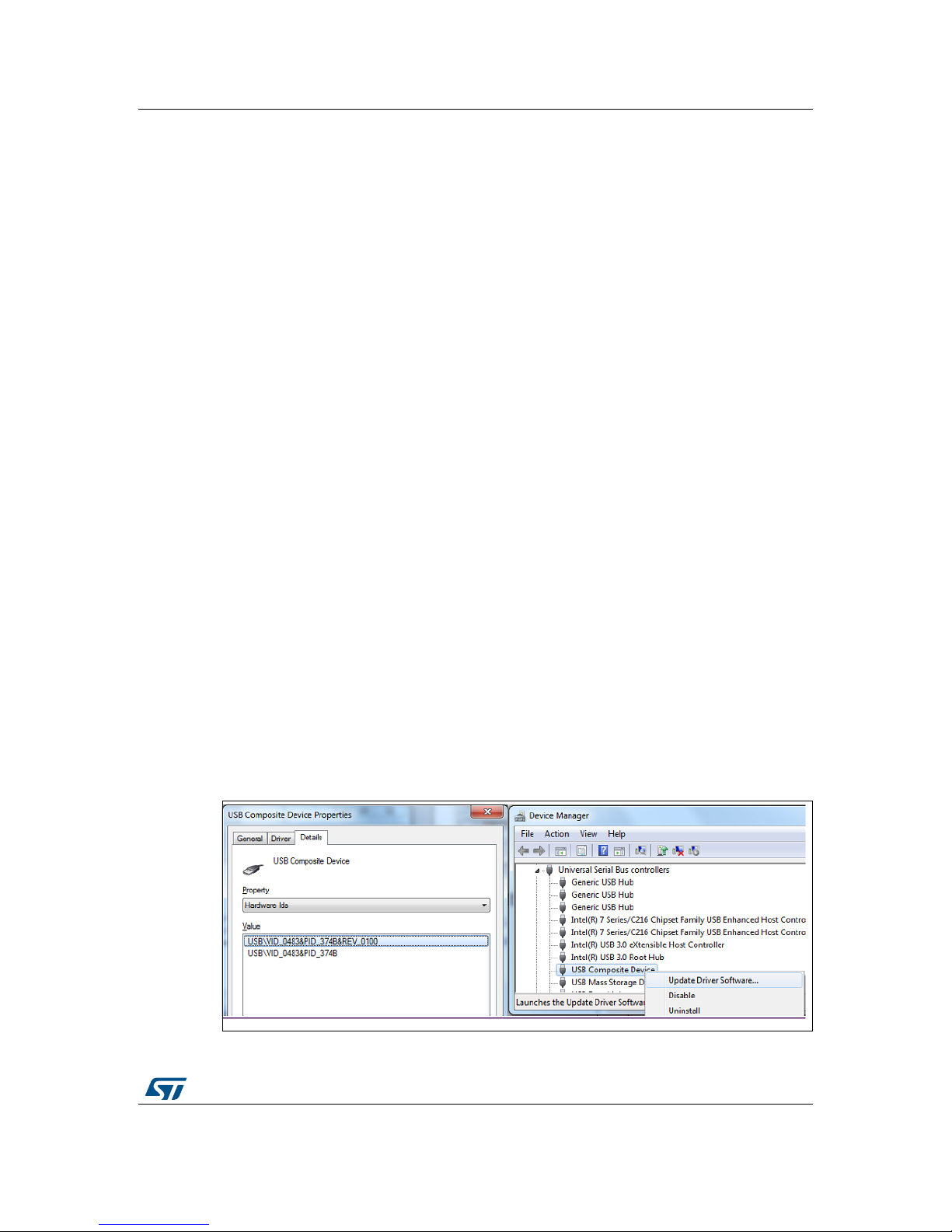

2.1.1 Drivers

Before connecting STM32L476G-EVAL to a Windows 7, Windows 8 or Windows XP PC via

USB, a driver for ST-LINK/V2-1 must be installed. It can be downloaded from www.st.com.

In case the STM32L476G-EVAL evaluation board is connected to the PC before installing

the driver, the Windows device manager may report some USB devices found on

STM32L476G-EVAL as “Unknown”. To recover from this situation, after installing the

dedicated driver downloaded from www.st.com, the association of “Unknown” USB devices

found on STM32L476G-EVAL to this dedicated driver must be updated in the device

manager manually. It is recommended to proceed using USB Composite Device line, as

shown in Figure 4.

Figure 4. USB Composite device

Page 14

Hardware layout and configuration UM1855

14/100 DocID027351 Rev 3

2.1.2 ST-LINK/V2-1 firmware upgrade

For its own operation, ST-LINK/V2-1 employs a dedicated MCU with Flash memory. Its

firmware determines ST-LINK/V2-1 functionality and performance. The firmware may evolve

during the life span of STM32L476G-EVAL to include new functionality, fix bugs or support

new target microcontroller families. It is therefore recommended to keep ST-LINK/V2-1

firmware up to date. The latest version is available from www.st.com.

2.2 ETM Trace

The connector CN12 can output trace signals used for debug. By default, the evaluation

board is configured such that, STM32L476ZGT6 signals PE2 through PE5 are not

connected to trace outputs Trace_D0, Trace_D1, Trace_D2, Trace_D3 and Trace_CK of

CN12. They are used for other functions.

Tabl e 1 shows the setting of configuration elements to shunt PE2, PE3, PE4 and PE5 MCU

ports to CN12 connector, to use them as debug trace signals.

Warning: Enabling the CN12 trace outputs through hardware modifications described in

Tabl e 1 results in reducing the memory address bus width to 19 address lines and so the

addressable space to 512 Kwords of 16 bits. As a consequence, the on-board SRAM and

NOR Flash memory usable capacity is reduced to 8 Mbits.

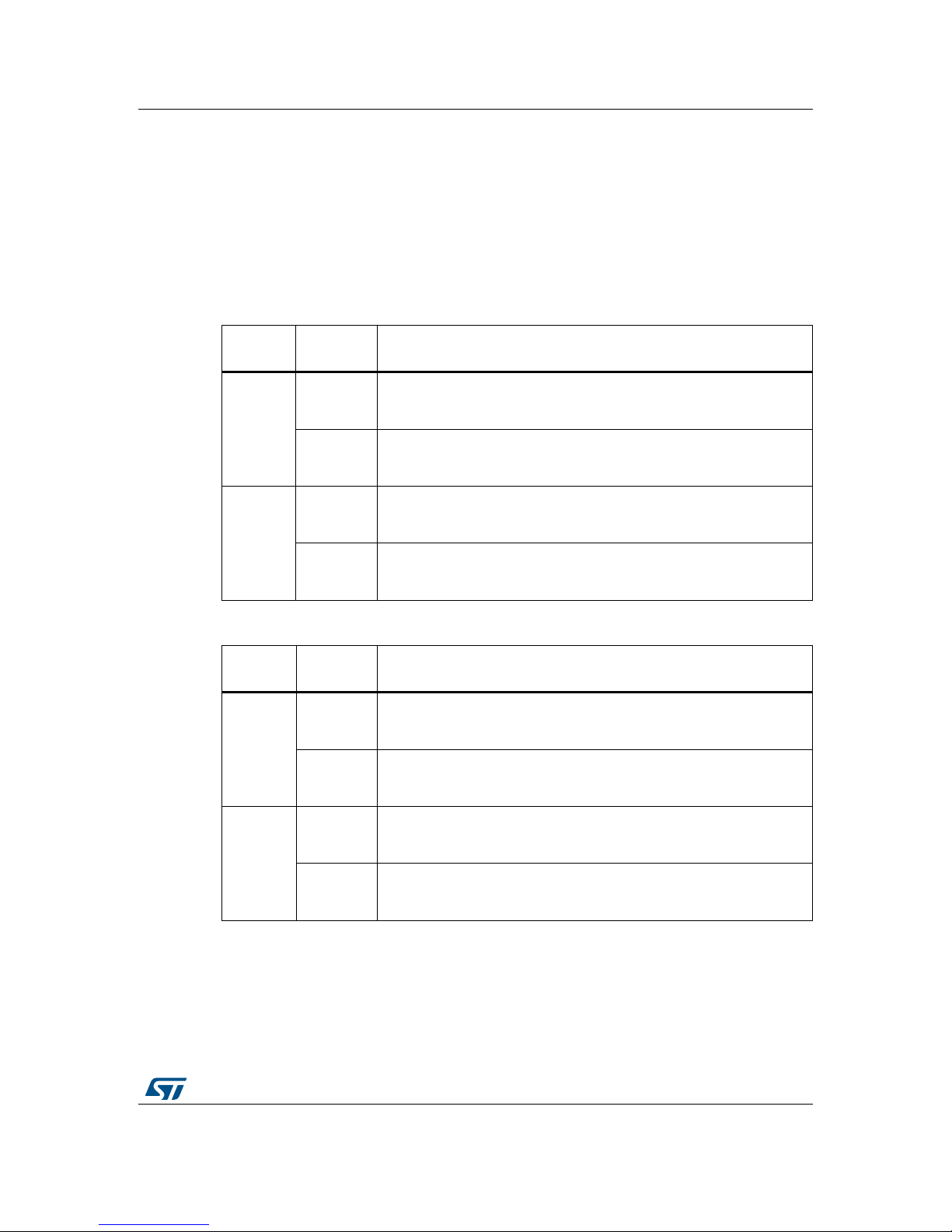

Table 1. Setting of configuration elements for trace connector CN12

Element Setting Use of PE2, PE3, PE4, PE5 terminals of STM32L476ZGT6

R103

SB26

R103 in

SB26 open

Default setting.

PE2 connected to LCDSEG38 and memory address line A23.

R103 out

SB26 closed

PE2 connected to TRACE_CK on CN12. A23 pulled down.

R104

R104 in

Default setting.

PE3 connected to LCDSEG39 and memory address line A19.

R104 out PE3 connected to TRACE_D0 on CN12. A19 pulled down.

R84

SB40

R84 in

SB40 open

Default setting.

PE4 connected to memory address line A20.

R84 out

SB40 closed

PE4 connected to TRACE_D1 on CN12. A20 pulled down.

R85

SB38

R85 in

SB38 open

Default setting.

PE5 connected to memory address line A21.

R85 out

SB38 closed

PE5 connected to TRACE_D2 on CN12. A21 pulled down.

R86

SB39

R86 in

SB39 open

Default setting.

PE6 is used for address bit A22.

R86 out

SB39 closed

PE6 connected to TRACE_D3 on CN12. A22 pulled down.

Page 15

DocID027351 Rev 3 15/100

UM1855 Hardware layout and configuration

99

2.3 Power supply

STM32L476G-EVAL evaluation board is designed to be powered from 5 V DC power

source. It incorporates a precise polymer Zener diode (Poly-Zen) protecting the board from

damage due to wrong power supply. One of the following four 5V DC power inputs can be

used, upon an appropriate board configuration:

• Power jack CN22, marked PSU_E5V on the board. A jumper must be placed in PSU

location of JP17. The positive pole is on the center pin as illustrated in Figure 5.

• Standard-B USB receptacle CN17 of ST-LINK/V2-1, offering enumeration feature

described in Section 2.3.1.

• Micro-AB USB receptacle CN1 of USB OTG interface, marked OTG_FS on the board.

Up to 500mA can be supplied to the board in this way.

• Pin 28 of CN6 extension connector for custom daughterboards, marked D5V on the

board.

No external power supply is provided with the board.

LD7 red LED turns on when the voltage on the power line marked as +5V is present. All

supply lines required for the operation of the components on STM32L476G-EVAL are

derived from that +5V line.

Tabl e 2 describes the settings of all jumpers related with powering STM32L476G-EVAL and

extension board. VDD_MCU is STM32L476ZGT6 digital supply voltage line. It can be

connected to either fixed 3.3 V or to an adjustable voltage regulator controlled with RV1

potentiometer and producing a range of voltages between 1.71 V and 3.6 V.

2.3.1 Supplying the board through ST-LINK/V2-1 USB port

To power STM32L476G-EVAL in this way, the USB host (a PC) gets connected with the

STM32L476G-EVAL board’s Standard-B USB receptacle, via a USB cable. This event starts

the USB enumeration procedure. In its initial phase, the host’s USB port current supply

capability is limited to 100 mA. It is enough because only ST-LINK/V2-1 part of

STM32L476G-EVAL draws power at that time. If the jumper header JP18 is open, the U37

ST890 power switch is set to OFF position, which isolates the remainder of

STM32L476G-EVAL from the power source. In the next phase of the enumeration

procedure, the host PC informs the ST-LINK/V2-1 facility of its capability to supply up to

300 mA of current. If the answer is positive, the ST-LINK/V2-1 sets the U37 ST890 switch to

ON position to supply power to the remainder of the STM32L476G-EVAL board. If the PC

USB port is not capable of supplying up to 300 mA of current, the CN22 power jack can be

used to supply the board.

The ST890 power switch protects the host’s USB port against current demand exceeding

600 mA, should a short-circuit occur on the board. In such an event, the LD9 LED lights on.

The STM32L476G-EVAL board can also be supplied from a USB power source not

supporting enumeration, such as a USB charger. In this particular case, the JP18 header

must be fitted with a jumper as shown in Tabl e 2. ST-LINK/V2-1 turns the ST890 power

switch ON regardless of enumeration procedure result and passes the power

unconditionally to the board.

The LD7 red LED turns on whenever the whole board is powered.

Page 16

Hardware layout and configuration UM1855

16/100 DocID027351 Rev 3

2.3.2 Using ST-LINK/2-1 along with powering through CN22 power jack

It can happen that the board requires more than 300 mA of supply current. It cannot be

supplied from host PC connected to ST-LINK/2-1 USB port for debugging or flashing

STM32L476ZGT6. In such a case, the board can be supplied through CN22 (marked PSU

_E5V on the board).

To do this, it is important to power the board before connecting it with the host PC, which

requires the following sequence to be respected:

1. set the jumper in JP15 header in PSU position

2. connect the external 5 V power source to CN22

3. check the red LED LD7 is turned on

4. connect host PC to USB connector CN17

In case the board demands more than 300 mA and the host PC is connected via USB

before the board is powered from CN22, there is a risk of the following events to occur, in

the order of severity:

1. The host PC is capable of supplying 300 mA (the enumeration succeeds) but it does

not incorporate any over-current protection on its USB port. It is damaged due to overcurrent.

2. The host PC is capable of supplying 300 mA (the enumeration succeeds) and it has a

built-in over-current protection on its USB port, limiting or shutting down the power out

of its USB port when the excessive current demand from STM32L476G-EVAL is

detected. This causes an operating failure to STM32L476G-EVAL.

3. The host PC is not capable of supplying 300 mA (the enumeration fails) so

ST-LINK/V2-1 does not supply the remainder of STM32L476G-EVAL from its USB port

VBUS line.

Figure 5. CN22 power jack polarity

Page 17

DocID027351 Rev 3 17/100

UM1855 Hardware layout and configuration

99

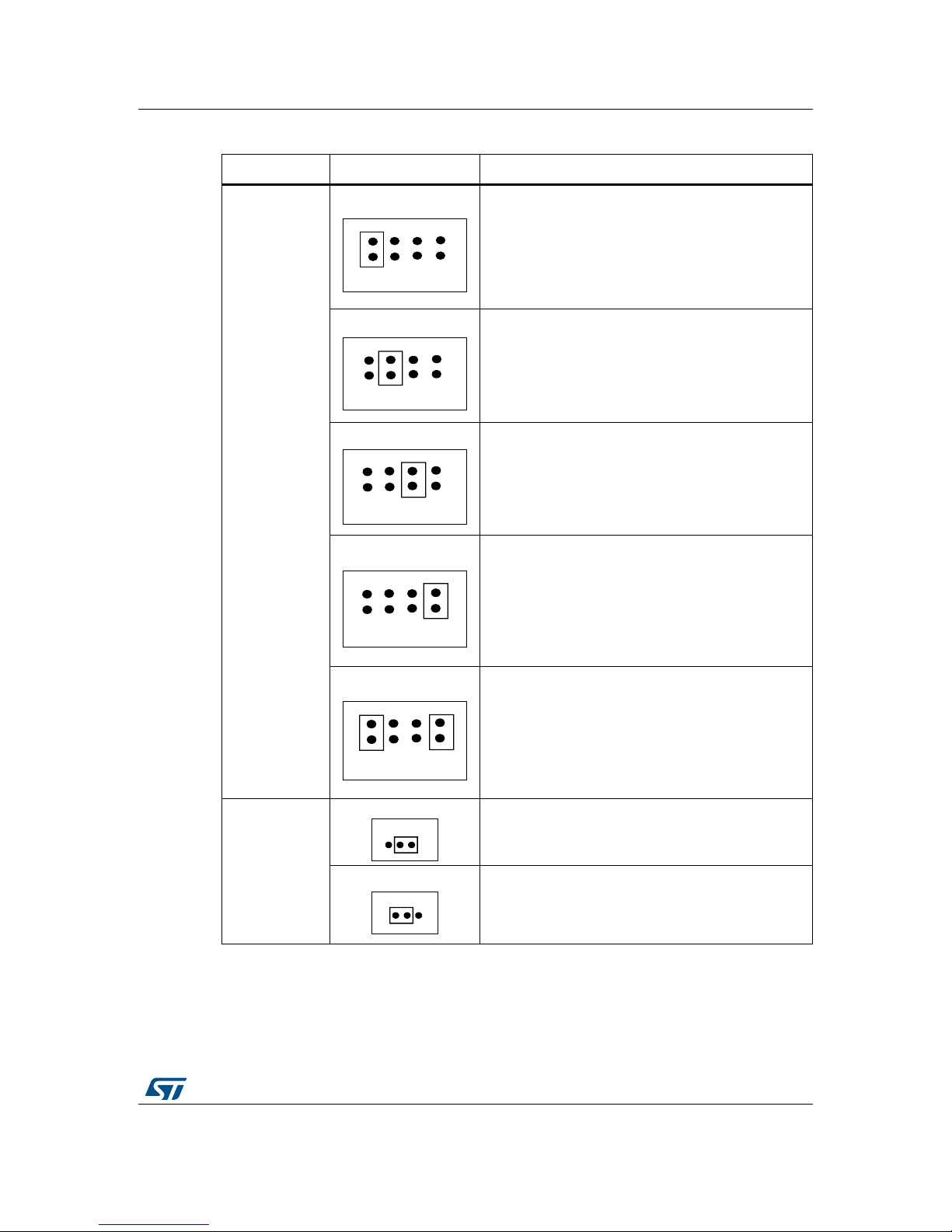

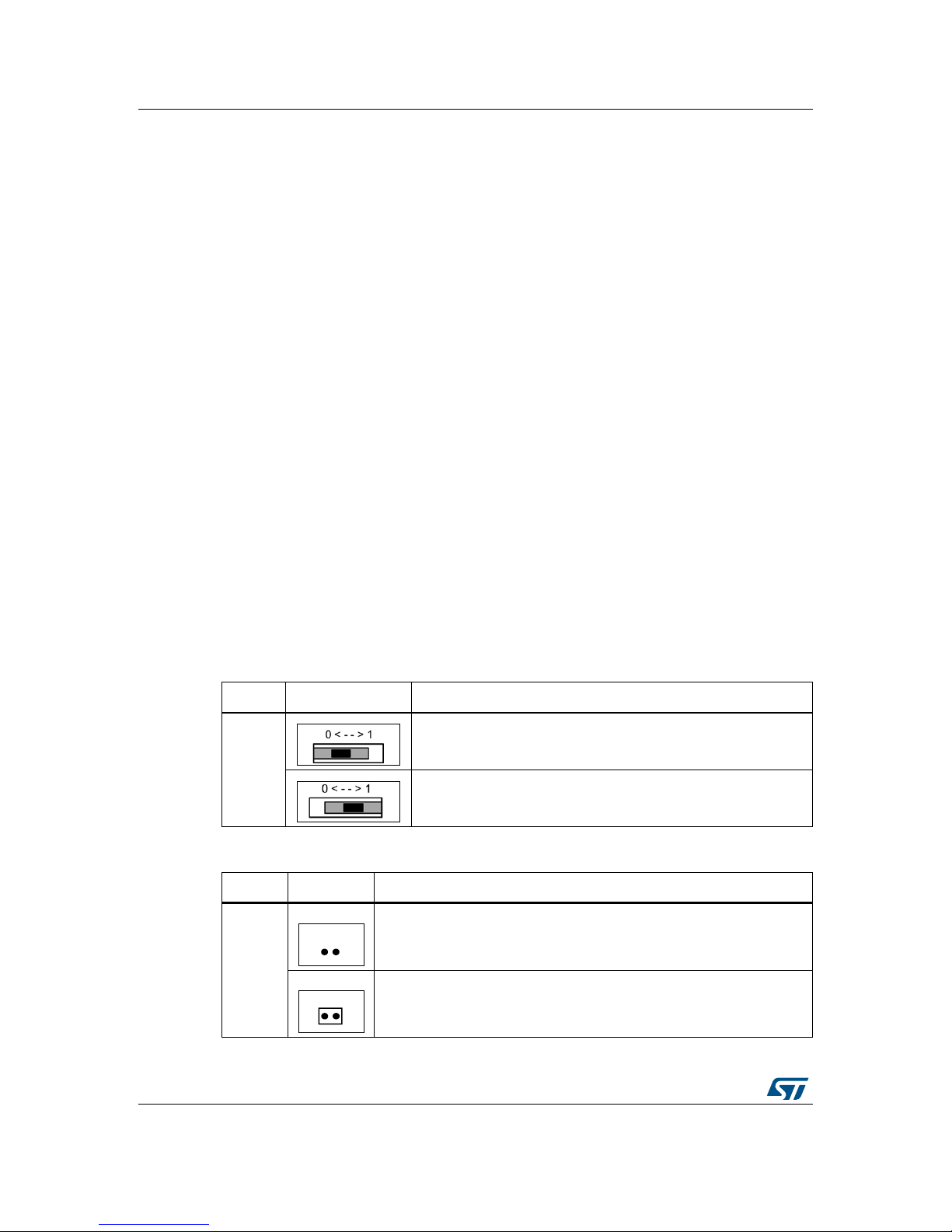

Table 2. Power-supply-related jumper settings

Jumper array Jumper setting Configuration

JP17

Power source

selector

JP17

STM32L476G-EVAL is supplied through CN22 power

jack (marked PSU_E5V). CN6 extension connector

does not pass the 5 V of STM32L476G-EVAL to

daughterboard.

JP17

STM32L476G-EVAL is supplied through CN1 Micro-AB

USB connector. CN6 extension connector does not

pass the 5 V of STM32L476G-EVAL to daughterboard.

JP17

Default setting.

STM32L476G-EVAL is supplied through CN17

Standard-B USB connector. CN6 extension connector

does not pass the 5 V of STM32L476G-EVAL to

daughterboard.

Check JP18 setting in Table 2.

JP17

STM32L476G-EVAL is supplied through pin 28 of CN6

extension connector.

JP17

STM32L476G-EVAL is supplied through CN22 power

jack (marked PSU_E5V). CN6 extension connector

passes the 5 V of STM32L476G-EVAL to

daughterboard. Make sure to disconnect from the

daughterboard any power supply that could generate

conflict with the power supply on CN22 power jack.

JP12

V

bat

connection

JP12

V

bat

is connected to battery.

JP12

Default setting.

V

bat

is connected to VDD.

3688967/.'9

3688967/.'9

3688967/.'9

3688967/.'9

3688967/.'9

Page 18

Hardware layout and configuration UM1855

18/100 DocID027351 Rev 3

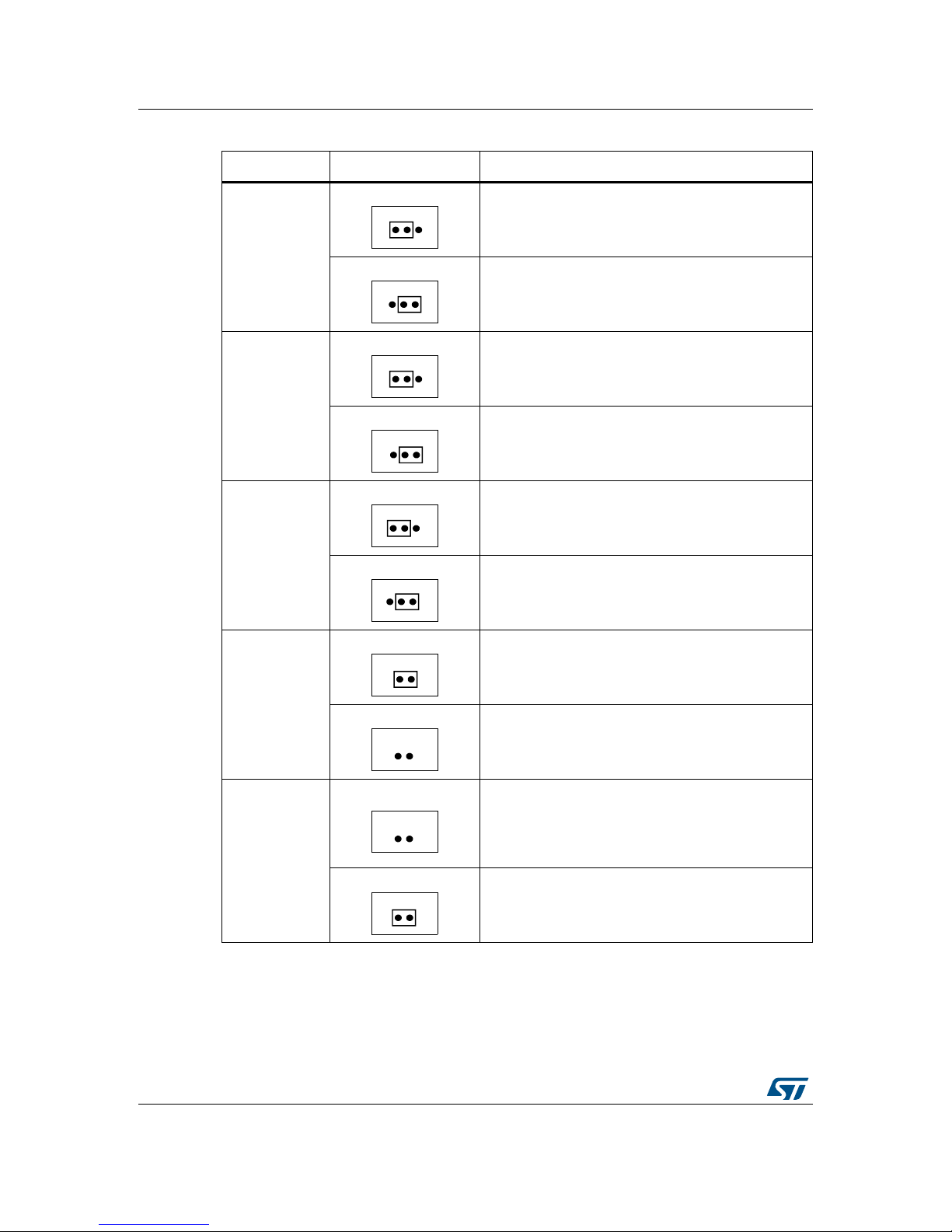

JP2

VDD_MCU

connection

JP2

Default setting.

VDD_MCU (VDD terminals of STM32L476ZGT6) is

connected to fixed +3.3 V.

JP2

VDD_MCU is connected to voltage in the range from

+1.71 V to +3.6 V, adjustable with potentiometer RV1.

JP10

VDDA

connection

JP10

Default setting.

VDDA terminal of STM32L476ZGT6 is connected with

VDD_MCU.

JP10

VDDA terminal of STM32L476ZGT6 is connected to

+3.3 V.

JP1

VDD_USB

connection

JP1

Default setting.

VDD_USB (VDDUSB terminal of STM32L476ZGT6) is

connected with VDD_MCU.

JP1

VDD_USB is connected to +3.3V.

JP3

VDD_IO

connection

JP3

Default setting.

VDD_IO

(VDDIO2 terminals of STM32L476ZGT6) is

connected with VDD_MCU

JP3

VDD_IO

is open.

JP18

Powering

through USB of

ST-LINK/V2-1

JP18

Default setting.

Standard-B USB connector CN17 of ST-LINK/V2-1 can

supply power to the STM32L476G-EVAL board

remainder, depending on host PC USB port’s powering

capability declared in the enumeration.

JP18

Standard-B USB connector CN17 of ST-LINK/V2-1

supplies power to the STM32L476G-EVAL board

remainder. Setting for powering the board through

CN17 using USB charger.

Table 2. Power-supply-related jumper settings (continued)

Jumper array Jumper setting Configuration

Page 19

DocID027351 Rev 3 19/100

UM1855 Hardware layout and configuration

99

2.4 Clock references

Two clock references are available on STM32L476G-EVAL for the STM32L476ZGT6 target

microcontroller:

• 32.768 kHz crystal X1, for embedded RTC

• 8 MHz crystal X2, for main clock generator

The main clock can also be generated using an internal RC oscillator. The X2 crystal is in a

socket. It can be removed when the internal RC oscillator is used.

2.5 Reset sources

Reset signal of the STM32L476G-EVAL board is active low.

Table 3. X1-crystal-related solder bridge settings

Solder

bridge

Setting Description

SB41

Open

Default setting.

PC14-OSC32_IN terminal is not routed to extension connector CN7. X1 is

used as clock reference.

Closed

PC14-OSC32_IN is routed to extension connector CN7.

R87 must be removed, for X1 quartz circuit not to disturb clock reference

or source on daughterboard.

SB33

Open

Default setting.

PC15-OSC32_OUT terminal is not routed to extension connector CN7.

X1 is used as clock reference.

Closed

PC15-OSC32_OUT is routed to extension connector CN7.

R88 must be removed, for X1 quartz circuit not to disturb clock reference

on daughterboard.

Table 4. X2-crystal-related solder bridge settings

Solder

bridge

Setting Configuration

SB24

Open

Default setting.

PH0-OSC_IN terminal is not routed to extension connector CN7. X2 is

used as clock reference.

Closed

PH0-OSC_IN is routed to extension connector CN7.

X2 and C54 must be removed, in order not to disturb clock reference or

source on daughterboard.

SB23

Open

Default setting.

PH1-OSC_OUT terminal is not routed to extension connector CN7. X2 is

used as clock reference.

Closed

PH1-OSC_OUT is routed to extension connector CN7.

R95 must be removed, in order not to disturb clock reference or source on

daughterboard.

Page 20

Hardware layout and configuration UM1855

20/100 DocID027351 Rev 3

Sources of reset are:

• reset button B1

• JTAG/SWD connector CN15 and ETM trace connector CN12 (reset from debug tools)

• through extension connector CN7, pin 32 (reset from daughterboard)

• ST-LINK/V2-1

• RS-232 connector CN9, terminal 8 (CTS signal), if JP9 is closed (open by default)

2.6 Boot

2.6.1 Boot options

After reset, the STM32L476ZGT6 MCU can boot from the following embedded memory

locations:

• main (user, non-protected) Flash memory

• system (protected) Flash memory

• RAM, for debugging

The microcontroller is configured to one of the listed boot options by setting the

STM32L476ZGT6 port BOOT0 level by the switch SW1 and by setting nBOOT1 bit of

FLASH_OPTR option bytes register, as shown in Tab l e 5. Depending on JP8, BOOT0 level

can be forced high and, SW1 action overruled, by DSR line of RS-232 connector CN9, as

shown in Tab l e 6. This can be used to force the execution of bootloader and start user Flash

memory flashing process (ISP) from RS-232 interface.

The option bytes of STM32L476ZGT6 and their modification procedure are described in the

reference manual RM0351. The application note AN2606 details the bootloader mechanism

and configurations.

Table 5. Boot selection switch

Switch Setting Description

SW1

Default setting.

BOOT0 line is tied low. STM32L476ZGT6 boots from user Flash

memory.

BOOT0 line is tied high. STM32L476ZGT6 boots from system Flash

memory (nBOOT1 bit of FLASH_OPTR register is set high) or from

RAM (nBOOT1 is set low).

Table 6. Bootloader-related jumper setting

Jumper Setting Description

JP8

JP8

Default setting.

BOOT0 level only depends on SW1 switch position

JP8

BOOT0 can be forced high with terminal 6 of CN9 connector (RS-232

DSR line). This configuration is used to allow the device connected via

RS-232 to initiate STM32L476ZGT6 flashing process.

Page 21

DocID027351 Rev 3 21/100

UM1855 Hardware layout and configuration

99

2.6.2 Bootloader limitations

Boot from system Flash memory results in executing bootloader code stored in the system

Flash memory protected against write and erase. This allows in-system programming (ISP),

that is, flashing the MCU user Flash memory. It also allows writing data into RAM. The data

come in via one of communication interfaces such as USART, SPI, I²C bus, USB or CAN.

Bootloader version can be identified by reading Bootloader ID at the address 0x1FFF6FFE.

The STM32L476ZGT6 part soldered on the STM32L476G-EVAL main board is marked with

a date code corresponding to its date of manufacture. STM32L476ZGT6 parts with the date

code prior or equal to week 22 of 2015 are fitted with bootloader V 9.0 affected by the

limitations to be worked around, as described hereunder. Parts with the date code starting

week 23 of 2015 contain bootloader V9.2 in which the limitations no longer exist.

To locate the visual date code information on the STM32L476ZGT6 package, refer to its

datasheet (DS10198) available on www.st.com, section Package Information. Date code

related portion of the package marking takes Y WW format, where Y is the last digit of the

year and WW is the week. For example, a part manufactured in week 23 of 2015 bares the

date code 5 23.

Bootloader ID of the bootloader V 9.0 is 0x90.

The following limitations exist in the bootloader V 9.0:

1. RAM data get corrupted when written via USART/SPI/I2C/USB interface

Description:

Data write operation into RAM space via USART, SPI, I²C bus or USB results in wrong

or no data written.

Workaround:

To correct the issue of wrong write into RAM, download STSW-STM32158 bootloader

V 9.0 patch package from www.st.com and load "Bootloader V9.0 SRAM patch" to the

MCU, following the information in readme.txt file available in the package.

2. User Flash memory data get corrupted when written via CAN interface

Description:

Data write operation into user Flash memory space via CAN interface results in wrong

or no data written.

Workaround:

To correct the issue of wrong write into Flash memory, download STSW-STM32158

bootloader V 0.9 patch package from www.st.com and load "Bootloader V9.0 CAN

patch" to the MCU, following the information in readme.txt file available in the package.

2.7 Audio

A codec connected to SAI interface of STM32L476ZGT6 supports TDM feature of the SAI

port. TDM feature offers to STM32L476ZGT6 the capability to stream two independent

stereo audio channels to two separate stereo analog audio outputs, simultaneously.

There are two digital microphones on board of STM32L476G-EVAL.

Page 22

Hardware layout and configuration UM1855

22/100 DocID027351 Rev 3

2.7.1 Digital microphones

U35 and U36 on board of STM32L476G-EVAL are MP34DT01TR MEMS digital omnidirectional microphones providing PDM (pulse density modulation) outputs. To share the

same data line, their outputs are interlaced. The combined data output of the microphones

is directly routed to STM32L476ZGT6 terminals, thanks to the integrated input digital filters.

The microphones are supplied with programmable clock generated directly by

STM32L476ZGT6.

As an option, the microphones can be connected to U29, Wolfson audio codec device,

WM8994. In that configuration, U29 also supplies the PDM clock to the microphones.

Regardless of where the microphones are routed to, STM32L476ZGT6 or WM8994, they

can be power-supplied from either VDD or MICBIAS1 output of the WM8994 codec device.

Tabl e 7 shows settings of all jumpers associated with the digital microphones on the board.

2.7.2 Headphones outputs

The STM32L476G-EVAL evaluation board can drive two sets of stereo headphones.

Identical or different stereo audio content can be played back in each set of headphones.

The STM32L476ZGT6 sends up to two independent stereo audio channels, via its SAI1

TDM port, to the WM8994 codec device. The codec device converts the digital audio stream

to stereo analog signals. It then boosts them for direct drive of headphones connecting to

3.5 mm stereo jack receptacles on the board, CN20 for Audio-output1 and CN21 for

Audio_output2. Figure 6 shows a top view of the CN20 and CN21 headphones jack

receptacles.

The CN21 jack takes its signal from the WM8994 codec device’s output intended for driving

an amplifier for loudspeakers. A hardware adaptation is incorporated on the board to make it

compatible with a direct headphone drive. The adaptation consists of coupling capacitors

blocking the DC component of the signal, attenuator and anti-pop resistors. The WM8994

codec device’s loudspeaker output must be configured by software in linear mode called

“class AB” and not in switching mode called “class D”.

The I²C-bus address of WM8994 is 0b0011010.

Table 7. Digital microphone-related jumper settings

Jumper Setting Configuration

JP14

JP14

Default setting.

PDM clock for digital microphones comes from STM32L476ZGT6

JP14

PDM clock for digital microphones comes from WM8994 codec.

JP16

JP16

Default setting.

Power supply of digital microphones is VDD.

JP16

Power supply of digital microphones is generated by WM8994 codec.

Page 23

DocID027351 Rev 3 23/100

UM1855 Hardware layout and configuration

99

Figure 6. CN20, CN21 top view

2.7.3 Limitations in using audio features

Due to the share of some terminals of STM32L476ZGT6 by multiple peripherals, the

following limitations apply in using the audio features:

• If the SAI1_SDA is used as part of SAI1 port, it cannot be used as FMC_NWAIT signal

for NOR Flash memory device. However, FMC_NWAIT is not necessary for operating

the NOR Flash memory device. More details on FMC_NWAIT are available in

Section 2.22: NOR Flash memory device.

• If the SAI1 port of STM32L476ZGT6 is used for streaming audio to the WM8994 codec

IC, STM32L476ZGT6 cannot control the motor.

• If the digital microphones are attached to STM32L476ZGT6, the LCD glass module

cannot be driven.

2.8 USB OTG FS port

The STM32L476G-EVAL board supports USB OTG full-speed (FS) communication.The

USB OTG connector CN1 is of Micro-AB type.

2.8.1 STM32L476G-EVAL used as USB device

When a “USB host” connection to the CN1 Micro-AB USB connector of STM32L476G-EVAL

is detected, the STM32L476G-EVAL board starts behaving as “USB device”. Depending on

the powering capability of the USB host, the board can take power from VBUS terminal of

CN1. In the board schematic diagrams, the corresponding power voltage line is called U5V.

Section 2.3 provides information on how to set associated jumpers for this powering option.

The JP19 jumper must be left open to prevent STM32L476G-EVAL from sourcing 5 V to

VBUS terminal, which would cause conflict with the 5 V sourced by the USB host. This may

06Y9

(YDOXDWLRQERDUG

5LJKW

FKDQQHO

/HIW

FKDQQHO

*1'

+HDGSKRQHVMDFN

+HDGSKRQHVMDFN

Page 24

Hardware layout and configuration UM1855

24/100 DocID027351 Rev 3

happen if the PC6 GPIO is controlled by the software of STM32L476ZGT6 such that, it

enables the output of U1 power switch.

2.8.2 STM32L476G-EVAL used as USB host

When a “USB device” connection to the CN1 Micro-AB USB connector is detected, the

STM32L476G-EVAL board starts behaving as “USB host”. It sources 5 V on the VBUS

terminal of CN1 Micro-AB USB connector to power the USB device. For this to happen, the

STM32L476ZGT6 MCU sets the U1 power switch STMPS2151STR to ON state. The LD5

green LED marked VBUS indicates that the peripheral is supplied from the board. The LD6

red LED marked FAULT lights up if over-current is detected. The JP19 jumper must be

closed to allow the PC6 GPIO to control the U1 power switch.

In any other STM32L476G-EVAL powering option, the JP19 jumper should be open, to

avoid accidental damage caused to an external USB host.

2.8.3 Configuration elements related with USB OTG FS port

The following STM32L476ZGT6 terminals related with USB OTG FS port control are shared

by other resources of the STM32L476G-EVAL board:

• PB12, used as USB over-current input (USBOTG_OVRCR signal); it is shared with

SWP, touch sensing, LCD glass module and motor control resources

• PB13, used as USB power ready input (USBOTG_PRDY signal); it is shared with NFC,

touch sensing and LCD glass module resources

• PC6, used as USB power switch control (USBOTG_PPWR signal); it is shared with

touch sensing, LCD glass module and motor control

Configuration elements related with the USB OTG FS port, such as jumpers, solder bridges

and zero-ohm resistors, shunt the shared ports toward different resources or determine the

operating mode of the USB OTG FS port. By default, they are set such as to enable the

USB OTG FS port operation where STM32L476G-EVAL plays USB device role and can be

connected to a USB host. Tab l e 8 gives an overview of all configuration elements related

with the USB OTG FS port. The LCD glass module daughterboard should be connected in

I/O position.

USBOTG_OVRCR and USBOTG_PRDY signals, requiring the PB12 and PB13 ports of

STM32L476ZGT6, are only exploited when STM32L476G-EVAL acts as USB host. That is

why, the USB host function of STM32L476G-EVAL is exclusive with alternate functions also

requiring PB12 and PB13 ports of STM32L476ZGT6 - NFC, touch sensing, motor control,

SWP.

The PB12 and PB13 ports of STM32L476ZGT6 are not required for the USB OTG FS port

operating as USB device.

Table 8. Configuration elements related with USB OTG FS port

Element Setting Description

JP19

Open

USB OTG FS port can be connected with a USB host and get power

from it. If connected with USB device, STM32L476G-EVAL cannot

supply power to it.

Closed

Default setting.

USB OTG FS port can be connected with a USB device and supply

power to it. It must not be connected with USB host.

Page 25

DocID027351 Rev 3 25/100

UM1855 Hardware layout and configuration

99

2.8.4 Limitations in using USB OTG FS port

• The USB OTG FS port operation as USB host is exclusive with NFC, SWP, LCD glass

module, touch sensing, motor control

• The USB OTG FS port operation as USB device is exclusive with LCD glass module,

touch sensing, motor control

2.8.5 Operating voltage

The USB-related operating supply voltage of STM32L476ZGT6 (VDD_USB line) must be

within the range from 3.0 V to 3.6 V.

2.9 RS-232 and IrDA ports

The STM32L476G-EVAL board offers one RS-232 communication port and one IrDA port.

2.9.1 RS-232 port

The RS-232 communication port uses the DE-9M 9-pole connector CN9. RX, TX, RTS and

CTS signals of USART1 port of STM32L476ZGT6 are routed to CN9.

Bootloader_RESET_3V3 and Bootloader_BOOT0_3V3 signals can also be routed to CN9,

for ISP (in-system programming) support. To route Bootloader_RESET_3V3 to CN9, the

R93 resistor must be removed and the JP9 jumper closed (open by default). To route

Bootloader_BOOT0_3V3 to CN9, the JP8 jumper must be closed.

R36

In

Default setting

PC6 is shunted to control the U1 power switch, transiting through the

LCD glass module daughterboard connector.

LCD glass module daughterboard should be in I/O position, with SB2

and SB27 open.

Out

PC6 is disconnected from the LCD glass module daughterboard

connector. It can be shunted to one of alternate resources, either

touch sensing (SB2 closed) or motor control (SB27 closed).

R39

In

Default setting.

PB12 receives USBOTG_OVRCR signal from U1 power switch,

transiting through the LCD glass module daughterboard connector.

SB3 should be open, R109 in, no smartcard in CN23 slot.

Out

PB12 is disconnected from the LCD glass module daughterboard

connector. It can be shunted to one of alternate resources, either

touch sensing or motor control (SB3 closed).

R38

In

Default setting.

PB13 receives USBOTG_PRDY signal from CN1 connector, transiting

through the LCD glass module daughterboard connector.

SB6 should be open and no daughterboard inserted in CN13 NFC

connector.

Out

PB13 s disconnected from the LCD glass module daughterboard

connector. It can be shunted to touch sensing (SB6 closed).

Table 8. Configuration elements related with USB OTG FS port (continued)

Element Setting Description

Page 26

Hardware layout and configuration UM1855

26/100 DocID027351 Rev 3

For configuration elements related with the RS-232 port operation, refer to Tab l e 6 and

Tabl e 9.

Section 2.10 brings information on using the LPUART port of STM32L476ZGT6 for RS-232,

instead of its USART1 port.

2.9.2 IrDA port

The IrDA communication port uses an IrDA transceiver (U11). Ta bl e 9 shows the

configuration elements related with the IrDA port operation

.

2.9.3 Limitations

The operation of RS-232 and IrDA ports is mutually exclusive. The operation of either port is

also mutually exclusive with the NFC peripheral operation.

2.9.4 Operating voltage

The RS-232- and IrDA-related operating supply voltage of STM32L476ZGT6 (VDD line)

must be within the range from 1.71 V to 3.6 V.

2.10 LPUART port

On top of USART1 port for serial communication, the STM32L476ZGT6 offers LPUART, a

low-power UART port.

Table 9. Settings of configuration elements for RS-232 and IrDA ports

Element Setting Description

JP15

JP15

Default setting.

RS-232 selected: PB7 port of STM32L476ZGT6 receives signal

originating from RXD terminal of CN9.

JP15

IrDA selected: PB7 port of STM32L476ZGT6 is connected with RxD

terminal of the IrDA transceiver U11.

JP15

NFC selected: PB7 port of STM32L476ZGT6 receives NFC_IRQOUT

signal from NFC peripheral. Section 2.28 provides more detail on the

NFC peripheral.

R93, R118,

R116

In Required for IrDA operation

R158, R119 Out Required for IrDA operation

3

1

5

4

6

2

3

1

5

4

6

2

3

1

5

4

6

2

Page 27

DocID027351 Rev 3 27/100

UM1855 Hardware layout and configuration

99

In the default configuration of STM32L476G-EVAL, the RX and TX terminals of the LPUART

port are routed to the USB virtual COM port of ST-LINK/V2-1 and, the RX and TX terminals

of USART1 port to the RS-232 connector CN9.

For specific purposes, the TX and RX of the LPUART port of STM32L476ZGT6 can be

routed to the RS-232 connector CN9 instead. As RTS and CTS terminals of CN9 keep

routed to USART1 port, they may block the LPUART communication flow. To avoid this, set

the USART1 hardware flow control off.

The default settings of LPUART are: 115200b/s, 8bits, no parity, 1 stop bit, no flow control.

2.11 microSD card

The CN18 slot for microSD card is routed to STM32L476ZGT6’s SDIO port, accepting SD

(up to 2 Gbytes), SDHC (up to 32 Gbytes) and SDXC (up to 2 Tbytes) cards. One 4-Gbyte

microSD card is delivered as part of STM32L476G-EVAL. The card insertion switch is

routed to the PA8 GPIO port.

For microSD card operation, the LCD glass module daughterboard must be plugged into

CN11 and CN14 in I/O-bridge position, as explained in Section 2.15.

2.11.1 Limitations

Due to the share of SDIO port and PA8 terminals, the following limitations apply:

• The microSD card cannot be operated simultaneously with LCD glass module or with

motor control.

• The microSD card insertion cannot be detected when the PA8 is used as

microcontroller clock output (MCO), one of alternate functions of PA8.

2.11.2 Operating voltage

The supply voltage for STM32L476G-EVAL microSD card operation must be within the

range from 2.7 V to 3.6 V.

Table 10. Hardware settings for LPUART

LPUART port use R188 R189 R158 R119 R118 JP15 1-2

Default setting

USB virtual COM port of ST-LINK/V2-1

In In Out Out

don’t

care

don’t

care

RS-232 (RX and TX) Out Out In In Out Closed

Table 11. Terminals of CN18 microSD slot

Terminal Terminal name (MCU port) Terminal Terminal name (MCU port)

1 SDIO_D2 (PC10) 6 Vss/GND

2 SDIO_D3 (PC11) 7 SDIO_D0 (PC8)

3 SDIO_CMD (PD2) 8 SDIO_D1 (PC9)

4 VDD 9 GND

5 SDIO_CLK (PC12) 10 MicroSDcard_detect (PA8)

Page 28

Hardware layout and configuration UM1855

28/100 DocID027351 Rev 3

2.12 Motor control

The CN2 connector is designed to receive a motor control (MC) module. Table 12 shows the

assignment of CN2 and STM32L476ZGT6 terminals.

Table 12 also lists the modifications to be made on the board versus its by-default

configuration. See Section 2.12.1 for further details.

Table 12. Motor control terminal and function assignment

Motor control

connector CN2

STM32L476ZGT6 microcontroller

Terminal

Ter minal

name

Port name Function

Alternate

function

Board modifications for

enabling motor control

1

Emergency

Stop

PC9 TIM8_BKIN2 -

Close SB29

Remove MB979 daughterboard

2GND - GND - -

3 PWM_1H PC6 TIM8_CH1 -

Close SB27

Open SB2

Remove MB979 daughterboard

4GND - GND - -

5 PWM_1L PA7 TIM8_CH1N -

Close SB19

Open SB18

Remove R66

6GND - GND - -

7 PWM_2H PC7 TIM8_CH2 -

Close SB30

Open SB4

Remove R33

8GND - GND - -

9 PWM_2L PB0 TIM8_CH2N -

Close SB15

Open SB14

Remove R62

10 GND - GND - -

11 PWM_3H PC8 TIM8_CH3 -

Close SB28

Remove MB979 daughterboard

12 GND - GND - -

13 PWM_3L PB1 TIM8_CH3N -

Close SB13

Open SB12

14 Bus Voltage PC5 ADC12_IN -

Close SB16

Remove MB979 daughterboard

15

PhaseA

current+

PC0 ADC123_IN -

Close SB34

Remove MB979 daughterboard

16

PhaseA

current-

-GND - -

17

PhaseB

current+

PC1 ADC123_IN - Close SB36

Page 29

DocID027351 Rev 3 29/100

UM1855 Hardware layout and configuration

99

2.12.1 Board modifications to enable motor control

Figure 7 (top side) and Figure 8 (bottom side) illustrate the board modifications listed in

Table 12, required for the operation of motor control. Red color denotes a component to

remove. Green color denotes a component to be fitted.

18

PhaseB

current-

-GND - -

19

PhaseC

current+

PC2 ADC123_IN -

Close SB42

Remove MB979 daughterboard

20

PhaseC

current-

-GND - -

21 ICL Shutout PG6 GPIO -

Close SB5

Remove R35

22 GND - GND - -

23

Dissipative

Brake

PB2 GPIO -

Close SB11

Remove R54

24

PFC ind.

curr.

PC4 ADC12_IN -

Close SB17

Remove MB979 daughterboard

25 +5V - +5V - -

26

Heatsink

Te mp .

PA3 ADC12_IN -

Close SB22

Remove MB979 daughterboard

27 PFC Sync PF9 TIM15_CH1 -

Close SB25

Remove R90

28 +3.3V - +3.3V - -

29 PFC PWM PF10 TIM15_CH2 -

Close SB37

Remove R91

30

PFC

Shutdown

PB12 TIM15_BKIN -

Close SB3

Remove MB979 daughterboard

31 Encoder A PA0 TIM2_CH1 ADC12_IN

Close SB35

Remove R83

32 PFC Vac PA6 ADC12_IN -

Close SB20

Open SB21

Remove MB979 daughterboard

33 Encoder B PA1 TIM2_CH2 ADC12_IN

Close SB32

Remove MB979 daughterboard

34

Encoder

Index

PA2 TIM2_CH3 ADC12_IN

Close SB31

Remove MB979 daughterboard

Table 12. Motor control terminal and function assignment (continued)

Motor control

connector CN2

STM32L476ZGT6 microcontroller

Terminal

Ter minal

name

Port name Function

Alternate

function

Board modifications for

enabling motor control

Page 30

Hardware layout and configuration UM1855

30/100 DocID027351 Rev 3

Figure 7. PCB top-side rework for motor control

Page 31

DocID027351 Rev 3 31/100

UM1855 Hardware layout and configuration

99

Figure 8. PCB underside rework for motor control

2.12.2 Limitations

Motor control operation is exclusive with LCD glass module, Quad-SPI Flash memory

device, audio codec, potentiometer, LDR, smartcard, LED1 drive and the use of sigma-delta

modulators.

2.13 CAN

The STM32L476G-EVAL board supports one CAN2.0A/B channel compliant with CAN

specification. The CN5 9-pole male connector of DE-9M type is available as CAN interface.

A 3.3 V CAN transceiver is fitted between the CN5 connector and the CAN controller port of

STM32L476ZGT6.

The JP4 jumper allows selecting one of high-speed, standby and slope control modes of the

CAN transceiver. The JP6 jumper can fit a CAN termination resistor in.

Page 32

Hardware layout and configuration UM1855

32/100 DocID027351 Rev 3

2.13.1 Limitations

CAN operation is exclusive with LCD glass module operation.

2.13.2 Operating voltage

The supply voltage for STM32L476G-EVAL CAN operation must be within the range from

3.0 V to 3.6 V.

2.14 Extension connectors CN6 and CN7

The CN6 and CN7 headers complement the LCD glass module daughterboard connector, to

give access to all GPIOs of the STM32L476ZGT6 microcontroller. In addition to GPIOs, the

following signals and power supply lines are also routed on CN6 or CN7:

• GND

• +3V3

• DSV

• RESET#

• VDD

• Clock terminals PC14-OSC32_IN, PC15-OSC32_OUT, PH0-OSC_IN, PH1-OSC_OUT

Each header has two rows of 20 pins, with 1.27 mm pitch and 2.54 mm row spacing. For

extension modules, SAMTEC RSM-120-02-L-D-xxx and SMS-120-x-x-D can be

recommended as SMD and through-hole receptacles, respectively (x is a wild card).

2.15 LCD glass module daughterboard

The MB979 daughterboard delivered in the STM32L476G-EVAL package bears a

segmented LCD glass module. The daughterboard inserts into CN11 and CN14 extension

headers of the main board, each having two rows of pins. The corresponding female

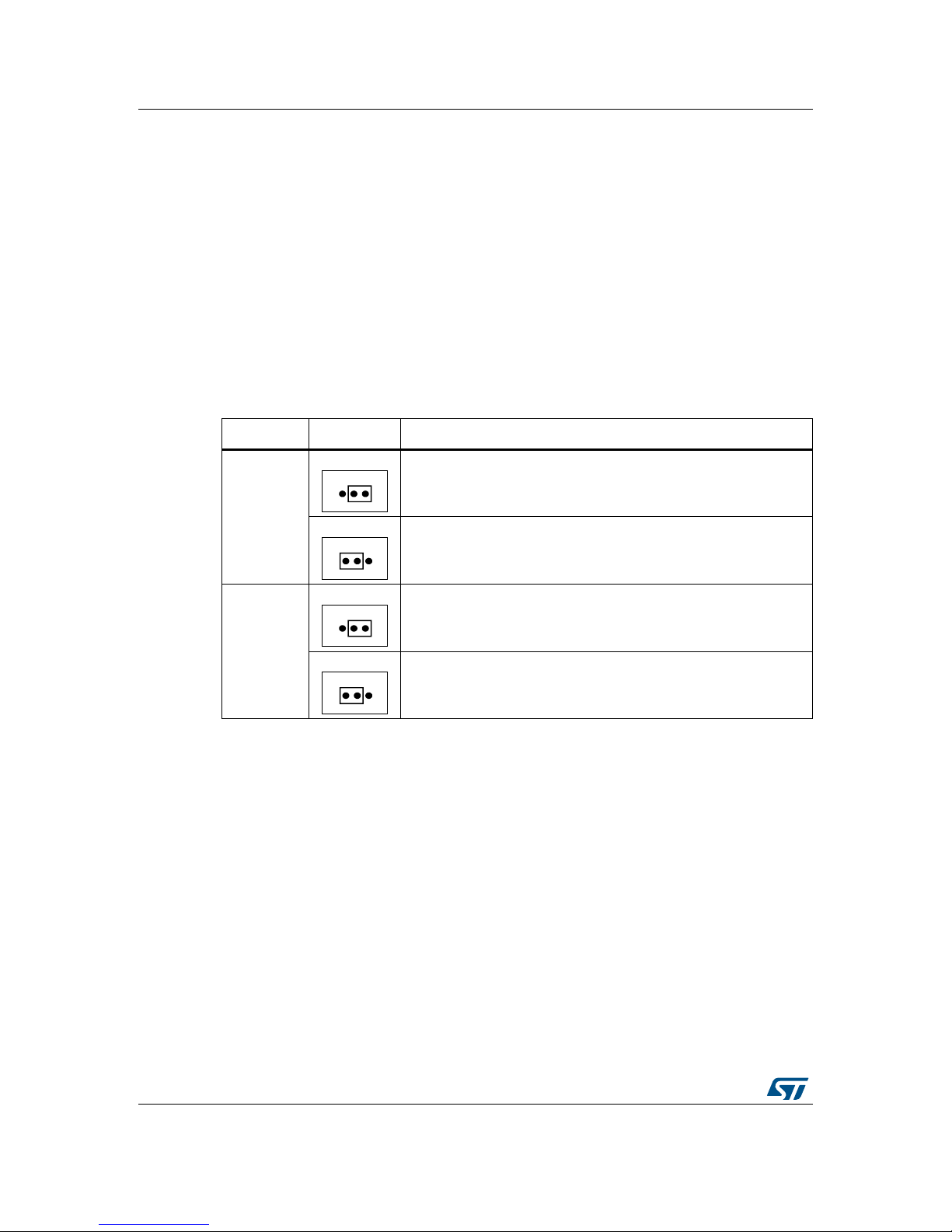

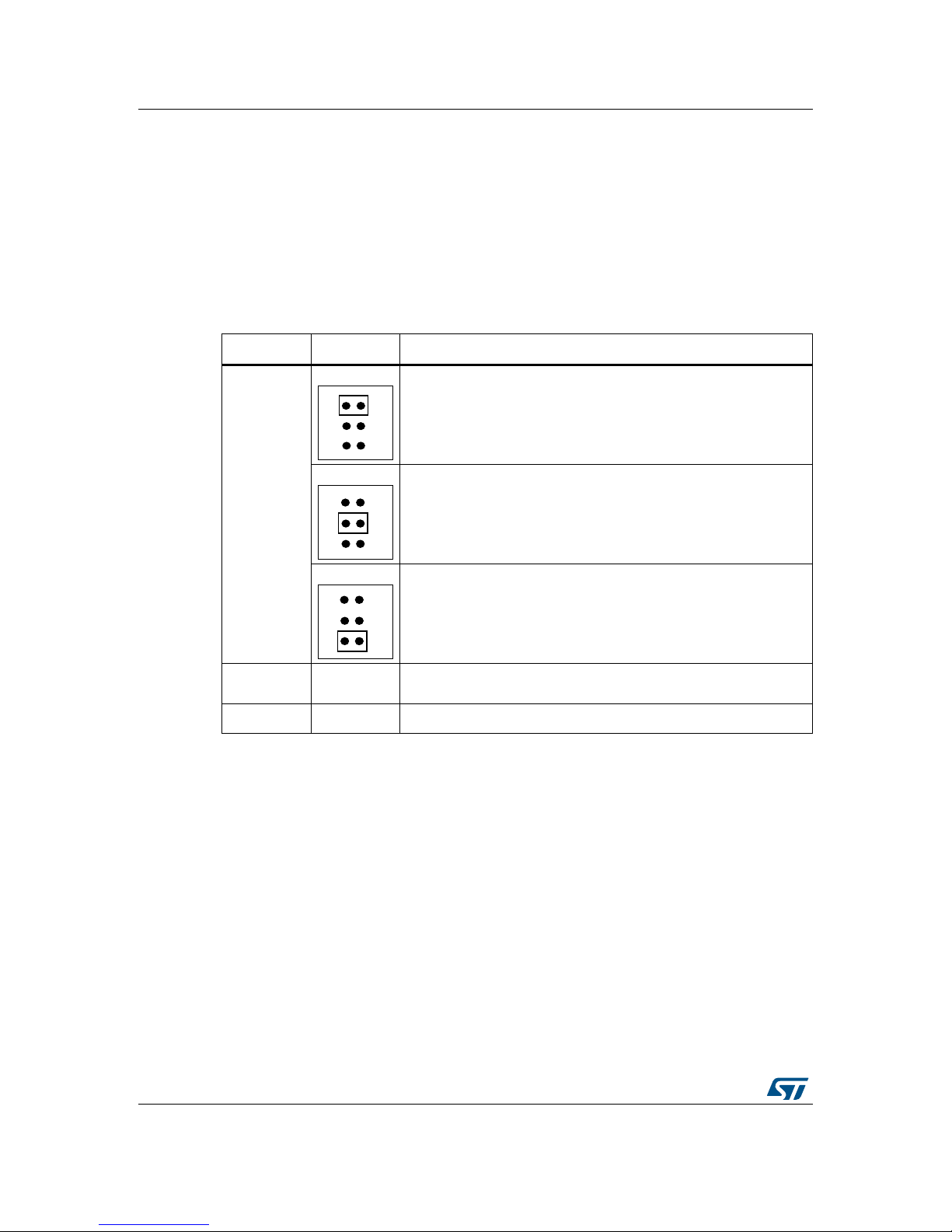

Table 13. CAN related jumpers

Jumper Setting Configuration

JP4

JP4

Default setting

CAN transceiver operates in high-speed mode

JP4

CAN transceiver is in standby mode

JP6

JP6

No termination resistor on CAN physical link

JP6

Default setting

Termination resistor fitted on CAN physical link

Page 33

DocID027351 Rev 3 33/100

UM1855 Hardware layout and configuration

99

connectors on the daughterboard have three rows of holes each. One raw is routed to

segments of the LCD. The other two rows are interconnected and form a series of jumpers.

The way of inserting the LCD glass module daughterboard into CN11 and CN14 headers

determines two functions of LCD glass module daughterboard. In its display function,

STM32L476ZGT6 terminals are routed to LCD segments. In its I/O-bridge function, they are

not. Instead, they transit from one row of CN11 pins to the other and from one row of CN14

pins to the other, thanks to interconnections fitted by the LCD glass module daughterboard.

Figure 9 shows how the LCD glass module daughterboard must be positioned for display

function. This position is designated in the document as display position.

Figure 10 shows how the LCD glass module daughterboard must be positioned for I/O-

bridge function. This position is designated in the document as I/O-bridge position.

The arrow indicates the side of the CN11 and CN14 headers where the extra row of holes of

each female counterpart on the LCD glass module daughterboard has to protrude.

When the LCD glass module daughterboard is not plugged in, CN11 and CN14 give access

to ports of the target microcontroller. Figure 36 shows the related schematic diagram.

Table 14 shows the default settings of board configuration elements linked with CN11 and

CN14 extension connectors and LCD glass module daughterboard.

Figure 9. LCD glass module daughterboard in display position

Page 34

Hardware layout and configuration UM1855

34/100 DocID027351 Rev 3

Figure 10. LCD glass module daughterboard in I/O-bridge position

Table 14. LCD-daughterboard-related configuration elements

LCD

segment

Element

Setting to enable

LCD glass

module

Description

SEG0

R82 In PA1 routed to LCDSEG0

SB32 Open PA1 not routed to motor control

SEG1

R81 In PA2 routed to LCDSEG1

SB31 Open PA2 not routed to motor control

SEG2

R78 In PA3 routed to LCDSEG2

SB22 Open PA3 not routed to motor control

SEG3

R68 In PA6 routed to LCDSEG3

SB21 Open PA6 not routed to Quad-SPI Flash memory device

SB20 Open PA6 not routed to motor control

SEG4

R66 In PA7 routed to LCDSEG4

SB18 Open PA7 not routed to Quad-SPI Flash memory device

SB19 Open PA7 not routed to motor control

SEG5

R62 In PB0 routed to LCDSEG5

SB14 Open PB0 not routed to Quad-SPI Flash memory device

SB15 Open PB0 not routed to motor control

SEG6

R56 In PB1 routed to LCDSEG6

SB12 Open PB1 not routed to Quad-SPI Flash memory device

SB13 Open PB1 not routed to motor control

SEG10

R50 In PB10 routed to LCDSEG10

SB9 Open PB10 not routed to Quad-SPI Flash memory device

Page 35

DocID027351 Rev 3 35/100

UM1855 Hardware layout and configuration

99

The custom LCD glass module used on MB979 daughterboard is XHO5002B. To optimize

the number of driving signals, the display elements are connected to eight common planes

called COMx (LCDCOMx in the schematic digrams), where “x” can be substituted with

figures from “0” to “7”. The other pole of each display element is called segment, SEGy

(LCDSEGy in the schematic diagrams), where “y” can be substituted with figures from “0” to

“39”. Each combination of COMx and SEGy addresses one display element. Table 15,

Table 16, Table 17 and Table 22 show the LCD element mapping. COMx are ordered in

rows, SEGy in columns. The table cells then display the display element names

SEG11

R48 In PB11 routed to LCDSEG11

SB8 Open PB11 not routed to Quad-SPI Flash memory device

SEG12

R39 In PB12 routed to LCDSEG12

SB3 Open PB12 not routed to Quad-SPI Flash memory device

SEG13

R38 In PB13 routed to LCDSEG13

SB6 Open PB13 not routed to Touch sensing

SEG18

R97 In PC0 routed to LCDSEG18

SB34 Open PC0 not routed to motor control

SEG19

R98 In PC1 routed to LCDSEG19

SB36 Open PC1 not routed to motor control

SEG20

R99 In PC2 routed to LCDSEG20

SB42 Open PC2 not routed to motor control

SEG22

R65 In PC4 routed to LCDSEG22

SB17 Open PC4 not routed to motor control

SEG23

R64 In PC5 routed to LCDSEG23

SB16 Open PC5 not routed to motor control

SEG24

R36 In PC6 routed to LCDSEG24

SB2 Open PC6 not routed to Touch sensing