STMicroelectronics STM32H747AI, STM32H747BI, STM32H747II, STM32H747XI, STM32H747ZI User manual

...

STM32H747xI/G

UFBGA169

(7 × 7 mm)

TFBGA240+25

(14x14 mm)

LQFP176

(24x24 mm)

LQFP208

(28x28 mm)

WLCSP156

(4.96x4.64 mm)

Dual 32-bit Arm® Cortex®-M7 up to 480MHz and -M4 MCUs, up to

2MB Flash, 1MB RAM, 46 com. and analog interfaces, SMPS, DSI

Datasheet - production data

Features

Dual core

• 32-bit Arm® Cortex®-M7 core with double-

precision FPU and L1 cache: 16 Kbytes of data

and 16 Kbytes of instruction cache; frequency

up to 480 MHz, MPU, 1027 DMIPS/

2.14 DMIPS/MHz (Dhrystone 2.1), and DSP

instructions

• 32-bit Arm

Adaptive real-time accelerator (ART

Accelerator™) for internal Flash memory and

external memories, frequency up to 240 MHz,

MPU, 300 DMIPS/1.25 DMIPS /MHz

(Dhrystone 2.1), and DSP instructions

Memories

• Up to 2 Mbytes of Flash memory with readwhile-write support

• 1 Mbyte of RAM: 192 Kbytes of TCM RAM (inc.

64 Kbytes of ITCM RAM + 128 Kbytes of

DTCM RAM for time critical routines),

864 Kbytes of user SRAM, and 4 Kbytes of

SRAM in Backup domain

• Dual mode Quad-SPI memory interface

running up to 133 MHz

• Flexible external memory controller with up to

32-bit data bus: SRAM, PSRAM,

SDRAM/LPSDR SDRAM, NOR/NAND Flash

memory clocked up to 125 MHz in

Synchronous mode

• CRC calculation unit

®

32-bit Cortex®-M4 core with FPU,

FBGA

Reset and power management

• 3 separate power domains which can be

independently clock-gated or switched off:

– D1: high-performance capabilities

– D2: communication peripherals and timers

– D3: reset/clock control/power management

• 1.62 to 3.6 V application supply and I/Os

• POR, PDR, PVD and BOR

• Dedicated USB power embedding a 3.3 V

internal regulator to supply the internal PHYs

• Embedded regulator (LDO) to supply the digital

circuitry

• High power-efficiency SMPS step-down

converter regulator to directly supply V

and/or external circuitry

• Voltage scaling in Run and Stop mode (6

configurable ranges)

• Backup regulator (~0.9 V)

• Voltage reference for analog peripheral/V

• 1.2 to 3.6 V V

BAT

supply

• Low-power modes: Sleep, Stop, Standby and

V

supporting battery charging

BAT

CORE

REF+

Security

• ROP, PC-ROP, active tamper

Low-power consumption

• V

battery operating mode with charging

BAT

capability

General-purpose input/outputs

• Up to 168 I/O ports with interrupt capability

• CPU and domain power state monitoring pins

• 2.95 µA in Standby mode (Backup SRAM OFF,

RTC/LSE ON)

May 2019 DS12930 Rev 1 1/242

This is information on a product in full production.

www.st.com

STM32H747xI/G

Clock management

• Internal oscillators: 64 MHz HSI, 48 MHz

HSI48, 4 MHz CSI, 32 kHz LSI

• External oscillators: 4-48 MHz HSE,

32.768 kHz LSE

• 3× PLLs (1 for the system clock, 2 for kernel

clocks) with Fractional mode

Interconnect matrix

• 3 bus matrices (1 AXI and 2 AHB)

• Bridges (5× AHB2-APB, 2× AXI2-AHB)

4 DMA controllers to unload the CPU

• 1× high-speed master direct memory access

controller (MDMA) with linked list support

• 2× dual-port DMAs with FIFO

• 1× basic DMA with request router capabilities

Up to 35 communication peripherals

• 4× I2Cs FM+ interfaces (SMBus/PMBus)

• 4× USARTs/4x UARTs (ISO7816 interface,

LIN, IrDA, up to 12.5 Mbit/s) and 1x LPUART

• 6× SPIs, 3 with muxed duplex I2S audio class

accuracy via internal audio PLL or external

clock, 1x I2S in LP domain (up to 150 MHz)

• 4x SAIs (serial audio interface)

• SPDIFRX interface

• SWPMI single-wire protocol master I/F

• MDIO Slave interface

• 2× SD/SDIO/MMC interfaces (up to 125 MHz)

• 2× CAN controllers: 2 with CAN FD, 1 with

time-triggered CAN (TT-CAN)

• 2× USB OTG interfaces (1FS, 1HS/FS) crystalless solution with LPM and BCD

• Ethernet MAC interface with DMA controller

• HDMI-CEC

• 8- to 14-bit camera interface (up to 80 MHz)

11 analog peripherals

• 2× operational amplifiers (7.3 MHz bandwidth)

• 1× digital filters for sigma delta modulator

(DFSDM) with 8 channels/4 filters

Graphics

• LCD-TFT controller up to XGA resolution

• MIPI DSI host including an MIPI D-PHY to

interface with low-pin count large displays

• Chrom-ART graphical hardware Accelerator™

(DMA2D) to reduce CPU load

• Hardware JPEG Codec

Up to 22 timers and watchdogs

• 1× high-resolution timer (2.1 ns max

resolution)

• 2× 32-bit timers with up to 4 IC/OC/PWM or

pulse counter and quadrature (incremental)

encoder input (up to 240 MHz)

• 2× 16-bit advanced motor control timers (up to

240 MHz)

• 10× 16-bit general-purpose timers (up to

240 MHz)

• 5× 16-bit low-power timers (up to 240 MHz)

• 4× watchdogs (independent and window)

• 2× SysTick timers

• RTC with sub-second accuracy and hardware

calendar

Debug mode

• SWD & JTAG interfaces

• 4-Kbyte Embedded Trace Buffer

True random number generators (3

oscillators each)

96-bit unique ID

All packages are ECOPACK

Table 1. Device summary

Reference Part number

®

2 compliant

• 3× ADCs with 16-bit max. resolution (up to 36

channels, up to 3.6 MSPS)

• 1× temperature sensor

• 2× 12-bit D/A converters (1 MHz)

• 2× ultra-low-power comparators

2/242 DS12930 Rev 1

STM32H747xISTM32H747AI, STM32H747BI,

STM32H747xGSTM32H747AG, STM32H747BG,

STM32H747II, STM32H747XI, STM32H747ZI

STM32H747IG, STM32H747XG

STM32H747xI/G Contents

Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 Functional overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.1 Dual Arm® Cortex® cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

3.1.1 Arm® Cortex®-M7 with FPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.1.2 Arm

3.2 Memory protection unit (MPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3 Memories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.3.1 Embedded Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.3.2 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.3.3 ART™ accelerator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

®

Cortex®-M4 with FPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.4 Boot modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.5 Power supply management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.1 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.2 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.5.3 Voltage regulator (SMPS step-down converter and LDO) . . . . . . . . . . . 18

3.5.4 SMPS step-down converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.6 Low-power strategy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.7 Reset and clock controller (RCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.7.1 Clock management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.7.2 System reset sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.8 General-purpose input/outputs (GPIOs) . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.9 Bus-interconnect matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.10 DMA controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.11 Chrom-ART Accelerator™ (DMA2D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.12 Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . . 24

3.13 Extended interrupt and event controller (EXTI) . . . . . . . . . . . . . . . . . . . . 24

3.14 Cyclic redundancy check calculation unit (CRC) . . . . . . . . . . . . . . . . . . . 24

3.15 Flexible memory controller (FMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.16 Quad-SPI memory interface (QUADSPI) . . . . . . . . . . . . . . . . . . . . . . . . . 25

DS12930 Rev 1 1/242

4

Contents STM32H747xI/G

3.17 Analog-to-digital converters (ADCs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.18 Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.19 V

operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

BAT

3.20 Digital-to-analog converters (DAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.21 Ultra-low-power comparators (COMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.22 Operational amplifiers (OPAMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.23 Digital filter for sigma-delta modulators (DFSDM) . . . . . . . . . . . . . . . . . . 28

3.24 Digital camera interface (DCMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.25 LCD-TFT controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.26 DSI Host (DSI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.27 JPEG Codec (JPEG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.28 Random number generator (RNG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.29 Timers and watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.29.1 High-resolution timer (HRTIM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.29.2 Advanced-control timers (TIM1, TIM8) . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.29.3 General-purpose timers (TIMx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.29.4 Basic timers TIM6 and TIM7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.29.5 Low-power timers (LPTIM1, LPTIM2, LPTIM3, LPTIM4, LPTIM5) . . . . 36

3.29.6 Independent watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.29.7 Window watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.29.8 SysTick timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.30 Real-time clock (RTC), backup SRAM and backup registers . . . . . . . . . . 37

3.31 Inter-integrated circuit interface (I

2

C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.32 Universal synchronous/asynchronous receiver transmitter (USART) . . . 38

3.33 Low-power universal asynchronous receiver transmitter (LPUART) . . . . 39

3.34 Serial peripheral interface (SPI)/inter- integrated sound interfaces (I2S) . 40

3.35 Serial audio interfaces (SAI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.36 SPDIFRX Receiver Interface (SPDIFRX) . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.37 Single wire protocol master interface (SWPMI) . . . . . . . . . . . . . . . . . . . . 41

3.38 Management Data Input/Output (MDIO) slaves . . . . . . . . . . . . . . . . . . . . 42

3.39 SD/SDIO/MMC card host interfaces (SDMMC) . . . . . . . . . . . . . . . . . . . . 42

3.40 Controller area network (FDCAN1, FDCAN2) . . . . . . . . . . . . . . . . . . . . . 42

3.41 Universal serial bus on-the-go high-speed (OTG_HS) . . . . . . . . . . . . . . . 43

3.42 Ethernet MAC interface with dedicated DMA controller (ETH) . . . . . . . . . 43

2/242 DS12930 Rev 1

STM32H747xI/G Contents

3.43 High-definition multimedia interface (HDMI)

- consumer electronics control (CEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.44 Debug infrastructure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4 Memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5 Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

6 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.1 Parameter conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.1.1 Minimum and maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.1.2 Typical values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.1.3 Typical curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.1.4 Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.1.5 Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.1.6 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

6.1.7 Current consumption measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.2 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.3 Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

6.3.1 General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

6.3.2 VCAP external capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

6.3.3 SMPS step-down converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

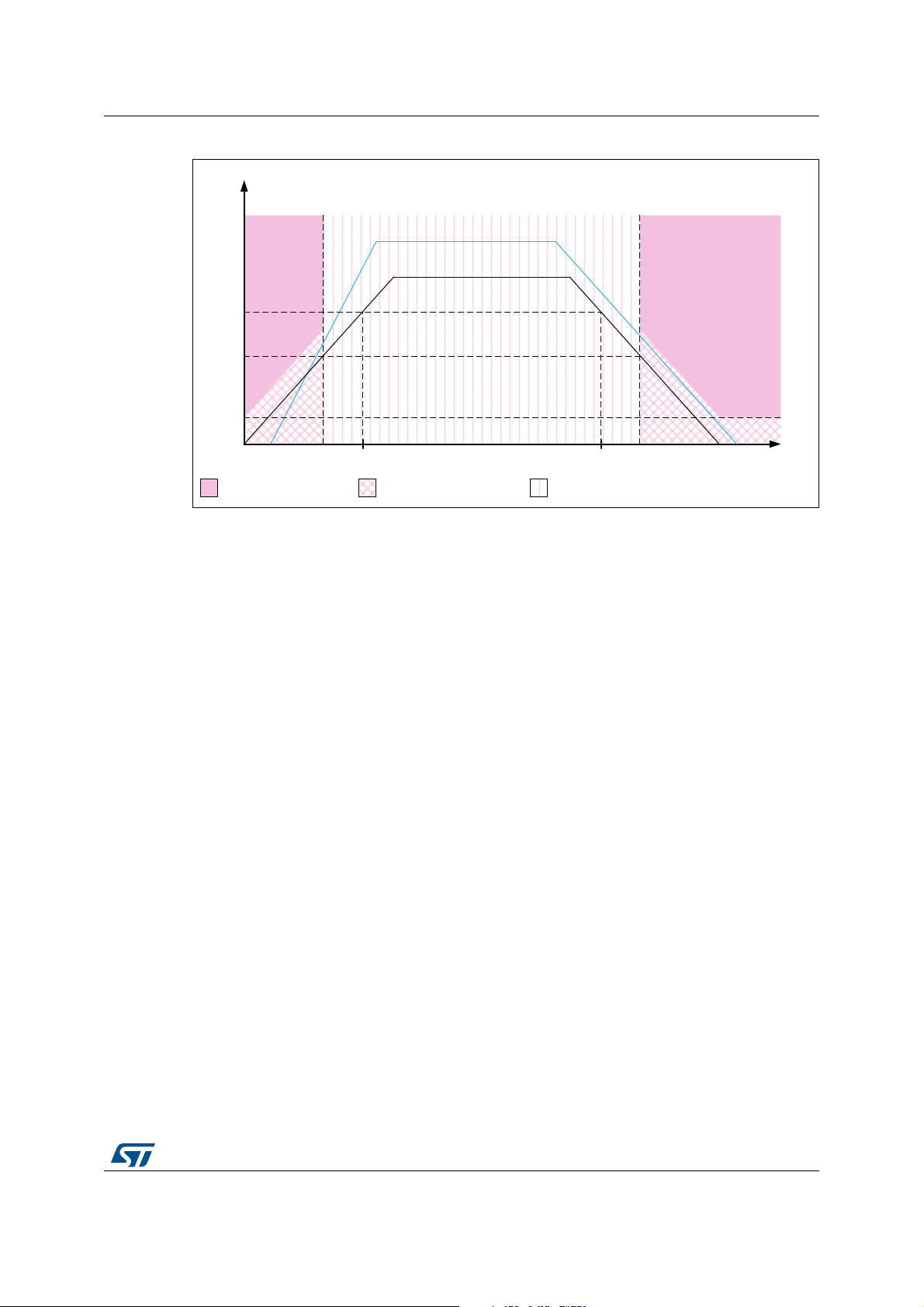

6.3.4 Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . 105

6.3.5 Embedded reset and power control block characteristics . . . . . . . . . . 106

6.3.6 Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.3.7 Supply current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

6.3.8 Wakeup time from low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . 128

6.3.9 External clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 129

6.3.10 Internal clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 133

6.3.11 PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

6.3.12 MIPI D-PHY characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

6.3.13 MIPI D-PHY regulator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 140

6.3.14 Memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

6.3.15 EMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

6.3.16 Absolute maximum ratings (electrical sensitivity) . . . . . . . . . . . . . . . . 144

6.3.17 I/O current injection characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

6.3.18 I/O port characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

DS12930 Rev 1 3/242

4

Contents STM32H747xI/G

6.3.19 NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

6.3.20 FMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

6.3.21 Quad-SPI interface characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

6.3.22 Delay block (DLYB) characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

6.3.23 16-bit ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

6.3.24 DAC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

6.3.25 Voltage reference buffer characteristics . . . . . . . . . . . . . . . . . . . . . . . 190

6.3.26 Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

6.3.27 Temperature and V

6.3.28 Voltage booster for analog switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

6.3.29 Comparator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

6.3.30 Operational amplifier characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 194

6.3.31 Digital filter for Sigma-Delta Modulators (DFSDM) characteristics . . . 196

6.3.32 Camera interface (DCMI) timing specifications . . . . . . . . . . . . . . . . . . 199

6.3.33 LCD-TFT controller (LTDC) characteristics . . . . . . . . . . . . . . . . . . . . . 200

6.3.34 Timer characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

6.3.35 Communication interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

BAT

7 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

7.1 WLCSP156 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

7.2 UFBGA169 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

7.3 LQFP176 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

7.4 LQFP208 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

7.5 TFBGA240+25 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

7.6 Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

7.6.1 Reference document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

8 Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

9 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

4/242 DS12930 Rev 1

STM32H747xI/G List of tables

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Table 1. STM32H747xI/G features and peripheral counts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 2. System vs domain low-power mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 3. DFSDM implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 4. Timer feature comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 5. USART features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 6. Legend/abbreviations used in the pinout table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 7. STM32H747xI/G pin/ball definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 8. Port A alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 9. Port B alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 10. Port C alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 11. Port D alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 12. Port E alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 13. Port F alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 14. Port G alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 15. Port H alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 16. Port I alternate functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 17. Port J alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 18. Port K alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 19. Voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 20. Current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 21. Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 22. General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 23. Supply voltage and maximum frequency configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 24. VCAP operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 25. Characteristics of SMPS step-down converter external components . . . . . . . . . . . . . . . . 104

Table 26. SMPS step-down converter characteristics for external usage . . . . . . . . . . . . . . . . . . . . 105

Table 27. Operating conditions at power-up / power-down (regulator ON) . . . . . . . . . . . . . . . . . . . 105

Table 28. Reset and power control block characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 29. Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 30. Internal reference voltage calibration values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 31. Typical and maximum current consumption in Run mode, code with data processing

running from ITCM for Cortex-M7 core, and Flash memory for Cortex-M4

(ART accelerator ON), LDO regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 32. Typical and maximum current consumption in Run mode, code with data processing

running from ITCM for Arm Cortex-M7 and Flash memory for Arm Cortex-M4,

ART accelerator ON, SMPS regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 33. Typical and maximum current consumption in Run mode, code with data processing

running from Flash memory, both cores running, cache ON,

ART accelerator ON, LDO regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 34. Typical and maximum current consumption in Run mode, code with data processing

running from Flash memory, both cores running, cache OFF,

ART accelerator OFF, LDO regulator ON. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 35. Typical and maximum current consumption in Run mode, code with data processing

running from ITCM, only Arm Cortex-M7 running, LDO regulator ON . . . . . . . . . . . . . . . 111

Table 36. Typical and maximum current consumption in Run mode, code with data processing

running from ITCM, only Arm Cortex-M7 running, SMPS regulator. . . . . . . . . . . . . . . . . 112

Table 37. Typical and maximum current consumption in Run mode, code with data processing

DS12930 Rev 1 1/242

4

List of tables STM32H747xI/G

running from Flash memory, only Arm Cortex-M7 running, cache ON,

LDO regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 38. Typical and maximum current consumption in Run mode, code with data processing

running from Flash memory, only Arm Cortex-M7 running, cache OFF,

LDO regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 39. Typical and maximum current consumption batch acquisition mode,

LDO regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 40. Typical and maximum current consumption in Run mode, code with data processing

running from Flash memory, only Arm Cortex-M4 running, ART accelerator ON,

LDO regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 41. Typical and maximum current consumption in Run mode, code with data processing

running from Flash bank 2, only Arm Cortex-M4 running, ART accelerator ON,

SMPS regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 42. Typical and maximum current consumption in Stop, LDO regulator ON . . . . . . . . . . . . . 115

Table 43. Typical and maximum current consumption in Stop, SMPS regulator . . . . . . . . . . . . . . . 116

Table 44. Typical and maximum current consumption in Sleep mode, LDO regulator . . . . . . . . . . 117

Table 45. Typical and maximum current consumption in Sleep mode, SMPS regulator . . . . . . . . . 117

Table 46. Typical and maximum current consumption in Standby . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 47. Typical and maximum current consumption in VBAT mode . . . . . . . . . . . . . . . . . . . . . . . 118

Table 48. Peripheral current consumption in Run mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 49. Low-power mode wakeup timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 50. High-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Table 51. Low-speed external user clock characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Table 52. 4-48 MHz HSE oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Table 53. Low-speed external user clock characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 54. HSI48 oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Table 55. HSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 56. CSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 57. LSI oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 58. PLL characteristics (wide VCO frequency range). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 59. PLL characteristics (medium VCO frequency range) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 60. MIPI D-PHY characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 61. MIPI D-PHY AC characteristics LP mode and HS/LP

transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Table 62. DSI regulator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Table 63. Flash memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 64. Flash memory programming (single bank configuration nDBANK=1) . . . . . . . . . . . . . . . 141

Table 65. Flash memory endurance and data retention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Table 66. EMS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Table 67. EMI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Table 68. ESD absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 69. Electrical sensitivities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 70. I/O current injection susceptibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 71. I/O static characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 72. Output voltage characteristics for all I/Os except PC13, PC14, PC15 and PI8 . . . . . . . . 148

Table 73. Output voltage characteristics for PC13, PC14, PC15 and PI8 . . . . . . . . . . . . . . . . . . . . 149

Table 74. Output timing characteristics (HSLV OFF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Table 75. Output timing characteristics (HSLV ON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 76. NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 77. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings . . . . . . . . . . . . . . . . . 155

Table 78. Asynchronous non-multiplexed SRAM/PSRAM/NOR read-NWAIT timings . . . . . . . . . . . 155

Table 79. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings . . . . . . . . . . . . . . . . . 157

2/242 DS12930 Rev 1

STM32H747xI/G List of tables

Table 80. Asynchronous non-multiplexed SRAM/PSRAM/NOR write-NWAIT timings. . . . . . . . . . . 157

Table 81. Asynchronous multiplexed PSRAM/NOR read timings. . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Table 82. Asynchronous multiplexed PSRAM/NOR read-NWAIT timings . . . . . . . . . . . . . . . . . . . . 159

Table 83. Asynchronous multiplexed PSRAM/NOR write timings . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Table 84. Asynchronous multiplexed PSRAM/NOR write-NWAIT timings . . . . . . . . . . . . . . . . . . . . 160

Table 85. Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 86. Synchronous multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 87. Synchronous non-multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . 166

Table 88. Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Table 89. Switching characteristics for NAND Flash read cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Table 90. Switching characteristics for NAND Flash write cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Table 91. SDRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 92. LPSDR SDRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 93. SDRAM Write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Table 94. LPSDR SDRAM Write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Table 95. QUADSPI characteristics in SDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Table 96. QUADSPI characteristics in DDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Table 97. Delay Block characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Table 98. ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Table 99. Minimum sampling time vs RAIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

Table 100. ADC accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Table 101. DAC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Table 102. DAC accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Table 103. VREFBUF characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Table 104. Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

Table 105. Temperature sensor calibration values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

Table 106. V

Table 107. V

monitoring characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

BAT

charging characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

BAT

Table 108. Temperature monitoring characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Table 109. Voltage booster for analog switch characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Table 110. COMP characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Table 111. Operational amplifier characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Table 112. DFSDM measured timing 1.62-3.6 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 113. DCMI characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Table 114. LTDC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

Table 115. TIMx characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Table 116. Minimum i2c_ker_ck frequency in all I2C modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Table 117. I2C analog filter characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Table 118. USART characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Table 119. SPI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Table 120. I

2

S dynamic characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 121. SAI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Table 122. MDIO Slave timing parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Table 123. Dynamics characteristics: SD / MMC characteristics, VDD=2.7 to 3.6 V . . . . . . . . . . . . . 214

Table 124. Dynamics characteristics: eMMC characteristics VDD=1.71V to 1.9V . . . . . . . . . . . . . . . 215

Table 125. Dynamics characteristics: USB ULPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

Table 126. Dynamics characteristics: Ethernet MAC signals for SMI . . . . . . . . . . . . . . . . . . . . . . . . 218

Table 127. Dynamics characteristics: Ethernet MAC signals for RMII . . . . . . . . . . . . . . . . . . . . . . . . 219

Table 128. Dynamics characteristics: Ethernet MAC signals for MII . . . . . . . . . . . . . . . . . . . . . . . . . 219

Table 129. Dynamics JTAG characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

Table 130. Dynamics SWD characteristics: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Table 131. WLCSP156 package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

DS12930 Rev 1 3/242

4

List of tables STM32H747xI/G

Table 132. WLCSP156 bump recommended PCB design rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Table 133. UFBGA169 package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Table 134. LQFP176 package mechanical data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

Table 135. LQFP208 package mechanical data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

Table 136. TFBG240+25 ball package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

Table 137. TFBGA240+25 recommended PCB design rules (0.8 mm pitch) . . . . . . . . . . . . . . . . . . . 237

Table 138. Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Table 139. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

4/242 DS12930 Rev 1

STM32H747xI/G List of figures

List of figures

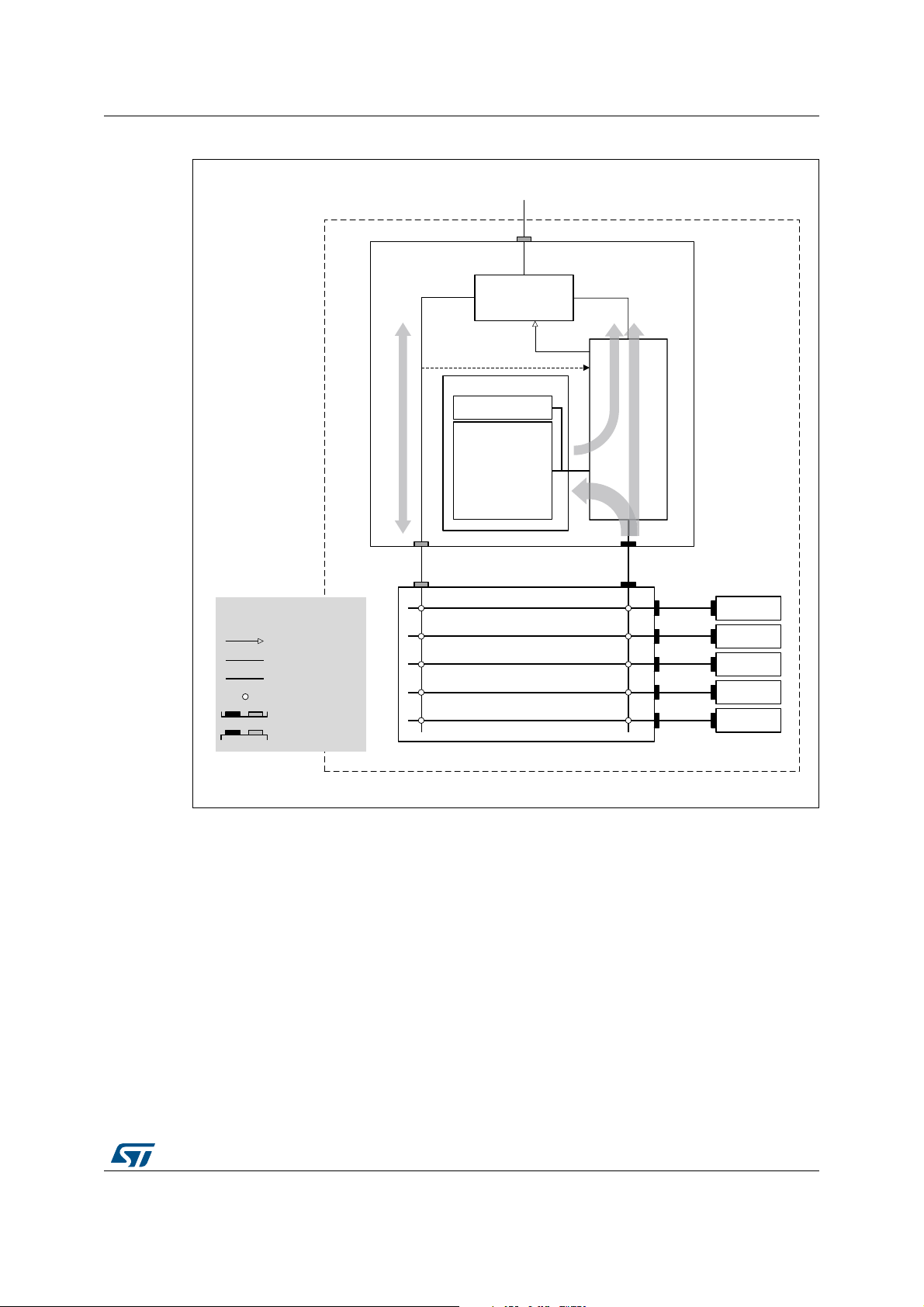

Figure 1. STM32H747xI/G block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

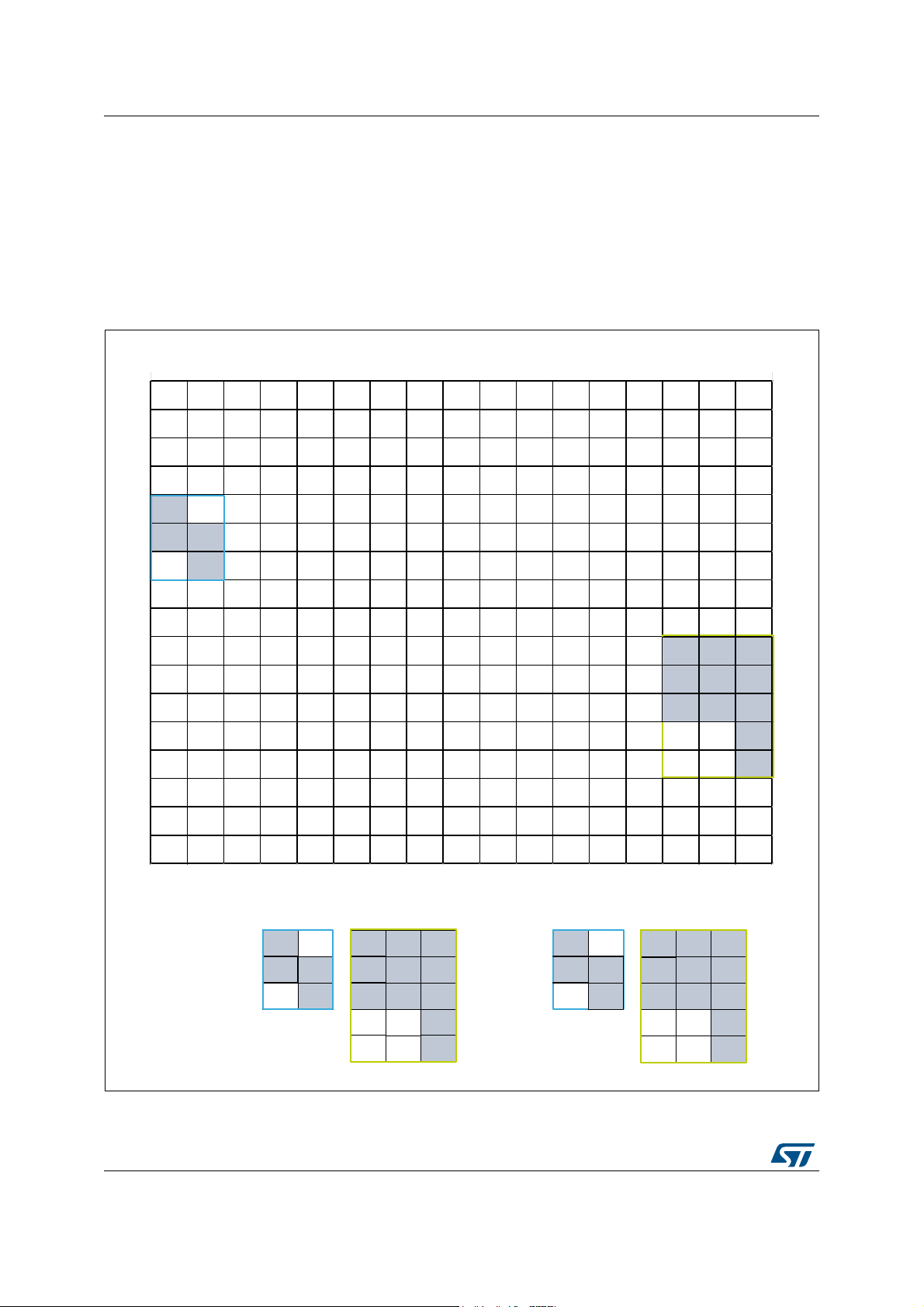

Figure 2. TFBGA240+25 ball assignment differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 3. ART™ accelerator schematic and environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 4. Power-up/power-down sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 5. STM32H747xI/G bus matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 6. WLCSP156 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 7. UFBGA169 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 8. LQFP176 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 9. LQFP208 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 10. TFBGA240+25 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 11. Pin loading conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 12. Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 13. Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 14. Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 15. External capacitor C

Figure 16. External components for SMPS step-down converter . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 17. Typical SMPS efficiency (%) vs load current (A) in Run mode at TJ = 30 °C. . . . . . . . . . 119

Figure 18. Typical SMPS efficiency (%) vs load current (A) in Run mode at TJ = TJmax . . . . . . . . 119

Figure 19. Typical SMPS efficiency (%) vs load current (A) in low-power mode at TJ = 30 °C . . . . . 120

Figure 20. Typical SMPS efficiency (%) vs load current (A) in low-power mode at TJ = TJmax . . . 121

Figure 21. High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 22. Low-speed external clock source AC timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Figure 23. Typical application with an 8 MHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Figure 24. Typical application with a 32.768 kHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Figure 25. MIPI D-PHY HS/LP clock lane transition timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . 140

Figure 26. MIPI D-PHY HS/LP data lane transition timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Figure 27. VIL/VIH for all I/Os except BOOT0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Figure 28. Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Figure 29. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms . . . . . . . . . . . . . . 154

Figure 30. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms . . . . . . . . . . . . . . 156

Figure 31. Asynchronous multiplexed PSRAM/NOR read waveforms. . . . . . . . . . . . . . . . . . . . . . . . 158

Figure 32. Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Figure 33. Synchronous multiplexed PSRAM write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Figure 34. Synchronous non-multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . 165

Figure 35. Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Figure 36. NAND controller waveforms for read access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Figure 37. NAND controller waveforms for write access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Figure 38. NAND controller waveforms for common memory read access . . . . . . . . . . . . . . . . . . . . 170

Figure 39. NAND controller waveforms for common memory write access . . . . . . . . . . . . . . . . . . . . 171

Figure 40. SDRAM read access waveforms (CL = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Figure 41. SDRAM write access waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Figure 42. Quad-SPI timing diagram - SDR mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Figure 43. Quad-SPI timing diagram - DDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Figure 44. ADC accuracy characteristics (12-bit resolution) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Figure 45. Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Figure 46. Power supply and reference decoupling (V

Figure 47. Power supply and reference decoupling (V

Figure 48. 12-bit buffered /non-buffered DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

EXT

not connected to V

REF+

connected to V

REF+

DDA

). . . . . . . . . . . . . 185

DDA

). . . . . . . . . . . . . . . . 185

DS12930 Rev 1 1/242

2

List of figures STM32H747xI/G

Figure 49. Channel transceiver timing diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Figure 50. DCMI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Figure 51. LCD-TFT horizontal timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Figure 52. LCD-TFT vertical timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Figure 53. USART timing diagram in Master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Figure 54. USART timing diagram in Slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Figure 55. SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Figure 56. SPI timing diagram - slave mode and CPHA = 1

Figure 57. SPI timing diagram - master mode

Figure 58. I

Figure 59. I

2

S slave timing diagram (Philips protocol)

2

S master timing diagram (Philips protocol)

(1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

(1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

(1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

(1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Figure 60. SAI master timing waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Figure 61. SAI slave timing waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Figure 62. MDIO Slave timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Figure 63. SDIO high-speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Figure 64. SD default mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Figure 65. DDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Figure 66. ULPI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

Figure 67. Ethernet SMI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

Figure 68. Ethernet RMII timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

Figure 69. Ethernet MII timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

Figure 70. JTAG timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Figure 71. SWD timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Figure 72. WLCSP156 package outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

Figure 73. WLCSP156 bump recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

Figure 74. WLCSP156 marking example (package top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Figure 75. UFBGA169 package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Figure 76. UFBGA169 marking example (package top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Figure 77. LQFP176 package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

Figure 78. LQFP176 package recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

Figure 79. LQFP176 marking example (package top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Figure 80. LQFP208 package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Figure 81. LQFP208 package recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

Figure 82. LQFP208 marking example (package top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

Figure 83. TFBGA240+25 package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

Figure 84. TFBGA240+25 package recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

Figure 85. TFBGA240+25 marking example (package top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

2/242 DS12930 Rev 1

STM32H747xI/G Introduction

1 Introduction

This document provides information on STM32H747xI/G microcontrollers, such as

description, functional overview, pin assignment and definition, electrical characteristics,

packaging, and ordering information.

This document should be read in conjunction

with the STM32H747xI/G reference manual

(RM0399), available from the STMicroelectronics website www.st.com.

For information on the Arm

the Cortex

®

-M7 Technical Reference Manual, available from the http://www.arm.com

®(a)

Cortex®-M7 core and Arm® Cortex®-M4 core, please refer to

website.

a. Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

DS12930 Rev 1 3/242

46

Description STM32H747xI/G

2 Description

STM32H747xI/G devices are based on the high-performance Arm® Cortex®-M7 and

®

Cortex

Cortex

supports Arm

(IEEE 754 compliant), including a full set of DSP instructions and a memory protection unit

(MPU) to enhance application security.

STM32H747xI/G devices incorporate high-speed embedded memories with a dual-bank

Flash memory of up to 2

up to 864

range of enhanced I/Os and peripherals connected to APB buses, AHB buses, 2x32-bit

multi-AHB bus matrix and a multi layer AXI interconnect supporting internal and external

memory access.

All the devices offer three ADCs, two DACs, two ultra-low power comparators, a low-power

RTC, a high-resolution timer, 12 general-purpose 16-bit timers, two PWM timers for motor

control, five low-power timers, a true random number generator (RNG). The devices support

four digital filters for external sigma-delta modulators (DFSDM). They also feature standard

and advanced communication interfaces.

• Standard peripherals

• Advanced peripherals including

-M4 32-bit RISC cores. The Cortex®-M7 core operates at up to 480 MHz and the

®

-M4 core at up to 240 MHz. Both cores feature a floating point unit (FPU) which

®

single- and double-precision (Cortex®-M7 core) operations and conversions

Mbytes, up to 1 Mbyte of RAM (including 192 Kbytes of TCM RAM,

Kbytes of user SRAM and 4 Kbytes of backup SRAM), as well as an extensive

–Four I

2

Cs

– Four USARTs, four UARTs and one LPUART

– Six SPIs, three I

2

Ss in Half-duplex mode. To achieve audio class accuracy, the I2S

peripherals can be clocked by a dedicated internal audio PLL or by an external

clock to allow synchronization.

– Four SAI serial audio interfaces

– One SPDIFRX interface

– One SWPMI (Single Wire Protocol Master Interface)

– Management Data Input/Output (MDIO) slaves

– Two SDMMC interfaces

– A USB OTG full-speed and a USB OTG high-speed interface with full-speed

capability (with the ULPI)

– One FDCAN plus one TT-FDCAN interface

– An Ethernet interface

– Chrom-ART Accelerator

™

– HDMI-CEC

– A flexible memory control (FMC) interface

– A Quad-SPI Flash memory interface

– A camera interface for CMOS sensors

– An LCD-TFT display controller

– A JPEG hardware compressor/decompressor

– A DSI Host interface.

4/242 DS12930 Rev 1

STM32H747xI/G Description

Refer to Tab le 1: STM32H747xI/G features and peripheral counts for the list of peripherals

available on each part number.

STM32H747xI/G devices operate in the –40 to +85 °C temperature range from a 1.62 to

3.6

V power supply. The supply voltage can drop down to 1.62 V by using an external power

supervisor (see

Section 3.5.2: Power supply supervisor) and connecting the PDR_ON pin to

VSS. Otherwise the supply voltage must stay above 1.71 V with the embedded power

voltage detector enabled.

Dedicated supply inputs for USB (OTG_FS and OTG_HS) are available on all packages to

allow a greater power supply choice.

A comprehensive set of power-saving modes allows the design of low-power applications.

STM32H747xI/G devices are offered in 5 packages ranging from 156 pins to 240 pins/balls.

The set of included peripherals changes with the device chosen.

These features make STM32H747xI/G microcontrollers suitable for a wide range of

applications:

• Motor drive and application control

• Medical equipment

• Industrial applications: PLC, inverters, circuit breakers

• Printers, and scanners

• Alarm systems, video intercom, and HVAC

• Home audio appliances

• Mobile applications, Internet of Things

• Wearable devices: smart watches.

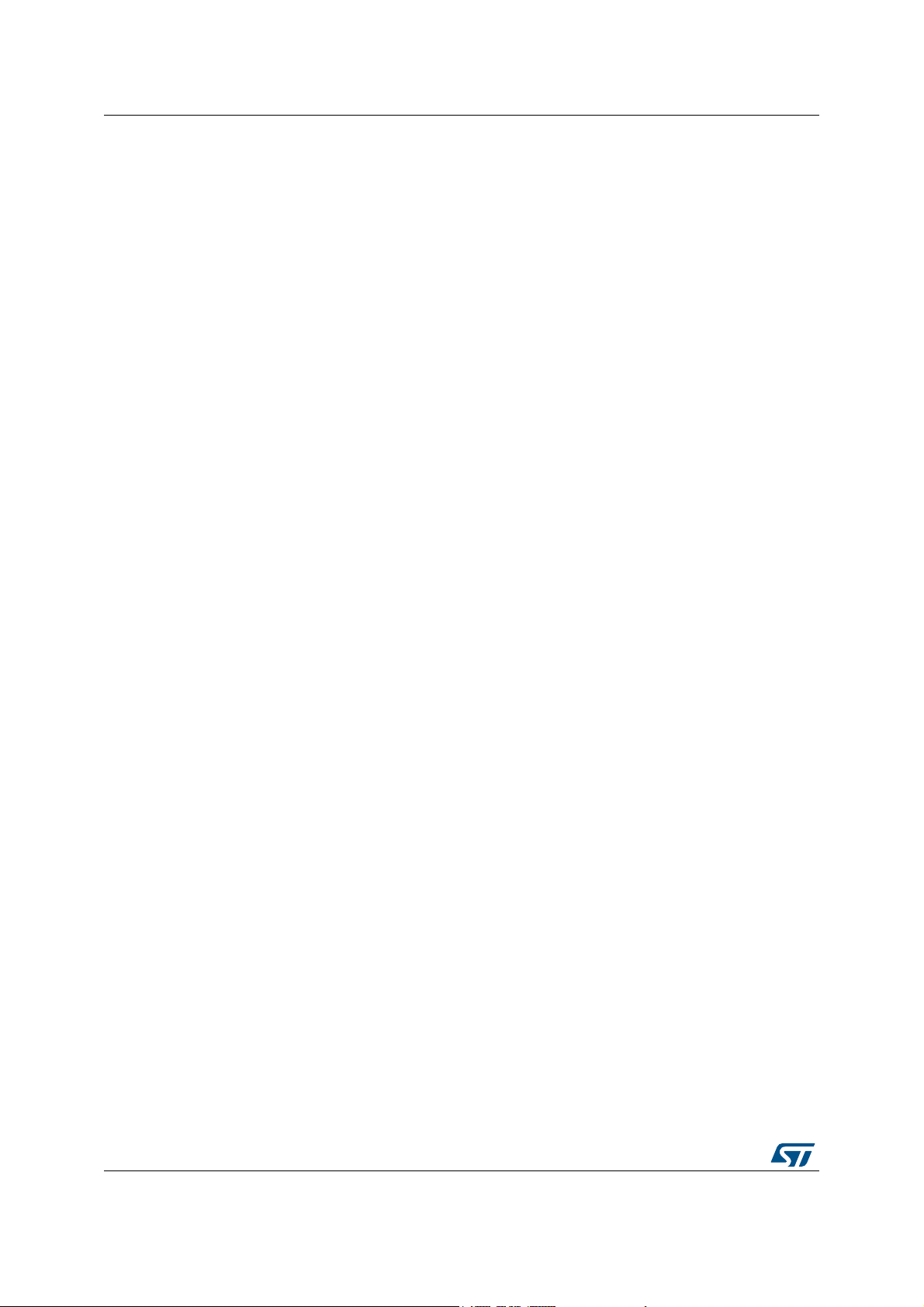

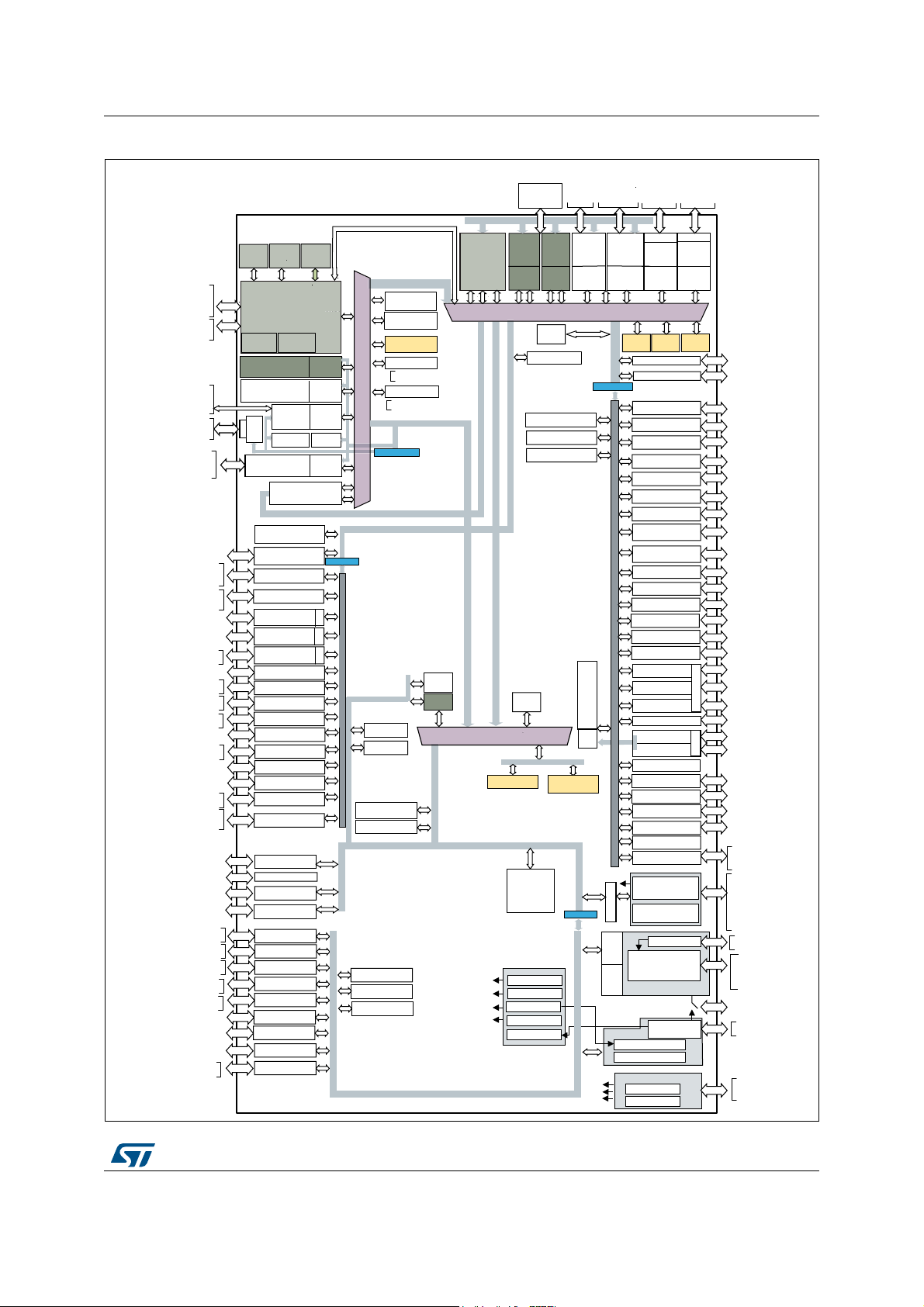

Figure 1 shows the device block diagram.

DS12930 Rev 1 5/242

46

Description STM32H747xI/G

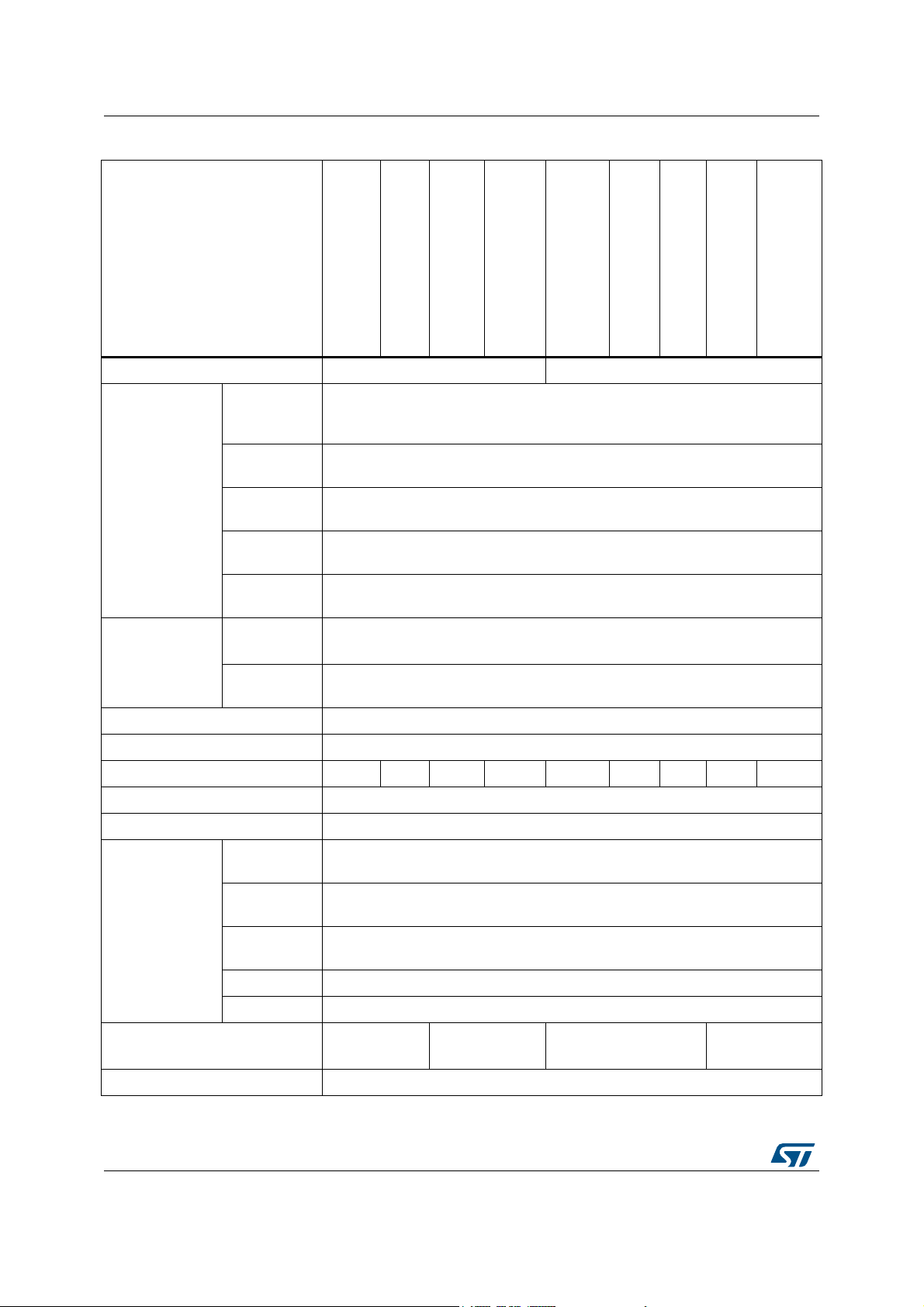

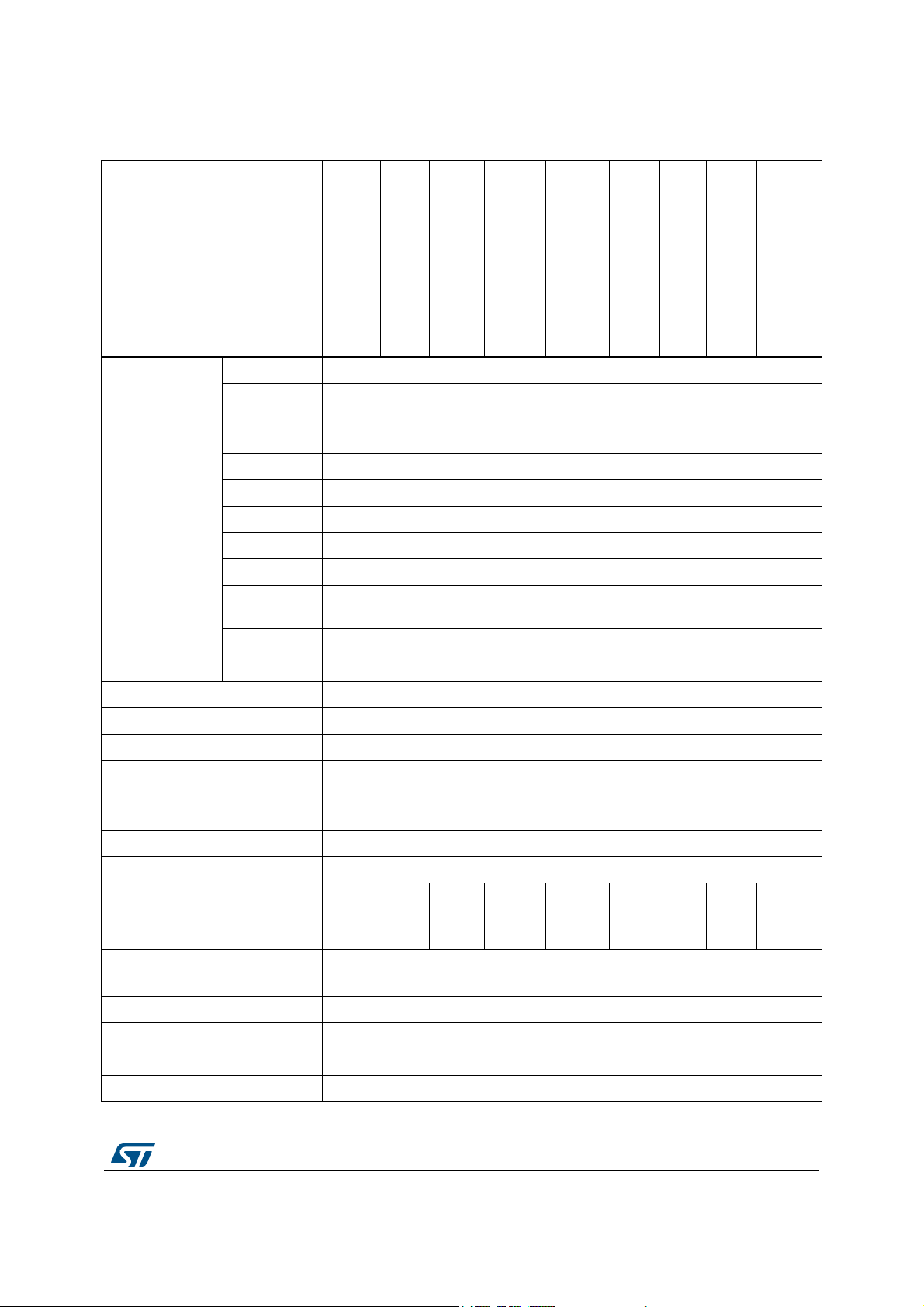

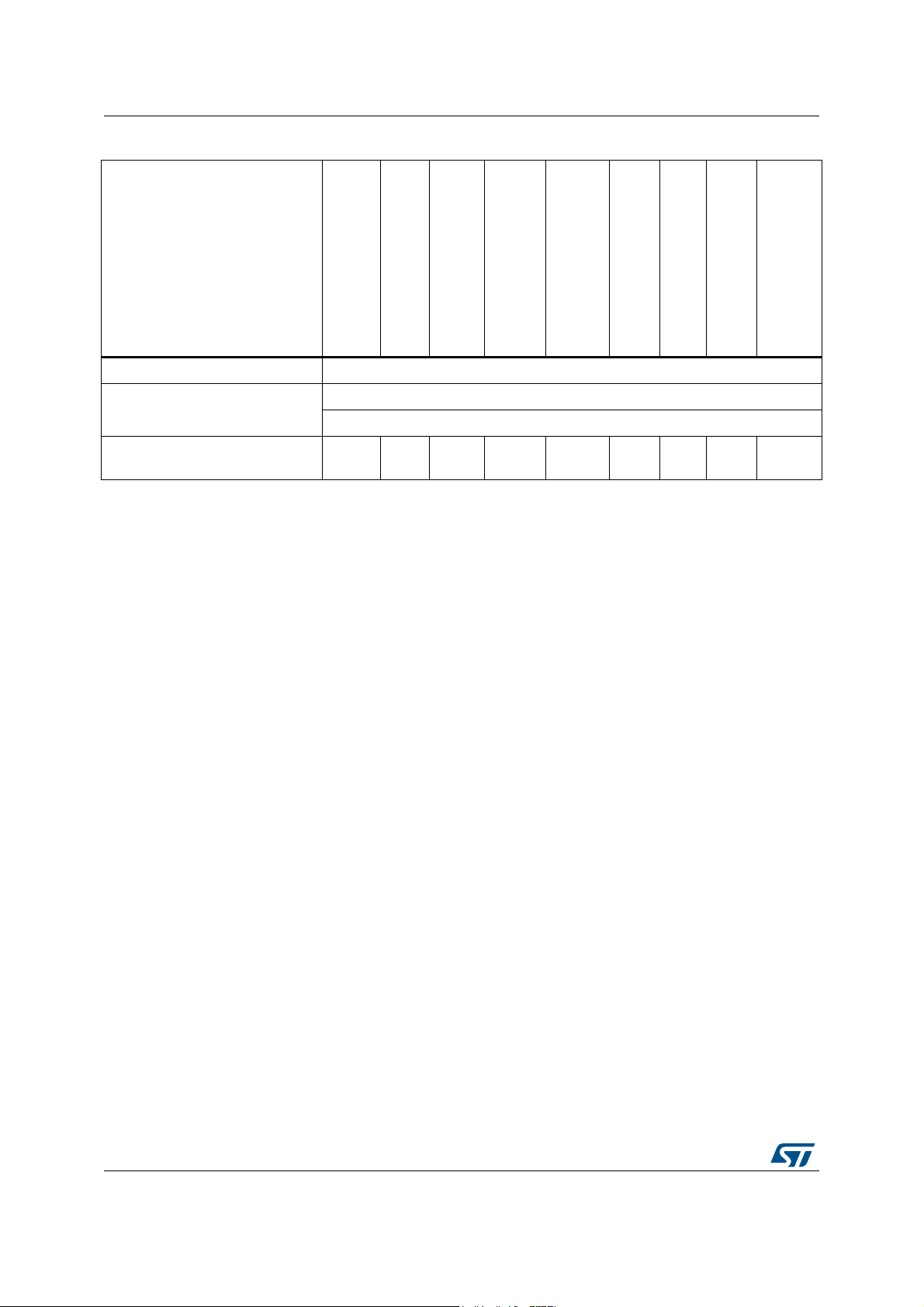

Table 1. STM32H747xI/G features and peripheral counts

Peripherals

STM32H747AG

Flash memory in Kbytes 2 x 512 Kbytes 2 x 1 Mbyte

SRAM

mapped onto

AXI bus

SRAM1

(D2 domain)

SRAM in Kbytes

TCM RAM in

Kbytes

Backup SRAM (Kbytes) 4

FMC Yes

SRAM2

(D2 domain)

SRAM3

(D2 domain)

SRAM4

(D3 domain)

ITCM RAM

(instruction)

DTCM RAM

(data)

STM32H747IG

STM32H747BG

STM32H747XG

STM32H747ZI

512

128

128

32

64

64

128

STM32H747AI

STM32H747II

STM32H747BI

STM32H747XI

General-purpose input/outputs 112 119 148 168 99 112 119 148 168

Quad-SPI Yes

Ethernet Yes

High-

resolution

General-

purpose

Timers

Wakeup pins

Tamper pins

Random number generator Yes

6/242 DS12930 Rev 1

Advanced-

control (PWM)

Basic 2

Low-power 5

4

2

6

3

10

1

2

4

2

6

3

STM32H747xI/G Description

Table 1. STM32H747xI/G features and peripheral counts (continued)

Peripherals

STM32H747AG

STM32H747IG

STM32H747BG

STM32H747XG

SPI / I2S6/3

I2C4

USART/UART

/LPUART

SAI 4

SPDIFRX 4 inputs

Communication

interfaces

SWPMI Yes

MDIO Yes

SDMMC 2

FDCAN/TT-

FDCAN

USB OTG_FS Yes

USB OTG_HS Yes

Ethernet and camera interface Yes

LCD-TFT Yes

MIPI-DSI Host Yes

4/4

/1

1/1

(1)

STM32H747ZI

STM32H747AI

STM32H747II

STM32H747BI

STM32H747XI

JPEG Codec Yes

Chrom-ART Accelerator™

(DMA2D)

Yes

GPIOs Up to 168

16-bit ADCs

Number of Direct channels

Number of Fast channels

Number of Slow channels

12-bit DAC

Number of channels

17

2

9

2

9

21

4

9

23

3

2

7

14

Yes

2

Comparators 2

Operational amplifiers 2

DFSDM Yes

Maximum CPU frequency 480 MHz

DS12930 Rev 1 7/242

17

2

9

2

9

21

4

9

23

46

Description STM32H747xI/G

Table 1. STM32H747xI/G features and peripheral counts (continued)

Peripherals

STM32H747AG

STM32H747IG

STM32H747BG

STM32H747XG

STM32H747ZI

Operating voltage 1.62 to 3.6 V

Ambient temperatures: –40 up to +85 °C

STM32H747AI

(2)

STM32H747II

(3)

STM32H747BI

Operating temperatures

Junction temperature: –40 to + 125 °C

Package

1. The SPI1, SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio

mode.

2. V

connecting PDR_ON pin to VSS. Otherwise the supply voltage must stay above 1.71 V with the embedded power voltage

detector enabled.

3. The product junction temperature must be kept within the –40 to +125 °C range.

can drop down to 1.62 V by using an external power supervisor (see Section 3.5.2: Power supply supervisor) and

DD/VDDA

UFBGA

169

LQFP

176

LQFP

208

TFBGA

240+25

WLCSP

156

UFBG

A169

LQFP

176

LQFP

208

TFBGA

240+25

STM32H747XI

8/242 DS12930 Rev 1

STM32H747xI/G Description

MSv43739V12

FDCAN1

FDCAN2

I2C1/SMBUS

I2C2/SMBUS

I2C3/SMBUS

AXI/AHB12 (200MHz)

4 compl. chan. (TIM1_CH1[1:4]N),

4 chan. (TIM1_CH1[1:4]ETR, BKIN as AF

APB1 30MHz

TX, RX

SCL, SDA, SMBAL as AF

APB1 100 MHz (max)

MDMA

PK[7:0]

4 compl. chan.(TIM8_CH1[1:4]N),

4 chan. (TIM8_CH1[1:4], ETR, BKIN as

AF

RX, TX, SCK,

CTS, RTS as AF

SCL, SDA, SMBAL as AF

SCL, SDA, SMBAL as AF

MOSI, MISO, SCK, NSS/SDO,

SDI, CK, WS, MCK, as AF

TX, RX

RX, TX as AF

RX, TX as AF

RX, TX, SCK

CTS, RTS as AF

RX, TX, SCK, CTS,

RTS as AF

1 channel as AF

smcard

irDA

1 channel as AF

2 channels as AF

4 channels

4 channels, ETR as AF

4 channels, ETR as AF

4 channels, ETR as AF

RX, TX as AF

FIFO

LCD-TFT

FIFO

CHROM-ART

(DMA2D)

SD, SCK, FS, MCLK as AF

FIFO

LCD_R[7:0], LCD_G[7:0],

LCD_B[7:0], LCD_HSYNC,

LCD_VSYNC, LCD_DE,

LCD_CLK

CLK, CS,D[7:0]

64-bit AXI BUS-MATRIX

CEC as AF

IN[1:4] as AF

MDC, MDIO

AXIM

AHBP

AHBS

TRACECK

TRACED[3:0]

JTRST, JTDI,

JTCK/SWCLK

JTDO/SWD, JTDO

JTAG/SW

ETM

I-Cache

16KB

D-Cache

16KB

ITCM

4KB

D-

TCM

64KB

16 Streams

FIFO

SDMMC1

SDMMC_D[7:0],SDMMC_D[7:3,1]Dir

SDMMC_D0dir, SDMMC_D2dir

CMD, CMDdir, CK, Ckin,

CKio as AF

FIFO

DMA1

FIFOs

8 Stream

DMA2

FIFOs

ETHER

MAC

SDMMC2

FIFO

OTG_HS

FIFO

OTG_FS

FIFO

SRAM1

128 KB

8 Stream

FMC_signals

DMA DMA/ DMA/

PHY PHY

MII / RMII

MDIO

as AF

DP, DM, STP,

NXT,ULPI:CK

, D[7:0], DIR,

ID, VBUS

AHB1 (200MHz)

ADC1

DAC1_OUT, DAC2_OUT as AF

16b

AXI/AHB34 (200MHz)

JPEGWWDG1

AHB2 (200MHz)

AHB2 (200MHz)

PA..J[15:0]

HSYNC, VSYNC, PUIXCLK, D[13:0]

SAI3

MOSI, MISO,

SCK, NSS as AF

MOSI, MISO, SCK, NSS as AF

smcard

irDA

32-bit AHB BUS-MATRIX

32-bit AHB BUS-MATRIX

AHB4 (200MHz)

BDMA

DMA

Mux2

Up to 20 analog inputs

common to ADC1 & 2

HSEM

AHB4 (200MHz)

AHB3

AHB4

AHB4

AHB4

AHB4

AHB4

VDDA, VSSA

NRESET

WKUP[5:0]

@VDD

RCC

Reset &

control

OSC32_IN

OSC32_OUT

VBAT = 1.2 to 3.6 V

AWU

VDD12

LS

LS

OSC_IN

OSC_OUT

RTC_TS

RTC_TAMP[1:3]

RTC_OUT

RTC_REFIN

VDD = 1.62 to 3.6V

VDDUSB33 = 3.0 to 3.6V

VDDDSI = 1.8 to 3.6V

VSS

VCAP

VDDMMC33 = 1.8 to 3.6 V

VDDSMPS, VSSSMPS

VLXSMPS, VFBSMPS

@VDD

@VDD33

@VSW

PWRCTRL

AHB4 (200MHz)

SUPPLY SUPERVISION

Int

POR

reset

@VDD

LPTIM1_IN1, LPTIM1_IN2,

LPTIM1_OUT as AF

OPAMPx_VINM

OPAMPx_VINP

OPAMPx_VOUT as AF

HRTIM1_CH[A..E]x

HRTIM1_FLT[5:1],

HRTIM1_FLT[5:1]_in, SYSFLT

DFSDM1_CKOUT,

DFSDM1_DATAIN[0:7],

DFSDM1_CKIN[0:7]

2 compl. chan.(TIM15_CH1[1:2]N),

2 chan. (TIM_CH15[1:2], BKIN as AF

1 compl. chan.(TIM16_CH1N),

1 chan. (TIM16_CH1, BKIN as AF

1 compl. chan.(TIM17_CH1N),

1 chan. (TIM17_CH1, BKIN as AF

SDMMC_

D[7:0],

CMD, CK as AF

Up to 17 analog inputs

common to ADC1 and 2

SD, SCK, FS, MCLK,

PDM_DI/CK[4:1] as AF

SCL, SDA, SMBAL as AF

COMPx_INP, COMPx_INM,

COMPx_OUT as AF

LPTIM5_OUT as AF

D-

TCM

64KB

AHB/APB

Quad-SPI

Up to 1 MB

FLASH

Up to 1 MB

FLASH

512 KB AXI

SRAM

FMC

Delay block

DCMI

AHB/APB

HRTIM1

DFSDM1

SD, SCK, FS, MCLK as AF

FIFO

SAI2

SD, SCK, FS, MCLK, D[3:1],

CK[2:1] as AF

FIFO

SAI1

SPI5

TIM17

TIM16

TIM15

SPI4

MOSI, MISO, SCK, NSS/

SDO, SDI, CK, WS, MCK, as AF

SPI/I2S1

USART6

RX, TX, SCK,

CTS, RTS as AF

irDA

USART1

TIM1/PWM

16b

TIM8/PWM

16b

APB2 100 MHz (max)

ADC3

GPIO PORTA.. J

GPIO PORTK

SAI4

COMP1&2

LPTIM5

LPTIM4_OUT as AF

LPTIM4

LPTIM3_OUT as AF

LPTIM3

I2C4

MISO, MOSI, SCK, NSS as AF

SPI6

RX, TX, CK, CTS, RTS as AF

LPUART1

LPTIM2

VREF

SYSCFG

EXTI WKUP

CRC

DAP

DMA

Mux1

To APB1-2

peripherals

SRAM2

128 KB

SRAM3

32 KB

ADC2

AHB/APB

TIM6

16b

TIM7

16b

SWPMI

TIM2

32b

TIM3

16b

TIM4

16b

TIM5

32b

TIM12

16b

TIM13

16b

TIM14

16b

USART2

smcard

irDA

USART3

UART4

UART5

UART7

RX, TX as AF

UART8

SPI2/I2S2

MOSI, MISO, SCK, NSS/SDO,

SDI, CK, WS, MCK, as AF

SPI3/I2S3

Digital filter

MDIOS

FIFO

10 KB SRAM

RAM

I/F

CRS

SPDIFRX1

HDMI-CEC

DAC1&2

LPTIM1

OPAMP1&2

AHB/APB

XTAL 32 kHz

RTC

Backup registers

XTAL OSC

4- 48 MHz

32 KHz LSI RC

PLL1+PLL2+PLL3

POR/PDR/BOR

PVD

smcard

LSI

HSI

CSI

RC48

LPTIM2_OUT as AF

AHB1 (200MHz)

DP, DM, ID,

VBUS

64 KB SRAM

4 KB BKP

RAM

AHB4

ARM

Cortex

M4

Arm

Cortex

M7

I-

Bus

D-

Bus

S-

Bus

D

S

I

DSI_D0_P, DSI_D0_N

DSI_D1_P, DSI_D1_N

DSI_CK_P, DSI_CK_N

PHY

ART

(instruction cache)

AHB ART (200MHz)

AHB ART(200MHz)

RNG

WWDG2

IWDG1

IWDG2

Voltage regulator

3.3 to 1.2V

SMPS step-down

converter

4 MHz CSI

48 MHz HSI48 RC

64 MHz HSI RC

APB4 100 MHz (max)

APB4 100 MHz (max)

IWDG1

IWDG2

VDDREF_ADC

Tem. sensor

Figure 1. STM32H747xI/G block diagram

XI

DS12930 Rev 1 9/242

46

Description STM32H747xI/G

MSv48802V2

VDD

SMPS

STM32H7x7 STM32H7x3

VLX

SMPS

VSS

SMPS

VFB

SMPS

NC

PI9

PF2

NC

NC

NC

12345678910 111213 14151617

A

VSS PI6 PI5 PI4 PB5 VDDLDO

VCAP

PK5 PG10 PG9 PD5 PD4 PC10 PA15 PI1 PI0 VSS

B

VBAT VSS PI7 PE1 PB6 VSS PB4 PK4 PG11 PJ15 PD6 PD3 PC11 PA14 PI2 PH15 PH14

C

PC15-

OSC32_

OUT

PC14-

OSC32_

IN

PE2 PE0 PB7 PB3 PK6 PK3 PG12 VSS PD7 PC12 VSS PI3 PA13 VSS VDDLDO

D

PE5 PE4 PE3 PB9 PB8 PG15 PK7 PG14 PG13 PJ14 PJ12 PD2 PD0 PA10 PA9 PH13

VCAP

E

PI9 PC13 PI8 PE6 VDD

PDR

_ON

BOOT0 VDD PJ13 VDD PD1 PC8 PC9 PA8 PA12 PA11

F

PI10 PI11 VDD PC7 PC6 PG8 PG7

VDD33

USB

G

PF2 PF1 PF0 VDD VSS VSS VSS VSS VSS VDD PG5 PG6 VSS

VDD5

USB

H

PI12 PI13 PI14 PF3 VDD VSS VSS VSS VSS VSS VDD PG4 PG3 PG2 PK2

J

PH1-

OSC_

OUT

PH0-

OSC_

IN

VSS PF5 PF4 VSS VSS VSS VSS VSS VDD PK0 PK1

VSS

DSI

VSSDSI

K

NRST PF6 PF7 PF8 VDD VSS VSS VSS VSS VSS VDD PJ11

L

VDDA PC0 PF10 PF9 VDD VSS VSS VSS VSS VSS VDD PJ10

M

VREF+ PC1 PC2 PC3 VDD VDD PJ9

N

VREF- PH2 PA2 PA1 PA0 PJ0 VDD VDD PE10 VDD VDD VDD PJ8 PJ7 PJ6 VSS

P

VSSA PH3 PH4 PH5 PI15 PJ1 PF13 PF14 PE9 PE11 PB10 PB11 PH10 PH11 PD15 PD14

R

PC2_C PC3_C PA6 VSS PA7 PB2 PF12 VSS PF15 PE12 PE15 PJ5 PH9 PH12 PD11 PD12 PD13

T

PA0_C PA1_C PA5 PC4 PB1 PJ2 PF11 PG0 PE8 PE13 PH6 VSS PH8 PB12 PB15 PD10 PD9

U

VSS PA3 PA4 PC5 PB0 PJ3 PJ4 PG1 PE7 PE14

VCAP

VDDLDO

PH7 PB13 PB14 PD8 VSS

VSSDSI

PI9

PF2

VSSDSI

DSI_CKP

DSI_CKN

DSI_D0N

DSI_D1P

DSI_D1N

VSS

VDDCAP

DSI

PJ6

PD14

VDDDSI

PD15

PI9

PF2 VSSDSI DSI_D0P

VSS

PI9

PF2

VSS

NC

NC

NC

NC

NC

VSS

NC

PJ6

PD14

VDD

PD15

VSS NC

Compatibility throughout the family

STM32H747xI/G devices are not pin-to-pin compatible with STM32H7x3 devices (single

core line):

• The TFBGA240+25 ballout is compatible with STM32H7x3 devices, except for a few

I/O balls as shown in Figure 2.

• LQFP208 and LQFP176 pinouts, as well as UFBGA176+25 ballout are not compatible

with STM32H7x3 devices.

Figure 2. TFBGA240+25 ball assignment differences

1. The balls highlighted in gray correspond to different signals on STM32H747xI/G and STM32H7x3 devices.

10/242 DS12930 Rev 1

STM32H747xI/G Functional overview

3 Functional overview

3.1 Dual Arm

The dual-core MIPI-DSI STM32H747xI/G devices embed two Arm® cores, a Cortex®-M7

and a Cortex

while the Cortex

The two cores belong to separate power domains. This allows designing gradual highpower efficiency solutions in combination with the low-power modes already available on all

STM32 microcontrollers.

®

Cortex

®

-M4. The Cortex®-M4 offers optimal performance for real-time applications

®

®

cores

-M7 core can execute high-performance tasks in parallel.

3.1.1 Arm® Cortex®-M7 with FPU

The Arm® Cortex®-M7 with double-precision FPU processor is the latest generation of Arm

processors for embedded systems. It was developed to provide a low-cost platform that

meets the needs of MCU implementation, with a reduced pin count and optimized power

consumption, while delivering outstanding computational performance and low interrupt

latency.

The Cortex®-M7 processor is a highly efficient high-performance featuring:

• Six-stage dual-issue pipeline

• Dynamic branch prediction

• Harvard architecture with L1 caches (16 Kbytes of I-cache and 16 Kbytes of D-cache)

• 64-bit AXI interface

• 64-bit ITCM interface

• 2x32-bit DTCM interfaces

The following memory interfaces are supported:

• Separate Instruction and Data buses (Harvard Architecture) to optimize CPU latency

• Tightly Coupled Memory (TCM) interface designed for fast and deterministic SRAM

accesses

• AXI Bus interface to optimize Burst transfers

• Dedicated low-latency AHB-Lite peripheral bus (AHBP) to connect to peripherals.

The processor supports a set of DSP instructions which allow efficient signal processing and

complex algorithm execution.

It also supports single and double precision FPU (floating point unit) speeds up software

development by using metalanguage development tools, while avoiding saturation.

Figure 1 shows the general block diagram of the STM32H747xI/G family.

Note: Cortex®-M7 with FPU core is binary compatible with the Cortex®-M4 core.

DS12930 Rev 1 11/242

46

Functional overview STM32H747xI/G

3.1.2 Arm® Cortex®-M4 with FPU

The Arm® Cortex®-M4 processor is a high-performance embedded processor which

supports DSP instructions. It was developed to provide an optimized power consumption

MCU, while delivering outstanding computational performance and low interrupt latency.

The Arm® Cortex®-M4 processor is a highly efficient MCU featuring:

• 3-stage pipeline with branch prediction

• Harvard architecture

• 32-bit System (S-BUS) interface

• 32-bit I-BUS interface

• 32-bit D-BUS interface

The Arm® Cortex®-M4 processor also features a dedicated hardware adaptive real-time

accelerator (ART Accelerator

four 256-bit lines, a 256-bit cache buffer connected to the 64-bit AXI interface and a 32-bit

interface for non-cacheable accesses.

™

). This is an instruction cache memory composed of sixty-

3.2 Memory protection unit (MPU)

The devices feature two memory protection units. Each MPU manages the CPU access

rights and the attributes of the system resources. It has to be programmed and enabled

before use. Its main purposes are to prevent an untrusted user program to accidentally

corrupt data used by the OS and/or by a privileged task, but also to protect data processes

or read-protect memory regions.

The MPU defines access rules for privileged accesses and user program accesses. It

allows defining up to 16 protected regions that can in turn be divided into up to 8

independent subregions, where region address, size, and attributes can be configured. The

protection area ranges from 32 bytes to 4

When an unauthorized access is performed, a memory management exception is

generated.

Gbytes of addressable memory.

12/242 DS12930 Rev 1

STM32H747xI/G Functional overview

3.3 Memories

3.3.1 Embedded Flash memory

The STM32H747xI/G devices embed up to 2 Mbytes of Flash memory that can be used for

storing programs and data.

The Flash memory is organized as 266-bit Flash words memory that can be used for storing

both code and data constants. Each word consists of:

• One Flash word (8 words, 32 bytes or 256 bits)

• 10 ECC bits.

The Flash memory is divided into two independent banks. Each bank is organized as

follows:

• A user Flash memory block of 512 Kbytes (STM32H7xxxG) or 1-Mbyte (STM32H7xxxI)

containing eight user sectors of 128 Kbytes (4 K Flash memory words)

• 128 Kbytes of System Flash memory from which the device can boot

• 2 Kbytes (64 Flash words) of user option bytes for user configuration

3.3.2 Embedded SRAM

All devices feature around 1 Mbyte of RAM with hardware ECC. The RAM is divided as

follows:

• 512 Kbytes of AXI-SRAM mapped onto AXI bus on D1 domain.

• SRAM1 mapped on D2 domain: 128 Kbytes

• SRAM2 mapped on D2 domain: 128 Kbytes

• SRAM3 mapped on D2 domain: 32 Kbytes

• SRAM4 mapped on D3 domain: 64 Kbytes

• 4 Kbytes of backup SRAM

The content of this area is protected against possible unwanted write accesses,

and is retained in Standby or V

• RAM mapped to TCM interface (ITCM and DTCM):

Both ITCM and DTCM RAMs are 0 wait state memories. They can be accessed either

from the Arm

AHB slave of the Cortex

®

Cortex®-M7 CPU or the MDMA (even in Sleep mode) through a specific

®

-M7(AHBS):

– 64 Kbytes of ITCM-RAM (instruction RAM)

This RAM is connected to ITCM 64-bit interface designed for execution of critical

real-times routines by the Cortex

– 128 Kbytes of DTCM-RAM (2x 64-Kbyte DTCM-RAMs on 2x32-bit DTCM ports)

The DTCM-RAM could be used for critical real-time data, such as interrupt service

routines or stack/heap memory. Both DTCM-RAMs can be used in parallel (for

load/store operations) thanks to the Cortex

The MDMA can be used to load code or data in ITCM or DTCM RAMs.

BAT

mode.

®

-M7.

®

-M7 dual issue capability.

DS12930 Rev 1 13/242

46

Functional overview STM32H747xI/G

Error code correction (ECC)

Over the product lifetime, and/or due to external events such as radiations, invalid bits in

memories may occur. They can be detected and corrected by ECC. This is an expected

behavior that has to be managed at final-application software level in order to ensure data

integrity through ECC algorithms implementation.

SRAM data are protected by ECC:

• 7 ECC bits are added per 32-bit word.

• 8 ECC bits are added per 64-bit word for AXI-SRAM and ITCM-RAM.

The ECC mechanism is based on the SECDED algorithm. It supports single-error correction

and double-error detection.

3.3.3 ART™ accelerator

The ART™ (adaptive real-time) accelerator block speeds up instruction fetch accesses of

the Cortex

®

-M4 core from D1-domain internal memories (Flash memory bank 1, Flash

memory bank 2, AXI SRAM) and from D1-domain external memories attached via QuadSPI controller and Flexible memory controller (FMC).

The ART™ accelerator is a 256-bit cache line using 64-bit WRAP4 accesses from the 64-bit

AXI D1 domain. The acceleration is achieved by loading selected code into an embedded

cache and making it instantly available to Cortex

®

-M4 core, thus avoiding latency due to

memory wait states.

Figure 3. shows the block schematic and the environment of the ART accelerator.

14/242 DS12930 Rev 1

STM32H747xI/G Functional overview

MSv39757V2

64-bit AXI bus matrix

Flash bank 1

Flash bank 2

AXI SRAM

QSPI

FMC

AHB from D2 domain

32-bit bus

64-bit bus

Bus multiplexer

Legend

Master interface

Slave interface

AXI AHB

ART accelerator

AHB switch

Non-cacheable

access path

Cacheable

access path

AXI access

AHB access

D1 domain

Control

control

Cache memory

64 x 256-bit

Cache memory

64 x 256-bit

Cache buffer

1 x 256-bit

Cache

non-

cacheable

access

Detect of

write to cacheable page

instruction

fetch

cache

hit

cache

miss

cache

refill

Cache

manager

Figure 3. ART™ accelerator schematic and environment

3.4 Boot modes

By default, the boot codes are executed simultaneously by both cores. However, by

programming the appropriate Flash user option byte, it is possible to boot from one core

while clock-gating the other core.

At startup, the boot memory space is selected by the BOOT pin and BOOT_ADDx option

bytes, allowing to program any boot memory address from 0x0000 0000 to 0x3FFF FFFF

which includes:

• All Flash address space