STMicroelectronics STM32F078CB, STM32F078RB, STM32F078VB Datasheet

STM32F078CB/RB/VB

Errata sheet

STM32F078CB/RB/VB device errata

Applicability

This document applies to STM32F078CB/RB/VB devices and the device variants as stated in this page.

It gives a summary and a description of the device errata, with respect to the device datasheet and reference manual RM0091.

Deviation of the real device behavior from the intended device behavior is considered to be a device limitation. Deviation of the

description in the reference manual or the datasheet from the intended device behavior is considered to be a documentation

erratum. The term “errata” applies both to limitations and documentation errata.

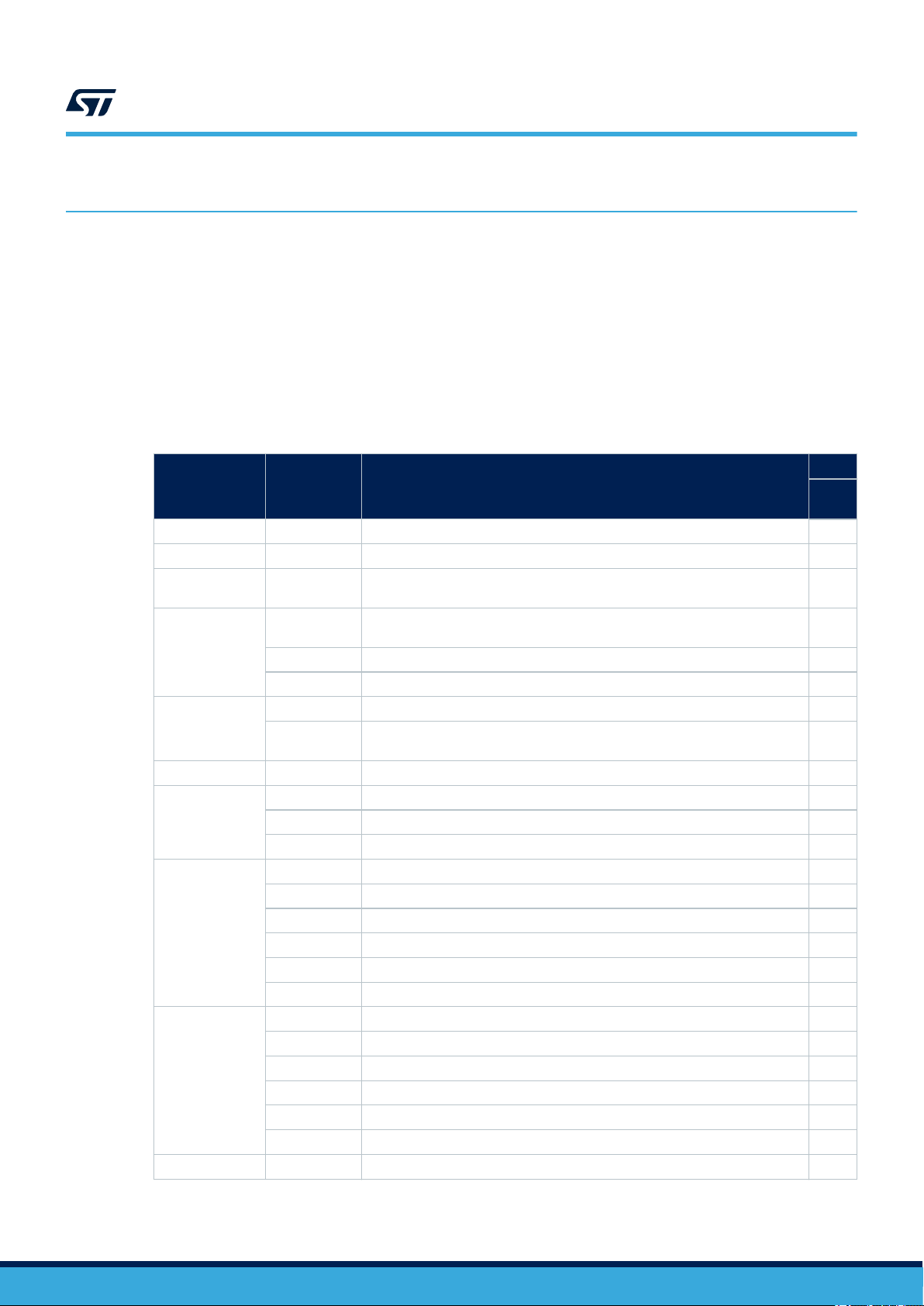

Table 1. Device variants

Reference

STM32F078CB/RB/VB

1. Refer to the device datasheet for how to identify this code on different types of package.

2. REV_ID[15:0] bitfield of DBGMCU_IDCODE register.

Device marking

Y or 1 0x2001

Silicon revision codes

(1)

REV_ID

(2)

ES0262 - Rev 4 - October 2020

For further information contact your local STMicroelectronics sales office.

www.st.com

1 Summary of device errata

The following table gives a quick reference to the STM32F078CB/RB/VB device limitations and their status:

A = workaround available

N = no workaround available

P = partial workaround available

Applicability of a workaround may depend on specific conditions of target application. Adoption of a workaround

may cause restrictions to target application. Workaround for a limitation is deemed partial if it only reduces the

rate of occurrence and/or consequences of the limitation, or if it is fully effective for only a subset of instances on

the device or in only a subset of operating modes, of the function concerned.

Table 2. Summary of device limitations

Function Section Limitation

System 2.2.1 RDP Level 1 issue

GPIO 2.3.1 GPIOx locking mechanism not working properly for GPIOx_OTYPER register P

DMA 2.4.1

2.5.1

ADC

DAC

COMP 2.7.1 Long VREFINT scaler startup time after power on N

TIM

IWDG

RTC and TAMP

I2C

2.5.2 Overrun flag is not set if EOC reset coincides with new conversion end P

2.5.3 ADEN bit cannot be set immediately after the ADC calibration A

2.6.1 DMA request not automatically cleared by clearing DMAEN A

2.6.2

2.9.1 PWM re-enabled in automatic output enable mode despite of system break P

2.9.3 Consecutive compare event missed in specific conditions N

2.9.4 Output compare clear not working with external counter reset P

2.10.1 RVU flag not reset in Stop A

2.10.2 PVU flag not reset in Stop A

2.10.3 WVU flag not reset in Stop A

2.10.4 RVU flag not cleared at low APB clock frequency A

2.10.5 PVU flag not cleared at low APB clock frequency A

2.10.6 WVU flag not cleared at low APB clock frequency A

2.11.1 Spurious tamper detection when disabling the tamper channel P

2.11.2 RTC calendar registers are not locked properly A

2.11.3 RTC interrupt can be masked by another RTC interrupt A

2.11.4 Calendar initialization may fail in case of consecutive INIT mode entry A

2.11.5 Alarm flag may be repeatedly set when the core is stopped in debug N

2.11.6 A tamper event preceding the tamper detect enable not detected A

2.12.1 10-bit slave mode: wrong direction bit value upon Read header receipt A

DMA disable failure and error flag omission upon simultaneous transfer error

and global flag clear

ADCAL bit is not cleared when successive calibrations are performed and

system clock frequency is considerably higher than the ADC clock frequency

DMA underrun flag not set when an internal trigger is detected on the clock

cycle of the DMA request acknowledge

STM32F078CB/RB/VB

Summary of device errata

Status

Rev.

Y, 1

P

A

A

N

ES0262 - Rev 4

page 2/31

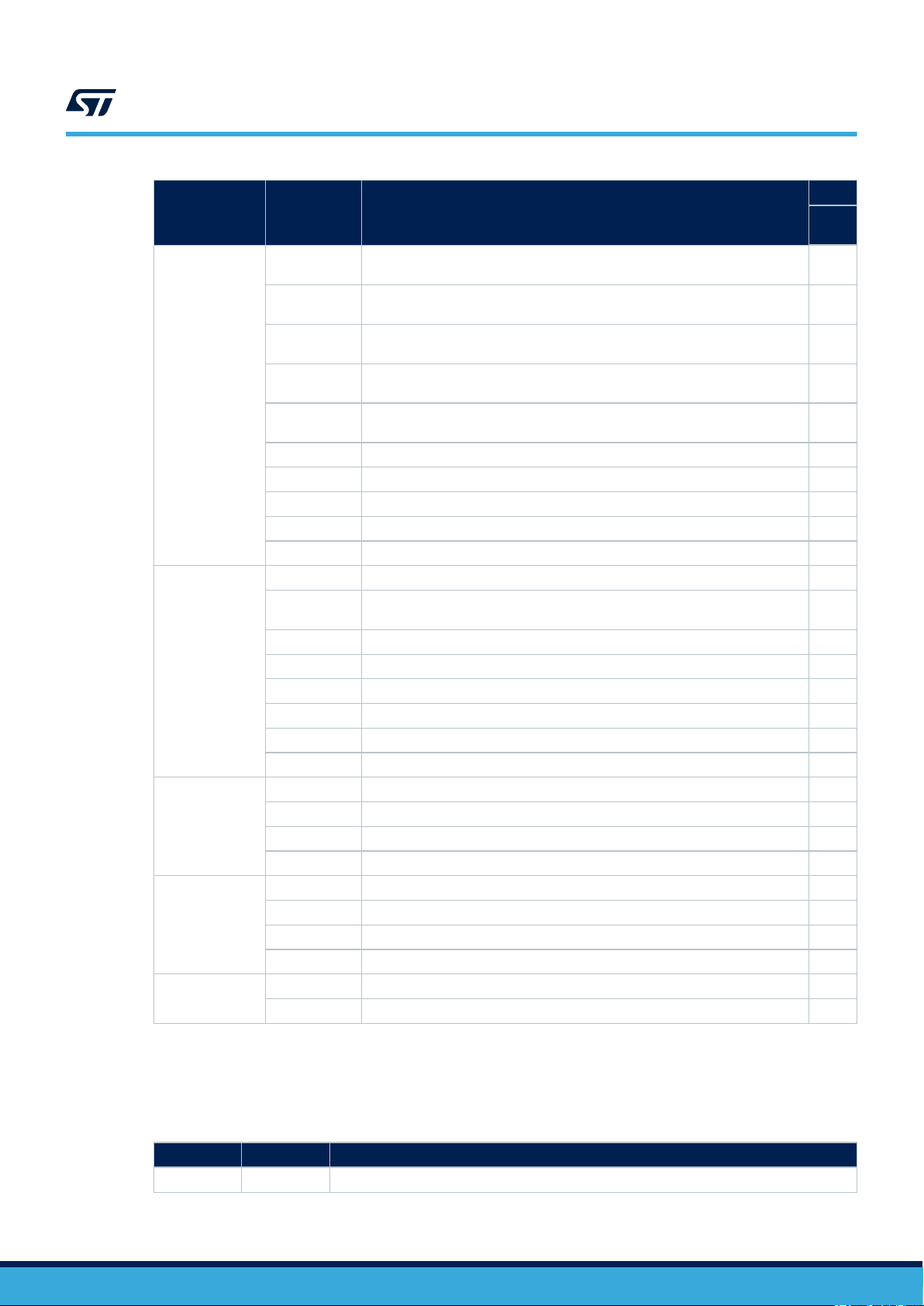

Function Section Limitation

10-bit combined with 7-bit slave mode: ADDCODE may indicate wrong slave

address detection

Wakeup frames may not wake up the MCU when Stop mode entry follows I2C

enabling

Wakeup frame may not wake up the MCU from Stop mode if tHD;STA is close

to I2C kernel clock startup time

10-bit master mode: new transfer cannot be launched if first part of the address

is not acknowledged by the slave

Wrong data sampling when data setup time (tSU;DAT) is shorter than one I2C

kernel clock period

Last byte written in TDR might not be transmitted if TE is cleared just after

writing in TDR

I2C

USART

SPI

USB

CEC

2.12.2

2.12.3

2.12.4

2.12.5

2.12.7

2.12.8 Spurious bus error detection in master mode A

2.12.9 Last-received byte loss in reload mode P

2.12.10 Spurious master transfer upon own slave address match P

2.12.11 OVR flag not set in underrun condition N

2.12.12 Transmission stalled after first byte transfer A

2.13.1 USART4 transmission does not work on PC11 N

2.13.2

2.13.3 Non-compliant sampling for NACK signal from smartcard N

2.13.4 Break request preventing TC flag from being set A

2.13.5 RTS is active while RE = 0 or UE = 0 A

2.13.6 Receiver timeout counter wrong start in two-stop-bit configuration A

2.13.7 Anticipated end-of-transmission signaling in SPI slave mode A

2.13.8 Data corruption due to noisy receive line N

2.14.1 BSY bit may stay high when SPI is disabled A

2.14.2 BSY bit may stay high at the end of data transfer in slave mode A

2.14.3 SPI CRC corruption upon DMA transaction completion by another peripheral P

2.14.4 In I2S slave mode, enabling I2S while WS is active causes desynchronization A

2.15.2 ESOF interrupt timing desynchronized after resume signaling A

2.15.3 Incorrect CRC16 in the memory buffer N

2.15.4 The USB BCD functionality limited below -20°C N

2.15.5 DCD function not compliant P

2.16.1 Transmission blocked when transmitted start bit is corrupted P

2.16.2 Missed CEC messages in normal receiving mode A

STM32F078CB/RB/VB

Summary of device errata

Status

Rev.

Y, 1

N

A

P

A

P

A

ES0262 - Rev 4

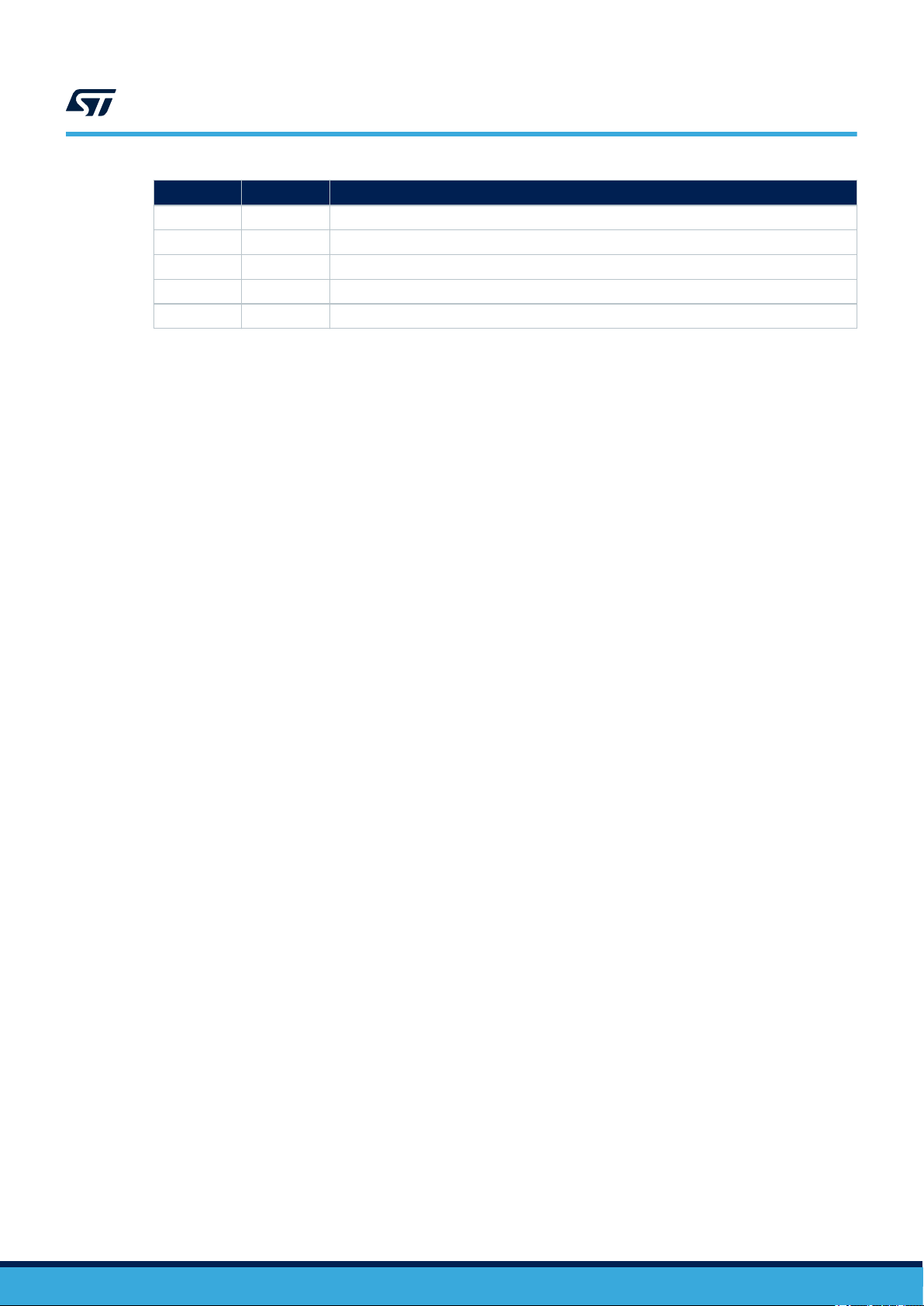

The following table gives a quick reference to the documentation errata.

Table 3. Summary of device documentation errata

Function

DMA 2.4.2 Byte and half-word accesses not supported

Section Documentation erratum

page 3/31

STM32F078CB/RB/VB

Summary of device errata

Function Section Documentation erratum

TSC 2.8.1 Inhibited acquisition in short transfer phase configuration

TIM 2.9.2 TRGO and TRGO2 trigger output failure

I2C 2.12.6 Wrong behavior in Stop mode when wakeup from Stop mode is disabled in I2C

SPI 2.14.5 CRC error in SPI slave mode if internal NSS changes before CRC transfer

USB 2.15.1 Possible packet memory overrun/underrun at low APB frequency

ES0262 - Rev 4

page 4/31

STM32F078CB/RB/VB

Description of device errata

2 Description of device errata

The following sections describe limitations of the applicable devices with Arm® core and provide workarounds if

available. They are grouped by device functions.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

2.1 Core

Reference manual and errata notice for the Arm® Cortex®-M4F core revision r0p0 is available from http://

infocenter.arm.com.

2.2 System

2.2.1 RDP Level 1 issue

Description

When the RDP Level 1 protection is set, there exists a logic issue that compromises protection of the Flash

memory against debugger access. When the debugger is connected to the device, the first transaction with the

Flash memory after a power on reset/power up is granted because of a race condition existing between this

debugger access and the protection mechanism of the Flash memory. As a result, the debugger may access one

data in the Flash memory after power up.

Workaround

For customers concerned by the confidentiality of their firmware, it is recommended to use the RDP Level 2

protection.

2.3 GPIO

2.3.1 GPIOx locking mechanism not working properly for GPIOx_OTYPER register

Description

Locking GPIOx_OTYPER[i] with i = 15 to 8 unduly depends on GPIOx_LCKR[i-8] instead on GPIOx_LCKR[i].

GPIOx_LCKR[i-8] locks both GPIOx_OTYPER[i] and GPIOx_OTYPER[i-8]. It is not possible to lock

GPIOx_OTYPER[i] with i = 15...8 without also locking GPIOx_OTYPER[i-8].

Workaround

The only way to lock GPIOx_OTYPER[i] with i=15 to 8 is to also lock GPIOx_OTYPER[i-8].

2.4

DMA

2.4.1 DMA disable failure and error flag omission upon simultaneous transfer error and global flag

clear

Description

Upon a data transfer error in a DMA channel x, both the specific TEIFx and the global GIFx flags are raised and

the channel x is normally automatically disabled. However, if in the same clock cycle the software clears the GIFx

flag (by setting the CGIFx bit of the DMA_IFCR register), the automatic channel disable fails and the TEIFx flag is

not raised.

This issue does not occur with ST's HAL software that does not use and clear the GIFx flag when the channel is

active, but uses and clears the HTIFx, TCIFx, and TEIFx specific event flags instead.

ES0262 - Rev 4

page 5/31

Workaround

Do not clear GIFx flags when the channel is active. Instead, use HTIFx, TCIFx, and TEIFx specific event flags and

their corresponding clear bits.

2.4.2 Byte and half-word accesses not supported

Description

Some reference manual revisions may wrongly state that the DMA registers are byte- and half-word-accessible.

Instead, the DMA registers must always be accessed through aligned 32-bit words. Byte or half-word write

accesses cause an erroneous behavior.

ST's low-level driver and HAL software only use aligned 32-bit accesses to the DMA registers.

This is a description inaccuracy issue rather than a product limitation.

Workaround

No application workaround is required.

2.5 ADC

STM32F078CB/RB/VB

ADC

2.5.1 ADCAL bit is not cleared when successive calibrations are performed and system clock

frequency is considerably higher than the ADC clock frequency

Description

The ADC calibration is launched by setting ADCAL bit of ADC_CR register. It can only be initiated when the ADC

is disabled (ADEN cleared in ADC_CR register). ADCAL bit stays at 1 during the whole calibration sequence and

is cleared by hardware as soon the calibration completes.

However, when at least two calibrations are performed in a row and the system clock frequency is considerably

higher than the ADC clock, the ADCAL bit is set again after being cleared by hardware when the first calibration

phase ends. The ADCAL bit remains set, waiting for the calibration to complete and hence for a hardware clear

that never occurs since the ADC clock is stopped.

Workaround

Avoid performing successive calibrations.

2.5.2 Overrun flag is not set if EOC reset coincides with new conversion end

Description

If the EOC flag is cleared by an ADC_DR register read operation or by software during the same APB cycle in

which the data from a new conversion are written in the ADC_DR register, the overrun event duly occurs (which

results in the loss of either current or new data) but the overrun flag (OVR) may stay low.

Workaround

Clear the EOC flag, by performing an ADC_DR read operation or by software within less than one ADC

conversion cycle period from the last conversion cycle end, in order to avoid the coincidence with the end of the

new conversion cycle.

2.5.3 ADEN bit cannot be set immediately after the ADC calibration

Description

At the end of the ADC calibration, an internal reset of ADEN bit occurs four ADC clock cycles after the ADCAL bit

is cleared by hardware. As a consequence, if the ADEN bit is set within those four ADC clock cycles, it is reset

shortly after by the calibration logic and the ADC remains disabled.

ES0262 - Rev 4

page 6/31

Workaround

Apply one of the following measures:

• When the ADC calibration is complete (ADCAL = 0), keep setting the ADEN bit until the ADRDY flag goes

high.

• After the ADCAL is cleared, wait for a minimum of four ADC clock cycles before enabling the ADC

(ADEN = 1).

• Always perform the ADC calibration with ADC clock frequency = APB frequency / 2.

2.6 DAC

2.6.1 DMA request not automatically cleared by clearing DMAEN

Description

Upon an attempt to stop a DMA-to-DAC transfer, the DMA request is not automatically cleared by clearing the

DAC channel bit of the DAC_CR register (DMAEN) or by disabling the DAC clock.

If the application stops the DAC operation while the DMA request is pending, the request remains pending while

the DAC is reinitialized and restarted, with the risk that a spurious DMA request is serviced as soon as the DAC is

enabled again.

STM32F078CB/RB/VB

DAC

Workaround

Apply the following sequence to stop the current DMA-to-DAC transfer and restart the DAC:

1. Check if DMAUDR bit is set in DAC_CR.

2. Clear the DAC channel DMAEN bit.

3. Disable the DAC clock.

4. Reconfigure the DAC, DMA and the triggers.

5. Restart the application.

2.6.2 DMA underrun flag not set when an internal trigger is detected on the clock cycle of the DMA

request acknowledge

Description

When the DAC channel operates in DMA mode (DMAEN of DAC_CR register set), the DMA channel underrun

flag (DMAUDR of DAC_SR register) fails to rise upon an internal trigger detection if that detection occurs during

the same clock cycle as a DMA request acknowledge. As a result, the user application is not informed that an

underrun error occurred.

This issue occurs when software and hardware triggers are used concurrently to trigger DMA transfers.

Workaround

None.

2.7 COMP

2.7.1 Long V

Description

The V

REFINT

comparator input.

The maximum V

of the V

time depends mainly on the voltage and temperature. See the device datasheet for more details.

ES0262 - Rev 4

scaler startup time after power on

REFINT

scaler is an embedded voltage follower providing the V

scaler startup time t

REFINT

scaler after powering on the device. In worst-case conditions, it can be as much as 1 s. The startup

REFINT

(max), specified to 0.2 ms, is not respected for the first activation

S_SC

or its fractions (½, ¼ or ¾) to the

REFINT

page 7/31

STM32F078CB/RB/VB

TSC

For correct operation of the V

Workaround

None.

scaler, the comparator analog supply voltage, V

REFINT

2.8 TSC

2.8.1 Inhibited acquisition in short transfer phase configuration

Description

Some revisions of the reference manual may omit the information that the following configurations of the TSC_CR

register are forbidden:

• The PGPSC[2:0] bitfield set to 000 and the CTPL[3:0] bitfield to 0000 or 0001

• The PGPSC[2:0] bitfield set to 001 and the CTPL[3:0] bitfield to 0000

Failure to respect this restriction leads to an inhibition of the acquisition.

This is a documentation inaccuracy issue rather than a product limitation.

Workaround

No application workaround is required.

2.9 TIM

, must not be below 2 V.

DDA

2.9.1 PWM re-enabled in automatic output enable mode despite of system break

Description

In automatic output enable mode (AOE bit set in TIMx_BDTR register), the break input can be used to do a cycleby-cycle PWM control for a current mode regulation. A break signal (typically a comparator with a current

threshold ) disables the PWM output(s) and the PWM is re-armed on the next counter period.

However, a system break (typically coming from the CSS Clock security System) is supposed to stop definitively

the PWM to avoid abnormal operation (for example with PWM frequency deviation).

In the current implementation, the timer system break input is not latched. As a consequence, a system break

indeed disables the PWM output(s) when it occurs, but PWM output(s) is (are) re-armed on the following counter

period.

Workaround

Preferably, implement control loops with the output clear enable function (OCxCE bit in the TIMx_CCMR1/CCMR2

register), leaving the use of break circuitry solely for internal and/or external fault protection (AOE bit reset).

2.9.2 TRGO and TRGO2 trigger output failure

Description

Some reference manual revisions may omit the following information.

The timers can be linked using ITRx inputs and TRGOx outputs. Additionally, the TRGOx outputs can be used as

triggers for other peripherals (for example ADC). Since this circuitry is based on pulse generation, care must be

taken when initializing master and slave peripherals or when using different master/slave clock frequencies:

• If the master timer generates a trigger output pulse on TRGOx prior to have the destination peripheral clock

enabled, the triggering system may fail.

• If the frequency of the destination peripheral is modified on-the-fly (clock prescaler modification), the

triggering system may fail.

As a conclusion, the clock of the slave timer or slave peripheral must be enabled prior to receiving events from

the master timer, and must not be changed on-the-fly while triggers are being received from the master timer.

This is a documentation issue rather than a product limitation.

ES0262 - Rev 4

page 8/31

Workaround

No application workaround is required or applicable as long as the application handles the clock as indicated.

2.9.3 Consecutive compare event missed in specific conditions

Description

Every match of the counter (CNT) value with the compare register (CCR) value is expected to trigger a compare

event. However, if such matches occur in two consecutive counter clock cycles (as consequence of the CCR

value change between the two cycles), the second compare event is missed for the following CCR value

changes:

in edge-aligned mode, from ARR to 0:

•

– first compare event: CNT = CCR = ARR

– second (missed) compare event: CNT = CCR = 0

•

in center-aligned mode while up-counting, from ARR-1 to ARR (possibly a new ARR value if the period is

also changed) at the crest (that is, when TIMx_RCR = 0):

– first compare event: CNT = CCR = (ARR-1)

– second (missed) compare event: CNT = CCR = ARR

•

in center-aligned mode while down-counting, from 1 to 0 at the valley (that is, when TIMx_RCR = 0):

– first compare event: CNT = CCR = 1

– second (missed) compare event: CNT = CCR = 0

This typically corresponds to an abrupt change of compare value aiming at creating a timer clock single-cyclewide pulse in toggle mode.

As a consequence:

• In toggle mode, the output only toggles once per counter period (squared waveform), whereas it is expected

to toggle twice within two consecutive counter cycles (and so exhibit a short pulse per counter period).

• In center mode, the compare interrupt flag does note rise and the interrupt is not generated.

Note: The timer output operates as expected in modes other than the toggle mode.

STM32F078CB/RB/VB

TIM

Workaround

None.

2.9.4 Output compare clear not working with external counter reset

Description

The output compare clear event (ocref_clr) is not correctly generated when the timer is configured in the following

slave modes: Reset mode, Combined reset + trigger mode, and Combined gated + reset mode.

The PWM output remains inactive during one extra PWM cycle if the following sequence occurs:

1. The output is cleared by the ocref_clr event.

2. The timer reset occurs before the programmed compare event.

Workaround

Apply one of the following measures:

• Use BKIN (or BKIN2 if available) input for clearing the output, selecting the Automatic output enable mode

(AOE = 1).

• Mask the timer reset during the PWM ON time to prevent it from occurring before the compare event (for

example with a spare timer compare channel open-drain output connected with the reset signal, pulling the

timer reset line down).

ES0262 - Rev 4

page 9/31

2.10 IWDG

2.10.1 RVU flag not reset in Stop

Description

Successful write to the IWDG_RLR register raises the RVU flag and prevents further write accesses to the

register until the RVU flag is automatically cleared by hardware. However, if the device enters Stop mode while

the RVU flag is set, the hardware never clears that flag, and writing to the IWDG_RLR register is no longer

possible.

Workaround

Ensure that the RVU flag is cleared before entering Stop mode.

2.10.2 PVU flag not reset in Stop

Description

Successful write to the IWDG_PR register raises the PVU flag and prevents further write accesses to the register

until the PVU flag is automatically cleared by hardware. However, if the device enters Stop mode while the PVU

flag is set, the hardware never clears that flag, and writing to the IWDG_PR register is no longer possible.

STM32F078CB/RB/VB

IWDG

Workaround

Ensure that the PVU flag is cleared before entering Stop mode.

2.10.3 WVU flag not reset in Stop

Description

Successful write to the IWDG_WINR register raises the WVU flag and prevents further write accesses to the

register until the WVU flag is automatically cleared by hardware. However, if the device enters Stop mode while

the WVU flag is set, the hardware never clears that flag, and writing to the IWDG_WINR register is no longer

possible.

Workaround

Ensure that the WVU flag is cleared before entering Stop mode.

2.10.4 RVU flag not cleared at low APB clock frequency

Description

Successful write to the IWDG_RLR register raises the RVU flag and prevents further write accesses to the

register until the RVU flag is automatically cleared by hardware. However, at APB clock frequency lower than

twice the IWDG clock frequency, the hardware never clears that flag, and writing to the IWDG_RLR register is no

longer possible.

Workaround

Set the APB clock frequency higher than twice the IWDG clock frequency.

2.10.5 PVU flag not cleared at low APB clock frequency

Description

Successful write to the IWDG_PR register raises the PVU flag and prevents further write accesses to the register

until the PVU flag is automatically cleared by hardware. However, at APB clock frequency lower than twice the

IWDG clock frequency, the hardware never clears that flag, and writing to the IWDG_PR register is no longer

possible.

ES0262 - Rev 4

page 10/31

Loading...

Loading...