Page 1

UM2792

User manual

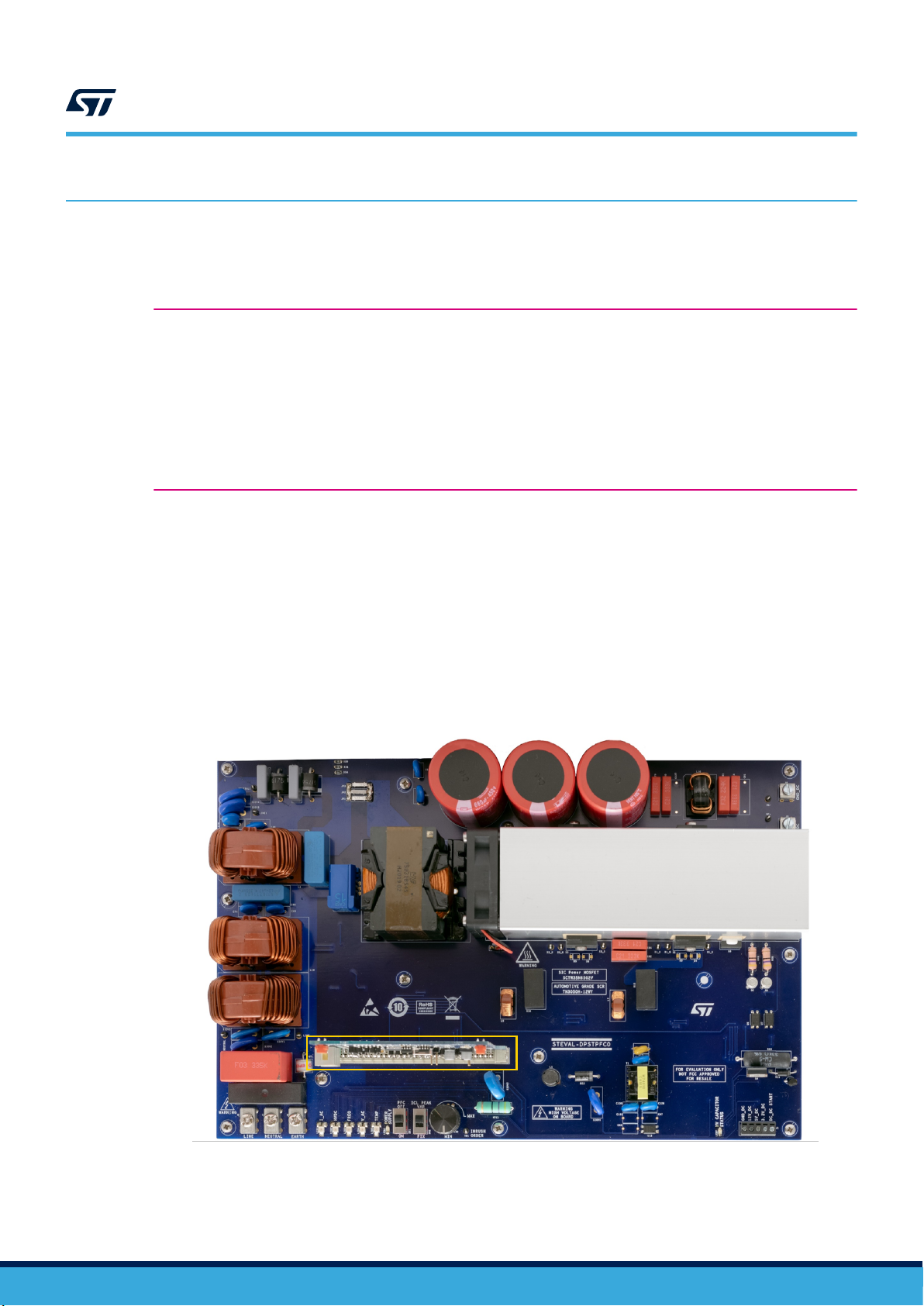

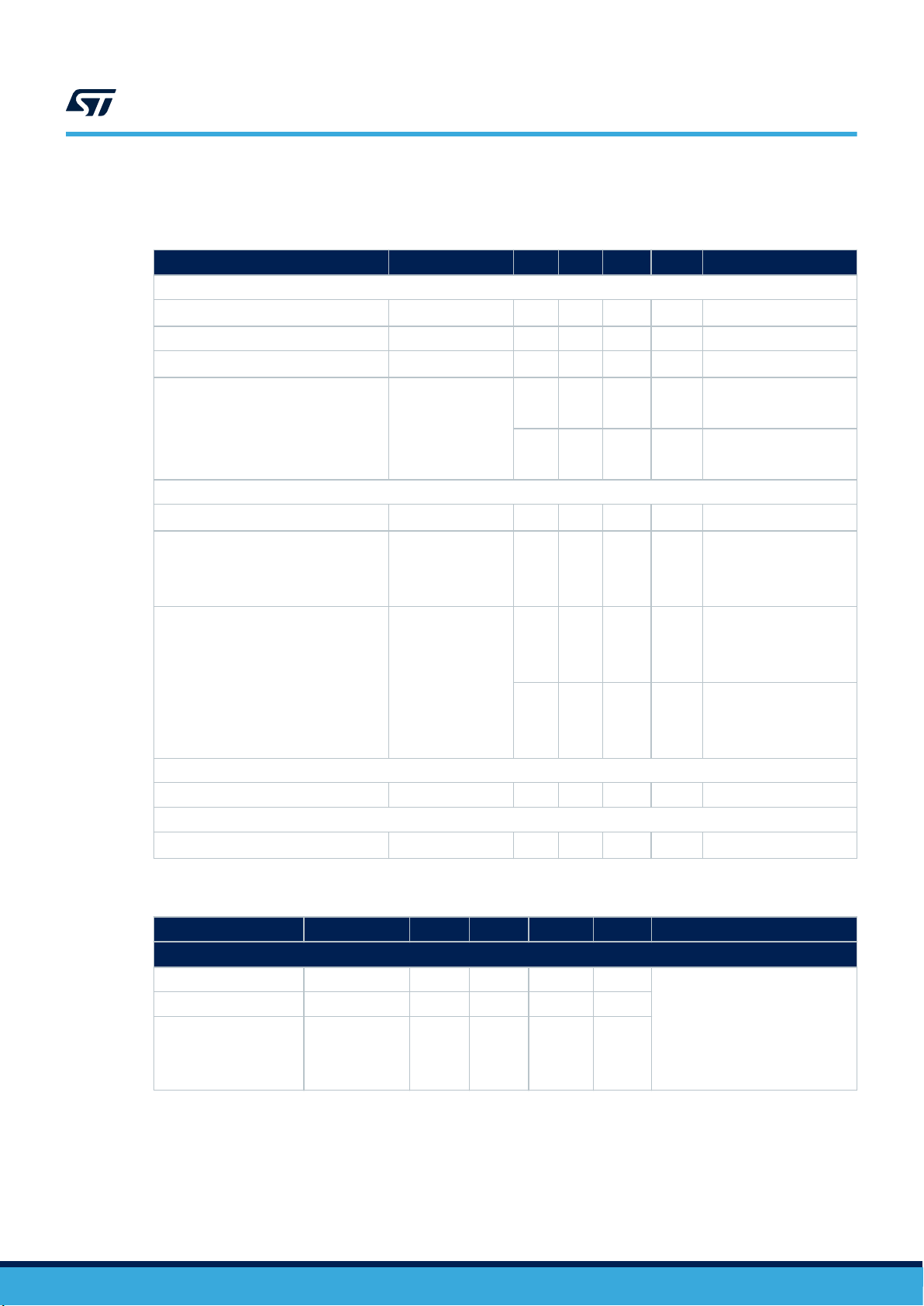

Getting started with the STEVAL-DPSTPFC1 3.6 kW PFC totem pole with inrush

current limiter reference design

Introduction

The STEVAL-DPSTPFC1 3.6 kW bridgeless totem pole boost circuit achieves a digital power factor correction (PFC) with inrush

current limiter (ICL). It helps you to design an innovative topology with the latest ST power kit devices: silicon carbide MOSFETs

(SCTW35N65G2V), thyristor SCRs (TN3050H-12WY), isolated FET drivers (STGAP2S) and a 32-bit MCU (STM32F334).

This reference design also opens the path to a compact converter running at 72 kHz offering a high peak efficiency, low THD

distortion (97.5 % with 3.7 % THD) and reduced bill of materials.

It achieves a robust circuit that meets EMC standards up to 4 kV delivering high switching lifetime with reduced EMI emissions.

Thyristor SCRs used as AC line polarity switches allow achieving an active current limitation at power up or line drop recovery:

the PFC efficiency is optimal and no EMI bouncing effect occurs.

The reference design includes a power board with a bridgeless totem pole boost (with an inrush limiter circuit, switch drivers and

an auxiliary power supply), a control board with its MCU, a PFC/ICL control firmware and an adapter board for software debug.

Figure 1. STEVAL-DPSTPFC1 totem pole

UM2792 - Rev 1 - January 2021

For further information contact your local STMicroelectronics sales office.

www.st.com

Page 2

UM2792

Getting started

1 Getting started

1.1 Safety instructions

Attention: The STEVAL-DPSTPFC1 evaluation board is designed for demonstration purposes only and is not intended for

domestic or industrial installations.

Danger:

The high voltage levels used to operate the STEVAL-DPSTPFC1 evaluation board could provoke

a serious electrical shock. This evaluation board has to be used in a suitable laboratory by

qualified personnel only, familiar with the installation, use, and maintenance of power electrical

systems.

The STEVAL-DPSTPFC1 radiated field levels could exceed the general public exposure limit if

positioned at less than 60 cm.

During operation, do not touch the board as some of its components could reach a very high

temperature.

1.2

Overview

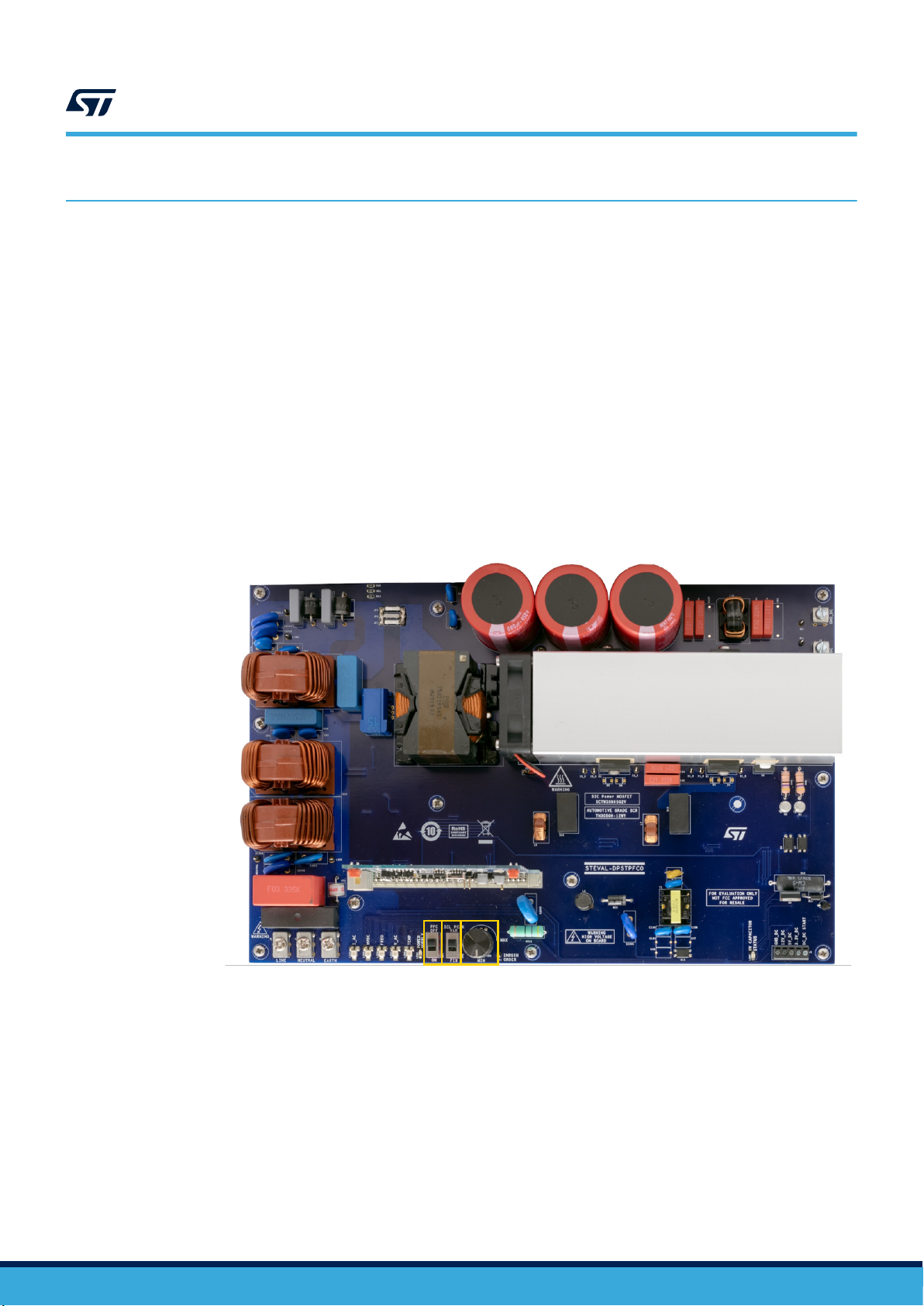

The STEVAL-DPSTPFC1 is a 3.6 kW PFC totem pole controlled by an STM32 MCU. It has been designed to

offer high performances in terms of efficiency, THD, power factor and reliability by controlling the inrush current at

board startup.

The totem pole board is composed of three different boards:

• an AC-DC power board

• a digital control board based on the STM32F334 microcontroller used to control the PFC stage

• an adapter board to debug the MCU firmware

Figure 2. STEVAL-DPSTPFC1 AC-DC power board and PFC control board (highlighted in yellow)

UM2792 - Rev 1

page 2/101

Page 3

Figure 3. STEVAL-DPSTPFC1 adapter board

UM2792

Main components

1.3

The STEVAL-DPSTPFC1 offers:

• inrush current limitation without inrush current resistor or NTC and relay

• very high efficiency AC-DC conversion

• DC power stage disconnection from the AC line grid thanks to SCRs

Main components

The STEVAL-DPSTPFC1 main components are:

• TN3050H-12WY inrush current limiter SCRs

• SCTW35N65G2V SiC MOSFETs

• STM32F334 MCU

• VIPER26LD flyback IC

UM2792 - Rev 1

page 3/101

Page 4

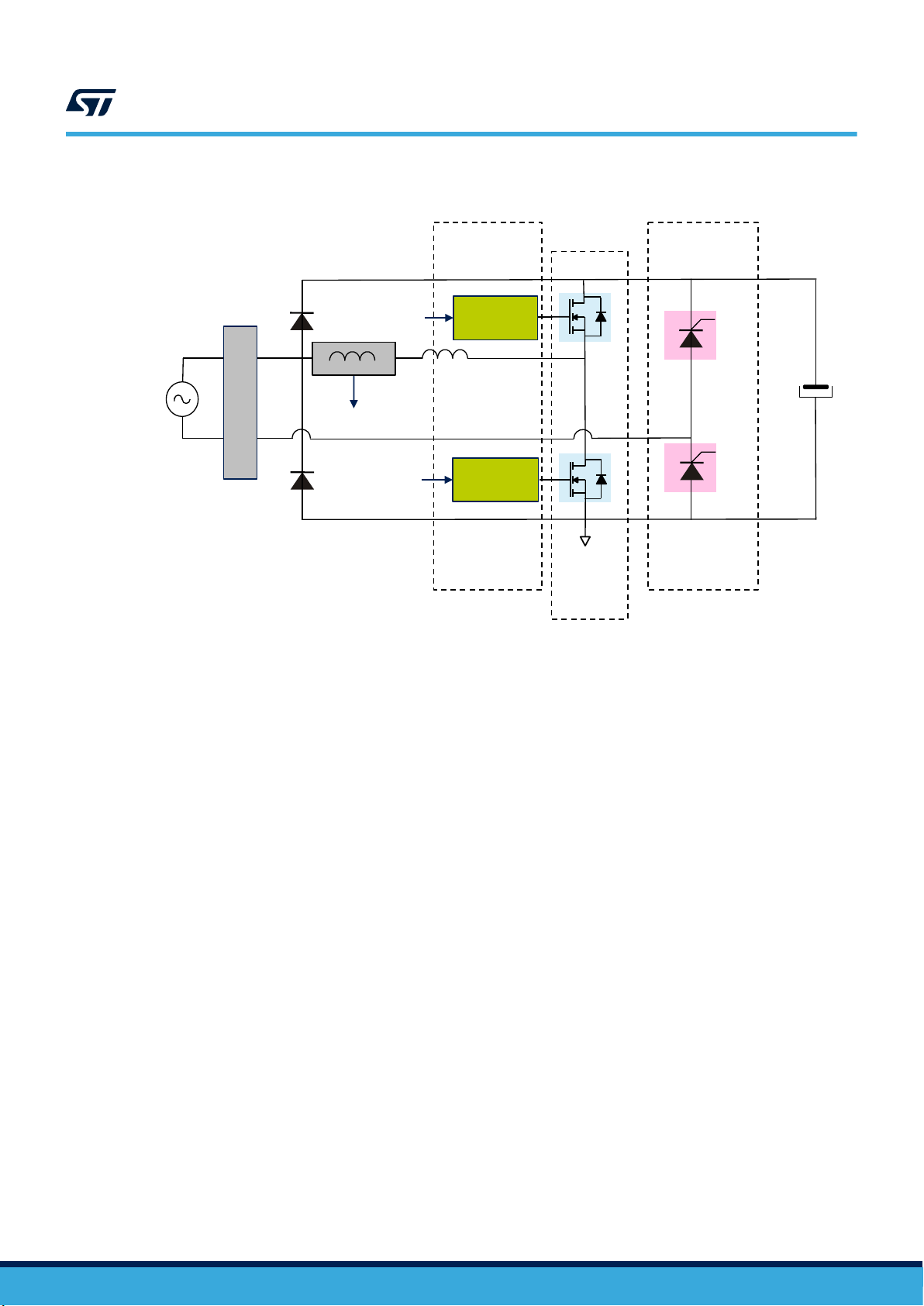

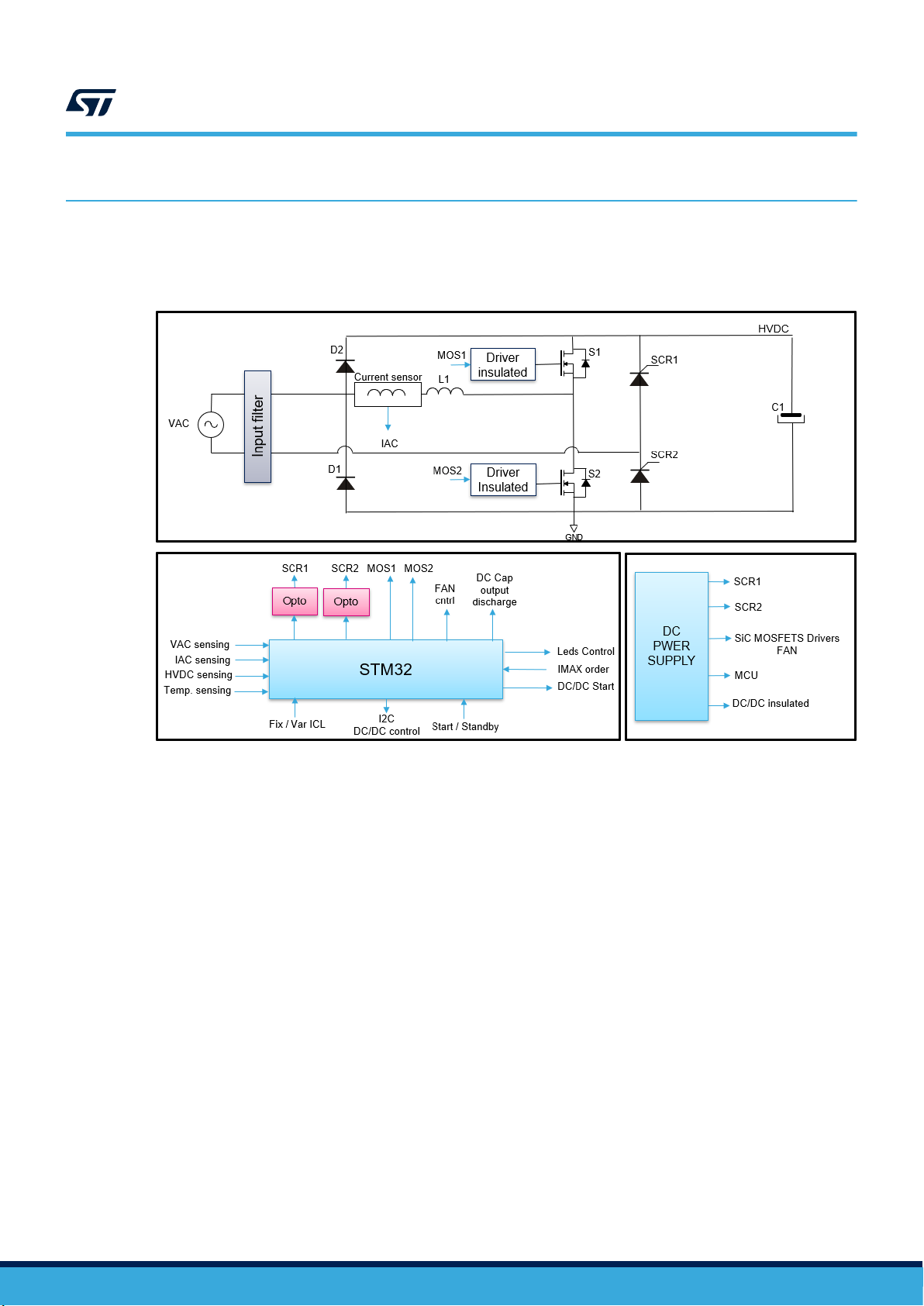

Figure 4. STEVAL-DPSTPFC1 main component diagram

Insulated

SCR

1

1

TN3050H-12WY

SCTW35N65G2V

STGAP2S

V

Driver

Current sensor

AC

S

AC

insulated

I

2

2

HVDC

Driver

Input filter

S

SCR

UM2792

Main components

UM2792 - Rev 1

page 4/101

Page 5

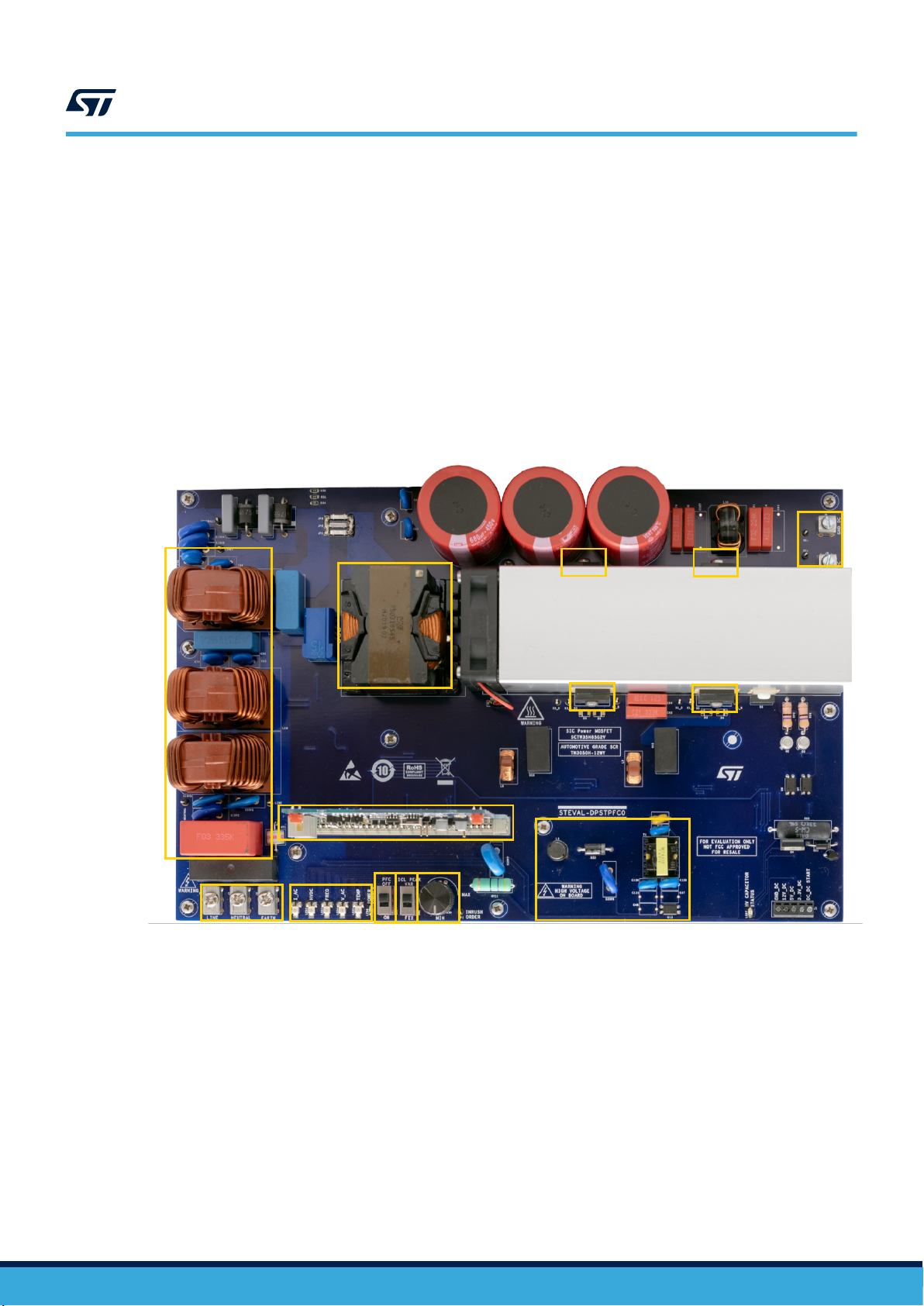

Figure 5. STEVAL-DPSTPFC1 components - overview

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1. Common mode filter + MOV

2. Boost inductor

3. SCR

4. SCR

5. DC load connectors

6. SiC MOSFET

7. SiC MOSFET

8. DC power supply

9. MCU daughter board

10. Potentiometer to control peak inrush current

11. ICL strategy control switch

12. ICL startup switch

13. PFC LEDs status

14. AC line connectors

UM2792

Main components

UM2792 - Rev 1

page 5/101

Page 6

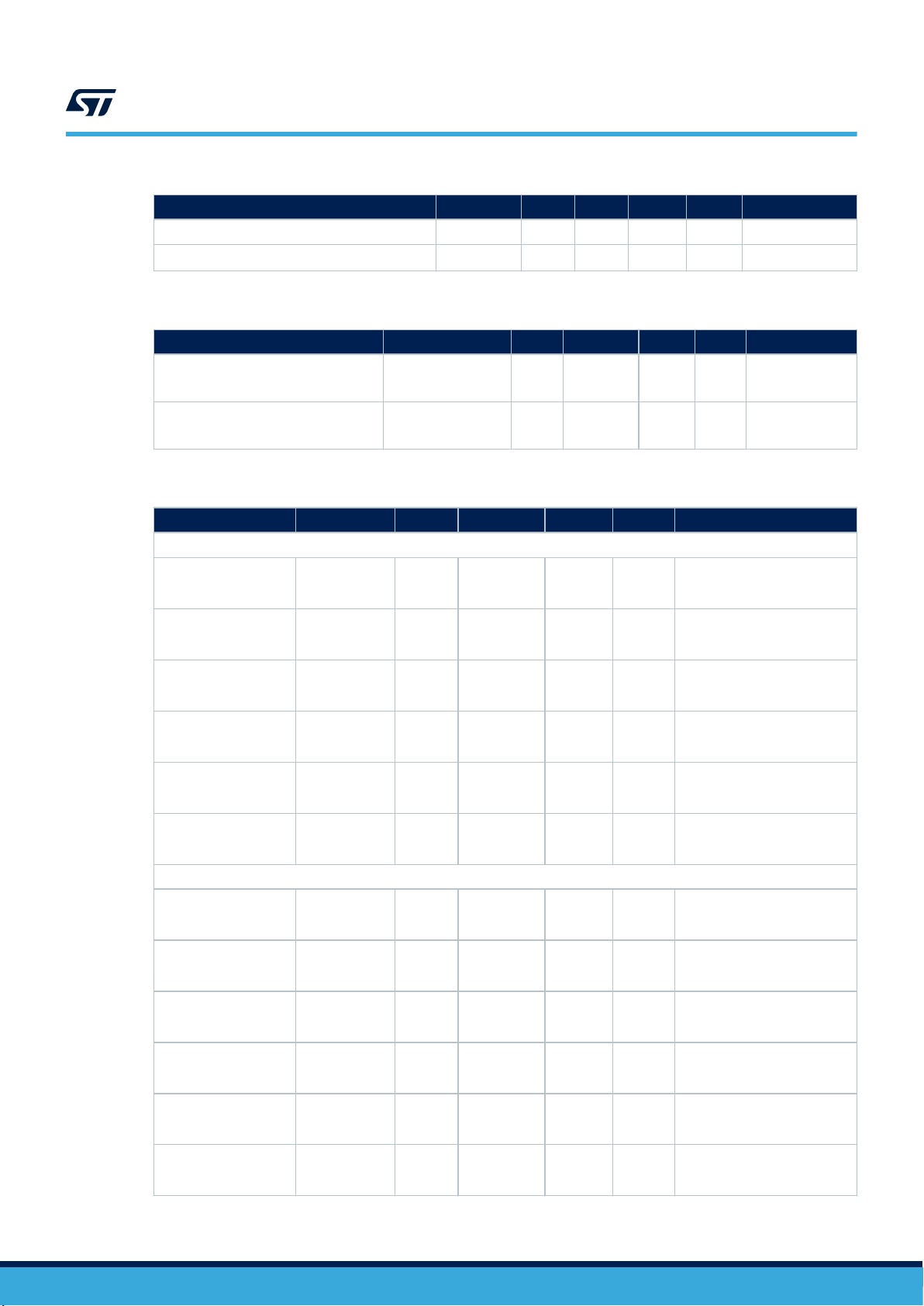

1.4 Totem pole PFC specifications

Table 1. PFC electrical specifications

Description Symbol Min. Typ. Max. Unit Comments

Input

AC line voltage

AC line frequency HZ 45 65

AC line current

Maximum input power PIN MAX

Output

Output voltage regulated HVDC 400 420

HVDC ripple Vripple (PK-PK) 15 V

Maximum output DC current

Control

Switching frequency Fs 72 kHz

Operating temperature

Maximum ambient temperature

V

AC

IAC MAX

IDC Max

T

AMB

MAX

85 264

16

3.6 kW

1.8 kW

9 A

4 A

45 °C

UM2792

Totem pole PFC specifications

V

RMS

A

RMS

VAC = 230 V

IAC MAX = 16 A

VAC = 110 V

IAC MAX = 16 A

V

DC

P

OUT

VAC = 230 V

IAC MAX = 16 A

P

OUT

VAC = 230 V

IAC MAX = 16 A

P

OUT

VAC = 110 V

IAC = 16 A

RMS

RMS

RMS

RMS

= 3.6 kW

RMS

RMS

= 3.6 kW

RMS

RMS

= 1.7 kW

RMS

RMS

UM2792 - Rev 1

Table 2. PFC temperature specifications

Description

Thermal components

Inductor T_Choke 120 °C T

Sic MOSFETs TC_MOS 80 °C

SCRs TC_SCR 65 °C

Symbol Min. Typ. Max. Unit Comments

= 30°C

AMB

FAN ON

P

= 3.6 kW

OUT

VAC = 230 V

RMS

IAC MAX = 16 A

RMS

page 6/101

Page 7

Totem pole PFC specifications

Table 3. PFC protection specifications

Description Symbol Min. Typ. Max. Unit Comments

HVDC overvoltage protection 450 VDC

IAC peak overcurrent protection

24 A

Table 4. Passive component specifications

Description Symbol Min. Typ. Max. Unit Comments

Primary EMI filter inductor

Output capacitor

L_FILT

L3 / L4 / L14

C_HVDC

C76/C77/C78

3 x 1.6 mH

3 x 680 µF

Table 5. PFC efficiency specifications

Description Symbol Min. Typ. Max. Unit Comments

Power factor

230 V

PF 0.9903 N.A.

PF 0.9956 N.A.

PF 0.9965 N.A.

PF 0.9932 N.A.

PF 0.9982 N.A.

PF 0.9981 N.A.

Distortion

THD 6.9 %

THD 3.7 %

THD 3.5 %

THD 9.7 %

THD 4.6 %

THD 4.2 %

RMS

IAC = 4.5 A

230 V

RMS

IAC = 8.8 A

230 V

RMS

IAC = 15.5 A

110 V

RMS

IAC = 3.8 A

110 V

RMS

IAC = 9.5 A

110 V

RMS

IAC = 15.5 A

230 V

RMS

IAC = 4.5 A

230 V

RMS

IAC = 8.8 A

230 V

RMS

IAC = 15.5 A

110 V

RMS

IAC = 3.8 A

110 V

RMS

IAC = 9.5 A

110 V

RMS

IAC = 15.5 A

UM2792

/50 Hz

RMS

/50 Hz

RMS

/50 Hz

RMS

/60 Hz

RMS

/50 Hz

RMS

/60 Hz

RMS

/50 Hz

RMS

/50 Hz

RMS

/50 Hz

RMS

/60 Hz

RMS

/50 Hz

RMS

/60 Hz

RMS

UM2792 - Rev 1

page 7/101

Page 8

Description Symbol Min. Typ. Max. Unit Comments

Efficiency

230 V

η 96.8 %

η 97.5 %

η 97.2 %

η 92.4 %

η 94.8 %

η 94.6 %

RMS

IAC = 4.5 A

230 V

RMS

IAC = 8.8 A

230 V

RMS

IAC = 15.5 A

110 V

RMS

IAC = 3.8 A

110 V

RMS

IAC = 9.5 A

110 V

RMS

IAC = 15.5 A

UM2792

Status LEDs

/50 Hz

RMS

/50 Hz

RMS

/50 Hz

RMS

/60 Hz

RMS

/50 Hz

RMS

/60 Hz

RMS

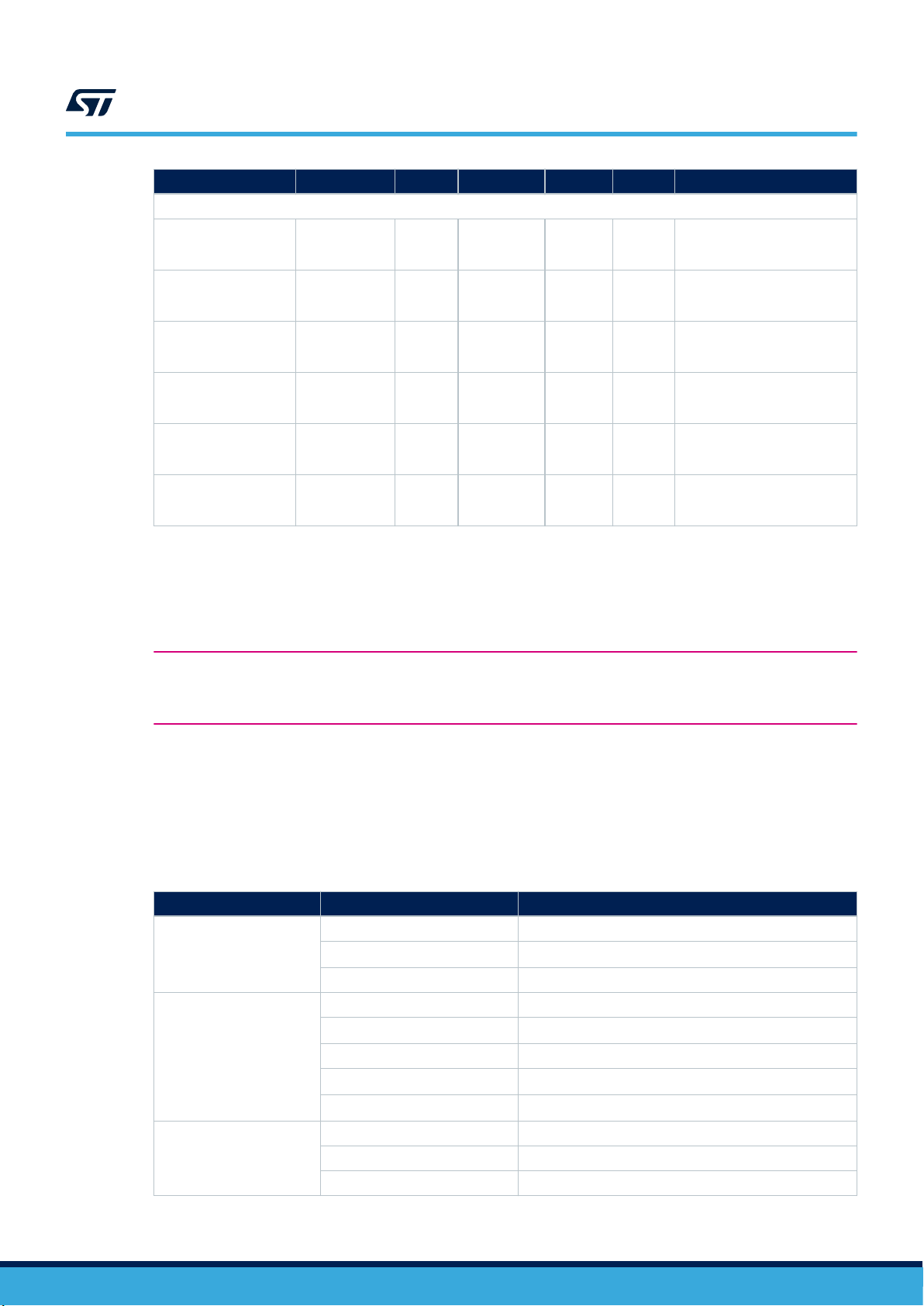

1.5 Status LEDs

The following board LEDs define the PFC status:

• HV CAPACITOR DISCHARGE - LED7: lights up in red when the HVDC output voltage is higher than 30 V

(voltage between HVDC and GND_DC terminals)

Danger:

While LED7 is red, the DC output capacitor is not discharged and could provoke a serious

electrical shock

• POWER_SUPPLY - LED6: lights up in red when the PFC totem pole board is powered

• PFC STATUS LEDs (LED 1/2/3/4/5): at board startup, all these LEDs are alternatively lit in red, then orange,

green and then OFF. This indicates the microcontroller has finalized the initialization procedure (right mains

connection, line frequency measurement, power supply available, etc.) and the board is ready to be used.

From this moment, the DC output capacitor can be charged when the HVDC switch (SW1) is in the ON

position.

LEDs definition LEDs state Comments

IAC (LED1)

HVDC (LED2)

FREQ (LED3)

Table 6. Status LEDs

OFF PFC board not supplied

GREEN

RED IAC_Peak > 25 A

OFF PFC board not supplied

GREEN

GREEN FLASHING DC output capacitor in charge

ORANGE

RED

OFF PFC board not supplied

GREEN 45 Hz < AC Line frequency < 65 Hz

ORANGE AC Line frequency < 45 Hz

IAC < 16 A

RMS

HVDC = 400 V

HVDC < 380 V

HVDC > 450 V

DC

DC

DC

DC

UM2792 - Rev 1

page 8/101

Page 9

LEDs definition LEDs state Comments

FREQ (LED3)

RED AC Line frequency > 65 Hz

OFF PFC board not supplied

VAC (LED4)

GREEN

ORANGE

RED

85 V

< VAC < 264 V

RMS

VAC < 85 V

VAC > 264 V

OFF PFC board not supplied

TEMP (LED5)

GREEN Heat sink temperature < 120 °C

ORANGE N.A.

RED Heat sink temperature > 120°C

Figure 6. PFC status LEDs overview

UM2792

Status LEDs

RMS

RMS

RMS

UM2792 - Rev 1

page 9/101

Page 10

2 Board connection and startup

1

2

3

2.1 Mechanical switches and potentiometer configuration

Step 1. Push the FC switch (SW1) on OFF position

Step 2. To control the inrush current by SCRs with a constant progressive phase control, push the ICL_PEAK

switch (SW2) on VAR position. The constant progressive phase control value is defined by the max.

inrush current potentiometer (R30)

Step 3. To control the inrush current by SCRs with a variable progressive phase control, push the ICL_PEAK

switch on FIX position.

Step 4. The max. inrush current potentiometer (R30) value is read only by the MCU if the ICL_PEAK switch

is set to VAR position. Max. inrush current potentiometer is used to define the constant progressive

phase control value. The DC capacitor charge speed can be increased if the allowed peak current is

increased. For this purpose, the max. inrush current potentiometer has to be turned clockwise.

Figure 7. STEVAL-DPSTPFC1 switches and potentiometer

1. PFC switch (SW1)

2. ICL_PEAK switch (SW2)

3. Max. inrush current potentiometer (R30)

UM2792

Board connection and startup

UM2792 - Rev 1

page 10/101

Page 11

2.2 AC line wires connection

Step 1. Connect the line (L), neutral (N) and earth (PE) wires with J3, J6 and J7 headers, respectively, to an

unpowered mains plug.

UM2792

AC line wires connection

Figure 8. AC line wire connection overview

2.3 Output DC load connection

Step 1. Connect the DC load between the HVDC and GND_DC connectors.

Figure 9. STEVAL-DPSTPFC1 output HVDC connection

If an electronic DC load is used:

– connect the positive input of the electronic DC load to HVDC connector

– connect the negative input of the electronic DC load to GND_DC connector

UM2792 - Rev 1

page 11/101

Page 12

2.4 PFC board power on

Step 1. Put the AC line voltage ON.

Danger: Do not touch components under the AC line voltage.

The power supply LED6 lights up in red to signal the PFC totem pole board is powered. The PFC

status LEDs (LED1/2/3/4/5) blinking sequence is red, orange, green. At board startup, parameters like

VAC, IAC, temperature and current sensor are checked. After board initialization, the PFC status LEDs

light up as per the table and figure below.

POWER SUPPLY - LED6 Red light

UM2792

PFC board power on

Table 7. STEVAL-DPSTPFC1 LEDs

Definition State

I_AC - LED1 OFF

HVDAC - LED2 OFF

FREQ - LED3 Green light

V_AC - LED4 Green light

TEMP - LED5 Green light

1. PFC status LEDs (LED1/2/3/4/5)

2. Power supply (LED6)

Figure 10. LED status overview

UM2792 - Rev 1

page 12/101

Page 13

2.5 PFC startup

Step 1. Slide the PFC switch (SW1) to ON to start up the PFC totem pole board (see Figure 7)

The PFC status LEDs must light up as per the following table and Figure 6.

2.6 PFC board turn off

Step 1. Slide the PFC switch (SW1) to OFF position to start up the PFC totem pole board (see Figure 7)

The PFC status LEDs must light up as per the following table and Figure 6. PFC status LEDs overview.

UM2792

PFC startup

Table 8. PFC LED status

Definition Status

I_AC - LED1 Green light

HVDAC - LED2 Green light

FREQ - LED3 Green light

V_AC - LED4 Green light

TEMP - LED5 Green light

POWER SUPPLY - LED6 Red light

HV_CAPACITOR STATUS Red light

Table 9. PFC LED status

Definition Status

I_AC - LED1 OFF

HVDAC - LED2 OFF

FREQ - LED3 Green light

V_AC - LED4 Green light

TEMP - LED5 Green light

POWER SUPPLY - LED6 Red light

HV_CAPACITOR STATUS - LED7 OFF

Note: HV_CAPACITOR STATUS (LED7) switches off after an interval of time that depends on the DC load impedance

(around 3 minutes if no DC load is connected to the HVDC output).

Danger:

When HV_CAPACITOR STATUS (LED7) lights up in red, the DC output capacitor is not

discharged and could provoke a serious electrical shock. This LED remains switched on as long

as the HVDC voltage remains above 30 V.

UM2792 - Rev 1

page 13/101

Page 14

3 DC bus capacitor discharge

R67

HVDC

STQ1NK80ZR-AP

R103

STN4NF03L

D11

D8

Q4

165k

R66

MMSZ5256BT1G

Q5

STN4NF03L

MMSZ5V6T3G

R65

High voltage

visualization

165k

1k

R105

Q7

3.3k

R106

5V_DC

HV_DISCHARGE

R64

R68

GND_DC

165k

R104

Q6

MMSZ5245BT1G

D10

10k

33k 5W

R63

165k

P6KE440A

BUL216

165k

DZ1

165k

HV capacitor discharge

A circuit has been implemented to accelerate the output DC capacitors (C76, C77 and C78) discharge through

R63 resistor. This circuit is turned on every time the PFC board is in OFF state. The full discharge time takes

around 3 minutes when no DC load is connected. LED7 (HV CAPACITOR DISCHARGE) is lit up as long as the

HVDC voltage remains above 30 V.

Figure 11. DC bus capacitor discharge circuit

UM2792

DC bus capacitor discharge

UM2792 - Rev 1

page 14/101

Page 15

4 Additional external components

The STEVAL-DPSTPFC1 board allows adding some external components to the front-end circuit.

4.1 DC-DC circuit connection

A DC-DC converter can be connected to the HVDC bus via HVDC (J3) and GND_DC (J8) connectors. To allow

the correct operation of the STEVAL-DPSTPFC1 front-end circuit, the DC-DC converter has to be activated after

the PFC_START signal has been set to high level state. The PFC_START signal indicates the PFC is operational

and the HVDC output voltage is 400 VDC. This signal refers to GND_DC terminal and is available from the J1

header.

Figure 12. DC-DC converter activation (DC_DC_Start signal) when PFC totem pole is operational

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

UM2792

Additional external components

4.2 Motor inverter connection

An inverter can be added behind the HVDC bus output. A 12 V positive output, referred to the DC Bus Ground

(GND_DC), is available on header J1 to supply an IPM module, if needed.

4.3 Control through an external microcontroller

Instead of using the embedded MCU daughter board, the STEVAL-DPSTPFC1 can be controlled through an

external MCU daughter board to directly check the compliance of its firmware with this board circuit. For

pin numbers and names of the daughter board connectors, refer to the external connectors section shown in

Figure 87. STEVAL-DPSTPFC0 circuit schematic (1 of 4).

UM2792 - Rev 1

page 15/101

Page 16

5 Totem pole PFC control

5.1 Bridgeless PFC totem pole overview

Figure 13. Bridgeless PFC totem pole synoptic

UM2792

Totem pole PFC control

The figure above highlights the main components:

• SCRs (SCR1 and SCR2) in the bridgeless PFC totem pole to:

– control inrush current at board startup

– disconnect the DC link bus (HVDC) from the AC line voltage

• SiC MOSFETs (S1 and S2) to shape the input AC line current

• STGAP2S drivers to control SiC MOSFETs

• an STM32 MCU which mainly drives SCRs and SiC MOSFETs

• a flyback power converter providing:

– 5V_SCR1: 5 VDC insulated output. This supply is used to control SCR1

– 5V_SCR2: 5 VDC insulated output. This supply is used to control SCR2

– 12V_DC: 12 VDC insulated regulated output referenced to the DC bus ground (GND_DC). This supply

is used to supply the insulated DC-DC converter (needed by SiC MOSFETs) and the fan. From this 12

VDC:

◦ a 5V_DC is created to supply current sensor

◦ a 3V3_DC is created to supply the PFC board control and all the control circuits

UM2792 - Rev 1

page 16/101

Page 17

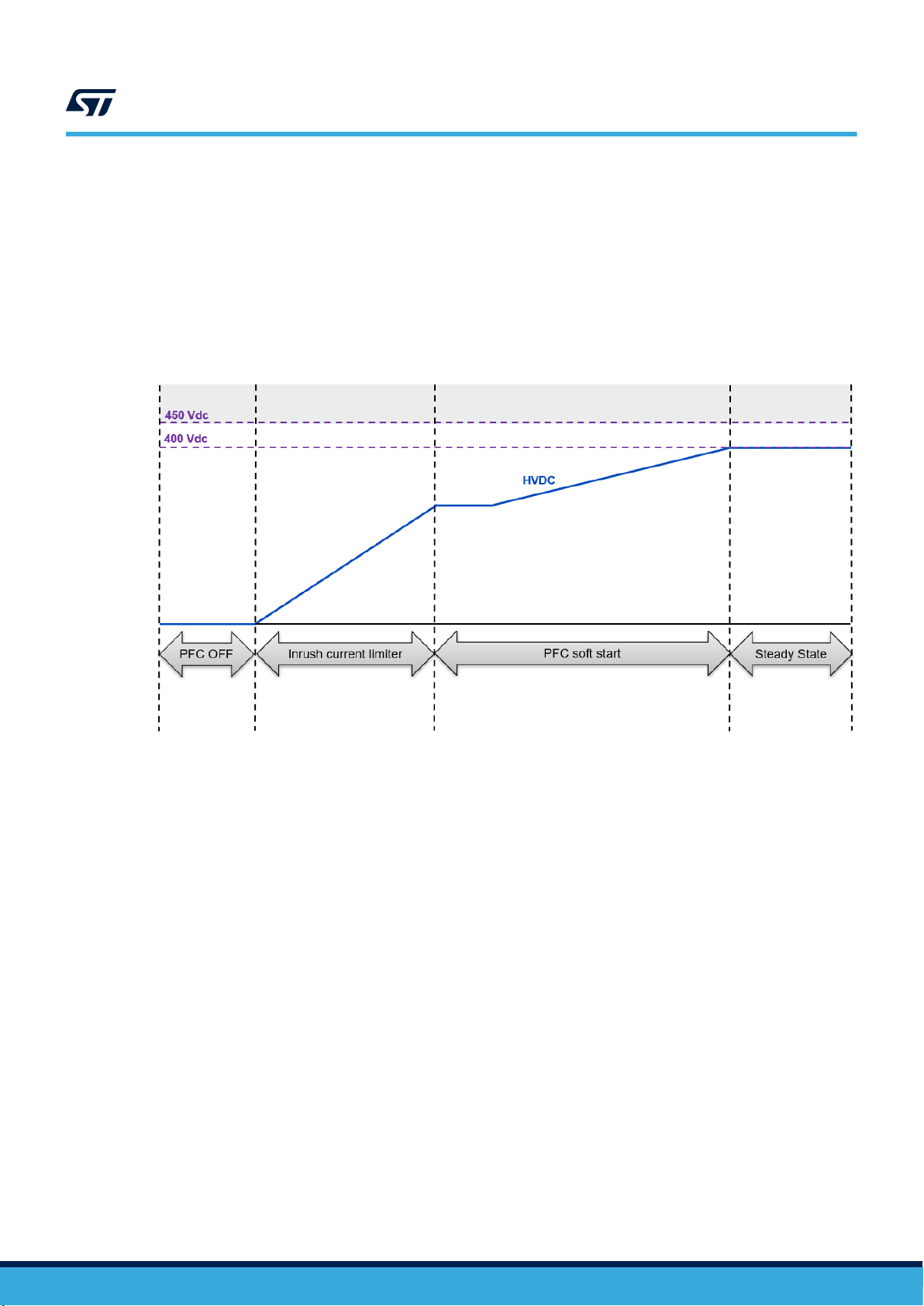

5.2 Soft start

To ensure a smooth PFC startup, a soft start procedure has been implemented in the STM32 MCU:

• to reduce the inrush current at board startup, SCRs are controlled by a progressive phase control and the

output DC capacitor can smoothly increase up to the AC line peak voltage

• to reduce the inrush current when the PFC output voltage (HVDC) switches from the peak AC line voltage to

regulated 400 V

• once the PFC output voltage reference is reached, the PFC output DC voltage (HVDC) is regulated

according to output and input conditions

UM2792

Soft start

DC

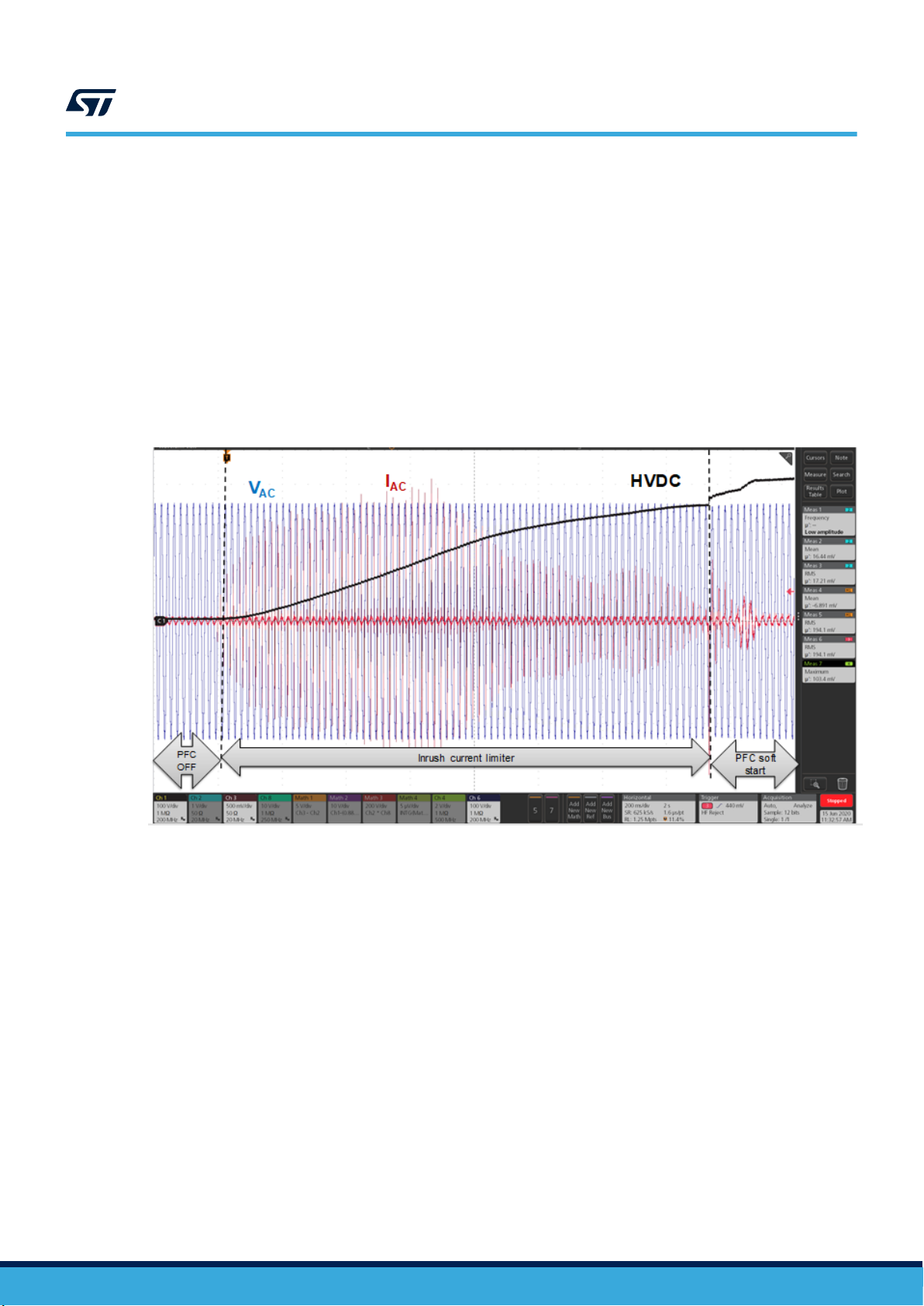

Figure 14. PFC soft start principle

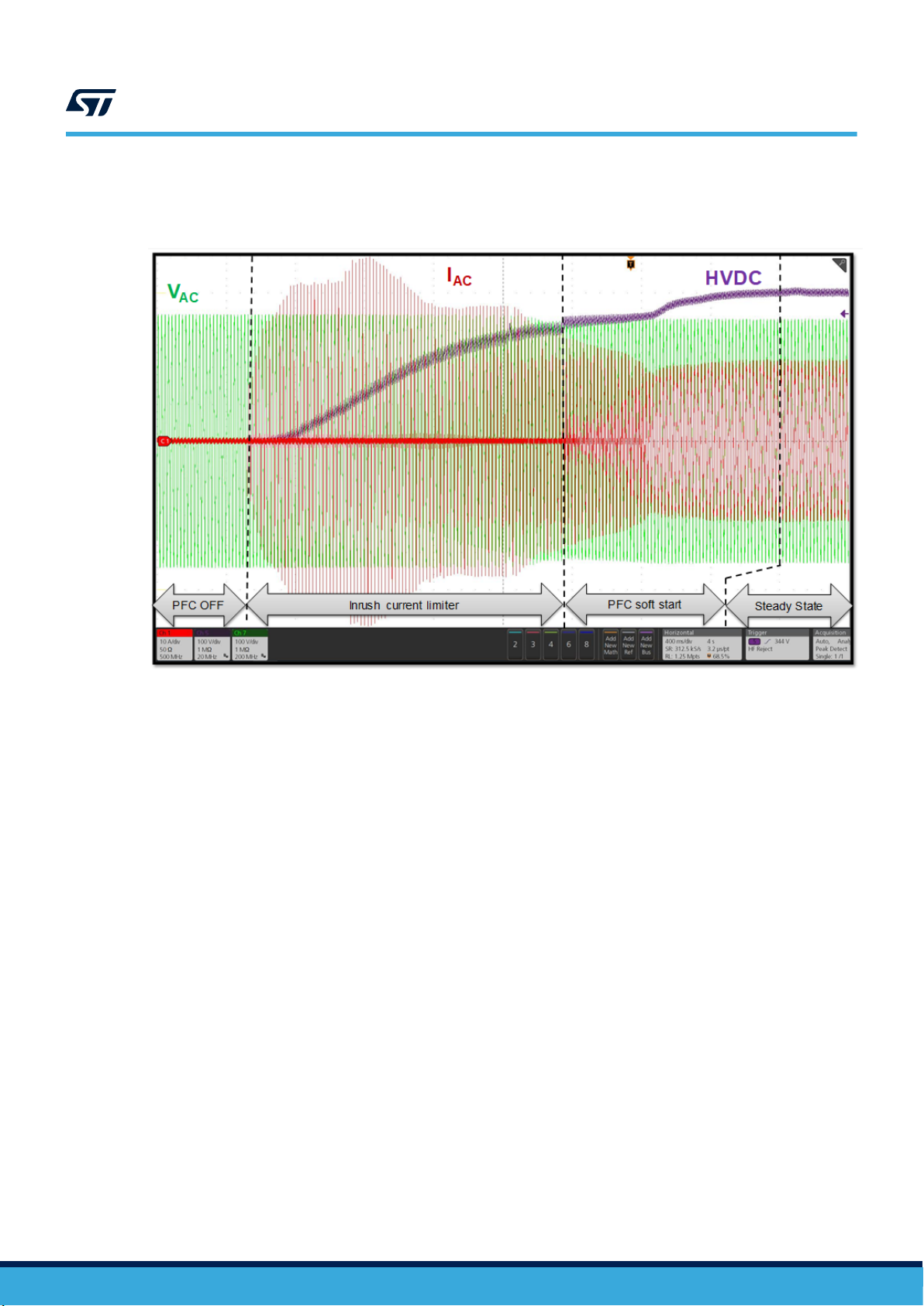

The following figure shows an example of the described progressive PFC soft start. Tests have been performed at

board startup with the board connected to a 230 V 50 Hz grid (VAC) with a 3.3 kW DC load.

UM2792 - Rev 1

page 17/101

Page 18

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

UM2792

Inrush current control

Figure 15. PFC soft start procedure

5.3 Inrush current control

5.3.1 IEC 61000-3-3 standard

The IEC 61000-3-3 standard gives the limitation of voltage changes and fluctuations for equipment with rated

RMS current lower than 16 A when connected to a public low voltage grid.

If a too high current is sunk from the grid, the equipment causes these voltage fluctuations and voltage drop

occurs due to the line impedance.

The mains voltage fluctuation causes undesired brightness variation of lamps and displays (flicker phenomenon).

For this reason, you should keep the inrush current sunk by your equipment lower than the specified limits.

5.3.2 Inrush current controlled by NTC resistor

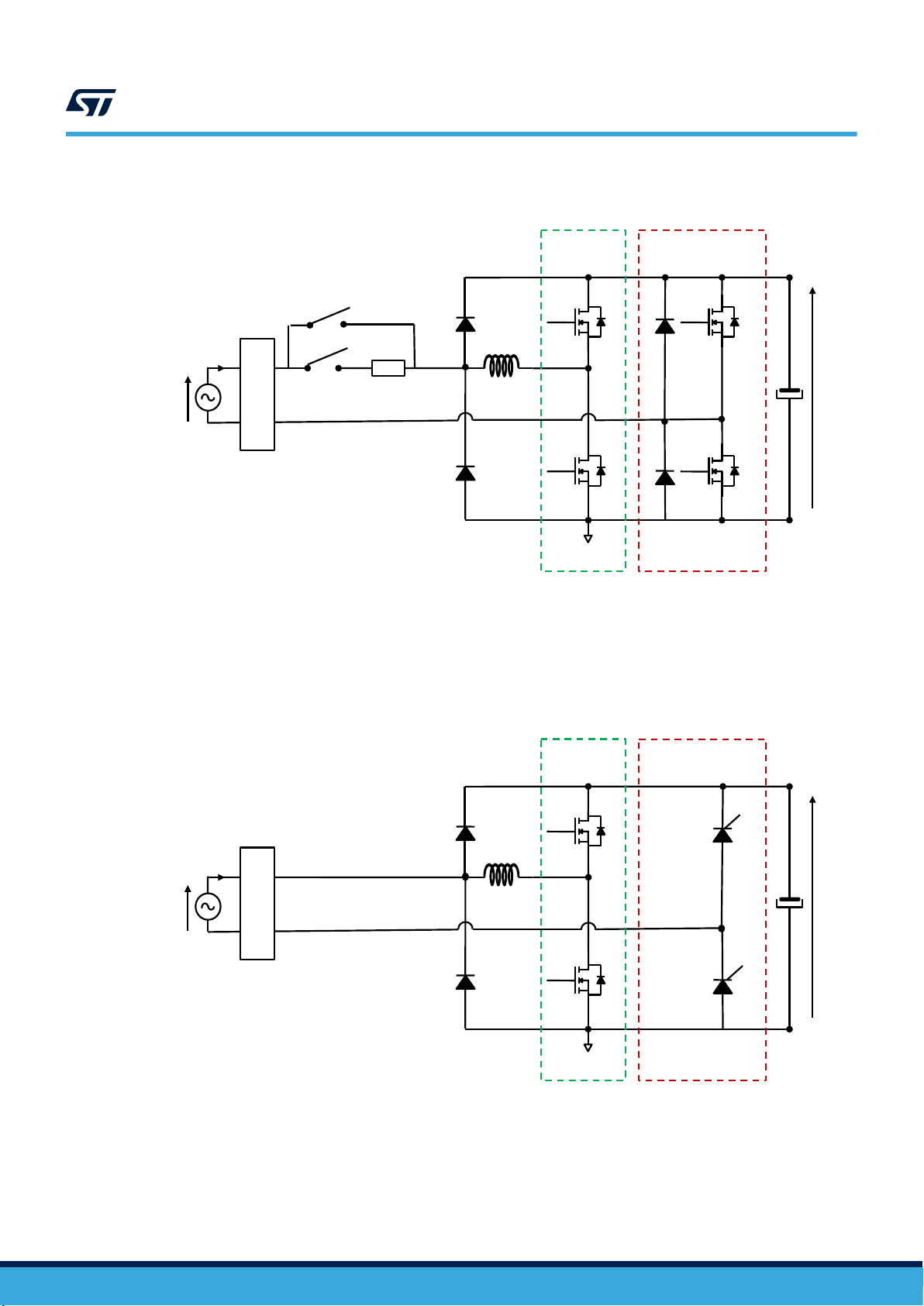

Usually, the PFC totem pole uses diodes (D1/D2) or a standard MOSFET (S3/S4) operating at low frequency.

However, MOSFETs or diodes need a resistor or an NTC (RLim) to control the inrush current at board startup.

The resistor has then to be bypassed by a relay (RL2) to limit the power losses during steady state operation. To

disconnect the DC bus in standby mode, a second relay (RL1) is required. In steady state operation, this solution

increases global power losses due to the relay contact resistor as well as the PFC converter cost.

Note: The contact resistor value increases according to the number of operating cycles and, therefore, decreases PFC

efficiency.

UM2792 - Rev 1

page 18/101

Page 19

Figure 16. PFC totem pole topology with NTC resistor

Low frequency

Diodes or MSOFETs

1

High frequency

4

D

1

D

BP2

GND

S

1

V

AC

AC

S

SiC MOSFETs

2

RLim

RL

EMI FILTER

RL

1

D

3

BP1

2

D

HVDC

S

S

I

C

L

2

SCR

EMI FILTER

S

Low frequency

D

SCRs

BP2

C

GND

SiC MOSFETs

1

V

AC

AC

1

S

BP1

D

1

SCR

L

HVDC

2

I

High frequency

2

UM2792

Inrush current control

5.3.3 Inrush current controlled by SCRs

With the totem pole PFC the capacitor can be smoothly charged with a progressive phase control and avoid the

use of an NTC or a resistor thanks to SCRs.

Figure 17. PFC totem pole topology with SCRs

UM2792 - Rev 1

page 19/101

Page 20

T_OFF_2

TT

T

T_OFF_Max

∆t

5x∆t

2x∆t

3x∆t

TT

T

HVDC

SCR1

T_OFF_Min

T

SCR2

AC

T_OFF_3

T_OFF_1

4x∆t

V

UM2792

Inrush current control

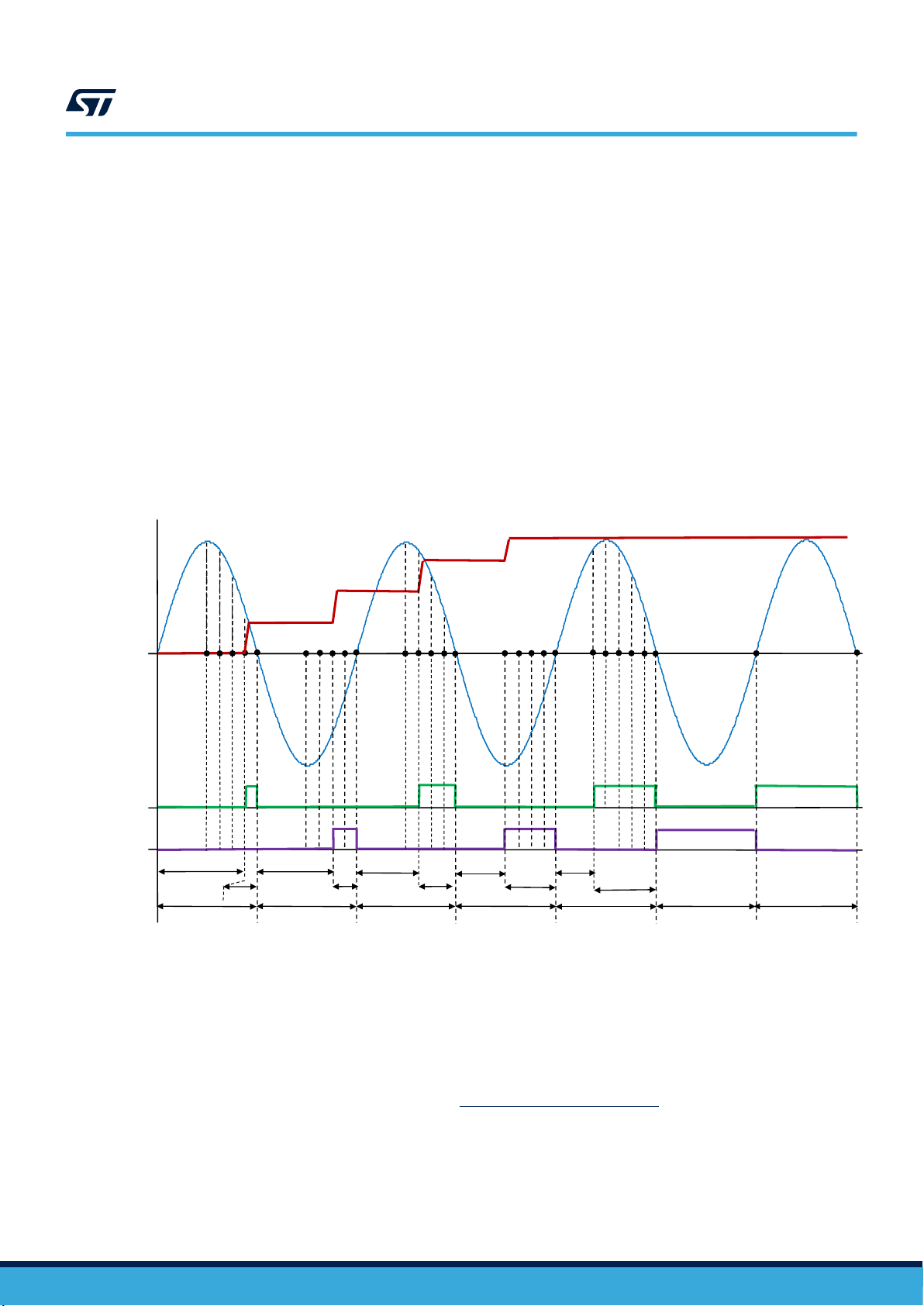

As long as SCRs are not triggered, the bridge does not conduct current and the DC bus capacitor is not charged.

To start charging the DC capacitor, SCR1 and SCR2 have to be turned on according to the AC line voltage

polarity (SCR1 is turned on when the AC line polarity is negative and SCR2 is turned on when the AC line polarity

is positive). To reduce the inrush current, SCRs are alternatively triggered at the end of the half line voltage cycle,

just few hundreds of microseconds before the line zero voltage. This allows the output capacitor to be charged to

a low level (around 10 to 30 V) and not directly to the peak line voltage. The current driven from the line is then

much lower than in case of a direct full charge of the DC capacitor.

This soft start solution can work only when an inductor is present on the line side as the rate of current increase

has also to be limited to prevent SCRs damage. The inductor is already present for most applications where

the EMI filter usually embeds a common mode choke which has a differential mode parasitic inductor due to the

copper turns of the windings.

To control the inrush current at PFC board startup with SCRs, two solutions have been implemented in the MCU

firmware: fixed SCRs on delay and variable SCRs on delay

Fixed SCRs on delay

To allow a complete charge of this capacitor to the peak line voltage, SCRs have to be triggered on the

subsequent half cycle with a shorter turn on delay than the one used to start charging. With VAC, the AC line

voltage and HVDC represent the PFC output voltage.

Figure 18. HV capacitor charges controlled by SCRs

UM2792 - Rev 1

By reducing SCRs turn-on delay by few tens or hundreds of microseconds from half-cycle to half-cycle, the output

capacitor is progressively charged while the line current is kept low. The step of SCRs turn-on delay reduction is

constant from one half-cycle to the following one.

The step of SCRs turn-on delay is defined by reading the MAX_INRUSH CURRENT potentiometer value

on the PFC totem pole board (see Eq. (1)). In the firmware, the step of SCRs turn-on delay is called

Delta_Phase_Angle_μs. Step_Phase_Control_Min_μs is the allowed minimum step of SCRs turn-on

delay (30 μs) and the Delta_Phase_Control_Max_μs parameter is the allowed maximum step of SCRs

turn-on delay (200 μs).

Delta_Control_Max_μs × ADC_Value

12

2

Delta_Pℎase_Angle_μs =

+ Step_Pℎase_Control_Min_μs

(1)

page 20/101

Page 21

UM2792

Inrush current control

When the SCRs turn-on delay is lower than 3 ms, the SCRs gate pulse is directly set to a continuous DC pulse

according to the AC line polarity (SCR1 is set to continuous DC pulse when the AC line polarity is negative and

SCR2 is set to continuous DC pulse when the AC line polarity is positive). Below approximately a 5 ms or 4.2

ms delay (respectively for 50 and 60 Hz line frequency), the output DC capacitor is fully charged. So it is not

necessary to ensure a soft start for turn-on delays much lower than a fourth cycle. In the firmware, the SCRs

turn-on delay to switch SCRs to a continuous DC pulse is called Phase_Control_ON_Max_μs.

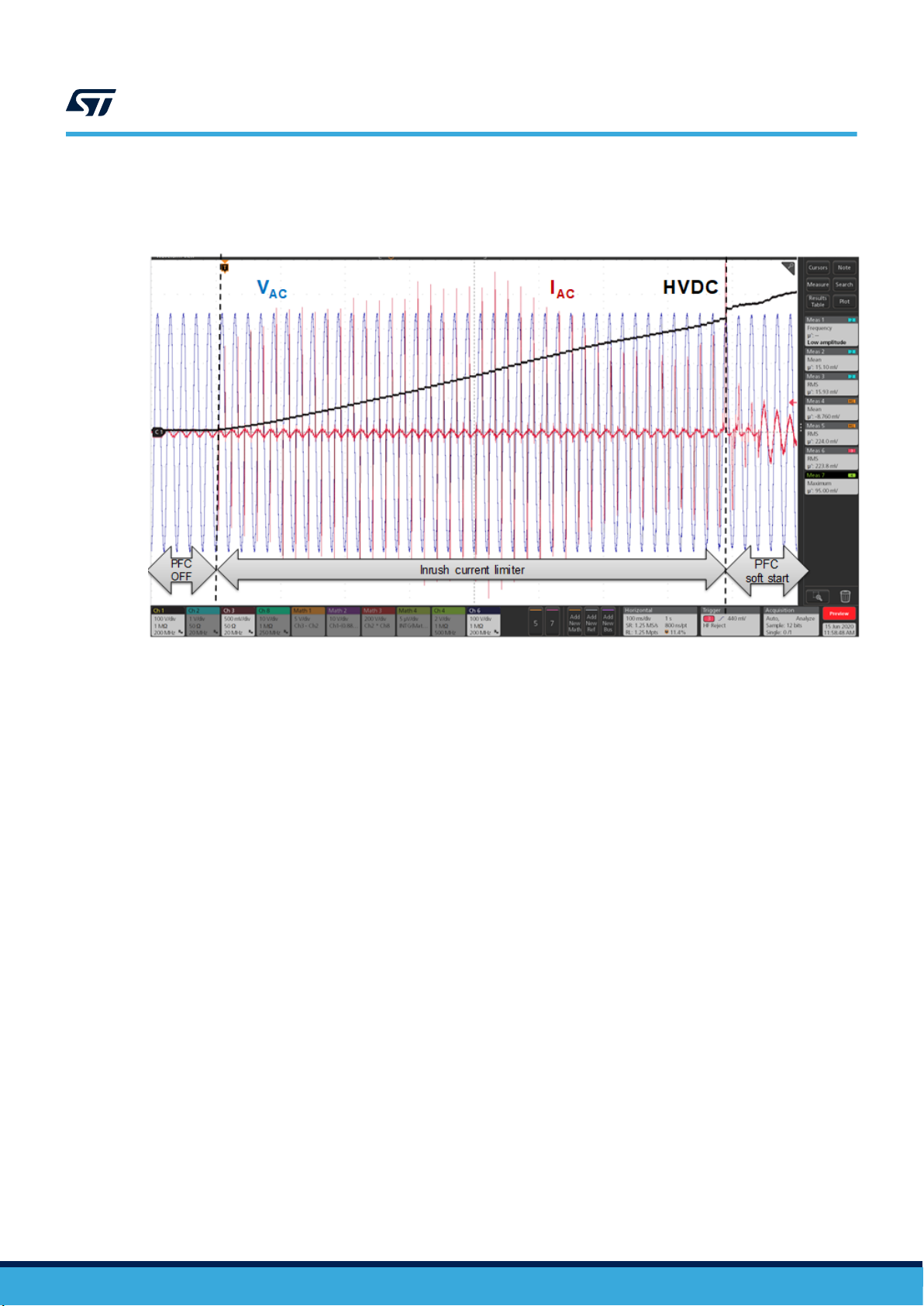

The following figure shows an example of progressive DC capacitor charge. The test has been performed at

startup when the STEVAL-DPSTPFC1 board is connected to a 230 V 50 Hz grid without an output DC load, while

the output DC capacitor is fully uncharged (i.e., its initial voltage is null). In these conditions, the maximum inrush

peak current is around 30 A and the output capacitor is charged in 1.5 s.

Figure 19. Inrush current control at board startup (with fixed SCRs on delay)

HVDC=PFC output voltage

IAC = AC line current

VAC = AC line voltage

UM2792 - Rev 1

Variable SCRs on delay

The peak current during the output capacitor charge is not constant. Only the reduction step of the SCRs turn-on

delay is constant. According to the time of the SCR turn-on, peak current can slightly vary from one period of the

AC line voltage to another. In this case, a second solution has been implemented in the firmware: by reducing

the SCRs turn-on delay defined in a look-up table, half-cycle to half-cycle, the output capacitor is progressively

charged while the line current is kept low with a constant value.

The look up table is defined according to the AC line voltage model (equivalent inductance and resistance), the

input common filter, the output DC bulk capacitor and the dynamic resistance of the SCRs and MOSFETs.

page 21/101

Page 22

Figure 20. Inrush current control at board startup (with variable SCRs on delay)

HVDC=PFC output voltage

IAC = AC line current

VAC = AC line voltage

UM2792

Inrush current control

The look-up table listing the steps of SCRs turn-on delay reduction is defined by the TAB_SCRs_Delay_us table

in the ICL_Current_Constant.h file.

Note: The look-up table has been defined without DC load connected at the output PFC.

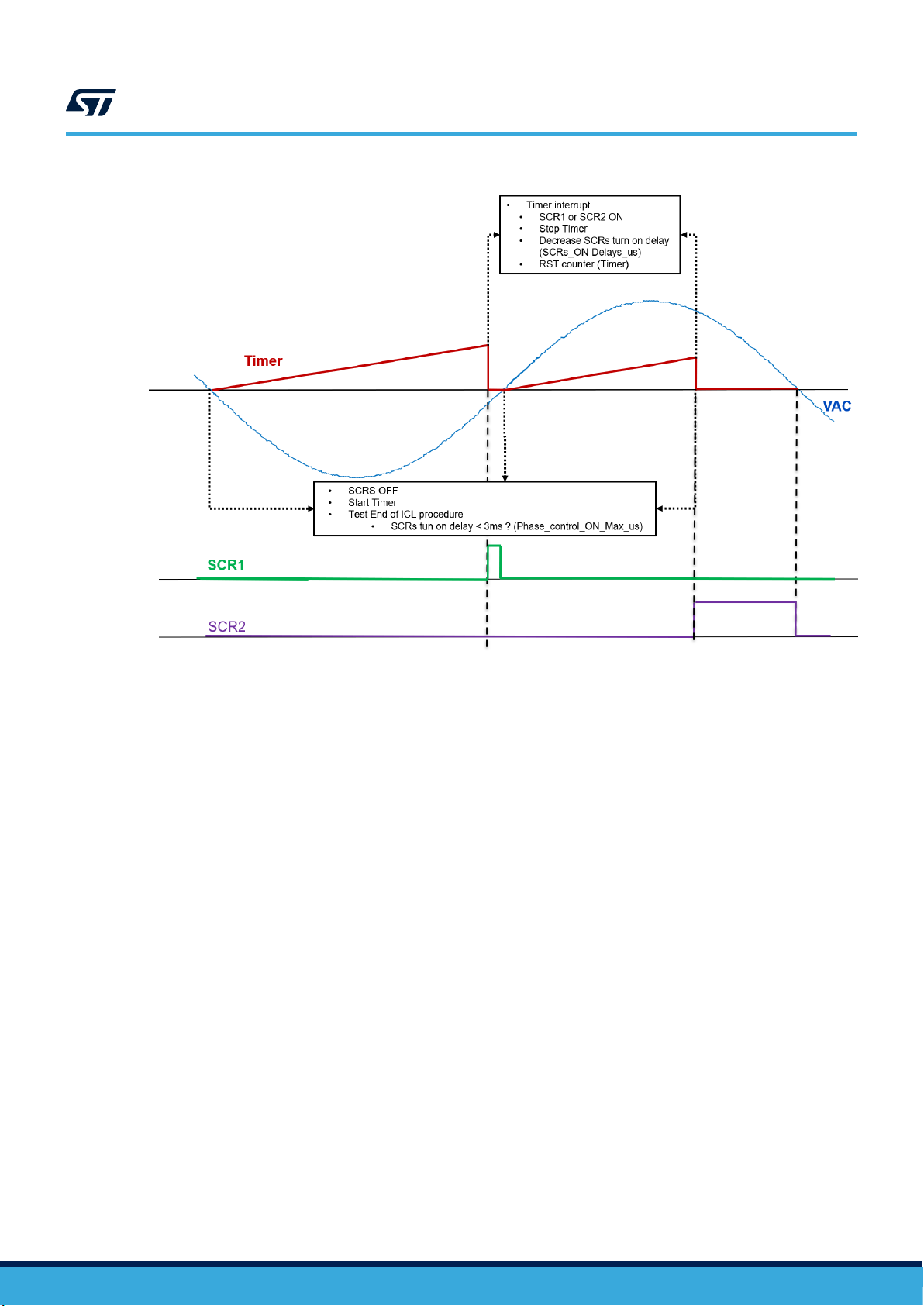

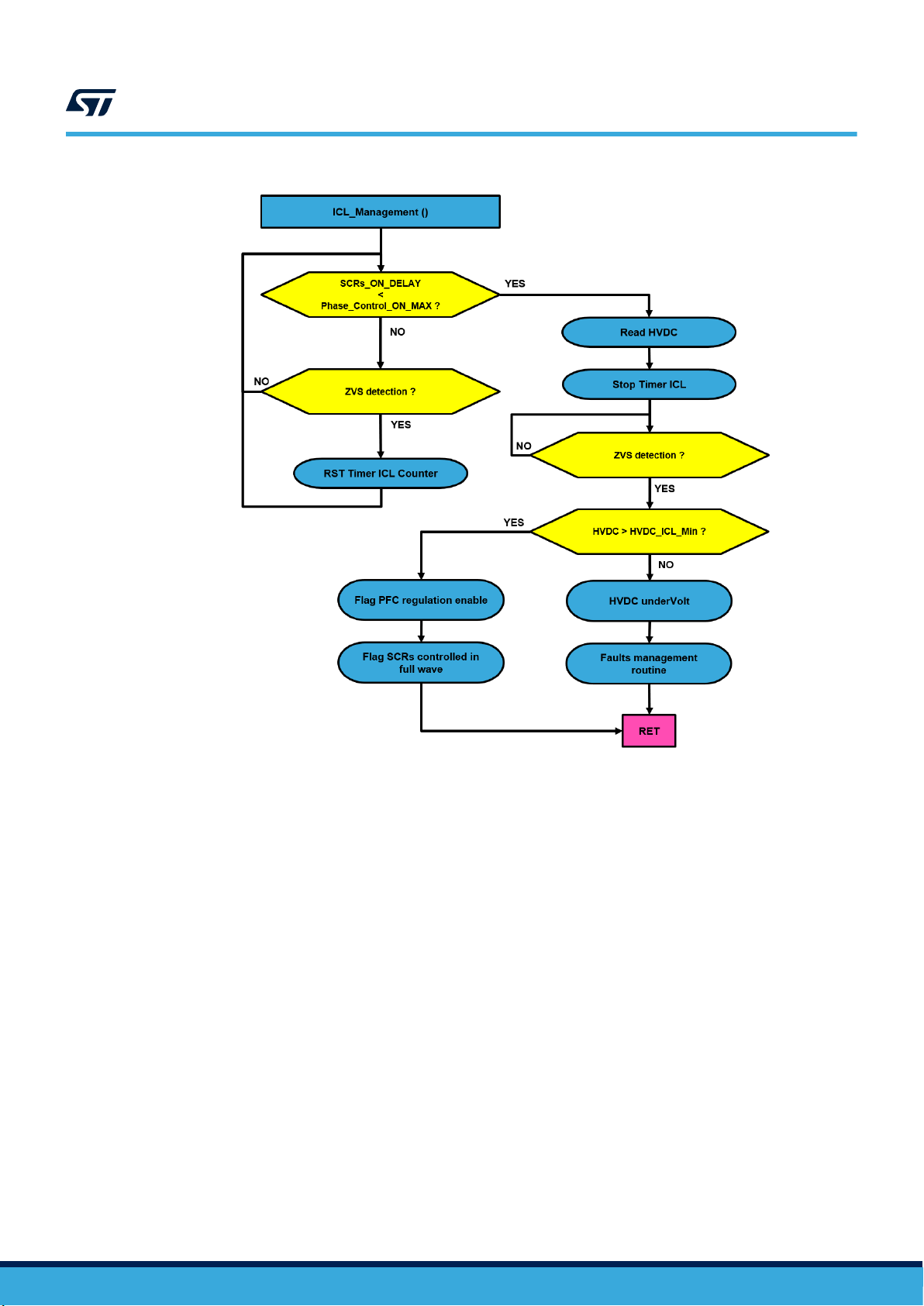

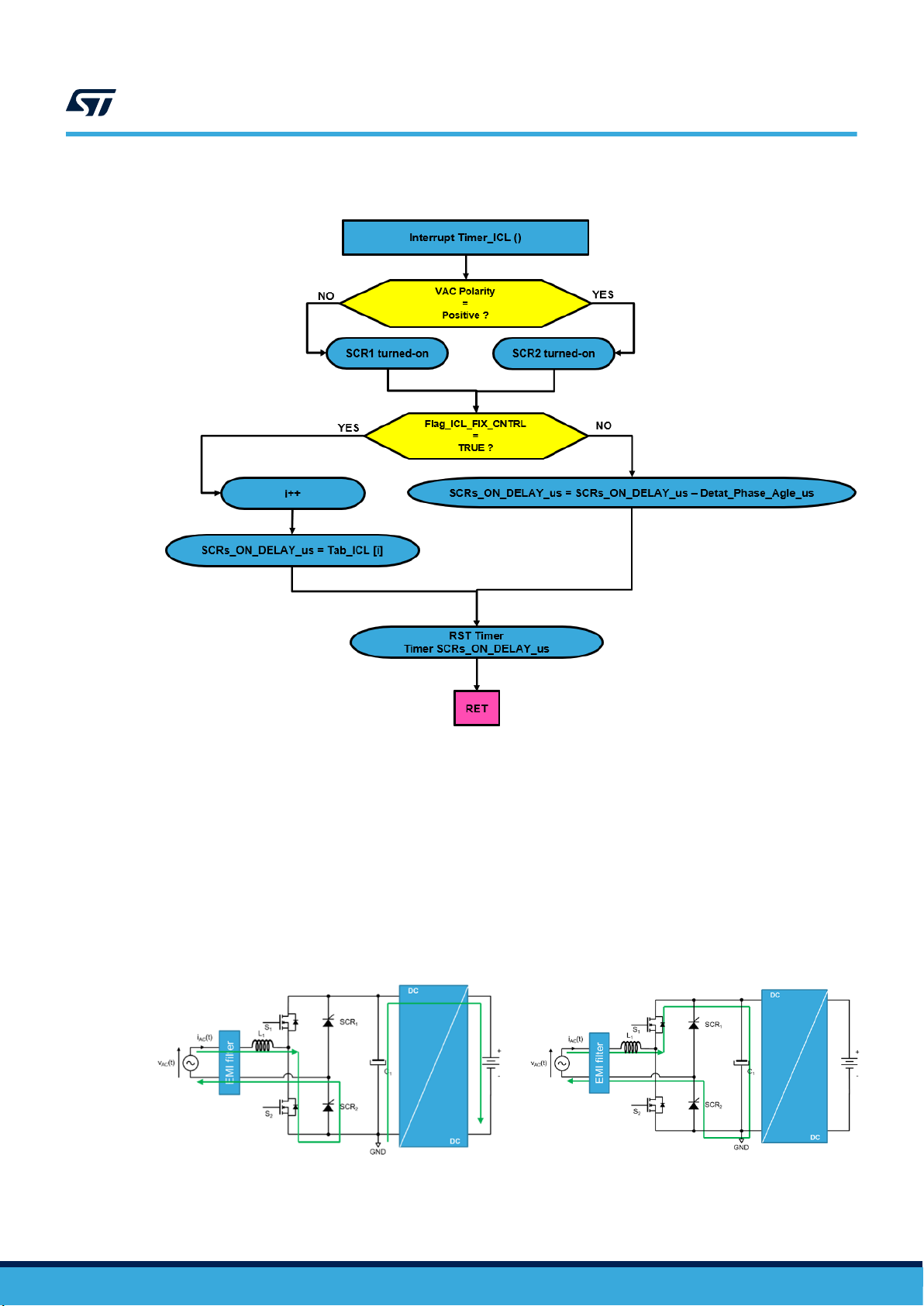

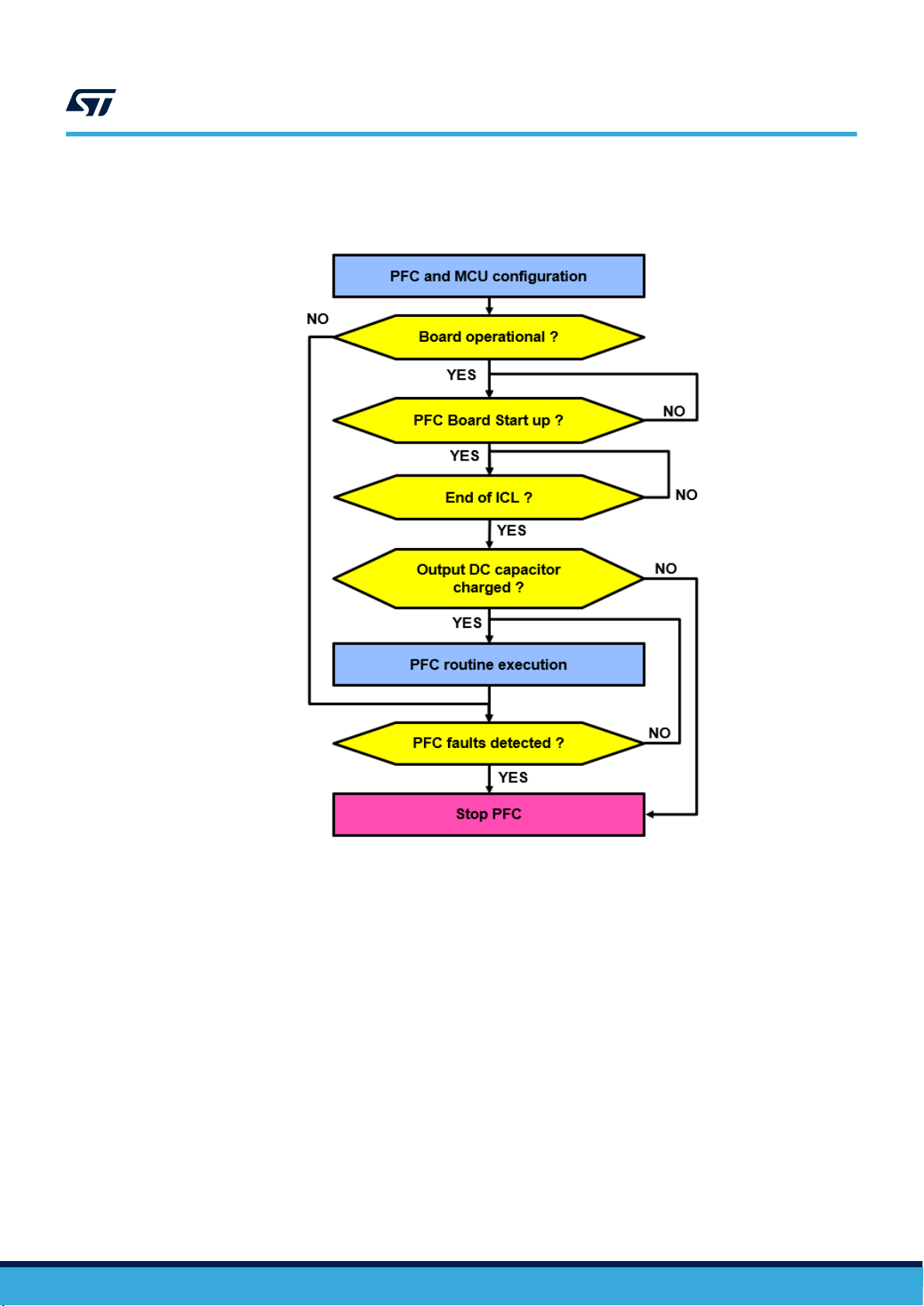

5.3.4 Inrush current control flowchart

SCRs are controlled to limit the inrush current at board startup (refer to Figure 21).

At each AC line voltage zero cross (see Figure 22. ICL flowchart (1 of 2) and Figure 23. ICL flowchart (2 of 2)):

• SCRs are switched to OFF state

• a timer is initialized to reduce SCR control turn-on delay from half-cycle to half-cycle

• test end of ICL procedure is performed:

– to check if the SCR turn-on delay is lower than 3 ms, the SCR gate pulse is directly set to a continuous

DC pulse according to the AC line polarity (SCR1 is set to continuous DC pulse when the AC line

polarity is negative and SCR2 is set to continuous DC pulse when the AC line polarity is positive). In

the firmware, the SCR turn-on delay is called Phase_Control_ON_Max_us.

– to check if the HVDC output DC voltage are charged at least 70% of the peak AC line voltage. In the

firmware, this value is called VAC_Rate_ICL_Min.

At each timer interrupt:

• SCRs are controlled according to the AC line voltage polarity

• the SCR control turn-on delay decreases

UM2792 - Rev 1

page 22/101

Page 23

Figure 21. SCR control management

UM2792

Inrush current control

UM2792 - Rev 1

page 23/101

Page 24

Figure 22. ICL flowchart (1 of 2)

UM2792

Inrush current control

UM2792 - Rev 1

page 24/101

Page 25

Figure 23. ICL flowchart (2 of 2)

UM2792

Steady state operation

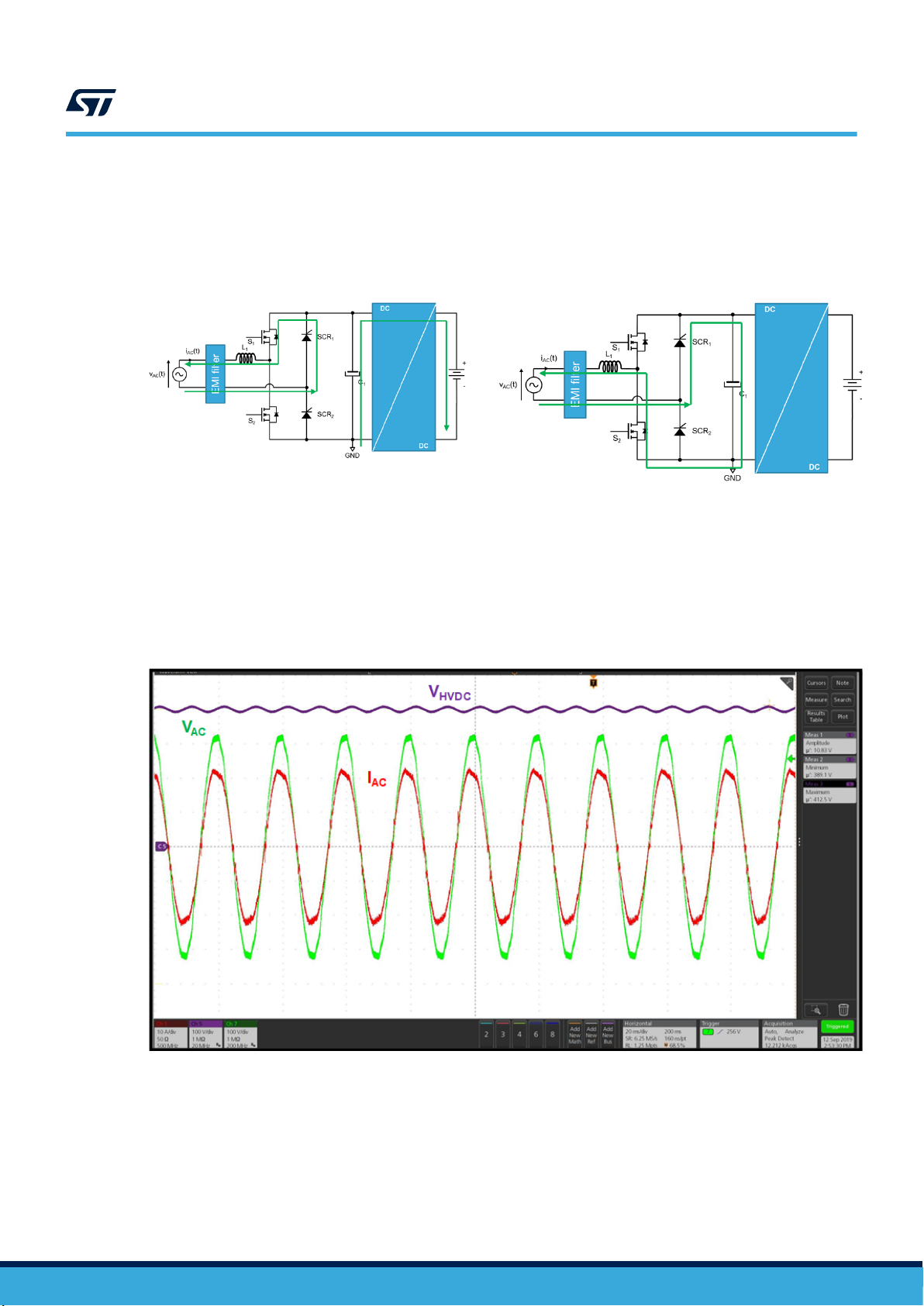

5.4 Steady state operation

The bridgeless PFC totem pole increases its efficiency by eliminating the diode bridge in the conventional PFC.

It uses two SiC MOSFETs (S1 and S2) that operate at fixed PWM frequency and two SCRs (SCR1 and SCR2)

which operate at AC line frequency.

During the positive AC line cycle, SCR2 is always ON and SCR1 is always OFF. S1 and S2 are controlled in

synchronous mode. S1 and S2, together with the input inductor L1 and the output capacitor C1, form a boost

converter topology. S2 switch increases the boost inductor current and S1 acts as freewheeling boost diode.

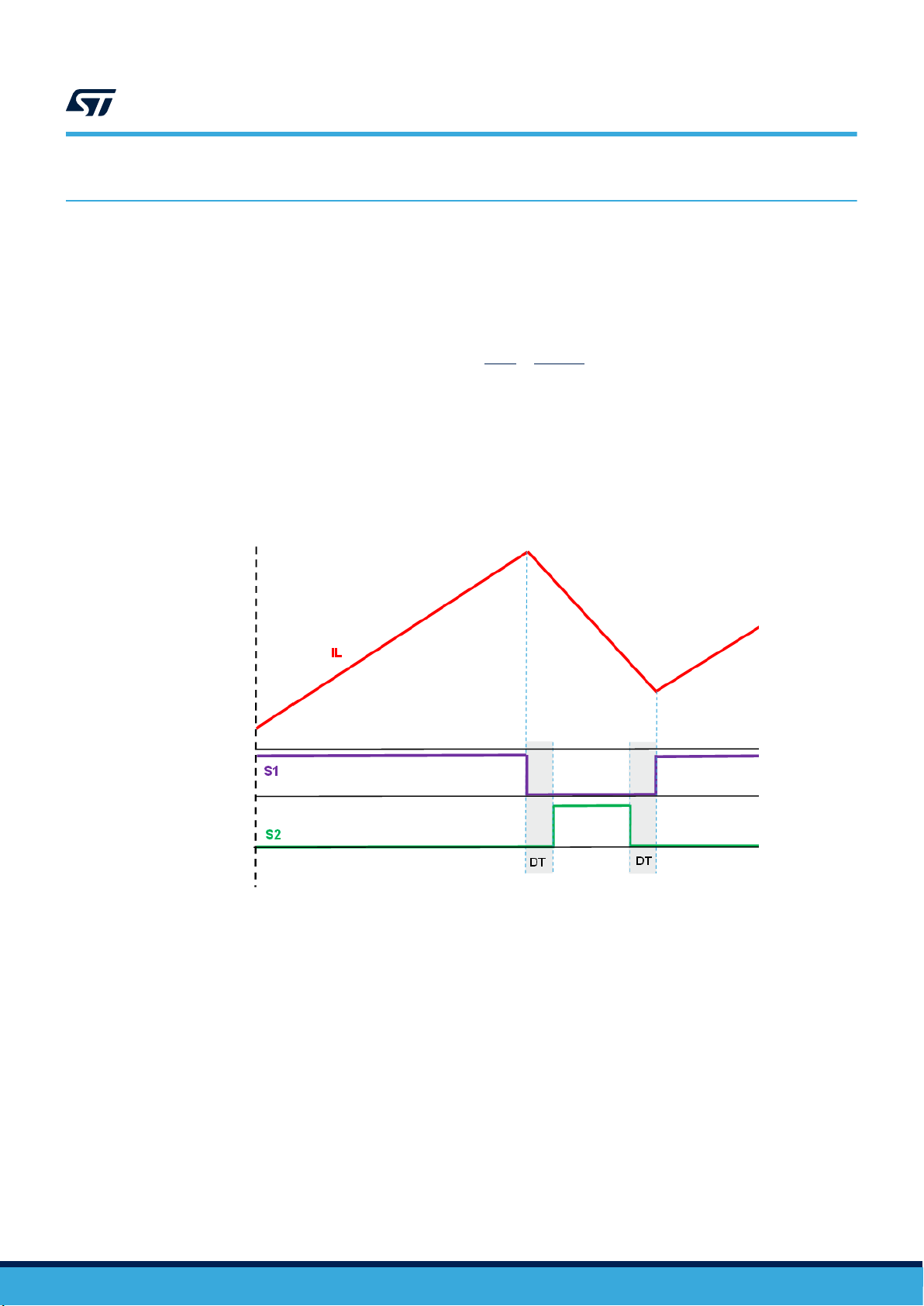

[0 ; d.TS] on the left

[d.Ts ; TS] on the right

Figure 24. Positive AC line cycle operation

UM2792 - Rev 1

page 25/101

Page 26

During the negative AC line cycle, SCR1 is always ON and SCR2 is always OFF. S1 and S2 are controlled in

synchronous mode. S1 and S2, together with the input inductor L1 and the output capacitor C1, form a boost

converter topology. S2 switch increases the boost inductor current and S1 acts as a freewheeling boost diode.

Figure 25. Negative AC line cycle operation

[0 ; d.TS] on the left

[d.Ts ; TS] on the right

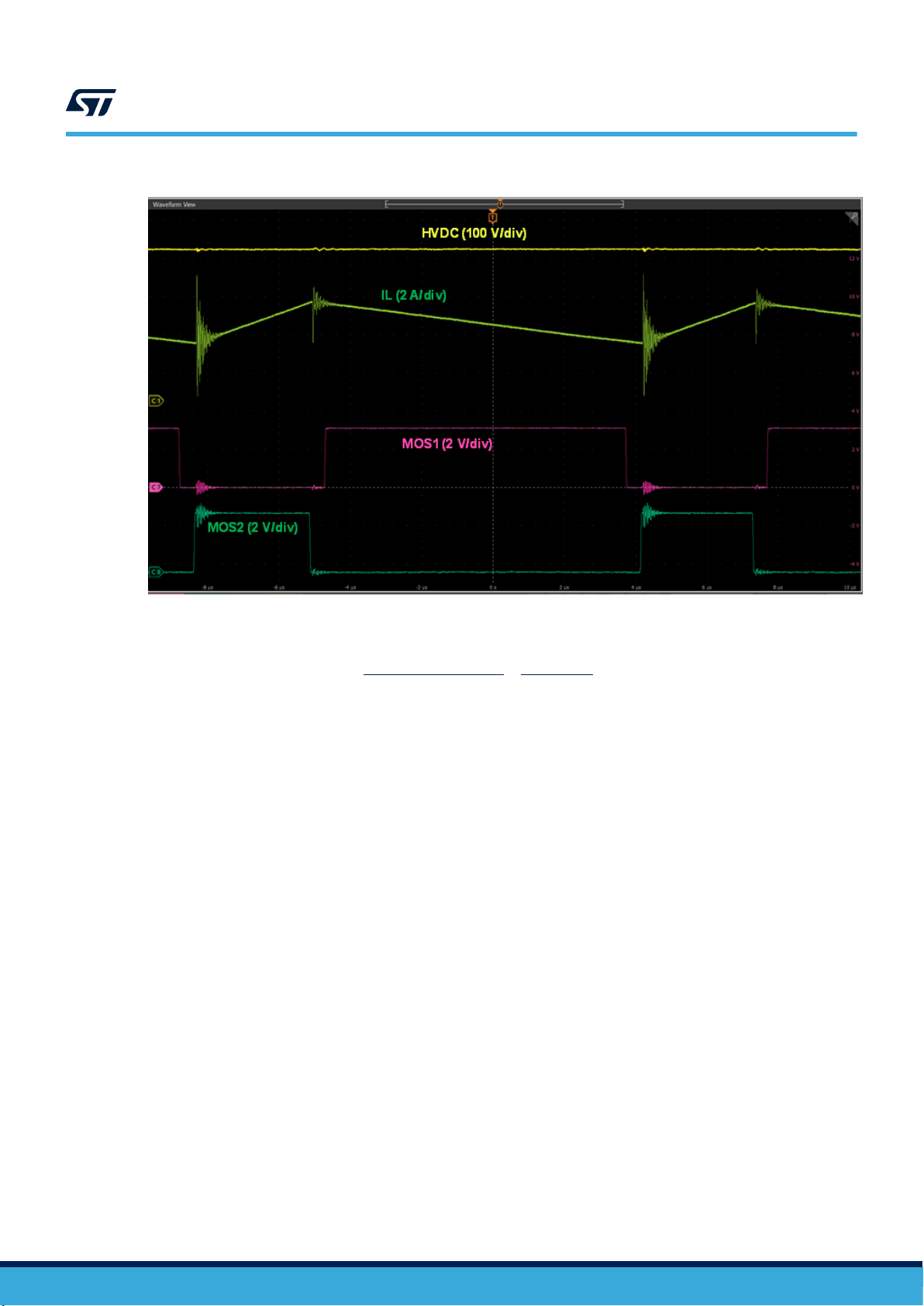

The following figure shows an example of the PFC totem pole behaviour in steady state operation with a 3.6 kW

DC load and VAC = 230 V

RMS

.

Note: Under the previous conditions, the HVDC peak to peak ripple is around 15 V.

UM2792

PFC soft start

HVDC = PFC output voltage

IAC = AC line current

VAC = AC line voltage

Figure 26. Steady state operation

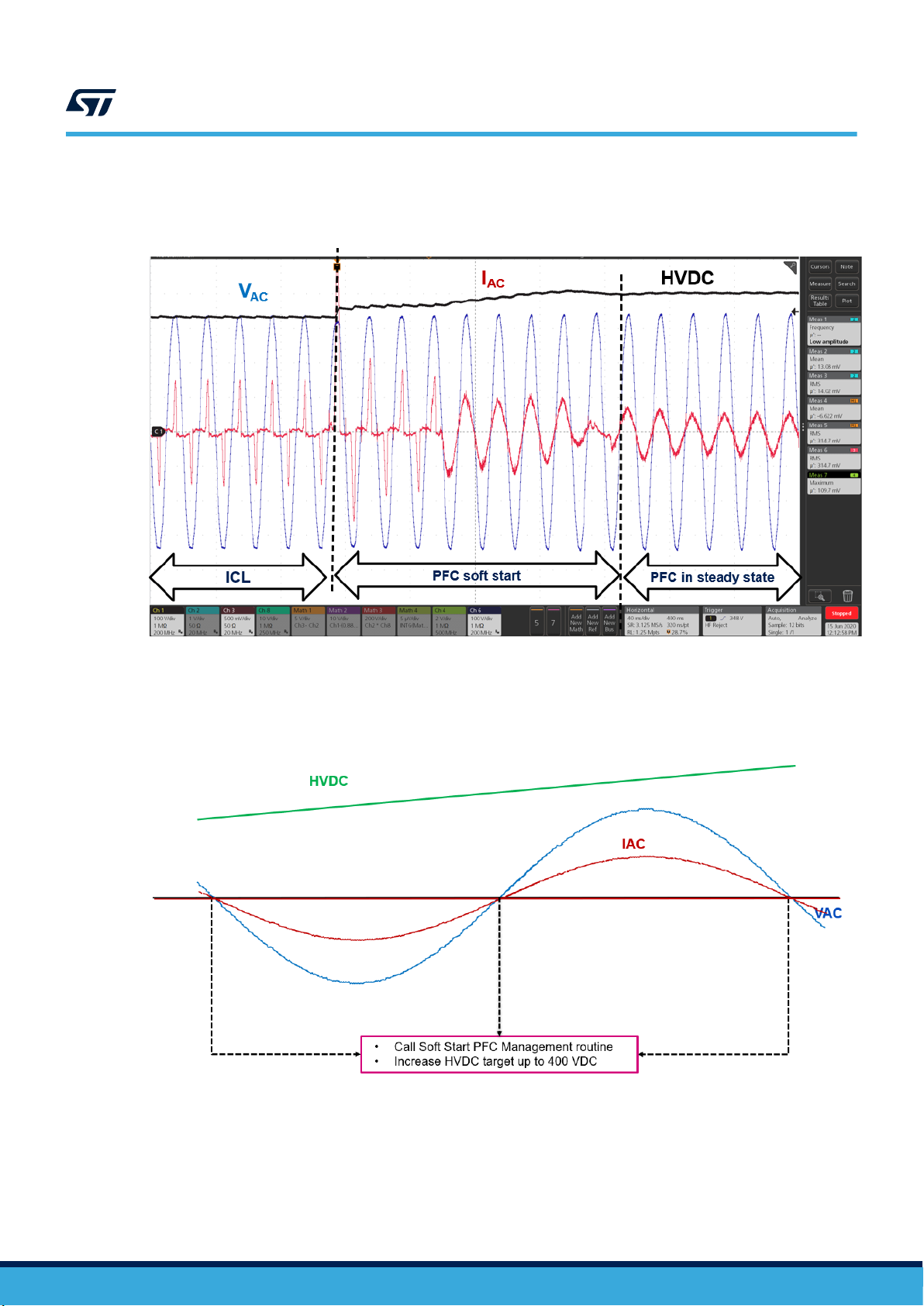

5.5

UM2792 - Rev 1

PFC soft start

After the inrush current control procedure, the internal voltage loop output increases from initial voltage under the

soft start control to reduce the current stress due to all power switches. Once HVDC has reached 400 VDC, the

soft start control is released to achieve the desired regulation.

page 26/101

Page 27

HVDC = PFC output voltage

IAC = AC line current

VAC = AC line voltage

UM2792

PFC soft start

Figure 27. PFC soft start

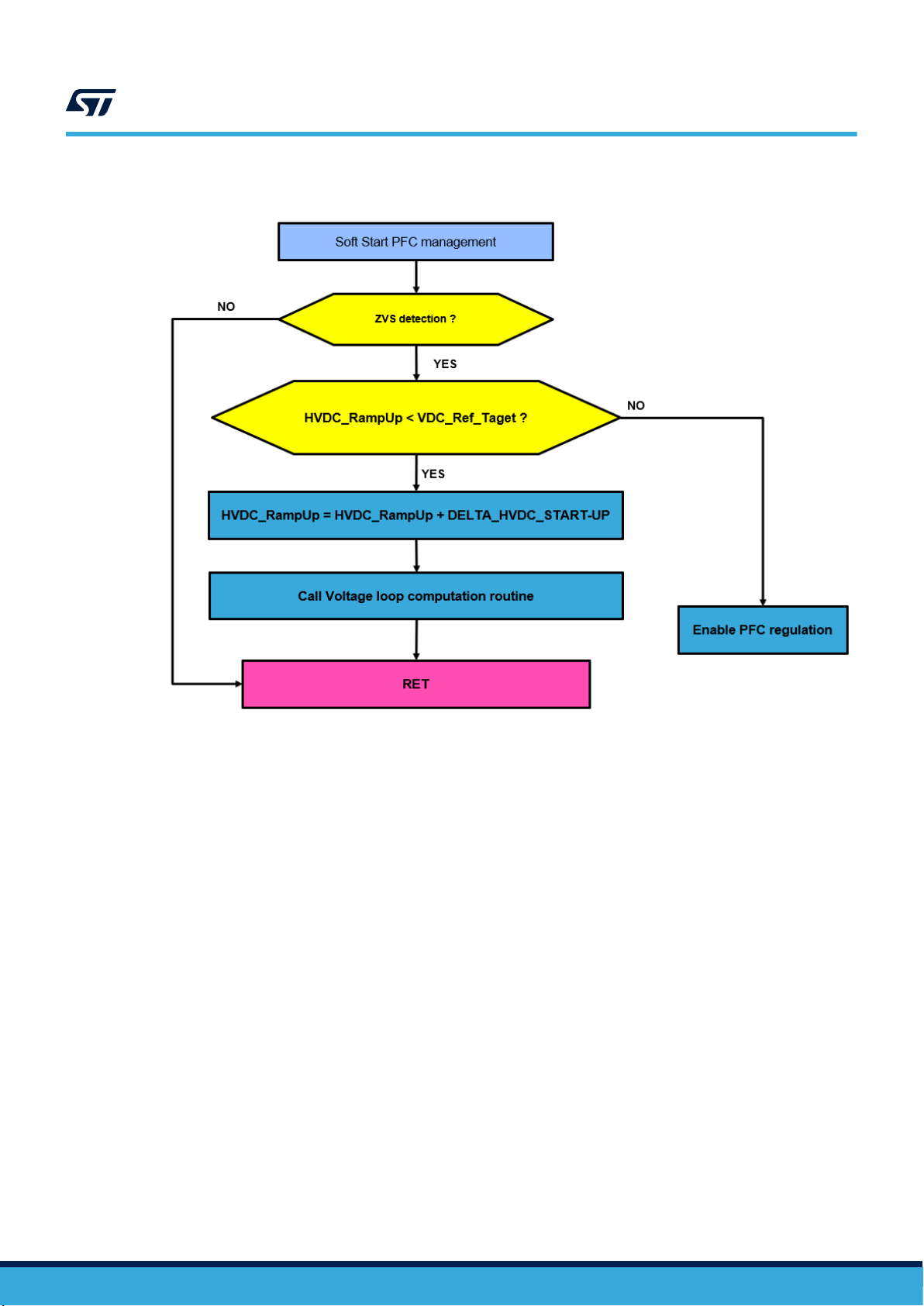

Figure 28 shows how the PFC soft start is managed after the inrush current control procedure. The soft start PFC

management routine is called at each zero cross of the AC line voltage (see Figure 29). This routine increases the

HVDC output voltage target up to 400 VDC.

Figure 28. PFC startup soft start management after inrush control procedure

UM2792 - Rev 1

page 27/101

Page 28

Figure 29. PFC startup soft start flowchart

UM2792

PFC soft start

UM2792 - Rev 1

page 28/101

Page 29

6 Switch control

6.1 SiC MOSFET control

A digital PWM signal is used to control SiC MOSFETs though STM32 timer (TIM1). Digital TIM1 counter period

is defined by Equation 2 where Fs is the PWM frequency fixed at 72 kHz and F

frequency fixed at 72 MHz.

Note: The duty cycle of the PWM control is defined by the STM32 TIM1 CCR2 register.

TIM1

Counter_Period

F

CPU

=

=

F

s

72 × 10

72 × 10

6

= 1000

3

The Duty cycle is clamped at the minimum (100 pulses) and the maximum (970 periods) of the digital TIM1 timer

counter.

To improve the PFC totem pole bridgeless efficiency, S1 and S2 SiC MOSFETS are operating in synchronous

conduction mode. Two complementary PWM signals (CH2 and CH2N) are used to control SiC MOSFETs. To

avoid the short circuits due to a slight turns ON and OFF of SiC MOSFETs, a dead time (DT) has been added

(see the following figure) with IL as the inductor current.

Figure 30. Synchronous SiC MOSFET control

CPU

UM2792

Switch control

is the STM32 oscillator

(2)

UM2792 - Rev 1

page 29/101

Page 30

Zero cross current spike control

Figure 31. Synchronous SiC MOSFET control waveform

UM2792

The digital dead time is called “DeadTime_MOSFET” in the firmware and this parameter is fixed at 20 periods of

the TIM1 Timer.

DT =

DeadTime

Fs⋅ TIM1

Counter_Period

6.2 Zero cross current spike control

An input current (IAC) spike is generated at each AC line zero cross (VAC). This issue is related to the PFC totem

pole. For example, during the negative AC line cycle, SCR1 is always on and SCR2 is always off and the PFC

output voltage (400 VDC) is applied across SCR2. S1 SiC MOSFET switch increases the boost inductor current

and S2 SiC MOSFET acts as a freewheeling boost diode. When the AC line voltage polarity is changing from

negative to positive AC line cycle, the duty cycle of the S1 SiC MOSFET changes from 100% to zero and the

active S2 SiC MOSFET change from zero to 100%. The SCR1 voltage is then applied across the boost inductor

and current spike is generated (see Figure 32 and Figure 33). The same phenomenon occurs with diodes or

MOSFETs.

MOSFET

20

=

72000 ⋅ 1000

= 278 ns

(3)

UM2792 - Rev 1

page 30/101

Page 31

Figure 32. PFC totem pole topology

LOAD

S

1

V

AC

I

AC

SCR

1

SCR

2

S

2

HVDC

UM2792

Zero cross current spike control

Figure 33. IAC current spike at each AC line voltage zero crossing

To reduce this current spike at each zero cross of the AC line voltage, S1 or S2 active switches (according to the

AC line polarity) are controlled by a small pulse width. This pulse is then gradually increased up to normal duty

cycle.

UM2792 - Rev 1

page 31/101

Page 32

Figure 34. Smart duty cycle control flowchart

DUTY_CYCLE > DUTY_CYCLE_MAX

?

RET

FLAG_DUTY_CYCLE_SOFT = TRUE ?

STEP = RESET

NO

DUTY CYCLE = DUTY_CYCLE_MIN + 100 x STEP

STEP = STEP + 1

DMA_CH1 Interrupt()

YES

DUTY CYCLE = DUTY_CYCLE_MAX

YES

NO

UM2792

Zero cross current spike control

Figure 35. Soft duty cycle control principle

duty cycle control, the control loop is frozen.

The following figures show how the AC line current spike peak is reduced thanks to this solution. During the smart

Note: At each zero cross of the AC line voltage, SCRs and SiC MOSFETs are turned off to ensure a safe permutation

of the power switches control and to avoid short-circuiting the output DC capacitor.

UM2792 - Rev 1

page 32/101

Page 33

Figure 36. Smart duty control principle

UM2792

Zero cross current spike control

Figure 37. IAC current spike at each AC line voltage zero crossing

Figure 38 defines the common mode noise without smart duty cycle control and Figure 39 defines the common

mode noise with smart duty cycle control with P

= 800 W and VAC = 240 V

OUT

/50 Hz. Thanks to a smart duty

RMS

cycle SiC MOSFET control, the common mode is widely reduced at each zero cross of the AC line voltage.

Note: For these two common mode noise measurements a snap ferrite has been connected to the AC line wires (Ref:

742 758 15 from Wurth).

UM2792 - Rev 1

page 33/101

Page 34

Zero cross current spike control

Figure 38. Common mode without smart SiC MOSFET control

UM2792

Figure 39. Common mode with smart SiC MOSFET control

UM2792 - Rev 1

page 34/101

Page 35

7 PFC totem pole design

7.1 Input inductor design

The PFC choke is designed to keep the inductor current ripple under 20% of the maximum peak input current in

CCM (16 A

duty cycle of S1 and S2 SiC MOSFETs. The minimum inductor value is defined when D = 0.5 (see Eq. (3)). HVDC

is 400 VDC output voltage and Fs is the 72 kHz frequency switching of S1 and S2 Sic MOSFETs.

To meet the previous criterion with 10% of inductance tolerance, a 337 µH inductor has been selected for this

PFC totem pole at the maximum peak input current in CCM (16 A

). Equation 4 defines the minimum inductance to operate in CCM at full load (3.6 kW). D is the

RMS

D × 1 − D × HVDC

L ≥

I

L_Ripple_ %

Figure 40. PFC estimated nominal inductance vs. current

× F

0.5 × 1 − 0.5 × 400

=

s

0.2 × 16 × 2 × 72 × 10

RMS

).

= 307μH

3

UM2792

PFC totem pole design

(4)

7.2 Output DC capacitor

The output DC capacitor is defined by the equations below according to the hold time and output voltage ripple

regulation. In this evaluation board, the hold time is set to 1 half AC line cycle (45 Hz in the worst case). HVDC is

400 VDC output voltage, the minimum normal operation output voltage is 290 V, the maximum input power is 3.6

kW and the output voltage ripple is set to 5%.

C

≥

OUT

C

To meet the previous criteria with 20% of capacitor tolerance, 3 x 680 µF/450 VDC electrolytic capacitors are

connected in parallel.

UM2792 - Rev 1

P

2 × π × f × HVDC × HVDC

≥

OUT

OUT

2 × P

HVDC2− HVDC

OUT

× t

ℎold

min

Ripple

2

=

2 × π × 45 × 400 × 20

2 × 3600 ×

=

4002− 290

3600

1

2 × 45

2

= 1.59mF (5)

= 1.05mF

(6)

page 35/101

Page 36

7.3 Analog signal sensing

2

Vcc-

3

In-

R17

A_GND

470k

68nF

470k

A_GND

C14

R18

U2

R22

470k

K

2

3V3_A

MCP6231UT-E/OT

A_GND

470k

R23

R24

5

10k

U1

100nF 4.7uF

L1

470k

C20

NC

1

In+

R21

COM

3

470k

VAC_SENSE

C9

Vcc+

Out

4

C8

C12

NC

N1

C15

3.9nF

R27

R29

470k

R35

5k

470k

A_GND

A

1

R16

470k

R31

R28

3V3_A

A_GND

68nF

10k

7.3.1 AC line voltage (VAC) measurement

The AC line voltage (VAC) measurement is mainly used to:

• control the inrush current at board startup

• shape the IAC line current to the AC line voltage in PFC steady state operation

• detect the zero cross of the AC line voltage

• manage the AC line dips

A differential measurement is performed to measure VAC based on the line voltage (VL) and the neutral voltage

(VN) measurements (VAC = VL - VN). To sense VL and VN, a resistor divider bridge is used. The typical voltage

sensor is 3.545 mV/VAC.

Figure 41. AC line voltage measurement

UM2792

Analog signal sensing

7.3.2 AC line current (IAC) measurement

The PFC choke inductor current is measured to shape the AC line current to the AC line voltage. A CASR

15-NP current transducer is used in series with the PFC choke as shown in the figure below. The typical current

transducer is 41.6 mV/IAC.

As the AC line current is an alternative signal, an offset is needed to be read by the MCU. The current transducer

sensor is supplied with 5 VDC. R3 resistor (1.3 kOhms) is connected to the VREF pin of the current transducer

UM2792 - Rev 1

sensor to set the offset to 1.64 VDC.

page 36/101

Page 37

Figure 42. PFC choke inductor current sensor

150pF

A_GND

+

-

10k

10k

40k

10

9

OUT2

C31

1.3k

8

A_GND

40k

12

GND

150pF

R43

IAC_OFFSET

4.7uF

R41

NC

IN1

1

C44

OUT3

IM2

150pF

IN3

3

13

VC

14

5V_A

IAC_SENSE

A_GND

C38

VREF

11

U28

C29

C46

680INT_REF

LEM CASR 15-NP

2

IN2

OUT1

100nF

VOUT

Rm

R59

160k

C59

A_GND

U4

3V3_DC

160k

3k

K

2

GND_DC

160k

10nF

GND_DC

R54

A

1

HVDC

C60

NC

NC

NC

R50

C33

3

COM

R51

UM2792

Analog signal sensing

7.3.3 Output PFC HVDC measurement

A resistor divider circuit is used to measure the output PFC voltage (HVDC). As the MCU ADC input port is a high

resistance, an amplifier is not needed. The typical voltage sensor is 6.2 mV/HVDC.

UM2792 - Rev 1

Figure 43. HVDC output measurement

page 37/101

Page 38

7.3.4 Signal sense filter

Q2

5V_SCR1

R45

1k

C58

R44

1

GND_SCR1

390R

R55

2

270R

270R

R47

2N2907A

R52

R58

GND_SCR1

C52

4 1

10nF

G_SCR2

10nF

3

U6

R56

2N2907A

390R

GND_DC

100R

R46

R48

C53

LTV-817

5V_SCR2

C51

3

Q3

10nF

R53

1k

R57

G_SCR1

GND_DC

10nF

4

390R

SCR1

LTV-817

R49

GND_SCR2

U7

C57

100R

GND_SCR2

2

SCR2

100nF

47R

100nF

390R

C56

An RC filter is used to filter all analog signals (VAC, IAC, HVDC, TEMP).

7.4 Power circuit driver

7.4.1 SCR control circuit

The VIPER26LD flyback provides two insulated DC output voltage to control SCR1 and SCR2. Insulated positive

power supplies are required to supply current to SCR gates. As the MCU is not at the same ground reference as

SCRs, optocouplers are needed as shown in the figure below.

To improve the circuit control immunity filters have been added:

• an RC filter connected between the base and the emitter of the PNP transistors (Q2 and Q3)

• R45/R53 = 1 kΩ

• C52/C57 = 10 nF

• capacitors (C53 and C58) associated with R46/R47 and R55/R56 resistors improve the immunity of the

optocouplers (U6 and U7)

UM2792

Power circuit driver

Figure 44. SCR insulated control

UM2792 - Rev 1

To define the resistor value of the SCR control circuit, the block of equations below define the new resistor

definition according to the previous figure.

RGK= R44= R

Rg= R49= R

RF1= R45= R

RF2= R47= R

RF3= R46= R

RL= R48= R

CF1= C52= C

CF2= C53= C

52

58

53

56

55

57

57

58

Knowing the SCR gate current (IGT), the gate resistor RGK to limit the SCR gate current can be defined according

to the equation below, where 5VSCR is the power supply to provide the gate current to the SCRs, VCE_SAT

is the transistor collector/emitter of the PNP transistors (Q2 and Q3), VGT is the SCR gate triggering voltage and

RGK is the gate cathode resistor used to increase the SCR immunity.

PNP

page 38/101

(7)

(8)

(9)

(10)

(11)

(12)

(13)

(14)

Page 39

UM2792

Power circuit driver

5V

Rg<

SCR

IGT

SAT_PNP

SCR

− VCE

The collector resistors (RF2 and RF3) of the optocoupler are defined by the equation below, where RF1 is

the PNP transistor resistor filter, VCC_AC is the power supply to provide the gate current to the AC switch,

VCE_SAT

is the transistor collector/emitter of the optocoupler, β is the PNP transistor gain and VBE_SAT

Opto

is the PNP transistor base/emitter.

RF2+ RF3=

5V

SCR

SCR

− VCE

SAT_OPTO

SAT_NPN

β ⋅ R

G

5V

− VCE

Knowing the optocoupler CTR, RF2 and RF3 resistors value, the LED resistor RL of the optocoupler is defined

by the equation below, where 5VSCR is the power supply to provide the gate current to the AC switch,

VCE_SAT

is the transistor collector/emitter of the optocoupler, VBE_SAT

Opto

emitter and VOH_Min_MCU is the output MCU voltage to drive the optocoupler.

RL=

1

CTR

VOH_Min_MCU − VF

VCC_AC − VCE_SAT

×

With LTV-817 optocoupler and 2N2907 PNP transistor, you have to choose the following resistor values.

RGK= R44= R52= 1kΩ (18)

Rg= R49= R58= 47kΩ (19)

RF1= R45= R53= 1kΩ (20)

RF2= R47= R56= 390kΩ (21)

RF3= R46= R55= 390kΩ (22)

RL= R48= R57= 1kΩ (23)

CF1= C52= C57= 10nF (24)

CF2= C53= C58= 10nF (25)

VGT

+

R

− VGT_SCR

Opto

RF2+ R

− VGT

SCR

GK

− VBE

Opto

− VBE_SAT

F3

SCR

SAT_PNP

VBE

+

SAT_PNP

R

F1

is the PNP transistor base/

PNP

PNP

(15)

PNP

(16)

(17)

7.4.2 SiC MOSFET control circuit

The STGAP2S driver is designed to drive ST SiC MOSFET providing high peak current during turn-on and turn-off

and to minimize the switching losses for better system efficiency and EMI.

SiC MOSFET switches have different requirements for gate turn-on and turn-off voltage levels. The turn-on

voltage level is performed with +20 VDC and the turn-off is operated with -3.3 VDC to ensure the gate source safe

operating area.

UM2792 - Rev 1

page 39/101

Page 40

Figure 45. STGAP2S driver

24R

1nF

C41

8

100nF

U3

100nF

C21

C42

1uF

C22

GND_S2

VH

5

GND_DC

100nF

D3

NC

4.7uF

C24

GON

6

C39

2

IN+

STGAP2SM

L16

2A

150pF

C40

R42

NC

2

D6

NC

GON

6

GND_S2

24R

R40

8

1nF

GND_S2

150pF

C19

C30

R34

L15

D4

1

VDD

MOS1

3V3_DC

3

IN-

C18

C35

C26

2.2nF

3V3_DC

-3V_S2

R38

10k

1uF

NC

C36

100nF

G_MOS1

3

IN-

GND_S1

10k

24R

510R

G_MOS2

4.7uF

R39

GND_ISO

2.2nF

C28

4

GND

MOS2

C43

R32

VH

5

C27

1uF

150pF

GND_S1

-

20V_S1

C23

GND_ISO

7

GOFF

20V_S2

C25

U5

D5

150pF

R36

C45

VDD

1

GND_DC

GND_S1

2A

7

GOFF

C34

R33

1uF

1uF

1uF

IN+

STGAP2SM

4

GND

24R

510R

3V_S1

+VIN

10nF

C118

C107

GND_DC

C120

60R

C105

33uF/25V

33uF/25V

D18

C117

C104

2

39 mH

2A

R94

U15

100nF

20V_S2

R90

+

C126

-VIN

6

-Vout

0V

R89

2

+VIN

7

MGJ2D122005SC

20V_S1

DZ2W03300L

10nF

C114

C125

C119

+

L9

C102

+

C116

-3V_S2

1

1

60R

12V_DC

60R

L12

C103

C101 33uF/25V

-3V_S1

C115

5

100nF

39 mH

100nF10nF

D19

60R

+

5

2A

R95

MGJ2D122005SC

100nF

GND_S1

60R

C113

22uF/25V

DZ2W03300L

L13

C106

L7

GND_DC

+Vout

U16

60R

33uF/25V

R87

10nF

R93

22uF/25V

60R

100nF

100nF

7

R88

+Vout

6

C112

-VIN

-Vout

0V

100nF

R96

60R

100nF

UM2792

Power circuit driver

UM2792 - Rev 1

The asymmetric SiC MOSFET gate voltages (+20 VDC/-3.3 VDC) are achieved thanks to a high insulated DC-DC

converter (MGJ2 series from MURATA) to power the high side and the low side gate drive circuits for SiC

MOSFETs.

Figure 46. STGAP2S driver - DC-DC converter

page 40/101

Page 41

8 PFC protections

OFFSET

IL

t

OVP_H

OVP_L

8.1 Analogue overcurrent protection

Two comparators are used to detect the positive and negative PFC choke inductor overcurrent. This I

overcurrent detection is achieved thanks to STM32 comparators (COMP2 and COMP4) and STM32 digital analog

converters (DAC CH1 and DAC CH2).

Figure 47. STM32 comparator configuration

UM2792

PFC protections

AC

Figure 48. Positive and negative overcurrent detection

UM2792 - Rev 1

page 41/101

Page 42

An interrupt is generated by COMP2 or COMP4 peripherals if the PFC inductor current image is higher than

OVP_H limit or lower than lower OVP_L limit, respectively. Upper limit (OVP_H) and lower limit (OVP_L) are

defined by the STM32 digital analog converter peripherals (DAC CH1 and DAC CH2). The equations below define

the digital upper and lower limit with IAC_OFFSET the digital value (2070) of the IAC current sensor offset value.

The PFC totem pole turns off if the maximum PFC choke inductor current is higher than 25 A peak.

DAC

DAC

CH1

CH2

n

2

=

× I

ref

2

ref

L_MAX

n

× I

L_MAX

V

=

V

ΔI

L

+

× K

2

ΔI

L

+

× K

2

8.2 Digital PFC choke inductor current clamping

The PFC totem pole has been designed to limit the AC line current at 16 A

current is clamped to 16 A

performed by clamping the peak current reference in the firmware. The PFC totem pole board switches off if the

HVDC voltage is lower than the peak AC line voltage measured at board startup.

, if the output DC current (IDC) increases, the HVDC voltage decreases. This is

RMS

Figure 49. Over input current protection

i_sense

i_sense

UM2792

Digital PFC choke inductor current clamping

+ I

AC_OFFSET

− I

AC_OFFSET

(IAC). In this case, as the input

RMS

(26)

(27)

UM2792 - Rev 1

page 42/101

Page 43

Figure 50. IAC inductor current clamp

390 Vdc

MOSFETs ON

400 Vdc

HVDC

Load variation

420 Vdc

450 Vdc

MOSFETs OFF

MOSFETs ON

UM2792

HVDC overvoltage protection

8.3 HVDC overvoltage protection

HVDC output overvoltage might occur with a DC load variation from high to light load. SiC MOSFETs are switched

off if the HVDC output voltage is higher than 420 VDC and switched on again if the HVDC output voltage is lower

than 390 VDC at the zero cross of the AC line voltage.

Figure 51. Overvoltage protection

8.4 Overtemperature protection

The PFC totem pole temperature protection is made with a TO-220 temperature sensor mounted on the heatsink

and connected to an MCU GPIO. If overtemperature is detected by the MCU, the PFC totem pole turns off.

UM2792 - Rev 1

page 43/101

Page 44

9 Control loop design

9.1 Timing diagram

The AC line voltage (VAC), the PFC chock current (IL) and HVDC output voltage are sampled at the center of the

PWM signal used to control SiC MOSFET switches. The inner current loop computation is executed at 72 kHz to

get the desired switching signal and configured accordingly. The outer voltage loop computation is executed at

each AC line zero crossing.

UM2792

Control loop design

Figure 52. Timing diagram

9.2

UM2792 - Rev 1

Digital power factor correction (DPFC)

The figure below shows the PFC totem pole regulation principle using a digital control implemented in the STM32

microcontroller:

• the outer voltage loop regulates the totem pole HVDC output voltage

• the current loop is the faster loop and is used to shape the current inductor to the sinusoidal reference

(I

)

L_REF

• PLL is used to synchronize the PFC to the AC line cycle

page 44/101

Page 45

Figure 53. Digital PFC control diagram

Ci(s)

KcADC

I

Hi(s) =

L_MES

-

+

d

DPWM

L

I

L_REF

i

d(s)

L

(s)

UM2792

Current loop control design

9.3 Current loop control design

9.3.1 Current loop model

The figure below shows the current loop small signal model block diagram. The current loop controller keeps the

error between the reference and the current inductor at zero.

Ci(s) = current loop controller

Hi(s) = current transfer function duty cycle

DPWM = digital PWM gain

ADC = ADC transfer function

kc = current sensor transfer function to measure PFC choke inductor current

IL_REF = current reference signal

Figure 54. Current loop diagram

UM2792 - Rev 1

The controller output is fed by the DPWM block to control SiC MOSFET. The duty cycle adapts the inductor

current to be in phase with the reference signal (I

The full transfer function of open current loop is defined by the following equation

Tis = Cis × His × ADC × DPWM × K

The PFC duty cycle of current transfer function is defined by

L_REF

).

c

page 45/101

(28)

Page 46

UM2792

Current loop control design

R ⋅ C

His =

ILs

d s

2 ⋅ HVDC

=

R ⋅ 1 − d

⋅

2

1 +

E

R ⋅ 1 − d

1 +

L

In high frequency:

ILs

His =

d s

=

HVDC

L ⋅ s

with

2

HVDC

R =

POUT

and duty cycle equilibrium point:

dE= 1 −

VAC

HVDC

where:

• POUT: PFC output power

• L: PFC boost inductance

• C : DC output capacitor

• VAC: Input AC line voltage

• HVDC : DC output voltage

The current loop controller Ci(s) is defined by the following equation with Kp_i and Ki_i PI controller analog

coefficients

Cis = K

p_i

K

i_i

+

= K

s

p_i

1 + τi× s

×

with

K

p_i

τi=

K

i_i

The current sensor sensitive coefficient is defined by

Kc= 0.0416

The ADC STM32 transfer function is defined by

n

12

2

ADC =

V

ref

2

=

= 1241

3.3

The Digital PWM gain based on 72 MHz timer resolution and a 72 kHz switching frequency (Fs_i) is defined by

DPWM =

F

s_i

F

CLK_MCU

=

72 × 10

72 × 10

3

6

2

⋅ s +

2

E

τi× s

= 1 × 10

⋅ s

1 − d

−3

L ⋅ C

2

⋅ s

2

E

(29)

(30)

(31)

(32)

(33)

(34)

(35)

(36)

(37)

9.3.2 Controller design

A good current loop performance needs the crossover frequency F

switching frequency. To ensure the stability of the loop, two criteria must be verified with PMi as phase margin.

According to the previous equations, τi, Kp_i and Ki_i analog coefficients are defined by

In bilinear transformation, the formula below is used

UM2792 - Rev 1

20 × log Tis = 1 (38)

arg Tis = + 180 + PM

tan PM

τi=

2 × π × F

K

=

p_i

HVDC × ADC × DPWM × Kc× 1 + τi× 2 × π × F

L × τi× 2 × π × F

K

i_i

s =

T

i

c_i

K

p_i

=

τ

i

2

z − 1

×

z + 1

s

to be around 15 time lower than the

C_i

i

2

c_i

c_i

2

(39)

(40)

(41)

(42)

(43)

page 46/101

Page 47

UM2792

Feedforward design

The current loop controller Ci(z) is defined by

K

⋅ T

p_i

s_i

− K

2 ⋅ τ

Ciz =

i

where

K

τi=

According to the previous equations Kpz_i and Kiz_i are defined by

K

= K

iz_i

−

p_i

=

2 × τi× F

pz_i

K

Note: The current loop is executed at the MOSFETs switching frequency and fixed at 72 kHz. Ts_i and Fs_i are

repectively the MOSFETs switching period and the MOSFETs switching frequency.

To thoroughly use MCU resources, the PI corrector coefficients are normalized to fixed-point decimal format (Q15

data format). The relation between the actual and normalized values is defined by

K

pz_i_Q15

K

iz_i_Q15

= K

= K

To optimize the HVDC regulation, the PI current loop coefficient has been defined according to the AC line

voltage.

The table below defines the controller coefficient to be set in the MCU. In the firmware:

• the integral gain is defined by “PI_IAC_KI_230” and “PI_IAC_KI_110” according to the AC line voltage range

• the proportional gain is defined by “PI_IAC_KP_230” and “PI_IAC_KP_110” according to the AC line voltage

range

K

⋅ T

p_i

2 × τ

s_i

i

s_i

⋅ z

+

p_i

−1 + z

p_i

K

i_i

K

p_i

2 × τi× F

K

p_i

s_i

× 8192 (48)

pz_i

× 8192 (49)

iz_i

(44)

(45)

(46)

(47)

Table 10. Integral and proportional gains of the current loop PI controller

Parameter

Kpz_i_Q15 3400 3400

Kiz_i_Q15 40 260

9.4 Feedforward design

When the main voltage or load current changes suddenly, the low bandwidth of the voltage loop may cause

output voltage fluctuations. To alleviate the feedback controller, a digital feedforward control (DFF) has been

included in the current loop to pre-calculate a duty ratio as defined by the equation below where HVDC is the PFC

output voltage and VAC the AC is the line voltage.

The feedforward duty ratio is added to the average current mode control output to generate the final duty ratio.

The regular current loop compensator changes the duty ratio around this calculated duty ratio pattern.

VAC = 110 V

P

OUT_MAX

dFF=

RMS

= 1.8 kW

HVDC − VAC

HVDC

VAC = 230 V

P

OUT_MAX

RMS

= 3.6 kW

(50)

UM2792 - Rev 1

page 47/101

Page 48

10 Voltage loop control design

10.1 Voltage loop model

The figure below shows the small signal model block diagram.

Figure 55. Voltage loop diagram

Cv(s) = voltage loop controller

Hv(s) = inductor current to output voltage transfer function

ADC = ADC transfer function

kv= inductor current transfer function

UM2792

Voltage loop control design

The full transfer function of open voltage loop is defined by

Tvs = Hvs × Cvs × ADC × K

v

The output voltage transfer function is defined by

Hvs =

VAC⋅ R

2 ⋅ HVDC ⋅ Kc⋅ ADC

1

×

R ⋅ C

1 +

⋅ s

2

with

2

HVDC

R =

POUT

where:

• POUT: PFC output power

• C : The DC output capacitor

• VAC: Input AC line voltage

• HVDC : DC output voltage

• Kc = 0.0416 (current sensor sensitive coefficient)

The voltage loop controller Cv(s) is defined by with Kp_v and Ki_v PI controller analog coefficients

Cvs = K

p_v

K

i_v

+

= K

s

p_v

1 + τv× s

×

τv× s

with

K

p_v

τi=

K

i_v

The output voltage sense gain is defined by

R

Kv=

2

R1+ R

= 0.0062

2

The ADC STM32 transfer function is defined by

n

12

2

ADC =

V

ref

2

=

= 1241

3.3

(51)

(52)

(53)

(54)

(55)

(56)

(57)

UM2792 - Rev 1

page 48/101

Page 49

UM2792

Controller design

The equivalent resistor on the PFC output with HVDC, the PFC output voltage and P

power are defined by

10.2 Controller design

A good current loop performance needs the crossover frequency F

switching frequency. To ensure the stability of the loop, two criteria must be verified with PMi as phase margin.

According to the previous equations, τv, Kp_v and Ki_v are defined by

In bilinear transformation, the formula below is used

The voltage loop controller Cv(z) is defined by

where

According to the previous equations Kpz_i and Kiz_i are defined by

τv=

tan PMi+ 90 × 2 × R × C × π2× F

4 × HVDC × Kv× π × F

K

=

p_v

Cvz =

HVDC

R =

P

20 × log Tvs = 1 (59)

arg Tvs = + 180 + PM

R × C × F

VAC× VR× R × Kv×

K

⋅ T

p_v

2 ⋅ τ

v

K

pz_v

s_v

= K

K

iz_v

K

s =

− K

i_v

τv=

p_v

=

c_v

c_v

=

2

T

s

p_v

−

2 × τv× F

2

OUT

to be around 15 time lower than the

C_v

i

− tan PMi+ 90

2

+ 2 × π × F

c_v

× τv× 1 + R × C × π × F

1 + τi× 2 × π × F

K

p_v

τ

v

z − 1

×

z + 1

K

⋅ T

p_v

+

2 × τ

−1 + z

K

p_v

K

i_v

K

p_v

2 × τv× F

K

s_v

p_v

s_v

s_v

v

+ K

c_v

p_v

c_v

2

⋅ z

c_v

, and the PFC output

out

2

(58)

(60)

(61)

(62)

(63)

(64)

(65)

(66)

(67)

(68)

Note: The voltage loop is executed at each zero cross of the AC line voltage. Fs_v is fixed at twice the AC line

frequency.

To thoroughly use MCU resources, the PI corrector coefficients are normalized to fixed-point decimal format (Q15

data format). The relation between the actual and normalized values is defined by

K

pz_v_Q15

K

iz_v_Q15

= K

= K

× 2048

pz_v

× 2048 (70)

iz_v

To optimize the HVDC regulation, the PI voltage loop coefficient has been defined according to the AC line

voltage.

The table below defines the controller coefficient to be set in the MCU. In the firmware:

• the integral gain is defined by “PI_VBUS_KI_230” and “PI_VBUS_KI_110” according to the AC line voltage

range

• the proportional gain is defined by “PI_VBUS_KP_230” and “PI_VBUS_KP_110” according to the AC line

voltage range

UM2792 - Rev 1

(69)

page 49/101

Page 50

Table 11. Integral and proportional gains of the current loop PI controller

UM2792

Controller design

Parameter

VAC = 110 V

P

OUT_MAX

RMS

= 1.8 kW

Kpz_v_Q15 2300 940

Kiz_v_Q15 500 400

VAC = 230 V

P

OUT_MAX

RMS

= 3.6 kW

UM2792 - Rev 1

page 50/101

Page 51

11 AC line zero crossing synchronization

ADC

VAC

PI

+

+

α

θ

/

Integral

α/β

d/q

d/q

α/β

wc

β

q

d

LPF

LPF

VAC

VRMS

Frequency

11.1 PLL loop control design

To track the frequency and phase of the AC line voltage, a phase-locked loop (PLL) is used. The block diagram of

this loop is defined in Figure 56 by using a low pass filter and a PI controller implemented in the STM32 firmware.

PLL is used to generate the current reference in phase with the AC line voltage to shape the input AC line current

to the AC line voltage.

Figure 56. PLL diagram

UM2792

AC line zero crossing synchronization

The PLL is a closed loop system where the phase error between the PLL output phase and the reference is

minimum. In steady state, the PLL output generates a sinusoidal wave close to the AC line voltage. A PI controller

is used to reduce the error between the reference and the Vq value measured. Vq is defined thanks to the Park

transformations of AC line voltage.

In steady state operation, the PLL and the grid frequency are closed. The simplified system for the PLL is defined

by the following figure.

Figure 57. PLL loop PI controller

The input voltage sense gain is defined by

The ADC STM32 transfer function is defined by

K

VAC_sense

ADC =

n

2

=

V

ref

= 0.003545

12

2

= 1241

3.3

(71)

(72)

UM2792 - Rev 1

page 51/101

Page 52

The full transfer function of open loop is defined by

T

PLL s

= Vm ⋅ Kp

PLL

1 + τ

⋅

τ

PLL

PLL

⋅ s

1

⋅

s

⋅ s

The current loop controller CPLL(s) is defined by the following equation with K

coefficients

C

PLL

s = K

p_PLL

1 + τ

×

τ

PLL

PLL

× s

× s

with

K

τ

PLL

p_PLL

=

K

i_PLL

The input voltage sense gain is defined by

K

VAC_sense

= 0.003545 (76)

The ADC STM32 transfer function is defined by

n

12

2

ADC =

V

ref

2

=

= 1241 (77)

3.3

Vm is defined by

Vm= VAC ⋅ Kv⋅ ADC (78)

p_PLL

and K

i_PLL

UM2792

Controller design

(73)

as analog

(74)

(75)

11.2 Controller design

A good current loop performance needs the crossover frequency F

stability of the loop, two criteria must be verified with PMi phase margin fixed at 45°C.

According to the previous equations, τ

K

p_PLL

In bilinear transformation, the formula below is used

The current loop controller CPLL(z) is defined by

According to the previous equations Kpz_i and Kiz_i are defined by

=

C

V

PLL

AC_Peak

z =

arg T

, K

PLL

× ADC × K

K

⋅ T

p_PLL

2 ⋅ τ

K

pz_PLL

K

20 × log T

PLL

p_PLL

τ

PLL

τ

PLL

VAC_Sense

K

i_PLL

s =

s_PLL

PLL

= K

iz_PLL

s = 1 (79)

PLL

s = + 180 + PM

and K

i_PLL

tan PM

× 1 + τ

=

2

×

s

K

K

−

K

p_PLL

τ

PLL

z − 1

z + 1

K

−1 + z

p_v

i_v

2 × τ

K

p_PLL

PLL

PLL

c_PLL

C_PLL

p_PLL

× F

=

2 × π × F

× 2 × π × F

T

− K +

τv=

p_PLL

=

2 × τ

to be fixed at 65 Hz. To ensure the

C_PLL

i

are defined by

2

× 2 × π × F

PLL

⋅ T

s_PLL

2 × τ

PLL

K

p_PLL

× F

PLL

s_PLL

s_PLL

+ K

C_PLL

p_PLL

= 0.546

2

⋅ z

(80)

(81)

(82)

(83)

(84)

(85)

(86)

(87)

(88)

Note: The PLL loop is executed at 9 kHz (Fs_PLL).

To thoroughly use MCU resources, the PI corrector coefficients are normalized to fixed-point decimal format (Q15

data format). The relation between the actual and normalized values is defined by

K

pz_PLL_Q15

UM2792 - Rev 1

= K

pz_PLL

× 2048

(89)

page 52/101

Page 53

UM2792

Controller design

K

iz_PLL_Q15

= K

× 2048 (90)

iz_PLL

To optimize the HVDC regulation, the PI PLL loop coefficient has been defined according to the AC line voltage.

The table below defines the controller coefficient to be set in the MCU. In the firmware:

• the integral gain is defined by “PI_PLL_KI_230” and “PI_PLL_KI_110” according to the AC line voltage range

• the proportional gain is defined by “PI_PLL_KP_230” and “PI_PLL_KP_110” according to the AC line voltage

range

Table 12. Integral and proportional gains of the current loop PI controller

Parameter

Kpz_PLL_Q15 1421 460

Kiz_PLL_Q15 30 10

VAC = 110 V

P

OUT_MAX

RMS

= 1.8 kW

VAC = 230 V

P

OUT_MAX

RMS

= 3.6 kW

UM2792 - Rev 1

page 53/101

Page 54

12 Experimental results

0

2

4

6

8

10

12

14

16

85

87

89

91

93

95

97

99

0 500 1000 30001500 2000 2500 3500 4000

THD (%)

Efficiency (%)

Output power (P

out

)

V

AC

= 230 V

RMS

- 50 Hz

12.1 Efficiency and THD

The figures below show the PFC totem pole efficiency and THD according to the output power (P

UM2792

Experimental results

).

out

Figure 58. PFC efficiency and THD for VAC = 230 V

Figure 59. PFC efficiency and THD for VAC = 110 V

RMS

RMS

/50 Hz

/60 Hz

UM2792 - Rev 1

page 54/101

Page 55

12.2 Load variation

HVDC

S1_CNTRL

S2_CNTRL

V

AC

I

AC

I

HVDC

2

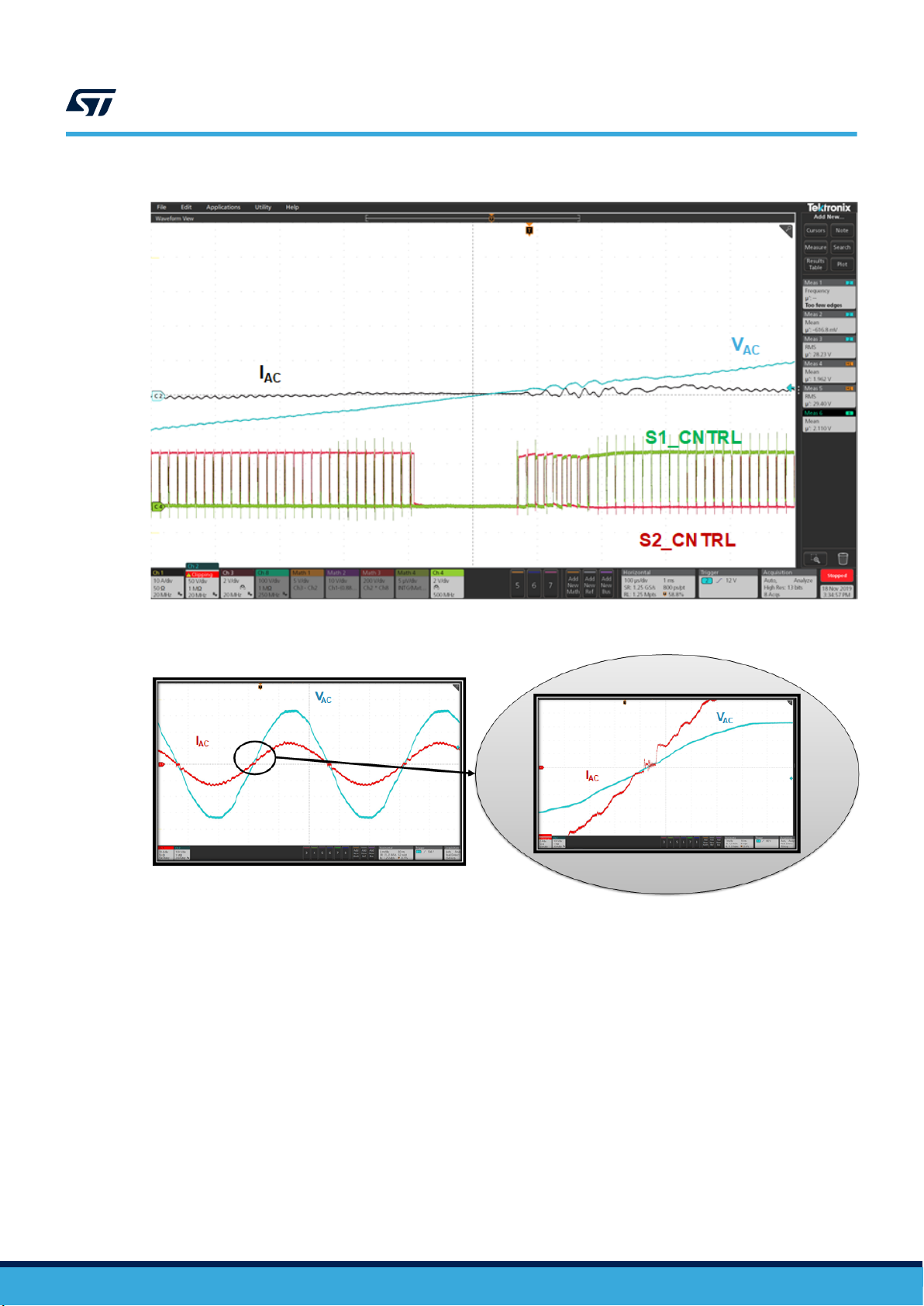

The figure below shows the transient response of the PFC totem pole when the AC line voltage is 230 V

and the DC load current (IHVDC) is stepped up from 0 % to 100 % (see 1) and stepped down from 100 % to 0 %

(see 2).

UM2792

Load variation

(VAC)

rms

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

IHVDC = PFC output current

Figure 60. Load variation with VAC = 230 V

RMS

/50 Hz

The figure below shows the transient response when the AC line voltage is 230 V

(VAC) and the DC load

rms

current (IHVDC) is stepped up from 50 % to 100 % (see 1) and stepped down from 100 % to 50 % (see 2).

UM2792 - Rev 1

page 55/101

Page 56

HVDC

S2_CNTRL

S1_CNTRL

V

AC

I

AC

I

HVDC

2

UM2792

PFC totem pole startup

Figure 61. Load variation with VAC = 230 V

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

IHVDC = PFC output current

/50 Hz (stepped up/down to 50%)

RMS

12.3 PFC totem pole startup

The figure below shows the startup sequence of the PFC totem pole with VAC = 230 V

DC load.

Figure 62. PFC startup with VAC = 230 V

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

/50 Hz and with a 1 kW

rms

/50 Hz and P

RMS

= 1 kW

out

UM2792 - Rev 1

The figure below shows the startup sequence of the PFC totem pole with VAC = 110 V

DC load.

/60 Hz and with a 1 kW

rms

page 56/101

Page 57

UM2792

Steady state operation

Figure 63. PFC startup with VAC = 110 V

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

Figure 64. PFC startup with VAC = 110 V

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

/60 Hz and P

RMS

/60 Hz and without DC load

RMS

out

= 1 kW

12.4

UM2792 - Rev 1

Steady state operation

The figures below show the PFC steady state current waveform at different load conditions.

page 57/101

Page 58

UM2792

Steady state operation

Figure 65. PFC steady state with VAC = 230 V

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

Figure 66. PFC steady state with VAC = 230 V

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

/50 Hz and Pout = 1 kW

RMS

/50 Hz and Pout = 2 kW

RMS

UM2792 - Rev 1

page 58/101

Page 59

UM2792

Mains voltage dips and interruptions

Figure 67. PFC steady state with VAC = 230 V

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

/50 Hz and Pout = 3 kW

RMS

12.5 Mains voltage dips and interruptions

12.5.1 IEC 61000-4-11 standard

IEC 61000-4-11 standard defines the test conditions to evaluate the immunity of the equipment to a voltage dip

or interrupt. As any appliance connected to the mains can be subject to line voltage dips or interruptions, a high

input current may occur when the line voltage suddenly increases to its nominal value. This high current may

damage the front-end circuit components such as the AC fuse for example.

12.5.2 PFC voltage dips

The STEVAL-DPSTPFC1 MCU firmware is programmed to comply with the IEC 61000-4-11 standard tests on the

basis of the following strategy:

UM2792 - Rev 1

page 59/101

Page 60

Mains voltage dips and interruptions

• if the peak AC line voltage falls below 70% of the AC line peak reference voltage, SCR1/SCR2 and

MOSFET1/MOSFET2 are switched off. The DC bus voltage is discharged by its load current. When the line

voltage is reapplied and if the HVDC voltage is higher than 80% of 400 VDC (PFC output voltage), the SCRs

are controlled back in full wave and MOSFET1/ MOSFET2 controlled in PWM.

Figure 68. AC line drop principle (HVDC > 80% of 400 VDC)

UM2792

Note: The SCR1/SCR2 and MOSFET1/MOSFET2 are switched on at the next zero cross of the AC line voltage when

the line voltage is reapplied.

• if the peak AC line voltage falls below 70% of the AC line peak reference voltage, SCR1/SCR2 and

MOSFET1/MOSFET2 are switched off. The DC bus voltage is discharged by its load current. When the line

voltage is reapplied and if the HVDC voltage is lower than 80% of 400 VDC, the SCRs are controlled back in

soft-start to ensure the inrush current limitation

Figure 69. AC line drop principle (HVDC < 80% of 400 VDC)

UM2792 - Rev 1

page 60/101

Page 61

UM2792

Mains voltage dips and interruptions

The figure below shows the PFC totem pole board behavior, working at 230 V

AC line voltage with a 1 kW

RMS

DC load, for an AC line voltage dip with a 0% residual voltage applied for 40 ms. When the voltage is reapplied

back and if HVDC voltage is higher than 80% of 400 VDC, SCRs are controlled in full wave according to the

AC line polarity and MOSFET1/ MOSFET2 controlled in PWM. The peak current is only 25 A as the DC voltage

decreased by just 100 V during the lack of AC line voltage.

Figure 70. Mains voltage dips with VAC = 230 V

VAC = AC line voltage

IAC = AC line current

HVDC = PFC output voltage

rms

and P

= 1 kW(0% residual voltage applied for 40 ms)

out

The figure below shows the PFC totem pole board behavior, working at 230 V

AC line voltage with a 1 kW

RMS

DC load, for an AC line voltage dip with a 0% residual voltage applied for 100 ms. When the voltage is reapplied

back and the HVDC voltage is lower than 80% of the 400 VDC, SCRs are controlled in soft-start (as at any system

startup) to avoid any component damage according to the AC line polarity.

UM2792 - Rev 1

page 61/101

Page 62

UM2792

Mains voltage dips and interruptions

Figure 71. Mains voltage dips with VAC = 230 V

VAC = AC line voltage

IAC = AC line current