5.0V OR 3.3V, 1 Mbit (128 Kb x 8) ZEROPOWER® SRAM

FEAT URES SUMMARY

M48Z129Y*

M48Z129V

■ INTEGRATED, ULT RA LOW POWER SRAM,

POWER-FAIL CONTROL CIRCUIT, AND

BATTERY

■ CONVENTIONAL SRAM OPERATION;

UNLIMITED WRITE CYCLES

■ 10 YEARS OF DATA RETENTION IN THE

ABSENCE OF POWER

■ MICROPROCESSOR POWER-ON RESET

(RESET VALID EVEN DURING BATTERY

BACK-UP MODE)

■ BATTERY LOW PIN - PROV IDES WARNI NG

OF BATTERY END-OF-LIFE

■ AUTOMATIC POWER-FAIL CHIP

DESELECT AND WRITE PROTECT ION

■ WRITE PROTECT VOLTAGES

= Power-fail Deselect Voltage):

(V

PFD

– M48Z129Y: V

4.2V ≤ V

PFD

– M48Z129V: V

2.7V ≤ V

■ SELF-CONTAINED BATTERY IN THE

PFD

= 4.5 to 5.5V

CC

≤ 4.5V

= 3.0 to 3.6V

CC

≤ 3.0V

CAPHAT™ DIP PACKAGE

■ PIN AND FUNCTION COMPATIBLE WITH

JEDEC STANDARD 128K x 8 SRAMs

Figure 1. 32-pi n PMDIP Mo du le

32

1

PMDIP32 (PM)

Module

* Contact local ST sales office for availability.

1/16March 2005

M48Z129Y*, M48Z129V

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. 32-pin PMDIP Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

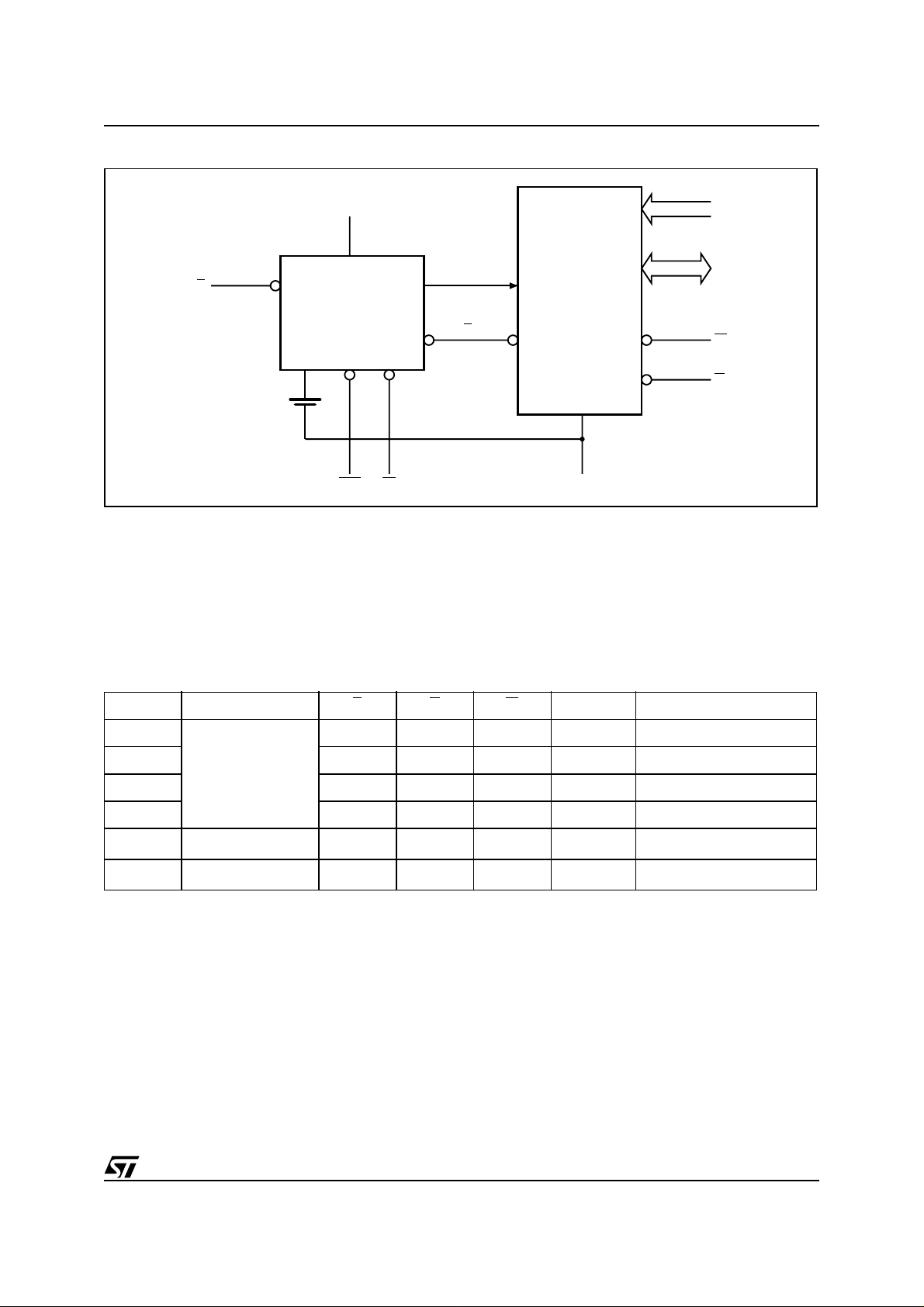

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 3. DIP Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 4. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

OPERATION MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 2. Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

READ Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 5. Address Controlled, READ Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Figure 6. Chip Enable or Output Enable Controlled, READ Mode AC Waveforms . . . . . . . . . . . . . 6

Table 3. RE A D Mode AC Charac teristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

WRITE Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 7. WRITE Enable Controlled, WRITE Mode AC Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 8. Chip Enable Controlled, WRITE Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 4. WRITE Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Data Retention Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

V

Noise And Negative Going Transients. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

CC

Figure 9. Supply Voltage Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 5. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 6. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 10.AC Testing Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 7. Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 8. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 11.Power Down/Up Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 9. Power Down/Up AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Table 10. Power Down/Up Trip Points DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

PACKAGE MECHANICAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 12.PMDIP32 – 32-pin Plastic Module DIP, Package Outline . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 11. PMDIP32 – 32-pin Plastic DIP, Package Mechanical Data. . . . . . . . . . . . . . . . . . . . . . . 13

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 12.Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

REVISION HISTO RY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2/16

M48Z129Y*, M48Z129V

Table 13.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3/16

M48Z129Y*, M48Z129V

SUMMARY DESCRIPTION

The M48Z129Y/V ZEROPOWER® SRAM is a

1,048,576 bit non-volatile static RAM organized as

131,072 words by 8 bits. The device combines an

internal lithium battery, a CMOS SRAM and a control circuit in a plastic 32-pin DIP Module. The

M48Z129Y/V directly replaces industry standard

128K x 8 SRAM. It also provides the non-volatility

of FLASH without any requirement for special

WRITE timing or limitations on the number of

WRITEs that can be performed.

Figure 2. Logic Diagram Table 1. Signal Names

V

CC

17

8

A0-A16 DQ0-DQ7

W RST

M48Z129Y

M48Z129V

E

BL

G

V

SS

AI02309

A0-A16 Address Inputs

DQ0-DQ7 Data Inputs / Outputs

E

G

W

RST

BL

V

CC

V

SS

Chip Enable

Output Enable

WRITE Enable

Reset Output (Open Drain)

Battery Low Output (Open Drain)

Supply Voltage

Ground

Figure 3. DIP C on ne ctions

1

RST V

2

A16

A14

3

A12

4

5

A7

6

A6

7

A5

A4

8

M48Z129Y

A3

A2

A1

A0

DQ0

M48Z129V

9

10

11

12

13

14

DQ2

15

16

SS

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

AI02310

CC

A15

BL

W

A13

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5DQ1

DQ4

DQ3V

4/16

Figure 4. Block Diagram

M48Z129Y*, M48Z129V

V

CC

A0-A16

E

INTERNAL

BATTERY

VOLTAGE SENSE

AND

SWITCHING

CIRCUITRY

RST V

BL

OPERATION MODES

The M48Z129Y/V also has its own Power-Fail Detect circuit. This control circuitry constantly monitors the supply voltage for an out of tolerance

condition. When V

write protects the SRAM, providing data security in

Table 2. Operating Modes

Mode

Deselect

WRITE

READ

READ

Deselect

Deselect

Note: X = VIH or VIL; VSO = Battery B ack-up Switc hover Voltage.

1. See Table 10., page 12 for details.

VSO to V

is out of tolerance, the circuit

CC

V

CC

4.5 to 5.5V

or

3.0to 3.6V

(min)

PFD

(1)

≤ V

SO

(1)

E G W DQ0-DQ7 Power

V

IH

V

IL

V

IL

V

IL

X X X High Z CMOS Standby

X X X High Z Battery Back-up Mode

X X High Z Standby

X

V

V

POWER

E

131,072 x 8

SRAM ARRAY

SS

DQ0-DQ7

W

G

the midst of unpredictable system operation. A s

falls, the cont rol circuit ry automaticall y switch-

V

CC

es to the battery, maintaining data until valid power

is restored.

V

IL

IL

IH

V

IH

V

IH

D

IN

D

OUT

Active

Active

High Z Active

AI03608

5/16

M48Z129Y*, M48Z129V

READ Mode

The M48Z129Y/V is in the READ Mode whenever

(WRITE Enable) is high and E (Chip Enable) is

W

low. The unique address specified by the 17 address inputs defines which one of the 131,072

bytes of dat a is to be acces sed . Vali d data w ill be

available at the Data I/O pins within t

AVQV

(Address Access Time) after the last address input

signal is stable, providing the E

times are also satisfied. If the E

and G access

and G access

times are not met, valid data will be available after

the latter of the Chip Enable Access Times (t

or Output Enable Access Time (t

The state of the eight t hree-state Da ta I/O si gnals

is controlled by E

ed before t

indeterminate state until t

puts are changed while E

and G. If the outputs are activat-

, the data lines will be driven to an

AVQV

AVQV

and G remain active,

output data will remain valid for t

Data Hold Time) but will go indeterminate until the

next Address Access.

Figure 5. Address Controlled, READ Mode AC Waveforms

tAVAV

A0-A16

tAVQV

tAXQX

DQ0-DQ7

Note: Chip Enable ( E) and Output Enable (G) = Low, WRITE Enable (W) = High.

DATA VALID

VALID

DATA VALID

Figure 6. Chip Enable or Output Enable Controlled, READ Mode AC Waveforms

ELQV

).

GLQV

. If the Ad dres s In-

(Output

AXQX

AI02324

)

A0-A16

E

G

DQ0-DQ7

tAVAV

VALID

tAVQV tAXQX

tELQV

tELQX

tGLQV

tGLQX

DATA OUT

tEHQZ

tGHQZ

AI01197

6/16

M48Z129Y*, M48Z129V

Table 3. READ Mode AC Characteristics

M48Z129Y M48Z129V

Symbol

t

AVAV

t

AVQV

t

ELQV

t

GLQV

t

ELQX

t

GLQX

t

EHQZ

t

GHQZ

t

AXQX

Note: 1. Valid for Ambient Operating Tem perature : TA = 0 to 70°C; VCC = 4.5 to 5.5V or 3. 0 to 3.6V (exc ept where noted ).

2. C

READ Cycle Time 70 85 ns

Address Valid to Output Valid 70 85 ns

Chip Enable Low to Output Valid 70 85 ns

Output Enable Low to Output Valid 35 45 ns

(2)

Chip Enable Low to Output Transition 5 5 ns

(2)

Output Enable Low to Output Transition 3 5 ns

(2)

Chip Enable High to Output Hi-Z 30 40 ns

(2)

Output Enable High to Output Hi-Z 20 25 ns

Address Transition to Output Transition 5 5 ns

= 5pF (see Figur e 10., page 11).

L

Parameter

(1)

Min Max Min Max

Unit–70 –85

WRITE Mode

The M48Z129Y/V is in the WRITE Mode whenever

(WRITE Enable) and E (Chip Enable) are ac-

W

tive. The start of a WRITE is referenced from the

latter occurring falling edge of W

terminated by the earlier rising edge of W

or E. A WRIT E is

or E.

The addresses must be hel d valid throughout t he

cycle. E

t

EHAX

or W must return hi gh for a minimum of

from Chip Enable or t

from WRITE En-

WHAX

able prior to the initiation of another READ or

WRITE cycle. Data -i n mu st be va l id t

the end of WRITE and remain valid for t

ward. G

should be kept high during WRITE cycles

to avoid bus contention; although, if the output bus

has been activated by a low on E

will disable the o ut p u t s t

W

Figure 7. WRITE Enable Controlled , WRITE Mode AC Waveform

tAVAV

A0-A16

tAVEL

E

tAVWL

W

tWLQZ

VALID

tAVWH

tWLWH

tWHDX

WLQZ

tWHAX

tWHQX

prior to

DVWH

WHDX

after-

and G a low on

after W falls.

DQ0-DQ7

tDVWH

DATA INPUT

AI02382

7/16

M48Z129Y*, M48Z129V

Figure 8. Chip Enable Controlled, WRITE Mode AC Waveforms

tAVAV

A0-A16

tAVEL

E

tAVWL

W

DQ0-DQ7

VALID

tAVEH

tWLWH

tELEH

tDVEH

tEHAX

tEHDX

DATA INPUT

AI03611

Table 4. WRITE Mode AC Characteristics

M48Z129Y M48Z129V

Symbol

t

AVAV

t

AVWL

t

AVEL

t

WLWH

t

ELEH

t

WHAX

t

EHAX

t

DVWH

t

DVEH

t

WHDX

t

EHDX

(2,3)

t

WLQZ

t

AVWH

t

AVEH

t

WHQX

Note: 1. Valid for Ambient Operating Tem perature : TA = 0 to 70°C; VCC = 4.5 to 5.5V or 3. 0 to 3.6V (exc ept where noted ).

2. C

3. If E

WRITE Cycle Time 70 85 ns

Address Valid to WRITE Enable Low 0 0 ns

Address Valid to Chip Enable Low 0 0 ns

WRITE Enable Pulse Width 55 65 ns

Chip Enable Low to Chip Enable High 55 75 ns

WRITE Enable High to Address Transition 5 5 ns

Chip Enable High to Address Transition 15 15 ns

Input Valid to WRITE Enable High 30 35 ns

Input Valid to Chip Enable High 30 35 ns

WRITE Enable High to Input Transition 0 0 ns

Chip Enable High to Input Transition 10 15 ns

WRITE Enable Low to Output Hi-Z 25 30 ns

Address Valid to WRITE Enable High 65 75 ns

Address Valid to Chip Enable High 65 75 ns

(2,3)

WRITE Enable High to Output Transition 5 5 ns

= 5pF (see Figur e 10., page 11).

L

goes low simultaneously with W going low, the outputs remai n in the high impedance stat e.

Parameter

(1)

Min Max Min Max

Unit–70 –85

8/16

Data Retention Mode

M48Z129Y*, M48Z129V

With valid V

applied, the M48Z129Y/V operates

CC

as a conventional BYTEWIDE™ static RAM.

Should the supply voltage decay, the RAM will automatically deselect, write protecting itself when

falls between V

V

CC

(max), V

PFD

PFD

(min) window. All outputs become high impedance and all

inputs are treated as “Don’t care”.

Note: A power failure during a W RITE cycle may

corrupt data at the current addressed location, but

does not jeopardize the rest of the RAM’s content.

At voltages below V

in a write protected state, provided the V

time is not less than t

spond to transient noise s pi kes on V

(min), the memory will be

PFD

that cr os s

CC

CC

. The M48Z129Y/V may re-

F

fall

into the deselect window during the time the device is sampling V

. Therefore, decoupling of the

CC

power supply lines is recommended.

When V

drops below VSO, the control circuit

CC

switches power to the internal b attery, preserving

data. The internal energy source will maintain data

in the M48Z129Y/V f or an accumulated pe riod of

at least 10 years at room temperature. As system

power rises above V

, the battery is disconnect-

SO

ed, and the power supply is switched to external

. Deselect continues for t

V

CC

PFD

(max).

es V

REC

after V

CC

reach-

For more information on Battery Storage Life refer

to the Application Note AN1012.

In addition to transients that are caused by normal

SRAM operation, power cycling can generate negative voltage spikes on V

below V

by as much as one volt. These negative

SS

that drive it to values

CC

spikes can cause data corruption in the SRAM

while in battery backup mode. To protect from

these voltage spikes, it is recommended to connect a schottky diode from V

connected to V

, anode to VSS). Schottky diode

CC

to VSS (cathode

CC

1N5817 is recommended for through hole and

MBRS120T3 is recommended for surface mount.

Figure 9. Supply Voltage Protection

V

CC

V

CC

0.1µF DEVICE

Noise And Negative Going Transients

V

CC

I

transients, including those produced by output

CC

switching, can produce voltage fluctuations, resulting in spikes on the V

bus. These transients

CC

can be reduced if capacitors are used to store energy which stabilizes the V

bus. The energy

CC

stored in the bypass capacitors will be released as

low going spikes are generated or energy will be

absorbed when overshoots occur. A ceramic bypass capacitor value of 0.1µF (as shown in Figure

9.) is recommended in order to provide the needed

filtering.

V

SS

AI02169

9/16

M48Z129Y*, M48Z129V

MAXIMUM RA T ING

Stressing the device above the rating l isted in t he

“Absolute Maximum Ratings” table may cause

permanent damage to the device. These are

stress ratings only and operation of the device at

these or any other conditions above those indicat-

not implied. Exposure to Absol ute Max imum Ra ting conditions for extended periods may affect device reliability. Refer also to the

STMicroelectronics SURE Program and other relevant quality documents.

ed in the Operating sections of this specification is

Table 5. Absolute Maximum Ratings

Symbol Parameter Value Unit

T

A

T

STG

(1)

T

SLD

V

IO

V

CC

I

O

P

D

Note: 1. Soldering temperature not to exceed 260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).

No preheat above 150°C , or di rect exposure to IR reflow (or IR preheat ) al l owed, to avoi d damaging the Lithium bat tery.

CAUTION: Negative undershoots bel ow –0.3V are not al l owed on any pin whi l e i n the Batter y Back-up mode.

Ambient Operating Temperature 0 to 70 °C

Storage Temperat ure (VCC Off, Oscillator Off)

Lead Solder Temperature for 10 seconds 260 °C

Input or Output Voltages –0.3 to 7 V

Supply Voltage –0.3 to 7 V

Output Current 20 mA

Power Dissipation 1 W

–40 to 85 °C

DC AND AC PARAMETERS

This section summarizes the operating and measurement conditions, as well as the DC and AC

characteristics of the device. The parameters in

the following DC and AC Characteristic tables are

derived from tests performed under the Meas ure-

Table 6. Operating and AC Measurement Conditions

Parameter M48Z129Y M48Z129V Unit

Supply Voltage (V

Ambient Operating Temperature (T

Load Capacitance (C

Input Rise and Fall Times ≤ 5 ≤ 5ns

Input Pulse Voltages 0 to 3 0 to 3 V

Input and Output Timing Ref. Voltages 1.5 1.5 V

Note: Output Hi-Z is defined as the poi nt where dat a i s no longer driven.

CC

)

)

A

)

L

ment Conditions listed in t he relevant tables. Designers should check that the operating conditions

in their projects match the measurement conditions when using the quoted parameters.

4.5 to 5.5 3.0 to 3.6 V

0 to 70 0 to 70 °C

100 50 pF

10/16

Figure 10. AC Testing Load Circuit

M48Z129Y*, M48Z129V

DEVICE

UNDER

TEST

CL includes JIG capacitance

Note: 1. 50pF for M 48Z 129V (3.3 V ).

650Ω

CL = 100pF

or 50pF

(1)

1.75V

AI03630

Table 7. Capacitance

Symbol

C

IN

C

IO

Note: 1. Effec tive capacit ance measured with power supply at 5V; sampled only, not 100 % te sted.

2. At 25°C, f = 1MHz.

3. Outputs deselect ed.

Input Capacitance 10 pF

(3)

Input / Output Capacitance 10 pF

Parameter

(1,2)

Min Max Unit

Table 8. DC Characteristics

M48Z129Y M48Z129V

IN

≤ V

≤ V

IH

CC

(1)

Min Max Min Max

±1 ±1 µA

CC

±1 ±1 µA

74mA

43mA

V

CC

+ 0.3

2.2

0.4 0.4 V

2.4 2.2 V

VCC + 0.3

Sym Parameter

I

LI

I

LO

I

CC

I

CC1

I

CC2

V

V

V

OL

V

OH

Note: 1. Valid for Ambient Operating Tem perature : TA = 0 to 70°C; VCC = 4.5 to 5.5V or 3. 0 to 3.6V (exc ept where noted ).

2. Outputs deselect ed.

Input Leakage Current

(2)

Output Leakage Current

Supply Current Outputs open 95 50 mA

Supply Current (Standby) TTL

Supply Current (Standby) CMOS

Input Low Voltage –0.3 0.8 –0.3 0.6 V

IL

Input High Voltage 2.2

IH

Output Low Voltage

Output High Voltage

Test Condition

0V ≤ V

0V ≤ V

OUT

E

= V

E

= VCC – 0.2V

I

= 2.1mA

OL

I

= –1mA

OH

Unit–70 –85

V

11/16

M48Z129Y*, M48Z129V

Figure 11. Power Down/Up Mode AC Waveforms

V

CC

V

(max)

PFD

V

(min)

PFD

VSO

E

OUTPUTS

RST

tF

tFB

tWPT

RECOGNIZED

VALID VALID

(PER CONTROL INPUT) (PER CONTROL INPUT)

tDR

tRB

DON'T CARE

HIGH-Z

tR

tREC

RECOGNIZED

Table 9. Power Down/Up AC Characteristics

Symbol

(2)

t

F

(3)

t

FB

t

R

t

RB

t

WPT

t

REC

Note: 1. Valid for Ambient Operating Tem perature : TA = 0 to 70°C; VCC = 4.5 to 5.5V or 3. 0 to 3.6V (exc ept where noted ).

2. V

es V

3. V

V

(max) to V

PFD

V

(min) to VSS VCC Fall Time

PFD

V

(min) to V

PFD

VSS to V

PFD

(min) VCC Fall Time

PFD

(max) VCC Rise Time

PFD

(min) VCC Rise Time

Write Protect Time

V

(max) to RST High

PFD

(max) to V

PFD

(min).

PFD

(min) to VSS fall time of less than tFB may cause corruption of RAM data.

PFD

(min) fall time of less than tF may result in deselection/write protection not occurring until 200µs after VCC pass-

PFD

Parameter

(1)

Min Max Unit

300 µs

M48Z129Y 10

M48Z129V 150

10 µs

1µs

M48Z129Y 40 150

M48Z129V 40 250

40 200 ms

AI03610

µs

µs

Table 10. Power Down/Up Trip Points DC Characteristics

Symbol

V

PFD

V

SO

t

DR

Note: 1. All voltages referenced to VSS.

2. Valid for Ambien t Operating Tem perature : T

3. At 25°C, V

Power-fail Deselect Voltage

Battery Back-up Switchover Voltage

(3)

Expected Data Retention Time 10 YEARS

= 0V.

CC

12/16

Parameter

(1,2)

M48Z129Y 4.2 4.35 4.5 V

M48Z129V 2.7 2.9 3.0 V

M48Z129Y 3.0 V

M48Z129V 2.45 V

= 0 to 70°C; VCC = 4.5 to 5.5V or 3. 0 to 3.6V (exc ept where noted ).

A

Min Typ Max Unit

PACKAG E MECHANICAL INFORMATION

Figure 12. PMDIP32 – 32-pin Plastic Module DIP, Package Outline

M48Z129Y*, M48Z129V

A1AL

S

B

e1

eA

e3

D

N

E

1

Note: Drawing is not to scale.

PMDIP

Table 11. PMDIP32 – 32-pin Plastic DIP, Package Mechanical Data

Symb

Typ Min Max Typ Min Max

A 9.27 9.52 0.365 0.375

A1 0.38 – 0.015 –

B 0.43 0.59 0.017 0.023

C 0.20 0.33 0.008 0.013

mm inches

C

D 42.42 43.18 1.670 1.700

E 18.03 18.80 0.710 0.740

e1 2.29 2.79 0.090 0.110

e3 34.29 41.91 1.350 1.650

eA 14.99 16.00 0.590 0.630

L 3.05 3.81 0.120 0.150

S 1.91 2.79 0.075 0.110

N32 32

13/16

M48Z129Y*, M48Z129V

PART NUMBERING

Table 12. Ordering Information Scheme

Example: M48Z 129Y –70 PM 1 TR

Device Type

M48Z

Supply Voltage and Write Protect Voltage

(1)

129Y

= VCC = 4.5 to 5.5V; 4.2V ≤ V

129V = V

Speed

–70 = 70ns (M48Z129Y)

–85 = 85ns (M48Z129V)

= 3.0 to 3.6V; 2.7V ≤ V

CC

PFD

PFD

≤ 3.0V

≤ 4.5V

Package

PM = PMDIP32

Temperature Range

1 = 0 to 70°C

Shipping Method

blank = Tubes

TR = Tape & Reel

Note: 1. Conta ct Local Sales O ffice

For other options, or for more information on any aspect of this device, please contact the ST Sales Office

nearest you.

14/16

M48Z129Y*, M48Z129V

REVISION HISTORY

Table 13. Document Revision History

Date Version Revision Details

December 1999 1.0 First Issue

30-Mar-00 2.0 From Preliminary Data to Data Sheet

t

20-Jun-00 2.1

14-Sep-01 3.0 Reformatted; Temperature information added to tables (Table 7, 8, 3, 4, 9, 10)

29-May-02 3.1 Add countries to disclaimer

02-Apr-03 4.0 v2.2 template applied; test condition updated (Table 10)

18-Feb-05 5.0 Reformatted; IR reflow update (Table 5)

changed for M48Z129Y (Table 3)

GLQX

15/16

M48Z129Y*, M48Z129V

Information furnished is believed to be accurate and reliable. However, STMicroelectronics a ssumes no responsibility fo r the c onsequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authori zed for use as crit i cal components in life support devices or systems w i th out express written approval of STMicroelectro nics.

The ST logo is a registered tra demark of STMi croelectronics.

All other nam es are the property of their respective owners

© 2005 STMi croelectro ni cs - All rights reserved

Australi a - Belgium - Brazil - Canad a - China - Czech Republic - F i nl and - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - M al ta - Morocco - Singapore - Spain - Swede n - S wi tzerland - United Kingdom - United States of Am eri ca

STMicroelectronics group of com panies

www.st.com

16/16

Loading...

Loading...