STMicroelectronics M48Z129Y, M48Z129V User Manual

5.0V OR 3.3V, 1 Mbit (128 Kb x 8) ZEROPOWER® SRAM

FEAT URES SUMMARY

M48Z129Y*

M48Z129V

■ INTEGRATED, ULT RA LOW POWER SRAM,

POWER-FAIL CONTROL CIRCUIT, AND

BATTERY

■ CONVENTIONAL SRAM OPERATION;

UNLIMITED WRITE CYCLES

■ 10 YEARS OF DATA RETENTION IN THE

ABSENCE OF POWER

■ MICROPROCESSOR POWER-ON RESET

(RESET VALID EVEN DURING BATTERY

BACK-UP MODE)

■ BATTERY LOW PIN - PROV IDES WARNI NG

OF BATTERY END-OF-LIFE

■ AUTOMATIC POWER-FAIL CHIP

DESELECT AND WRITE PROTECT ION

■ WRITE PROTECT VOLTAGES

= Power-fail Deselect Voltage):

(V

PFD

– M48Z129Y: V

4.2V ≤ V

PFD

– M48Z129V: V

2.7V ≤ V

■ SELF-CONTAINED BATTERY IN THE

PFD

= 4.5 to 5.5V

CC

≤ 4.5V

= 3.0 to 3.6V

CC

≤ 3.0V

CAPHAT™ DIP PACKAGE

■ PIN AND FUNCTION COMPATIBLE WITH

JEDEC STANDARD 128K x 8 SRAMs

Figure 1. 32-pi n PMDIP Mo du le

32

1

PMDIP32 (PM)

Module

* Contact local ST sales office for availability.

1/16March 2005

M48Z129Y*, M48Z129V

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. 32-pin PMDIP Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 3. DIP Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 4. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

OPERATION MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 2. Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

READ Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 5. Address Controlled, READ Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Figure 6. Chip Enable or Output Enable Controlled, READ Mode AC Waveforms . . . . . . . . . . . . . 6

Table 3. RE A D Mode AC Charac teristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

WRITE Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 7. WRITE Enable Controlled, WRITE Mode AC Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 8. Chip Enable Controlled, WRITE Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 4. WRITE Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Data Retention Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

V

Noise And Negative Going Transients. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

CC

Figure 9. Supply Voltage Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 5. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 6. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 10.AC Testing Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 7. Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 8. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 11.Power Down/Up Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 9. Power Down/Up AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Table 10. Power Down/Up Trip Points DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

PACKAGE MECHANICAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 12.PMDIP32 – 32-pin Plastic Module DIP, Package Outline . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 11. PMDIP32 – 32-pin Plastic DIP, Package Mechanical Data. . . . . . . . . . . . . . . . . . . . . . . 13

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 12.Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

REVISION HISTO RY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2/16

M48Z129Y*, M48Z129V

Table 13.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3/16

M48Z129Y*, M48Z129V

SUMMARY DESCRIPTION

The M48Z129Y/V ZEROPOWER® SRAM is a

1,048,576 bit non-volatile static RAM organized as

131,072 words by 8 bits. The device combines an

internal lithium battery, a CMOS SRAM and a control circuit in a plastic 32-pin DIP Module. The

M48Z129Y/V directly replaces industry standard

128K x 8 SRAM. It also provides the non-volatility

of FLASH without any requirement for special

WRITE timing or limitations on the number of

WRITEs that can be performed.

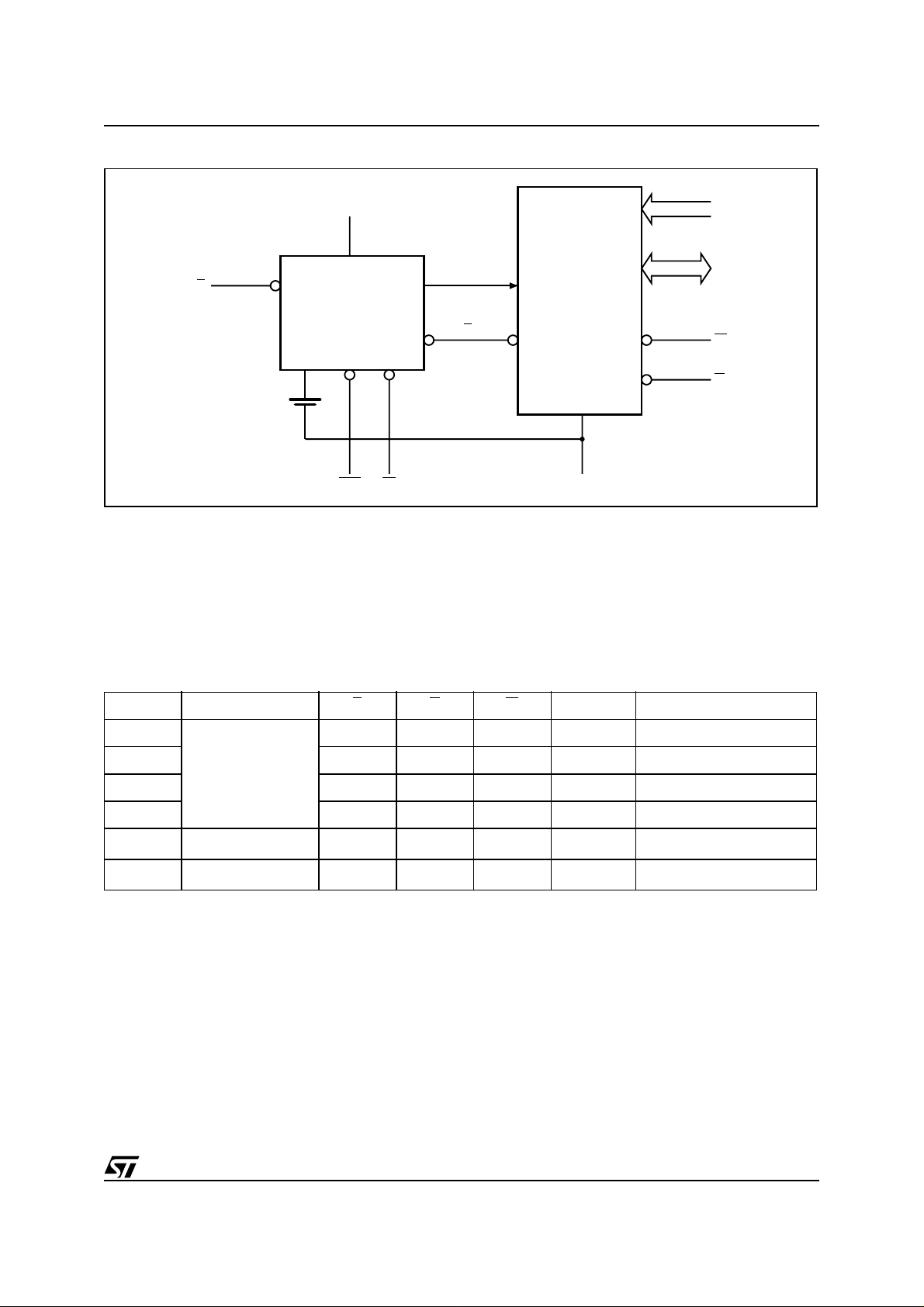

Figure 2. Logic Diagram Table 1. Signal Names

V

CC

17

8

A0-A16 DQ0-DQ7

W RST

M48Z129Y

M48Z129V

E

BL

G

V

SS

AI02309

A0-A16 Address Inputs

DQ0-DQ7 Data Inputs / Outputs

E

G

W

RST

BL

V

CC

V

SS

Chip Enable

Output Enable

WRITE Enable

Reset Output (Open Drain)

Battery Low Output (Open Drain)

Supply Voltage

Ground

Figure 3. DIP C on ne ctions

1

RST V

2

A16

A14

3

A12

4

5

A7

6

A6

7

A5

A4

8

M48Z129Y

A3

A2

A1

A0

DQ0

M48Z129V

9

10

11

12

13

14

DQ2

15

16

SS

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

AI02310

CC

A15

BL

W

A13

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5DQ1

DQ4

DQ3V

4/16

Figure 4. Block Diagram

M48Z129Y*, M48Z129V

V

CC

A0-A16

E

INTERNAL

BATTERY

VOLTAGE SENSE

AND

SWITCHING

CIRCUITRY

RST V

BL

OPERATION MODES

The M48Z129Y/V also has its own Power-Fail Detect circuit. This control circuitry constantly monitors the supply voltage for an out of tolerance

condition. When V

write protects the SRAM, providing data security in

Table 2. Operating Modes

Mode

Deselect

WRITE

READ

READ

Deselect

Deselect

Note: X = VIH or VIL; VSO = Battery B ack-up Switc hover Voltage.

1. See Table 10., page 12 for details.

VSO to V

is out of tolerance, the circuit

CC

V

CC

4.5 to 5.5V

or

3.0to 3.6V

(min)

PFD

(1)

≤ V

SO

(1)

E G W DQ0-DQ7 Power

V

IH

V

IL

V

IL

V

IL

X X X High Z CMOS Standby

X X X High Z Battery Back-up Mode

X X High Z Standby

X

V

V

POWER

E

131,072 x 8

SRAM ARRAY

SS

DQ0-DQ7

W

G

the midst of unpredictable system operation. A s

falls, the cont rol circuit ry automaticall y switch-

V

CC

es to the battery, maintaining data until valid power

is restored.

V

IL

IL

IH

V

IH

V

IH

D

IN

D

OUT

Active

Active

High Z Active

AI03608

5/16

Loading...

Loading...