STMicroelectronics M48T59, M48T59Y, M48T59V User Manual

5.0 or 3.3V, 64 Kbit (8 Kbit x8) TIMEKEEPER® SRAM

FEAT URES SUM MARY

■ INTEGRATED ULTRA LOW POWER SRAM,

REAL TIME CLOCK, POWER-FAIL

CONTROL CIRCUIT, AND BATTERY

■ FREQUENCY TEST OUTPUT FOR REAL

TIME CLOCK SOFTWARE CALIBRATION

■ AUTOMATIC POWER-FAIL CHIP

DESELECT AND WRITE PROTECT ION

■ WRITE PROTECT VOLTAGES

= Power-fail Deselect Voltage):

(V

PFD

– M48T59: V

4.5V ≤ V

– M48T59Y: V

4.2V ≤ V

– M48T59V*: V

2.7V ≤ V

■ SELF-CONTAINED BATTERY AND

CRYSTAL IN THE CAPHAT™ DIP

PACKAGE

■ PACKAGING INCLUDES A 28-LEAD SOIC

AND SNAPHAT

separately)

■ SOIC PACKAGE PROVIDES DIRECT

CONNECTION FOR A SNAPHAT TOP

WHICH CONTAINS THE BATTERY AND

CRYSTAL

■ MICROPROCESSOR POWER-ON RESET

(Valid even during battery back-up mode)

■ PROGRAMMABLE ALAR M OUTPUT

ACTIVE IN THE BATTERY BACK-UP MODE

■ BATTERY LOW FLAG

= 4.75 to 5.5V

CC

≤ 4.75V

PFD

= 4.5 to 5.5V

CC

≤ 4.5V

PFD

= 3.0 to 3.6V

CC

≤ 3.0V

PFD

®

TOP (to be ordered

M48T59

M48T59Y, M48 T5 9V *

Figure 1. 28-pin PCDIP, CAPHAT™ Package

28

1

PCDIP28 (PC)

Battery/Crystal

CAPHAT

Figure 2. 28-pi n S O I C Package

SNAPHAT (SH)

Battery/Crystal

28

1

SOH28 (MH)

* Contact local ST sales office for availability of 3.3V version.

1/29November 2004

M48T59, M48T59Y, M48T59V*

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. 28-pin PCDIP, CAPHAT™ Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 2. 28-pin SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 3. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 4. 28-pin SOIC Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 5. PCDIP28 CAPHAT Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 6. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

OPERATION MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 2. Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

READ Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 7. READ Mode AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 3. RE A D Mode AC Charac teristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

WRITE Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 8. WRITE Enable Controlled, WRITE Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . .8

Figure 9. Chip Enable Controlled, WRITE Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 4. WRITE Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Data Retention Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 0

CLOCK OPERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Reading the Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Setting the Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Stopping and Starting the Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 5. Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Calibrating the Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 10.Crystal Accuracy Across Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 11.Clock Calibration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Setting the Alarm Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 12.Alarm Interrupt Reset Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Table 6. A larm Repeat Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 13.Back-up Mode Alarm Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Power-on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Programmable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Battery Low Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Century Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Initial Power-on Defaults. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 7. Default Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

V

Noise And Negative Going Transients. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

CC

Figure 14.Supply Voltage Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2/29

M48T59, M48T59Y, M48T59V*

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 8. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 9. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 15.AC Measurement Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 10.Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 11.DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 16.Power Down/Up Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 12.Power Down/Up AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 13.Power Down/Up Trip Points DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

PACKAGE MECHANICAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 17.PCDIP28 – 28-pin Plastic DIP, battery CAPHAT, Package Outline . . . . . . . . . . . . . . . . 23

Table 14. PCDIP28 – 28-pin Plastic DIP, battery CAPHAT, Package Mechanical Data. . . . . . . . . 23

Figure 18.SOH28 – 28-lead Plastic Small Outline, battery SNAPHAT, Package Outline . . . . . . . . 24

Table 15. SOH28 – 28-lead Plastic Small Outline, battery SNAPHAT, Pack. Mech. Data . . . . . . . 24

Figure 19.SH – 4-pin SNAPHAT Housing for 48mAh Battery & Crystal, Package Outline . . . . . . . 25

Table 16. SH – 4-pin SNAPHAT Housing for 48mAh Battery & Crystal, Package Mech. Data. . . . 25

Figure 20.SH – 4-pin SNAPHAT Housing for 120mAh Battery & Crystal, Package Outline . . . . . . 26

Table 17. SH – 4-pin SNAPHAT Housing for 120mAh Battery & Crystal, Package Mech. Data. . . 26

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 18.Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 19.SNAPHAT Battery Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 20.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3/29

M48T59, M48T59Y, M48T59V*

SUMMARY DESCRIPTIO N

The M48T59/Y/V TIMEKEEPER® RAM is an

8 Kb x8 non-volatile static RAM and real time

clock. The monolithic chip is available in two special packages to provid e a highly integrated battery backed-up memory and real time clock

solution.

The M48T59/Y/V is a non-volatile pin and function

equivalent to any JEDEC standard 8 Kb x8 SRAM.

It also easi ly fits into many ROM, EPROM, and

EEPROM sockets, providing the non-volatility of

PROMs without any requirement for special write

timing or limitations on t he number of writes that

can be performed.

The 28-pin, 600mil DIP CAPHAT™ houses the

M48T59/Y/V silicon with a quartz crystal and a

long life lithium button cell in a single package.

The 28-pin, 330mil SOIC provides sockets with

gold plated contacts at bot h ends for direct connection to a separate SNAPHAT

®

housing con-

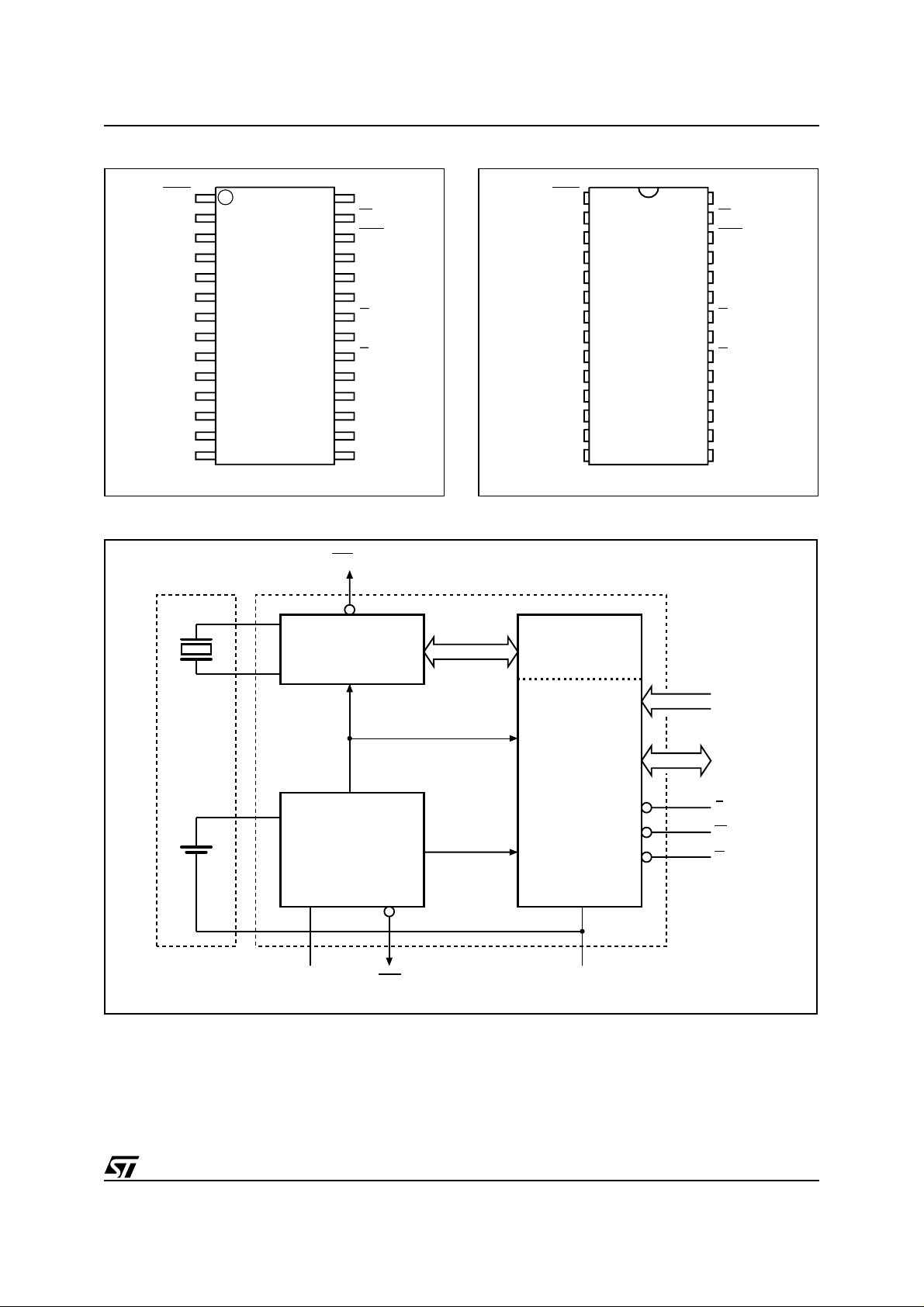

Figure 3. Logic Diagram Table 1. Signal Names

taining the battery and crystal. The unique design

allows the SNAPHAT battery package to be

mounted on top of the SOIC package after the

completion of the surface mount process. Insertion of the SNAPHAT housing after reflow prevents potential battery and c rystal dam age due to

the high temperatures required for device surfacemounting. The SNAPHAT housing is keyed to prevent reverse insertion.

The SOIC and battery/crystal packages are

shipped separately in plastic anti-static tubes or in

Tape & Reel form. For the 2 8-lead SOIC, t he ba ttery/crystal package (e.g., SNAPHAT) part number is “M4T28-BR12SH” or “M4T32-BR12SH”

(see Table 19., page 27).

Caution: Do not place the SNAPHAT battery/crystal top in conductive foam, as this will drain the lithium button-cell battery.

A0-A12

W

V

CC

13

M48T59

M48T59Y

E

G

M48T59V

V

SS

8

DQ0-DQ7

IRQ/FT

RST

AI01380E

A0-A12 Address Inputs

DQ0-DQ7 Data Inputs / Outputs

IRQ

RST

E

G

W

V

CC

V

SS

/FT

Interrupt / Frequency Test Output

(Open Drain)

Reset Output (Open Drain)

Chip Enable

Output Enable

Write Enable

Supply Voltage

Ground

4/29

M48T59, M48T59Y, M48T59V*

Figure 4. 28-pi n S O I C Co nnections Figure 5. PC DIP 28 CA P H A T Connectio ns

RST V

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

1

2

3

4

5

6

7

8

9

10

11

M48T59Y

M48T59V

12

DQ2

SS

13

14

Figure 6. Block Diagram

32,768 Hz

CRYSTAL

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AI01382E

OSCILLATOR AND

CLOCK CHAIN

CC

W

IRQ/FT

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5DQ1

DQ4

DQ3V

IRQ/FT

RST V

1

A12

2

A7

3

A6

4

A5

5

A4

6

A3

7

A2

8

A1

9

A0

10

DQ0

11

12

DQ2

13

14

SS

16 x 8 BiPORT

SRAM ARRAY

M48T59

M48T59Y

28

27

26

25

24

23

22

21

20

19

18

17

16

15

AI01381D

CC

W

IRQ/FT

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5DQ1

DQ4

DQ3V

A0-A12

LITHIUM

CELL

VOLTAGE SENSE

AND

SWITCHING

CIRCUITRY

CC

RSTV

POWER

V

PFD

8176 x 8

SRAM ARRAY

V

SS

DQ0-DQ7

E

W

G

AI01383D

5/29

M48T59, M48T59Y, M48T59V*

OPERATION MODES

As Figure 6., page 5 shows, the static memory array and the quartz-controlled clock oscillator of the

M48T59/Y/V are integrated on one silicon chip.

The two circuits are interconnected at the upper

eight memory locations to provide user accessible

BYTEWIDE™ clock information in t he bytes with

addresses 1FF8h-1FFFh. The clock locations

contain the century, year, month, date, day, hour,

minute, and second in 24 hour BCD format (except

for the century). Corrections for 28, 29 (l eap year valid until 2100), 30, and 31 day months are made

automatically. Byte 1FF8h is the clock control register. This byte controls user access to the clock

information and also stores the clock calibration

setting.

The eight clock bytes are not the actual clock

counters themselves; they are memory locations

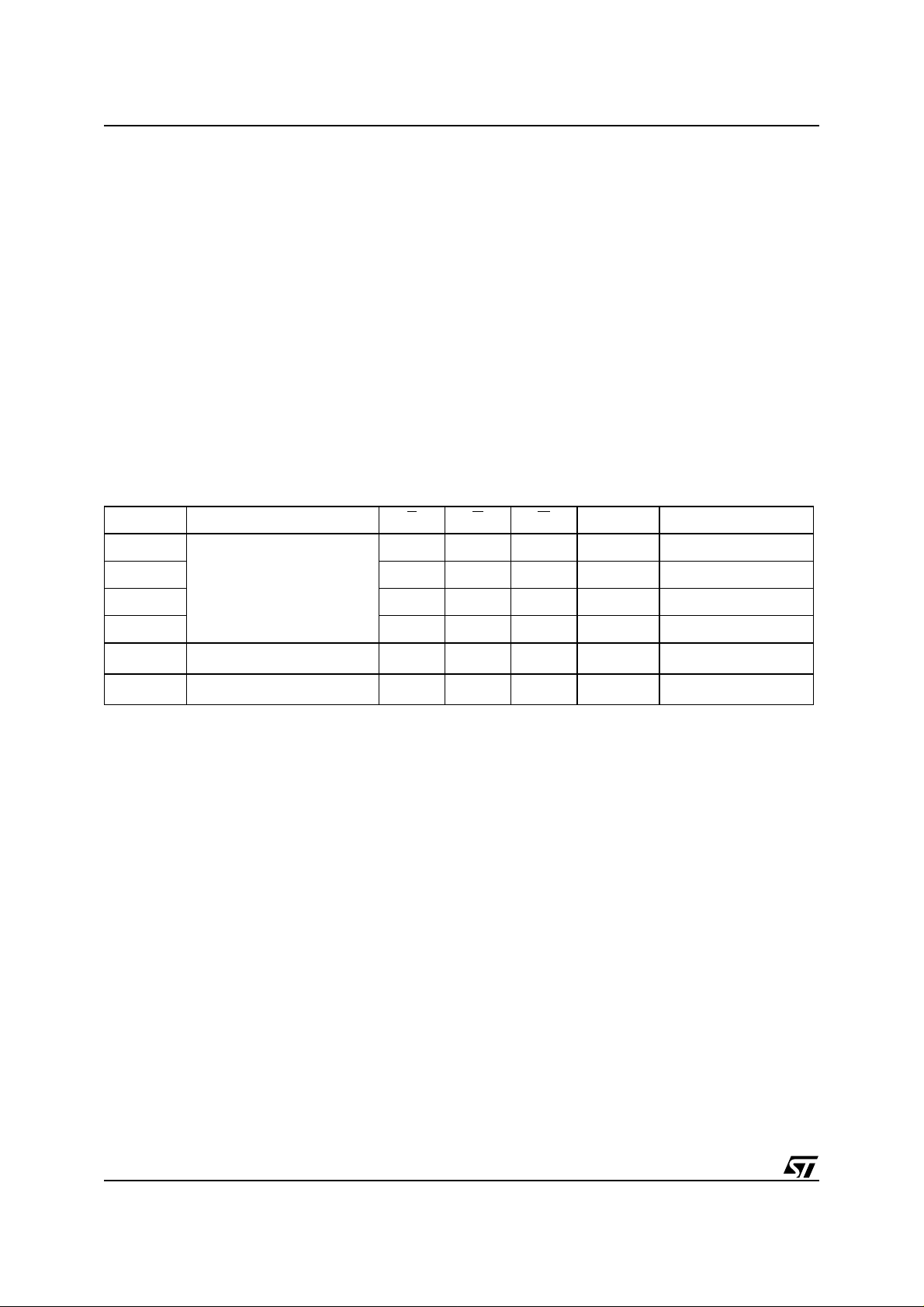

Table 2. Operating Modes

Mode

Deselect

WRITE

READ

READ

Deselect

Deselect

Note: X = VIH or VIL; VSO = Battery B ack-up Switc hover Voltage.

1. See Table 13., page 22 for details.

V

V

4.75 to 5.5V

4.5 to 5.5V

3.0 to 3.6V

to V

SO

PFD

≤ V

or

or

SO

CC

(min)

(1)

(1)

E G W DQ7-DQ0 Power

V

IH

V

IL

V

IL

V

IL

X X X High Z CMOS Standby

X X X High Z Battery Back-up Mode

consisting of BiPORT™ READ/WRITE memory

cells. The M48T59/Y/V includes a clock control circuit which updates the clock bytes with current information once per second. The information can

be accessed by the user in the same manner as

any other location in the static memory array.

The M48T59/Y/V also has its ow n Power-fail Detect circuit. The control circuitry constantly monitors the single 5V/3.3V supply for an out of

tolerance condition. When V

is out of tolerance,

CC

the circuit write protects the SRAM, providing a

high degree of data security in the midst of unpredictable system operation brought on by low V

As V

Voltage (V

falls below the Battery Back-up Switchover

CC

), the control circuitry connects the

SO

battery which maintains data and cloc k operation

until valid power returns.

X X High Z Standby

X

V

IL

V

IH

V

IL

V

IH

V

IH

D

IN

D

OUT

High Z Active

Active

Active

CC

.

6/29

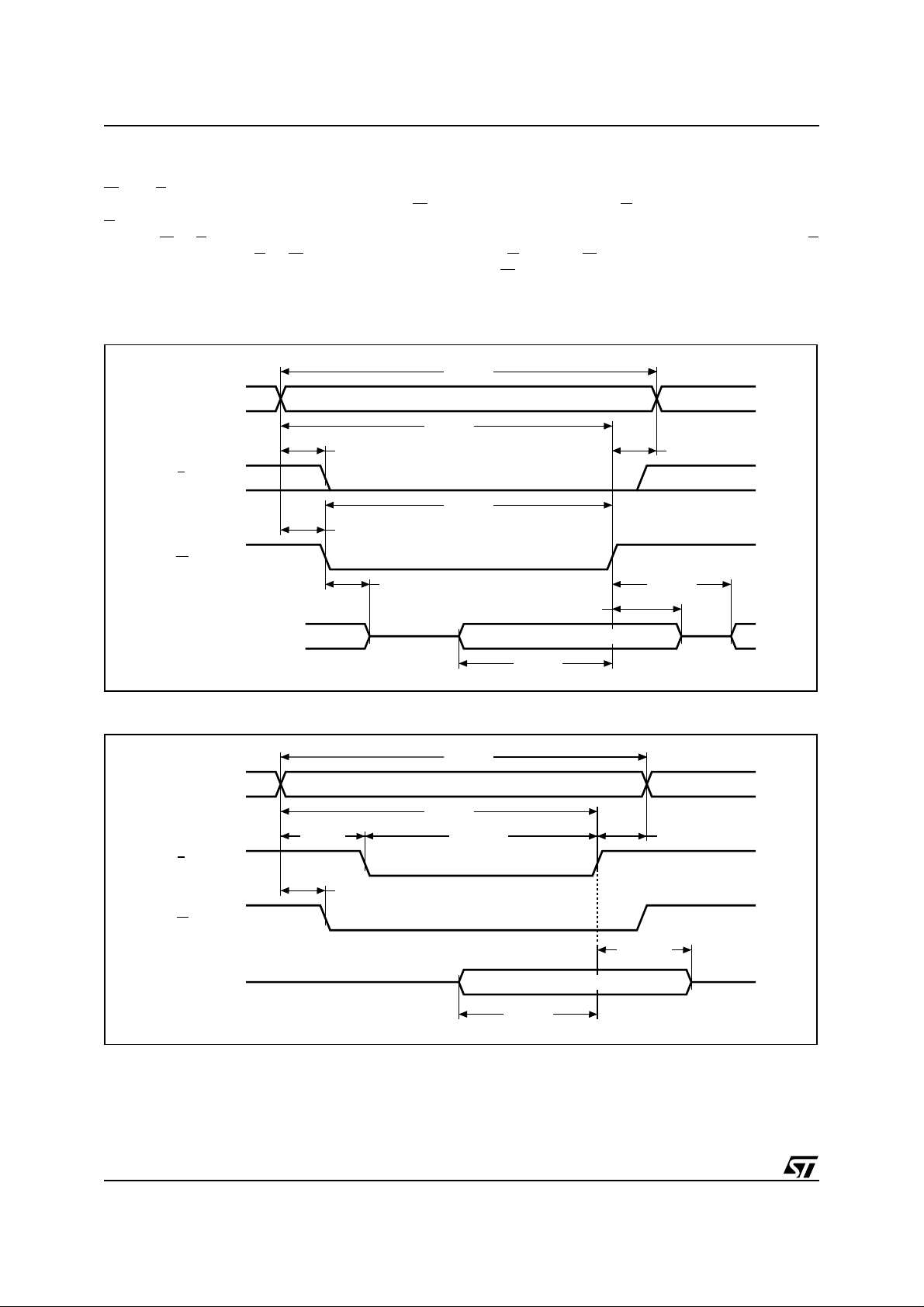

READ Mode

The M48T59/Y/V is in the READ M ode whenev er

(WRITE Enable) is high and E (Chip Enable) is

W

low. The unique address specified by the 13 address inputs defines which one of the 8,192 bytes

of data is to be acces sed . Vali d data w ill be av ailable at the Data I/O pi ns within Address Access

time (t

stable, providing that the E

are also satisfied. If the E

) after the last address input signal is

AVQV

and G access times

and G access times are

not met, valid data will be available after the latter

Figure 7. READ Mode AC Waveforms

M48T59, M48T59Y, M48T59V*

of the Chip Enable Access time (t

Enable Access time (t

GLQV

).

The state of the eight t hree-state Da ta I/O si gnals

is controlled by E

ed before t

indeterminate state until t

puts are changed while E

and G. If the outputs are activat-

, the data lines will be driven to an

AVQV

AVQV

and G remain active,

output dat a will re main valid for Ou tput D ata H old

time (t

) but will go indeterminate until the next

AXQX

Addr e ss Access.

tAVAV

ELQV

. If the Ad dres s In-

) or Output

A0-A12

tAVQV tAXQX

tELQV

E

tELQX

tGLQV

G

tGLQX

DQ0-DQ7

Note: W RITE Enable (W) = High.

VALID

tEHQZ

tGHQZ

VALID

AI01385

Table 3. READ Mode AC Characteristics

M48T59/Y/V

Symbol

t

AVAV

t

AVQV

t

ELQV

t

GLQV

t

ELQX

t

GLQX

t

EHQZ

t

GHQZ

t

AXQX

Note: 1. Valid for Ambient Operating Temperat ure: TA = 0 to 70°C; VCC = 4.5 to 5.5V, 4.7 5 to 5.5V, or 3.0 to 3.6V (except where noted) .

2. C

3. C

READ Cycle Time 70 ns

(2)

Address Valid to Output Valid 70 ns

(2)

Chip Enable Low to Output Valid 70 ns

(2)

Output Enable Low to Output Valid 35 ns

(3)

Chip Enable Low to Output Transition 5 ns

(3)

Output Enable Low to Output Transition 5 ns

(3)

Chip Enable High to Output Hi-Z 25 ns

(3)

Output Enable High to Output Hi-Z 25 ns

(2)

Address Transition to Output Transition 10 ns

= 100pF (see Figure 15 .,page 20).

L

= 5pF (see Figure 15., page 20).

L

Parameter

(1)

Unit–70

Min Max

7/29

M48T59, M48T59Y, M48T59V*

WRITE Mode

The M48T59/Y/V is in the WRITE Mode whenever

and E are low. The start of a WRITE is refer-

W

enced from the latter occurring falling edge of W

. A WRITE is terminated by the earlier rising

E

edge of W

throughout the cycle. E

a minimum of t

or E. The addresses must be held valid

or W must return high for

from Chip Enable or t

EHAX

or

WHAX

from WRITE Enable prior to the initiation of anoth-

Figure 8. WRITE Enable Controlled, WRITE Mode AC Waveforms

er READ or WRITE cycle. Data-in must be valid

t

for t

prior to the end of WRITE and remain valid

DVWH

afterward. G should be kept high during

WHDX

WRITE cycles to avoid bus contention; however, if

the output bus has b een activated by a low on E

and G a low on W will disable the outputs t

falls .

ter W

tAVAV

WLQZ

af-

A0-A12

tAVEL

E

tAVWL

W

tWLQZ

DQ0-DQ7

VALID

tAVWH

tWLWH

DATA INPUT

tDVWH

Figure 9. Chip Enable Controlled, WRITE Mode AC Waveforms

tAVAV

A0-A12

tAVEL

VALID

tAVEH

tELEH

tWHAX

tWHQX

tWHDX

AI01386

tEHAX

8/29

E

W

DQ0-DQ7

tAVWL

tDVEH

tEHDX

DATA INPUT

AI01387B

M48T59, M48T59Y, M48T59V*

Table 4. WRITE Mode AC Characteristics

M48T59/Y/V

Symbol

Parameter

(1)

Min Max

t

AVAV

t

AVWL

t

AVEL

t

WLWH

t

ELEH

t

WHAX

t

EHAX

t

DVWH

t

DVEH

t

WHDX

t

EHDX

(2,3)

t

WLQZ

t

AVWH

t

AVEH

(2,3)

t

WHQX

Note: 1. Valid for Ambient Operating Temperat ure: TA = 0 to 70°C; VCC = 4.5 to 5.5V, 4.7 5 to 5.5V, or 3.0 to 3.6V (except where noted) .

= 5pF (see Figure 15., page 20).

2. C

L

3. If E

WRITE Cycle Time 70 ns

Address Valid to WRITE Enable Low 0 ns

Address Valid to Chip Enable Low 0 ns

WRITE Enable Pulse Width 50 ns

Chip Enable Low to Chip Enable High 55 ns

WRITE Enable High to Address Transition 0 ns

Chip Enable High to Address Transition 0 ns

Input Valid to WRITE Enable High 30 ns

Input Valid to Chip Enable High 30 ns

WRITE Enable High to Input Transition 5 ns

Chip Enable High to Input Transition 5 ns

WRITE Enable Low to Output Hi-Z 25 ns

Address Valid to WRITE Enable High 60 ns

Address Valid to Chip Enable High 60 ns

WRITE Enable High to Output Transition 5 ns

goes low simultaneously with W going low , t he outputs remai n in the high impedance state.

Unit–70

9/29

Loading...

Loading...