Page 1

Automotive multiple power supply IC

GAPGPS00129

TQFP64 (exposed pad down)

Features

AEC-Q100 qualified

Full ISO26262 compliant, ASIL-D systems

ready

Integrated boost regulator, 9 V, 300 mA,

2 MHz (opt. populated diode & inductor) for

deep cranking pulse (Stop&Start) & weak

battery conditions

Integrated buck pre-regulator, 6.5 V / 7.2 V,

1 A, 465 kHz

Integrated LDO, 5 V, 250 mA for µC I/O and

ADC supply

Integrated configurable LDO, 3.3 V / 5 V,

100 mA for µC I/O supply

Configurable and programmable regulator with

external FET, 0.8 V to 5 V for µC core supply

– up to 1 A in buck configuration

– up to 750 mA in linear configuration

Spread spectrum approach to reduce EMC

emissions

Table 1. Device summary

L9396

Datasheet - production data

Four channels configurable remote sensor

interface

– wheel speed sensor protocol

– tracking regulator supply (3.3 V - 5 V)

– reverse battery protection and integrated

digital decoding

High-side pre-drivers for fail safe (On/off

control) and for motor pump (PWM control)

SPI communication bus

Configurable 3.3 V / 5 V I/O level

Configurable and programmable double

watchdog (Q&A WD and time-windowed WD)

Double voltage reference for regulated rail

reference and monitoring

Configurable Fail-Safe Functionality (Mode /

Safe Delay)

Fail-Safe Output (FSN)

Wake-up input

Low-side general purpose output with

programmable PWM control

Integrated 10-bits ADC with system

diagnostics

Discrete analog inputs for integrated ADC

measurement (3 ch.)

Voltage monitoring UV/OV on all regulated rails

Temperature monitoring and thermal shutdown

Operating voltage: VBATP: 4.5 V to 19 V with

boost; 6 V to 19 V without boost

Ambient temperature range: -40 °C to 135 °C

Package: TQFP64EP (10x10x1mm)

Order code Package Packing

L9396

November 2020 DS12539 Rev 3 1/109

This is information on a product in full production.

TQFP64 10 x 10 x 1 mm

(exposed pad down)

Tube

www.st.com

Page 2

Contents L9396

Contents

1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 Overall description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

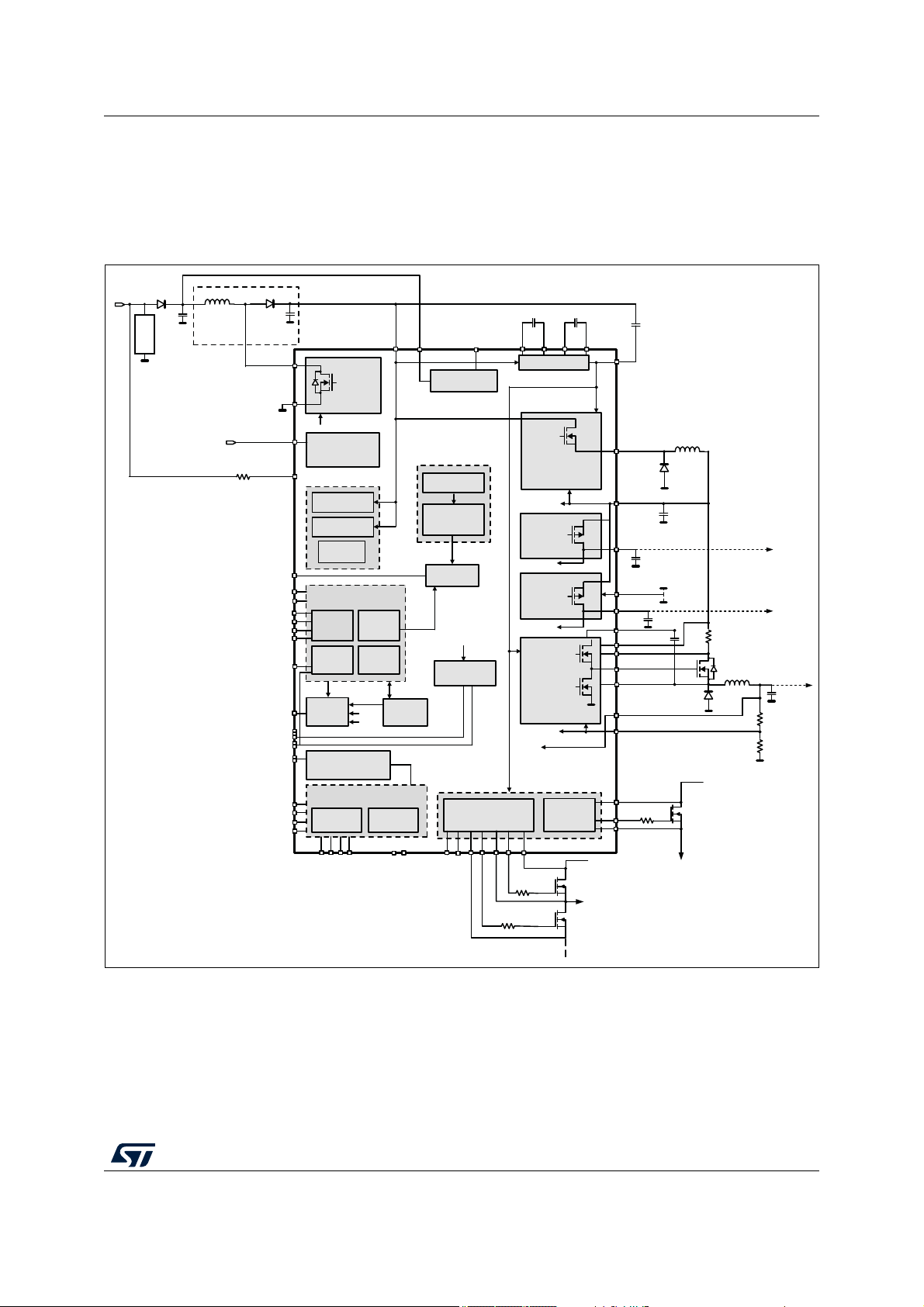

2.1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

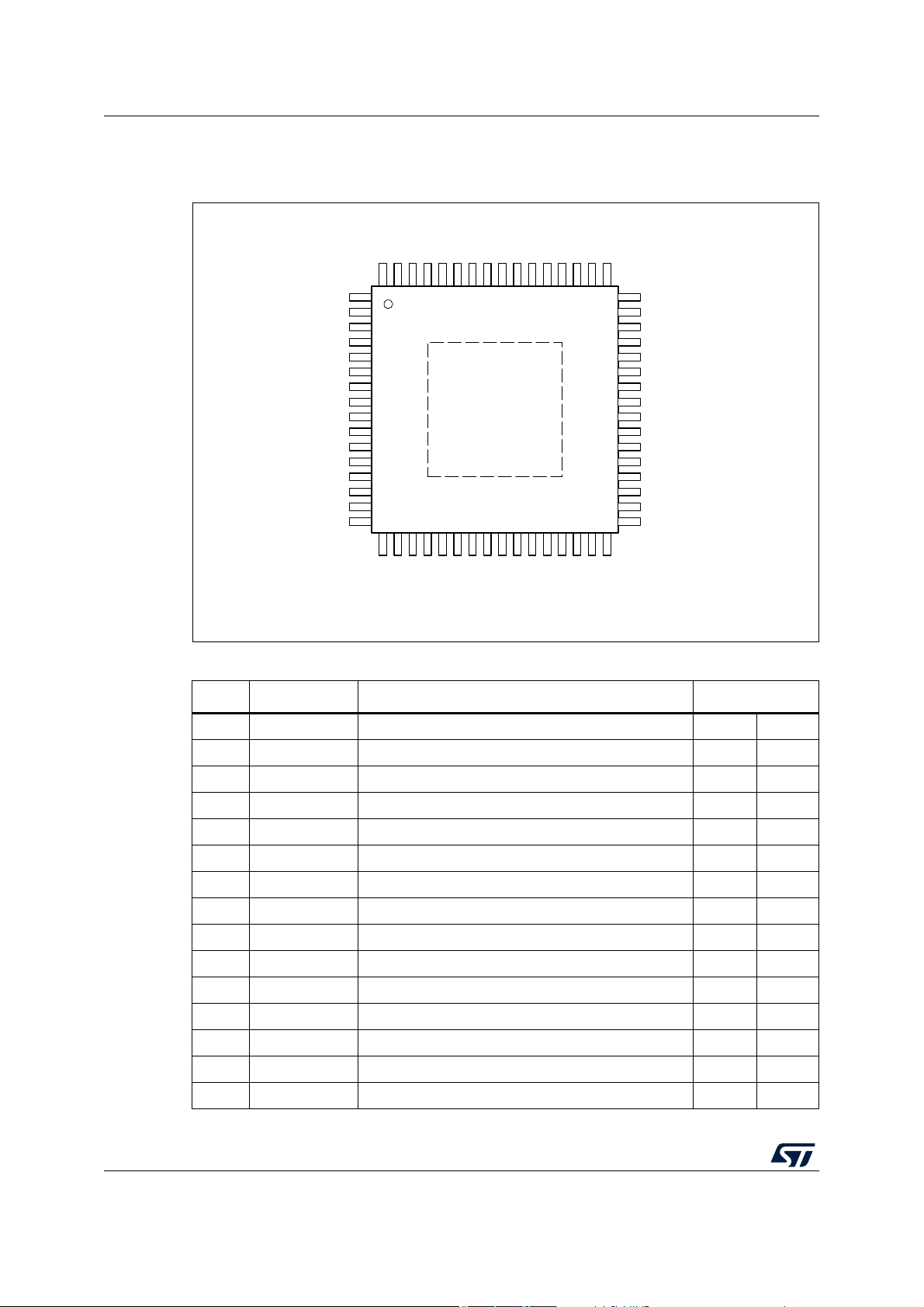

2.2 Pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.4 Operating range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3 Power supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.1 Battery range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.2 Boost regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.3 Internal supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.4 Wake-up input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.5 Charge pump . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.6 VPREREG buck regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.7 VCORE regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.8 VCC5 regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.9 VCC regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.10 Protected battery switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.11 Power up and power down sequences . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4 Pre-drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.1 Fail safe pre-driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2 Pump motor pre-driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3 Pump motor diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5 Remote sensor interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.1 Active wheel speed sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.1.1 Wheel speed data register formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.1.2 Testmode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.1.3 Wheel Speed SPI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.2 Tracking regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

2/109 DS12539 Rev 3

Page 3

L9396 Contents

5.3 Remote sensor interface fault protection . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

6 General purpose output (GPO) driver . . . . . . . . . . . . . . . . . . . . . . . . . . 62

7 System functional safety implementations . . . . . . . . . . . . . . . . . . . . . 64

7.1 General functional safety implementations . . . . . . . . . . . . . . . . . . . . . . . 64

7.2 System monitoring and reset handling . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

7.2.1 Analog to Digital algorithmic converter . . . . . . . . . . . . . . . . . . . . . . . . . 64

7.2.2 Voltage measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

7.2.3 Reset output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

7.2.4 Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

7.3 Fault output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

7.4 Watchdog control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

7.4.1 Watchdog (WD1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

7.4.2 Second Watchdog (WD2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.4.3 Watchdog Timer Disable Input (WDTDIS) . . . . . . . . . . . . . . . . . . . . . . . 84

7.5 Fail safe output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.6 Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

7.7 Over temperature protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

7.8 Bist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

7.8.1 Logic Bist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

7.8.2 Analog Bist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

7.8.3 OTP check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

8 Serial Peripheral Communication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

8.1 CRC Field Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

8.2 SPI frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

8.3 SPI registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

8.4 SPI parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

8.4.1 DC Electrical Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

8.4.2 AC electrical parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

9 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

9.1 TQFP64 (10x10x1 mm exp. pad down) package information . . . . . . . . 104

9.2 TQFP64 (10x10x1 mm exp. pad down) marking information . . . . . . . . . 107

DS12539 Rev 3 3/109

4

Page 4

Contents L9396

10 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

4/109 DS12539 Rev 3

Page 5

L9396 List of tables

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. Pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 3. Pin absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 4. Pin operating range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 5. Configuration and control DC specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 6. Boost regulator electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 7. Internal supply electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 8. Wake-up input electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 9. Charge pump electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 10. VPREREG buck regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 11. Vcore configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 12. VCORE regulator electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 13. VCC5 regulator electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 14. VCC regulator electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 15. Protected battery switch electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 16. Power up and power down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 17. Fail Safe pre-driver electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 18. Logical operation definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 19. Pump motor diagnostics electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 20. WSS_TEST register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 21. WSS_TEST register bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 22. RS_CFG_0_1 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 23. RS_CFG_0_1 register bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 24. RS_CFG_2_3 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 25. RS_CFG_2_3 register bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 26. RS_CTRL register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 27. RS_CTRL register bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 28. RS_AUX_CFG register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 29. RS_AUX_CFG register bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 30. RS_DATA_RSDR_0-3 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 31. RS_DATA_RSDR_0-3 registers bit description [Bit 15 = 0] . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 32. RS_DATA_RSDR_0-3 registers bit description [Bit 15 = 1] . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 33. RS_DATA_RSDR_4-7 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 34. RS_DATA_RSDR_4-7 registers bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 35. RS_DATA_RSDR_8-11 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 36. RS_DATA_RSDR_8-11 registers bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 37. RS_DATA_RSDR_12 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 38. RS_DATA_RSDR_12 register bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 39. RSU_STATUS register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 40. RSU_STATUS register bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 41. WSS configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 42. Tracking regulation configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 43. Assignment matrix configured via SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 44. GPO electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 45. Analog to digital converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 46. Conversion time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 47. Divider ratios vary by measurement are summarized by function . . . . . . . . . . . . . . . . . . . 66

Table 48. Voltage measurement electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

DS12539 Rev 3 5/109

6

Page 6

List of tables L9396

Table 49. Reset electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 50. Oscillator electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 51. Masking bits and fault sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 52. Fault characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 53. Description of the timing parameter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 54. WD2 characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 55. WDTDIS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 56. Masking bits and fault sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 57. Fail safe output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 58. Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 59. Logic Bist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 60. Registers summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 61. DC electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 62. SPI timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 63. TQFP64 (10x10x1 mm exp. pad down) package mechanical data . . . . . . . . . . . . . . . . . 105

Table 64. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

6/109 DS12539 Rev 3

Page 7

L9396 List of figures

List of figures

Figure 1. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 2. Pins connection diagram (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 3. Boost regulator block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 4. Charge pump block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 5. VCORE configuration diagram (buck regulator - top, linear regulator - bottom) . . . . . . . . . 27

Figure 6. Power up sequence from wake up input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 7. Power down sequence from wake up input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 8. Standstill operation diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 9. Wheel speed sensor protocol types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 10. ADC conversion time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 11. Reset input logic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 12. Reset output logic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 13. WD1 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 14. Mono-directional timing check evolution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 15. Bidirectional timing check evolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 16. Timing State evolution depending on WD_TO_RST_EN and WD_REQ_CHECK_EN . . . 74

Figure 17. WD1 state machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 18. WD1_RESET & DRIVERS ENABLE versus WD_CNT value. . . . . . . . . . . . . . . . . . . . . . . 76

Figure 19. Seed generation algorithm block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 20. Seed selection and elaboration flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 21. Answer check generation algorithm block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 22. WD2 timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 23. WD2 diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 24. GSW[8..0] bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Figure 25. SPI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Figure 26. TQFP64 (10x10x1 mm exp. pad down) package outline . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 27. TQFP64 (10x10x1 mm exp. pad down) marking information . . . . . . . . . . . . . . . . . . . . . . 107

DS12539 Rev 3 7/109

7

Page 8

Description L9396

1 Description

The L9396 is an integrated power management System Basis Chip targeting a large

spectrum of automotive electronics applications, in particular ABS, EPS and Transmission,

compatible with single (12

It combines a switched mode power supply for pre-regulation along with 3 independent

integrated linear regulators and a powerful configurable regulator for µC supply that can

operate either in buck or linear mode with an external FET.

The device also integrates a 4-channel flexible interface for Wheel Speed Sensor or tracking

regulation, 2 configurable pre-drivers for fail safe and motor pump, 1 configurable general

purpose outputs, wake-up detection circuitry, advanced fail-safe functionality, watchdog

control and system monitoring.

The boost regulator (optionally enabled) is intended to sustain cold cranking pulses,

stop

& start and weak battery conditions, while the buck pre-regulator drastically improves

the power efficiency and CO2 emissions.

Different combinations enable to supply the system microcontroller and external peripheral

loads and sensors with wide current ranges and adjustable voltage levels.

In addition, the L9396 provides enhanced system standby functionalities.

V) battery system.

8/109 DS12539 Rev 3

Page 9

L9396 Overall description

FAULT

WDTDIS

Voltage Monitor

UV / OV

Wake-up Monitor

IGN

Boost

Controller

9V

300mA

2MHz

GNDBST

BSTSW

VM_OUT

VBG Reference

& Monitor

VBM

VBST

CP

GNDA

Reset

RESET

VM_OUT

WD_OUT

Control & Logic Blocks

SPI

Control &

Status Reg.

Temperature

Monitoring

Operating

Modes

Fail-Safe

Operation

FSN

Watchdog

CSN

SDI

SDO

CLK

WD_OUT

VM_OUT

TSD_OUT

Internal analog

3V3 supply

Internal digital

3V3 supply

POR & Osc.

BCKSW

VPREREG

VCC5

VCC

VCCSEL

Volt. Mon.

VCOREFDBK

Fail Safe FET

HS pre driver

(On/Off control)

Pump Motor FET

HS pre driver

(PWM control)

PDS

VDBATT

WSS / Tracking regulation Interface

RSU0H/L

WSO0

WSO1

WSO2

WSO3

AI[2/3/4]

HV Mux +

ADC Converter

Battery protected

switch

VB

VB_SW

KL30

KL15

Boost

components

option .

populated

2.2uH

22uH

‘1’

‘0’

Decoding

uC I/O supply

GCORE

VC1

VC2

Transient

Protection

VBATP

VBATP

PDG

VDS

VBATP

VDG

SCORE

System

Voltages

LS GPO driver

(PWM control)

GPOD0

Voltage

regulation

VC3

VC4

I_CORE_SH

I_CORE_SL

uC I/O & ADC

supply

VCORE

PRN

RSU1H/L

RSU2H/L

RSU3H/L

PRS

PRG

PRI

PDI

PDBATT

Volt. Mon.

AI[0/1]

GNDD

CBS

GADG1801171059PS

Lin with ext. FET

500 mA

0.8 V / 5.0 V

Buck with ext. FET

1 A

0.8 V / 5.0 V

(μC Core)

VCORE Regulator

I/O ref

Volt. Mon.

Volt. Mon.

WSS/Tracking IF

Volt. Mon.

100 mA

3.3 V / 5.0 V

(μC I/O)

LDO VCC

250 mA

5.0 V

(μC I/O & ADC)

LDO VCC5

465 kHz

1000 mA

6.5 V / 7.2 V

Controller

Buck

Charge Pump

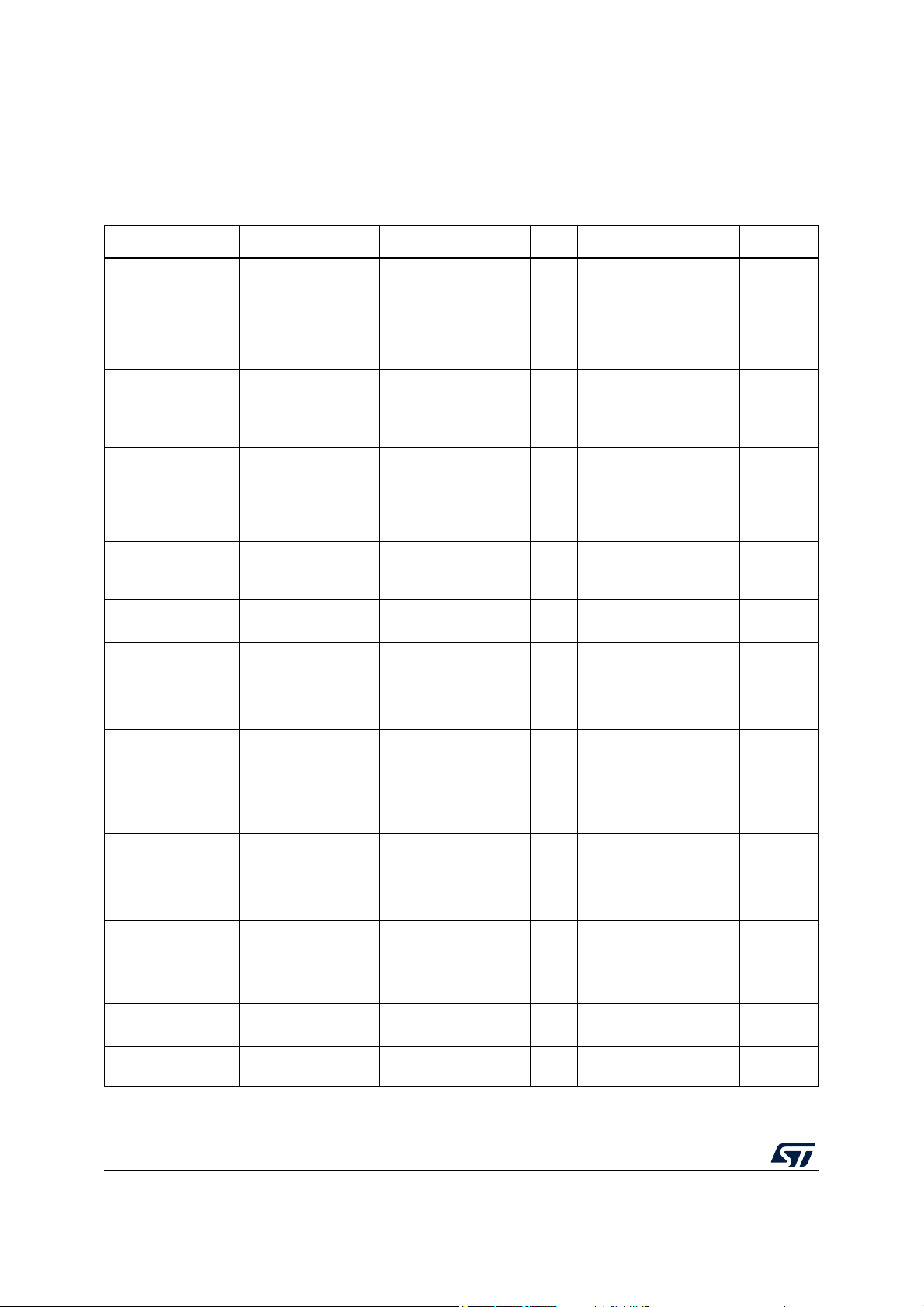

2 Overall description

2.1 Block diagram

Figure 1. Block diagram

DS12539 Rev 3 9/109

108

Page 10

Overall description L9396

49

50

51

52

53

54

55

56

57

58

59

60

WSO0

61

62

WSO2

63

WSO3

WSO1CSPRN

CLK

SDI

SDO

GNDDNUGNDBST

BSTSW

FSN

RESET

AI4

AI3

AI2

AI1

AI0

RSUL0

RSUH0

RSUL1

RSUH1

RSUL2

RSUH2

RSUL3

RSUH3

GNDA

GPOD0

PDI

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

VC1

47

VC2

VC3

VC4

46

45

44

CP

VBST

BCKSW

VCCSEL

VCC5

VCC

I_CORE_SH

I_CORE_SL

CBS

GCORE

SCORE

VPREREG

43

42

41

40

39

38

37

36

35

34

33

VCORE

VCOREFDBK

IGN

VBM

WDTDIS

VDS

VDG

VDBATT

VB

VB_SW

PDBATT

PDS

PDG

PRS

PRG

PRI

181920212223242526272829303132

17 64

FAULT

GADG1801171148PS

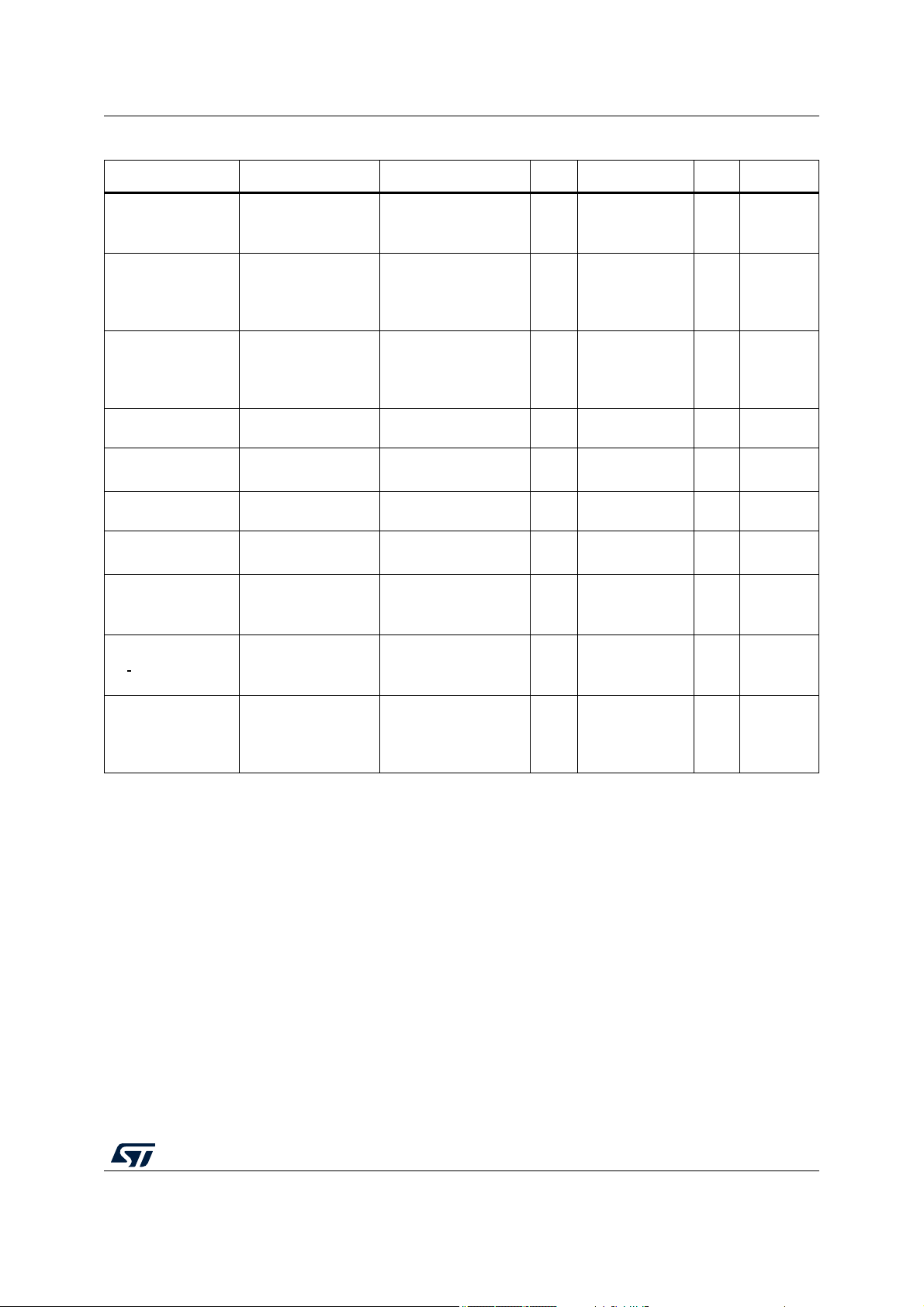

2.2 Pins description

Figure 2. Pins connection diagram (top view)

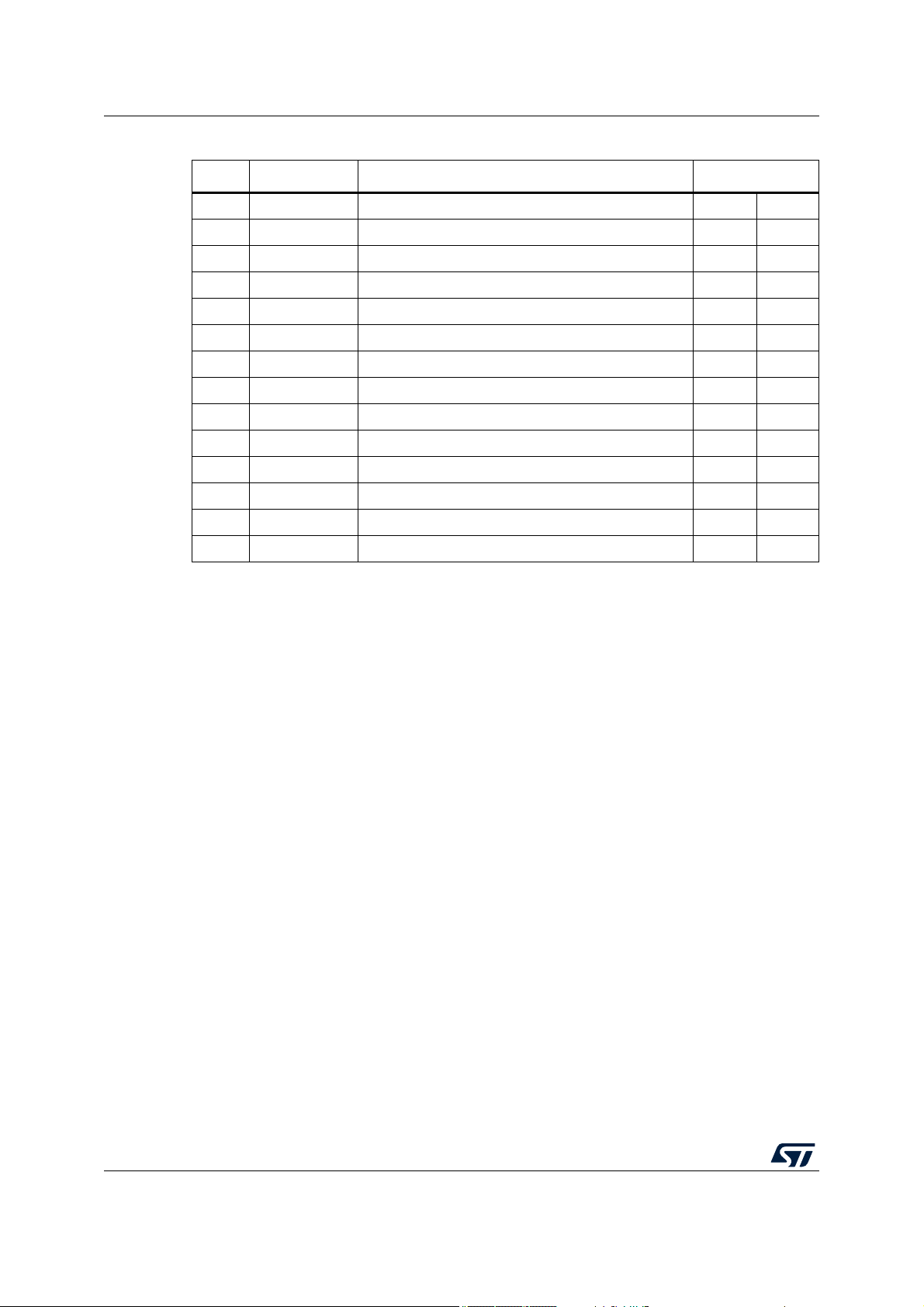

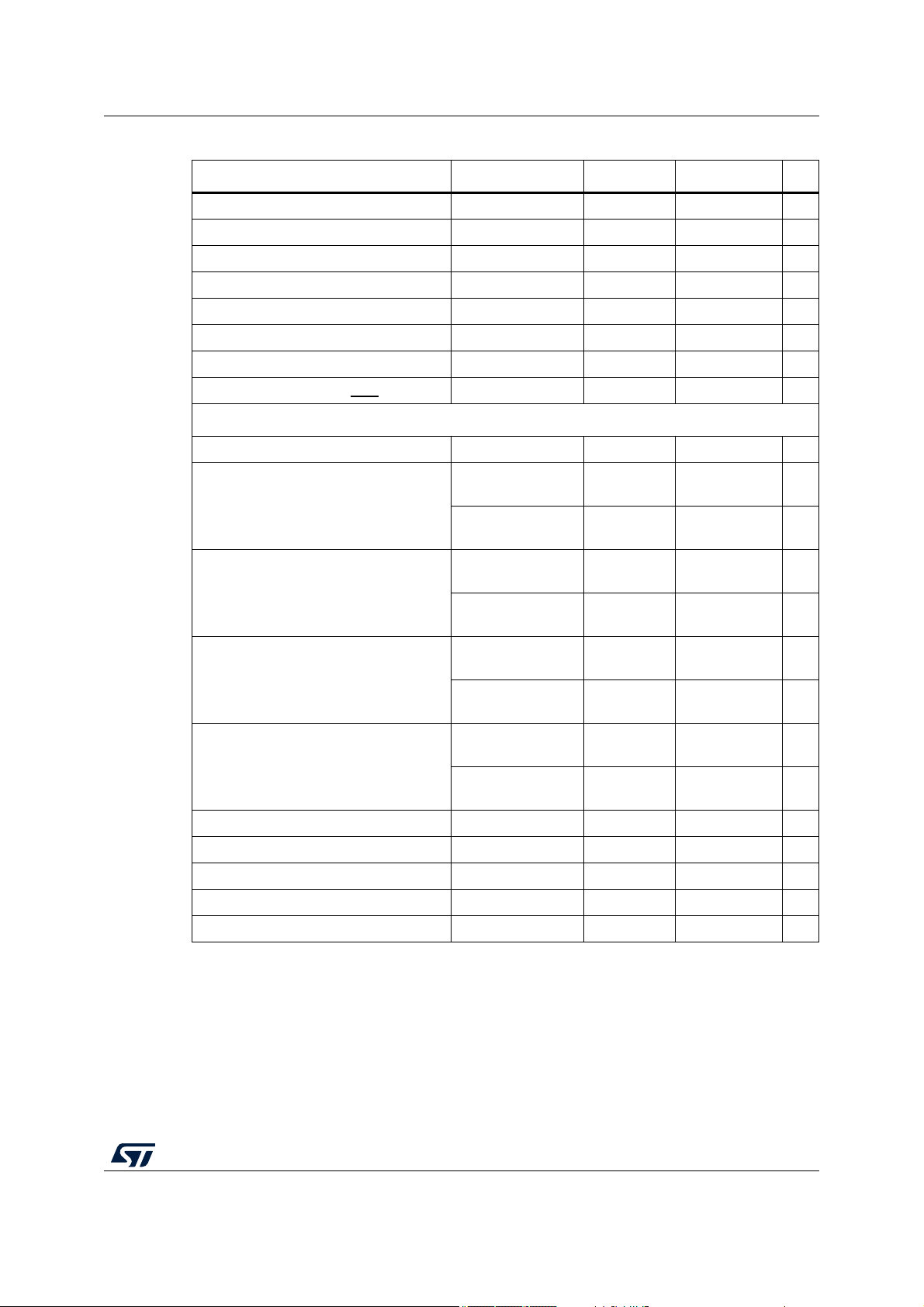

Table 2. Pins description

Pin Name Description Pin type

1 AI4 Analog input to ADC converter I Local

2 AI3 Analog input to ADC converter I Local

3 AI2 Analog input to ADC converter I Local

4 AI1 Input 1 to select VCORE function I Local

5 AI0 Input 0 to select VCORE function I Local

6 RSUL0 WSS ground return I/O Global

7 RSUH0 WSS / tracking regulated output I/O Global

8 RSUL1 WSS ground return I/O Global

9 RSUH1 WSS / tracking regulated output I/O Global

10/109 DS12539 Rev 3

10 RSUL2 WSS ground return I/O Global

11 RSUH2 WSS output I/O Global

12 RSUL3 WSS ground return I/O Global

13 RSUH3 WSS output I/O Global

14 GNDA Analog ground Supply Local

15 GPOD0 GPO driver drain terminal I/O Global

Page 11

L9396 Overall description

Table 2. Pins description (continued)

Pin Name Description Pin type

16 PDI Motor Pump HS FET control pin I Local

17 PRI Motor Pump recirculation FET control pin I Local

18 PRG Motor Pump recirculation FET gate control O Local

19 PRS Motor Pump recirculation FET source pin I Local

20 PDG Motor Pump HS FET gate control O Local

21 PDS Motor Pump HS FET source pin I Local

22 PDBATT Battery sense for Motor Pump FET pre-driver I Global

23 VB_SW Battery protected output I/O Local

24 VB Battery line input Supply Global

25 VDBATT Battery sense for Fail Safe FET pre-driver I Global

26 VDG Fail Safe FET gate control O Local

27 VDS Fail Safe FET source pin I Local

28 WDTDIS Watchdog disable I Local

29 VBM Battery sense I Local

30 IGN Wake up pin for battery connection I Global

31 VCOREFDBK VCORE voltage feedback I Local

32 VCORE µC core voltage supply I Local

33 SCORE Source pin for VCORE regulator external FET I/O Local

34 GCORE Gate control for VCORE regulator external FET I/O Local

35 CBS VCORE bootstrap capacitor I/O Local

36 I_CORE_SL Shunt input for current sensing on VCORE regulator I Local

37 I_CORE_SH Shunt input for current sensing on VCORE regulator I Local

38 VCC 3.3 V / 5 V µC I/O supply Supply Local

39 VCC5 5 V µC I/O and ADC supply O Local

40 VPREREG Pre-regulator output Supply Local

41 VCCSEL Voltage selection for VCC regulator I Local

42 BCKSW Switched pre-regulator output I/O Local

43 VBST Device battery line input or boost regulated output Supply Global

44 CP Charge pump output Supply Local

nd

45 VC4 Charge pump 2

46 VC3 Charge pump 2

47 VC2 Charge pump 1

48 VC1 Charge pump 1

cap high terminal I/O Local

nd

cap low terminal I/O Local

st

cap high terminal I/O Local

st

cap low terminal I/O Local

49 RESET Reset output pin O Local

50 FSN Fail safe negated digital output O Local

DS12539 Rev 3 11/109

108

Page 12

Overall description L9396

Table 2. Pins description (continued)

Pin Name Description Pin type

51 BSTSW Switched boost regulator output I/O Local

52 GNDBST Boost regulator ground Supply Local

53 NU Not used. To be connected to ground voltage. I Local

54 GNDD Digital Ground Supply Local

55 SDO SPI data digital output O Local

56 SDI SPI data digital input I Local

57 CLK SPI clock I Local

58 PRN MCU clock signal I/O Local

59 CS Chip select digital input I Local

60 WSO0 WSS pass-through output O Local

61 WSO1 WSS pass-through output O Local

62 WSO2 WSS pass-through output O Local

63 WSO3 WSS pass-through output O Local

64 FAULT General fault output O Local

12/109 DS12539 Rev 3

Page 13

L9396 Overall description

2.3 Absolute maximum ratings

Within the maximum ratings, no damage to the component shall occur. Exposure to

absolute maximum rated conditions for extended periods may affect device reliability.

All maximum ratings can occur at the same time.

All analog and digital voltages are related to the potential at substrate ground GNDA.

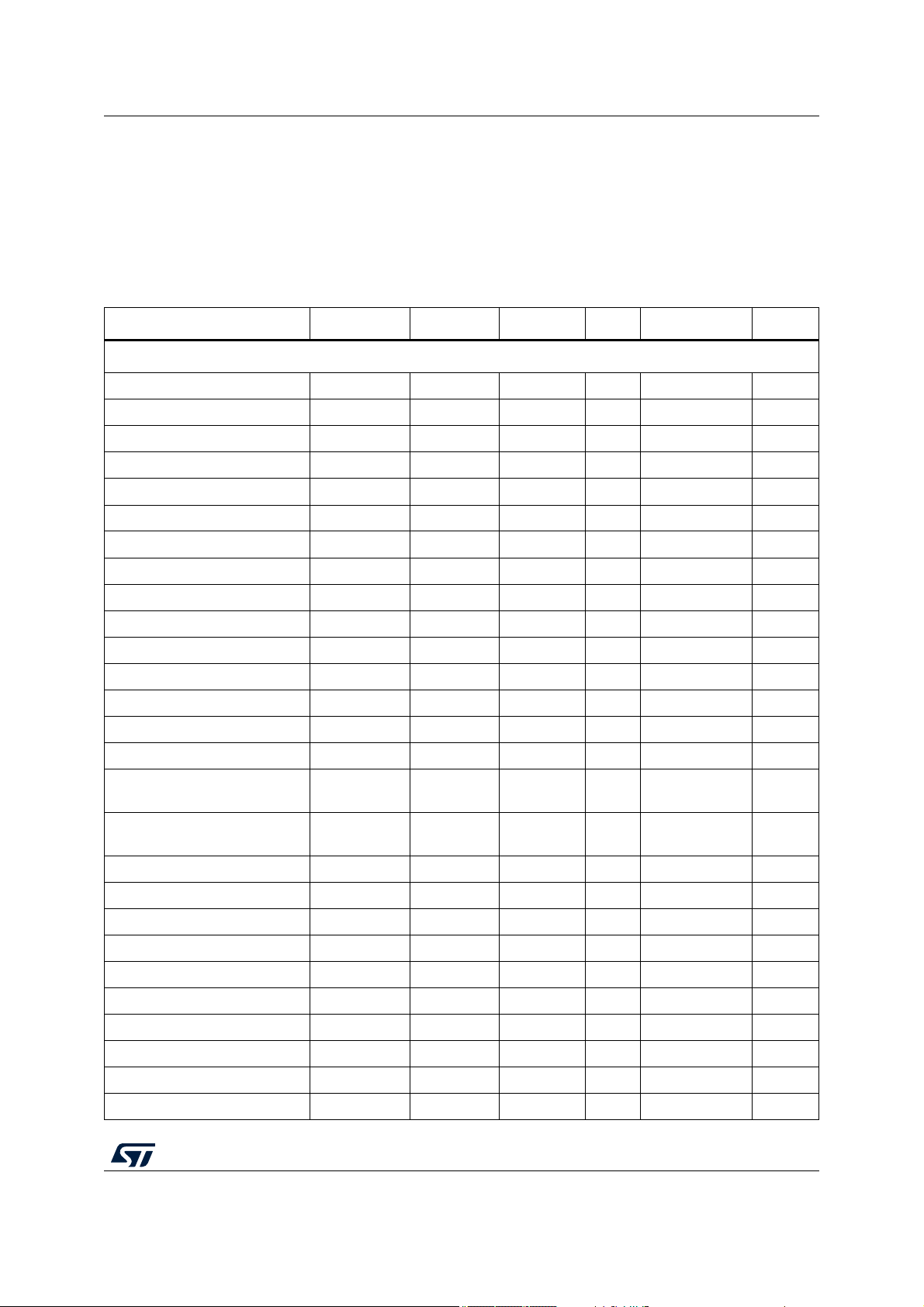

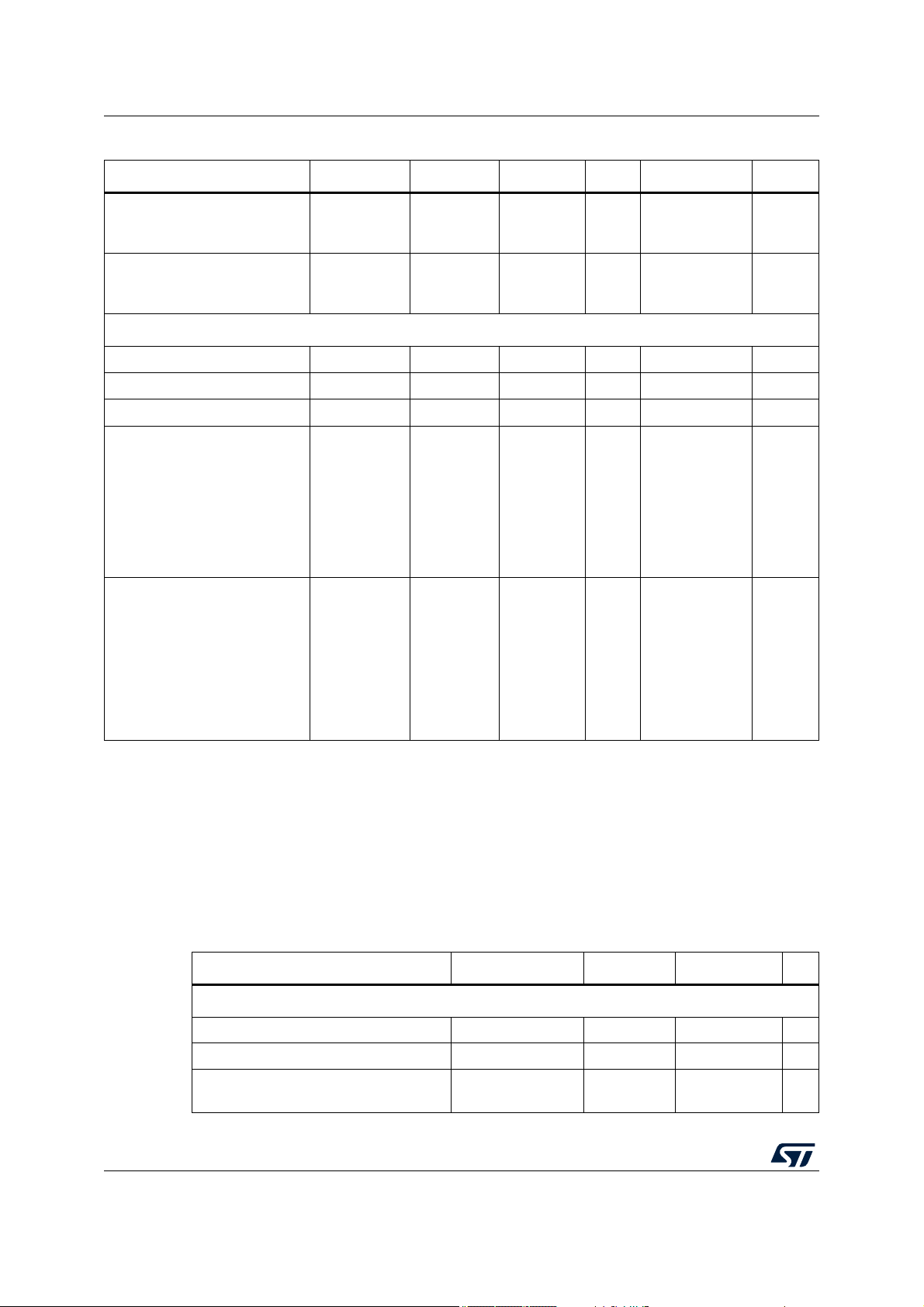

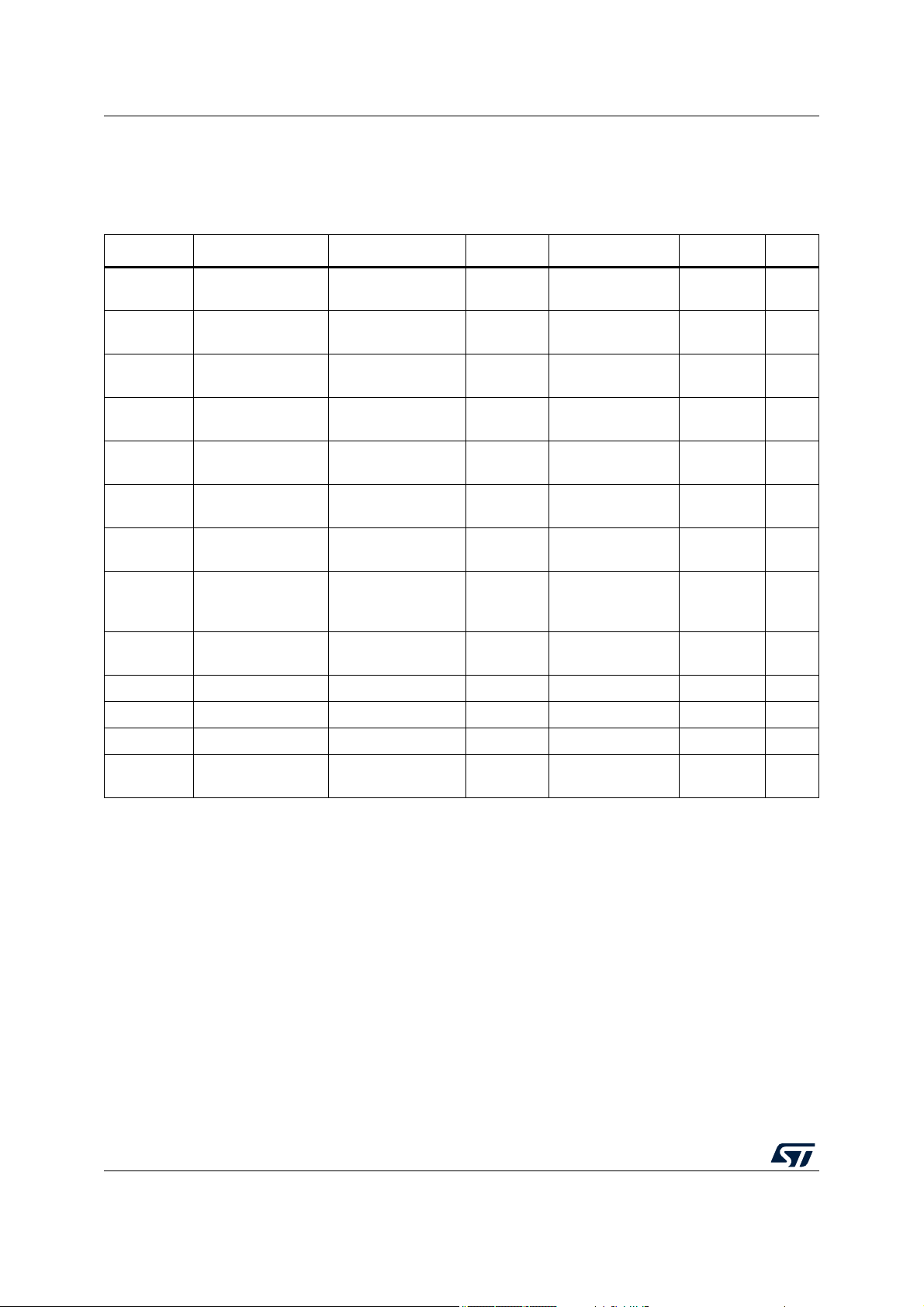

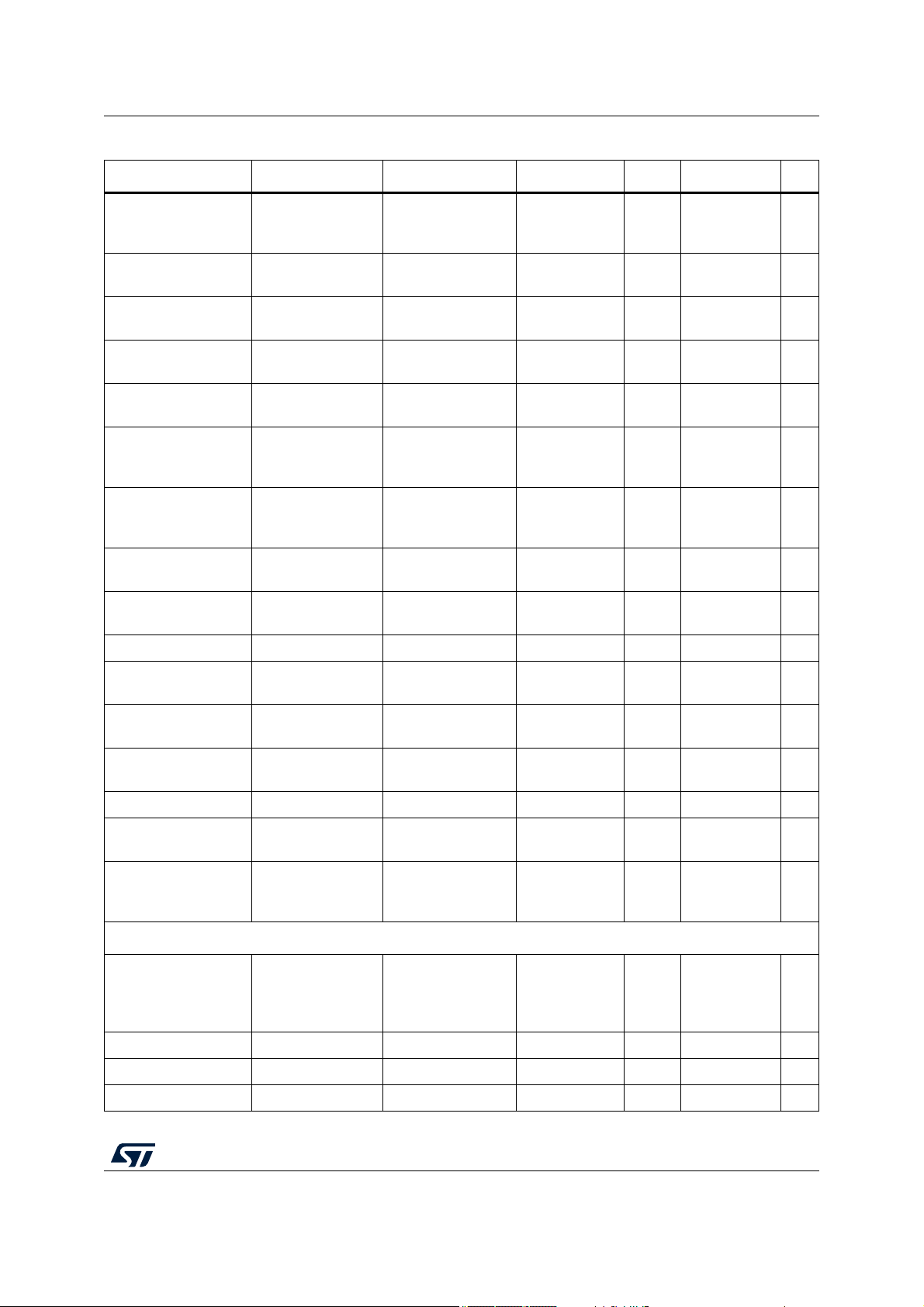

Symbol Parameter Condition Min Typ Max Unit

Power Supply

ABS_VB - - -0.3 - 40 V

ABS_VBST - - -0.3 - 40 V

ABS_VBM - - -0.3 - 40 V

ABS_VB_SW - - -18 - 40 V

ABS_BSTSW - - -0.3 - 40 V

ABS_VPREREG - - -0.3 - 40 V

ABS_I_CORE_SH - - -0.3 - 40 V

ABS_I_CORE_SL - - -0.3 - 40 V

Table 3. Pin absolute maximum ratings

ABS_BCKSW - - -1 - 40 V

ABS_SCORE - - -1 - 40 V

ABS_VC4 - - VBST-0.6 - VBST+13 ≤ 51 V

ABS_VC2 - - VBST-0.3 - VBST+13 ≤ 51 V

ABS_CP - - VBST-0.3 - VBST+13 ≤ 51 V

ABS_VC1 - - -0.3 - 40 V

ABS_VC3 - - -0.3 - 40 V

ABS_CBS - - -0.3 -

ABS_GCORE - - -0.3 -

ABS_NU - - -0.3 - 4.6 V

ABS_VCC5 - - -0.3 - 40 V

ABS_VCC - - -0.3 - 40 V

ABS_VCOREFDBK - - -0.3 - 40 V

ABS_VCORE - - -0.3 - 40 V

ABS_VCCSEL - - -0.3 - 40 V

ABS_IGN - - -0.3 - 40 V

SCORE+

20≤40

SCORE+

20≤40

V

V

ABS_GNDA - - -0.3 - 0.3 V

ABS_GNDD - - -0.3 - 0.3 V

ABS_GNDBST - - -0.3 - 0.3 V

DS12539 Rev 3 13/109

108

Page 14

Overall description L9396

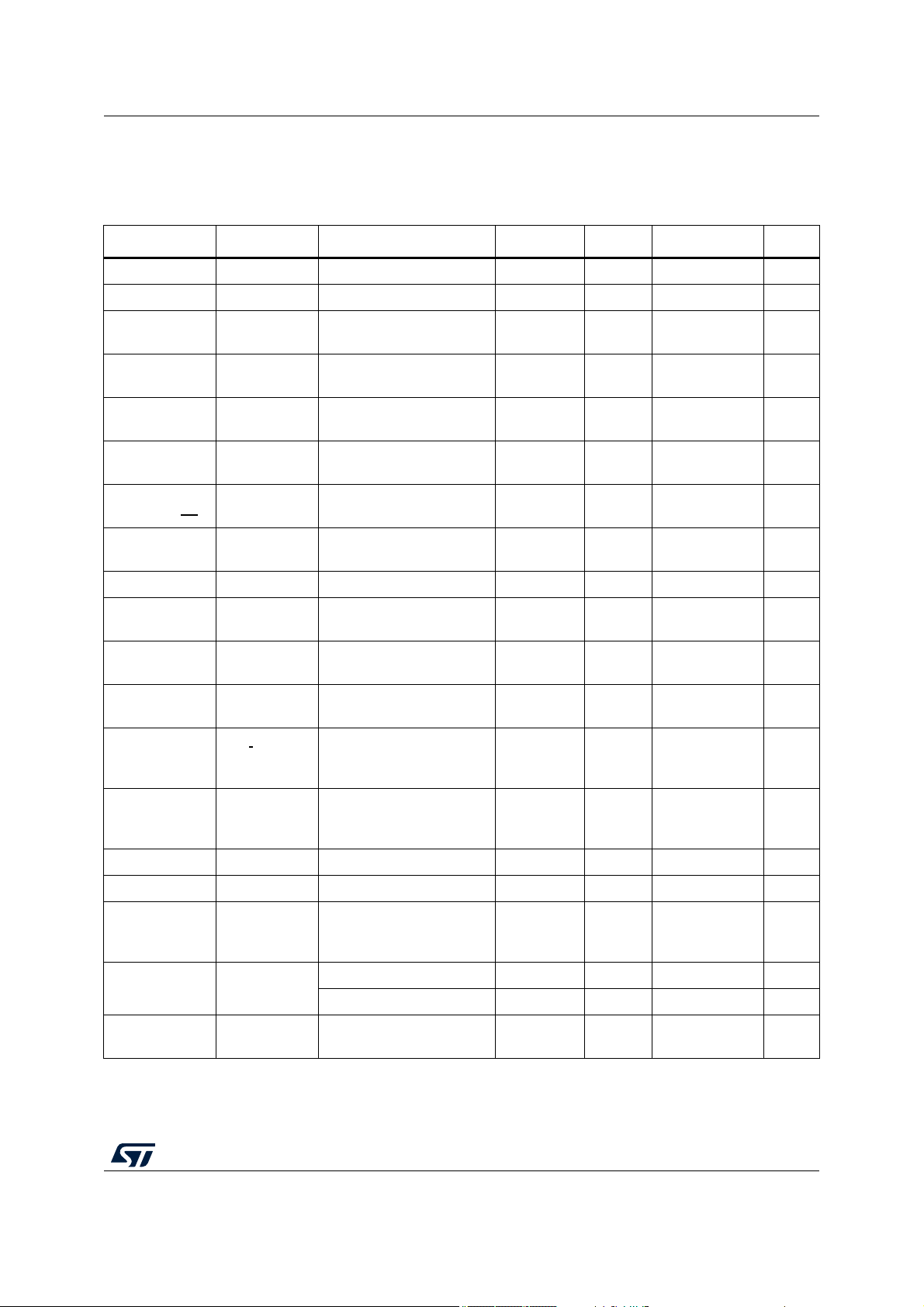

Table 3. Pin absolute maximum ratings (continued)

Symbol Parameter Condition Min Typ Max Unit

Interfaces

ABS_VDBATT - - -18 - 40 V

ABS_PDBATT - - -18 - 40 V

IC in sleep

-

ABS_VDG

-

-

ABS_PDG

-

-

ABS_PRG

-

mode (IGN

low)

IC in

operative

mode (IGN

high)

IC in sleep

mode (IGN

low)

IC in

operative

mode (IGN

high)

IC in sleep

mode (IGN

low)

IC in

operative

mode (IGN

high)

-0.3 - VDS+12≤51 V

-18 - VDS+12≤51 V

-0.3 - PDS+12≤51 V

-18 - PDS+12≤51 V

-0.3 - PRS+12≤51 V

-18 - PRS+12≤51 V

ABS_VDS

ABS_PDS

ABS_PRS

IC in sleep

-

-

-

-

-

-

mode (IGN

low)

IC in

operative

mode (IGN

high)

IC in sleep

mode (IGN

low)

IC in

operative

mode (IGN

high)

IC in sleep

mode (IGN

low)

IC in

operative

mode (IGN

high)

-0.3 - 40 V

-18 - 40 V

-0.3 - 40 V

-18 - 40 V

-0.3 - 40 V

-18 - 40 V

14/109 DS12539 Rev 3

Page 15

L9396 Overall description

Table 3. Pin absolute maximum ratings (continued)

Symbol Parameter Condition Min Typ Max Unit

ABS_WDTDIS - - -0.3 - 7 V

ABS_AI0 - - -0.3 - 40 V

ABS_AI1 - - -0.3 - 40 V

ABS_AI2 - - -0.3 - 40 V

ABS_AI3 - - -0.3 - 40 V

ABS_AI4 - - -0.3 - 40 V

ABS_FSN - - -0.3 - 40 V

ABS_FAULT - - -0.3 - 40 V

ABS_PRN - - -0.3 - 40 V

ABS_RESET - - -0.3 - 40 V

ABS_WSO0 - - -0.3 - 40 V

ABS_WSO1 - - -0.3 - 40 V

ABS_WSO2 - - -0.3 - 40 V

ABS_WSO3 - - -0.3 - 40 V

ABS_CS - - -0.3 - 40 V

ABS_CLK - - -0.3 - 40 V

ABS_SDI - - -0.3 - 40 V

ABS_SDO - - -0.3 - 40 V

ABS_PRI - - -0.3 - 40 V

ABS_PDI - - -0.3 - 40 V

ABS_GPOD0 - - -18 - 40 V

ABS_RSUH0 - - -18 - 40 V

ABS_RSUH1 - - -18 - 40 V

ABS_RSUH2 - - -18 - 40 V

ABS_RSUH3 - - -18 - 40 V

ABS_RSUL0 - - -18 - 40 V

ABS_RSUL1 - - -18 - 40 V

ABS_RSUL2 - - -18 - 40 V

ABS_RSUL3 - - -18 - 40 V

ESD requirements

ESD according to the Human

Body Model (HBM), Q100-002

for global pins; (100pF/1.5kΩ)

ESD according to the Human

Body Model (HBM), Q100-002

for all other pins; (100pF/1,5kΩ)

- - - - ±4000 V

- - - - ±2000 V

DS12539 Rev 3 15/109

108

Page 16

Overall description L9396

Table 3. Pin absolute maximum ratings (continued)

Symbol Parameter Condition Min Typ Max Unit

ESD according to the Charged

Device Model (CDM), Q100011 Corner pins

ESD according to the Charged

Device Model (CDM), Q100011 Non-corner pins

Temperature requirements

----±750V

----±500V

T

a

T

storage

T

j

Thermal

R

th j-a

resistance

junction to

ambient

Thermal

R

th j-c

resistance

junction to

case

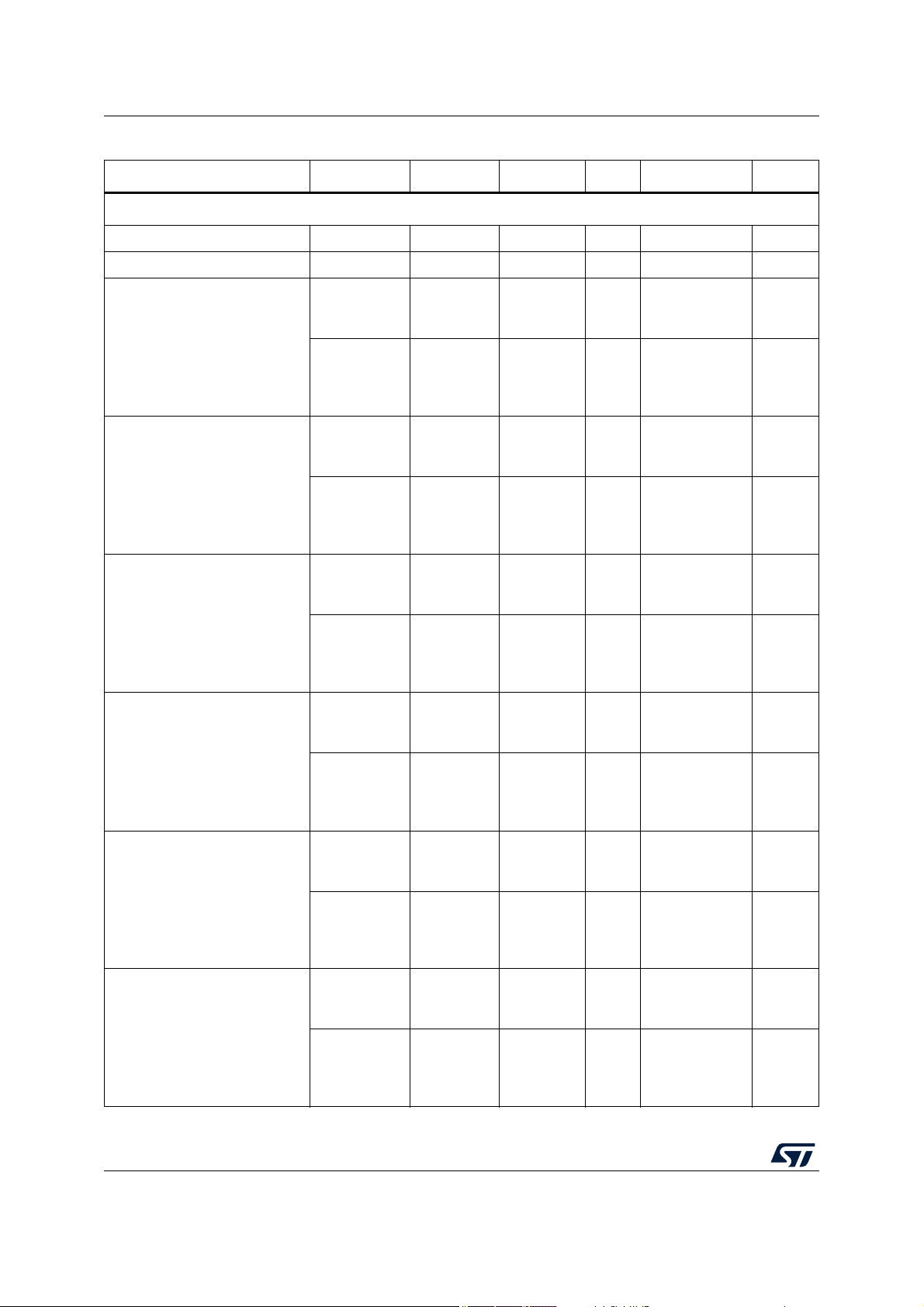

2.4 Operating range

---40-135°C

---55-150°C

---40-175°C

With 2s2p

PCB std

Jedec.

Natural

convenction.

-26 - °C/W

Standard

Jedec best

JESD51-7

Bottom cold

plate in

contact with

package

bottom case

-- 2.9

°C/W

(e-pad side).

JESD51

best practice

guidlines.

Within the operating ratings the part operates as specified and without parameter

deviations. Once taken beyond the operative ratings and returned back within, the part will

recover with no damage or degradation.

Additional supply voltage and temperature conditions are given separately at the beginning

of each specification table.

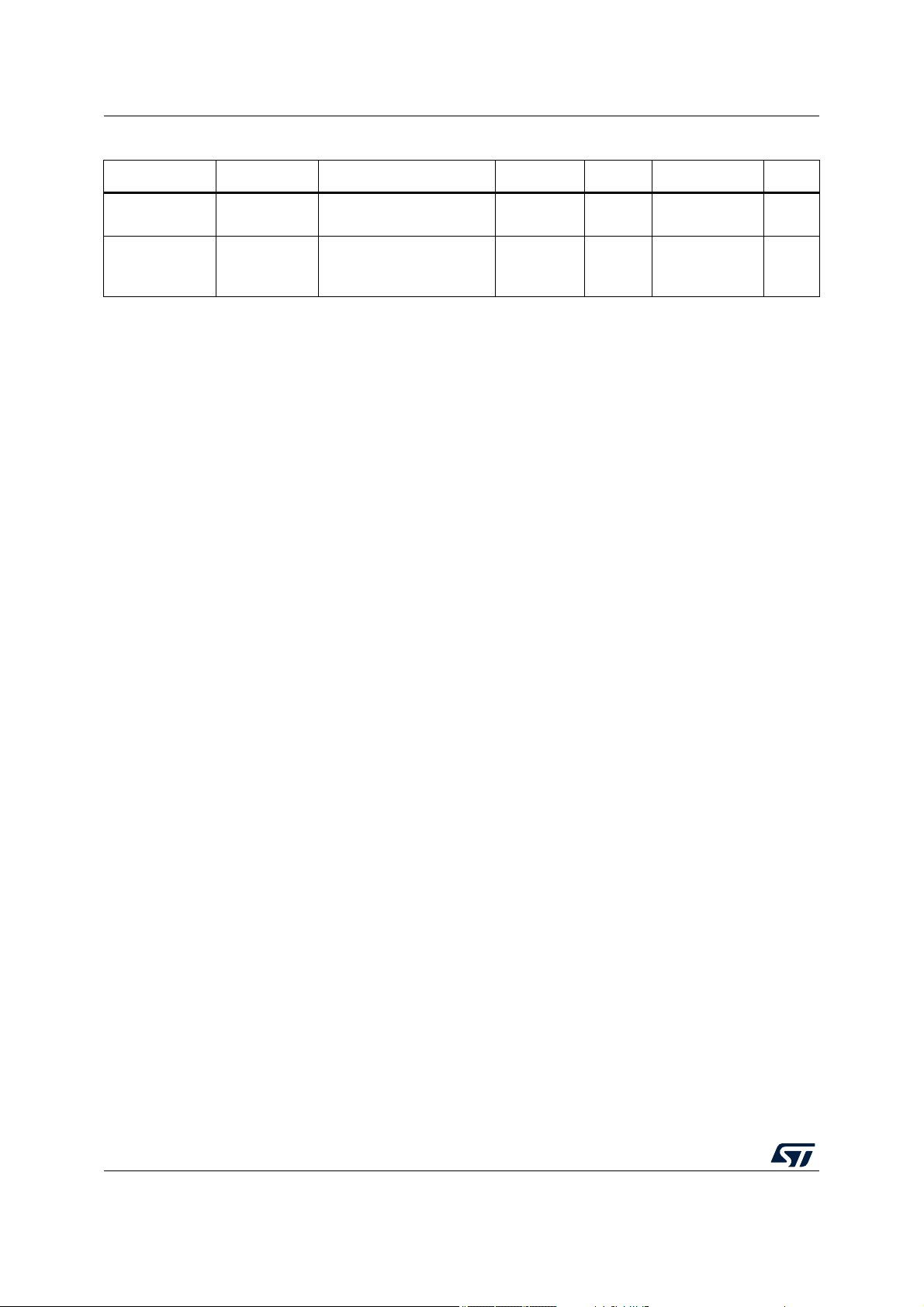

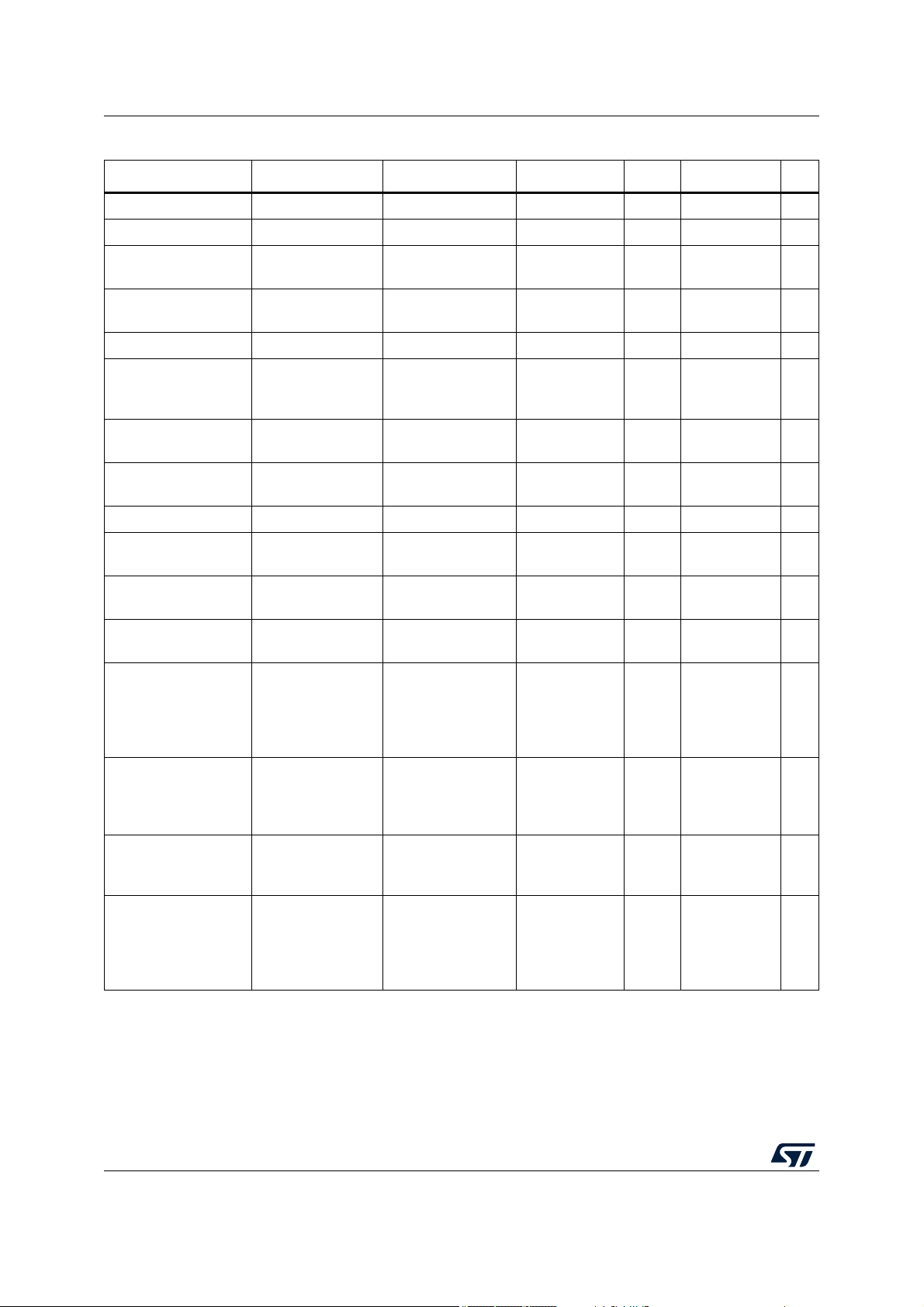

Pin name Condition Min Max Unit

Power supply

VB, VBST, VBM - -0.1 19 V

VB_SW - -1 19 V

BSTSW, VPREREG, I_CORE_SH,

I_CORE_SL

16/109 DS12539 Rev 3

Table 4. Pin operating range

--0.119V

Page 17

L9396 Overall description

Table 4. Pin operating range (continued)

Pin name Condition Min Max Unit

BCKSW, SCORE - -1 19 V

VC4 - VBST-0.6 VBST+10 V

VC2, CP - VBST-0.3 VBST+10 V

VC1, VC3 - -0.1 19 V

CBS, GCORE - -0.1 SCORE+8 V

VCC5, VCC, VCOREFDBK, VCORE - -0.1 5.5 V

VCCSEL, IGN - -0.1 19 V

GNDA, GNDD, GNDBST, NU

--0.10.1V

Interfaces

VDBATT, PDBATT - -0.1 19 V

IC in sleep mode

(IGN low)

-0.3 VDS+10 V

VDG

IC in operative

mode (IGN high)

IC in sleep mode

(IGN low)

-7 VDS+10 V

-0.3 PDS+10 V

PDG

IC in operative

mode (IGN high)

IC in sleep mode

(IGN low)

-7 PDS+10 V

-0.3 PRS+10 V

PRG

IC in operative

mode (IGN high)

IC in sleep mode

(IGN low)

-7 PRS+10 V

-0.3 19 V

VDS, PDS, PRS

IC in operative

mode (IGN high)

-7 19 V

WDTDIS - -0.1 5.5 V

AI[0..4] - -0.1 19 V

FSN, FAULT, PRN, RESET, WSO[0..3] - -0.1 5.5 V

CS, CLK, SDI, SDO, PRI, PDI - -0.1 5.5 V

RSUH/L[0..3], GPOD0 - -0.1 19 V

DS12539 Rev 3 17/109

108

Page 18

Power supply L9396

3 Power supply

3.1 Battery range

The device operates on 12 V system. Transient operation for these systems can reach 40 V

maximum. Particular care is to be taken in PCB manufacturing to keep thermal dissipation

to a reasonable level.

All electrical characteristics are valid for the following conditions unless otherwise noted:

-40 °C ≤ Tj ≤ +175 °C.

Symbol Parameter Conditions / Comments Min Typ Max Unit

Table 5. Configuration and control DC specifications

VBATP

VBATP

NOV_OB

NOV_WB

Normal Operating

Voltage without boost

Normal Operating

Voltage with boost

Design Info 6 13 19 V

Design Info

4.5

(6 to start-up)

-19V

18/109 DS12539 Rev 3

Page 19

L9396 Power supply

Comp

BST

control

CLAMP

enable

BSTSW

VBST

GNDBST

TH

TH

VB

GADG1801171332PS

BST_DISABLE

driver &

CLAMP_EN

3.2 Boost regulator

The boost regulator can be enabled or disabled via SPI depending on the needs of the

application with respect to the operating battery level. It features an integrated power stage

and operates at 2

capability should be enough to grant full I/O pin supply and minimal µC operation.

When not used, BSTSW pin can be connected to ground and VBST directly to the protected

battery line. The device enables or keeps disabled the boost converter at start-up depending

on the external circuitry: if BSTSW pin is shorted to ground, the boost is disabled at power

up and kept disabled; in case the BSTSW experiences a high voltage at power up, given by

battery connection through the inductor, the boost is enabled. This condition is reported via

SPI with bit BOOST_KEPT_OFF of SUPPLY_CONTROL_2 register (it means that boost

has been kept off and will not operate).

Boost converter diagnostics include under voltage, reported via SPI and FAULT pin (if the

regulator is enabled). The integrated FET featuring the boost switch is protected against

short to battery by means of a thermal shutdown circuit. When thermal fault is detected the

FET is switched off and latched in this state until the related fault flag is read. In case of loss

of ground the FET is switched off and automatically reactivated as soon as ground

connection is restored. Over-voltage protection from load-dump and inductive flyback is

provided via an active clamp and a disable circuitry. A dedicated circuitry is implemented to

keep the boost off at start-up till the voltage difference between VB and VBST pins is lower

than BST_DISABLETH in order to reduce in-rush current and diagnose VBST pin loss

condition or diode loss. An SPI bit is present to report output of this comparator (bit

BOOST_READY of SUPPLY_CONTROL_2 register goes high when VBST>=VBBST_DISABLETH).

MHz to allow the use of external low cost 2.2 µH inductor. The current

State of boost regulator is reported via SPI bit BOOST_ON_FLAG in register

SUPPLY_CONTROL_2. In case boost is disabled due to diagnostic or battery voltage

above output regulation voltage this bit is cleared to 0.

Figure 3. Boost regulator block diagram

DS12539 Rev 3 19/109

108

Page 20

Power supply L9396

All electrical characteristics are valid for the following conditions unless otherwise noted:

-40 °C ≤ Tj ≤ +175 °C; 4.5 V ≤ VBATP ≤ 19 V

Symbol Parameter Conditions Min Typ Max Unit

VBST

NOV

VBST

UV_UP

VBST

UV_DN

Table 6. Boost regulator electrical characteristics

Design Info With

boost, VBST is more

Normal Operating

Voltage at VBST

VBST under voltage

release threshold

VBST under voltage

detection threshold

than minimum boost

output (> 6 V); Without

boost, VBST is

shorted to VBATP

VBST rising. VBST

under-voltage release

leads to charge pump

switch on

VBST falling. VBST

under-voltage

detection leads to

charge pump shut

down.

61319V

6.5 - 7.1 V

5.6 - 6 V

t

flt_VBST_UV

Under voltage filter

time

VBST Boost Output Voltage

I

O_BST

dV

dV

L

R

C

R

C

SR_ac

LR_ac

BST

LBST

BST

BST

BSTF

Boost Output

Current

Line Transient

Response

Load Transient

Response

Output Inductance

Output Inductance

Impedance

Output Bulk

Capacitance

Bulk Capacitor ESR Design Information - - 0.1 Ω

Output Filter

Capacitance

--12-µs

Across all line and

load (steady state)

Excluding current on

analog and digital 3.3V

All line, load;

dt = 100 µs

All line, load;

dt = 100 µs

8.55 - 9.6 V

20 - 300 mA

-8% - 8% %

-8% - 8% %

2.2 µH nominal

tolerance ±30%

1.6 - 2.8 µH

Design Information

Design Information - - 0.1 Ω

Design Information 1.76 - - µF

Min 100 nF nominal

Design Information

80 - - nF

Over Current

Detection

Switch R

DSon

- 1.2- 2A

---0.8Ω

R

I

OC

DSon

20/109 DS12539 Rev 3

Page 21

L9396 Power supply

Table 6. Boost regulator electrical characteristics (continued)

Symbol Parameter Conditions Min Typ Max Unit

V

BSTSW

BST_DISABLE

CLAMP_EN

f

BSTSW

t

BSTSW

T

JSDBST

T

HYS_TSDBST

I

BSTSW_LO_OFF

I

BSTSW_HI_OFF

BSTSW Voltage

Clamp

Active when not in

load dump

(VB

LOADDUMP

)

30 - 36 V

Voltage difference

between VB and

TH

VBST to deactivate

VB – VBST 1.6 - 2.6 V

the Boost regulator

Voltage difference

between BSTSW

TH

and VBST to activate

BSTSW – VBST 1.5 - 4.5 V

the Boost CLAMP

Operating Frequency - - f

BSTSW Transition

Time

VB = 4.5 V,

= 300 mA

I

O_BST

8 - 50 ns

/8.5(1.88) - MHz

OSCINT

Thermal Shutdown - 175 - 200 °C

Thermal Shutdown

hysteresis

-5-15°C

BSTSW current

consumption when

BSTSW - VBST<1.5V 3 - 20 µA

BOOST is OFF

BSTSW current

consumption when

BSTSW – VBST>4.5V 30 - 70 µA

BOOST is OFF

Voltage threshold to

V

TH_BST_KEEP_OFF

deactivate the Boost

regulator when not

used

3.3 Internal supply

The internal analog and digital part is supplied by the supply voltage VBST through

integrated voltage regulators. The generated voltage is monitored. In case of under/overvoltage, the device performs a power on reset (POR).

An undervoltage condition on VBST will lead to an internal reset of the IC. Above this

undervoltage threshold, full functionality is granted.

The device integrates two separated instances of Bandgap voltage regulators; one of these

bandgaps is used as voltage reference for the internal regulators, while the other one is

used for monitoring the voltage levels.

GNDD ground line is protected against ground loss scenarios. In case GNDD line would be

at least GNDD

GNDD is used for digital logic and charge pump while GNDA is used for analog blocks.

GNDBST is used for boost regulator only.

above the reference ground line GNDA, a POR is asserted.

OPEN

-0.5-1V

DS12539 Rev 3 21/109

108

Page 22

Power supply L9396

The device returns to normal operation with full functionality as soon as the POR is

released.

Symbol Parameter Conditions Min Typ Max Unit

Table 7. Internal supply electrical characteristics

GNDD

OPEN

T

FLT_ GNDD_OPEN

GNDBST

GNDBST

T

FLT_ GNDBST_OPEN

OPEN

PU

GNDD threshold GNDx = 0 180 300 420 mV

GNDD Open deglitch filter

time

--10-µs

GNDBST threshold GNDx=0 200 300 400 mV

GNDBST pull-up current Boost OFF 50 - 200 µA

GNDBST Open deglitch

filter time

-7.5-11µs

VDD VDD Output Voltage - 3.15 3.3 3.4 V

VDD

OV

VDD

UV

T

FLT_ VDD_OV_UV

VDD Over-voltage

threshold

VDD Under-voltage

threshold

VDD Over-voltage / Undervoltage deglitch filter time

-3.47-3.7V

- 2.7 - 2.9 V

--10-µs

VINTA VINTA Output Voltage - 3.2 3.3 3.4 V

VINTA

VINTA

OV

UV

VINTA Over-voltage

threshold

VINTA Under-voltage

threshold

-3.47-3.7V

- 2.95 - 3.13 V

VINTA Over-voltage /

T

FLT_ VINTA_OV_UV

Under-voltage deglitch filter

--10-µs

time

3.4 Wake-up input

The input pin IGN can be used as a wake up source connection. In case the voltage on IGN

pin raises above WAKE

The device moves to sleep in case IGN falls below WAKE

longer than WAKE

flt_down

transceiver inhibit outputs. A filter time is implemented to reject spurious glitches. The filter

time is started when the input signal exceeds the specified threshold.

All electrical characteristics are valid for the following conditions unless otherwise noted:

-40 °C ≤ Tj ≤ +175 °C; 4.5 V ≤ VBATP ≤ 19 V.

22/109 DS12539 Rev 3

for an interval longer than WAKE

high_th

. This input can be connected to ignition battery switches or

high_th

, the device wakes up.

flt_up

- WAKE

for an interval

hys

Page 23

L9396 Power supply

Charge Pump

CTANK

VBST VCP

GADG1801171544PS

C1 C2

VC1 VC2 VC3 VC4

Table 8. Wake-up input electrical characteristics

Symbol Parameter Conditions Min Typ Max Unit

VBATP = 19 V Wake

VB

stby_cur

Battery standby current

consumption

disable Sum of leakage

currents from BSTSW,

- - 30 µA

VBST, VB and VBM

WAKE

WAKE

WAKE

WAKE

WAKE

WAKE

high_th

low_th

hys

pd

flt_up

flt_down

Wake-up high voltage

threshold

Wake-up low voltage

threshold

Wake-up voltage

hysteresis

Wake-up pull down IGN = 14 V 300 - 900 kΩ

Wake up ON deglitch - - 10 - µs

Wake up OFF deglitch - - 10 - µs

-3.5--V

---1.5V

- 0.5 - 1.5 V

KA_period Keep-alive period - - 200 - ms

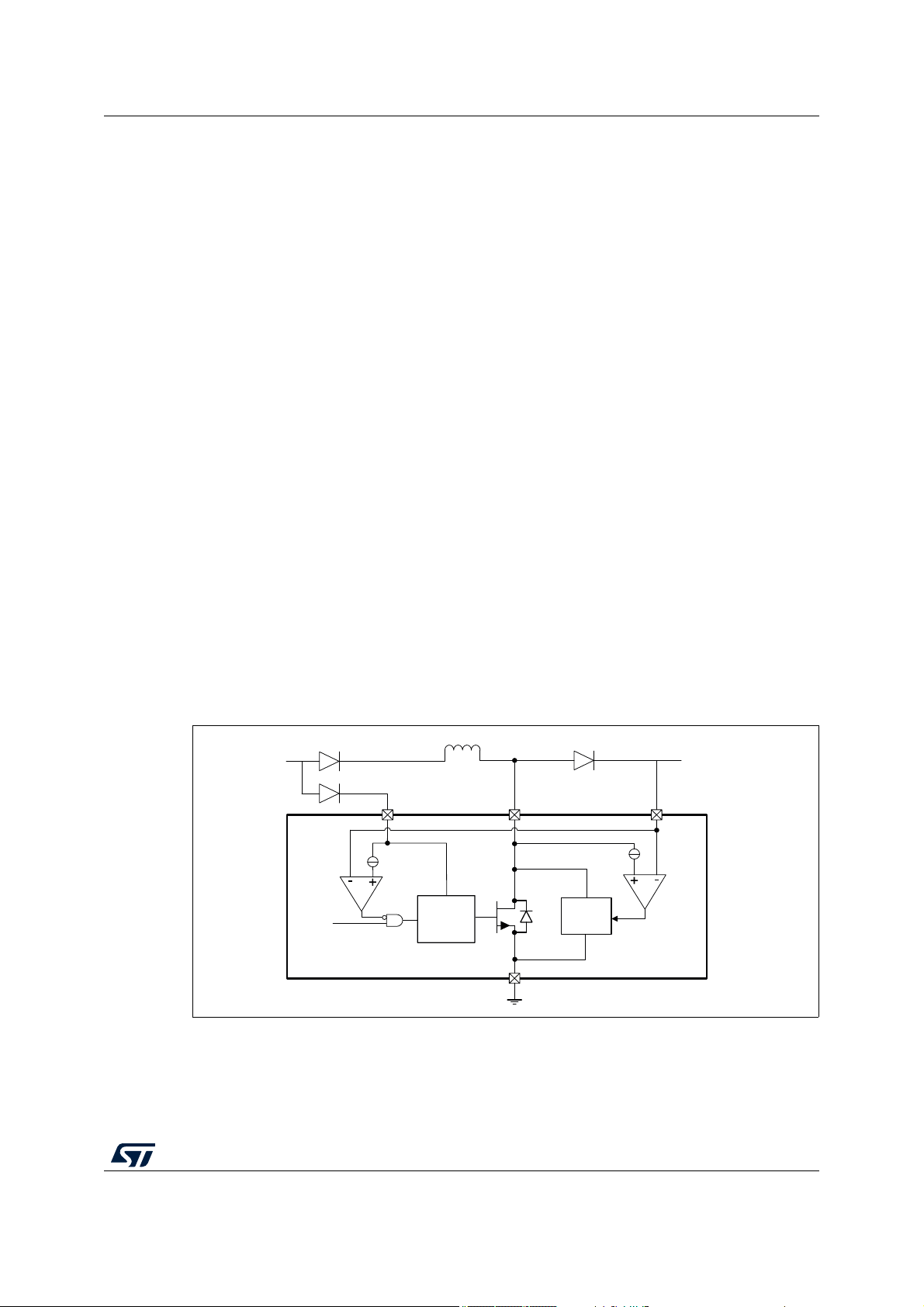

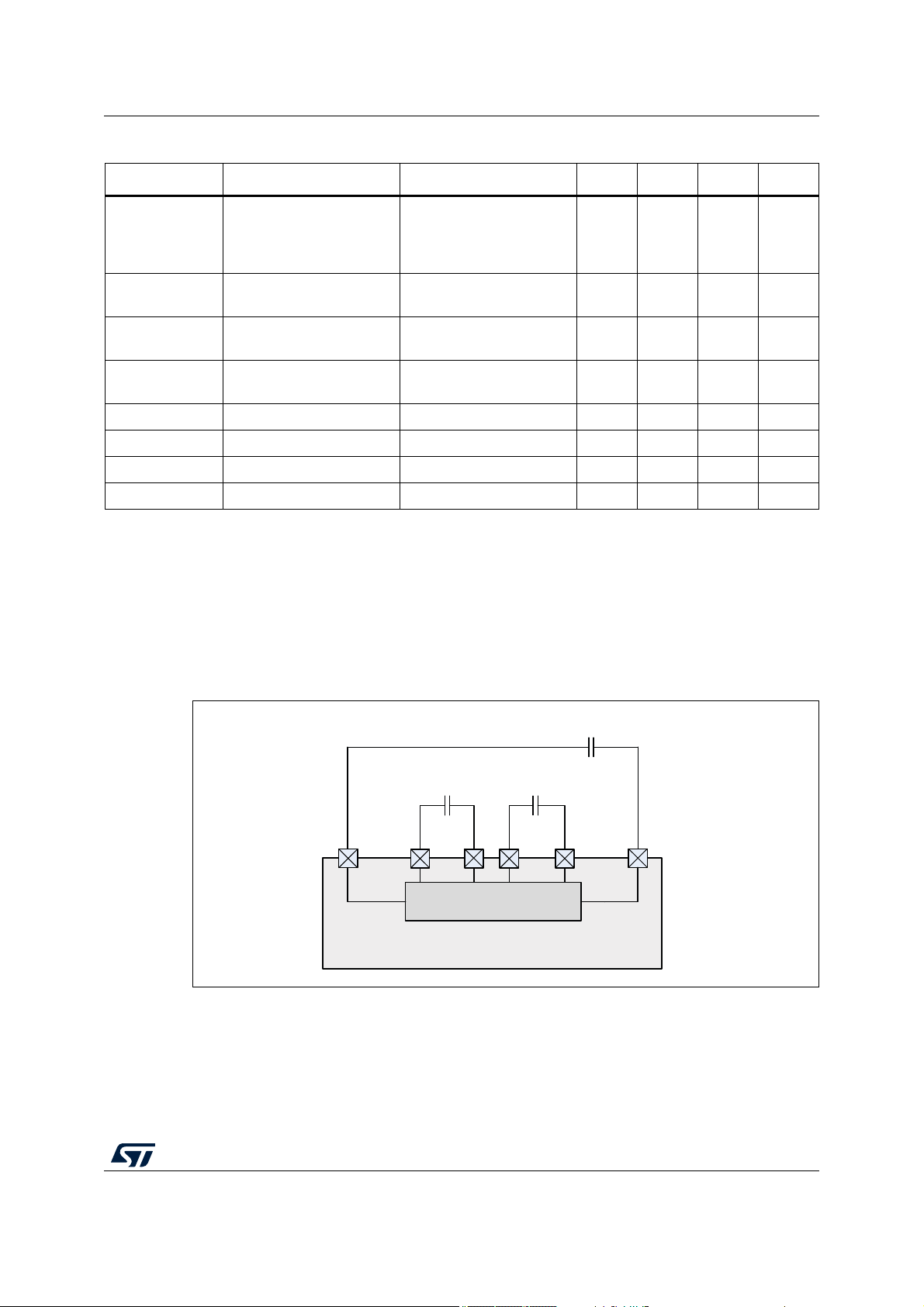

3.5 Charge pump

A two-stage charge pump is integrated to supply the high voltage circuit in the VPREREG

and VCORE regulators and in the pump motor and fail safe pre-drivers.

The charge pump is supplied by the rail connected to VBST pin. External charging

capacitors are used to achieve a high current capability.

Figure 4. Charge pump block diagram

It features a current limitation protection when either C1 or C2 is being charged up. The

charge pump is protected against over temperature with dedicated thermal sensor. In

standby mode the charge pump is disabled.

In case the CP output voltage remains too low for longer than tfCP the CP LOW bit is

latched, which leads to shutdown of VPREREG, pump motor driver and fail safe driver. In

turn, under voltage of VPREREG leads to shutdown of VCC, VCC5 and VCORE regulators.

DS12539 Rev 3 23/109

108

Page 24

Power supply L9396

A second undervoltage threshold is present (V

CPLOW2

) with a higher value. It can be used

together with PDG turn-on threshold voltage to detect that low charge pump voltage is

responsible for low PDG ON voltage.

Symbol Parameter Conditions Min Typ Max Unit

V

CP_5V6

V

CP_8V

V

CP_8V55

I

CP_5V6

I

CP_8V

f

CP

V

CPLOW

Charge pump

output voltage

Charge pump

output voltage

Charge pump

output voltage

Charge pump

output current

Charge pump

output current

Charge pump

frequency

Charge pump low

voltage threshold

Charge pump

V

CPLOW2

second low voltage

threshold

t

fCP

C

TAN K

, C

C

CP1

T

JSDCP

T

HYS_TSDCP

Low voltage filter

time

Output capacitor Design Info - 220 - nF

Switching capacitor Design Info - 68 - nF

CP2

Thermal Shutdown - 175 - 200 °C

Thermal Shutdown

hysteresis

Table 9. Charge pump electrical characteristics

VBST > 5.6 V

Iload_ext = 8 mA

VBST >8V

Iload_ext=10mA

VBST >8.55V

Iload_ext=1mA

VBST>5.6V - - 8 mA

VBST>8V - - 10 mA

--f

- VBST+5.6 VBST+6 VBST+6.8 V

- VBST+7.85 VBST+8.35 VBST+8.85 V

--10-µs

-5-15°C

VBST+7.0 - VBST+11 V

VBST+8.9 - VBST+11 V

VBST+9.1 - VBST+11 V

/34(0.470) - MHz

OSCINT

3.6 VPREREG buck regulator

The integrated buck regulator provides a reduced voltage supply to the remaining regulators

and to the WSS / tracking interface. Its default output level 6.5

7.2

V via register of BUCK VOLTAGE SELECTION in SPI.

This regulator is protected against short circuits and over temperature with dedicated

thermal sensor, and an over/under voltage monitor is implemented. VPREREG itself is not

shut down in case of over/under voltage at its output. VPREREG itself is not shut down in

case of overcurrent, only in case of over temperature the regulator is switched off.

This regulator is not protected against diode loss and the IC may be irreparably damaged

due to diode loss.

Under voltage of VPREREG (VPREREG_UV) leads to shutdown of VCC, VCC5 and

VCORE regulators.

24/109 DS12539 Rev 3

V can be further increased to

Page 25

L9396 Power supply

All electrical characteristics are valid for the following conditions unless otherwise noted:

-40 °C ≤ Tj ≤ +175 °C; 6 ≤ VBST ≤ 19 V.

Symbol Parameter Conditions Min Typ Max Unit

Table 10. VPREREG buck regulator

V

PREREG_H

V

PREREG_L

V

PREREG_UV

t

flt_VPREREG_UV

V

PREREG_OV

t

flt_VPREREG_OV

I

VPREREG_HI

I

VPREREG_LO

L

VPREREG

C

VPREREG

dV

SR_ac

dV

LR_ac

I

OC_VPREREG_HI

Output Voltage VBST > 8.2 V 6.984 7.2 7.416 V

Output Voltage VBST > 7.5 V 6.305 6.5 6.695 V

Under voltage

threshold

Under voltage

filter time

Over voltage

threshold

Over voltage

filter time

Output load

current

Output load

current

- 5.05 5.21 5.32 V

--12-µs

+5%

x

-

V

PREREG_

+10%

V

-

PREREG_

x

V

--12-µs

SYS_CONFIG_1[9]=1 0.01 - 1 A

SYS_CONFIG_1[9]=0

(default)

0.01 - 0.5 A

Buck inductor - 17.6 22 26.4 µH

Output

capacitor

Line Transient

Response

Load Transient

Response

- 14.3 22 29.7 µF

All line, load; dt = 10 µs

VBST> V

PREREG

(Typ)+3V

All line, load; dt = 10 µs

VBST> V

PREREG

(Typ)+3V

-8% - 8% %

-8% - 8% %

High Over

current

SYS_CONFIG_1[9]=1 1.8 - 3 A

detection

I

OC_VPREREG_LO

- High side t

- High side t

Fv

preregsw

R

DSon

t

softstart

Low Over

current

detection

on

off

Operating

Frequency

High side

Rds_ON

Softstart time

SYS_CONFIG_1[9]=0

(default)

0.9 - 1.6 A

---40ns

---40ns

f

/

--

OSCINT

34

-MHz

(0.470)

= 25 °C - - 0.4 Ω

T

j

T

= 175 °C - - 0.44 Ω

j

From 10% to 90% of

nominal output voltage

130 - 390 µs

DS12539 Rev 3 25/109

108

Page 26

Power supply L9396

Table 10. VPREREG buck regulator (continued)

Symbol Parameter Conditions Min Typ Max Unit

T

JSDVPRE

T

HYS_TSDVPRE

Thermal

Shutdown

Thermal

Shutdown

hysteresis

-175-200°C

-5-15°C

26/109 DS12539 Rev 3

Page 27

L9396 Power supply

CP

Buck

Configuration

VCOREFDBK

GCORE

SCORE

VCORE

CBS

Linear

configuration

VCOREFDBK

GCORE

SCORE

VCORE

CP

GADG1901171138PS

I_CORE_SL

I_CORE_SH

I_CORE_SL

I_CORE_SH

(w/ Stop Mode bypass

with ext. FET

LDO)

Volt. Mon.

Volt. Mon.

22uH

VPREREG

VPREREG

L9396

L9396

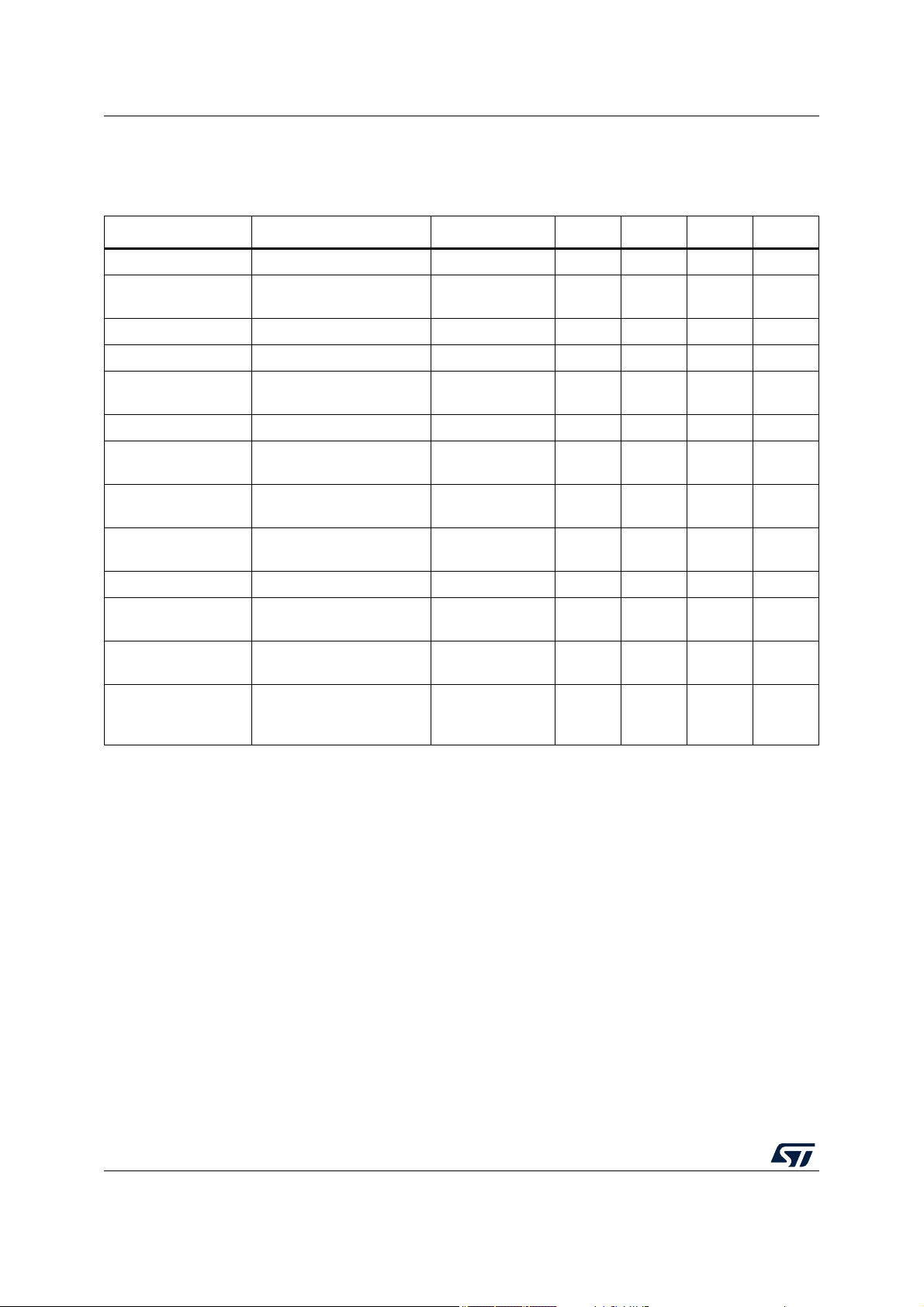

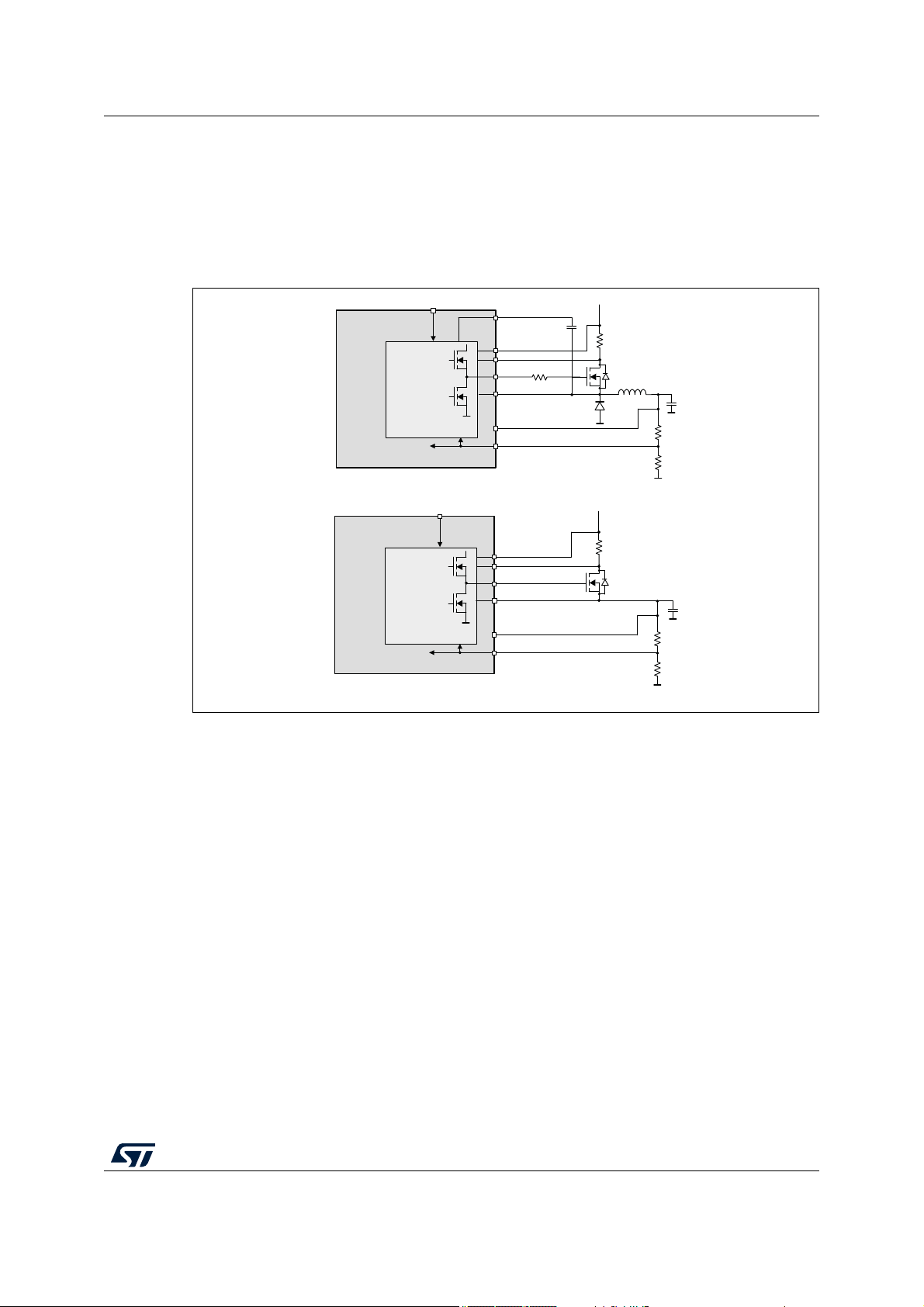

3.7 VCORE regulator

This regulator provides the supply to the µC core. The flexible approach with the external

voltage divider allows the rail to be regulated from 0.8

either as a buck controller or as a linear controller, driving an external FET in both cases.

Figure 5. VCORE configuration diagram (buck regulator - top, linear regulator -

bottom)

V to 5 V. It can also be configured

Typically 100 Ω resistor is to be inserted between GCORE pin and gate of the external FET

for buck configuration. For buck configuration, the source of the external FET should be

connected to the SCORE pin, and the output tank capacitor should be connected to the

VCORE pin. For linear configuration, the output tank capacitor should be connected with the

source of the external FET and the SCORE pin, while VCORE pin could be left either

floating, tied to ground or still connected to VCORE to allow ADC internal measurement.

The VCORE regulator has over and under voltage detections and the VCORE is not shut

down in case of over or under voltage. It is also protected against short to ground by

monitoring regulation loop for VCORE buck or over current for VCORE linear. When short to

ground is detected and lasts more than the filter time of tflt_oc_vcore, the vcore is shut down

and the restart is automatic in tflt_restart. No thermal protection is implemented for VCORE

because the power MOS is external.

Both VPREREG and VCORE regulators could be disabled by connecting I_CORE_SH pin

to ground or leaving it open. In this case, VPREREG pin should be connected to VBST pin.

Moreover two pins (AI0 and AI1) are used to configure additional features of VCORE

regulator. It's possible to disable only VCORE regulator leaving VPREREG enabled. It's

possible to change the monitor of regulated voltage (monitor on VCORE pin or monitor on

VCOREFDBK pin). All the possibilities are listed in the following table.

DS12539 Rev 3 27/109

108

Page 28

Power supply L9396

Table 11. Vcore configuration

AI0 AI1 I_CORE_SH VCORE state VPREREG state VCORE monitor

Low Low High Enabled Enabled

Low High High Enabled Enabled

High Low High Enabled Enabled

VCORE_UV_L,

VCORE_OV_L

VCORE_UV_H,

VCORE_OV_H

VCOREFDBK_UV,

VCOREFDBK_OV

High High High Disabled Enabled Disabled

Don’t care Don’t care Low Disabled Disabled Disabled

The state of configuration pins (AI0, AI1 and I_CORE_SH) is latched at power up when

VPREREG voltage exceeds the V

PREREG_

UV threshold and stays latched until next POR

event.

Microcontroller can monitor the voltage of AI0 and AI1 pins using embedded ADC converter

and latched configuration is available via SPI bits.

All electrical characteristics are valid for the following conditions unless otherwise noted:

-40 °C ≤ Tj ≤ +175 °C; V

Table 12. VCORE regulator electrical characteristics

PREREG

_L(Min) ≤ VPREREG ≤ V

PREREG

_H(Max).

Symbol Parameter Conditions Min Typ Max Unit

R

SH_HI_CURR

R

SH_LO_CURR

VCORE FDBK_RES

VCOREFDBK_UV

VCOREFDBK_OV

Shunt resistor high

current

Shunt resistor low

current

Feedback resistor

range

Undervoltage

threshold

Overvoltage

threshold

- 99 100 101 mΩ

Only in linear mode 327 330 333 mΩ

- 10 - 100 kΩ

Excluding external

voltage divider

accuracy

Excluding external

voltage divider

accuracy

VCOREFDBK

– 10%

VCOREFDBK +

5%

VCOREFDBK

-

VCOREFDBK

-

– 5%

+ 10%

VCORE low

VCORE_UV_L

Undervoltage

- 2.97 - 3.135 V

threshold

VCORE low

VCORE_OV_L

Overvoltage

- 3.465 - 3.63 V

threshold

VCORE high

VCORE_UV_H

Undervoltage

- 4.5 - 4.75 V

threshold

V

V

28/109 DS12539 Rev 3

Page 29

L9396 Power supply

Table 12. VCORE regulator electrical characteristics (continued)

Symbol Parameter Conditions Min Typ Max Unit

VCORE high

VCORE_OV_H

t

flt_VCORE_VCOREFDBK

_UVOV

VICORESH_IH

Overvoltage

threshold

Under/overvoltage

filter time

I_CORE_SH input

high voltage

-5.25-5.5V

--12-µs

-1.75--V

VICORESH_IL

VICORESH_Ihys

Ipd_ICORESH_L

Ipd_ICORESH_B

V_AI0_IH

V_AI0_IL

I_CORE_SH input

low voltage

I_CORE_SH input

hysteresis

I_CORE_SH input

Pull down current

I_CORE_SH input

Pull down current

AI0 input high

voltage

AI0 input low

voltage

---0.75V

-100-1000mV

VCORE linear

mode,

5 - 20 µA

I_CORE_SH=3.3V

VCORE buck

mode,

100 - 300 µA

I_CORE_SH=3.3V

-1.75--V

---0.75V

V_AI0_Ihys AI0 input hysteresis - 100 - 1000 mV

Ipd_AI0

V_AI1_IH

V_AI1_IL

AI0 input Pull down

current

AI1 input high

voltage

AI1 input low

voltage

AI0=3.3V 10 - 100 µA

-1.75--V

---0.75V

V_AI1_Ihys AI1 input hysteresis - 100 - 1000 mV

Ipd_AI1

AI1 input Pull down

current

AI1 = 3.3 V 10 - 100 µA

From 10% to 90%

t

softstart

Softstart time

of nominal output

240 - 720 µs

voltage

Buck configuration

VCORE Output voltage

I

VCORE

C

VCORE

C

VCORE

Nominal 0.8V to 5V

Excluding external

voltage divider

0.776 - 5.15 V

accuracy

Output load current R

SH_HI_CURR

0.01 - 1 A

Output capacitor VCORE > 1.2 V -35% 22 +35% µF

Output capacitor VCORE ≤ 1.2V -35% 47 +35% µF

DS12539 Rev 3 29/109

108

Page 30

Power supply L9396

Table 12. VCORE regulator electrical characteristics (continued)

Symbol Parameter Conditions Min Typ Max Unit

L

VCORE

L

VCORE

R

LVC ORE

C

C

FET

BS

Buck inductor VCORE > 1.2 V -20% 22 +20% µH

Buck inductor VCORE ≤ 1.2 V -20% 12 +20% µH

Buck inductor

resistance

External FET gate

charge

- - - 105 mΩ

---30nC

Bootstrap capacitor - - 100 - nF

Excluding external

VCOREFDBK Feedback voltage

voltage divider

0.8 -3% - 0.8 +3% V

accuracy

dV

dV

SR_ac

LR_ac

Line Transient

Response

Load Transient

Response

All line, load;

dt = 10 µs

All line, load;

dt = 10 µs

-8% - 8% %

-8% - 8% %

VCORE ripple Ripple voltage - -20 - +20 mV

I

OC_VCORE_BUCK

Rdson_hs

Rdson_ls

Over current

detection

High side on

resistance

Low side on

resistance

R

SH_HI_CURR

---28Ω

---8.3Ω

1.6 - 2.6 A

tflt_oc_vcore

tflt_restart

Sw_fr

PSRR

Shut down filter

time for short to

ground

restart filter time for

short to ground

Switching

frequency

Power supply

rejection ratio

Filter time starts to

count from when

current in power

85 100 115 µs

MOS is more than

I

O_LIM

Filter time starts to

count from when

core buck is

1.7 2 2.3 ms

disabled

f

OSCINT

--

/34

-MHz

(0.470)

VPREREG = 6.5 V,

V

= 1 Vpp

noise

f

noise

C

VCORE

L

VCORE

= 20 kHz,

= 22 µF

= 22 µH

40 - - dB

30/109 DS12539 Rev 3

Page 31

L9396 Power supply

Table 12. VCORE regulator electrical characteristics (continued)

Symbol Parameter Conditions Min Typ Max Unit

Linear configuration

Nominal 0.8 V to

VCORE Output voltage

5 V Excluding

external voltage

divider accuracy

0.78 - 5.125 V

I

VCORE_HI

I

VCORE_LO

C

VCORE

R

CVCORE

C

VCORE_EMI

C

FET

Output load current

high

Output load current

low

R

SH_HI_CURR

R

SH_LO_CURR

Output capacitor - 5 - 40 µF

Output capacitor

ESR

Drain output

stability capacitor

External FET gate

charge

-0.01-0.1Ω

-0.1--µF

---50nC

0.07 - 0.75 A

0.07 - 0.25 A

Excluding external

VCOREFDBK Feedback voltage

voltage divider

0.8 -2.5% - 0.8 + 2.5% V

accuracy

dV

SR_ac

dV

LR_ac

GCORE_pd

Line Transient

Response

Load Transient

Response

Gate internal pull

down

All line, load;

dt = 10 µs

All line, load;

dt = 10 µs

Not tested,

guaranteed by

design.

-5% - 5% %

-5% - 5% %

100 - - kΩ

GCORE_Vclamp Gate voltage clamp - 8 - 12 V

I

COREL_HI

I

COREL_HI

Ilim

_OC

High Current

limitation

High Overcurrent

threshold

-0.8-1.6A

-0.8-1.6A

I

COREL_LO

I

COREL_LO

tflt_oc_vcore

Ilim

_OC

Low Current

limitation

Low Overcurrent

threshold

Shut down filter

time for short to

ground

- 0.26 - 0.48 A

- 0.26 - 0.48 A

Filter time starts to

count from when

current in power

85 100 115 µs

MOS is more than

Ilimx

I

COREL

DS12539 Rev 3 31/109

108

Page 32

Power supply L9396

Table 12. VCORE regulator electrical characteristics (continued)

Symbol Parameter Conditions Min Typ Max Unit

Filter time starts to

tflt_restart

restart filter time for

short to ground

count from when

core buck is

1.7 2 2.3 ms

disabled

VPREREG = 6.5V,

= 1 Vpp

V

PSRR

Power supply

rejection ratio

noise

f

= 20 kHz,

noise

C

VCORE

L

VCORE

40 - - dB

= 22µF

= 22µH

3.8 VCC5 regulator

This regulator provides a fixed 5V rail to supply µC I/Os and ADC. The VCC5 regulator has

over and under voltage detections and is also protected against short circuits and over

temperature with shared thermal sensor with VCC regulator.

All electrical characteristics are valid for the following conditions unless otherwise noted:

-40 °C ≤ Tj ≤ +175 °C; V

Table 13. VCC5 regulator electrical characteristics

PREREG

_L(Min) ≤ VPREREG ≤ V

PREREG

_H(Max).

Symbol Parameter Conditions Min Typ Max Unit

VCC5

VCC5_UV

Regulated output

voltage

Undervoltage threshold -

VCC5_OV Overvoltage threshold -

t

flt_VCC5_UVOV

I

VCC5

C

VCC5

C

ESR Output capacitor ESR - 0.01 - 0.1 Ω

VCC5

dV

SR_ac

dV

LR_ac

R

DSon

Under/overvoltage filter

time

Output load current - 0 - 250 mA

Output capacitor - 2.2 4.7 20 µF

Line Transient

Response

Load Transient

Response

High side Rds_ON - - - 4 Ω

0mA ≤ I

250mA

--12-µs

All line, load;

dt = 10 µs

All line, load;

dt = 10 µs

VCC5

≤

4.88 5 5.12 V

VCC5 -

10%

VCC5 +

5%

-

-

VCC5 -

5%

VCC5 +

10%

-5% - 5% %

-5% - 5% %

VCC5_cur lim Current limitation - 300 - 600 mA

VCC5_oc Overcurrent threshold - 300 - 600 mA

VCC5_ilim_oc_delta Delta_Ilim_Oc

VCC5_cur_lim –

VCC5_oc

0.1 - 100 mA

V

V

32/109 DS12539 Rev 3

Page 33

L9396 Power supply

Table 13. VCC5 regulator electrical characteristics (continued)

Symbol Parameter Conditions Min Typ Max Unit

From 10% to 90%

t

softstart

Softstart time

of nominal output

345 - 1035 µs

voltage

T

JSDVCCx

T

HYS_TSDVCCx

Thermal Shutdown - 175 - 200 °C

Thermal Shutdown

hysteresis

-5-15°C

3.9 VCC regulator

This regulator provides a dedicated rail to supply µC I/Os. It can be configured via VCCSEL

pin to output either 3.3 V or 5 V. The VCC regulator has over and under voltage detections

and is also protected against short to ground and over temperature with shared thermal

sensor with VCC5.

The state of VCCSEL pin is latched at power up when VPREREG voltage exceeds the

VPREREG_UV threshold and stays latched until next POR event.

All electrical characteristics are valid for the following conditions unless otherwise noted:

-40 °C ≤ Tj ≤ +175 °C; V

Table 14. VCC regulator electrical characteristics

PREREG

_L(Min) ≤ VPREREG ≤ V

PREREG

_H(Max).

Symbol Parameter Conditions Min Typ Max Unit

VCC_L

VCC_H

VCCSEL_IH

VCCSEL_IL

VCCSEL_Ihys

Ipd_VCCSEL

VCC_UV

Regulated output

voltage

Regulated output

voltage

VCCSEL input high

voltage

VCCSEL input low

voltage

VCCSEL input

hysteresis

VCCSEL input Pull

down current

Undervoltage

threshold

VCC_OV Overvoltage threshold -

t

flt_VCC_UVOV

Under/overvoltage

filter time

0mA ≤ I

VCCSEL = ‘0’

VPREREG ≥ 6V, 0mA

≤ I

VCC

VCCSEL = ‘1’

-1.75--V

---0.75V

- 100 - 1000 mV

VCCSEL=3.3V 1 - 10 µA

-

--12-µs

≤ 100mA;

VCC

≤ 100mA;

3.220 3.3 3.380 V

4.88 5 5.12 V

VCC_x

- 10%

VCC_x

+ 5%

-

-

VCC_x -

5%

VCC_x +

10%

V

V

I

C

VCC

VCC

Output load current - 0 - 100 mA

Output capacitor - 2.2 4.7 20 µF

DS12539 Rev 3 33/109

108

Page 34

Power supply L9396

Table 14. VCC regulator electrical characteristics (continued)

Symbol Parameter Conditions Min Typ Max Unit

C

ESR Output capacitor ESR - 0.01 - 0.1 Ω

VCC

dV

SR_ac

dV

LR_ac

R

DSon

VCC_cur lim Current limitation - 125 - 240 mA

VCC_oc Overcurrent threshold - 125 - 240 mA

VCC_ilim_oc_delta Delta_Ilim_Oc

t

softstart

Line transient

response

Load transient

response

High side Rds_ON - - - 12 Ω

Softstart time

All line, load;

dt = 10 µs

All line, load;

dt = 10 µs

VCC_cur_lim –

VCC_oc

From 10% to 90% of

nominal output

voltage

-5% - 5% %

-5% - 5% %

0.1 - 100 mA

345 - 1035 µs

3.10 Protected battery switch

The device provides a fully protected switched battery output VB_SW, always active when

the device is not in stand-by mode and WD1 is correctly served. This functionality can be

used as further battery supply, e.g. for external sensors requiring battery level, or as a pullup voltage rail.

The output can be disabled through SPI. Should the VB_SW diagnostics detect an over

current condition, the output is turned off and the over current SPI fault is set. Once an overcurrent condition is detected, the output can only be re-enabled through SPI command,

when the fault disappears, writing the bit PROTECTED BATTERY SWITCH COMMAND at

1 after the related OVER CURRENT flag is cleared on read.

All electrical characteristics are valid for the following conditions unless otherwise noted:

-40 °C ≤ Tj ≤ +175 °C; 4.5 ≤ VB = VBATP ≤ 19 V.

Symbol Parameter Conditions Min Typ Max Units

- Saturation voltage

- Operating current - - - 150 mA

VB_SW_oc

VB_SW _cur lim Current limitation - 165 - 250 mA

VB_SW _ilim_oc_delta Delta_Ilim_Oc

Table 15. Protected battery switch electrical characteristics

Overcurrent

shutdown

VB – VB_SW @

max. current

-165-250mA

VB_SW_cur_lim –

VB_SW_oc

--0.5V

0.1 - 20 mA

34/109 DS12539 Rev 3

Page 35

L9396 Power supply

VBATP

IGN

ON

VPREREG

VCORE

VPREREG _UV

RESET

OFF

Ton

RESET

VCC

GADG1901171330PS

VCC5_UV

VCORE_UV

VCC_UV

VCC_dly

VCC5_dly

WAKE_FLT_up

St-by

VCC 5

Table 15. Protected battery switch electrical characteristics (continued)

Symbol Parameter Conditions Min Typ Max Units

-

Ileak

Shutdown delay

time

Off state leakage

current

-90-110µs

VB_SW off -1 - 1 µA

3.11 Power up and power down sequences

Wake-up signal turns on the device and initiates the regulator power up sequence as in the

figure below.

Figure 6. Power up sequence from wake up input

The device provides three different possibilities to stay in ON state:

a persistent high signal on IGN pin,

the setting of the POWERHOLD bit through SPI,

the refreshing of the KEEPALIVE bit through SPI within a specified time frame.

At each transition H->L on the wake-up pin the device enters the keep-alive mode for one

keep-alive period (KA_period).

DS12539 Rev 3 35/109

108

Page 36

Power supply L9396

VBATP

13.5V

VCC5_UV

VCC_UV

VPREREG

IGN

VCC5

VCC

RESET

WAKE_FLT_down

KA_period

VCORE

Tflt_VCC5_UVOV/Tflt_VCC_UVOV/Tflt_VCORE_VCOREFDBK_UVOV

VCORE_dly

VDD_UV/VINTA_UV

VDD/VINTA

POR

Tflt_ VDD_OV_UV / Tflt_ VINTA_OV_UV

GADG1901171502PS

If the device receives an SPI command to set the POWERHOLD bit within the first keepalive period the device remains awake. Similarly, if the device receives an SPI command to

refresh the KEEPALIVE bit within the first keep-alive period the device remains awake.

Once the KEEPALIVE bit is refreshed a new KA_period starts and so forth. To stay on the

keep-alive bit should be refreshed at each KA_period.

Should the KA_period elapse without any of the above 3 conditions, the device exits the

keep-alive mode and enters in power down.

The power down sequence depends on the keep alive choice being done.

In the following figure, the power down sequence related to a H->L transition on the wake-

up input pin without SPI conditioning is shown.

Figure 7. Power down sequence from wake up input

Table 16. Power up and power down

Symbol Parameter Conditions Min Typ Max Units

VCC5_dly

VCC_dly

VCORE_dly

VCC5 delay at

power-up

VCC delay at

power-up

VCORE delay at

power-down

Ton_RESET RESET hold time

From VPREREG_UV to VCC5

start

From VPREREG_UV to VCC

start

From end of KA_period

VCORE switch off

From regulators in range to

RESET High

to

-200 - µs

-200 - µs

-200 - µs

11 12 13 ms

36/109 DS12539 Rev 3

Page 37

L9396 Pre-drivers

4 Pre-drivers

4.1 Fail safe pre-driver

The device integrates a pre-driver of an external FET for fail safe purposes. It can be used

as a HS pre-driver in case the external FET is used as a switch. The device controls the fail

safe pre-driver in On/Off via SPI. The function remains active while no internal voltage faults

or watchdog faults are detected.

This pre-driver implements a monitor against over current thanks to the diagnostics on

drain-source monitoring of the external FET (in case of overcurrent SPI bit 15 of

DRV_CONTROL_1 register goes high). If charge pump level goes below the disable

voltage, the pre-driver is turned off. When the level returns above the disable voltage, the

pre-driver returns to normal operation.

Symbol Parameter Conditions Min Typ Max Units

VDG_ON VDG On voltage (VDG-VDS)@-0.1mA 5.2 - 12 V

VDG_OFF VDG Off voltage (VDG-VDS)@0.1 mA - - 1 V

Rpd_VDG_VDS

VDG_Isource VDG current source

Table 17. Fail Safe pre-driver electrical characteristics

Pull down resistor at VDGVDS

-130-270kΩ

V(VDG)=V(VDS)

V(CP)– V(VDG)=2V

0.2 1 2 mA

VDG_Isink VDG current sink V(VDG)-V(VDS)=1V 1 5 9 mA

QFS_turn-on_00

QFS_turn-on_01

QFS_turn-on_10

QFS_turn-on_11

IVDBATT_ds

t

QFS_ON

QFS turn-on threshold

voltage

QFS turn-on threshold

voltage

QFS turn-on threshold

voltage

QFS turn-on threshold

voltage

VDBATT leakage current

for drain-source monitor

Filter time of QFS turn-on guaranteed by scan - 12 - µs

V(VDBATT) – V(VDS)

VDS_TH=’00’

V(VDBATT) – V(VDS)

VDS_TH=’01’

V(VDBATT) – V(VDS)

VDS_TH=’10’

V(VDBATT) – V(VDS)

VDS_TH=’11’

FAIL SAFE DRIVER

ENABLE=0

0.25 - 0.75 V

0.75 - 1.25 V

1.25 - 1.8 V

1.75 - 2.4 V

7 - 67 µA

DS12539 Rev 3 37/109

108

Page 38

Pre-drivers L9396

4.2 Pump motor pre-driver

The device can drive a pump motor through this pre-driver for external FETs. It provides predriver circuitry for the motor high-side FET and the motor recirculation FET.

The PDG gate drive signal is referenced to PDS, and the pre-driver pair shall be able to float

below the logic ground voltage, while keeping full on/off control on the external FET. This is

required to prevent the FET from being partially turned on in the case of a ground offset

between ECU and motor ground, or in case of loss of ECU ground.

Similarly, the PRG gate drive signal shall be referenced to PRS, and the pre-driver pair shall

be able to float below the logic ground voltage, while keeping full on/off control on the

external recirculation FET.

The motor FET pre-drivers shall be controlled by logic level input pins PDI and PRI, with

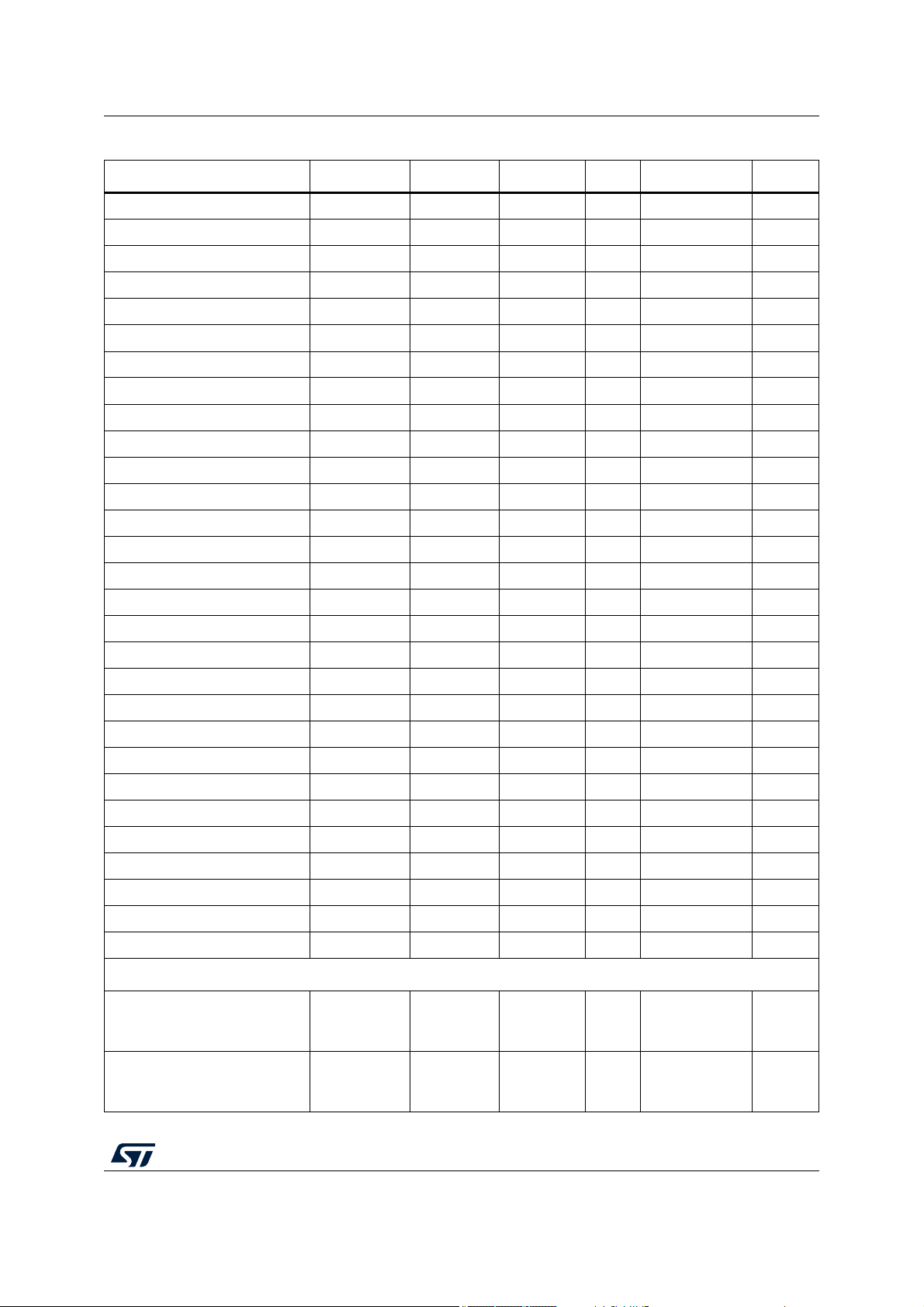

logical operation defined as:

PDI PRI PDG PRG High-side FET Recirculation FET

L L L L OFF OFF

H L H L ON OFF

L H L H OFF ON

H H H L ON OFF

Table 18. Logical operation definition

The state of the PDI and PRI pins can be observed via SPI.

The device is able to generate software selectable dead time between PDG and PRG

transitions, to prevent cross-conduction on the external FETs.

In order to enable either PDG or PRG the following conditions must be met: