Page 1

®

DALC208SC6

Application Specific Discretes

A.S.D.

MAIN APPLICATIONS

Where ESD and/or over and undershoot protection

for datalines is required :

Sensitive logic input protection

Microprocessor based equipment

Audio / Video inputs

Portable electronics

Networks

ISDN equipment

USB interface

DESCRIPTION

The DALC208SC6 diode array is designed to

protect components which are connected to data

and transmission lines from overvoltages caused

by electrostatic discharge (ESD) or other

transients. It is a rail-to-rail protection device also

suited for overshoot and under shoot suppression

on sensitive logic inputs.

The low capacitance of the DALC208SC6

prevents from significant signal distortion.

TM

LOW CAPACITANCE

DIODE ARRAY

1

SOT23-6L (SC74)

FUNCTIONAL DIAGRAM

FEATURES

PROTECTION OF 4 LINES

PEAK RE VER SE V OLTA GE :

= 9 V per diode

V

RRM

VERY LOW CA PA CIT ANCE PER DIODE:

C < 5 pF

VERY LOW LEAKAGE CURRE NT: IR < 1 µA

BENEFITS

Cost-effectiveness compared to discrete solution

High efficiency in ESD s uppression

No significant signal distortion thanks to very low

capacitance

High reliability offered by monolithic integration

Lower PCB area consumption versus discrete

solution

February 1999 - Ed: 3A

I/O 1

REF 2 REF 1

I/O 2 I/O 3

COMPLIES WITH THE FOLLOWING STANDARDS :

IEC 1000- 4-2 level 4

MIL STD 883C - M ethod 3015-6

(human body test) class 3

I/O 4

1/10

Page 2

DALC208SC6

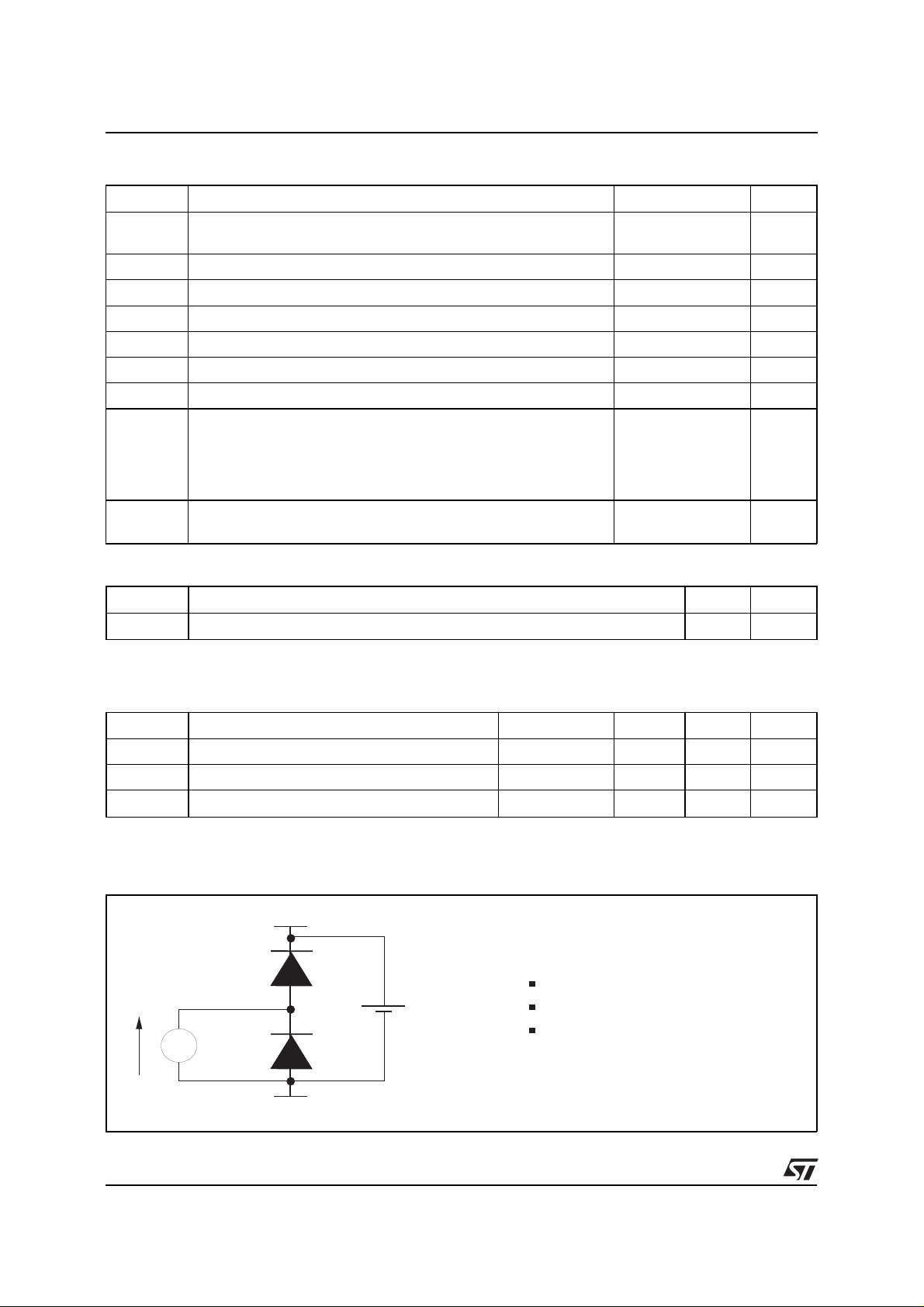

ABSOLUTE MAXIMUM RATINGS

(T

= 25° C) .

amb

Symbol Parameter Value Unit

V

PP

IEC1000-4-2, air discharge

IEC1000-4-2, contact discharge

V

RRM

∆

V

REF

max.

V

In

min. Minimum operating signal input voltage V

V

In

I

F

I

FRM

I

FSM

Peak reverse voltage per diode 9 V

Reference voltage gap between V

REF2

and V

REF1

Maximum operating signal input voltage

Continuous forward current (single diode loaded) 200 mA

Repetitive peak forward current (tp = 5 µs, F = 50 kHz)

Surge non repetitive forward current -

15

8

9V

V

REF2

REF1

700 mA

rectangular waveform (see curve on figure 1)

t

= 2.5 µs

p

= 1 ms

t

p

= 100 ms

t

p

T

stg

T

j

Storage temperature range

Maximum junction temperature

6

2

1

-55 to + 150

150

THERMAL RESISTANCE

Symbol Parameter Value Unit

R

th(j-a)

Note 1:

device mounted on FR4 PCB with recommended footprint dimensions.

Junction to ambient (note 1)

500 ° C/W

kV

V

V

A

°

°

C

C

ELECTRICAL CHARACTERI STICS

(T

= 25° C) .

amb

Symbol Parameter Conditions Typ. Max. Unit

V

F

I

R

C

Note 2:

The dynamical behavior is described in the Technical Information section, on page 4.

Note 3:

Forward voltage IF = 50 mA 1.2 V

Reverse leakage current per diode VR = 5 V 1

Input capacitance between Line and G ND see note 3 7 pF

Input capacitance measurement

REF2

REF1 connected to GND

I/O

+V

CC

REF2 connected to +Vcc

Input applied :

R

V

G

Vcc = 5V,Vsign = 30 mV, F = 1 MH z

REF1

µ

A

2/10

Page 3

DALC208SC6

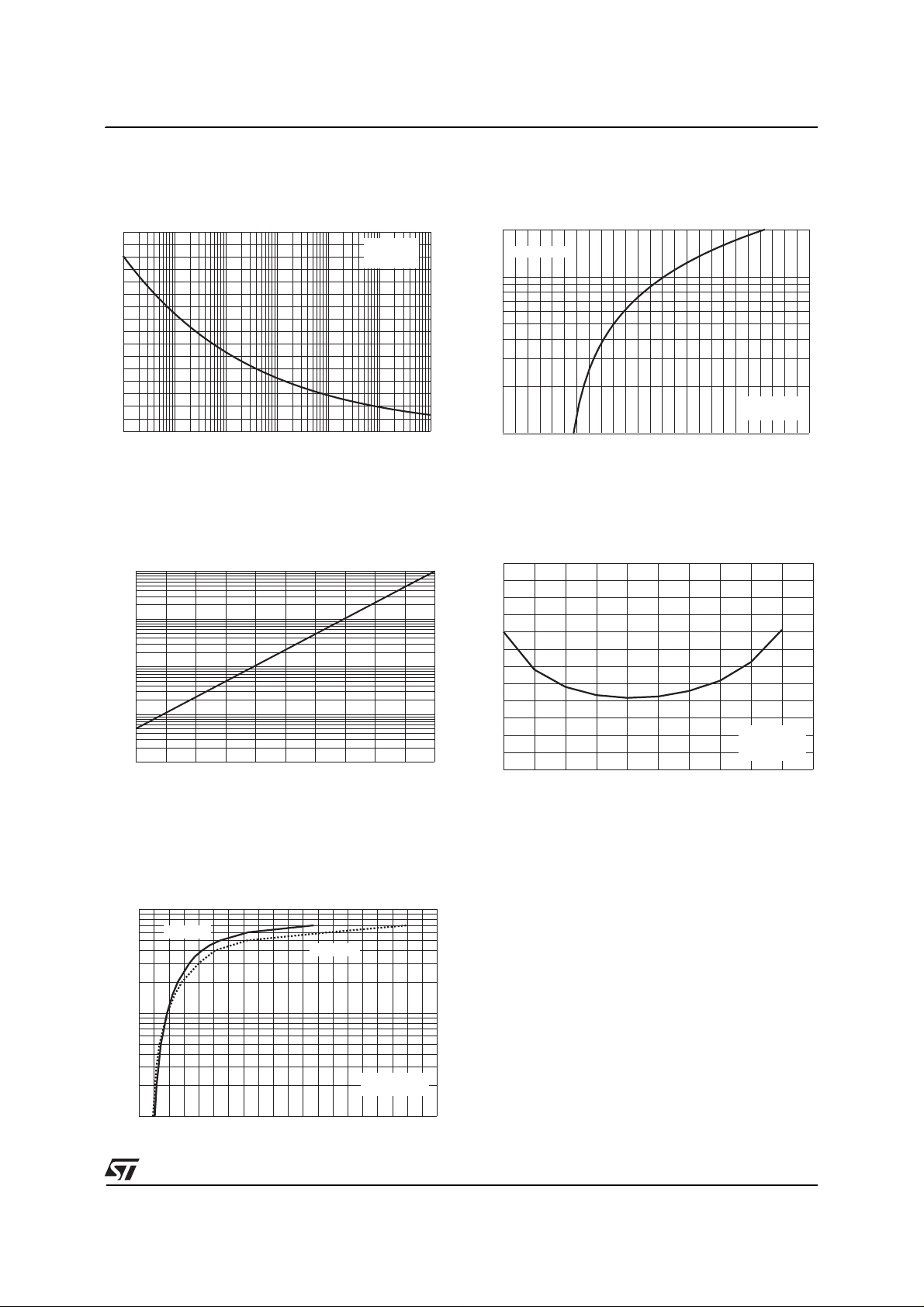

Fig. 1:

Maximum non-repet itive pea k forwar d curre nt

versus rec tangular puls e duration (Tj initial = 25°C).

IFSM(A)

8

7

I/O vs

REF1 or

REF2

6

5

4

3

2

1

0

0.001 0.01 0.1 1 10 100 1000

tp(ms)

Fig. 3:

Variation of leakage current versus junction

temperature (typical values).

IR(µA)

100

10

Fig. 2:

Reverse clamping voltage versus peak

pulse current (Tj initial = 25°C), typical values.

Rectangular waveform tp = 2.5 µs.

Ipp(A)

2.0

tp=2.5µs

1.0

I/O vs REF1

or REF2

0.1

5 1015202530

Vcl(V)

Fig. 4:

Input capacitance versus reverse applied

voltage (typical values).

C(pF)

8.0

7.5

7.0

1

0.1

0.01

25 50 75 100 125 150

Tj(°C)

Fig. 5:

Peak forward voltage drop versus peak forward current (typical values).

Rectangular waveform tp = 2.5 µs.

IFM(A)

10.0

Tj=25°C

Tj=150°C

1.0

I/O vs REF 1

or REF2

6.5

6.0

5.5

5.0

012345

F=1MHz

Vsign=30mV

Vref1/ref2=5V

VR(V)

0.1

0 2 4 6 8 10 12 14 16 18 20

VFM(V)

3/10

Page 4

DALC208SC6

TECHNICAL INFORMA TION

SURGE PROTECTION

The DALC208SC6 is particularly optimized to

perform surge protection based on the rail to rail

topology.

The clamping voltage V

follow :

+ = V

V

CL

- = V

V

CL

with : V

(V

= Vt + rd.Ip

F

forward drop voltage) / (Vt forward drop

F

REF2

REF1 -

+ V

threshold voltage)

can be calculated as

CL

for positive surges

F

VF for negative surges

APPLICATION EXAMPLE

If we consider that the connections from the pin

REF

to VCC and from REF1 to GND are done by

2

two tracks of 10mm long and 0.5mm large; we

assume that the parasitic inductances of these

tracks are about 6nH.

So when an IEC 1000-4-2 surge occurs, due to the

rise time of this spike (tr=1ns), the voltage V

CL

has

an extra value equal to Lw.dI/dt.

The dI/dt is calculated as: di/dt = Ip/tr ≈ 24 A/ns

The overvoltage due to the parasitic inductances

is: Lw.di/dt = 6 x 24 ≈ 144V

According to the curve Fig.5 on page 3, we

assume that the value of the dynamic resistance of

the clamping diode is typically rd = 0.7Ω and V

=

t

1.2V.

For an IEC 1000-4-2 surge Level 4 (Contact

Discharge: Vg=8kV, Rg=330Ω), V

V

= 0V, and if in first approximation, we

REF1

REF2

= +5V,

assume that : Ip=Vg/Rg ≈ 24A.

So, we find:

+ ≈ +23V

V

CL

V

- ≈ -18V

CL

Note:

the calculations do not take into account

phenomena due to parasitic inductances

Fig. A1:

ESD behavior; parasitic phenomena due to unsuitable layout.

ESD

SURGE

Vf

I/O

By taking into account the effect of these parasitic

inductances due to unsuitable layout, the clamping

voltage will be :

+ = +23 + 144 ≈ 167V

V

CL

V

- = -18 - 144 ≈ -162V

CL

We can reduce as much as possible these

phenomena with simple layout optimization.

It’s the reason why some recommendations have

to be followed (

good ESD protection"

Lw

Lw

di

dt

REF2=+Vcc

see paragraph "How to ensure a

).

4/10

167V

Lw

Vcc+Vf

di

Lw

Lw

dt

-Vf

di

dt

-162V

di

dt

tr=1ns

surge >0

surge <0

t

NEGATIVE

SURGE

Vcl-

Vcc+Vf+

Vcl+ =

VI/O

Vcl+

di

dt

tr=1ns

di

Lw

dt

POSITIVE

SURGE

REF1=GND

Vcl- =

t

-Vf-

-Lw

Page 5

DALC208SC6

HOW TO ENSURE A GOOD ESD PROTECTION

While the DALC208SC6 provides a high immunity

to ESD surge, an eff icient protection depends on

the layout of the board. In the same way, with the

rail to rail topology, the track from the V

the power supply +V

and from the V

CC

REF2

REF1

pin to

pin to

GND must be as short as possible to avoid

overvoltages due to parasitic phenomena (see Fig.

A1).

It’s often harder to connect the power supply near

to the DALC208SC6 unlike the ground thanks to

the ground plane that allows a short connection.

To ensure the same efficiency for positive surges

when the connections can’t be short enough, we

recommend to put close to the DALC208SC6,

between V

and ground, a capacitance of

REF2

100nF to prevent from these kinds of overvoltage

disturbances (see Fig. A2).

The add of this capacitance will allow a better

protection by providing during surge a constant

voltage.

Fig. A3, A4a and A4b show the improvement of the

ESD protection according to the recommendations

described above.

Fig. A2:

ESD behavior: optimized layout and add

of a capacitance of 100nF.

C=100nF

Lw

REF2=+Vcc

ESD

SURGE

Fig. A3:

ESD behavior: measurements conditions

(with coupling capacitance).

TEST BOARD

DALC

208

+5V

Fig. A4a:

DALC208SC6 during positive ESD surge.

Remaining voltage after the

IEC 1000-4-2

Air Discharge

(150pF/330Ω)

Vpp=15kV

ESD

SURGE

I/O

Vcc+Vf

VI/O

Vcl+

Vcl+ =

Vcl- =

REF1=GND

POSITIVE

SURGE

t

-Vf

surge >0

surge <0

t

NEGATIVE

SURGE

Vcl-

Important:

A main precaution to take is to put the protection

device closer to the disturbance source (generally

the connector).

Note:

The measurements have been done with the DALC208SC6

in open circuit.

Fig. A4b:

Remaining voltage after the

DALC208SC6 during negative ESD surge.

IEC 1000-4-2

Air Discharge

(150pF/330Ω)

Vpp=15kV

5/10

Page 6

DALC208SC6

CROSSTALK BE HAV IOR

1- Crosstalk phenomena

Fig. A4:

Crosstalk phenomena.

V

G1

V

G2

R

G1

R

G2

DRIVERS

Line 1

Line 2

The crosstalk phenomena are due to the coupling

between 2 lines. The coupling factor (β12 or β21)

increases when the gap across lines decreases,

particularly in silicon dice. In the example above

the expected signal on load R

L2

is

2VG2

, in fact

α

the real voltage at this point has got an extra value

β

. This part of the VG1 signal represents the

21VG1

effect of the crosstalk phenomenon of the line 1 on

the line 2. This phenomenon has to be t aken into

account when the drivers impose fast digital data

or high frequency analog signals in the disturbing

line. The perturbed line will be more affected if it

works with low voltage signal or high load

impedance (few kΩ). The following chapters give

the value of both digital and analog crosstalk.

R

L2

RECEIVERS

β

α

V

V

+

R

L1

1

α

β

+

V

G2

21

2

G2

G1

12

V

G1

2- Digital Crosstalk

Fig. A5:

Square

Pulse

Generator

5KHz

Digital crosstalk measurements.

+5V

+5V +5V

74HC04

Line 1

V

Line 2

G1

+5V

DALC208SC6

β

100nF

21

V

G1

74HC04

Figure A5 shows the measurement circuit used to

quantify the crosstalk effect in a classical digital

application.

Figure A6 shows that in such a condition: signal

from 0V to 5V and a rise time of 5 ns, the impact on

the disturbed line is less than 100mV peak to peak.

No data disturbance was noted on the concerned

line. The same results were obtained with falling

edges.

Note:

The measurements have been done in the worst case i.e. on

two adjacent cells (I/O1 & I/O4).

Fig. A6:

Digital crosstalk results.

6/10

Page 7

3- Analog Crosstalk

DALC208SC6

Fig. A7:

Analog crosstalk measurements.

TRACKING GENERATOR

50

Ω

+5V

Vg

Vin

TEST BOARD

C=100nF

Figure A7 gives the measurement circuit for the

analog application. In usual frequency range of

analog signals (up to 100MHz) the effect on

disturbed line is less than -45 dBm (please s ee Fig.

A8).

Fig. A8:

dBm

Analog crosstalk results.

0

-20

-40

-60

DALC

208

Fig. A9:

TRACKING GENERATOR

Vg

SPECTRUM ANALYSER

50

Ω

Vout

Measurement conditions.

Vin

+5V

TEST BOARD

C=100nF

DALC

208

50

Ω

SPECTRUM ANAL YSER

Vout

50

Ω

-80

-100

1 10 100 1,000

f(MHz)

As the DALC208SC6 is designed to protect high

speed data lines, it must ensure a good

transmission of operating signals. The attenuation

curve give such an information.

Fig. A10 shows that the DALC208SC6 is well

suitable for data line transmission up to 100 M bit/s

while it works as a filter for undesirable signals as

GSM (900MHz).

Fig. A10:

DALC206SC6 attenuation.

dBm

0

-10

-20

-30

1 10 100 1,000

f(MHz)

7/10

Page 8

DALC208SC6

APPLICATION EXAMPLES

Video line protection

T1/E1 protection

Tx

SMP75-8

100nF

Rx

SMP75-8

+Vcc

100nF

100nF

+Vcc

+Vcc

5

15

DALC

208

DALC

208

DALC

1

208

DAT A

TRANSCEIVER

Pin N° Signal

1 RED VIDEO

2 GREEN VIDEO

or COMPOSITE SYNC with GREEN VIDEO

3 BLUE VIDEO

4 GROUND

5 DDC (Display Data Channel) GROUND

6 RED GROUND

7 GREEN GROUND

8 BLUE GROUND

9 NC

10 SYNC GROUND

11 GROUND

12 SDA (Sérial Data)

13 HORIZONTAL SYNC

14 VERTICAL SYNC (VCLK)

15 SCL (Serial Clock)

or COMPOSITE SYNC

USB port protection

VBUS

D+

DGND

+V

100nF

VBUS

D+

DGND

DALC

208

15k 15k

+V

1.5k

(1)

(1) Full speed

(2) Low speed

1.5k

(2)

USB

TRANSCEIVER

only

only

USB

TRANSCEIVER

Another way to connect the DALC208SC6

I/O2

I/O1

DALC208

I/O3

GND

I/O4

Note It's absolutely necessary to connect

the pin 5 (REF1) to GND !

8/10

Page 9

PSPICE MODEL

DALC208SC6

Fig. A11:

PSpice model of one DALC208SC6 cell.

Vref2

0.8nH

0.3Ω

Dpos

0.8nH 0.3Ω

I/O

Dneg

0.5Ω

1.45nH

Vref1

Figure A11 shows the PSpice model of one

DALC208SC6 cell. In this model, the diodes are

defined by the PSpice parameters given in table

below (Fig A12).

Fig. A12:

PSpice parameters.

DPOS DNEG

BV

CJO

IBV

IKF

IS

ISR

M

N

NR

RS

VJ

99

7p 7p

1u 1u

28.357E-3 1000

118.78E-15 5.6524E-9

100E-12 472.3E-9

0.3333 0.3333

1.3334 2.413

22

0.68377 0.71677

0.6 0.6

Fig. A13a:

PSpice model simulation: surge > 0

IEC 1000-4-2 contact dis charge r esponse.

Current (A) /Voltage (V )

60

50

40

30

20

10

0

0 50 100

t(ns)

Fig. A13b:

PSpice model simulation: surge < 0

Current

V oltage

IEC 1000-4-2 contact dis charge r esponse.

Current (A) /Voltage (V )

0

-10

-20

-30

-40

-50

0 50 100

t(ns)

Fig. A14:

dBm

0

-10

Attenuation comparison.

Current

V oltage

Measured

Surge

I/O

Surge

I/O

PSpice

Note:

This simulation mo del is available only for an ambient tem-

perature of 27°C.

The simulations done (Fig. A13, A14, A15) shows

that the PSpice model is close to the product

behavior.

-20

-30

1 10 100 1,000

f(MHz)

9/10

Page 10

DALC208SC6

MARKING

Type Marking Order Code Packaging (Base Qty)

DALC208SC6 DALC DALC208SC6 tape & r eel ( 3000)

PACKAGE MECHANICAL DATA

SOT23-6L (Plastic)

H

e

D

e

L

M

E

FOOTPRINT DIMENSIONS

b

c

(in millimeters)

0.65

0.025

A

A2

A1

DIMENSIONS

REF.

Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 0.90 1.45 0.035 0.057

A1 0 0.15 0 0.006

A2 0.90 1.30 0.035 0.0512

b 0.35 0.50 0.0137 0.02

C 0.09 0.20 0.004 0.008

D 2.80 3.00 0.11 0.118

E 1.50 1.75 0.059 0.0689

e 0.95 0.0374

H 2.60 3.00 0.102 0.118

L 0.10 0.60 0.004 0.024

M 10° 10°

1.3

0.051

1

0.040

3.6

0.137

0.95

0.037

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of

use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by

implication or otherwi se un der any pat ent or patent rights of STMic roelec tronics. S pecifications ment ioned in t his publ ication are subject to

change without notice. This publication supersedes and replaces all information previously supplied.

STMicroelectronics products ar e not authorized for use as crit ic al components in life support devices or systems wi thout express wri tten approval of STMicroelectronics.

mm

inch

The ST logo is a registered trademark of STMicroe lectronics

© 1999 STMicroelectronics - Printed in Italy - All rights reser ved.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco -

The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com

10/10

Loading...

Loading...