MACH2 PARALLEL ATA

2.5-INCH SOLID STATE DRIVE

PRODUCT MANUAL

Export Administration Regulations

This document may contain technica l data con trolled by the U .S. Ex port Adm inistration Regula tions, and

may be subject to the approval of the U.S. Department of Commerce prior to export. Any export, directly or

indirectly, in contravention of the U.S. Export Administration Regu lation is prohibited.

Trademark Information

The STEC name, logo and design are trademarks of STEC Inc. No right, license, or interest to suc h

trademarks is granted hereunder, and you agree that no such right, license, or interest shall be asserted by

you with respect to such trademark. O ther produ ct and corpora te names me ntioned in this docume nt are

used for identification purposes only and may be trademarks or registered trademarks of their respective

companies.

Disclaimer of Liability

The performance information and specifications furnished in this document reflect the engineering

development objectives of STEC Inc. and should be us ed for comparative analysis and reference purposes.

The content of this document is accurate as of th e date of this publication; however, the inf ormation

contained herein, including but not limited to any instructions, description s and product specific ations, is

subject to change without prior notice.

STEC INC. (STEC) PROVIDES NO WARRANTY WITH REGARD TO THIS DOCUMENT OR

ANY OTHER INFORMATION CONTAINED HEREIN AND HEREBY EXPRESSLY DISCLAIMS

ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY

PARTICULAR PURPOSE WITH REGARD TO ANY OF THE FOREGOING. STEC INC.

ASSUMES NO LIABILITY FOR ANY DAMAGES INCURRED DIRECTLY OR INDIRECTLY

FROM ANY TECHNICAL OR TYPOGRAPHICAL ERRORS OR OMMISSIONS CONTAINED

HEREIN. IN NO EVENT SHALL STEC INC. BE LIABLE FOR ANY INCIDENTAL,

CONSEQUENTIAL, SPECIAL, OR EXEMPLARY DAMAGES, WHETHER BASED ON TORT,

CONTRACT OR OTHERWISE, ARISING OUT OF OR IN CONNECTION WITH THIS

DOCUMENT OR ANY OTHER INFORMATION CONTAINED HEREIN OR THE USE

THEREOF.

Copyright Notice

Copyright © 2007 by STEC Inc. All rights reserved. Informa ti on c ontained in this document, including but

not limited to any instructions, descriptions and product specifications, is proprietary to STEC Inc. and shall

not be modified, used, copied, reproduced or disclose d in whole or in part, in any form or by any mean s,

electronic or mechanical, for any purpose, without the wri tt en c onse nt of STEC Inc.

ii MACH2 2.5-Inch ATA Solid State Drive

PRELIMINARY/CONFIDENTIAL

CONVENTIONS

The following icons are used throughout this document to identify additional information

of which the reader should be aware.

SHOCK HAZARD: This icon indicates the danger of

an electrical shock that may harm or otherwise prove

fatal to the user.

CAUTION: This icon indicates the exis tence of a

hazard that could result in equipment or prop erty

damage or equipment failure if the safety instruction

is not observed.

ELECTROSTATIC DISCHARGE: This icon indicates

the possible presence of Electrostatic Discharge

(ESD or “static electricity”) that may harm the

internal electronic components. The us er is a dvised

to handle the device only after discharging any

possible electrostatic buildup that may be present.

NOTE: This icon identifies information that relates to

the safe operation of the equipment or related items.

TIP: This icon identifies helpful hints and tips.

MACH2 2.5-Inch ATA Solid State Drive iii

PRELIMINARY/CONFIDENTIAL

iv MACH2 2.5-Inch ATA Solid State Drive

PRELIMINARY/CONFIDENTIAL

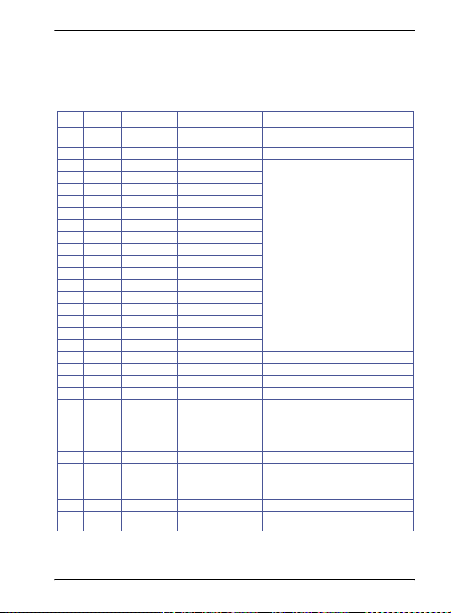

REVISION HISTORY

Revision Status Summary Sheet

Revision Date Sheet(s) Affected

1.0 07/10/2007 Official release.

1.1 08/10/2007 Page 59: Warranty period updated.

1.2 10/10/2007 Page 53: Updated contact and ordering information.

1.3 11/01/2007 Page 33: Added “Identify Device Command Output” topic and table.

1.4 11/09/2007 Pages 23 - 24. Added S.M.A.R.T. Support, Commands and Attributes topics

1.5 01/24/2008 Pages 2 and 7: Corrected Burst Transfer Rate to 100MB/sec.

MACH2 2.5-Inch ATA Solid State Drive v

respectively.

PRELIMINARY/CONFIDENTIAL

vi MACH2 2.5-Inch ATA Sol id State Drive

PRELIMINARY/CONFIDENTIAL

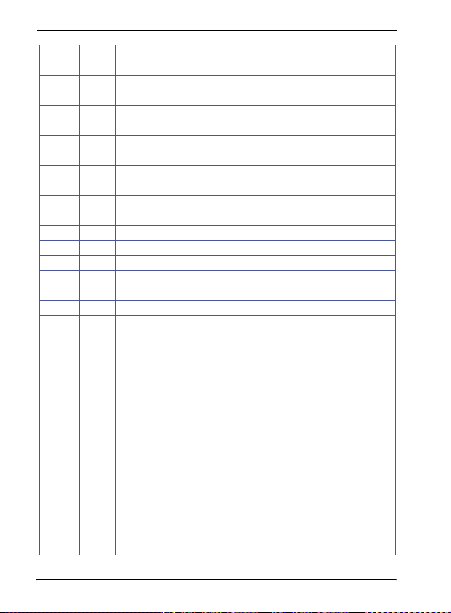

TABLE OF CONTENTS

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iii

Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .v

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xii

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiv

Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Feature Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Standards and Reference Documents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Commercial Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Reference Documents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Manufacturing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Product Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

General Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

ATA Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Drive Capacities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Performance Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

ATA Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Endurance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Wear-Leveling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Bad-Block Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Data Retention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Error Detection and Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Reliability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Error Rates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Built-In Self Test (BIST). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Mount Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

MACH2 2.5-Inch ATA Solid State Drive vii

PRELIMINARY/CONFIDENTIAL

Seek Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Data Transfer Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Repairs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Preventative Maintenance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Power Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Start-Up Time and Current Draw. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Activity LED. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Power-On Ready Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Power Savings Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Power Mode at Power On . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Interface Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

SSD Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Write Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Read Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Primary and Secondary Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

I/O Primary and Secondary ATA (IDE) Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Addressing Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

44-Pin ATA Bus Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Connector Pinout Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

ATA Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Standard ATA Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Standard ATA Command Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

S.M.A.R.T. Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

S.M.A.R.T. Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

S.M.A.R.T. Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

viii MACH2 2.5-Inch ATA Solid State Drive

PRELIMINARY/CONFIDENTIAL

Identify Device Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Identify Device Command Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Vendor-Specific ATA Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Physical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

General Physical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Drive Assembly Weight . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Storage Capacities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Exterior Dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Connector Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Environmental Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Operating Temperatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Operating Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Non-Operating Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Relative Humidity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Altitude Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Restriction of Hazardous Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Shock and Vibration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Failure Criteria. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Random Vibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 2

Shock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Drop Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Conformal Coating (Optional) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

System Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Drive Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Jumper Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Drive Orientation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

MACH2 2.5-Inch ATA Solid State Drive ix

PRELIMINARY/CONFIDENTIAL

Primary Heat Generation Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Cooling Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Installation Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Mounting Hole Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Drive Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Grounding Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Operating System Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Microsoft OS Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Non-Microsoft OS Compatibility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

System POST, Boot and Resume Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Diagnostic Software. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Default S.M.A.R.T. Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Regulatory Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Marks, Approvals and Documentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Electromagnetic Susceptibility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Electromagnetic Compatibility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

CB Certificate and CB Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Declaration of Conformity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Radio Frequency Emissions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Radio Frequency Immunity Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

EMI Test Site Correlation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Verification Samples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Verification Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Electrostatic Discharge (ESD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Acceptance Criteria Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

x MACH2 2.5-Inch AT A Solid State Drive

PRELIMINARY/CONFIDENTIAL

Contact and Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Certification and Warranty . . . . . . . . . . . . . . . . . . . . . . . . . . Inside Back Cover

MACH2 2.5-Inch ATA Solid State Drive xi

PRELIMINARY/CONFIDENTIAL

LIST OF TABLES

1. ATA Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2. Endurance Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3. Error Limits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4. Data Transfer Rates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

5. SSD Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

6. SSD Typical Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

7. Start-Up Time and Current Draw . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

8. ATA (IDE) Bus Addressing Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

9. ATA Connector Pinout Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

10. Supported ATA Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

11. ATA Command Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

12. S.M.A.R.T. Command Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

13. Supported S.M.A.R.T. Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

14. Identify Device Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

15. ECh Command Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

16. SSD Capacities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

17. Drive Assembly Dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

18. Operating Temperatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

19. Operating Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

20. Non-Operating Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

21. Relative Humidity Criteria. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

22. Operating and Non-Operating Altitudes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

23. Random Vibration Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

24. Shock Test Results. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

25. ATA (IDE) Cable Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

26. Default SMART Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

27. Regulatory Marks and Documentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

xii MACH2 2.5-Inch ATA Solid State Drive

PRELIMINARY/CONFIDENTIAL

28. EMI Specification Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

29. ESD Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

30. Acceptance Criteria Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

MACH2 2.5-Inch ATA Solid State Drive xiii

PRELIMINARY/CONFIDENTIAL

LIST OF FIGURES

1. The MACH2 2.5-Inch ATA Solid State Drive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Start-Up Current Draw . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3. 44-pin ATA (IDE) Bus Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4. SDD Exterior Dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5. ATA Connector Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6. Primary/Secondary Jumper Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7. Possible Drive Orientations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

8. Primary Heat Generation Area. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

9. Suggested Air Flow Patterns for Cooling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10. Exterior Mounting Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

11. Mounting Hole Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

xiv MACH2 2.5-Inch AT A Solid State Drive

PRELIMINARY/CONFIDENTIAL

SCOPE

Overview

Figure 1. The MACH2 2.5-Inch ATA Solid State Drive

This datasheet describes the applications, specifications, and installation of the MACH2 2.5-inch ATA

Solid State Drive (SSD). See Figure 1.

Audience

This datasheet is intended for system engineers or system designers employed by an Original

Equipment Manufacturer (OEM). This datasheet was therefore written specifically for a technically

advanced audience; it is not intended for end-users that will eventually purchase the commercially

available product. The user, as referenced throughout this document, is primarily concerned with

industrial, commercial, or military computing applications.

MACH2 2.5-Inch ATA Solid State Drive 1

PRELIMINARY/CONFIDENTIAL

Feature Overview

Feature Description

Form Factor 2.5-Inch

ATA Interface ATA 6 or higher

Connector 44-Pin IDE/ATA (40/80 conductor)

Drive Capacities 4, 8, 16 and 32 gigabytes

Operating Voltage 5.0V +/-5%

Operating Temperature -40oC to +85oC

Average Latency 0.5 msec

Burst Transfer Rate 100MB/sec

Sustained Read Throughput 35MB/sec

Sustained Write Throughput 25MB/sec

Wear-Levelling Dynamic and static algorithms

Bad-Block Management 2% reserve of total flash capacity

EDC/ECC Correction: up to 4 bytes; Detection: up to 5 bytes

Data Retention 10 years storage

RoHS Compliance Pb-free components

Warranty 2 years

2 MACH2 2.5-Inch ATA Solid State Drive

PRELIMINARY/CONFIDENTIAL

Standards and Reference Documents

This section discusses the formal standards that may apply to the SSD, including electrical product

standards and military information security standards. In addition, this section lists reference

documents relevant to the ATA protocols used for the SSD.

Commercial Standards

The SSD complies, in whole or in part, with the following commercial standards:

S/NZS 3548 Class B Underwriters Laboratories (UL)

BSMI CNS 13438 Class B NEBS Level 3

CAN/CAS-V3/2001.04 (VCCI) IEC 61000-4-2

CE (Conformite Europenne) IEC 61000-4-3

CISPR 22 Class B IEC 61000-4-4

EN 55022 Class B IEC 61000-4-5

EN 61000-3-2 IEC 61000-4-6

EN 61000-3-3 IEC 61000-4-8

FCC Part 15 Class B IEC 61000-4-11

Reference Documents

The following list of ANSI documents are relevant to the SSD:

INCITS T13 1321 D Information Technology - AT Attachment with Packet

INCITS T13 e01122r0 Erratum

INCITS T13 1401 D Information Technology - AT Attachment with Packet

INCITS T13 1532 D Information Technology - AT Attachment with Packet

Interface - 5 (ATA/ATAPI-5)

Interface - 6 (ATA/ATAPI-6)

Interface - 7, Volumes 1, 2 and 3 (ATA/ATAPI-7)

Manufacturing

Location Certifications

Santa Ana, California ISO 9001 Certified

United States of America ISO 14001 Certified

MACH2 2.5-Inch ATA Solid State Drive 3

PRELIMINARY/CONFIDENTIAL

PRODUCT DESCRIPTION

General Description

The MACH2 2.5-inch ATA Solid State Drive (SSD) is a non-volatile mass storage device. The drive

is intended as replacement for a standard ATA-compliant hard disk drive (HDD). The drive can be

configured as a boot or data storage device. The drive is Plug and Play (PnP) compatible; no

additional device drivers are required to install the drive. The SSD is recognized by PnP-compatible

operating systems and PnP-aware BIOS.

ATA Interface

The SSD can be installed in any operating system environment that supports ATA-6 or greater

devices. The SSD has a fully ATA/ATAPI-6 compliant 44-pin interface and can be configured for

Primary/Secondary (Device 0/Device 1) device mode operation.

Drive Capacities

The SSD is available in unformatted memory capacities of 4, 8, 16 and 32 gigabytes. The memory

consists of Single-Level Cell (SLC) NAND Flash components.

Performance

The SSD can operate at sustained data transfer rates of up to 35 MB per second. Power consumption

is kept to a minimum; the SSD can be powered from a single 5-volt source. The solid state design

eliminates electromechanical noise and delay inherent in traditional magnetic rotating media. The

wear-leveling and bad-block mapping algorithms ensure data integrity; the embedded Error

Detection and Error Correction Code (EDC/ECC) ensures data reliability.

4 MACH2 2.5-Inch ATA Solid State Drive

PRELIMINARY/CONFIDENTIAL

PERFORMANCE CHARACTERISTICS

ATA Modes

Table 1 lists the ATA-6 operating modes supported by the SSD.

Endurance

The product life of a SSD is approximately two (2) years when operating within the environmental

specifications. See Environm ental Characteristics. For a detailed life expectancy of the drive under

different conditions, please refer to the SSD Life Endurance Calculator. The remaining conditions

are outlined in Table 2.

Wear-Leveling

The dynamic and static wear-leveling algorithms integrated in the firmware guarantees that erase/

write cycles are evenly distributed across all of the flash memory block locations. Wear-leveling

eliminates repeated writes to the same physical flash memory location, thereby preventing premature

wear.

MACH2 2.5-Inch ATA Solid State Drive 5

Table 1. ATA Operating Modes

Mode Specification

PIO 0 - 4

DMA 0 - 2

Ultra DMA 0 - 5

Table 2. Endurance Conditions

Condition Value

Power-On Hours 100%

Active/Idle 90%

Write Percentage 25%

Drive Capacity 16GB

File Transfer Size 64KB

PRELIMINARY/CONFIDENTIAL

Bad-Block Management

The bad-block mapping algorithm replaces bad blocks with new ones from available spares. Two

percent (2%) of the flash memory is held in reserve (spare block) for bad block replacement. Bad

blocks in the media are flagged when detected. The next time an attempt is made to access a flagged

block, it is immediately replaced by a spare block. The bad block mapping function enables data to

be automatically transferred from a bad sector to an available spare block.

The drive is scanned for bad blocks during the initialization of

the flash components. An initial bad bl ock table is created

from these identified marked bad blocks and any ba d b loc ks

discovered during the testing process.

Data Retention

Data stored on the SSD will remain valid for ten (10) years without requiring power support. The unit

can be stored under certain environmental conditions for extended periods without any occurrence

of data degradation. See Environmental Characteristics.

Error Detection and Correction

The Error Detection Code and Error Correcting Code (EDC/ECC) helps maintain data integrity by

allowing single or multiple bit corrections to the data stored in the flash array. If the data in the flash

array is corrupted due to aging or during the programming process, the EDC/ECC will compensate

for the errors to ensure the delivery of accurate data to the host computer. The EDC/ECC engine is

capable of correcting up to 4 bytes in error and detecting up to 5 bytes in error. An extensive retry

algorithm is also implemented on the SSD, so that single event disturbances such as ESD or EMF

occurring during a read operation can be readily overcome.

Reliability

The following factors affect the reliability statistics of the SSD:

• DC power is maintained as specified in this document

• Errors caused by the host are excluded from rates

• Errors from the same causes are counted as 1 block

• Data stream is assumed random

6 MACH2 2.5-Inch ATA Solid State Drive

PRELIMINARY/CONFIDENTIAL

Error Rates

Table 3 lists the error limit specifications. When all data correction mechanisms are enabled, the error

rate will be sustained through all operating temperature ranges as specified in the previous sections.

Table 3. Error Limits

Error Type Maximum Number of Errors

Recoverable Data Error 1 bit in 10

Unrecoverable Data Error Less than 1 bit in 10

20

20

Built-In Self Test (BIST)

The micro-controller tests the controller memory during power-up, and then performs a back-end

status check to verify proper flash memory controller operations. If a fault condition is detected in the

flash memory controller, the SSD’s status is reported as failed.

Mount Time

The amount of time required to initialize and mount a SSD varies according to the operating system

®

(Windows

, Linux®, etc.) environment and the storage capacity of the drive.

Seek Time

The SSD has no read/write heads or rotating platters. There is no seek time or rotational latency

issues. The SSD dramatically improves transaction throughput, particularly for applications that are

configured to take advantage of the characteristics of the drive.

Data Transfer Rates

The data transfer rate varies according to the flash controller/flash memory configuration of the drive.

The scalable architecture of the drive is capable of accommodating sustained and burst data transfer

rates as listed in Table 4.

Table 4. Data Transfer Rates

Parameter Value Units

Burst Transfer Rate 100 Megabytes/sec

Sustained Read Throughput 35 Megabytes/sec

Sustained Write Throughput 25 Megabytes/sec

MACH2 2.5-Inch ATA Solid State Drive 7

PRELIMINARY/CONFIDENTIAL

Repairs

A defective SSD should be replaced. There are no parts, assemblies or subassemblies that can be

repaired by the user. Please see the section titled Certification and Warranty on the inside of the

back cover page. Unauthorized repairs to the SSD will void the warranty.

Preventative Maintenance

No preventative maintenance is required. The SSD unit is sealed at the factory, and there are no

parts, assemblies, or subassemblies that require preventative maintenance on behalf of the user.

Please see the section titled Certification and Warranty on the inside of the back cover page.

Unauthorized maintenance to the SSD will void the warranty.

8 MACH2 2.5-Inch ATA Solid State Drive

PRELIMINARY/CONFIDENTIAL

ELECTRICAL SPECIFICATIONS

Power Requirements

The SSD requires a 5V power source. If a power failure occurs, the drive design ensures that the data

contained in the storage memory is preserved. Data loss or corruption does not occur.

Note: (1) The voltage rail, which includes ripples, does not exceed or fall below the voltage range as

specified by the Minimum and Maximum values, i.e., values are the absolute floor and ceiling for the

input voltages.

Power Consumption

The amount of power consumed by a SSD is determined by the storage (memory) capacity of the

drive, and the flash controller/memory configuration of the drive. See Table 6.

MACH2 2.5-Inch ATA Solid State Drive 9

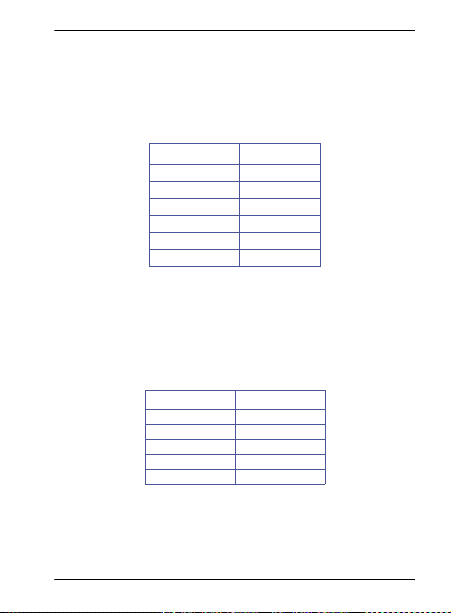

Table 5. SSD Power Requirements

Item Requirement

1

Input Voltage

Minimum Voltage 4.75V

Maximum Voltage 5.25V

Ripple (0-30MHz) 70 mV p-p (for 3.3V)

Supply Rise Time 7 - 100 ms

Supply Fall Time < 5s

5V +/-5%

Table 6. SSD Typical Power Consumption

Operation Power Consumption

Standby 0.1W

Idle 0.3W

Read (35MB/sec) TBDW

Write (25MB/sec) TBDW

Purge TBDW

PRELIMINARY/CONFIDENTIAL

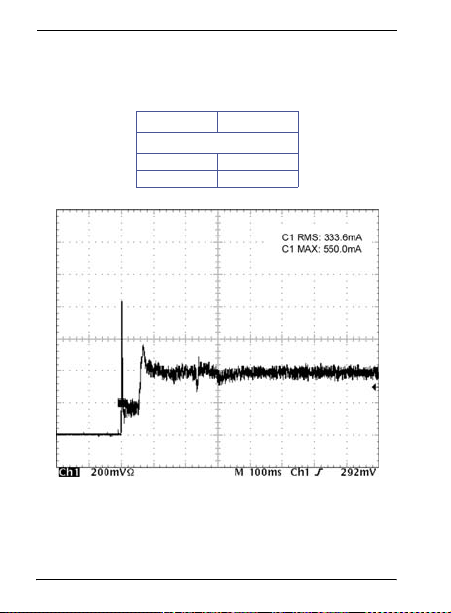

Start-Up Time and Current Draw

The Start-Up current is measured during the power-on phase of the computer and drive. See Table

7 and Figure 2.

Table 7. Start-Up Time and Current Draw

Start-Up Time ~850mS

Current Draw

Average RMS

Maximum Peak

333.6mA

550.0mA

Activity LED

Figure 2. Start-Up Current Draw

The SSD is configured to drive Pin 39 (-DASP; Disk Present/Secondary Active) of the ATA cable

during all command activity and during periods when the drive indicates a busy state. (Example: Offline diagnostic activities.)

10 MACH2 2.5-Inch ATA Solid State Dri ve

PRELIMINARY/CONFIDENTIAL

Power-On Ready Time

The Power-On Ready Time is less than 2.5 seconds. Power-On Ready Time is measured from the

time the drive is powered on to the time the drive is ready to accept the first command from the host.

Power Savings Commands

The drive will comply with all specifications that define the behavior of storage devices as it relates

to power management and Advanced Power Management (APM). When the SSD receives a power

management command, all data in the Write cache buffer is written to the media before Drive Ready

is asserted. The SSD supports the following Power Savings commands and respond with the

appropriate status:

Check Power Mode Standby Immediate

Idle Sleep

Standby

Power Mode at Power On

The drive will comply with the ATA-6 Power Management Specification. During the Power On Reset

sequence, the drive functions properly and responds as appropriate. In addition, if a SRST (ATA

Interface Reset) occurs during this sequence, the drive will still respond normally. After power on or

hard reset, the drive enters IDLE or STANDBY mode, depending on the setting by the host.

Grounding

Signal and chassis grounds are connected together in the drive. To ensure minimal EM emissions,

the user should provide maximum surface contact area when connecting the drive to the chassis

ground.

MACH2 2.5-Inch ATA Solid State Drive 11

PRELIMINARY/CONFIDENTIAL

INTERFACE SPECIFICATIONS

SSD Operation

The SSD is comprised of three primary functional blocks: the ATA (IDE) interface connector, SSD

controller and NAND flash memory. Read/write data transfer requests are initiated by the host via the

ATA (IDE) bus interface. Once received, the controller, under the direction of the microcontroller,

processes the request.

Commands that do not require data to be read from or written to the flash memory controller are

typically handled by the controller. Some commands may require the controller to use external

circuitry that do not involve the flash memory controller.

Write Operations

When a write operation is requested and data is received, the controller uses integrated DMA

controllers to transfer the data from host memory to the flash memory controller. Through a standard

ATA (IDE) interface, the flash memory controller transfers the data from the controller to available

locations in the local flash memory of the SSD. The controller notifies the host after the write

operation is completed.

Read Requests

If a read request is received, the controller retrieves the data from the local flash memory via the flash

memory controller. If the controller is responding to a PIO read operation, it presents the data to the

ATA bus. If it is responding to a UDMA read request, the controller writes the data directly to system

memory on the host. Regardless of the type of operation (PIO or UDMA), the controller notifies the

host when the data is ready for transmission.

12 MACH2 2.5-Inch ATA Solid State Dri ve

The microcontroller initiates and controls all activity within th e

controller, including bad-block mapping and executing the wearleveling algorithms.

The controller decodes an incoming host command, and

configures the appropriate interrupts and statu s for the local

microprocessor to handle various ATA commands. For read and

write transfer commands, the hardware can handle the initial

handshake with the host automatically. If firmware enab les full

auto mode, read and write transfers can be fully handled by

hardware with minimum firmware support.

PRELIMINARY/CONFIDENTIAL

Primary and Secondary Modes

The SSD supports Primary (Device 0) and Secondary (Device 1) modes:

Device Mode Description

Drive address at system ATA I/O address 1F0h - 1F7h and 3F6h - 3F7h. The

Primary

host must provide chip-enable #CS0 and #CS1. The SSD decodes addresses

DA0 - DA2.

Drive address at system ATA I/O address 170h - 177h and 376h - 377h. The

Secondary

host must provide chip-enable #CS0 and #CS1. The SSD decodes addresses

DA0 - DA2.

I/O Primary and Secondary ATA (IDE) Modes

Primary and secondary drive addressing modes allow hosts to use the reserved disk drive I/O

addresses as defined by the ATA specification. This provides system designers with the simplest way

to accommodate ATA-protocol devices.

Addressing Modes

The SSD, on a command-by-command basis, can operate in either CHS or LBA addressing modes.

Identify Device Information (See Identify Device Information) signals the host whether the drive

supports LBA mode. The host selects LBA mode via the Drive/Head Register. Sector Number,

Cylinder Low, Cylinder High, and Drive/Head register bits HS3=0 contain the zero-based LBA. The

sectors are linearly mapped with: LBA = 0 => Cylinder 0, Head 0, Sector 1. Regardless of the

translation mode, a sector LBA address does not change. LBA = (Cylinder * No of Heads + Head) *

(Sectors/Track) + (Sector - 1). Table 8 lists the supported IDE addressing modes.

Table 8. ATA (IDE) Bus Addressing Modes

#CS0 #CS1 DA2 DA1 DA0 #IORD - “0” #IOWR - “0”

1 1 X X X Hi-Z Not Used

1 0 0 X X Hi-Z Not Used

1 0 1 0 X Hi-Z Not Used

0 0 X X X Invalid Invalid

1 0 1 1 0 Alternate Status Device Control

1 0 1 1 1 Device Address Not Us ed

0 1 0 0 0 Data Data

0 1 0 0 1 Error Feature

0 1 0 1 0 Sector Count Sector Count

0 1 0 1 1 Sector Number Sector Number

0 1 1 0 0 Cylinder Low Cylinder Low

0 1 1 0 1 Cylinder High Cylinder High

0 1 1 1 0 Drive/Head Drive/Head

0 1 1 1 1 Status Command

MACH2 2.5-Inch ATA Solid State Drive 13

PRELIMINARY/CONFIDENTIAL

44-Pin ATA Bus Connector

The SSD is equipped with a 44-pin ATA bus connector. See Figure 3. DC power and IDE bus traffic

is supplied through a non-shielded 44-conductor I/O cable.

14 MACH2 2.5-Inch ATA Solid State Dri ve

The SSD has a plastic key to block pin 20 on the ATA bus

(IDE) interface connector. This prevents possible damag e to

the SSD by making an improper connection impossible.

ATA standards require 80-conductor cables to be used for

Ultra DMA (UDMA) Modes 3 through 5.

The length of the non-shielded cable should not exceed

457.2mm (18 inches).

Figure 3. 44-pin ATA (IDE) Bus Connector

PRELIMINARY/CONFIDENTIAL

Connector Pinout Signals

Table 9 provides the signal assignment for each pin on the ATA (IDE) bus connector. The table

applies to the 44-pin ATA bus/DC power combination connector used on 2.5-inch drives.

Pin Pin Type Signal Symbol Signal Name Signal Description

1 1 -RESET HOST RESET Reset signal from host. Reset is active on power up

2 Ground GND - Ground

3 I/O D07 HOST DATA 07 Pins 3 through 18 (16 lines (15-0) ca rry the data

4 I/O D08 HOST DATA 08

5 I/O D06 HOST DATA 06

6 I/O D09 HOST DATA 09

7 I/O D05 HOST DATA 05

8 I/O D10 HOST DATA 10

9 I/O D04 HOST DATA 04

10 I/O D11 HOST DATA 11

11 I/O D03 HOST DATA 03

12 I/O D12 HOST DATA 12

13 I/O D02 HOST DATA 02

14 I/O D13 HOST DATA 13

15 I/O D01 HOST DATA 01

16 I/O D14 HOST DATA 14

17 I/O D00 HOST DATA 00

18 I/O D15 HOST DATA 15

19 Ground GND - Ground

20 - - - No connection. Reserved for connector key.

21 O DREQ DMA REQUEST Not used.

22 Ground GND - Ground

23 I -IOWR I/O WRITE This I/O Write strobe pulse is used to clock I/O data

24 Ground GND - Ground

25 I -IORD I/O READ This is a Read strobe gen erated by the host. Th e

26 Ground GND - Ground

27 I IORDY I/O READY Not used. Pulled up to Vcc through a 4.7k oh m

MACH2 2.5-Inch ATA Solid State Drive 15

Table 9. ATA Connector Pinout Configuration

and inactive thereafter.

between the controller and the host. The low 8 lines

transfer commands and the ECC information

between the host and the controller.

or commands on the drive data bus into the drive

controller registers when the drive is configured to

use the I/O interface. The clocking will occur on the

negative to positive edge of the signal (trailing

edge.

signal gates I/O data or status on the host bus and

strobes the data from the controller into the host on

the low to high transition (trailing edge).

resistor.

PRELIMINARY/CONFIDENTIAL

Pin Pin Type Signal Symbol Signal Name Signal Description

28 I -CSEL CABLE SELECT This internally pulled up signal is used to configure

29 I -DACK DMA ACKNOWLEDGE Not used.

30 Ground GND - Ground

31 O INTRQ INTERRUPT REQUEST This is an interrupt request from the controller to the

32 O -IOS16 I/O SELECT 16 Not used.

33 I A1 HOST ADDRESS 1 The addres s line A1 is used to select one of eight

34 I/O -PDIAG After an Executive diagnostic command to indicate

35 I A0 HOST ADDRESS 0 The address lines A0 and A2 are used to select one

36 I A2 HOST ADDRESS 2

37 I -CS1 HOST CHIP SELECT 1 The chip select signal used to select the Task F ile

38 I -CS2 HOST CHIP SELECT 2 The chip select signal used to select the Alternate

39 I/O -DASP DISK ACTIVE/

40 Ground GND - Ground

41 - V

42 - V

43 Ground GND - Ground

44 - - - No Connection

SECONDARY PRESENT

Supply Voltage 5V Power Supply

CC

Supply Voltage 5V Power Supply

CC

the drives as the Primary or the Secondary device.

When the pin is grounded, the device is configured

as the Primary device. When the pin is open, the

device is configured as a Secondary device.

host, asking for service. This signal is the acti ve

high Interrupt Request to the host.

registers in the controller Task File.

that the Primary device has passed its diagnostics,

this bi-directional open drain signa l is asserte d by

the Secondary device.

of eight registers in the controller Task File.

register.

Status register and the Device Control register.

This input/output is the Disk Active/Secondary

Present signal in the Primary/Secondary

handshake protocol.

16 MACH2 2.5-Inch ATA Solid State Dri ve

PRELIMINARY/CONFIDENTIAL

ATA COMMANDS

Overview

This section provides information on the ATA commands supported by the SSD. The commands are

issued to the ATA by loading the required registers in the command block with the supplied

parameter, and then writing the command code to the register.

Standard ATA Commands

Table 10 lists each command along with its respective command code and registers accessed by the

command. For detailed descriptions of the ATA commands, refer to the ATA-6 specification.

Command

CHECK POWER MODE 98h or E5h No Yes No No

DOWNLOAD MICROCODE 92h Yes No No No No

ERASE SECTOR C0h No Yes Yes Yes

EXECUTE DRIVE DIAGNOSTIC 90h No No No No

FLUSH CACHE E7h TBD TBD TBD TBD TBD

FLUSH CACHE EXTENDED EAh TBD TBD TBD TBD TBD

FORMAT TRACK 50h No Yes No Yes

IDENTIFY DEVICE ECh Yes No No No

IDLE 97h, E3h No Y No No

IDLE IMMEDIATE 95h, E1h No No No No

INITIALIZE DRIVE PARAMETERS 91h No Yes No No

NOP 00h No No No No

READ BUFFER E4h No No No No No

READ DMA C8h No Yes Yes Yes

READ DMA EXTENDED 25h No Yes Yes Yes

READ DMA QUEUED C7h No Yes Yes Yes

READ DMA QUEUED EXT 26h No Yes Yes Yes

READ MULTIPLE C4h No Yes Yes Yes

READ MULTIPLE EXTENDED 29h No Yes Yes Yes

READ SECTOR(S) 20h No Yes Yes Yes

READ SECTOR(S) EXTENDED 24h No Yes Yes Yes

READ VERIFY SECTOR(S) 40h No Yes Yes Yes

READ VERIFY EXTENDED 42h No Yes Yes Yes

MACH2 2.5-Inch ATA Solid State Drive 17

Table 10. Supported ATA Commands

Feature

Register

Sector

Count

Register

Command

Code (Hex)

Sector

Number

Register

Cylinder

High/Low

Register

Drive/Head

Number

Register

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

(a)

(a)

(a)

(b)

(a)

(a)

(a)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

PRELIMINARY/CONFIDENTIAL

Sector

Sector

Cylinder

Command

Command

RECALIBRATE 10h No No No No

SECURITY DISABLE PASSWORD F6h No No No No

SECURITY ERASE PREPARE F3h No No No No

SECURITY ERASE UNIT F4h No No No No

SECURITY FREEZE LOCK F5h No No No No

SECURITY SET PASSWORD F1h No No No No

SECURITY UNLOCK F2h No No No No

SEEK 70h - 7Fh No No Yes Yes

SET FEATURES EFh No Yes Yes Yes

SET MULTIPLE MODE C6h No Yes No No

SLEEP E6h No No No No

SMART B0h Yes Yes Yes Yes

STANDBY 96h or E2h No Yes No No

STANDBY IMMEDIATE 94h or E0h No No No No

WRITE BUFFER E8h No Yes Yes Yes

WRITE DMA CAh No Yes Yes Yes

WRITE DMA EXTENDED 35h No Yes Yes Yes

WRITE DMA QUEUED CCh No Yes Yes Yes

WRITE DMA QUEUED EXT 36h No Yes Yes Yes

WRITE MULTIPLE C5h No Yes Yes Yes

WRITE MULTIPLE EXTENDED 39h No Yes Yes Yes

WRITE MULTIPLE FUA EXT CEh No Yes Yes Yes

WRITE SECTOR(S) 30h No Yes Yes Yes

WRITE SECTOR(S) EXTENDED 34h No Yes Yes Yes

Code (Hex)

Feature

Register

Count

Register

Number

Register

High/Low

Register

Drive/Head

Number

Register

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Notes:

(a) Only drive parameters are valid.

(b) Drive and head parameters are valid.

(c) Address to Drive 0 (zero). When executed, both drives (Primary and Secondary)

execute this command.

18 MACH2 2.5-Inch ATA Solid State Dri ve

(a)

(a)

(a)

(a)

(a)

(a)

(a)

(b)

(b)

(a)

(a)

(b)

(a)

(a)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

(b)

PRELIMINARY/CONFIDENTIAL

Standard ATA Command Summary

Table 11 provides a summary of each supported ATA command.

Command Hex Value Description

CHECK POWER MODE 98h, E5h The Check Power Mode command allows the host to determ ine

DOWNLOAD MICROCODE 92h The command allows the host to alt er the microcode of the

ERASE SECTOR C0h This command w ill pre-erase and c ondition the data sectors in

EXECUTE DRIVE DIAGNOSTIC 90h This command performs the internal diagnostic tests

FLUSH CACHE E7h This command is used by the host to request the device to flush

FLUSH CACHE EXTENDED EAh This command is used by the ho st to request the device to flush

FORMAT TRACK 50h This command writes the desired head and cylinder of the

IDENTIFY DEVICE ECh This command allows the host to receive parameter information

IDLE 97h, E3h This command will cause the drive to set BSY, enter the IDLE

MACH2 2.5-Inch ATA Solid State Drive 19

Table 11. ATA Command Summary

the current power mode of the device. The C heck Power Mo de

command shall not cause the device to change po wer or affect

the operation of the Standby timer.

device. The data transferred using the Dow nload Microcode

command is vendor-specific. All transfers are an inte ger mult iple

of the sector size. The size of the data transfer is determined by

the contents of the LBA Low register and the Sector Count

register. The LBA Low register will extend the Se ctor Count

register to create a 16-bit sector count value. The LBA Low

register will be the most significant eight bits and the Sector Count

register will be the least significant eight bits. A value of zero in

the LBA Low and Sector Count registers specify that no data is to

be transferred. This allows transfer sizes from 0 bytes to

33,553,920 bytes, in 512-byte increments. The Features register

will determine the effect of the Download Microcode command.

advance.

implemented by the controller.

the Write cache. If there is data in the Write cache, that data shall

be written to the media. The command will not indicate

completion until the data is flushed to t he media or an error

occurs. If the device supports more tha n 28 bits of addre ssing,

this command shall attempt to flush all the data in the cache. If the

Write cache is disabled or is not p res en t, th e device will indicate

completion without er ror . Th e com mand is ma ndat or y for de vic es

not implementing the PACKET feature set.

the Write cache. If there is data in the Write cache, that data shall

be written to the media. The command will not indicate

completion until the data is flushed to t he media or an error

occurs. If the Write cache is disabled or is not present, the device

will indicate completion without error. This command is

mandatory for devices that implement the 48-bit Address feat ure

set.

selected drive with a vendor-unique data pattern (typically 00h or

FFh). The drive accepts a sector buffer of data from the host to

follow the command with the same protocol as the Write Sector(s)

- 30h command, although the information in the cach e is not

used.

from the drive.

mode, clear BSY, and generate an interrupt. If the sector count is

zero, the automatic power down mode is disabled.

PRELIMINARY/CONFIDENTIAL

IDLE IMMEDIATE 95h, E1h This command will cause the driv e to set BSY, enter th e IDLE

INITIALIZE DRIVE PARAMETERS 91h This command will enable the host to set the num ber o f sect ors

NOP 00h This command is mandatory for devices that implement the

READ BUFFER E4h This command is optional for devices tha t do not implem ent the

READ DMA C8h This comman d is mandato ry for devices that do no t implement

READ DMA EXT 25h This command is mandatory for devices that implement the 48-bit

READ DMA QUEUED C7h This command is mandatory for devices that implement the TCQ

READ DMA QUEUED EXT 26h This command is mandatory for devices that implement the TCQ

READ MULTIPLE C4h This command is similar to the Read S ector(s) - 20h command.

READ MULTIPLE EXTENDED 29h This command is mandatory for all devices that impleme nt the

READ SECTOR(S) 20h This command will read from 1 to 256 sectors as specified in the

READ SECTOR(S) EXTENDED 24h This command is mandatory for devices that implement the 48-bit

READ/VERIFY SECTOR(S) 40h This command will verify one or more sectors by transferring data

(READ) mode, clear BSY, and generate an interrupt.

per track and the number of heads per cylinder.

PACKET and TCQ feature sets. The device will re spond with

command aborted. For devices that imple ment the TC Q feature

set, the subcommand 00h in the Featur e field shall abort any

outstanding queue. Subcommand codes 01h through FFh in the

Feature field shall not affect the status of any outstanding queue.

PACKET feature set. The command wil l enable the ho st to re ad

a 512-byte block of data . The Writ e Buf fer ( E8h) c ommand shou ld

precede the Read Buffer (E4h) com man d, les t th e d ata re turn ed

be indeterminate.

the PACKET feature set. The command will allow the host to read

data using the DMA data transfer protocol.

Address feature set. The command will allow the host to read

data using the DMA data transfer protocol.

feature set. The command is similar in function to the Read DMA

(C8h) command. The device may releas e or execute the data

transfer without performing a release if the data is ready to

transfer.

and 48-bit feature sets. The command is similar in function to the

Read DMA (C8h) command. The device may release or execute

the data transfer with ou t per f o rm ing a re l e as e if th e da t a i s re ad y

to transfer.

Interrupts are not generated on each sector, but on the transfer of

a block that contains the number of sectors as de fined by a Set

Multiple Mode - C6h command.

48-bit Address feature set. The command will read the number of

logical sectors specified in the Count field. The number of logical

sectors determines the DRQ data block count, which in turn will

determine the number of logical sectors that are to be transferred.

Sector Count Register. A sector count of 0 (zero) request s 256

sectors. The transfer will begin at the s ector specified in the

Sector Number Register.

Address feature set. This comman d will read from 1 to 256 to

65,536 logical sectors as specified in the S ect or C oun t Re gis ter.

A sector count of 0 (zero) will request 65,536 logical sectors. The

transfer will begin at the sector specified in the LBA field.

from the flash media to th e dat a buf fer and v erif yin g tha t th e ECC

is correct. The command is identical to t he Rea d S ect or(s) - 20h

command, except that DRQ is never set and no data is

transferred to the host.

20 MACH2 2.5-Inch ATA Solid State Dri ve

PRELIMINARY/CONFIDENTIAL

READ/VERIFY EXTENDED 42h This command is mandatory for devices that implement the 48-bit

RECALIBRATE 10h The SSD performs only the interface timing and register

SECURITY DISABLE PASSWORD F6h This command is ma ndatory for devices that implement the

SECURITY ERASE PREPARE F3h This command is mandatory for devices that implement the

SECURITY ERASE UNIT F4h This command is ma ndatory for devices that implement the

SECURITY FREEZE LOCK F5h This command is mandatory for devices tha t implement the

SECURITY SET PASSWORD F1h This command is mandatory for dev ices that implement the

SECURITY UNLOCK F2h This command is mandatory for devices that implement the

Address feature set. The command is i dentical to the Read

Sector(s) Extended (24) command, except that no data is

transferred from the device to the host. The d evice will read the

data stored in the media and verify that no errors exist.

operations. When th is co mmand is i ssued , the S SD se ts BS Y and

waits for an appropriate length of time, after which it clears B SY

and issues an interrupt. When this command ends normally, the

SSD is initialized.

Security Mode feature set. The com ma nd will tra nsf er 5 12 by tes

of predefined data from the host. If the p assword selected by

Word 0 matches the password th at wa s pre viou sly sa ved b y the

device, the device shall disable Lock mode. The co mmand will

not change the Master password. T he Master password is

reactivated when a User password is set. The command will only

complete successfully if the device is in Unlocked mode.

Security Mode feature set. The comm and i s issu ed im media tely

before the Security Erase Unit (F4h) command to en able dev ice

erasing and unlocking. The command prevents accidental loss of

data on the device.

Security Mode feature set. The com ma nd will tra nsf er 5 12 by tes

of predefined data from th e h os t . If th e pa s sw o rd do es no t mat c h

the password previously saved by the device, the device shall

reject the command and abort it. W he n a N orm al Erase mode is

specified, the Security Erase Unit command shall write bin ary

zeros to all user data areas. If the optional Enhanced Erase mode

is specified, the device shall write predetermined data patterns to

all user data areas; the current d ata is overwritten, including

sectors that are no longer in use due to reallocation.

Security Mode feature set. The c om man d sha ll set th e device to

Frozen mode. Other commands that upd ate the device Lock

mode are aborted. Frozen mode can be disabled by a power -off

or hardware reset. If the command is issued while the device is in

Frozen mode, the command is ex ecuted and the device will

remain in Frozen mode.

Security Mode feature set. The com ma nd will tra nsf er 5 12 by tes

of predefined data from the host. The data controls the function of

this command, which in turn defines the intera ction of the

identifier and security level bits. The user can in tu rn set the

Master or User passwords, and the security level of the device.

Security Mode feature set. The com ma nd will tra nsf er 5 12 by tes

of predefined data from the host. The data controls the function of

this command, which in turn defines the intera ction of the

Identifier bit. If the Identifier bit is set to Master and the current

security level is high, the password is com pared with the stored

Master password. If the device is in maximum security level then

the unlock shall be rejected. If the Identifier bit is set to User, then

the device shall compare the supplied password with the stored

User password. If the password comparison fails, the device shall

abort the command and report a decrea se in the incremental

value in the unlock counter.

MACH2 2.5-Inch ATA Solid State Drive 21

PRELIMINARY/CONFIDENTIAL

SEEK 70h, 7Fh This command is effectively a NOP command to the SSD

SET FEATURES E Fh This command is used by the host to establish or select cert ain

SET MULTIPLE MODE C6h This comman d enables the SSD to p erform multiple read and

SET SLEEP MODE 99h, E6h This is the only command that allows the host to configure the

SLEEP E6h This command is mandatory for devices that implement the

SMART B0h See S.M.A.R.T. Support.

STANDBY 96h, E2h This command will config ure the drive for Standby Mode. If the

STANDBY IMMEDIATE 94h, E0h This command will cause the SSD to set BYS, enter the Standby

WRITE BUFFER E8h This command is optional for devices that implement the General

WRITE DMA CAh This command is ma ndatory for devices that implement the

WRITE DMA EXT 35h This command is mandatory for devices that implement the 48-bit

WRITE DMA FUA EXT 3Dh This command is mandatory for devices that implement the 48-bit

although it does perform a range check.

features supported by the drive. When the SSD receives this

command, it sets BSY, checks the contents of th e Features

register, applies changes as necessary, clears BSY and

generates an interrupt. If the valu e in the register does not

represent a feature supported by the drive, the command is

canceled with the Abort Error condition.

write operations and establishes the block cou nt for these

commands.

drive for Sleep Mode. When the driv e is set t o Sleep M ode, the

SSD clears the BSY line and issues an interrupt. The card enters

Sleep Mode and the hardware or software must be reset to

activate the drive.

Power Management feature set. The co mmand will cause the

device to enter Sleep mode. The dev ice will not power-on in

Sleep mode nor remain in Sleep mode following a reset

sequence. The method used to dea ctivate Sleep mode is

transport specific. The Power Management feature set is

mandatory for devices that do not im plement the PACKET

Command set. This command is mandatory when power

management is not implemented b y the PA CK ET Command set

device.

Sector Count Register is a value other than 0H, an Auto Power

Down is enabled and when the dri ve returns to Idle M ode, the

timer starts a countdown. The time is set in the Sector Count

Register.

Mode, clear BSY, and return the interrupt immediately.

feature set. This command allows the hos t to write th e contents

of one 512-byte block of data in the in the buffer of the device.

General feature set. The command allo ws the host to write d ata

using the DMA data transfer protocol.

Address feature set. The comman d allo ws th e h ost to write data

using the DMA data transfer protocol.

Address feature set. The command provides the same function

as Write DMA Extended (35h) regardles s of whether write

caching is enabled. The user data is written to the me dia bef ore

ending status for the command is reported.

22 MACH2 2.5-Inch ATA Solid State Dri ve

PRELIMINARY/CONFIDENTIAL

WRITE DMA QUEUED CCh This command is mandatory for devices that implement the TCQ

WRITE DMA QUEUED EXT 38h This command is mandatory for devices that implement the TCQ

WRITE DMA QUEUED FUA EXT 3Eh This command is mandatory for devices that implement the TCQ

WRITE MULTIPLE C5h This comma nd is simila r to the Wri te Sector(s ) - 30h com mand.

WRITE MULTIPLE EXT 39h This command is mandatory for devices that implement the 48-bit

WRITE MULTIPLE FUA EXT CEh This command is mandatory for devices that implement the 48-bit

WRITE SECTOR(S) 30h This command will write from 1 to 256 sectors as specified in the

WRITE SECTOR(S) EXT 34h This command is mandatory for devices that implement the 48-bit

feature set. The command is similar to the Write DMA (CAh)

command. The device may perform a release or may execute the

data transfer without performing a rele ase if the da ta is re ady to

transfer. If the device performs a release, the host should reselect

the device using the SERVICE command. Once the data transfer

has begun, the device shall not perform a release until the entire

data transfer is complete.

and 48-bit Address feature sets. The command is similar to Write

DMA Extended (35h). The device may perform a release or may

execute the data transfer without performing a release if the data

is ready to transfer. If the device performs a release, the host

should reselect the device using the SERVI CE comma nd. On ce

the data transfer has begun, the device shall not perform a

release until the entire data transfer is complete.

and 48-bit Address feature sets. The comm and is similar to the

Write DMA Extended (35h) command. The device may perform a

release or may execute the dat a transfer without per forming a

release if the data is ready to transfer. If the device performs a

release, the host should reselect the device using th e SERVI CE

command. The device does not perform a release onc e the data

transfer has begun and has been completed.

Interrupts are not presented on each sector, but on the transfer of

a block which contains the number of se cto rs d efin ed by the Set

Multiple Mode - C6h command.

Address feature set. The command will write the number of

logical sectors specified in the Count field. The command is

similar to Write Sector(s) (30h). Interrupts are not presen ted on

each sector, but on the transfer of blocks that contain the number

of sectors defined by LBA mode.

Address feature set. The command has the same functionality of

Write Multiple Ext (39h), except tha t regar dless of whe ther w rite

caching is enabled, the user data is written to the media bef ore

the ending status of the command is reported.

Sector Count Register. A sector count of 0 (zero) will request 256

sectors. The transfer begins at the se ctor sp ecif ied in t he Sec tor

Number Register.

Address feature set. The command will write 1 to 6 5,536 logical

sectors as specified in the Sector Count Register. A sector count

value of 0 will request 65,536 logical sectors.

MACH2 2.5-Inch ATA Solid State Drive 23

PRELIMINARY/CONFIDENTIAL

S.M.A.R.T. Support

S.M.A.R.T. is an acronym for Self-Monitoring, Analysis and Reporting Technology. The S.M.A.R.T.

feature set protects the user from unscheduled downtime by monitoring and storing critical drive

performance and calibration parameters. A S.M.A.R.T. feature set device attempts to predict the

occurrence of near-term degradation or fault conditions. The host system is warned of a negative

reliability condition, which in turn warns the user of the impending risk of data loss. The user can then

take appropriate action to minimize the risk.

Support for the S.M.A.R.T. feature set is indicated by the Identify Device (ECh) command:

Word 82 Bit 0 The S.M.A.R.T. feature set is supported. This information is set during the drive

Word 85 Bit 0 The S.M.A.R.T. feature set has been enabled via the SMART ENABLE

initialization sequence.

OPERATIONS command. The information is dynamic; the SMART ENABLE

OPERATIONS command and SMART DISABLE OPERATIONS command are

invoked. The most current setting must be reflected in the output of the IDENTIFY

DEVICE command. S.M.A.R.T. operations are enabled by default.

S.M.A.R.T. Commands

Table 12 lists the commands that are identified by the value placed in the Feature register.

Table 12. S.M.A.R.T. Command Values

Value Command Note

00h-CFh Reserved RSVD

D0h SMART READ DATA Optional

D1h Obsolete OBS

D2h SMART ENABLE/DISABLE ATTRIBUTE AUTOSAVE Mandatory

D3h Obsolete OBS

D4h SMART EXECUTE OFF-LINE IMMEDIATE Optional

D5h SMART READ LOG Optional

D6h SMART WRITE LOG Optional

D7h Obsolete OBS

D8h SMART ENABLE OPERATIONS Mandatory

D9h SMART DISABLE OPERATIONS Mandatory

DAh SMART RETURN STATUS Mandatory

DBh Obsolete OBS

DCh-DFh Reserved RSVD

E0h-FFh Vendor-Specific VSC

24 MACH2 2.5-Inch ATA Solid State Dri ve

PRELIMINARY/CONFIDENTIAL

S.M.A.R.T. Attributes

Table 13 lists the S.M.A.R.T. attributes that are supported.

Table 13. Supported S.M.A.R.T. Attributes

ID Name Description

1 Raw Read Error Frequency of errors while reading raw data from a disk.

9 Power-On Hours Number of hours elapsed in the Power-On state.

12 Power Cycle Number of Power-On events.

187 Reported Uncorrectable Errors The number of uncorrectable errors reported at the interface.

194 Temperature Temperature of base casting. (Requires integrated

195 ECC On-the-Fly Number of ECC on-the-fly errors.

196 Offline Reallocation Event Total number of sectors remapped.

197 Pending Defects Number of sectors currently suspected in need of remapping.

198 Offline Surface Scan Number of uncorrected errors that occurred during offline

199 UDMA CRC Error (PATA Only) Number of CRC errors during UDMA mode.

temperature sensor.)

scan.

Identify Device Information

The Identify Device command enables the host to receive parameter information from the SSD.

When the Identify Device command executes, the SSD sets the BSY bit, prepares to transfer the 256

words of SSD identification data to the host, sets the DRQ bit, clears the BSY bit, and then generates

an interrupt. The host can then transfer the data by reading the Data register. All reserved bits or

words are all zero. Table 14 contains typical Identify Device Information for the SSD.

Identify Device Information Key

F Content of the word is Fixed and does not change. For removable medi a devices, thes e value

may change when the media is removed or changed.

V Content of the w ord is Variable and may change depending on the state of the device or the

commands executed by the device.

X Content of the word is Vendor-Specific and may be fixed or variable.

R Content of the word is Reserved and shall be 0 (zero).

MACH2 2.5-Inch ATA Solid State Drive 25

PRELIMINARY/CONFIDENTIAL

Table 14. Identify Device Information

Word F/V/X/R Description

0 General configuration bit-significant information

F15 0 = ATA Device

X 14:8 Retired

F 7 1 = Removable Media Device

X6 Obsolete

X5:3Retired

V 2 Response Incomplete

X1 Retired

F0 Reserved

1VObsolete

2 V Specific Configuration

3XObsolete

4 -5 X Retired

6XObsolete

7 - 8 V Reserved for assignment by the CompactFlash™ Association

9XRetired

10 - 19 F Serial Number (20 ASCII Characters)

20 - 21 X Retired

22 X Obsolete

23 - 26 F Firmware Revision (8 ASCII Characters)

27 - 46 F Model Number (40 ASCII Characters)

47 F 15:8 80h

F 7:0 00h = Reserved

F 01h - FFh = Maximum number of sectors that shall be transferred per

48 F Reserved

49 Capabilities

F 15:14 Reserved for IDENTIFY PACKET DEVICE Command

F 13 1 = Standby timer values as specified in this standard are supported

F 12 Reserved for IDENTIFY PACKET DEVICE Command

F 11 1 = IORDY supported

26 MACH2 2.5-Inch ATA Solid State Dri ve

interrupt on READ/WRITE MULTIPLE Commands

0 = Standby timer values shall be managed by the device

PRELIMINARY/CONFIDENTIAL

F 10 1 = IORDY may be disabled

F 9 1 = LBA supported

F 8 1 = DMA supported

X7:0Retired

50 Capabilities

F 15 Shall be cleared to zero

F 14 Shall be set to one

F13 :2Reserved

X1 Obsolete

F 0 Shall be set to one to indicate a device-specific Standby Timer Value

51 - 52 X Obsolete

53 F 15:3 Reserved

F 2 1 = The fields reported in Word 88 are valid

F 1 1 = The fields reported in Words 70:64 are valid

X0 Obsolete

54 - 58 X Obsolete

59 F 15:9 Reserved

V 8 1 = Multiple Sector Setting is Valid

V 7:0 xxh = Current setting for number of sectors that shall be transferred per

60 - 61 F Total Number of User-Addressable Sectors

62 X Obsolete

63 F 15:11 Reserved

V 10 1 = Multiword DMA Mode 2 is selected

V 9 1 = Multiword DMA Mode 1 is selected

V 8 1 = Multiword DMA Mode 0 is selected

F7:3Reserved

F 2 1 = Multiword DMA Mode 2 and below are supported

MACH2 2.5-Inch ATA Solid State Drive 27

0 = IORDY may be supported

minimum

0 = The fields reported in Word 88 are invalid

0 = The fields reported in Words 70:64 are invalid

interrupt on R/W MULTIPLE Command

0 = Multiword DMA Mode 2 is not selected

0 = Multiword DMA Mode 1 is not selected

0 = Multiword DMA Mode 0 is not selected

PRELIMINARY/CONFIDENTIAL

F 1 1 = Multiword DMA Mode 1 and below are supported

F 0 1 = Multiword DMA Mode 0 is supported

64 F 15:8 Reserved

F 7:0 PIO Modes supported

65 Minimum Multiword DMA Transfer Cycle Per Word

F 15:0 Cycle Time in Nanoseconds

66 Manufacturer’s Recommended Multi-word DMA Transfer Cycle

F 15:0 Cycle Time in Nanoseconds

67 Minimum PIO Transfer Cycle Time without Flow Control

F 15:0 Cycle Time in Nanoseconds

68 Minimum PIO Transfer Cycle Time with IORDY Flow Control

F 15:0 Cycle Time in Nanoseconds

69 - 70 F Reserved (For Future Command Overlap and Queuing)

71 - 74 F Reserved for IDENTIFY PACKET DEVICE Command

75 Queue Depth

F 15:5 Reserved

F 4:0 Maximum Queue Depth - 1

76 - 79 F Reserved

80 F Major Version Number

28 MACH2 2.5-Inch ATA Solid State Dri ve

0000h or FFFFh = Device does not report version

F 15 Reserved

F 14 Reserved for ATA/ATAPI-14

F 13 Reserved for ATA/ATAPI-13

F 12 Reserved for ATA/ATAPI-12

F 11 Reserved for ATA/ATAPI-11

F 10 Reserved for ATA/ATAPI-10

F 9 Reserved for ATA/ATAPI-9

F 8 Reserved for ATA/ATAPI-8

F 7 Reserved for ATA/ATAPI-7

F 6 1 = Supports ATA/ATAPI-6

F 5 1 = Supports ATA/ATAPI-5

F 4 1 = Supports ATA/ATAPI-4

F 3 1 = Supports ATA-3