ST VNB14N04, VNK14N04FM, VNV14N04 User Manual

Features

VNB14N04 - VNK14N04FM

VNV14N04

"OMNIFET"

fully autoprotected Power MOSFET

Type V

VNB14N04

VNK14N04FM

VNV14N04

■

Linear current limitation

■

Thermal shutdown

■

Short circuit protection

■

Integrated clamp

■

Low current drawn from input pin

■

Diagnostic feedback through input pin

■

ESD protection

■

Direct access to the gate of the power

clamp

42 V

42 V

42 V

R

DS(on)

0.07 Ω

0.07 Ω

0.07 Ω

MOSFET (analog driving)

■

Compatible with standard power MOSFET

I

lim

14 A

14 A

14 A

Description

The VNB14N04, VNK14N04FM and VNV14N04

are monolithic devices made using

STMicroeletronics VIPower M0 Technology,

intended for replacement of standard power

MOSFETS in DC to 50 kHz applications. Built-in

thermal shutdown, linear current limitation and

overvoltage clamp protect the chip in harsh

environment.

Fault feedback can be detected by monitoring the

voltage at the input pin.

Table 1. Device summary

Part number Order code

VNB14N04

VNK14N04FM VNK14N04FM

VNV14N04 VNV14N04, VNV14N04-E

April 2009 Rev 6 1/17

VNB14N04, VNB14N04-E,

VNB14N0413TR, VNB14N04TR-E

www.st.com

17

Contents VNB14N04 - VNK14N04FM - VNV14N04

Contents

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.1 Absolute maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 Protection features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2/17

VNB14N04 - VNK14N04FM - VNV14N04 Block diagram

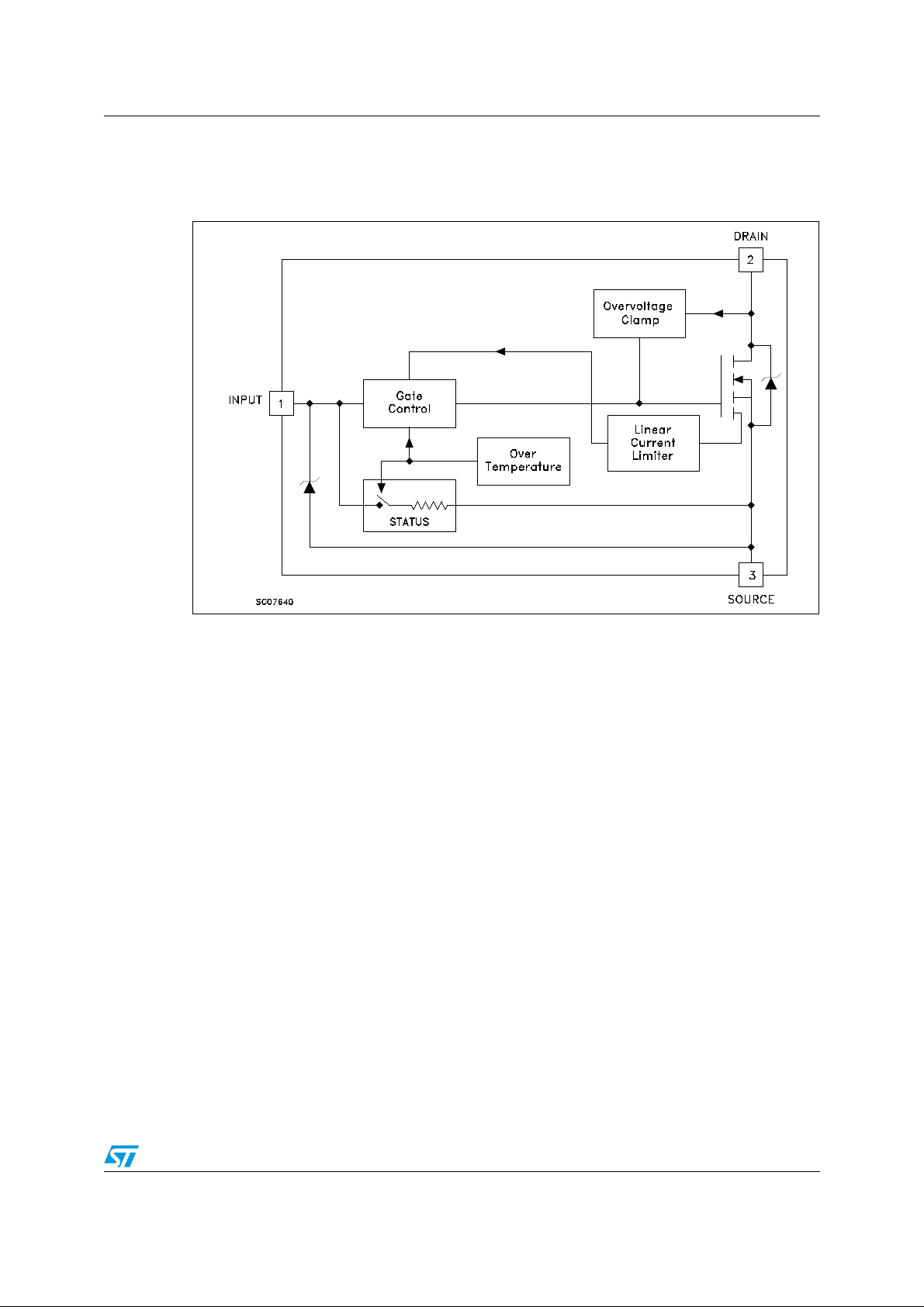

1 Block diagram

Figure 1. Block diagram

1. PowerSO-10 pin configuration : INPUT = 6,7,8,9,10; SOURCE = 1,2,4,5; DRAIN = TAB

3/17

Electrical specification VNB14N04 - VNK14N04FM - VNV14N04

2 Electrical specification

2.1 Absolute maximum rating

Table 2. Absolute maximum rating

Value

Symbol Parameter

V

DS

V

I

D

I

R

V

esd

P

tot

T

T

T

stg

Drain-source voltage (Vin = 0) Internally clamped V

in

Input voltage 18 V

Drain current Internally limited A

Reverse DC output current -14 A

Electrostatic discharge (C = 100 pF,

R=1.5 KΩ)

Total dissipation at Tc = 25 °C 50 9.5 W

j

Operating junction temperature Internally limited °C

c

Case operating temperature Internally limited °C

Storage temperature -55 to 150 °C

2.2 Thermal data

Table 3. Thermal data

Symbol Parameter PowerSO-10 SOT82-FM D2PAK Unit

R

thj-case

R

thj-amb

Thermal resistance junction-case max 2.5 13 2.5 °C/W

Thermal resistance junction-ambient

max

PowerSO-10

D2PAK

SOT-82FM

2000 V

50 100 62.5 °C/W

Unit

2.3 Electrical characteristics

T

=25 °C unless otherwise specified.

case

Table 4. Electrical characteristics

Symbol Parameter Test conditions Min. Typ. Max. Unit

Off

V

CLAMP

V

CLTH

V

INCL

4/17

Drain-source clamp voltage ID = 200 mA Vin = 0 36 42 48 V

Drain-source clamp threshold voltage ID = 2 mA Vin = 0 35 V

Input-source reverse clamp voltage Iin = -1 mA -1 -0.3 V

VNB14N04 - VNK14N04FM - VNV14N04 Electrical specification

Table 4. Electrical characteristics (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

On

V

R

I

DSS

I

DS(on)

Zero input voltage drain current (Vin = 0)

Supply current from input pin VDS = 0 V Vin = 10 V 250 500 µA

ISS

(1)

Input threshold voltage VDS = Vin ID + Iin = 1 mA 0.8 3 V

IN(th)

Static drain-source on resistance

Dynamic

(1)

gfs

C

Switching

t

d(on)

t

d(off)

t

d(on)

t

d(off)

Forward transconductance VDS = 13 V ID = 7 A 8 10 S

Output capacitance VDS = 13 V f = 1 MHz Vin = 0 400 500 pF

oss

(2)

Turn-on delay time

t

Rise time

r

Turn-off delay time

t

Fall time

f

Turn-on delay time

t

Rise time

r

Turn-off delay time

t

Fall time

f

(di/dt)onTurn-on current slope

Q

Total input charge VDD = 12 V ID = 7 A Vin = 10 V 30 nC

i

Source drain diode

(1)

VSD

trr

Qrr

I

RRM

Forward on voltage ISD = 7 A Vin = 0 1.6 V

(2)

Reverse recovery time

(2)

Reverse recovery charge

(2)

Reverse recovery current

Protection

VDS = 13 V Vin = 0

VDS = 25 V Vin = 0

Vin = 10 V ID = 7 A

Vin = 5 V ID = 7 A

VDD = 15 V Id = 7 A

V

= 10 V R

gen

gen

= 10 Ω

(see Figure 26)

VDD = 15 V Id = 7 A

V

= 10 V R

gen

= 1000 Ω

gen

(see Figure 26)

VDD = 15 V ID = 7 A

Vin = 10 V R

gen

= 10 Ω

ISD = 7 A di/dt = 100 A/µs

VDD = 30 V Tj = 25 °C

(see test circuit, Figure 28)

50

200µAµA

0.7

0.1ΩΩ

60

160

250

100

300

1.5

5.5

1.8

120

300

400

200

500

2.2

7.5

2.5

ns

ns

ns

ns

ns

µs

µs

µs

120 A/µs

110

0.34

6.1

ns

µC

A

t

dlim

T

T

I

jsh

jrs

Drain current limit

lim

Step response

(2)

Current limit

(2)

Overtemperature shutdown 150 °C

(2)

Overtemperature reset 135 °

Vin = 10 V VDS = 13 V

Vin = 5 V VDS = 13 V

Vin = 10 V

Vin = 5 V

101014142020A

308060

5/17

A

150µsµs

C

Electrical specification VNB14N04 - VNK14N04FM - VNV14N04

Table 4. Electrical characteristics (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

(2)

I

gf

Eas

1. Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %

2. Parameters guaranteed by design/characterization

Fault sink current

(2)

Single pulse avalanche energy

Vin = 10 V VDS = 13 V

Vin = 5 V VDS = 13 V

starting Tj = 25°C VDD = 20 V

Vin = 10 V R

= 1 KΩ L = 10 mH

gen

50

20

mA

mA

0.65 J

6/17

Loading...

Loading...