ST VND810PEP-E User Manual

Features

Type R

VND810PEP-E 160mW

DS(on)

(1)

I

OUT

3.5A

(1)

V

CC

36V

VND810PEP-E

Double channel high-side driver

1. Per each channel.

■ CMOS compatible inputs

■ Open drain status outputs

■ On-state open-load detection

■ Off-state open-load detection

■ Shorted load protection

■ Undervoltage and overvoltage shutdown

■ Loss of ground protection

■ Very low standby current

■ Reverse battery protection

■ In compliance with the 2002/95/EC european

directive

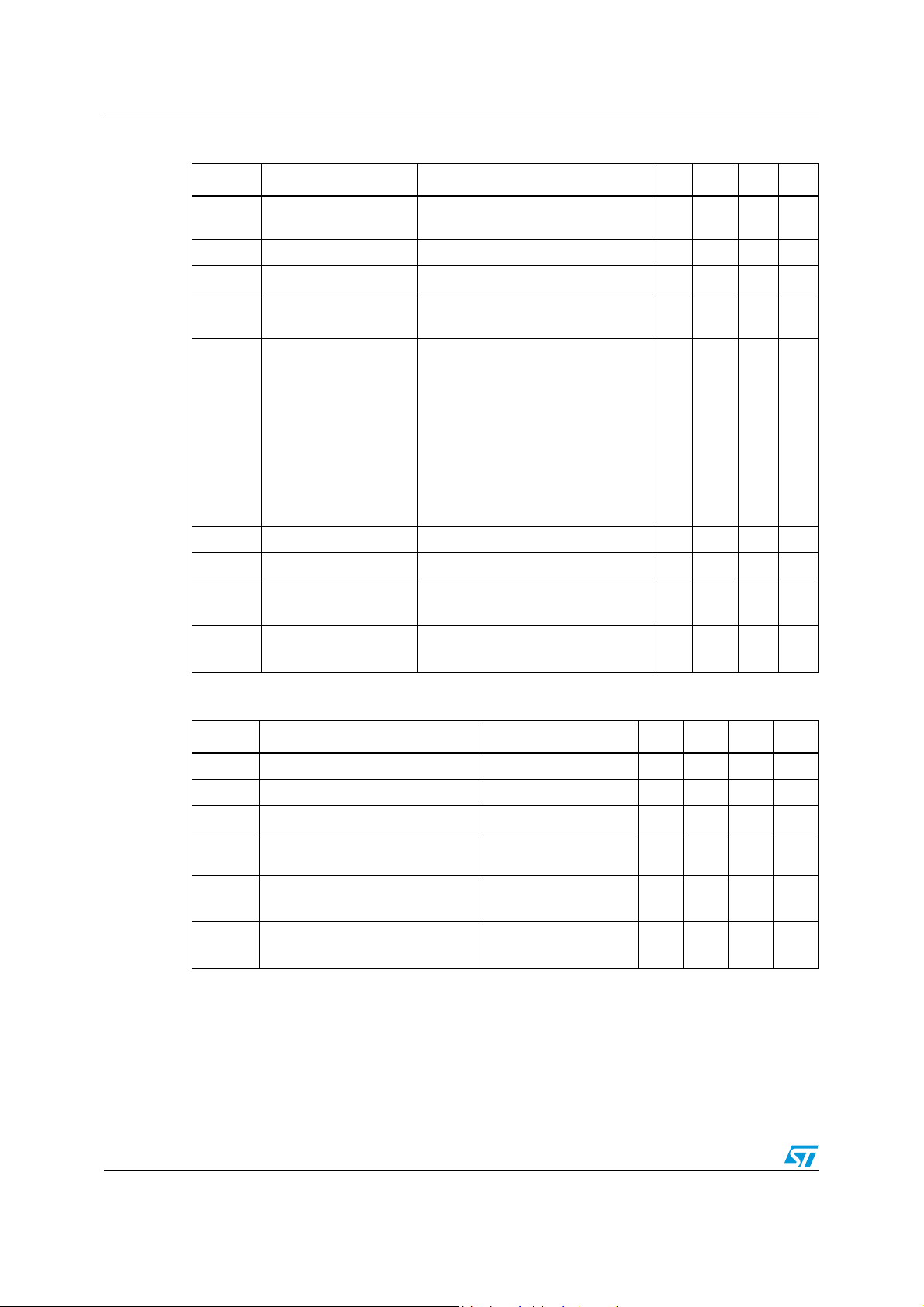

Table 1. Device summary

PowerSSO-12

Description

The VND810PEP-E is a monolithic device made

using| STMicroelectronics

Technology. The VND810PEP-E is intended for

driving any type of multiple load with one side

connected to ground.

The active V

pin voltage clamp protects the

CC

device against low energy spikes (see ISO7637

transient compatibility table).

Active current limitation combined with thermal

shutdown and automatic restart protects the

device against overload. The device detects the

open-load condition in both the on and off-state.

In the off-state the device detects if the output is

shorted to V

. The device automatically turns off

CC

in the case where the ground pin becomes

disconnected.

®

VIPower™ M0-3

Order codes

Package

Tub e Tap e and r eel

PowerSSO-12 VND810PEP-E VND810PEPTR-E

November 2011 Doc ID 10858 Rev 5 1/25

www.st.com

1

Contents VND810PEP-E

Contents

1 Block diagram and pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3 Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.1 GND protection network against reverse battery . . . . . . . . . . . . . . . . . . . 14

3.1.1 Solution 1: a resistor in the ground line (RGND only) . . . . . . . . . . . . . . 14

3.1.2 Solution 2: a diode (D

3.2 Load dump protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

) in the ground line . . . . . . . . . . . . . . . . . . . . 15

GND

3.3 MCU I/O protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.4 Open-load detection in off-state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4 Package and PC board thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.1 PowerSSO-12 thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5 Package and packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.1 ECOPACK® packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.2 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.3 Packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

6 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2/25 Doc ID 10858 Rev 5

VND810PEP-E List of tables

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. Suggested connections for unused and not connected pins . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 3. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 4. Thermal data (per island) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 5. Power outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 6. Protections and diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 7. V

Table 8. Switching (V

Table 9. Logic inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 10. Protections and diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 11. Status pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 12. Open-load detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 13. Truth table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 14. Electrical transient requirements (part 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 15. Electrical transient requirements (part 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 16. Electrical transient requirements (part 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 17. Thermal parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 18. PowerSSO-12 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 19. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

- output diode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

CC

= 13V; Tj = 25°C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

CC

Doc ID 10858 Rev 5 3/25

List of figures VND810PEP-E

List of figures

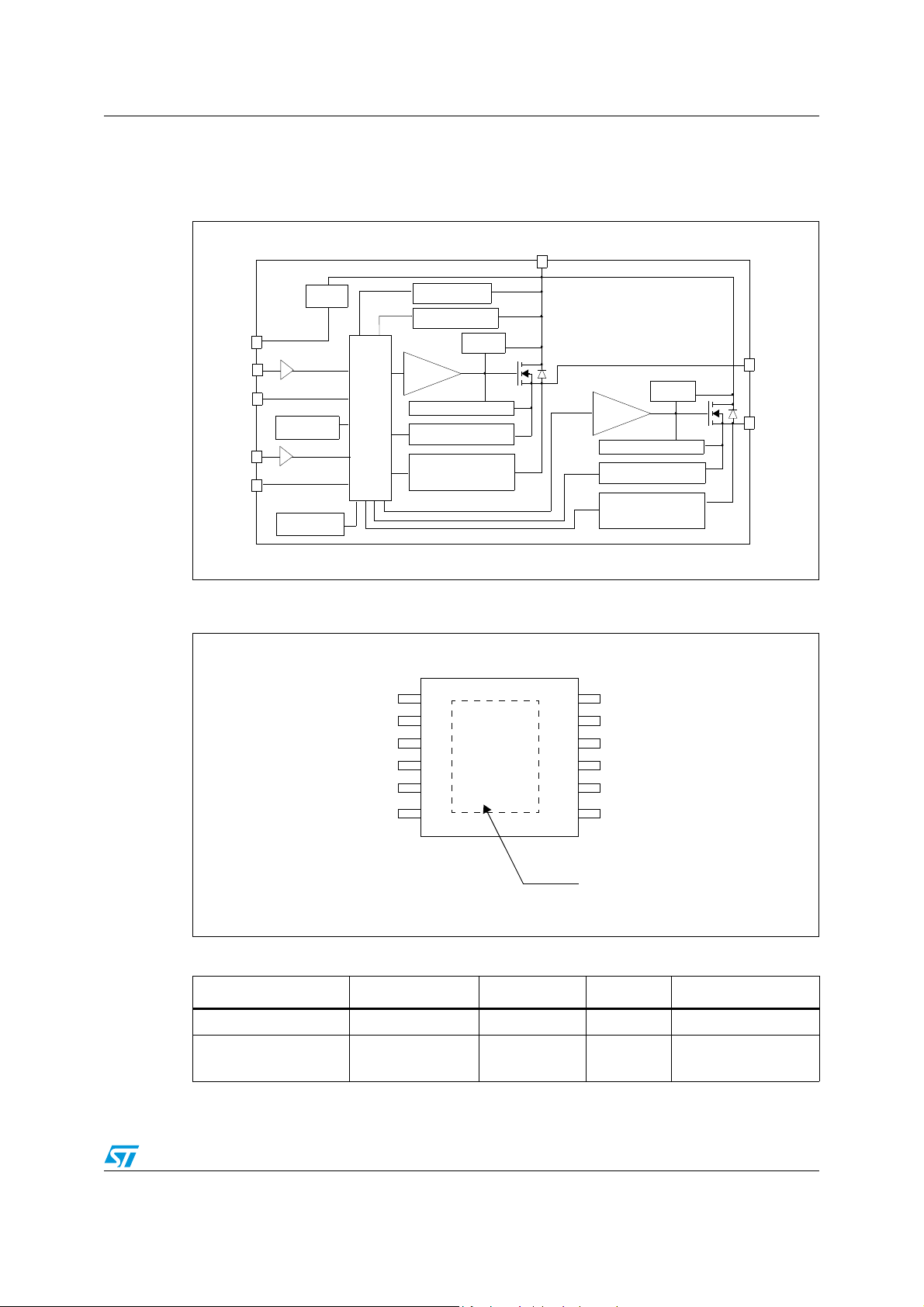

Figure 1. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. Configuration diagram (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 3. Current and voltage conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 4. Status timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 5. Switching characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 6. Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 7. Application schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 8. Open-load detection in off-state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 9. PowerSSO-12 PC board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 10. Rthj-amb vs. PCB copper area in open box free air condition (one channel ON). . . . . . . . 17

Figure 11. PowerSSO-12 thermal impedance junction ambient single pulse (one channel ON). . . . . 18

Figure 12. Thermal fitting model of a double channel HSD in PowerSSO-12 . . . . . . . . . . . . . . . . . . . 18

Figure 13. PowerSSO-12 package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 14. PowerSSO-12 tube shipment (no suffix) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 15. PowerSSO-12 tape and reel shipment (suffix “TR”) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4/25 Doc ID 10858 Rev 5

VND810PEP-E Block diagram and pin description

1 Block diagram and pin description

Figure 1. Block diagram

V

cc

V

GND

INPUT1

STATUS1

INPUT2

STATUS2

cc

CLAMP

OVERTEMP. 1

OVERTEMP. 2

LOGIC

OVERVOLTAGE

UNDERVOLTAGE

CLAMP 1

DRIVER 1

CURRENT LIMITER 1

OPEN-LOAD ON 1

OPEN-LOAD OFF 1

CLAMP 2

DRIVER 2

CURRENT LIMITER 2

OPEN-LOAD ON 2

OPEN-LOAD OFF 2

OUTPUT1

OUTPUT2

Figure 2. Configuration diagram (top view)

GND

NC

INPUT1

STATUS1

STATUS2

INPUT2

Table 2. Suggested connections for unused and not connected pins

Connection / pin Status Not connected Output Input

Floating X X X X

To ground X

1

2

3

4

5

6

12

11

10

9

8

7

V

cc

OUTPUT1

OUTPUT1

OUTPUT2

OUTPUT2

V

cc

TAB = V

cc

Through 10KΩ

resistor

Doc ID 10858 Rev 5 5/24

Electrical specifications VND810PEP-E

2 Electrical specifications

2.1 Absolute maximum ratings

Stressing the device above the rating listed in Table 3: Absolute maximum ratings may

cause permanent damage to the device. These are stress ratings only and operation of the

device at these or any other conditions above those indicated in the Operating sections of

this specification is not implied. Exposure to Absolute Maximum Rating conditions for

extended periods may affect device reliability. Refer also to the STMicroelectronics SURE

Program and other relevant quality document available on www.st.com.

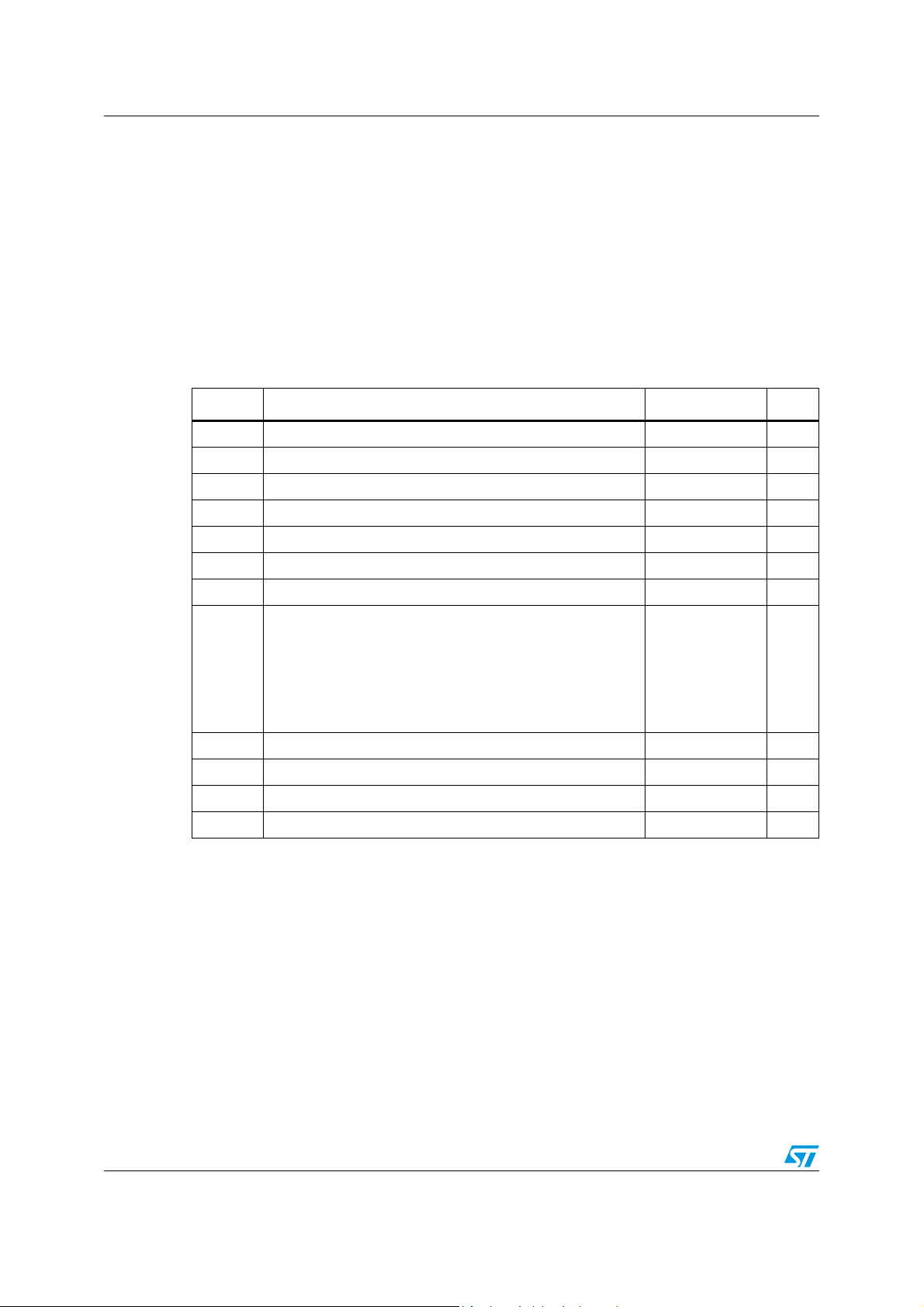

Table 3. Absolute maximum ratings

Symbol Parameter Value Unit

V

- V

- I

I

- I

I

V

T

CC

CC

GND

OUT

OUT

I

IN

STAT

ESD

P

tot

T

T

c

stg

DC supply voltage 41 V

Reverse DC supply voltage - 0.3 V

DC reverse ground pin current - 200 mA

DC output current Internally limited A

Reverse DC output current - 6 A

DC input current +/- 10 mA

DC Status current +/- 10 mA

Electrostatic discharge (human body model: R=1.5KΩ;

C = 100pF)

- INPUT

- STATUS

- OUTPUT

- V

CC

4000

4000

5000

5000

Power dissipation (per island) at TC = 25°C 54 W

Junction operating temperature Internally limited °C

j

Case operating temperature - 40 to 150 °C

Storage temperature - 55 to 150 °C

V

V

V

V

6/24 Doc ID 10858 Rev 5

VND810PEP-E Electrical specifications

2.2 Thermal data

Table 4. Thermal data (per island)

Symbol Parameter Maximum value Unit

R

thj-case

R

thj-amb

1. When mounted on a standard single-sided FR-4 board with 1cm2 of Cu (at least 35 µm thick) connected to

all V

2. When mounted on a standard single-sided FR-4 board with 8cm2 of Cu (at least 35 µm thick) connected to

all V

Thermal resistance junction-case 2.3 °C/W

Thermal resistance junction-ambient

(one chip ON)

pins.

CC

pins.

CC

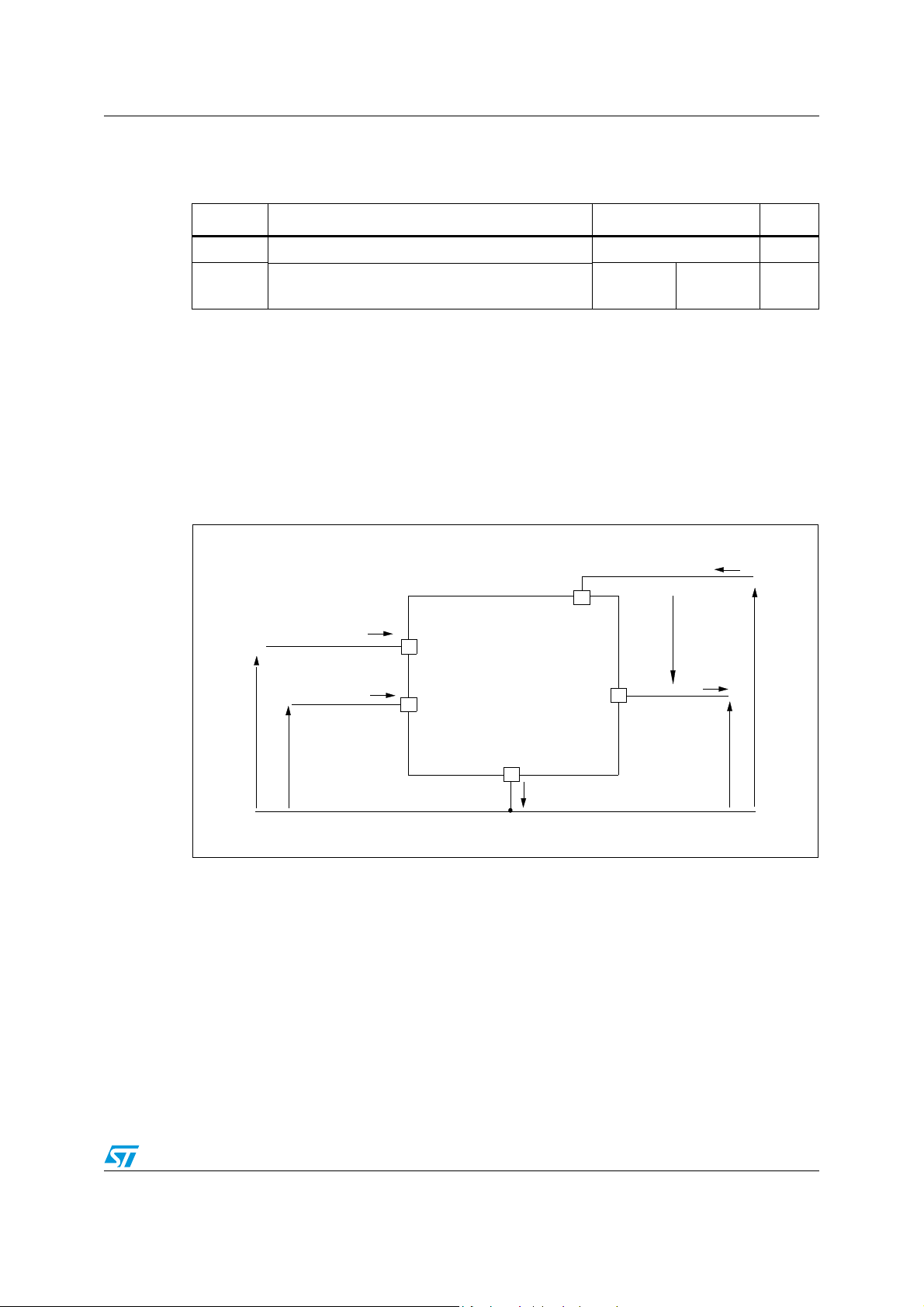

2.3 Electrical characteristics

Values specified in this section are for 8V < V

otherwise stated.

Figure 3. Current and voltage conventions

I

INn

V

INn

V

STATn

I

STATn

INPUTn

STATUSn

(1)

61

< 36V; -40°C < Tj < 150°C, unless

CC

V

(*)

F1

V

CC

I

OUTn

OUTPUTn

V

GND

50

OUTn

(2)

°C/W

I

S

V

CC

Note: V

Fn

= V

CCn

- V

during reverse battery condition.

OUTn

Doc ID 10858 Rev 5 7/24

I

GND

Electrical specifications VND810PEP-E

Table 5. Power outputs

Symbol Parameter Test conditions Min Typ Max Unit

V

CC

V

USD

V

OV

R

ON

I

S

I

L(off1)

I

L(off2)

I

L(off3)

I

L(off4)

Operating supply

voltage

5.5 13 36 V

Undervoltage shutdown 3 4 5.5 V

Overvoltage shutdown 36 V

12

12

5

160

320mΩmΩ

40

µA

25

µA

7

mA

5µA

3µA

On-state resistance

Supply current

Off-state output current V

Off-state output current V

Off-state output current

Off-state output current

I

= 1A; Tj = 25°C

OUT

= 1A; V

I

OUT

Off-state; V

= V

V

IN

OUT

Off-state; V

= V

V

IN

OUT

Tj = 25°C

On-state; V

= 0A

I

OUT

= V

IN

OUT

= 0V; V

IN

V

= V

IN

OUT

Tj = 125°C

V

= V

IN

OUT

Tj = 25°C

> 8V

CC

= 13V;

CC

= 0V

= 13V;

CC

= 0V;

= 13V; V

CC

IN

= 5V;

= 0V 0 50 µA

= 3.5V -75 0 µA

OUT

= 0V; V

= 0V; V

CC

CC

= 13V;

= 13V;

Table 6. Protections and diagnostics

Symbol Parameter Test conditions Min. Typ. Max. Unit

T

T

t

SDL

I

V

demag

Shutdown temperature 150 175 200 °C

TSD

T

Reset temperature 135 °C

R

Thermal hysteresis 7 15 °C

hyst

Status delay in overload

conditions

Current limitation

lim

Turn-off output clamp

voltage

T

j

V

CC

5.5V < V

I

= 1A; L = 6mH

OUT

> T

= 13V

CC

TSD

< 36V

3.5 5 7.5

V

-41V

CC

CC

-48V

20 µs

7.5AA

-

CC

55

V

Note: To ensure long term reliability under heavy overload or short circuit conditions, protection

and related diagnostic signals must be used together with a proper software strategy. If the

device is subjected to abnormal conditions, this software must limit the duration and number

of activation cycles.

8/24 Doc ID 10858 Rev 5

Loading...

Loading...