现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

®

VIPer50/SP

- VIPer50A/ASP

SMPS PRIMARY I.C .

TYPE V

DSS

I

n

R

DS(on)

VIPer50/SP 620V 1.5 A 5 Ω

VIPer50A/ASP 700V 1.5 A 5.7 Ω

■ ADJUSTABLE SWITCHING FREQUENCY UP

TO 200 kHz

■ CURRENT MODE CONTROL

■ SOFT START AND SHUT DOWN CONTROL

■ AUTOMATIC BURST MODE OPERATION IN

STAND-BY CONDITION ABLE TO MEET

“BLUE ANGEL” NORM (<1W TOTAL POWER

CONSUMPTION)

■ INTERNALLY TRIMMED ZENER REFERENCE

■ UNDERVOLTAGE LOCK-OUT WITH

HYSTERESIS

■ INTEGRATE D START-UP SUPPLY

■ AVALANCHE RUGGED

■ OVERTEMPERATURE PROTECTION

■ LOW STAND-BY CURRENT

■ ADJUSTABLE CURRENT LIMITATION

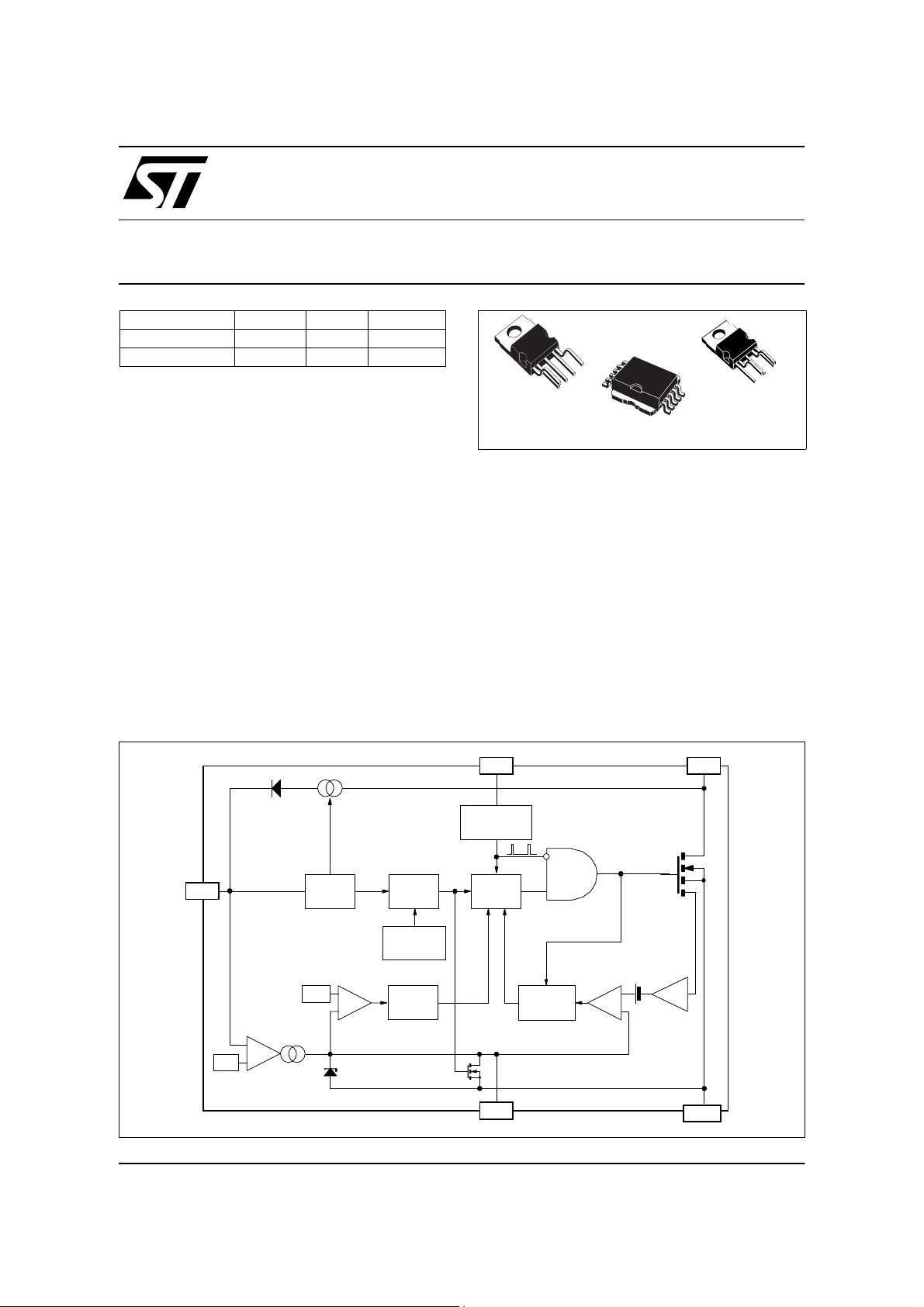

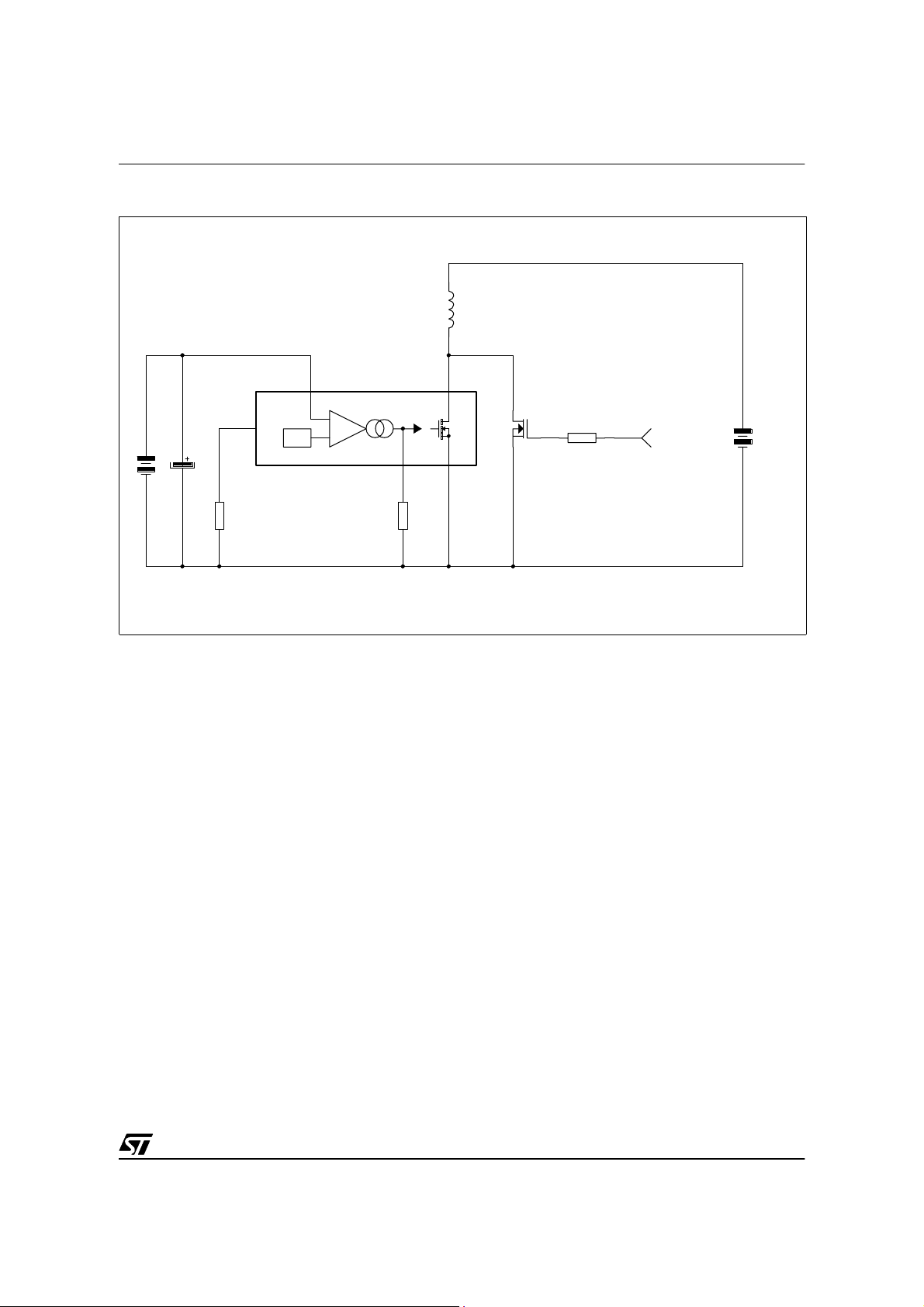

BLOCK DIAGRAM

PENTAWATT HV PENTAWATT HV

10

1

(022Y)

PowerSO-10™

DESCRIPTION

VIPer50

™/50A, made using VIPower M0

Technology, combines on the same silicon chip a

state-of-the-art PWM circuit together with an

optimized high voltage avalanche rugged Vertical

Power MOSFET (620V or 700V / 1.5A).

Typical appli cations cover off line power supp lies

with a secondary power capability of 25W in wide

range conditio n and 50W in single range or with

doubler configuration. It is compatible from both

primary or secondary regulation loop despite

using around 50% less components when

compared with a discrete solution. Burst mode

operation is an additional featur e of this device ,

offering the possibility to operate in stand-by

mode without extra components.

OSC

DRAIN

ON/OFF

OSCILLATOR

VDD

13 V

+

ERROR

AMPLIFIER_

UVLO

LOGIC

0.5 V +

_

4.5 V

SECURITY

LATCH

FF

R/S

S

OVERTEMP.

DETECTOR

1.7 µs

DELAY

PWM

LATCH

R1

S

FF

R2 R3

COMP

Q

250 ns

BLANKING

0.5V

+

+

_

_

2 V/A

CURRENT

AMPLIFIER

SOURCE

1

9

2

0

0

C

F

Q

May 2003 1/23

1

VIPer50/SP - VIPer50A/ASP

ABSOLUTE MAXIMUM RATING

Symbol Parameter Value Unit

Continuous Drain-Source Volt age (Tj=25 to 125° C)

V

I

V

V

OSC

V

COMP

I

COMP

V

esd

for VIPer50/SP

DS

for VIPe r50A/ASP

Maximum Current Internally limited A

D

Supply Voltage 0 to 15 V

DD

Voltage Range Input 0 to V

Voltage Range Input 0 to 5 V

Maximum Continuous Current ± 2mA

Electros tatic Disc harge (R =1.5kΩ; C=100pF) 4000 V

Avalanche Drain-Source Current, Repetitive or Not Re petitive

I

D(AR)

(TC=100°C; Pulse width li m ited by Tj max; δ < 1%)

for VIPer50/SP

for VIPer50A/ASP

P

T

T

Power Dissipation at Tc=25ºC60W

tot

Junction Operating Temperature Internally limited °C

j

Storage Temperature -65 to 150 °C

stg

THERMAL DATA

Symbol Parameter PENTAWATT HV PowerSO-10™ (*) Unit

R

thj-case

R

thj-amb.

(*) When mounted using the minimum reco m m ended pad size on FR-4 board .

Thermal Resista nce Juncti on-case Max 1.9 1.9 °C/W

Thermal Resistance Ambient-case Max 60 50 °C/W

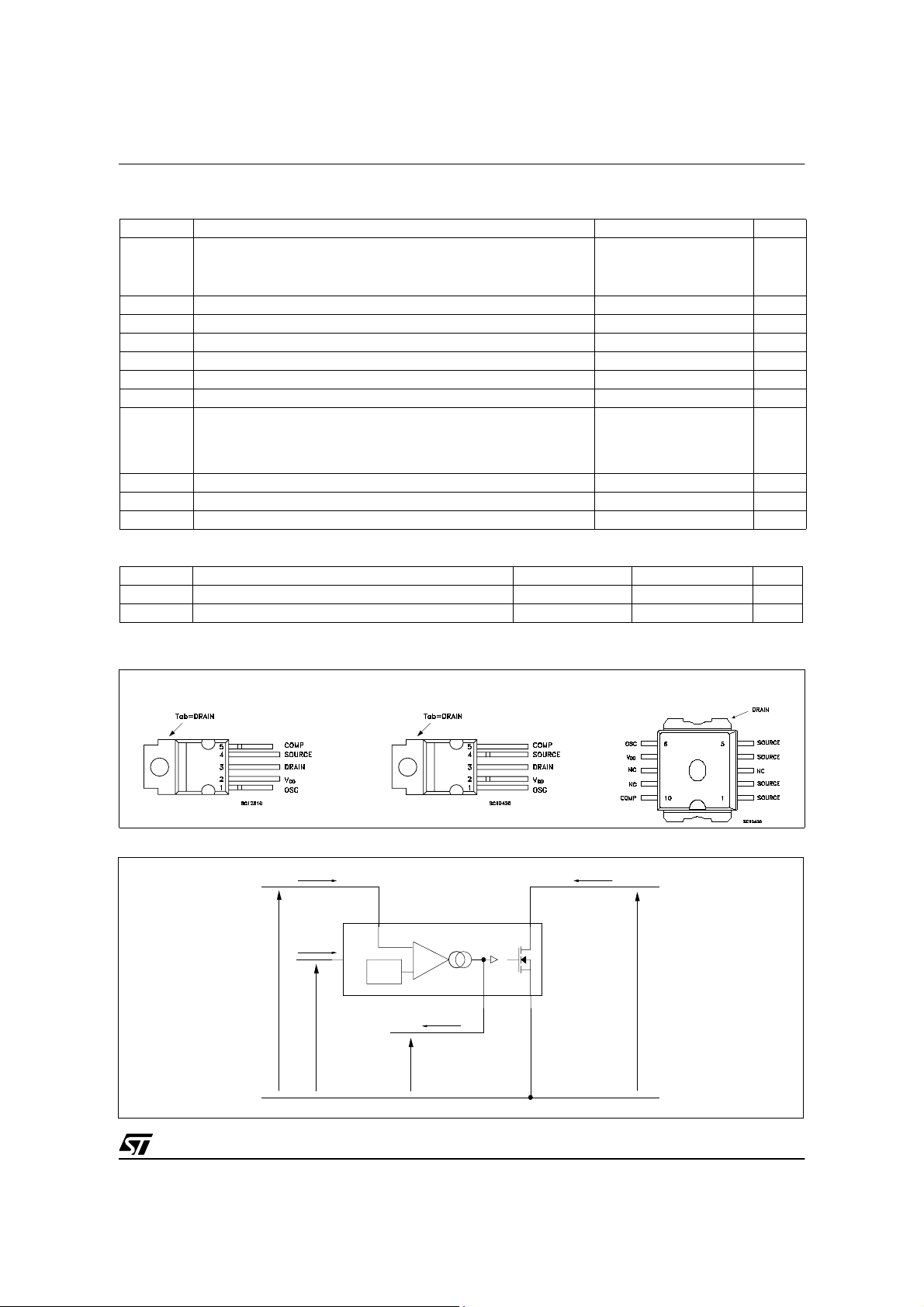

CONNECTION DIAGRAMS (Top View)

-0.3 to 620

-0.3 to 700

DD

1.5

1

V

V

V

A

A

PENTAWATT HV PENTAWATT HV (022Y)

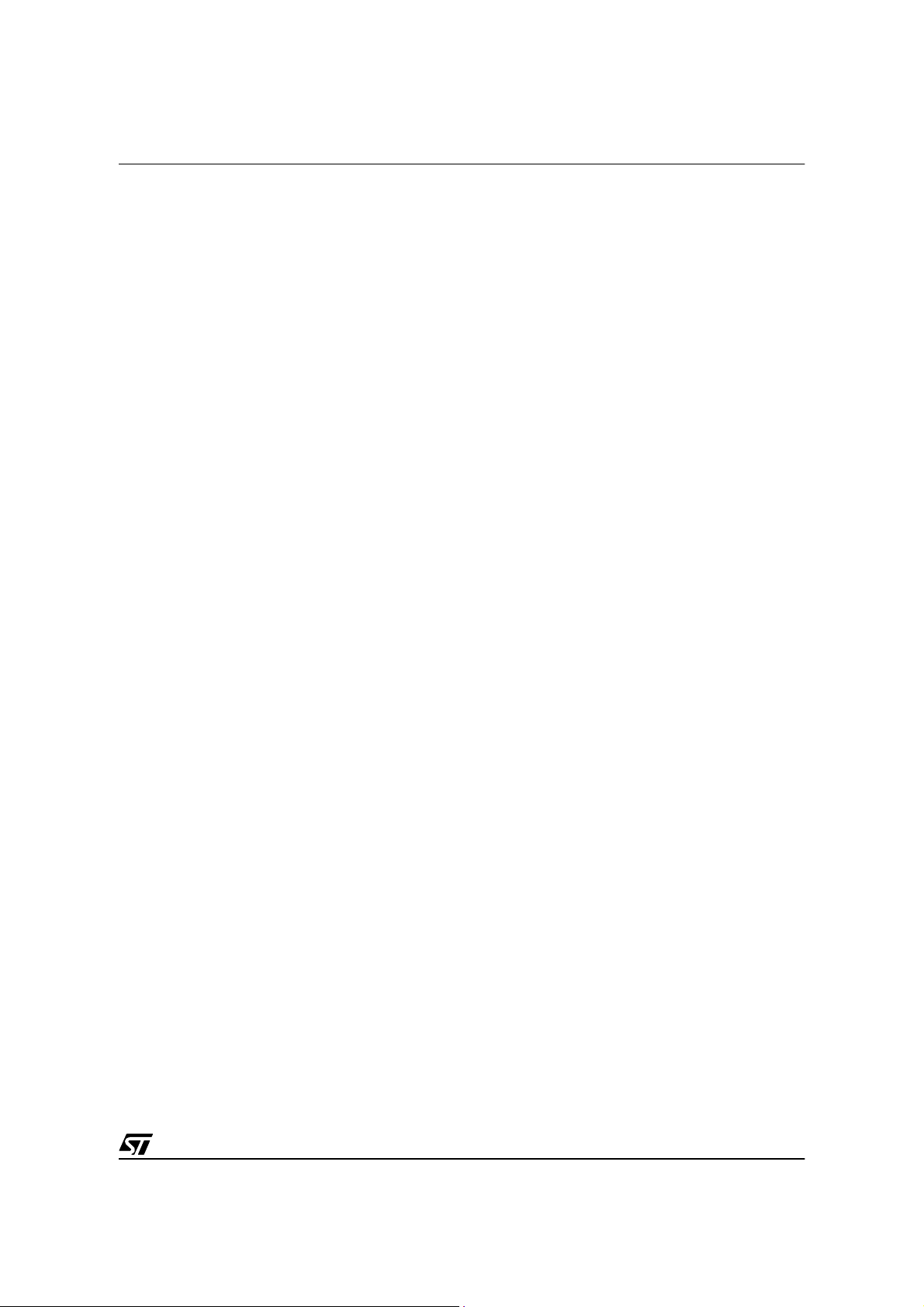

CURRENT AND VOLTAGE CONVENTIONS

DD

I

IOSC

OSC

13V

VDD

VOSC

+

VCOMP

COMP

I

DRAINVDD

COMP SOURCE

I

FC00020

PowerSO-10™

D

VDS

2/23

1

VIPer50/SP - VIPer50A/ASP

ORDERING NUMBERS

PENTAWATT HV PENTAWATT HV (022Y) PowerSO-10™

VIPer50 VIPer50 (022Y) VIPer50SP

VIPer50A VIPer50A ( 022Y) VIPer50ASP

PINS FUNCTIONAL DESCRIPTION

DRAIN PIN:

Integrated Power MOSFET drain pin. It provide s

internal bias current during start-up via an

integrated high voltage current source which is

switched o ff during normal opera tion. The device

is able to handle an uncl amped current dur ing its

normal opera tion, assu ring self pr otectio n agains t

voltage surges, PCB stray inductance, and

allowing a snubberless operation for low output

power.

SOURCE Pin:

Power MOSFET source pin. Primary side circuit

common ground connection.

VDD Pin:

This pin provides two functions:

- It corresponds to th e low voltage su pply of the

control part of the circuit. If VDD goes below 8V,

the start-up cur rent sou rce is activ ate d and the

output power MOS FET is sw itc he d off until the

VDD voltage reache s 11V. During this phase,

the internal current consumption is reduced,

the VDD pin sources a current of about 2mA

and the COMP pin is shorted to ground. After

that, the curren t source is shut down, and the

device tries to start up by switching again.

- This pin is also connected to the error amplifier,

in order to all ow primary as wel l as secondar y

regulation configurations. In case of primary

regulation, an internal 13V trimmed reference

voltage is used to maintain VDD at 13V. For

secondary reg ulation, a voltag e between 8.5V

and 12.5V will be put on VDD pin by transformer

design, in order to stick the output of the

transconductance amplifier to the high state.

The COMP pin behaves as a constant current

source, and can easily be connected to the

output of an optocoupler. Note that any

overvoltage due to regulation loop failure is still

detected by the error amplifier through the V

DD

voltage, which cannot overpass 13V. The

output voltage will be somewhat higher than the

nominal one, but still under control.

COMP PIN:

This pin provides two functions:

- It is the output of the error transconductance

amplifier, and allows for the connection of a

compensation network to pro vide the desir ed

transfer function of the regulation loop. Its

bandwidth can easily be adjusted to the

needed value with usual components value. As

stated above, secondary regulation

configurations are also implemented through

the COMP pin.

- When the COMP voltage goes bel ow 0.5V , the

shut-down of the circuit occurs, with a zero

duty cycle for the power MOSFET. This fea ture

can be used to sw itch off the converter, and is

automatically activ ated by the regulation l oop

(whatever is the configuration) to provide a

burst mode operation in case of negligible

output power or open load condition.

OSC PIN:

An Rt-Ct network must be connected on that pin to

define the swi tching frequen cy. Note tha t despite

the connection of Rt to VDD, no significant

frequency change oc curs for VDD varying from 8V

to 15V. It also provides a synchronization

capability, when connected to an external

frequency source.

3/23

1

VIPer50/SP - VIPer50A/ASP

AVALANCHE CHARACTERISTICS

Symbol Parameter Max Value Unit

Avalanch e Curr en t, Rep etitive or Not Repeti tiv e

I

D(AR)

E

(ar)

(pulse widht limited by Tj max; δ < 1%)

for VIPe r50/SP

for VIPe r50A/ASP (see fig. 12)

Sing l e Pu lse Aval an che Ener gy

(starting Tj =25ºC, ID=I

) (see fig.12)

D(ar)

1.5

1.0

30 mJ

A

A

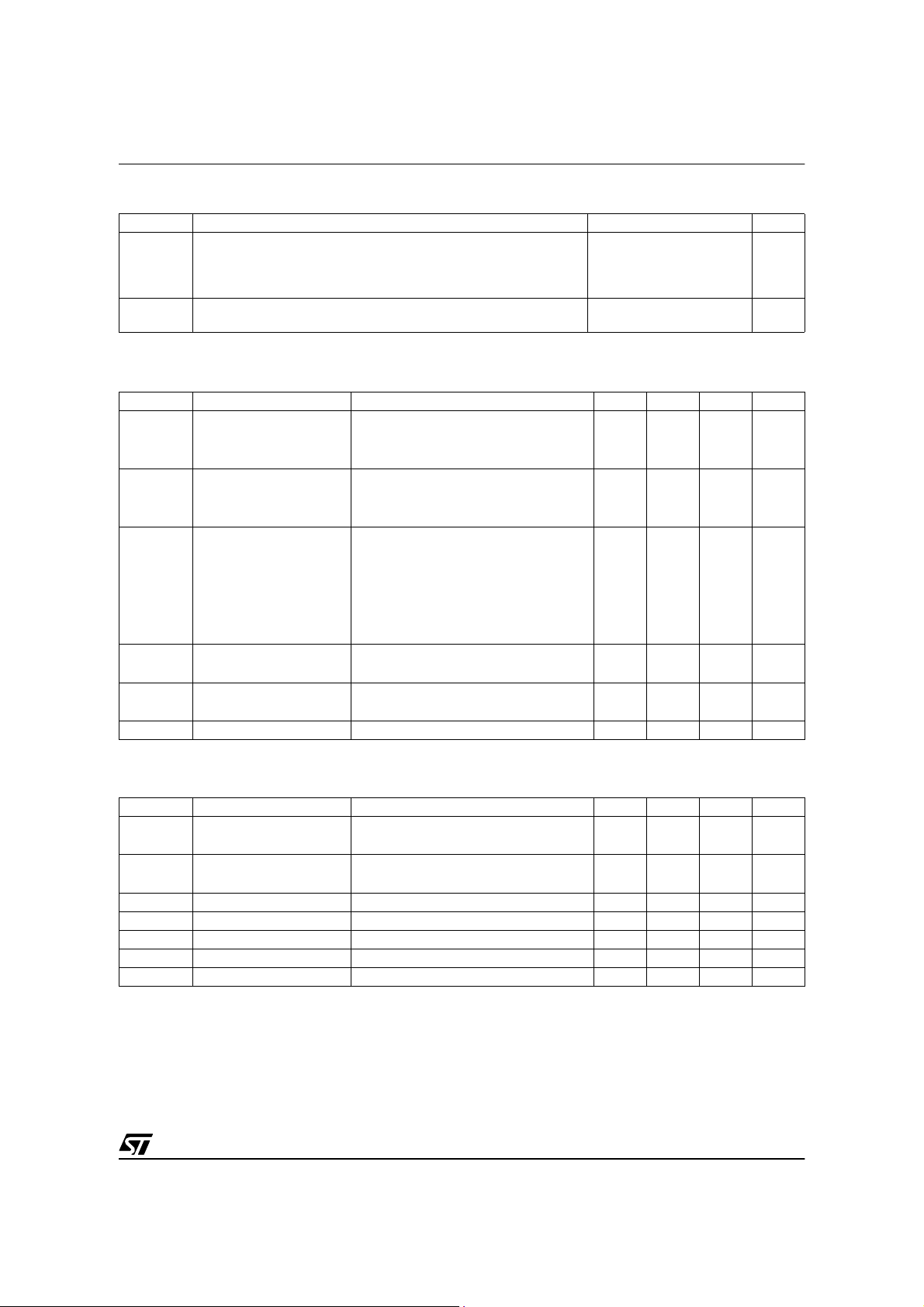

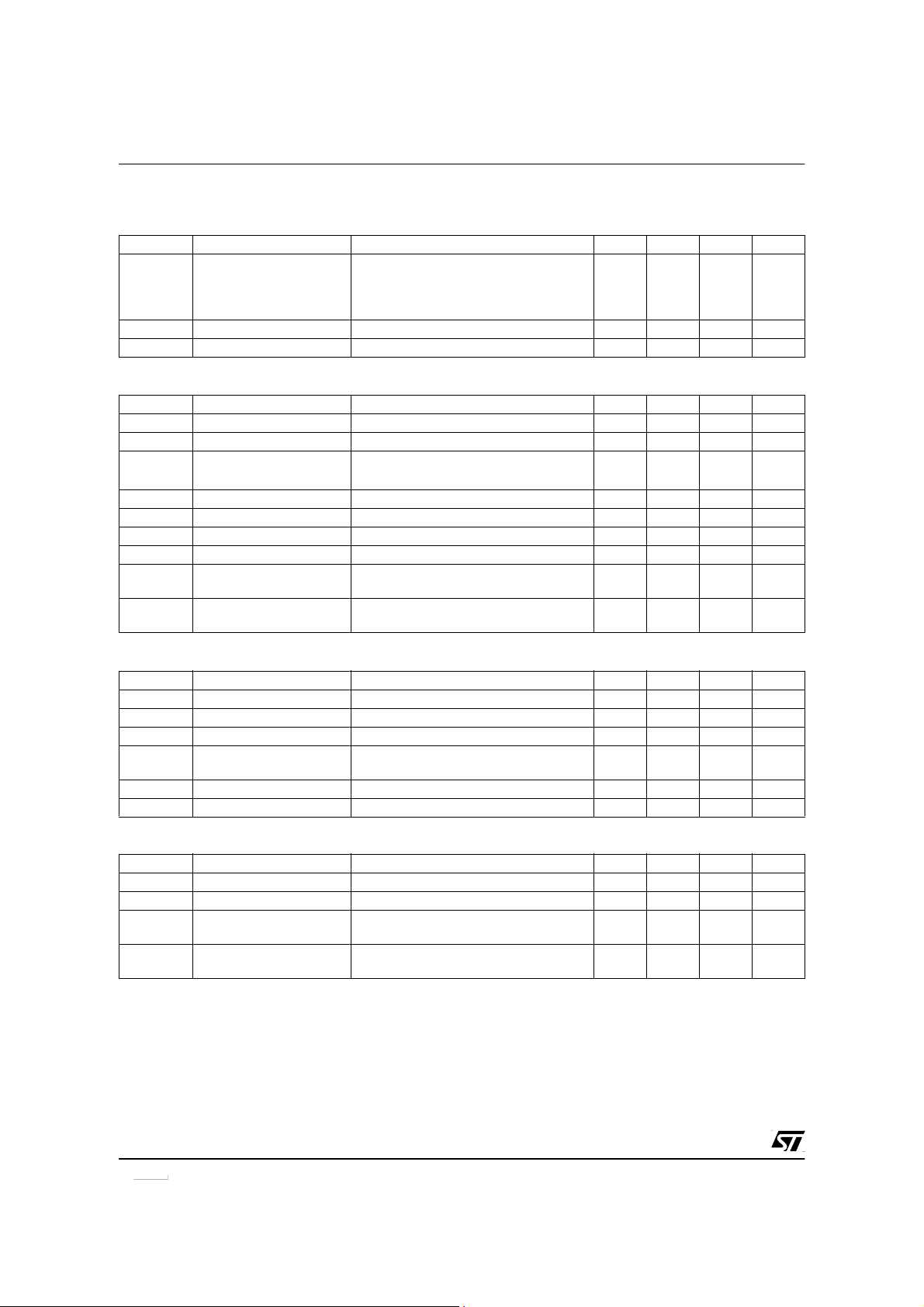

ELECTRICAL CHARACTERISTICS

(T

=25°C; VDD=13V, unless otherwise specified)

j

POWER SECTION

Symbol Parameter Test Conditions Min Typ Max Unit

BV

I

DSS

R

DS(on)

t

C

(1) On Induct iv e Load, Clamped.

Drain-Source Voltage

DSS

Off-State Drain Curre nt

Static Drain-Source

On Resist ance

t

Fall Time

f

Rise Time

r

Output Capacitance VDS=25V 120 pF

oss

ID=1mA; V

for VIPer50/SP

for VIPer50A/ASP (see fig.5)

V

=0V; Tj=125°C

COMP

VDS=620V for VIPer50/SP

VDS=700V for VIPer50A/ASP

I

=1A

D

for VIPer50/SP

for VIPer50A/ASP

=1A; Tj=100°C

I

D

for VIPer50/SP

for VIPer50A/ASP

=0.2A; VIN=300V (1)

I

D

(See fig. 3)

=1A; VIN=300V (1)

I

D

(See fig. 3)

COMP

=0V

620

700

1

1

4.0

4.6

5.0

5.7

9.0

10.3

100 ns

50 ns

SUPPLY SECTION

Symbol Parameter Test Conditions Min Typ Max Unit

I

DDch

I

DD0

I

DD1

I

DD2

V

DDoff

V

DDon

V

DDhyst

Start-Up Charging

Current

VDD=5V; VDS=35V

(see fig. 2 and fig. 15)

Oper at i ng Su pp ly Cu rrent VDD=12V; FSW=0kHz

(see fig. 2)

Oper at i ng Su pp ly Cu rrent VDD=12V; Fsw=100kHz 14 mA

Oper at i ng Su pp ly Cu rrent VDD=12V; Fsw=200kHz 16 mA

Undervoltage Shutdo wn (See fig. 2) 7.5 8 9 V

Undervoltage Reset (See fig. 2) 11 12 V

Hyst ere sis Star t -u p (See fig. 2) 2.4 3 V

-2 mA

12 16 mA

V

V

mA

mA

Ω

Ω

Ω

Ω

4/23

VIPer50/SP - VIPer50A/ASP

ELECTRICAL CHARACTERISTICS (continued)

OSCILLATOR SECTION

Symbol Parameter Test Conditions Min Typ Max Unit

Rt=8.2KΩ; Ct=2.4nF

F

V

OSCih

V

OSCil

SW

Oscillat or Freque ncy

Total Variation

Oscillator Peak Voltage 7.1 V

Oscillator Valley Voltage 3.7 V

VDD=9 to 15V;

with R

± 1%; Ct± 5%

t

(see fig. 6 and fig. 9)

ERROR AMPLIFIER SECTIO N

Symbol Parameter Test Conditions Min Typ Max Unit

V

DDreg

∆V

DDreg

G

A

VOL

G

V

COMPLO

V

COMPHI

I

COMPLO

I

COMPHI

VDD Regulati on Point I

=0mA (see fig . 1) 12.6 13 13.4 V

COMP

Total Variation Tj=0 to 100°C 2 %

Unity Gain Bandwidth

BW

From Input =VDD to Output = V

COMP pin is open (see fig. 10)

COMP

Open Loop Voltage Gain COMP pin is open (see fig. 10) 45 52 dB

DC Transconductance V

m

Output Low Level I

Output High Level I

Output Low Current

Capability

Output High Current

Capability

=2.5V (see fig. 1) 1.1 1.5 1.9 mA/V

COMP

= -400µA; VDD=14V 0.2 V

COMP

=400µA; VDD=12V 4.5 V

COMP

V

=2.5V; VDD=14V -600 µA

COMP

V

=2.5V; VDD=12V 600 µA

COMP

90 100 110 kHz

150 kHz

PWM COMPARATOR SECTION

Symbol Parameter Test Conditions Min Typ Max Unit

H

V

COMPoffVCOMP

I

Dpeak

t

t

t

on(min)

∆V

ID

/ ∆I

COMP

DPEAK

Offs et I

V

=1 to 3 V 1.422.6V/A

COMP

=10mA 0.5 V

DPEAK

Peak Current Limitation VDD=12V; COMP pin open 1.5 2 2.7 A

Current Sense Delay to

d

Turn-Off

Blanking Time 250 360 ns

b

ID=0.5A 250 ns

Minimum On Time 350 1200 ns

SHUTDOWN AND OVERTEMPERATURE SE CTIO N

Symbol Parameter Test Conditions Min Typ Max Unit

V

COMPth

t

DISsu

T

T

hyst

Restart Th reshold (see fig. 4) 0.5 V

Disable Set Up Time (see fig. 4) 1.7 5 µs

Ther ma l Shutdo w n

tsd

Temperature

Ther ma l Shutdo w n

Hysteresis

(See fig. 8) 140 170 °C

(See fig. 8) 40 °C

5/23

VIPer50/SP - VIPer50A/ASP

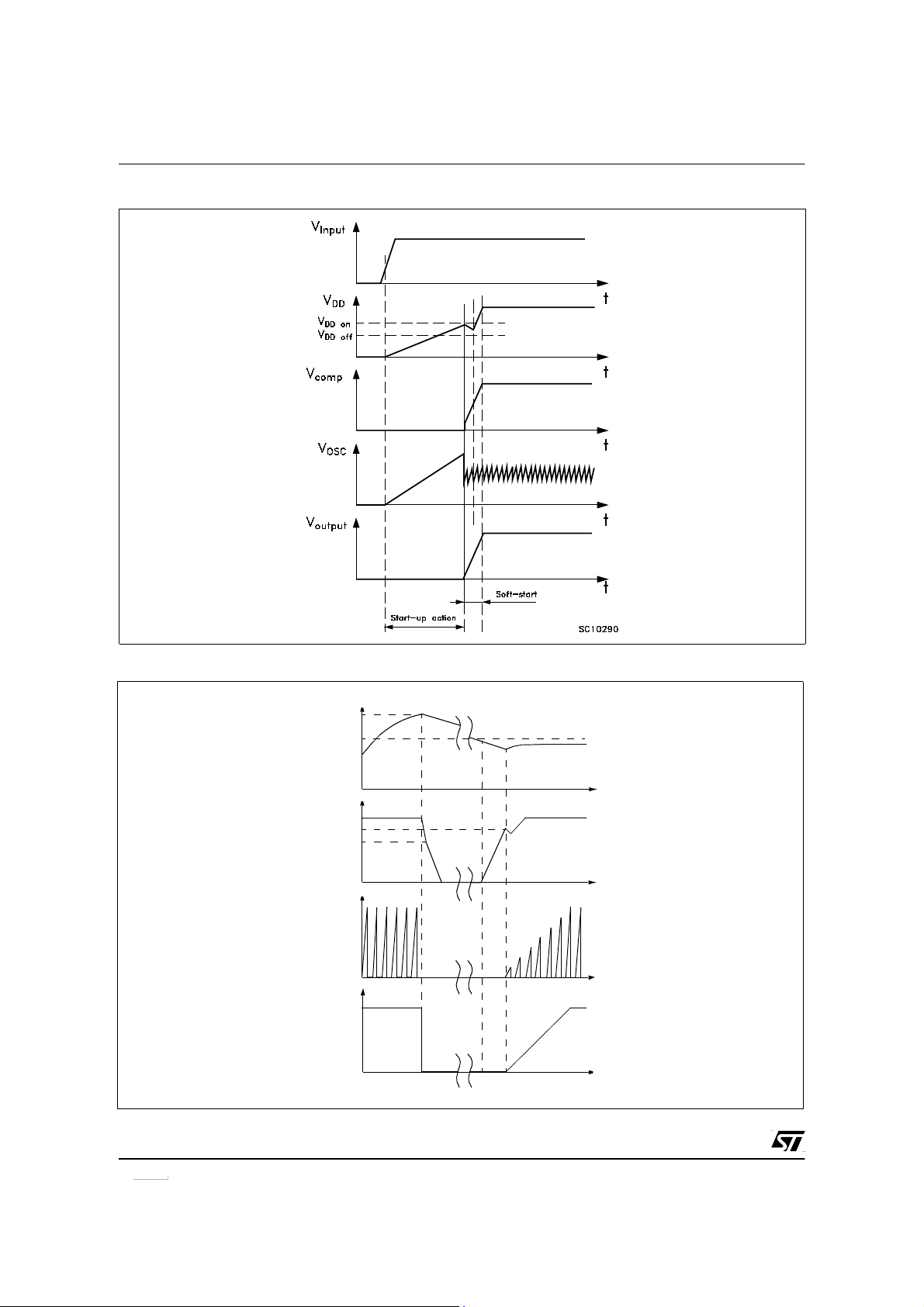

Figure 1: VDD Regulation Point

ICOM P

ICOMPHI

0

ICOMPLO

VDDreg

Figure 3: Transition Time

I

D

10% Ipeak

Slope =

Gm in mA/V

FC00150

Figure 2: Undervoltage Lockout

I

DD

I

DD0

VDD

VDDhyst

VDDoff

VDS= 35 V

Fsw = 0

VDDon

V

DD

IDDch

FC00170

Figure 4: Shut Down Action

VOSC

t

VCOMP

t

tDISsu

V

DS

90% V

10% V

tf

D

D

t

tr

FC00160

VCOMPth

ID

ENABLE

DISA BLE

Figure 5: Breakdown Voltage Vs. Temperature Figure 6: Typical Frequency Variation

1.15

BVDSS

(Normalized)

1.05

0.95

1.1

1

0 20406080100120

Temp erature (°C)

FC00180

1

(%)

0

-1

-2

-3

-4

-5

0 20406080100120140

Temperature (°C)

t

t

ENABLE

FC00060

FC00190

6/23

VIPer50/SP - VIPer50A/ASP

Figur e 7: Start-Up Waveforms

Figure 8: Overtemperature Protection

T

T

tsd-Thyst

V

ddon

V

ddoff

V

comp

tsc

V

T

dd

I

J

t

t

d

t

t

SC10191

7/23

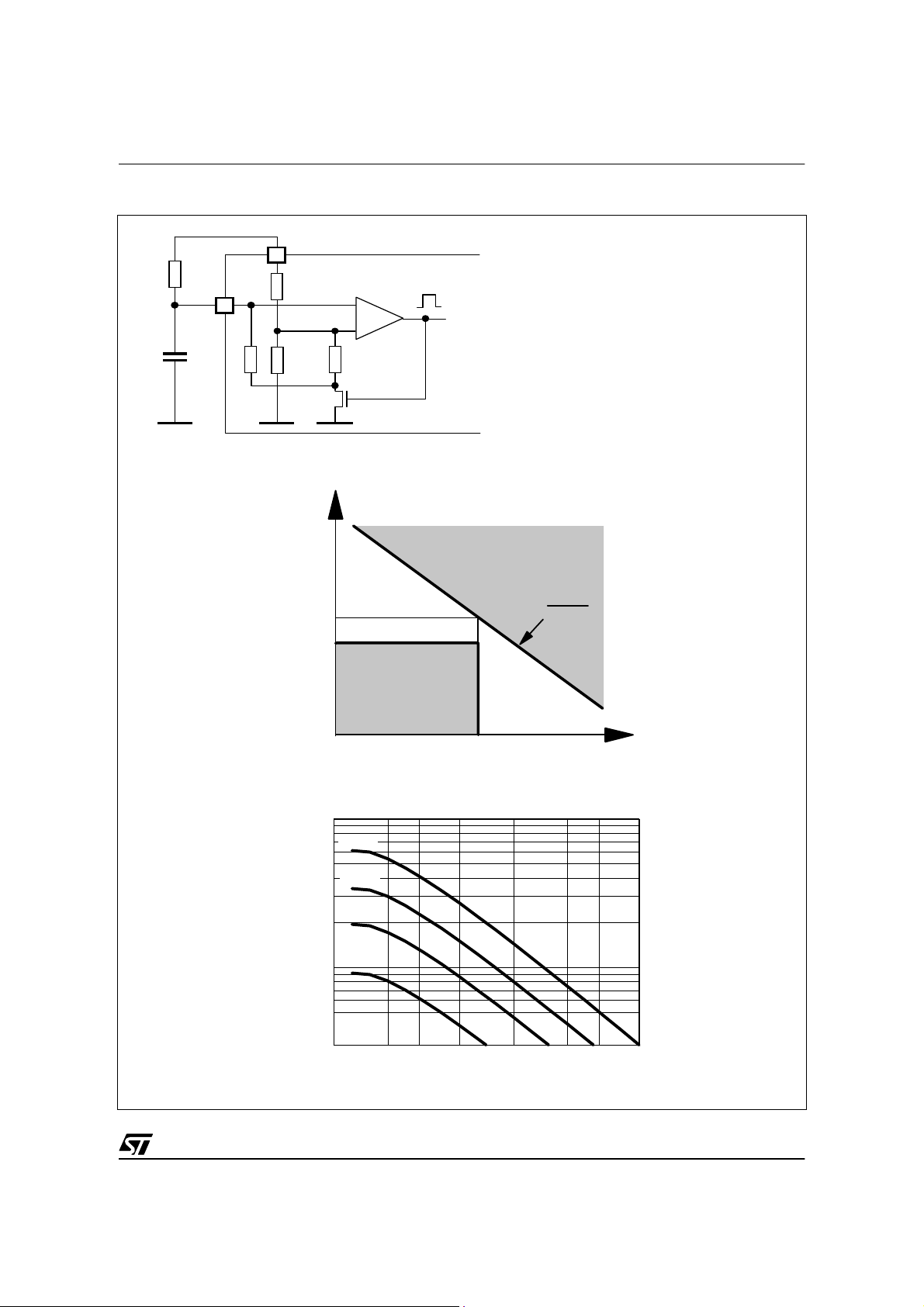

Figur e 9: Oscillator

VIPer50/SP - VIPer50A/ASP

Ct

Rt

OSC

~360Ω

VDD

C

t

22nF

15nF

FC00050

Forbidden area

CLK

Forbidden area

For Rt >1.2KΩ

and

Ct ≥ 15nF if FSW ≤ 40KHz

F

SW

Ct(nF) =

2.3

----------- -

=

880

Fsw(kHz)

⋅

RtC

t

550

--------------------- -

–

1

Rt150

–

40kHz

Fsw

Oscillator frequency vs Rt and Ct

1,000

500

300

200

100

Ct = 1.5 nF

Ct = 2.7 nF

Ct = 4.7 nF

Ct = 10 nF

FC00030FC00030

Frequency (kHz)

50

30

1 2 3 5 10 20 30 50

Rt (kΩ)

8/23

1

VIPer50/SP - VIPer50A/ASP

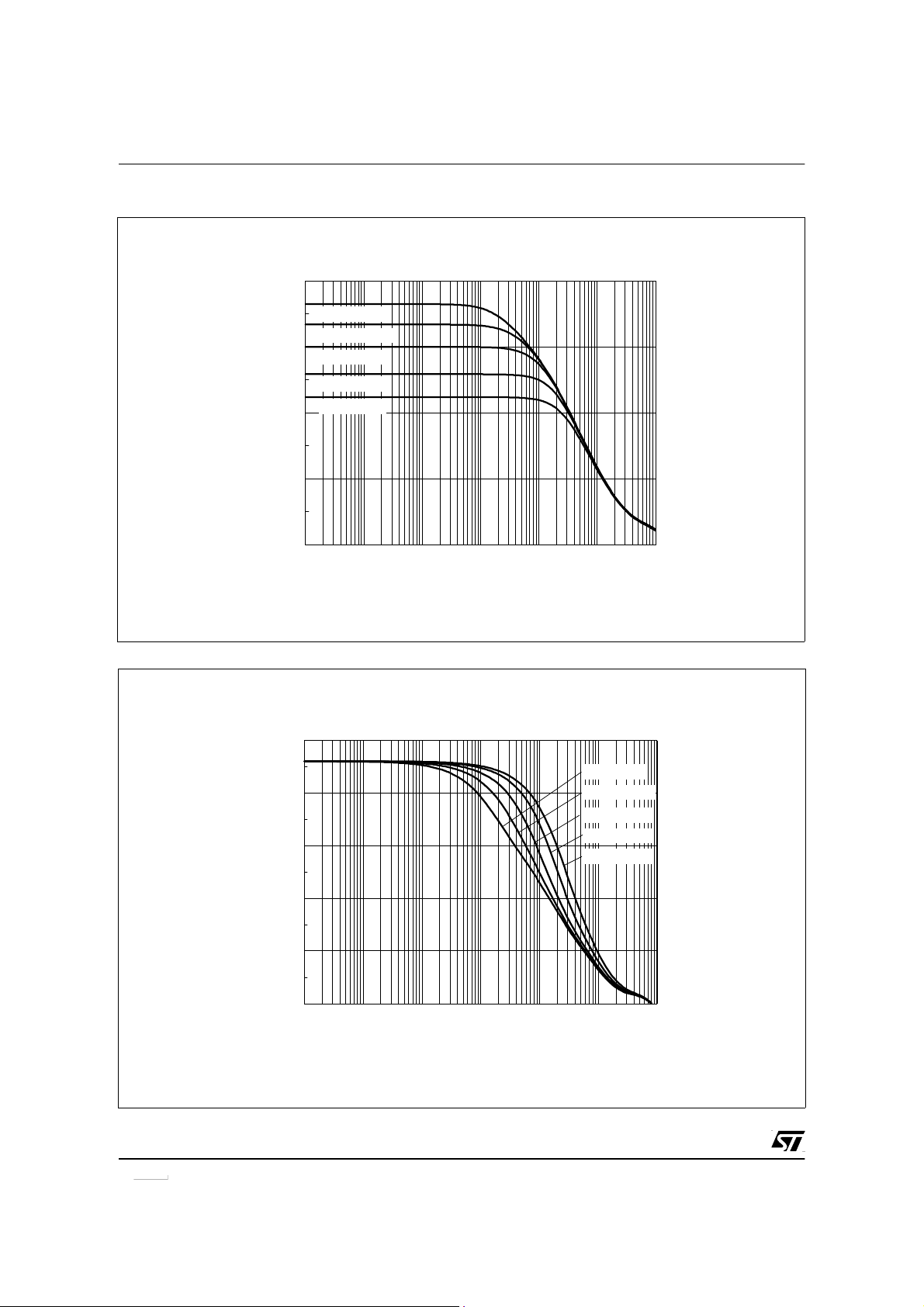

Figure 10: Error Amplifier Frequency Response

60

RCOMP = +∞

RCOMP = 270k

40

RCOMP = 82k

RCOMP = 27k

RCOMP = 12k

20

V oltage Gain (dB)

0

(20)

0.001 0.01 0.1 1 10 100 1,000

Figure 11: Error Amplifier Phase Response

FC00200

Frequency (kHz)

9/23

200

RCOMP = +

RCOMP = 270k

RCOMP = 82k

RCOMP = 27k

RCOMP = 12k

Phase (°)

150

100

50

0

(50)

0.001 0.01 0.1 1 10 100 1,000

Frequency (kHz)

FC00210

∞

1

Figure 12: Avalanche Test Circuit

L1

1mH

VIPer50/SP - VIPer50A/ASP

BT2

12V

C1

47uF

16V

1

R2

1k

OSC

U1

VIPer100

23

DRAINVDD

-

13V

+

COMP SOURCE

54

R3

100

Q1

2 x STHV102FI in parallel

R1

47

GENERATOR INPUT

500us PULSE

FC00195

BT1

0 to 20V

10/23

1

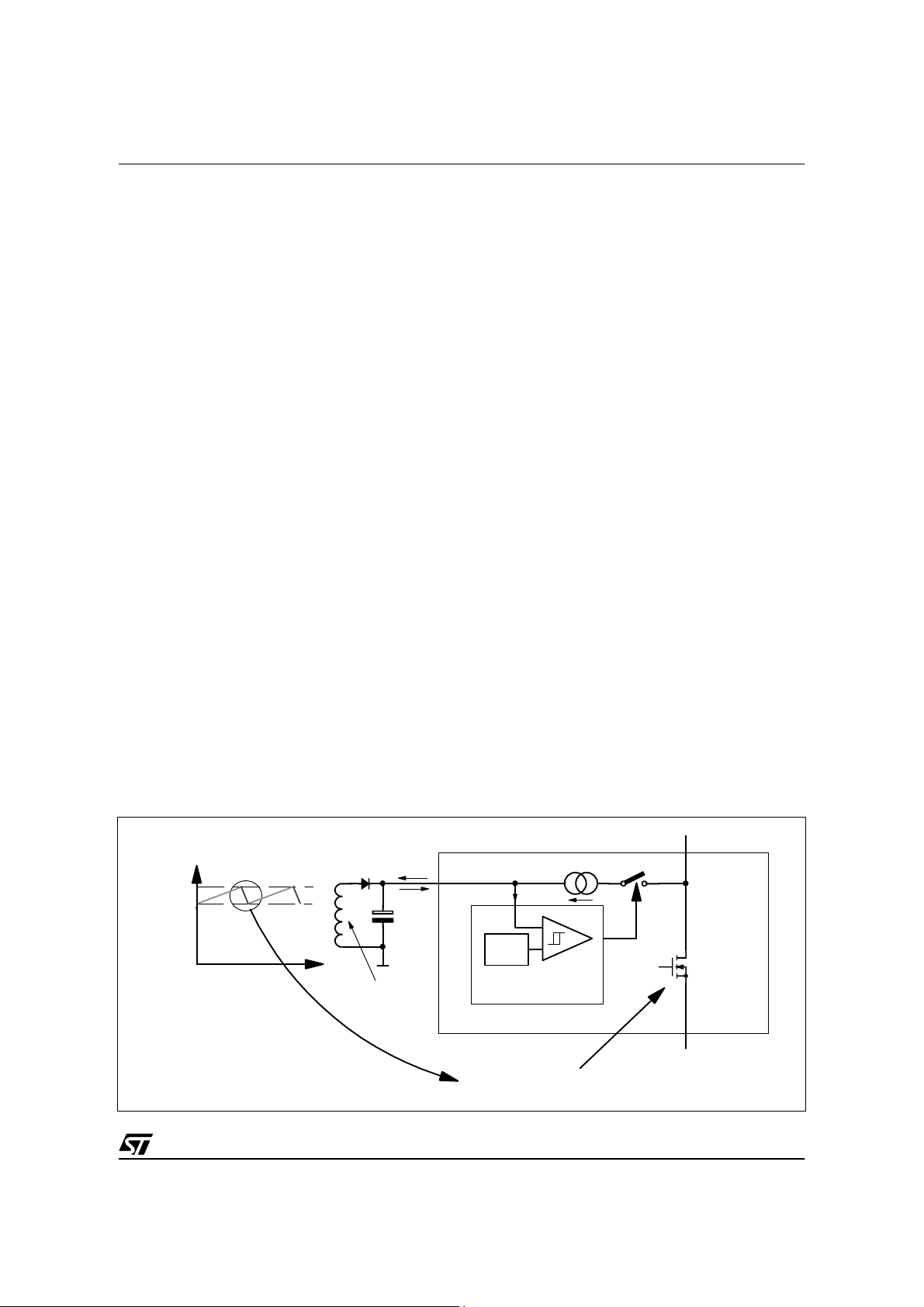

Figure 13: Off Line Power Supply With Auxiliary Supply Feedback

F1

13V

BR1

C2

C4

+

C11

D1

R1

D3

R7

COMP SOURCE

C6

R3

C3

DRAINVDD

VIPer50

AC IN

TR2

C1

R9

R2

OSC

C5

VIPer50/SP - VIPer50A/ASP

TR1

D2

C7

C10

L2

C9

FC00301

+Vcc

GND

Figure 14: Off Line Power Supply With Optocoupler Feedback

F1

13V

BR1

+

C2

D3

C4

COMP SOURCE

C11

D1

R1

C3

R7

DRAINVDD

VIPer50

C6

R3

AC IN

TR2

C1

R9

R2

OSC

C5

TR1

D2

C7

C10

R6

ISO 1

U2

C8

L2

C9

R4

R5

+Vcc

GND

FC0 0311

11/23

1

VIPer50/SP - VIPer50A/ASP

OPERATION DESCRIPTION:

CURRENT MODE TOPOLOGY

The current mode control method, like the one

integrated in the VIPer50/50A uses two control

loops - an i nner curr ent contro l loop an d an outer

loop for voltage control. When the Power

MOSFET output transistor is on, the inductor

current (primary side of the transformer) is

monitored with a SenseFET technique and

converted into a voltage V

current. When V

output voltage error) the pow e r swi tch i s swi tched

reaches V

S

proportional to this

S

(the amplified

COMP

off. Thus, the outer voltage control loop defines

the level at which the inner loop regulat es peak

current thro ugh the pow er swi tch and the p rimary

winding of the transformer.

Excellent D.C. open loop and dynamic line

regulation is ensured due to the inherent input

voltage feedforward characteristic of the current

mode control. This results in an improved line

regulation, instantaneous correction to line

changes and better stability for the voltage

regulation loop.

Current mode topology also ensures good

limitation in the case of short circuit. During the

first phase the output current increases slowly

following the dynamic of the regulation loop. Then

it reaches the maximum limitation current

internally s et an d f inal ly sto ps because t he power

supply on V

applications the max imum peak current internally

is no long er correct. For specific

DD

set can be overridden by limiting the voltage

excursion externally on the COMP pin. An

integrated blanking filter inhibits the PWM

comparator output for a short time after the

integrated Power MOSFET is switched on. This

function prevents anomalous or premature

termination o f the switching pulse in the case of

current spikes caused by primary side capacitance

or secondary side rectifier reverse recovery time.

STAND-BY MODE

Stand-by operation in nearl y open load condition

automatically leads to a burst mode operation

allowing voltage regulation on the secondary side.

The transition from normal operation to burst

mode operation happe ns for a power P

by:

2

1

P

STBY

---

=

LPI

2

STBY

F

SW

STBY

given

Where:

L

is the primary inductance of the transformer.

P

is the normal switching frequency.

F

SW

I

is the minimum controllable current,

STBY

corresponding to the minimum on time that the

device is able to provide in normal operation. This

current can be computed as:

+

tbt

()V

d

I

STBY

+ td is the sum of the blanking time and of the

t

b

propagation time of the internal current sense and

--------------------------------

=

IN

L

P

comparator, and roughly represents th e minimu m

on time of the device. Note that P

affected by the effi ciency of the converter at low

STBY

may be

load, and must include the power drawn on the

primary auxiliary voltage.

As soon as the power goes below this limit , the

auxiliary secondary voltage starts to increase

above the 1 3V regulation level for cing the outp ut

voltage of the transconductance amplifier to low

state (V

the shutdown mode where the power switch is

COMP

< V

). This situation le ads to

COMPth

maintained in the off state, resulting in missing

cycles and zero duty cycle. As soon as V

back to the regulation level and the V

threshold is reached, the device op erates again.

gets

DD

COMPth

The above cycle repeats itself indefinitely,

providing a burst mode of which the effective duty

cycle is much lower than the minimum one when in

normal operation. The equivalent switching

frequency is also lower than the normal one,

leading to a reduced consumption on the input

mains lines. This mode of operation allows the

VIPer50/50A to meet the new German "Blue

Angel" Norm with less than 1W total power

consumption for the system when working in

stand-by. The output voltage remains regulated

around the normal level, with a low frequency

ripple corresponding to the burst mode. The

amplitude of this ripple is low, because of the

output capacitors and because of the low output

current drawn in such conditions. The normal

operation resumes a utomatical ly when the power

gets back levels which are higher than P

STBY

.

HIGH VOLTAGE START-UP CURRENT

SOURCE

An integrated high voltage current source provides

a bias current from the DRAIN pin during the startup phase. This current is partially absorbed by

internal control circuits which are placed into a

standby mode with redu ced consum ption and are

also provided to the externa l capaci tor connect ed

to the V

reaches the high voltage threshold V

pin. As so on a s the volt ag e on this pin

DD

DDon

of the

12/23

VIPer50/SP - VIPer50A/ASP

UVLO logic, the device turns into active mode and

starts switching.

The start up current generator is switched off, and

the converter sho ul d nor mall y pro vid e the ne eded

current on the V

winding of the transformer, as shown on figure 15.

pin through the auxiliary

DD

In case of abnormal condition where the auxiliary

winding is unable to provide the low voltage supply

current to the V

output of the converter), the external capacitor

pin (i.e. short circuit on the

DD

discharges itself down to the low threshold voltage

V

of the UVLO logic, and the device gets back

DDoff

to the inactive state where the internal circuits are

in standby mode and the start up current source is

activated. The converter enters an endless start

up cycle, with a start-up duty cycle def ined by the

ratio of charging current towards discharging when

the VIPer50/50A tries to start. This ratio is fixed by

design from 2 to 15, whic h gives a 12% st art up

duty cycle while the power dissipa tion at start up is

approximately 0.6 W, for a 230 Vrms input voltage.

This low value of start-up duty cycle prevents the

stress of the output rectifiers and of the

transformer when in short circuit.

The exter nal capacitor C

be sized according to the time needed by the

on the VDD pin must

VDD

converter to start up, when the device starts

switching. This time t

parameters, among which transformer design,

depends on many

SS

output capacitors, soft start feature and

compensation network implemented on the COMP

pin. The following formula can be used for defining

the minimum capacitor needed:

IDDt

SS

C

VDD

------------------------- -

>

V

DDhyst

where:

I

is the consumption current on the VDD pin

DD

when switching. R efer to specified I

values.

t

is the start up time of the co nverter when the

SS

device begins to switch. Worst case is generally at

DD1

and I

DD2

full load.

V

logic. Refer to the minimum specified value.

is the voltage hysteresis of the UVLO

DDhyst

Soft start feature can be implemented on the

COMP pin through a simple capa citor which will

also be used as the compensation network. In this

case, the regu lation lo op bandwi dth is ra ther l ow,

because of the large value of this capacitor. In

case of a large regulation loop bandwidth is

mandatory, the schematics in figure 16 can be

used. It mixes a high performance compensation

network together w ith a separate high value soft

start capacitor. Both soft start time an d regulati on

loop bandwidth can be adjusted separately.

If the device i s intentio nally shut d own by putti ng

the COMP pin to ground, the device is also

performing start-up cycles, and the V

oscillating between V

DDon

and V

DDoff

voltage is

DD

.

This voltage can be used for supplying external

functions, provided that their consumption doesn’t

exceed 0.5mA. Figure 17 shows a typical

application of this function, with a latched shut

down. Once the "Shutdown" signal has been

activated, the de vice re mains in the off state unti l

the input voltage is removed.

Figure 15: Behavior of the high voltage current source at start-up

VDD

VDDon

VDDoff

t

Auxiliary primary

winding

2 mA

15 mA

CVDD

VDD

15 mA1 mA

Ref.

UNDERVOLTAGE

LOCK OUT LOGIC

VIPer50

Start up duty cycle ~ 12%

3 mA

DRAIN

SOURCE

FC00320

13/23

VIPer50/SP - VIPer50A/ASP

TRANSCONDUCTANCE ERROR AMPLIFIER

The VIPer50/50A includes a transconductance

error amplifier. Transconductance Gm is the

change in output current (I

input voltage (V

∂I

COMP

m

------------------------

=

∂V

G

DD

). Thus:

DD

The output impedance Z

amplifier (COMP pin) can be defined as:

∂V

COMP

---------------------------

Z

COMP

==

∂I

COMP

) versus change in

COMP

at the output of this

COMP

∂ V

1

---------

G

m

COMP

---------------------------

×

∂V

DD

This last equation show s that the open loop gain

can be related to Gm and Z

A

VOL

A

= Gm x Z

VOL

COMP

COMP

:

where Gm value for VIPer50/50A is 1.5 mA/V

typically.

G

is well defined by specification, but Z

m

therefore A

impedance Z can be connected between the

are subject to large tolerances. An

VOL

COMP

and

COMP pin and ground in order to define more

accurately the transfer function F of the error

amplifier, according to the following equation, very

similar to the one above:

F

= Gm x Z(S)

(S)

The error amplifier frequency response is reported

in figure 10 for different values of a simple

resistance connected on the COMP pin. The

unloaded tr anscon ductance er ror amp lifier s hows

an int e r na l Z

impedance can be connected on the COMP pin to

of about 330 KΩ. More complex

COMP

achieve differ ent compensation laws. A capaci tor

will provide an integrator function, thus eliminating

the DC static error, and a resistance in series

leads to a flat gain at hi gher fre quency , insuri ng a

correct phase margin. This configuration is

illustrated in figure 18.

As shown in figu re 18 an a dditiona l noise fil tering

capacitor o f 2.2 nF is general ly needed to avoid

any high frequency interference.

It can also be interesting to implement a slope

compensation when working in c ontinuous mode

with duty cycle higher than 50%. Figur e 19 shows

such a conf iguration. Note that R1 and C2 build

the classical compensation network, and Q1 is

injecting the slope comp ensation with the correct

polarity from the oscillator sawtooth.

EXTERNAL CLOCK SYNCHRONIZATION

The OSC pin provides a synchronisation

capability, when connected to an external

frequency so urce. Figure 2 0 shows one poss ible

schematic to be adapted depending on the

specific needs. If the proposed schematic is used,

the pulse duration must be kept at a low value

(500ns is sufficient) for minimizing con sumption.

The optocoupler must be able to provide 20mA

through the optotransistor.

PRIMARY PEAK CURRENT LIMITATION

The primary I

effect, the outp ut power can be limited using t he

current and, as resulting

DPEAK

simple circuit shown in figure 21. The circuit based

on Q1, R

and R2 clamps the voltage on the

1

Figure 16: Mixed Soft Start and Compensation Figure 17: Latched Shut Down

D2

C2

+

D3

R3

R2

FC00331

AUXILIARY

WINDING

Shutdown

R1

Q2

R4

OSC

R2R3

Q1

VIPer50

-

OSC

13V

+

C4

C3

+

DRAINVDD

COMP SOURCE

R1

C1

D1

VIPer50

-

13V

+

D1

DRAINVDD

COMP SOURCE

FC00340

14/23

VIPer50/SP - VIPer50A/ASP

-

+

13V

OSC

COMP SOURCE

DRAINVDD

VIPer50

R1

C1

FC00351

C2

COMP pin in order to limit the primary peak current

of the device to a value:

–

0.5

H

ID

I

DPEAK

V

COMP

-------------------------------------

=

where:

+

R1R

2

0.6

--------------------- -

×

R

2

is in the range of

1+R2

V

COMP

=

The suggeste d value for R

220KΩ.

Figure 18: Typical Compensation Network

OVER-TEMPERATURE PROTECTION:

Over-temperature protection is based on chip

temperature sensing. The minimum junction

temperature at which over-temperature cut-out

occurs is 140ºC while the typical v alue is 170ºC.

The device is automatically restarted when the

junction temperature decreases to the restart

temperature th resho ld that i s t y pical ly 40ºC below

the shutdown value (see figure 8).

Figure 19: Slope Compensation

R1R2

OSC

13V

C2

VIPer50

+

DRAINVDD

COMP SOU RCE

Figure 20: External Clock Synchronization

OSC

Ω

10 k

13V

VIPer50

+

DRAINVDD

COMP SOURCE

FC00370

Q1

C1 R3

C3

FC00361

Figure 21: Current Limitation Circuit Example

VIPer50

DRAINVDD

COMP SOURCE

Q1

FC00380

OSC

13V

-

+

R1

R2

15/23

Figure 22: Input Volta ge Surg es Protecti on

VIPer50/SP - VIPer50A/ASP

R2

39R

13V

VDD

+

C1

Bulk capacitor

ELECTRICAL OVER STRESS RUGGEDNESS

C2

22nF

OSC

VIPerXX0

The VIPer may be submitted to electrical over

stress caused by violent input voltage surges or

lightning. Following the enclosed Layout

Considerations chapter rules is the most of the

time sufficient to prevent catastrophic damages,

however in some cases the voltage surges

coupled through the transformer auxiliary winding

R1

(Optional)

D1

Auxilliary winding

DRAIN

COMP SOURCE

can overpass the VDD pin absolute maximum

rating voltag e valu e. Such ev ents may trigg er the

VDD internal protection circuitry which could be

damaged by the strong discharge current of the

VDD bulk capacitor . T he si mp le R C fi lter s hown in

figure 22 can be implemented to improve the

application immunity to such surges.

16/23

Figure 23: Re comme nded Layout

VIPer50/SP - VIPer50A/ASP

)URPLQSXW

GLRGHVEULGJH

R1

C1

1

C2

OSC

U1

VIPerXX0

13V

ISO1

2

+

COMP SOURCE

R2

C3

C4

LAYOUT CONSIDERATIONS

Some simple rules insure a correct running of

switching pow er suppli es. They m ay be class ified

into two categories:

- To minimize power loops: the way the switched

power curre nt must be carefull y analyzed and

the corresponding paths must present the

smallest p ossible inner loop area. This avoids

radiated EMC noises, conducted EMC noises

by magnetic coupling, and provides a better

efficiency by eliminating parasitic i nductances,

especially on secondary side.

T1

D2

3

DRAINVDD

C5

4

5

D1

7RVHFRQGDU\

C7

ILOWHULQJDQGORDG

C6

FC00500

- To use different tracks for low level signals and

power ones. T he in terference s due to a mi xing

of signal and power may result in instabilities

and/or anomalous behavior of the device in

case of violent power surge (Input overvoltages,

output short circuits...).

In case of VIPer, these rules apply as shown i n

figure 23. The loops C1-T1-U1, C5-D2-T1, C7-D1T1 must be minimized. C6 must be as close as

possible to T1. The sign al compon ents C2, ISO1,

C3 and C4 use a dedicated track to be connected

directly to the source of the device.

17/23

1

VIPer50/SP - VIPer50A/ASP

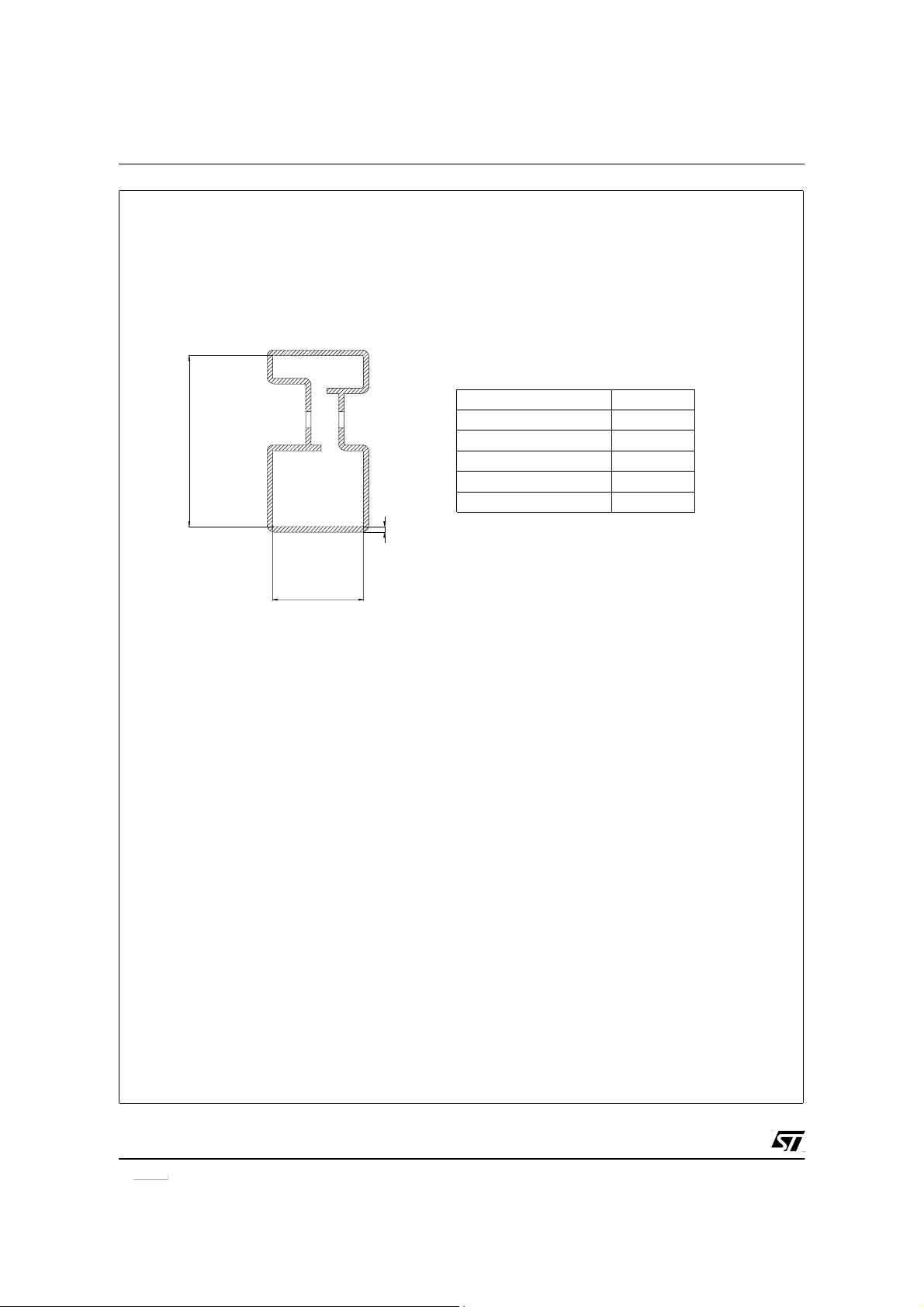

PowerSO-10™ MECHANICAL DATA

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

mm. inch

A 3.35 3.65 0.132 0.144

A (*) 3.4 3.6 0.134 0.142

A1 0.00 0.10 0.000 0.004

B 0.40 0.60 0.016 0.024

B (*) 0.37 0.53 0.014 0.021

C 0.35 0.55 0.013 0.022

C (*) 0.23 0.32 0.009 0.0126

D 9.40 9.60 0.370 0.378

D1 7.40 7.60 0.291 0.300

E 9.30 9.50 0.366 0.374

E2 7.20 7.60 0.283 300

E2 (*) 7.30 7.50 0.287 0.295

E4 5.90 6.10 0.232 0.240

E4 (*) 5.90 6.30 0.232 0.248

e 1.27 0.050

F 1.25 1.35 0.049 0.053

F (*) 1.20 1.40 0.047 0.055

H 13.80 14.40 0.543 0.567

H (*) 13.85 14.35 0.545 0.565

h 0.50 0.002

L 1.20 1.80 0.047 0.070

L (*) 0.80 1.10 0.031 0.043

α 0º 8º 0º 8º

α (*) 2º 8º 2º 8º

(*) Muar only POA P013P

HE

h

A

F

A1

10

1

eB

0.25

D

= =

D1

= =

E2

DETAIL "A"

DETA IL "A"

B

0.10 A

SEATING

PLANE

A

C

α

B

E4

SEATING

PLANE

A1

L

P095A

18/23

VIPer50/SP - VIPer50A/ASP

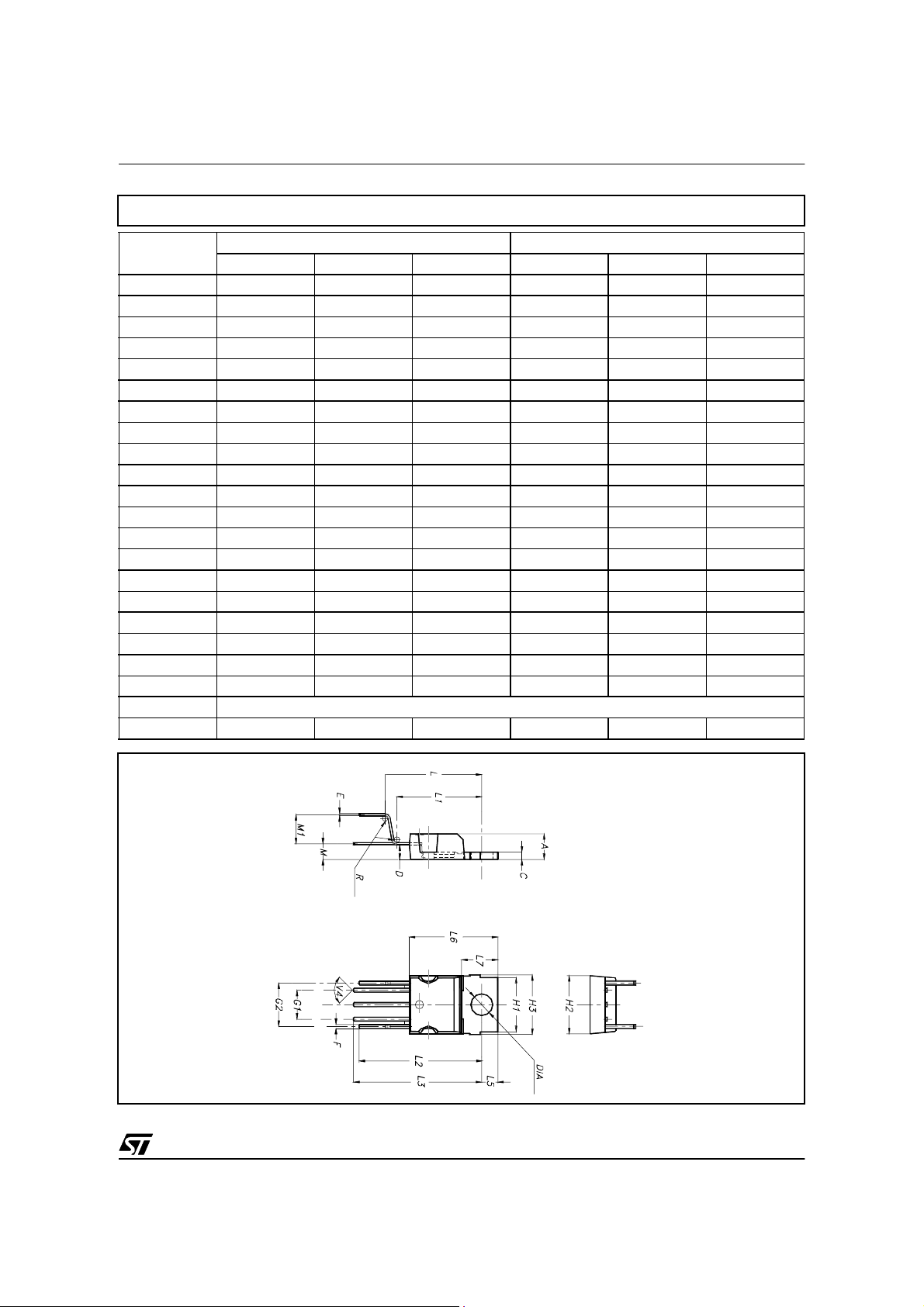

PENTAWATT HV MECHANICAL DATA

DIM.

A 4.30 4.80 0.169 0.189

C 1.17 1.37 0.046 0.054

D 2.40 2.80 0.094 0.11

E 0.35 0.55 0.014 0.022

F 0.60 0.80 0.024 0.031

G1 4.91 5.21 0.193 0.205

G2 7.49 7.80 0.295 0.307

H1

H2 10.40 0.409

H3

L 15.60 17.30 6.14 0.681

L1 14.60 15.22 0.575 0.599

L2 21.20 21.85 0.835 0.860

L3 22.20 22.82 0.874 0.898

L5 2.60 3 0.102 0.118

L6 15.10 15.80 0.594 0.622

L7 6 6.60 0.236 0.260

M 2.50 3.10 0.098 0.122

M1 4.50 5.60 0.177 0.220

R 0.50 0.02

V4 90° (typ)

Diam 3.65 3.85 0.144 0.152

MIN. TYP MAX. MIN. TYP. MAX.

9.30

mm. inch

9.70 0.366 0.382

10.05

10.40 0.396 0.409

P023H3

19/23

11

VIPer50/SP - VIPer50A/ASP

PENTAWATT HV 022Y (VERTICAL HIGH PITCH) MECHANICAL DATA

DIM.

MIN. TYP MAX. MIN. TYP. MAX.

mm. inch

A 4.30 4.80 0.169 0.189

C 1.17 1.37 0.046 0.054

D 2.40 2.80 0.094 0.110

E 0.35 0.55 0.014 0.022

F 0.60 0.80 0.024 0.031

G1 4. 91 5. 21 0.193 0.205

G2 7. 49 7. 80 0.295 0.307

H1 9.30 9.70 0.366 0.382

H2 10.40 0.409

H3 10.05 10. 40 0.396 0.40 9

L 16.42 17.42 0. 64 6 0.686

L1 14.60 15.22 0. 57 5 0.599

L3 20.52 21.52 0. 80 8 0.847

L5 2.60 3.00 0.102 0.118

L6 15.10 15.80 0. 59 4 0.622

L7 6.00 6.60 0.236 0.260

M 2.50 3.10 0.098 0.122

M1 5.00 5. 70 0.197 0.224

R 0.50 0.020

V4 90° 90°

Diam. 3.70 3.90 0.146 0.154

L

E

M1

M

R

Resin between

leads

G2

G1

V4

F

L1

A

D

L6

L3

C

L7

H2

H3

H1

L5

DIA

20/23

1

VIPer50/SP - VIPer50A/ASP

PowerSO-10™ SUGGESTED PAD LAYOUT

14.6 - 14.9

10.8 - 11

6.30

0.67 - 0.73

1

2

3

9.5

4

5

10

0.54 - 0.6

9

8

7

1.27

6

TAPE AND REEL SHIPMENT ( suffix “13TR”)

TUBE SHIPMENT (no suffix)

C

A

B

A

All dimensi ons ar e in mm.

Base Q.ty Bulk Q.ty Tube length (± 0. 5) A B C (± 0.1)

Casablanca 50 1000 532 10.4 16.4 0. 8

Muar 50 1000 532 4.9 17.2 0.8

MUARCASABLANCA

B

REEL DIMENSIONS

Base Q.ty 600

Bulk Q.ty 600

A (max) 330

B (min) 1.5

C (± 0.2) 13

F 20.2

G (+ 2 / -0) 24.4

N (min) 60

T (max) 30.4

C

TAPE DIMENSIONS

According to Electronic Industries Association

(EIA) Standard 481 rev. A, Feb. 1986

Tape width W 24

Tape Hole Spacing P0 (± 0.1) 4

Component Spacing P 24

Hole Diameter D (± 0.1/-0) 1.5

Hole Diameter D1 (min) 1.5

Hole Position F (± 0.05) 11.5

Compartm ent Depth K (max) 6.5

Hole Spacing P1 (± 0.1) 2

All dimensions are in mm.

Top

cover

tape

End

500mm min

All dimensions are in mm.

Empty components pockets

saled with cover tape.

User direction of feed

Start

No componentsNo components Components

500mm min

21/23

1

1

VIPer50/SP - VIPer50A/ASP

PENTAWATT HV TUBE SHIPMENT (no suffix)

B

A

Base Q.ty 50

Bulk Q.ty 1000

Tube length (± 0.5) 532

A 18

B 33.1

C

C (± 0.1) 1

All dimensions are in mm.

22/23

1

VIPer50/SP - VIPer50A/ASP

Information furnished is believ ed to be accurate and reliable. However, S TMicroelectronics ass um es no respons ibility for the con s equences

of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No license is

granted by implication or o therwise unde r any patent or pat ent rights of STMicroelec tronics. Specifications mentioned in this publication are

subject to c hange without notice. This public ation super s edes and replaces all information previous ly s upplied. STMicroelectroni c s pr oducts

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

Australia - Brazil - Canada - Ch ina - Finland - Fr anc e - Germany - Ho ng K ong - India - Israel - Italy - J apan - Malay s ia -

Malta - Moro c c o - S ingapore - Sp ain - Sweden - Sw itzerland - United Kingdom - U.S.A.

The ST logo is a trademark o f STMicroelectronics

2003 STMicroelectronics - Printed in ITALY- All Rights Reserved.

STMicroelectronics GROUP OF COMPANIES

http://www.st.com

23/23

1

Loading...

Loading...